SG75474中文资料

AO4704中文资料

AO4704AO4704SymbolTyp Max 28405475R θJL 2130SymbolTyp Max 36406775R θJL 2530Maximum Junction-to-LeadCSteady-State°C/WParameterUnits Maximum Junction-to-AmbientAt ≤ 10s R θJA °C/W Maximum Junction-to-AmbientASteady-State °C/W °C/W Maximum Junction-to-AmbientASteady-State Thermal Characteristics: Schottky Maximum Junction-to-Lead CSteady-State°C/WThermal Characteristics ParameterUnits Maximum Junction-to-AmbientAt ≤ 10s R θJA °C/W A: The value of R θJA is measured with the device mounted on 1in 2 FR-4 board with 2oz. Copper, in a still air environment with T A =25°C. The value in any given application depends on the user's specific board design. The current rating is based on the t ≤ 10s thermal resistance rating.B: Repetitive rating, pulse width limited by junction temperature.C. The R θJA is the sum of the thermal impedence from junction to lead R θJL and lead to ambient.D. The static characteristics in Figures 1 to 6 are obtained using 80 µs pulses, duty cycle 0.5% max.E. These tests are performed with the device mounted on 1 in 2 FR-4 board with 2oz. Copper, in a still air environment with T A =25°C. The SOA curve provides a single pulse rating.F. The Schottky appears in parallel with the MOSFET body diode, even though it is a separate chip. Therefore, we provide the net forward drop, capacitance and recovery characteristics of the MOSFET and Schottky. However, the thermal resistance is specified for each chip separately.Rev5: August 2005THIS PRODUCT HAS BEEN DESIGNED AND QUALIFIED FOR THE CONSUMER MARKET. APPLICATIONS OR USES AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS ARE NOT AUTHORIZED. AOS DOES NOT ASSUME ANY LIABILITY ARISINGOUT OF SUCH APPLICATIONS OR USES OF ITS PRODUCTS. AOS RESERVES THE RIGHT TO IMPROVE PRODUCT DESIGN,FUNCTIONS AND RELIABILITY WITHOUT NOTICE.AO4704SymbolMin TypMaxUnits BV DSS 30V0.0070.053.2101220I GSS 100nA V GS(th)0.6 1.12V I D(ON)40A 9.111.5T J =125°C13.316.510.513m Ωg FS 3037S V SD 0.450.5V I S5A DYNAMIC PARAMETERS C iss 36564050pF C oss 322pF C rss 168pF R g0.86 1.1ΩSWITCHING PARAMETERS Q g (4.5V)30.536nC Q gs 4.6nC Q gd 8.6nC t D(on) 6.29ns t r 4.87ns t D(off)5575ns t f 7.311ns t rr 20.325ns Q rr8.412.5nCTHIS PRODUCT HAS BEEN DESIGNED AND QUALIFIED FOR THE CONSUMER MARKET. APPLICATIONS OR USES AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS ARE NOT AUTHORIZED. AOS DOES NOT ASSUME ANY LIABILITY ARISING OUT OF SUCH APPLICATIONS OR USES OF ITS PRODUCTS. AOS RESERVES THE RIGHT TO IMPROVE PRODUCT DESIGN,FUNCTIONS AND RELIABILITY WITHOUT NOTICE.Gate resistanceGate Drain Charge Body Diode+Schottky Reverse Recovery ChargeI F =13A, dI/dt=100A/µsBody Diode+Schottky Reverse Recovery Time Turn-Off DelayTime V GS =10V, V DS =15V, R L =1.1Ω, R GEN =0ΩTurn-Off Fall TimeTotal Gate Charge Gate Source Charge I F =13A, dI/dt=100A/µs On state drain currentForward TransconductanceDiode + Schottky Forward Voltage I S =1A,V GS =0VV GS =4.5V, V DS =5V Turn-On DelayTime V GS =10V, V DS =15V, I D =13AV GS =0V, V DS =0V, f=1MHzTurn-On Rise Time Electrical Characteristics (T J =25°C unless otherwise noted)STATIC PARAMETERS Parameter Conditions I DSS mA Gate Threshold Voltage Drain-Source Breakdown Voltage I D =250µA, V GS =0VZero Gate Voltage Drain Current.(Set by Schottky leakage)Gate-Body leakage current V DS =V GS I D =250µA V R =30VV DS =0V, V GS = ±12V R DS(ON)Static Drain-Source On-Resistancem ΩV GS =4.5V, I D =12.2AV GS =10V, ID=13AV R =30V, T J =125°CV R =30V, T J =150°C Reverse Transfer Capacitance V DS =5V, I D =13AOutput Capacitance (FET+Schottky)Maximum Body-Diode + Schottky Continuous CurrentV GS =0V, V DS =15V, f=1MHz Input Capacitance A: The value of R θJA is measured with the device mounted on 1in 2 FR-4 board with 2oz. Copper, in a still air environment with T A =25°C. The value in any given application depends on the user's specific board design. The current rating is based on the t ≤ 10s thermal resistance rating.B: Repetitive rating, pulse width limited by junction temperature.C. The R θJA is the sum of the thermal impedence from junction to lead R θJL and lead to ambient.D. The static characteristics in Figures 1 to 6 are obtained using 80 µs pulses, duty cycle 0.5% max.E. These tests are performed with the device mounted on 1 in 2 FR-4 board with 2oz. Copper, in a still air environment with T A =25°C. The SOA curve provides a single pulse rating.F. The Schottky appears in parallel with the MOSFET body diode, even though it is a separate chip. Therefore, we provide the net forward drop, capacitance and recovery characteristics of the MOSFET and Schottky. However, the thermal resistance is specified for each chip separately Rev5: August 2005.AO4704AO4704。

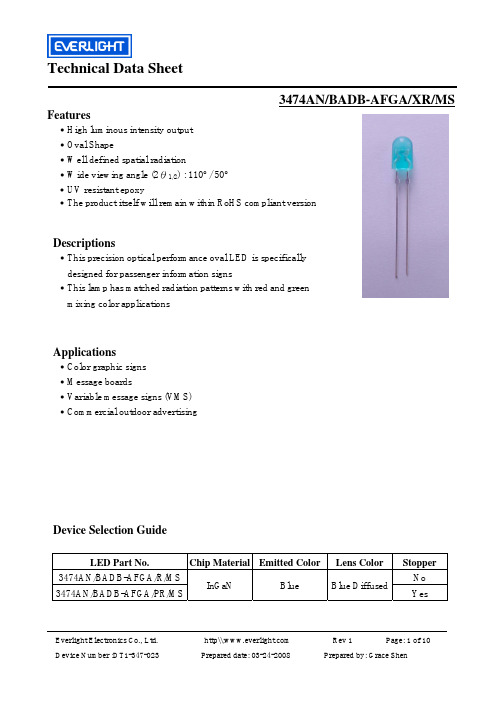

3474AN资料

元器件交易网Technical Data Sheet3474AN/BADB-AFGA/XR/MSFeatures․High luminous intensity output ․Oval Shape ․Well defined spatial radiation ․Wide viewing angle (2θ1/2) : 110o / 50o ․UV resistant epoxy ․The product itself will remain within RoHS compliant versionDescriptions․This precision optical performance oval LED is specifically designed for passenger information signs ․This lamp has matched radiation patterns with red and green mixing color applicationsApplications․Color graphic signs ․Message boards ․Variable message signs (VMS) ․Commercial outdoor advertisingDevice Selection GuideLED Part No. 3474AN/BADB-AFGA/R/MS 3474AN/BADB-AFGA/PR/MS Chip Material Emitted Color InGaN Blue Lens Color Blue Diffused Stopper No YesEverlight Electronics Co., Ltd. Device Number :DT1-347-023http\\: Prepared date: 03-24-2008Rev 1Page: 1 of 10Prepared by: Grace Shen元器件交易网Technical Data Sheet3474AN/BADB-AFGA/XR/MSPackage Dimensions Stopper Type No Stopper TypeNotes: ․All dimensions are in millimeters, tolerance is 0.25mm except being specified. ․Protruded resin under flange is 1.5mm Max LED. ․Bare copper alloy is exposed at tie-bar portion after cutting.Everlight Electronics Co., Ltd. Device Number :DT1-347-023 http\\: Prepared date: 03-24-2008 Rev 1 Page: 2 of 10Prepared by: Grace Shen元器件交易网Technical Data Sheet3474AN/BADB-AFGA/XR/MSAbsolute Maximum Rating (Ta=25℃)Parameter Forward Current Pulse Forward Current (Duty1/10@ 1KHz) Operating Temperature Storage Temperature Soldering Temperature Power Dissipation Reverse Voltage Electrostatic Discharge Symbol IF IFP Topr Tstg Tsol Pd VR ESD Absolute Maximum Rating 30 100 -40 ~ +85 -40 ~ +100 260 100 5 1K Unit mA mA ℃ ℃ ℃ mW V VNotes: Soldering time≦5 seconds.Electro-Optical Characteristics (Ta=25℃)Parameter Luminous Intensity Viewing Angle Peak Wavelength Dominant Wavelength Spectrum Half width Forward Voltage Reverse Current Symbol IV 2θ1/2 λp λd Δλ VF IR Min. 430 --465 -2.8 -Typ. -X:110Y:50 468 470 26 --Max. 860 --475 -3.6 50 Unit mcd deg nm V μA ConditionIF=20mAVR=5VRank Combination (IF=20mA)Rank F1 F2 G1 600~720 G2 720~860 Unit:mcd Luminous Intensity 430~520 520~600 *Measurement Uncertainty of Luminous Intensity: ±10% Rank 1 2 Unit:nmDominant Wavelength 465~470 470~475 *Measurement Uncertainty of Dominant Wavelength ±1.0nmEverlight Electronics Co., Ltd. Device Number :DT1-347-023http\\: Prepared date: 03-24-2008Rev 1Page: 3 of 10Prepared by: Grace Shen元器件交易网Technical Data Sheet3474AN/BADB-AFGA/XR/MSTypical Electro-Optical Characteristics CurvesEverlight Electronics Co., Ltd. Device Number :DT1-347-023http\\: Prepared date: 03-24-2008Rev 1Page: 4 of 10Prepared by: Grace Shen元器件交易网Technical Data Sheet3474AN/BADB-AFGA/XR/MSTaping DimensionsEverlight Electronics Co., Ltd. Device Number :DT1-347-023http\\: Prepared date: 03-24-2008Rev 1Page: 5 of 10Prepared by: Grace Shen元器件交易网Technical Data Sheet3474AN/BADB-AFGA/XR/MSTaping Sizes Specifications Symbol Items Tape Feed Hole Diameter Component Lead Pitch Front-to-Read Deflection Feed Hole to Button of Component Feed Hole to Overall Component Height Lead Length after Component Removal Feed Hole Pitch Lead Location Center of Component Location Overall Taped Package Thickness Feed Hole Location Adhesive Tape Width Adhesive Tape Position Tape Width Symbol mm D F △H H1 H2 L P P1 P2 T W0 W1 W2 W3 4.00 2.54 2.0 18.5 24.6 11.00 12.70 5.10 6.35 1.42 9.00 13.00 4.00 18.00 Avg. Inch 0.157 0.100 0.078 0.729 0.969 0.433 0.500 0.200 0.250 0.056 0.354 0.512 0.157 0.709 Tolerance (mm) ±0.2 ±0.3 Max ±1.0 ±1.0 Max ±0.3 ±0.7 ±1.2 Max ±0.5 ±0.5 Max ±0.75Everlight Electronics Co., Ltd. Device Number :DT1-347-023http\\: Prepared date: 03-24-2008Rev 1Page: 6 of 10Prepared by: Grace Shen元器件交易网Technical Data Sheet3474AN/BADB-AFGA/XR/MSPacking Specification■Inner Carton EVERLIGHT CPN: P/N:XXXXXXXXXXRoHSXXX/XXXX-XXXX QTY:XXXXCAT:XX HUE:XX REF:XXLOT NO: MADE IN TAIWAN■Label Form Specification CPN: Customer’s Production Number P/N : Production Number QTY: Packing Quantity CAT: Rank of Luminous Intensity HUE: Rank of Dominant Wavelength REF: Reference LOT No: Lot Number MADE IN TAIWAN: Production Place■Outside Carton■Packing Quantity 1. 2500 PCS/1 Inner Carton 2. 10Inner Cartons/1 Outside CartonEverlight Electronics Co., Ltd. Device Number :DT1-347-023http\\: Prepared date: 03-24-2008Rev 1Page: 7 of 10Prepared by: Grace Shen元器件交易网Technical Data Sheet3474AN/BADB-AFGA/XR/MSNotes1. Lead Forming During lead formation, the leads should be bent at a point at least 3mm from the base of the epoxy bulb. Lead forming should be done before soldering. Avoid stressing the LED package during leads forming. The stress to the base may damage the LED’s characteristics or it may break the LEDs. Cut the LED leadframes at room temperature. Cutting the leadframes at high temperatures may cause failure of the LEDs. When mounting the LEDs onto a PCB, the PCB holes must be aligned exactly with the lead position of the LED. If the LEDs are mounted with stress at the leads, it causes deterioration of the epoxy resin and this will degrade the LEDs. 2. Storage The LEDs should be stored at 30°C or less and 70%RH or less after being shipped from Everlight and the storage life limits are 3 months. If the LEDs are stored for 3 months or more, they can be stored for a year in a sealed container with a nitrogen atmosphere and moisture absorbent material. Please avoid rapid transitions in ambient temperature, especially, in high humidity environments where condensation can occur. 3. Soldering Careful attention should be paid during soldering. When soldering, leave more then 3mm from solder joint to epoxy bulb, and soldering beyond the base of the tie bar is recommended. Recommended soldering conditions: Hand Soldering Temp. at tip of iron Soldering time Distance 300℃ Max. (30W Max.) 3 sec Max. 3mm Min.(From solder joint to epoxy bulb) Preheat temp. Bath temp. & time Distance DIP Soldering 100℃ Max. (60 sec Max.) 260 Max., 5 sec Max 3mm Min. (From solder joint to epoxy bulb)Rev 1 Page: 8 of 10Everlight Electronics Co., Ltd. Device Number :DT1-347-023http\\: Prepared date: 03-24-2008Prepared by: Grace Shen元器件交易网Technical Data Sheet3474AN/BADB-AFGA/XR/MSRecommended soldering profilelaminar waveFluxingPreheadAvoiding applying any stress to the lead frame while the LEDs are at high temperature particularly when soldering. Dip and hand soldering should not be done more than one time After soldering the LEDs, the epoxy bulb should be protected from mechanical shock or vibration until the LEDs return to room temperature. A rapid-rate process is not recommended for cooling the LEDs down from the peak temperature. Although the recommended soldering conditions are specified in the above table, dip or handsoldering at the lowest possible temperature is desirable for the LEDs. Wave soldering parameter must be set and maintain according to recommended temperature and dwell time in the solder wave. 4. Cleaning When necessary, cleaning should occur only with isopropyl alcohol at room temperature for a duration of no more than one minute. Dry at room temperature before use. Do not clean the LEDs by the ultrasonic. When it is absolutely necessary, the influence of ultrasonic cleaning on the LEDs depends on factors such as ultrasonic power and the assembled condition. Ultrasonic cleaning shall be pre-qualified to ensure this will not cause damage to the LED.Everlight Electronics Co., Ltd. Device Number :DT1-347-023http\\: Prepared date: 03-24-2008Rev 1Page: 9 of 10Prepared by: Grace Shen元器件交易网Technical Data Sheet3474AN/BADB-AFGA/XR/MS5. Heat Management Heat management of LEDs must be taken into consideration during the design stage of LED application. The current should be de-rated appropriately by referring to the de-rating curve found in each product specification. The temperature surrounding the LED in the application should be controlled. Please refer to the data sheet de-rating curve. 6. ESD (Electrostatic Discharge) Electrostatic discharge (ESD) or surge current (EOS) can damage LEDs. An ESD wrist strap, ESD shoe strap or antistatic gloves must be worn whenever handling LEDs. All devices, equipment and machinery must be properly grounded. Use ion blower to neutralize the static charge which might have built up on surface of the LEDs plastic lens as a result of friction between LEDs during storage and handing. 7. Other Above specification may be changed without notice. EVERLIGHT will reserve authority on material change for above specification. When using this product, please observe the absolute maximum ratings and the instructions for using outlined in these specification sheets. EVERLIGHT assumes no responsibility for any damage resulting from use of the product which does not comply with the absolute maximum ratings and the instructions included in these specification sheets. These specification sheets include materials protected under copyright of EVERLIGHT corporation. Please don’t reproduce or cause anyone to reproduce them without EVERLIGHT’s consent.EVERLIGHT ELECTRONICS CO., LTD. Office: No 25, Lane 76, Sec 3, Chung Yang Rd, Tucheng, Taipei 236, Taiwan, R.O.CTel: 886-2-2267-2000, 2267-9936 Fax: 886-2267-6244, 2267-6189, 2267-6306 http:\\Everlight Electronics Co., Ltd. Device Number :DT1-347-023http\\: Prepared date: 03-24-2008Rev 1Page: 10 of 10Prepared by: Grace Shen。

744731471;中文规格书,Datasheet资料

4.1 4.0 3.02012-06-282012-05-102011-04-07SStSStCZSStCZWürth Elektronik eiSos GmbH & Co. KGEMC & Inductive SolutionsMax-Eyth-Str. 174638 WaldenburgGermanyTel. +49 (0) 79 42 945 - 0A Dimensions: [mm]F Typical Inductance vs. Current Characteristics:H4: Classification Wave Soldering Profile:H5: Classification Wave ProfileProfile FeaturePreheat- Temperature Min (T smin )- Temperature Typical (T stypical ) - Temperature Max (T smax ) - Time (t s ) from (T smin to T smax )Δ preheat to max Temperature Peak temperature (T p )Time of actual peak temperature (t p )Ramp-down rate - Min - Typical - MaxTime 25°C to 25°C Pb-Free Assembly 100°C 120°C 130°C 70 seconds 150°C max.250°C - 260°C max. 10 secondsmax. 5 second each wave ~ 2 K/s ~ 3.5 K/s ~ 5 K/s 4 minutesSn-Pb Assembly 100°C 120°C 130°C 70 seconds 150°C max.235°C - 260°C max. 10 secondsmax. 5 second each wave ~ 2 K/s ~ 3.5 K/s ~ 5 K/s 4 minutesrefer to EN 61760-1:2006H Soldering Specifications:I Cautions and Warnings:The following conditions apply to all goods within the product series of WE-TISof Würth Elektronik eiSos GmbH & Co. KG:General:All recommendations according to the general technical specifications of the data-sheet have to be complied with.The disposal and operation of the product within ambient conditions which probably alloy or harm the wire isolation has to be avoided.If the product is potted in customer applications, the potting material might shrink during and after hardening. Accordingly to this the product is exposed to the pressure of the potting material with the effect that the core, wire and termination is possibly damaged by this pressure and so the electrical as well as the mechanical characteristics are endanger to be affected. After the potting material is cured, the core, wire and termination of the product have to be checked if any reduced electrical or mechanical functions or destructions have occurred.The responsibility for the applicability of customer specific products and use in a particular customer design is always within the authority of the customer. All technical specifications for standard products do also apply for customer specific products.Washing varnish agent that is used during the production to clean the application might damage or change the characteristics of the wire in-sulation, the marking or the plating. The washing varnish agent could have a negative effect on the long turn function of the product.Direct mechanical impact to the product shall be prevented as the ferrite material of the core could flake or in the worst case it could break. Product specific:Follow all instructions mentioned in the datasheet, especially:•The solder profile has to be complied with according to the technical wave soldering specification, otherwise no warranty will be sustai-ned.•All products are supposed to be used before the end of the period of 12 months based on the product date-code, if not a 100% solderabi-lity can´t be warranted.•Violation of the technical product specifications such as exceeding the nominal rated current will result in the loss of warranty.1. General Customer ResponsibilitySome goods within the product range of Würth Elektronik eiSos GmbH & Co. KG contain statements regarding general suitability for certain application areas. These statements about suitability are based on our knowledge and experience of typical requirements concerning the are-as, serve as general guidance and cannot be estimated as binding statements about the suitability for a customer application. The responsibi-lity for the applicability and use in a particular customer design is always solely within the authority of the customer. Due to this fact it is up to the customer to evaluate, where appropriate to investigate and decide whether the device with the specific product characteristics described in the product specification is valid and suitable for the respective customer application or not.2. Customer Responsibility related to Specific, in particular Safety-Relevant ApplicationsIt has to be clearly pointed out that the possibility of a malfunction of electronic components or failure before the end of the usual lifetime can-not be completely eliminated in the current state of the art, even if the products are operated within the range of the specifications.In certain customer applications requiring a very high level of safety and especially in customer applications in which the malfunction or failure of an electronic component could endanger human life or health it must be ensured by most advanced technological aid of suitable design of the customer application that no injury or damage is caused to third parties in the event of malfunction or failure of an electronic component.3. Best Care and AttentionAny product-specific notes, warnings and cautions must be strictly observed.4. Customer Support for Product SpecificationsSome products within the product range may contain substances which are subject to restrictions in certain jurisdictions in order to serve spe-cific technical requirements. Necessary information is available on request. In this case the field sales engineer or the internal sales person in charge should be contacted who will be happy to support in this matter.5. Product R&DDue to constant product improvement product specifications may change from time to time. As a standard reporting procedure of the Product Change Notification (PCN) according to the JEDEC-Standard inform about minor and major changes. In case of further queries regarding the PCN, the field sales engineer or the internal sales person in charge should be contacted. The basic responsibility of the customer as per Secti-on 1 and 2 remains unaffected.6. Product Life CycleDue to technical progress and economical evaluation we also reserve the right to discontinue production and delivery of products. As a stan-dard reporting procedure of the Product Termination Notification (PTN) according to the JEDEC-Standard we will inform at an early stage about inevitable product discontinuance. According to this we cannot guarantee that all products within our product range will always be available. Therefore it needs to be verified with the field sales engineer or the internal sales person in charge about the current product availability ex-pectancy before or when the product for application design-in disposal is considered.The approach named above does not apply in the case of individual agreements deviating from the foregoing for customer-specific products.7. Property RightsAll the rights for contractual products produced by Würth Elektronik eiSos GmbH & Co. KG on the basis of ideas, development contracts as well as models or templates that are subject to copyright, patent or commercial protection supplied to the customer will remain with Würth Elektronik eiSos GmbH & Co. KG.8. General Terms and ConditionsUnless otherwise agreed in individual contracts, all orders are subject to the current version of the “General Terms and Conditions of Würth Elektronik eiSos Group”, last version available at .J Important Notes:The following conditions apply to all goods within the product range of Würth Elektronik eiSos GmbH & Co. KG:分销商库存信息: WURTH-ELECTRONICS 744731471。

744043151;中文规格书,Datasheet资料

description :A mmB mmC mmD mm Emm= Start of winding Marking = Inductance codeEigenschaften / properties Wert / valueEinheit / unittol.Induktivität /inductanceDC-Widerstand /DC-resistance DC-Widerstand /DC-resistance Nennstrom /rated currentSättigungsstrom /saturation current Eigenres.-Frequenz /self-res.-fequency33% Umgebungstemperatur / temperature:+20°CFerrit Endoberfläche / finishing electrode:CZ10-08-01ME 09-01-15MST08-04-11SSt08-05-20SST05-10-10Name Datum / dateKunde / customerFreigabe erteilt / general release:C Lötpad / soldering spec.:B Elektrische Eigenschaften / electrical properties:E Testbedingungen / test conditions:Luftfeuchtigkeit / humidity:It is recommended that the temperature of the part does F Werkstoffe & Zulassungen / material & approvals:Draht / wire:Class HG Eigenschaften / general specifications:Betriebstemp. / operating temperature: -40°C - + 125°C Sn/Ag/Cu - 96.5/3.0/0.5%DATUM / DATE : 2010-08-01max.mA Datum / date.................................................................................Unterschrift / signature Kontrolliert / approvedTestbedingungen / test conditions D-74638 Waldenburg · Max-Eyth-Strasse 1 - 3 · Germany · Telefon (+49) (0) 7942 - 945 - 0 · Telefax (+49) (0) 7942 - 945 - 400Geprüft / checked SRFMHzUmgebungstemp. / ambient temperature: -40°C - + 85°C Basismaterial / base material:not exceed 125°C under worst case operating conditions.POWER-CHOKE WE-TPCA Mechanische Abmessungen / dimensions:1,60 typ.1,60typ.2,8 ± 0,2HP 34401 A für/for R DC und I DC0,860± 30%150,00µH220R DC typ 0,770I DC D Prüfgeräte / test equipment:HP 4274 A für/for L und/and Q @ 20°C @ 20°C ∆T=30 K 100 kHZ / 0,1V4207,0I sat |ΔL/L|<35%Version 5.....................................................................................................................................................................................................................................................Würth Elektroniktyp.R DC max typ.L max.mA typ.Version 44,8 ± 0,24,8 ± 0,2Type 4828Änderung / modificationVersion 1Version 2Version 6[mm]5,302,001,502,001,80MarkingABCDDEdescription :CZ10-08-01ME 09-01-15MST08-04-11SSt08-05-20SST05-10-10Name Datum / dateFreigabe erteilt / general release:Kontrolliert / approvedDATUM / DATE : 2010-08-01Würth ElektronikKunde / customer...................................................................................................................................................................POWER-CHOKE WE-TPCH Induktivitätskurve / Inductance curve :Version 4Version 5Änderung / modificationVersion 1Version 2D-74638 Waldenburg · Max-Eyth-Strasse 1 - 3 · Germany · Telefon (+49) (0) 7942 - 945 - 0 · Telefax (+49) (0) 7942 - 945 - 400Datum / dateUnterschrift / signature Version 6 ...................................................................................................................................................................Geprüft / checked 0,0020,0040,0060,0080,00100,00120,00140,00160,000,000,100,200,300,400,500,600,70L (µH )Current (A)Induktivität vs Strom (typ.) / Inductance vs Current (typ.)description :I Rollenspezifikation / tape and reel specification:A 8,0± 1,0mm B4,00± 0,1mma178± 0,5mm b 20,20± 0,1mm+ 0,5- 1,0d 50,0± 1,0mmCZ10-08-01ME 09-01-15MST08-04-11SSt08-05-20SST05-10-10Name Datum / dateWürth Elektronik...................................................................................................................................................................Würth Elektronik eiSos GmbH & Co.KGD-74638 Waldenburg · Max-Eyth-Strasse 1 - 3 · Germany · Telefon (+49) (0) 7942 - 945 - 0 · Telefax (+49) (0) 7942 - 945 - 400Geprüft / checked Kontrolliert / approvedÄnderung / modification...................................................................................................................................................................Datum / dateUnterschrift / signature Gurtspezifikation / Tape specification: Rollenspezifikation / Reel specification:Freigabe erteilt / general release:Kunde / customermm 13,00POWER-CHOKE WE-TPCDATUM / DATE : 2010-08-01Version 5c Version 1Version 2Version 4Version 6Ø cadbThe force for tearing off cover tape is 20 to 70 grams in arrow direction150feeding directionThis electronic component has been designed and developed for usage in general electronic equipment. Before incorporating this component into any equipment where higher safety and reliability is especially required or if there is the possibility of direct damage or injury to human body, for example in the range of aerospace, aviation, nuclear control, submarine, transportation, (automotive control, train control, ship control),transportation signal, disaster prevention, medical, public information network etc, Würth Elektronik eiSos GmbH must be informed before the design-in stage. In addition, sufficient reliability evaluation checks for safety must be performed on every electronic component which is used in electrical circuits that require high safety and reliability functions or performance.分销商库存信息: WURTH-ELECTRONICS 744043151。

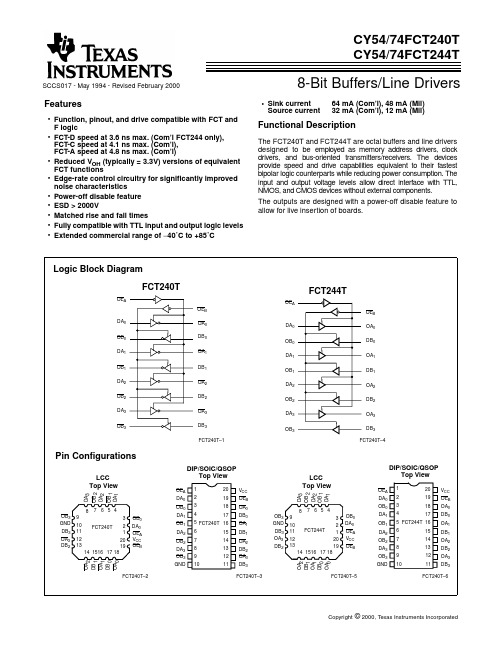

CY5474FCT240T中文资料

Power Dissipation .......................................................... 0.5W

Static Discharge Voltage............................................>2001V (per MIL-STD-883, Method 3015)

Electrical Characteristics Over the Operating Range

Parameter

Description

Test Conditions

Min. Typ.[5] Max. Unit

VOH

VOL

VIH VIL VH VIK II IIH IIL IOZH

Output HIGH Voltage

OEB OA0 DB0 OA1 DB1 OA2 DB2 OA3 DB3 FCT240T–1

FCT244T

OEA

OEB

DA0

OA0

OB0

DB0

DA1

OA1

OB1 DA2 OB2 DA3

DB1 OA2 DB2 OA3

OB3

DB3

FCT240T–4

Pin Configurations

LCC Top View

DA3

OB3 GND

DB3 OA3 DB2

8 7 654

9

3

10

2

11 FCT244T 1

12

20

13

19

14 1516 17 18

OB0 DA0 OEA VCC OEB

OA0

DB0

OA1

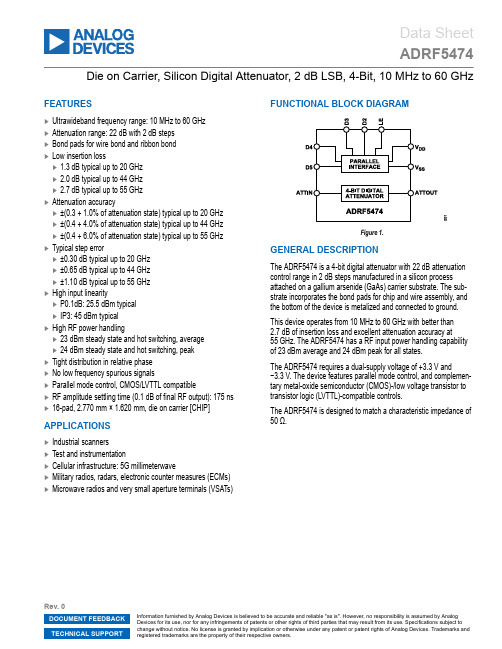

安寰科技 ADRF5474 芯片载板数据手册说明书

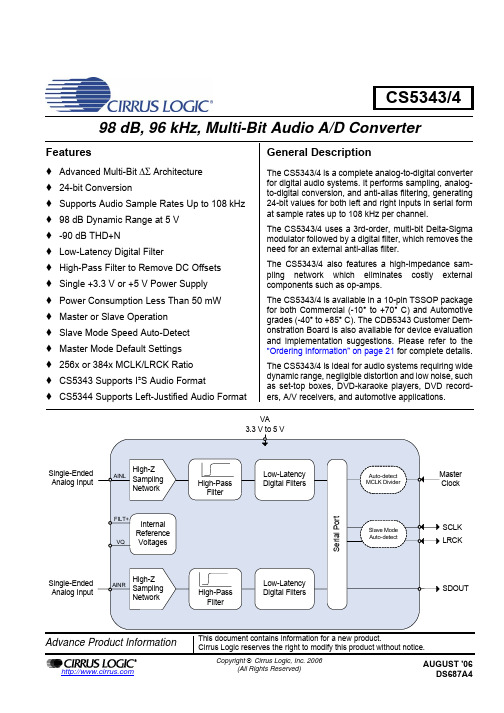

Data SheetADRF5474 Die on Carrier, Silicon Digital Attenuator, 2 dB LSB, 4-Bit, 10 MHz to 60 GHzFEATURES►Ultrawideband frequency range: 10 MHz to 60 GHz►Attenuation range: 22 dB with 2 dB steps►Bond pads for wire bond and ribbon bond►Low insertion loss►1.3 dB typical up to 20 GHz►2.0 dB typical up to 44 GHz►2.7 dB typical up to 55 GHz►Attenuation accuracy►±(0.3 + 1.0% of attenuation state) typical up to 20 GHz ►±(0.4 + 4.0% of attenuation state) typical up to 44 GHz ►±(0.4 + 6.0% of attenuation state) typical up to 55 GHz ►Typical step error►±0.30 dB typical up to 20 GHz►±0.65 dB typical up to 44 GHz►±1.10 dB typical up to 55 GHz►High input linearity►P0.1dB: 25.5 dBm typical►IP3: 45 dBm typical►High RF power handling►23 dBm steady state and hot switching, average►24 dBm steady state and hot switching, peak►Tight distribution in relative phase►No low frequency spurious signals►Parallel mode control, CMOS/LVTTL compatible►RF amplitude settling time (0.1 dB of final RF output): 175 ns ►16-pad, 2.770 mm × 1.620 mm, die on carrier [CHIP] APPLICATIONS►Industrial scanners►Test and instrumentation►Cellular infrastructure: 5G millimeterwave►Military radios, radars, electronic counter measures (ECMs)►Microwave radios and very small aperture terminals (VSATs)FUNCTIONAL BLOCK DIAGRAMFigure 1.GENERAL DESCRIPTIONThe ADRF5474 is a 4-bit digital attenuator with 22 dB attenuation control range in 2 dB steps manufactured in a silicon process attached on a gallium arsenide (GaAs) carrier substrate. The sub-strate incorporates the bond pads for chip and wire assembly, and the bottom of the device is metalized and connected to ground. This device operates from 10 MHz to 60 GHz with better than2.7 dB of insertion loss and excellent attenuation accuracy at55 GHz. The ADRF5474 has a RF input power handling capability of 23 dBm average and 24 dBm peak for all states.The ADRF5474 requires a dual-supply voltage of +3.3 V and−3.3 V. The device features parallel mode control, and complemen-tary metal-oxide semiconductor (CMOS)-/low voltage transistor to transistor logic (LVTTL)-compatible controls.The ADRF5474 is designed to match a characteristic impedance of 50 Ω.TABLE OF CONTENTSFeatures (1)Applications (1)Functional Block Diagram (1)General Description (1)Specifications (3)Electrical Specifications (3)Timing Specifications (4)Absolute Maximum Ratings (5)Thermal Resistance (5)Power Derating Curves (5)Electrostatic Discharge (ESD) Ratings (5)ESD Caution (6)Pad Configuration and Function Descriptions (7)Interface Schematics..........................................7Typical Performance Characteristics (8)Insertion Loss, Return Loss, State Error,Step Error, and Relative Phase (8)Input Power Compression and Third-OrderIntercept (10)Theory of Operation (11)Power Supply (11)RF Input and Output (11)Parallel Mode Interface (12)Applications Information (13)Die Assembly (13)Handling, Mounting and Epoxy Die Attach (13)Outline Dimensions (14)Ordering Guide (14)REVISION HISTORY5/2022—Revision 0: Initial VersionELECTRICAL SPECIFICATIONSV DD = 3.3 V, V SS = −3.3 V, control voltages = 0 V or V DD, die temperature (T DIE) = 25°C, and 50 Ω system, unless otherwise noted.S-parameters are measured with microstrip launchers and 3 mil width ribbon bonds using ground-signal-ground (GSG) probes. The launchers are deembeded. See the Applications Information section for assembly details.Table 1.Parameter Test Conditions/Comments Min Typ Max Unit FREQUENCY RANGE1060,000MHz INSERTION LOSS10 MHz to 20 GHz 1.3dB20 GHz to 44 GHz 2.0dB44 GHz to 55 GHz 2.7dB55 GHz to 60 GHz 4.0dB RETURN LOSS ATTIN and ATTOUT, all attenuation states10 MHz to 20 GHz13dB20 GHz to 44 GHz11dB44 GHz to 55 GHz9dB55 GHz to 60 GHz6dB ATTENUATIONRange Between minimum and maximum attenuation states22dBStep Size Between any successive attenuation states2dB Accuracy Referenced to insertion loss10 MHz to 20 GHz±(0.3 + 1.0% of state)dB20 GHz to 44 GHz±(0.4 + 4.0% of state)dB44 GHz to 55 GHz±(0.4 + 6.0% of state)dB55 GHz to 60 GHz±(0.4 + 12.0% of state)dBStep Error Between any successive state10 MHz to 20 GHz±0.30dB20 GHz to 44 GHz±0.65dB44 GHz to 55 GHz±1.10dB55 GHz to 60 GHz±1.30dB RELATIVE PHASE Referenced to insertion loss10 MHz to 20 GHz25Degrees20 GHz to 44 GHz60Degrees44 GHz to 55 GHz75Degrees55 GHz to 60 GHz85Degrees SWITCHING CHARACTERISTICS All attenuation states at input power (P IN) = 10 dBmRise and Fall Time (t RISE and t FALL)10% to 90% of RF output50nsOn and Off Time (t ON and t OFF)50% triggered control to 90% of RF output100nsRF Amplitude Settling Time0.1 dB50% triggered control to 0.1 dB of final RF output175ns0.05 dB50% triggered control to 0.05 dB of final RF output225ns Overshoot2dB Undershoot0.75dBRF Phase Settling Time Frequency = 40 GHz5°50% triggered control to 5° of final RF output105ns 1°50% triggered control to 1° of final RF output120ns INPUT LINEARITY1100 MHz to 50 GHz0.1 dB Power Compression (P0.1dB)25.5dbmTable 1.Parameter Test Conditions/Comments Min Typ Max Unit45dBm Third-Order Intercept (IP3)Two-tone P IN = 12 dBm per tone, Δf = 1 MHz, allattenuation statesDIGITAL CONTROL INPUTS LE, D2, D3, D4, and D5VoltageLow (V INL)00.8V High (V INH) 1.2 3.3V CurrentLow (I INL)–10µA High (I INH)<1µA SUPPLY CURRENTPositive Supply CurrentBias Low LE, D2, D3, D4, and D5 = 0 V52µA Bias High LE, D2, D3, D4, and D5 = 3.3 V2µA Negative Supply Current–110μA RECOMMENDED OPERATING CONDITIONSSupply VoltagePositive (V DD) 3.15 3.45V Negative (V SS)−3.45−3.15V Digital Control Voltage0V DD V RF Power Handling 2Frequency = 100 MHz to 50 GHz, T DIE3 = 85°C,4 allattenuation statesInput at ATTIN Steady state, average23dBmSteady state, peak24dBmHot switching, average23dBmHot switching, peak24dBm Input at ATTOUT Steady state, average15dBmSteady state, peak16dBmHot switching, average15dBmHot switching, peak16dBm T DIE3−40+105°C 1Input linearity performance degrades over frequency, see Figure 19 and Figure 22.2For power derating over frequency, see Figure 2 to Figure 3. Applicable for all ATTIN and ATTOUT power specifications.3T DIE refers to the bottom of the die on carrier.4For 105°C operation, the power handling degrades from the T DIE = 85°C specifications by 3 dB.TIMING SPECIFICATIONSSee Figure 24 for the timing diagrams.Table 2.Parameter Description Min Typ Max Unit t LEW Minimum LE pulse width, see Figure 2410ns t PH Hold time, see Figure 2410ns t PS Setup time, see Figure 242nsTable 3.Parameter RatingPositive Supply Voltage−0.3 V to +3.6 V Negative Supply Voltage−3.6 V to +0.3 VDigital Control InputsVoltage−0.3 V to V DD + 0.3 V Current 3 mARF Power1 (Frequency = 100 MHz to 50 GHz,T DIE = 85°C2)Input at ATTINSteady State, Average24 dBmSteady State, Peak25 dBmHot Switching, Average24 dBmHot Switching, Peak25 dBmInput at ATTOUTSteady State, Average16 dBmSteady State, Peak17 dBmHot Switching, Average16 dBmHot Switching, Peak17 dBmRF Power Under Unbiased Condition (V DD andV SS = 0 V)Input at ATTIN17 dBmInput at ATTOUT9 dBmTemperatureJunction (T J)135°CStorage−55°C to +150°C Processing170°CContinuous Power Dissipation (P DISS)0.20 W1For power derating over frequency, see Figure 2 and Figure 3. Applicable for all ATTIN and ATTOUT power specifications.2For 105°C operation, the power handling degrades from the T DIE = 85°C specifications by 3 dB.Stresses at or above those listed under absolute maximum ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operat-ing conditions for extended periods may affect product reliability.THERMAL RESISTANCEThermal performance is directly linked to printed circuit board (PCB) design and operating environment. Careful attention to PCB thermal design is required.θJC is the junction to case bottom (channel to carrier bottom) thermal resistance.Table 4. Thermal ResistancePackage TypeθJCUnitC-16-5250°C/W POWER DERATING CURVESFigure 2. Power Derating vs. Frequency, Low Frequency Detail, T DIE= 85°CFigure 3. Power Derating vs. Frequency, High Frequency Detail, T DIE = 85°C ELECTROSTATIC DISCHARGE (ESD) RATINGS The following ESD information is provided for handling of ESD-sen-sitive devices in an ESD protected area only.Human body model (HBM) per ANSI/ESDA/JEDEC JS-001.ESD Ratings for ADRF5474Table 5. ADRF5474, 16-Pad Die on Carrier [CHIP]ESD Model Withstand Threshold (V) Human Body Model (HBM)±250±250 for ATTIN and ATTOUT Pads±2000 for Supply and Control PadsESD CAUTIONP IN CONFIGURATION AND FUNCTION DESCRIPTIONSFigure 4. Pad ConfigurationTable 6. Pad Function Descriptions Pad No.Mnemonic Description1, 3, 4, 6, 7, 11, 16GND Ground. Bonding of these ground pads are optional. See the Applications Information section.2ATTIN Attenuator Input. No dc blocking capacitor is necessary when the RF line potential is equal to 0 V dc. See Figure 5 for the interface schematic.5ATTOUT Attenuator Output. No dc blocking capacitor is necessary when the RF line potential is equal to 0 V dc. See Figure 5 for the interface schematic.8V SS Negative Supply Input. See Figure 8 for the interface schematic.9V DD Positive Supply Input. See Figure 7 for the interface schematic.10LE Latch Enable Input. See the Theory of Operation section for more information. See Figure 6 for the interface schematic.12D2Parallel Control Input for 2 dB Attenuator Bit. See the Theory of Operation section for more information. See Figure 6 for the interface schematic.13D3Parallel Control Input for 4 dB Attenuator Bit. See the Theory of Operation section for more information. See Figure 6 for the interface schematic.14D4Parallel Control Input for 8 dB Attenuator Bit.See the Theory of Operation section for more information. See Figure 6 for the interface schematic.15D5Parallel Control Input for 8 dB Attenuator Bit. See the Theory of Operation section for more information. See Figure 6 for the interface schematic.Carrier BottomThe carrier bottom is gold metalized and must be directly attached to the ground plane using conductive epoxy.INTERFACE SCHEMATICSFigure 5. ATTIN and ATTOUT Interface SchematicFigure 6. Digital Input Interface Schematic (LE, D2, D3, D4, and D5)Figure 7. V DD Input Interface SchematicFigure 8. V SS Input Interface SchematicINSERTION LOSS, RETURN LOSS, STATE ERROR, STEP ERROR, AND RELATIVE PHASE V DD = 3.3 V, V SS = −3.3 V, control voltages = 0 V or V DD , T DIE = 25°C, and a 50 Ω system, unless otherwise noted.S-parameters are measured with microstrip launchers and 3 mil width ribbon bonds using GSG probes. The launchers are deembedded. See the Applications Informationsection for assembly details.Figure 9. Insertion Loss vs. Frequency over TemperatureFigure 10. Input Return Loss vs. FrequencyFigure 11. Normalized Attenuation vs. Frequency for All StatesFigure 12. Output Return Loss vs. FrequencyFigure 13. Step Error vs. FrequencyFigure 14. State Error vs. FrequencyFigure 15. Relative Phase vs. FrequencyFigure 16. Step Error vs. Attenuation State over FrequencyFigure 17. State Error vs. Attenuation State over FrequencyFigure 18. Relative Phase vs. Attenuation State over FrequencyINPUT POWER COMPRESSION AND THIRD-ORDER INTERCEPTV DD = 3.3 V, V SS = −3.3 V, control voltages = 0 V or V DD , T DIE= 25°C, and a 50 Ω system, unless otherwise noted.Figure 19. Input P0.1dB vs. FrequencyFigure 20. Input IP3 vs. FrequencyFigure 21. Input P0.1dB vs. Frequency, Low Frequency DetailFigure 22. Input IP3 vs. Frequency, Low Frequency DetailThe ADRF5474 incorporates a 4-bit fixed attenuator array that offers an attenuation range of 22 dB in 2 dB steps. An integrated driver provides parallel mode control of the attenuator array.The ADRF5474 has four digital control inputs, D2 (LSB) to D5 (MSB), to select the desired attenuation state in parallel mode, as shown in Figure 23. Internally, there are two 8 dB stages, and these stages can be controlled by the D4 and D5 pins.POWER SUPPLYThe ADRF5474 requires a positive supply voltage applied to theV DD pad and a negative supply voltage applied to the V SS pad. Bypassing capacitors are recommended on the supply lines to filter high frequency noise.The power-up sequence is as follows:1.Connect GND.2.Power up the V DD and V SS voltages. Power up V SS after V DD toavoid current transients on V DD during ramp up.3.Power up the digital control inputs. The order of the digitalcontrol inputs is not important. However, powering the digitalcontrol inputs before the V DD voltage supply can inadvertently forward bias and damage the internal ESD structures. To avoidthis damage, use a series 1 kΩ resistor to limit the currentflowing into the control pad.4.Apply an RF input signal to ATTIN or ATTOUT.The power-down sequence is the reverse order of the power-up sequence.Power-Up StateThe ADRF5474 has an internal pull-up resistor (see Figure 6). The internal pull-up resistor sets the attenuator to the maximum attenuation state (22 dB) when the V DD and V SS voltages are applied.RF INPUT AND OUTPUTBoth RF ports (ATTIN and ATTOUT) are dc-coupled to 0 V. No dc blocking is required at the RF ports when the RF line potential is equal to 0 V.The ADRF5474 supports bidirectional operation at a lower power level. The power handling of the ATTIN and ATTOUT ports are different. Therefore, the bidirectional power handling is defined by the ATTOUT port. Refer to the RF input power specifications in Table 1.Table 7. Truth TableDigital Control Input1Attenuation State (dB)D52D42D3D2Low Low Low Low0 (reference)Low Low Low High 2.0Low Low High Low 4.0Low Low High High 6.0Low High Low Low8.0Low High Low High10.0Low High High Low12.0Low High High High14.0High High Low Low16.0High High Low High18.0High High High Low20.0High High High High22.01Any combination of the control voltage input states shown in this table provides an attenuation equal to the sum of the bits selected. 2D4 and D5 both correspond to the 8 dB state. D4 has slightly better state accuracy at higher frequencies.Figure 23. Simplified Circuit DiagramPARALLEL MODE INTERFACEThe ADRF5474 has four digital control inputs, D2 (LSB) to D5 (MSB), to select the desired attenuation state in parallel mode, as shown in Table 7.There are two modes of parallel operation: direct parallel and latched parallel.Direct Parallel ModeTo enable direct parallel mode, keep the LE pad high. To change the attenuation state, use the control voltage inputs (D2 to D5) directly. Direct parallel mode is for manual control of the tched Parallel ModeTo enable latched parallel mode, the LE pad must be kept low when changing the control voltage inputs (D2 to D5) to set the attenuation state. When the desired state is set, toggle LE high to transferthe 4-bit data to the bypass switches of the attenuator array, and then toggle LE low to latch the change into the device until the next desired attenuation change (see Figure 24 and Table 2 foradditional information).Figure 24. Latched Parallel Mode Timing DiagramAPPLICATIONS INFORMATION DIE ASSEMBLYAn assembly diagram of the ADRF5474 is shown in Figure 25.Figure 25. Die Assembly DiagramThe ADRF5474 is designed to have the optimum RF input and output impedance match with 3 mil × 0.5 mil gold ribbon wire and 3 mil loop height typical. The bonding diagrams are shown in Figure 26 and Figure 27. Alternatively, using multiple wire bonds with equivalent inductance yields similar performance. For RF rout-ing from the device, coplanar wave guide or microstrip transmission lines can be used. No impedance matching is required on the transmission line pad because the device is designed to match internally to the recommended ribbon bond. A spacing of 3 mils from the RF transmission line to the device edge is recommended for optimum performance.DC pads can be connected using standard 1 mil diameter wire by keeping the wire lengths as short as possible to minimize the para-sitic inductance. The dc pads are large enough to accommodate ribbon bonds, if preferred.All bonds must be thermosonically bonded at a nominal stage temperature of 150°C, and a minimum amount of ultrasonic energy must be applied to achieve reliable bonds.The device is metalized on the backside, and the ground connec-tion can be done by attaching the device directly to the RF ground plane using a conductive epoxy. In this case, connecting the ground pads is optional but still recommended to ensure a solid groundconnection.Figure 26. Bonding Diagram Top ViewFigure 27. Bonding Diagram Side ViewHANDLING, MOUNTING AND EPOXY DIE ATTACHKeep devices in ESD protective sealed bags for shipment, and store all bare die in a dry nitrogen environment.For manual picking, it is a common practice to use a pair oftweezers for GaAs devices. However, for die on carrier devices, the use of a vacuum tool is recommended to avoid any damage on the device substrate. Handle these devices in clean environment.To attach the die with epoxy, apply an amount of epoxy to the mounting surface so that a thin epoxy fillet is observed around the perimeter of the chip after it is placed into position. Set epoxy cure temperatures per the recommendations of the manufacturer and the maximum ratings of the device to minimize accumulated mechanical stress after assembly.Because both dies are attached with solder joints, users must follow best practices for the thermomechanical design of their module assemblies. The temperature expansion coefficient of the substrate material must match the thermal expansion coefficient of the GaAs and silicon (Si) die. Do not allow warpage or other mechanical deformation on the substrate. Set the die attach process and the epoxy cure temperatures to lower the accumulated stress after assembly.OUTLINE DIMENSIONSFigure 28. 16-Pad Die on Carrier [CHIP](C-16-5)Dimensions shown in millimeters ORDERING GUIDEModel1Temperature Range Package Description Packing Information Package OptionADRF5474BCZ–40°C to +105°C16-Pad Die on Carrier [CHIP]Waffle Pack, 50C-16-5 ADRF5474BCZ-GP–40°C to +105°C16-Pad Die on Carrier [CHIP]Gel Pack, 50C-16-5 ADRF5474BCZ-SX–40°C to +105°C16-Pad Die on Carrier [CHIP]Waffle Pack, 2C-16-51Z = RoHS Compliant Part.。

7-36149-1资料

7-36149-1 Product DetailsHome | Customer Support | Suppliers | Site Map | Privacy Policy | Browser Support© 2008 Tyco Electronics Corporation All Rights Reserved SearchProducts Documentation Resources My Account Customer Support Home > Products > By Type > Product Feature Selector > Product Details7-36149-1Active View 3D PDF Ring and Spade Tongue TerminalsAlways EU RoHS/ELV Compliant (Statement of Compliance)Product Highlights:?Terminal Shape = Ring Tongue?Receptacle Style = Straight?Body Style = PIDG?Barrel Type = Closed Barrel?Wire/Cable Type = Regular WireView all Features | Find SimilarProductsCheck Pricing &AvailabilitySearch for ToolingProduct FeatureSelectorContact Us AboutThis ProductQuick LinksDocumentation & Additional InformationProduct Drawings:?TERMINAL, RING TONGUE, PIDG, WIRE SIZE, 22-16 AWG(PDF, English)Catalog Pages/Data Sheets:?STANDARD TERMINALS AND SPLICES(PDF, English)Product Specifications:?None AvailableApplication Specifications:?Pre-Insulated Diamond Grip (PIDG) Terminals, Splices...(PDF, English)Instruction Sheets:?None AvailableCAD Files: (CAD Format & Compression Information)?2D Drawing (DXF, Version U)?3D Model (IGES, Version U)?3D Model (STEP, Version U)List all Documents Additional Information:?Product Line InformationRelated Products:?ToolingProduct Features (Please use the Product Drawing for all design activity)Product Type Features:?Terminal Shape = Ring Tongue?Receptacle Style = Straight?Body Style = PIDG?Barrel Type = Closed Barrel?Wire/Cable Type = Regular Wire?Insulation = Yes?Insulation Support = Insulation Support?Insulation Diameter (mm [in]) = 3.18 [.125]Max.?Stud Size = 6 [M3.5]?Stud Diameter (mm [in]) = 3.68 [0.145]?Shape = RING-041?Heavy Duty = No?Material = Copper?Finish = Tin?Tongue Material Thickness (mm [in]) = 0.79[0.031]?Color Code = Red Electrical Characteristics:?Voltage (VAC) = 300Body Related Features:?Wire Range (mm [AWG]) = 0.50-0.60²[20] ?Wire Range (CMA) = 509 –3,260?Insulation Sleeve Material = NylonIndustry Standards:?Government/Industry Qualification = No?RoHS/ELV Compliance = RoHS compliant, ELVcompliant?Lead Free Solder Processes = Not relevant forlead free process?RoHS/ELV Compliance History = Always wasRoHS compliantPackaging Related Features:?Packaging Method = Loose PieceOther:?Brand = AMPProvide Website Feedback | Contact Customer Support。

74437349022;中文规格书,Datasheet资料

1.2 1.1 1.02012-06-282012-02-292011-10-01SStSStSStSStBDBDWürth Elektronik eiSos GmbH & Co. KGEMC & Inductive SolutionsMax-Eyth-Str. 174638 WaldenburgGermanyTel. +49 (0) 79 42 945 - 0A Dimensions: [mm]F Typical Inductance vs. Current Characteristics: F Typical Temperature rise vs. Current Characteristics:H1: Classification Reflow Profile for SMT components:H2: Classification Reflow ProfilesProfile FeaturePreheat- Temperature Min (T smin ) - Temperature Max (T smax ) - Time (t s ) from (T smin to T smax )Ramp-up rate (T L to T P )Liquidous temperature (T L )Time (t L ) maintained above T L Peak package body temperature (T p )Time within 5°C of actual peak temperature (t p )Ramp-down rate (T P to T L )Time 25°C to peak temperature Pb-Free Assembly 150°C 200°C60-180 seconds 3°C/ second max.217°C60-150 seconds See Table H320-30 seconds 6°C/ second max.8 minutes max.refer to IPC/JEDEC J-STD-020DH3: Package Classification Reflow TemperaturePB-Free Assembly PB-Free Assembly PB-Free Assembly Package Thickness< 1.6 mm 1.6 - 2.5 mm ≥ 2.5 mmVolume mm³<350260°C 260°C 250°CVolume mm³350 - 2000260°C 250°C 245°CVolume mm³>2000260°C 245°C 245°Crefer to IPC/JEDEC J-STD-020DH Soldering Specifications:I Cautions and Warnings:The following conditions apply to all goods within the product series of WE-LHMIof Würth Elektronik eiSos GmbH & Co. KG:General:All recommendations according to the general technical specifications of the data-sheet have to be complied with.The disposal and operation of the product within ambient conditions which probably alloy or harm the wire isolation has to be avoided.If the product is potted in customer applications, the potting material might shrink during and after hardening. Accordingly to this the product is exposed to the pressure of the potting material with the effect that the core, wire and termination is possibly damaged by this pressure and so the electrical as well as the mechanical characteristics are endanger to be affected. After the potting material is cured, the core, wire and termination of the product have to be checked if any reduced electrical or mechanical functions or destructions have occurred.The responsibility for the applicability of customer specific products and use in a particular customer design is always within the authority of the customer. All technical specifications for standard products do also apply for customer specific products.Washing varnish agent that is used during the production to clean the application might damage or change the characteristics of the wire in-sulation, the marking or the plating. The washing varnish agent could have a negative effect on the long turn function of the product.Direct mechanical impact to the product shall be prevented as the iron powder material of the core could flake or in the worst case it could break.Product specific:Follow all instructions mentioned in the datasheet, especially:•The solder profile has to be complied with according to the technical reflow soldering specification, otherwise no warranty will be sustai-ned.•All products are supposed to be used before the end of the period of 12 months based on the product date-code, if not a 100% solderabi-lity can´t be warranted.•Violation of the technical product specifications such as exceeding the nominal rated current will result in the loss of warranty.1. General Customer ResponsibilitySome goods within the product range of Würth Elektronik eiSos GmbH & Co. KG contain statements regarding general suitability for certain application areas. These statements about suitability are based on our knowledge and experience of typical requirements concerning the are-as, serve as general guidance and cannot be estimated as binding statements about the suitability for a customer application. The responsibi-lity for the applicability and use in a particular customer design is always solely within the authority of the customer. Due to this fact it is up to the customer to evaluate, where appropriate to investigate and decide whether the device with the specific product characteristics described in the product specification is valid and suitable for the respective customer application or not.2. Customer Responsibility related to Specific, in particular Safety-Relevant ApplicationsIt has to be clearly pointed out that the possibility of a malfunction of electronic components or failure before the end of the usual lifetime can-not be completely eliminated in the current state of the art, even if the products are operated within the range of the specifications.In certain customer applications requiring a very high level of safety and especially in customer applications in which the malfunction or failure of an electronic component could endanger human life or health it must be ensured by most advanced technological aid of suitable design of the customer application that no injury or damage is caused to third parties in the event of malfunction or failure of an electronic component.3. Best Care and AttentionAny product-specific notes, warnings and cautions must be strictly observed.4. Customer Support for Product SpecificationsSome products within the product range may contain substances which are subject to restrictions in certain jurisdictions in order to serve spe-cific technical requirements. Necessary information is available on request. In this case the field sales engineer or the internal sales person in charge should be contacted who will be happy to support in this matter.5. Product R&DDue to constant product improvement product specifications may change from time to time. As a standard reporting procedure of the Product Change Notification (PCN) according to the JEDEC-Standard inform about minor and major changes. In case of further queries regarding the PCN, the field sales engineer or the internal sales person in charge should be contacted. The basic responsibility of the customer as per Secti-on 1 and 2 remains unaffected.6. Product Life CycleDue to technical progress and economical evaluation we also reserve the right to discontinue production and delivery of products. As a stan-dard reporting procedure of the Product Termination Notification (PTN) according to the JEDEC-Standard we will inform at an early stage about inevitable product discontinuance. According to this we cannot guarantee that all products within our product range will always be available. Therefore it needs to be verified with the field sales engineer or the internal sales person in charge about the current product availability ex-pectancy before or when the product for application design-in disposal is considered.The approach named above does not apply in the case of individual agreements deviating from the foregoing for customer-specific products.7. Property RightsAll the rights for contractual products produced by Würth Elektronik eiSos GmbH & Co. KG on the basis of ideas, development contracts as well as models or templates that are subject to copyright, patent or commercial protection supplied to the customer will remain with Würth Elektronik eiSos GmbH & Co. KG.8. General Terms and ConditionsUnless otherwise agreed in individual contracts, all orders are subject to the current version of the “General Terms and Conditions of Würth Elektronik eiSos Group”, last version available at .J Important Notes:The following conditions apply to all goods within the product range of Würth Elektronik eiSos GmbH & Co. KG:分销商库存信息: WURTH-ELECTRONICS 74437349022。

建龙软件全套表格

施工单位用表指南工程质量事故报告/SG-001填写说明一、本表为发生工程质量事故时施工单位向建设、监理、质量监督机构报告所用表格。

二、本报表由施工单位项目负责人部填写。

三、填写要求:1.本表中的工程名称、地点、建设单位、施工单位应填写全称,应和《工程质量监督登记表》相一致。

2.事故发生的时间及部位应详细准确,估计经济损失为初步估计的直接经济损失。

3.伤亡人数应按轻伤、重伤、死亡人数分别填写。

4.最后一栏施工单位名称应写明项目负责人部全称,且盖上施工单位(项目负责人部)公章,负责人由项目负责人签名。

5.施工单位应在工程事故发生后及时填写,并采取必要措施防止事故扩大。

施工单位应如实填写、不得隐瞒。

四、如事故中发生了人员伤亡,还应按安全事故有关程序报告。

五、本表一工四份,分别报当地建设、监理、质量监督机构,施工单位各存一份。

单位工程开工报告编号:第册施工日志施工日志技术核定单SG-004填写说明一、该表适用于施工单位提出的技术修改和工程变更。

二、工程变更的要求可能来自建设单位、设计单位或施工单位。

为保证工程质量,不同情况下,工程变更的实施、设计图纸的澄清、修改、具有不同的工作程序。

三、施工单位提出的要求及处理:在施工过程中,施工单位的工程变更可能是:1.要求作某些技术修改:这里是指施工单位根据施工现场的具体条件和自身技术、经验和施工设备及条件,在不改变原设计图纸原则的前提下,提出的对设计图纸某些技术上的修改要求,如对某种规格的钢筋采用替代规格的钢筋,这种变更需通过监理、建设、设计同意并按程序批准后才能实施。

2.要求作设计变更:这里是指施工期间,对于设计单位在设计图纸中所表达的设计标准状态的改变和修改。

这种修改,一般均会涉及重新出图的问题,必须待修改图出来以后才能实施。

四、需要注意的是,不论是建设单位或者施工单位提出的工程变更或图纸修改,均要按规定程序通过监理工程师审查并经有关各方研究,确认其必要性后,才能实施。

COP8SGA544N7资料