基于DDS与FPGA的信号产生器设计与实现

基于FPGA的DDS型数字信号发生器设计

/

图 2 数字 信 号发 生 器 结 构 图

储 器 的 地 址 , 这 个 地 址 读 取 波 形 用 存 储 器 的 内 容 ,送 到 D A 转 换 器 /

图 S控 制 电路 结 构 框 图 中进 行 数模 转 换 , 可 以获 得 所 需 1 DD 就

wa e frte fu in l,n a du tbe f q e c u cin v o h o rs asa d h s a jsa l r u n y fn t g e o

Ke wors: GA, y d FP DDS, gi l i l en at di t sgna g er or a

依 据 图 2中 各 个 单 元 的 功 能 ,使 用 Qu R s l a u l 软 件 完 成 V D 程 序 设 H L

计 。 源程 序 如 下 :

/

形 发生 器 、 / 转换 器 和滤 波器 。 DA 相 位 累 加 器 对 代 表 频 率 的 输 入 步

进 数 值 进 行 累加 运 算 , 给 定 相 位 在

关 键 词 :P F GA, S, 字信 号发 生 器 DD 数

Absr t tac

Di t si al n aor s fe en l u e gi al gn ge er t i a r qu t y s d tol n ne a e ci ui o i it gr t d r t c de gn nd si a de ggig bu n pr c sBas d o es e on PGA F

时 , 字 信 号 发 生 器 所 产 生 数 的信 号 最 高 频 率 为 1 1 6 xO / 1 8 73 H , 幅 度 精 度 为 2 = .k z

基于FPGA的DDS信号发生器设计分析

基于FPGA的DDS信号发生器设计分析摘要:随着现代电子技术的飞速发展,直接数字频率合成DDS 技术逐渐被广泛使用,DDS 是目前数据调度常用的数据分发技术,此技术能够有效结合数据服务质量要求,完成数据分发操作。

为此提出基于FPGA的DDS信号发生器设计,以提升信号发生器精度效果。

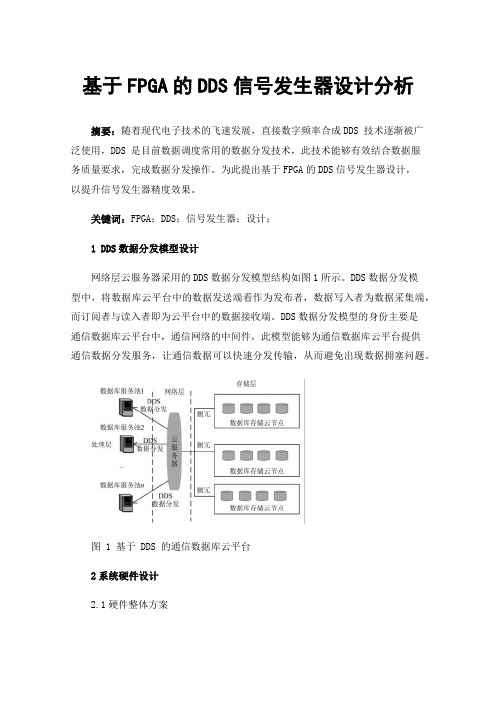

关键词:FPGA;DDS;信号发生器;设计;1 DDS数据分发模型设计网络层云服务器采用的DDS数据分发模型结构如图1所示。

DDS数据分发模型中,将数据库云平台中的数据发送端看作为发布者,数据写入者为数据采集端,而订阅者与读入者即为云平台中的数据接收端。

DDS数据分发模型的身份主要是通信数据库云平台中,通信网络的中间件,此模型能够为通信数据库云平台提供通信数据分发服务,让通信数据可以快速分发传输,从而避免出现数据拥塞问题。

图 1 基于 DDS 的通信数据库云平台2系统硬件设计2.1硬件整体方案函数信号发生器的硬件系统主要包括MCU控制电路,FPGA构成的DDS发生器、DAC转换和低通滤波电路,及一些用于输入输出的器件等。

按键输入和LCD输出显示主要由MCU负责控制,MCU然后将输入的信号运算处理后发送给FPGA,FPGA根据输入的各种参数在ROM表中寻址,同时输出对应控制的波形、频率和幅度的数字信号,最后经过DA转换为对应的模拟电压信号,在经过一个低通滤波器使得模拟电压信号变得平滑。

2.2硬件模块电路系统的硬件电路主要分为两个部分,一是系统主控电路,二是DDS信号发生器电路。

系统主控电路包括以STM32F103C8T6为主控的最小系统板、四路用户按键输入、OLED显示屏输出(SPI)、UART通信连接上位机、硬件SPI连接FPGA负责信号数据传输。

DDS信号发生器电路,其中的FPGA模块的核心芯片为LatticeLCMXO2-4000HC-4MG132,其模块上内置8路输出LED指示灯、4路按键输入、4路拨码输入和两位数码管输出灯资源。

【毕业设计】基于FPGA的DDS信号发生器

术中的佼佼者。现场可编程门阵列FPGA设计灵活、速度快在数字专用集

成电路的设计中得到了广泛的应用由于现场可编程门阵列(FPGA)具有高集成

度、高速度、可实现大容量存储器功能的特性能有效地实现DDS技术极大

generators have become increasingly demanding. In recent years, direct digital

synthesizers (DDS) has a frequency resolution because of its high-frequency

I

基于FPGA的DDS波形发生器 姓名:张怡 专业班级:电子2班 指导教师:易诗

摘 要

波形发生器己成为现代测试领域应用最为广泛的通用仪器之一代表了波形

发生器的发展方向。随着科技的发展对波形发生器各方面的要求越来越高。近

年来,直接数字频率合成器DDS由于其具有频率分辨率高、频率变换速度快、

analyzer on the results of observation and analysis. By analyzing the results, it show

that the design meets the requirements intended to.

And Proved that using Flex way to programming the FPGA to produce a

technology to become the leader in . Field-programmable gate array (FPGA) design

基于FPGA的DDS信号发生器设计

基于FPGA的DDS信号发生器设计随着数字信号处理(DSP)技术的发展,直接数字频率合成器(DDS)逐渐取代了传统的频率合成器,成为一种高性能的信号发生器。

DDS信号发生器通过数字信号直接产生模拟信号,具有频率精度高、可编程性强和快速调频等优点。

本文将通过FPGA实现DDS信号发生器的设计。

首先,我们需要了解DDS信号发生器的基本原理。

DDS信号发生器的核心是相位累加器、查找表和数模转换器(DAC)。

通过累加器产生相位累积,将相位累积的结果通过查找表得到对应的振幅值,并经过数模转换器输出模拟信号。

1.确定需要生成的信号的参数,包括输出频率、相位步进精度、振幅等。

根据这些参数,计算累加器的增量值,即每个时钟周期累加器需要累加的值。

2.在FPGA中设计相位累加器。

相位累加器的宽度取决于相位步进精度,一般为32位或64位。

通过在每个时钟周期加上增量值,实现相位的累加。

3.设计查找表。

查找表的大小取决于数字信号的分辨率,一般为2^N 位。

通过输入相位值查找对应的振幅值。

4.设计数模转换器(DAC)。

通过DAC将数字信号转换为模拟信号输出。

5.在FPGA中实现控制逻辑,包括控制相位累加器和查找表的读写操作,使其按照设定的参数进行相位累加和振幅输出。

6.将设计好的FPGA模块进行综合、布局和时序约束,生成比特流文件。

通过以上步骤,基于FPGA的DDS信号发生器的设计就完成了。

设计好的FPGA模块可以实现高精度、高稳定性的信号发生器,广泛应用于通信、雷达、医疗设备等领域。

需要注意的是,在设计过程中需要考虑到FPGA的资源限制,包括LUT资源的利用、频率分辨率和输出频率的限制等。

此外,还可以通过增加相位累积周期、使用多路查找表和多路DAC等方法进一步优化设计。

综上所述,基于FPGA的DDS信号发生器设计是一个较为复杂的过程,需要对DDS原理有深入的理解,并结合FPGA的特点进行设计。

通过合理的设计和优化,可以实现高性能的DDS信号发生器。

基于FPGA和DDS的数字调制信号发生器设计与实现

V0 1 . 2 l

No . 6

电子 设计 程

E l e c t r o n i c De s i g n E n g i n e e r i n g

2 0 1 3年 3月

Ma r .201 3

基亏 F P GA 和 D DS的数 字调制 信 号发 生器设计 与实现

a n d i mp l e me n t e d a c c o r d i n g t o t h e b a s i c p r i n c i p l e o f t h e d i g i t a l mo d u l a t i o n s c h e me i n a c o mmu n i c a t i o n s y s t e m ,a n d b y t h e

Ab s t r a c t :I n t h i s p a p e r ,a d e s i g n me t h o d o f d i g i t a l mo d u l a t i o n s i g n a l g e n e r a t o r b a s e d O H F P GA a n d DDS t e c h n o l o g y i s

和二进制幅移键控 ( 2 A S K) 3种 基 本 的 二 进 制 数 字调 制 。所 得 仿 真 结 果 表 明 设 计 方 法 的 正 确 性 和 实 用性 。

关键 词 : 数 字调 制信 号 ; 直 接 数 字频 率合 成 器 ; F P G A; D S P B u i l d e r 中图分类号 : 仲3 9 文献标识码 : A 文 章 编 号 :1 6 7 4 — 6 2 3 6 ( 2 0 1 3 ) 0 6 — 0 0 9 0 — 0 4

基于FPGA的并行DDS信号发生器的设计与实现

通 过 解 析 来 自N o IC U的指 令 用 于 各 个 模 块 之 间 的控 制 与 isI P

调 节 。两 路 D S电路 都 包 括 由 F G 实现 的 相 位 累 加 器 、 D P A 波 形 存 储 器 等 电路 ,其 中波 形 存 储 器 采 用 F G 片 内 的双 端 口 P A R M 来实现 。 A 本 设 计 将 各 种 标 准 波 形 的波 形 幅度 值 存 储 在 Fah的 文 ls 件 系 统 中 , 统 运 行 时根 据 需 要 将 相 应 的 波 形 数 据 写入 D S 系 D

储 器 的 寻址 ;调制 D 用 于 产 生 内部 调 制 信 号 , 控 制模 块 DS 主

时 钟 F l 控 制 下 以频 率 控 制 字 F w 为步 长 做 累 加 , 加 的 c k的 c 累

结 果 作 为 波 形 存 储 器 R M 的寻 址 , 了减 小 波 形 存 储 器 所 需 O 为

妒 f=2 () () 2

电路 的 波 形 存 储 器 中 。系 统通 过 双 D S 电路 产 生 两 路波 形 D 信 号在 双 通 道 的 模 式 下 可 作 为双 通 道 的 信 号 输 出 , 在 做 信 而

号 的调 制 时 , D S电路 产 生 的 双 路 波 形 信 号 可 以分 别 的 作 双 D

DE NG u —ig X AO i jn Y epn . I Te u -

(co l f o p tr c ne n e cmmu i t n n ier g i guU iesy Z ej n 10 3 C i ) Sh o o C m ue i c d l o Se a Te nc i g ei ,J n s nvri , hni g2 2 1, hn ao E n n a t a a

基于dds技术的信号发生器的设计与实现

文章标题:基于S技术的信号发生器的设计与实现一、引言在电子通信和信号处理领域,信号发生器是一种常见的设备,用于产生各种类型的信号波形,包括正弦波、方波、三角波等。

基于直接数字合成(S)技术的信号发生器在现代电子设备中越来越受到重视,因为它具有频率稳定性高、频率分辨率高、频率和相位调制灵活等优点。

本文将围绕基于S技术的信号发生器的设计和实现展开讨论。

二、S技术的基本原理S技术是一种通过数字方式直接合成信号的技术,其基本原理是利用数字信号处理器(DSP)生成离散时间信号序列,再通过数模转换器将其转换为模拟信号输出。

S技术的核心在于其通过累加相位增量的方式来实现信号的频率合成,因此频率分辨率高,相位调制灵活,并且可以实现快速切换频率和相位。

三、基于S技术的信号发生器的硬件设计1. 时钟模块:基于S技术的信号发生器的时钟模块需要具有极高的稳定性和精度,以确保合成信号的频率稳定性和精度。

2. 数字信号处理模块:数字信号处理模块是实现基于S技术的信号发生器的关键,它需要具有高速的计算能力和精确的相位累加器,以实现频率和相位的精确合成。

3. 数模转换模块:数模转换模块将数字信号处理模块生成的数字信号转换为模拟信号输出,需要具有高精度和低失真的特性。

四、基于S技术的信号发生器的软件设计1. 频率和相位控制算法:基于S技术的信号发生器的软件设计需要包括频率和相位控制算法,以实现对合成信号频率和相位的灵活调节。

2. 用户界面设计:为了方便用户操作和监控合成信号的参数,基于S技术的信号发生器的软件设计还需要包括用户界面设计,以实现对信号发生器的参数设置和监控。

五、基于S技术的信号发生器的实现基于S技术的信号发生器的实现需要在硬件和软件两方面充分考虑,确保其在频率稳定性、频率分辨率和相位调制灵活性等方面具有优秀的性能。

在实际应用中还需要考虑其输出功率、谐波失真等参数,以满足不同场景的需求。

六、个人观点与展望基于S技术的信号发生器在现代电子领域中具有广泛的应用前景,其高稳定性、高频率分辨率和灵活的相位调制特性,使其在通信、雷达、医疗等领域都有着重要的地位。

基于FPGA的DDS基本信号发生器的设计

De i n fDDS ba i i n lg n r t r b s d o sg o sc sg a e e a o a e n FPGA

Z HAO i a L — ,GUO B o z n ,L U S a ・ e g,MA T o n a —e g I h o p n a

D S D rc D g a F e u n yS n ei) D ( i t ii l rq e c y t s 即直 接 数 字 式 频 e t h s

l 时 五k 基准 钟 1 l

.

率 合 成 , 从 相 位 概 念 出 发 直 接 合 成 所 需 波 形 的 一 种 频 率 合 是 成 技 术 l。 传 统 信 号 源 所 采 用 的用 模 拟 方 式 生 成 信 号 不 同 , l与 l 它 是 将 先 进 的数 字 信 号 处 理 理 论 与 方 法 引 入 信 号 合 成 领 域 。

据依 次 全 部 存 储 在 R M 波 形 表 里 , 过 外接 设 备 拨 扭 开 关 和键 盘 控 制 所 需 波 形 信 号 的 输 出 . 终 将 波形 信 息 显 示 在 O 通 最

L D液 晶 显 示 屏 上 。 各 硬 件 模 块之 间 的 协 调 工 作 通 过 嵌 入 式软 核 处 理 器 N o Ⅱ用 编程 实 现 控 制 。 本 设 计 所 搭 建 的 C i s

mo u e T eL D 2 6 o t l r nt i e i n i nI o e ra ie yp o r mmi g d l. h C 1 8 4 c nr l sd sg sa c r e l d b r g a oei h P z n.

Ke r s y wo d :DDS P e h ooy;sq e c fsoaewa s ;F GA tc n lg e u n eo trg y ;Nis ;I oe o Ⅱ P c r

基于DDS技术的信号发生器的设计与实现_毕业设计(论文)

毕业设计设计题目:基于DDS技术的信号发生器的设计与实现基于DDS技术的信号发生器的设计与实现摘要DDS是直接数字式频率合成器(Direct Digital Synthesizer)的英文缩写。

与传统的频率合成器相比,DDS具有低成本、低功耗、高分辨率和快速转换时间等优点,广泛使用在电信与电子仪器领域,是实现设备全数字化的一个关键技术。

本设计采用单片机为核心处理器,利用键盘输入信号的参数,控制DDS的AD9850模块产生信号,信号的参数在LCD1602上显示,完成正弦信号和方波信号的输出,用示波器输出验证。

DDS是一种全数字化的频率合成器,由相位累加器、波形ROM、D/A转换器和低通滤波器构成。

时钟频率给定后,输出信号的频率取决于频率控制字,频率分辨率取决于累加器位数,相位分辨率取决于ROM的地址线位数,幅度量化噪声取决于ROM的数据位字长和D/A转换器位数。

与传统的频率合成方法相比,DDS合成信号具有频率切换时间短、频率分辨率高、相位变化连续等诸多优点。

使用单片机灵活的控制能力与AD9850的高性能、高集成度相结合,可以克服传统DDS设计中的不足,从而设计开发出性能优良的信号发生器系统。

关键词:单片机直接数字频率合成AD9850 DDSDesign and Implementation of the SignalGenerator Based on DDS TechnologyAbstractDDS is Direct Digital frequency Synthesizer (Direct Digital Synthesizer) English abbreviations. Compared with the traditional frequency synthesizer, with low cost, DDS low power consumption, high resolution and fast converting speed time and so on, widely used in telecommunications and electronic instruments field, is to realize equipment full digital a key technology.This design uses the single chip processor as the core, using a keyboard input signal parameters, control of DDS AD9850 module produce signals, the signal parameters in LCD1602 show that the complete sine signal and square wave signal output, the output with an oscilloscope validation.DDS is A full digital frequency synthesizer, by phase accumulators, waveform ROM, D/A converter and low pass filter composition. The clock frequency after A given, the output depends on the frequency of the signal frequency control word, the frequency resolution depends on accumulators digits, phase resolution depends on the ROM address line digits, amplitude quantization noise depends on the ROM data A word length and D/A converter digits. And the frequency of the traditional method than the synthesis, DDS synthesis signal has a frequency switching frequency of short time, high resolution and continuous phase changes, and many other advantages. Using single chip microcomputer control of the flexible ability and high performance, high level of integration of the AD9850 combination, can overcome the disadvantage of the traditional DDS design, to design the developed good performance of signal generator system.Key word:MCU; direct digital frequency synthesis;AD9850;DDS目录1 引言 (1)2DDS概要 (2)2.1DDS介绍 (2)2.1.1 DDS结构 (2)2.1.2典型的DDS函数发生器 (3)2.2DDS数学原理 (5)3 总体设计方案 (8)3.1系统设计原理 (8)3.2总体设计框图 (8)4 系统硬件模块的组成 (9)4.1单片机控制模块 (9)4.1.1 STC89C52主要性能 (9)4.1.2 STC89C52功能特性描述 (9)4.1.3 时钟电路 (11)4.1.4复位电路 (11)4.2AD9850模块 (12)4.2.1 AD9850简介 (12)4.2.2 AD9850的控制字与控制时序 (14)4.2.3单片机与AD9850的接口 (15)4.3滤波电路设计 (15)4.4键盘控制模块 (16)4.5LCD显示模块 (16)4.5.1液晶显示器显示原理 (16)4.5.2 1602LCD引脚与时序 (17)4.6A/D转换模块 (20)5 软件设计与调试 (21)5.1程序流程图 (21)5.2软件调试 (22)5.2.1 keil编程工具介绍 (22)5.2.2 STC-ISP下载工具介绍 (23)6 硬件电路制作 (24)6.1原理图的绘制 (24)6.2电路实现的基本步骤 (24)6.3硬件测试波形图 (25)7 结论 (27)谢辞 .............................................................................................. 错误!未定义书签。

基于FPGA的DDS信号发生器设计

基于FPGA的DDS信号发生器设计随着现代科技的不断发展,数字信号发生器(DDS)已成为各种电子设备中常用的一种功能模块。

使用DDS技术可以生成高质量、高稳定性的各种频率和波形的信号。

而FPGA(Field Programmable Gate Array)作为一种可编程逻辑器件,具有高集成度、高速度和灵活性等优势,逐渐成为了实现DDS信号发生器的主要选择之一一、DDS技术概述DDS(Direct Digital Synthesis)技术是一种基于数字直接合成的方法,通过计算机算法精确地合成期望的波形。

它的工作原理是将时钟信号分频得到一系列的离散相位值,再通过查表和插值的方法得到对应的幅值,最后通过一个DAC(Digital to Analog Converter)将数字信号转换为模拟信号输出。

二、基于FPGA的DDS信号发生器设计步骤1.系统架构设计根据DDS信号发生器的要求,确定所需的系统架构。

一般包括时钟模块、相位累加器、查找表、插值器、DAC和控制逻辑等模块。

2.时钟模块使用FPGA内部的资源或外部时钟源生成所需的系统时钟信号。

可以通过时钟分频和PLL(Phase-Locked Loop)锁相环技术来实现对系统时钟的精确控制。

3.相位累加器利用FPGA的寄存器或分频模块实现相位累加功能。

通过周期性地累加相位增量,可以得到DDS信号的相位。

4.查找表利用FPGA内部的RAM(Random Access Memory)存储相位对应的幅值。

根据相位的大小来查找对应的幅值,存储在RAM中。

5.插值器可以通过线性插值或差值的方法对相位查找表的输出进行插值,以提高输出信号的精度和稳定性。

6.DAC将插值器输出的数字信号转换为模拟信号,通过FPGA的IO端口或专用的DAC芯片输出到外部电路。

7.控制逻辑设计合适的控制逻辑,可以通过外部接口或FPGA内部的控制模块来控制DDS信号发生器的频率、幅值、相位偏移等参数。

DDS原理及基于FPGA的实现

DDS原理及基于FPGA的实现DDS(Direct Digital Synthesis)全称直接数字合成,是一种数字合成功能信号发生器的工作原理。

它是通过根据一些固定的参考信号,加上一个可控的数字增量,形成一个频率可调的数字信号。

DDS工作原理及路线图:DDS的核心是一个数字控制的累加器和一个查找表。

其具体实现如下所示:1.预先存储波形表:首先,需要在DSP处理器或FPGA中事先存储好波形表(一般是一个周期的波形值),该波形表由特定的设计方法生成,例如正弦函数合成、加窗等。

2.相位累加器:DDS在每个时钟周期内累加相位增量。

具体来说,它将前一周期的相位值与当前周期的相位增量相加,并将结果存储在一个相位累加器中。

3.相位查找:相位查找操作通过查找表来实现。

在每个时钟周期中,DDS从查找表中根据相位累加器的值来获取对应的波形数值。

4.数字输出:DDS将查找表中获取的波形数值直接转换为模拟输出信号的幅度。

基于FPGA的DDS实现:DDS在FPGA上实现具有以下优点:灵活性高、资源利用率高、功耗低、随机存取等。

基于FPGA的DDS实现主要包括以下几个关键步骤:1.数字波形表生成:使用FPGA的片上RAM(BRAM)或外部存储器存储一个周期的数字波形表。

2.相位累加器:DDS的核心是一个相位累加器,可以使用FPGA的片上计数器或者DSP48E资源实现,实现相位的累加。

3.查找表选择:DDS使用查找表来获取波形数值,可以根据需求选择合适的查找表,如ROM、LUT等,FPGA提供了不同的资源来实现查找表。

4.数字输出:DDS通过数字转模拟转换器(DAC)将输出信号转换为模拟信号。

FPGA通常具有丰富的IO资源,可直接与DAC连接。

5.控制接口:DDS通常需要提供一些控制接口,允许外部调整频率、相位、振幅等参数。

FPGA可以提供适当的接口,如基于UART或SPI的串行接口、基于GPIO的并行接口等。

总结:DDS是一种基于数字合成的信号发生器原理,通过累加器和查找表实现信号的频率可调。

基于DDS的信号发生器设计

基于DDS的信号发生器设计一、引言信号发生器是电子测量仪表中常见的一种设备,用于产生具有不同特性的信号,以便在各种实验、测试和校准工作中使用。

传统的信号发生器通常通过模拟电路来实现,但由于其受到尺寸、可调性和稳定性等限制,逐渐被数字信号发生器(DDS)所取代。

DDS信号发生器利用数字技术直接生成信号,具有调频范围广、频率稳定度高、精度高等优点。

二、DDS技术原理DDS技术(Direct Digital Synthesis,直接数字合成)是一种通过数字信号直接合成模拟信号的技术,它将数字信号与时钟同步,并通过数模转换得到模拟信号。

DDS技术的实现核心是相位累加器、数控振荡器和数模转换器。

相位累加器用于累加相位值,数控振荡器通过相位值生成相应频率的信号,而数模转换器将生成的数字信号转换为模拟信号。

基于DDS的信号发生器可以通过使用FPGA(Field Programmable Gate Array)和AD(Analog Devices)公司的AD9854芯片来实现。

使用FPGA实现相位累加器和控制逻辑,AD9854负责生成模拟信号。

下面是基于DDS的信号发生器的设计步骤:1.系统架构设计DDS信号发生器可分为控制模块、相位累加模块、频率累加模块和数模转换模块。

控制模块负责接收用户输入的参数,并控制相位、频率等;相位累加模块负责相位的累加和输出;频率累加模块负责频率的累加和输出;数模转换模块负责将数字信号转换为模拟信号。

2.相位累加模块设计相位累加器使用FPGA中的计数器模块实现。

设置计数器的位宽,根据所需的相位分辨率来确定。

通过改变计数器的初始值和计数步长,可以实现相位的变化。

3.频率累加模块设计频率累加器使用FPGA中的加法器模块实现。

根据所需的频率范围和分辨率,对加法器的输入信号进行控制,实现频率的变化。

4.数模转换器设计AD9854芯片负责将数字信号转换为模拟信号。

将FPGA中的数字信号输入AD9854中,经过数模转换后输出模拟信号。

基于FPGA的DDS信号发生器设计

基于FPGA的DDS信号发生器设计一、引言随着科技的不断发展,数字信号处理(Digital Signal Processing,简称DSP)在各个领域得到广泛应用。

其中,一种常见的应用是通过数字直接合成(Digital Direct Synthesis,简称DDS)来生成各种信号。

DDS信号发生器能够快速准确地产生高质量的信号,被广泛应用于通信、电子测量、医疗器械等领域。

本文将阐述基于现场可编程门阵列(Field-Programmable Gate Array,简称FPGA)的DDS信号发生器设计。

二、FPGA的简介FPGA是一种可编程的逻辑器件,其内部包含了大量可编程的逻辑单元和存储单元。

FPGA具有灵活性高、可重构性强等特点,可以根据设计者的需求,灵活地实现各种数字电路。

因此,FPGA成为DDS信号发生器设计的理想平台。

三、DDS技术原理DDS技术通过数字控制相位累加器和振荡器来实现信号的直接合成。

其中,相位累加器用于控制振荡器输出频率的连续调节,振荡器则根据相位累加器的输出产生正弦波。

DDS信号发生器的主要步骤如下:1. 初始化相位累加器:将初始相位值存入相位累加器。

2. 累加相位值:相位累加器根据设定的增量值不断累加,得到一个新的相位值。

3. 查表获得振荡器的输出值:通过查表法,根据相位值获得振荡器的输出幅度。

4. 输出信号:根据振荡器的输出幅度,形成DDS信号。

四、1. 系统架构设计:本设计采用基于FPGA的硬件逻辑实现DDS信号发生器。

系统由相位累加器、振荡器、幅度调节模块和输出模块组成。

其中,相位累加器使用FPGA中的计数器实现,振荡器采用三角函数计算逼近的方式实现,幅度调节模块用于调节振荡器的输出幅度,输出模块将DDS信号输出到外部。

2. 相位累加器设计:相位累加器是DDS信号发生器的核心模块。

本设计采用基于FPGA的计数器实现相位累加器,通过控制计数器的计数速度来调节信号的频率。

FPGA基于DDS的移相调频调幅信号发生器

《EDA》课程设计报告实验题目:基于DDS的数字移相信号发生器基于DDS的数字移相信号发生器一、课程设计目的1、进一步熟悉Quartus Ⅱ的软件使用方法;2、熟悉利用VHDL设计数字系统并学习LPM ROM的使用方法;3、学习FPGA硬件资源的使用和控制方法;4、掌握DDS基本原理,学习利用此原理进行信号发生器的设计。

二、设计任务1、完成8位输出数据宽度的频率可调的移相正弦信号发生器。

2、完成8位输出数据宽度的频率可调的移相三角波、方波信号发生器。

3、以上三种波形使用一个按键依次切换。

4、波形发生器实现幅度可调。

5、信号发生器的原始数据存储在外部存储器里,由FPGA进行读取,经过D/A转换输出,由示波器观察最终结果。

三、基本原理直接数字频率合成器(DDS)是通信系统中常用到的部件,利用DDS可以制成很有用的信号源。

与模拟式的频率锁相环PLL相比,它有许多优点,突出为(1)频率的切换迅速;(2)频率稳定度高。

一个直接数字频率合成器由相位累加器、波形ROM、D/A转换器和低通滤波器构成。

DDS的原理框图如下所示:图 1 直接数字频率合成器原理图其中K为频率控制字, fc为时钟频率,N为相位累加器的字长,D为ROM数据位及D/A 转换器的字长。

相位累加器在时钟 fc的控制下以步长K作为累加,输出N位二进制码作为波形ROM的地址,对波形ROM进行寻址,波形ROM输出的幅码S(n)经D/A转换器变成梯形波S(t),再经低通滤波器平滑后就可以得到合成的信号波形了。

合成的信号波形形状取决于波形ROM中存放的幅码,因此用DDS可以产生任意波形。

本设计中直接利用D/A转换器得到输出波形,省略了低通滤波器这一环节。

1、频率预置与调节电路不变量K被称为相位增量,也叫频率控制字。

DDS方程为:f0= fc K/2n,f0为输出频率,fc 为时钟频率。

当K=1时,DDS输出最低频率(也既频率分辩率)为fc /2nDDS的最大输出频率由 Nyguist 采样定理决定,即fc /2,也就是说K的最大值为2n-1.因此,只要N足够大,DDS可以得到很细的频率间隔。

基于FPGA的DDS信号发生器的设计与实现

基于FPGA的DDS信号发⽣器的设计与实现⼀、实现环境 软件:Quartus II 13.0 硬件:MP801⼆、DDS基本原理 DDS(Direct Digital Synthesizer)即数字合成器,是⼀种新型的频率合成技术,具有相对带宽⼤,频率转换时间短,分辨率⾼和相位连续性好等优点。

较容易实现频率、相位及幅度的数控调制,⼴泛应⽤于通信领域。

DDS的实现⽰意图如下图所⽰: 1、将需要合成的信号的数据存储在rom中,合成待输出信号的⽅法请参考: 2、dds_control实现的功能是将存储在rom中的待合成的信号的数据按照⼀定的规则取出来: dds_control主要由相位累加和频率累加来实现,简单的说,通过控制相位累加和频率累加来实现从rom中取出不同时刻的数据。

(1)相位累加器位数为N位(24~32),相位累加器把正弦信号在相位上的精度定义为N位,其分辨率位1/2N ,决定⼀个波形的起始时刻在哪个点; (2)频率累加器⽤来控制每隔⼏个点从rom中取⼀个数据,决定⼀个波形的频率; (3)若DDS的时钟频率为F clk ,频率控制字fword = 1,则输出频率为 F out = F clk/2N,这个频率相当于“基频”,若fword = B,则输出频率 F out = B * F clk/2N。

因此理论上由以上三个参数就可以得出任意的 f o 输出频率,且可以得出频率分辨率由时钟频率和累加器的位数决定的结论。

当参考时钟频率越⾼,累加器位数越⾼,输出频率分辨率就越⾼。

3、从FPGA中出来的信号都是数字信号(dds_control输出的信号都为数字信号),需要通过dac芯⽚来将数字信号转换为模拟信号,这样将dac芯⽚输出的信号接⼊到⽰波器中,才能看到波形; 4、举例说明频率控制和相位控制: 如上图所⽰,这个是⼀个由33个点构成的正弦波信号,(rom_addr,rom_data),纵坐标为存储在rom中的正弦波信号,横坐标为dds_control ⽣成的地址信号。

基于FPGA+DDS的信号源设计与实现

宽 带 信 号 源 所 需 要 的 各 类 信 号 , 盖 3  ̄l z频 段 , 率 达 到 2 。 在 完 成 了 具 体 的 设 计 和 实 覆 0MHz GH 功 0W

验 后 实 现 了样 机 的 制 作 , 过 现 场 测 试 验 证 了其 完 全 满 足 应 用 需 求 。 通 .

Har wa e Te hnq e d r c iu

基 于 F G D S的信 号 源设 计 与 实现 P A+ D

刘 伟 ,钟 子 发 ,叶 春 逢

( 电子 工 程 学 院 ,安 徽 合 肥 2 0 3 3 07)

摘 要 :采 用 D S F G D C 数 字 信 号 激 励 器 硬 件 电 路 和 数 字 波 形 合 成 软 件 算 法 设 计 实现 了 D + P A+ A

关 键 词 :软 件 无 线 电 ;F G D S P A+ D ;超 宽 带 上 变 频 ;宽 带 功 率 放 大

中 图 分 类 号 :T 9 17 N 1 .2 文 献 标 识 码 :B 文 章 编 号 :1 7 — 7 0 2 1 1 8 0 1 — 3 6 4 7 2 (0 0 1 — 0 8 0

基 带 信 号 s() S n 。 字 基 带 信 号 S n 、Qn 通 过 D C l 、q ) 数 n I )S( ) A

变 换 为 模 拟 基 带 信 号 S( 、Q ) 再 通 过 上 变 频 模 块 即 可 l ) S( , f

定 的通 信 体 制 、 号 调 制 样 式 以 及 信 号 特 征 参 数 , 如 信 例 G M 移 动 通 信 信 号 只 有 GMS S K一 种 调 制 样 式 , 调 制 速 其 率 为 2 . bts 因 此 这 类 通 信 设 备 中 的 数 字 信 号 激 励 28K i , /

基于fpga的dds正弦信号发生器的设计和实现

基于fpga的dds正弦信号发生器的设计和实现

基于FPGA的DDS正弦信号发生器可以使用两种常见的实现

方法:Look-Up Table (LUT) 方法和相位累积器方法。

1. LUT方法:

- 首先,定义一个存储正弦波样本值的LUT (Look-Up Table),LUT的大小取决于所需的精度和波形频率范围。

- 使用一个计数器来生成一个相位值,该相位值是一个0到LUT大小之间的数字。

- 将该相位值作为索引,通过查找LUT来获取对应的正弦波

样本值。

- 将该正弦波样本值通过数字-模拟转换器(DAC)转换为模拟

信号输出。

2. 相位累积器方法:

- 使用一个固定频率的时钟作为参考信号输入,例如50 MHz。

- 使用一个相位累积器累积每个时钟周期的相位值。

- 计算相位值对应的正弦波样本值,并通过DAC转换为模拟信号输出。

- 相位累积器的更新频率由所需的输出频率确定,可以通过

增加或减小相位值的增量来调节输出频率。

需要注意的是,FPGA上实现DDS正弦信号发生器时,需要

一个高速的DAC来将数字信号转换为模拟信号输出。

同时,

为了提高性能和减少功耗,可以采用流水线技术,通过并行处理来提高输出频率的精度和速度。

此外,还可以通过添加相位调制、振幅调制等功能来进一步扩展DDS正弦信号发生器的

功能。

要设计和实现基于FPGA的DDS正弦信号发生器,可以使用硬件描述语言如Verilog或VHDL编写相应的代码,并使用FPGA开发工具进行综合、布局以及生成比特流文件。

最后,将比特流文件加载到目标FPGA芯片上,就可以实现DDS正弦信号发生器的功能。

基于fpga的dds信号发生器实现方法

基于fpga的dds信号发生器实现方法基于FPGA的DDS信号发生器可以实现高精度、高速率、高可靠性的信号发生。

DDS即直接数字频率合成技术,通过数字控制实现对信号的精确控制,从而生成各种复杂的信号。

其基本原理是将频率可调的数字信号直接进行混频、加权求和等数学处理,得到所需的复杂信号。

在实现基于FPGA的DDS信号发生器时,需要进行如下步骤:

1. 确定FPGA芯片型号和开发环境:根据需求选择合适的FPGA 芯片,同时选择相应的开发环境,如Quartus II、Xilinx ISE等。

2. 编写Verilog/VHDL代码:根据DDS原理,编写相应的Verilog/VHDL代码,实现数字控制和信号处理等功能。

3. 设计电路板:根据芯片的引脚布局,设计相应的电路板,包括时钟电路、功率供应电路、信号输入/输出接口等。

4. 调试和验证:对设计好的电路板进行调试和验证,确保实现的DDS信号发生器能够正常工作。

5. 优化和扩展:根据需求,对实现的DDS信号发生器进行优化和扩展,如增加信号处理模块、扩大频率范围等。

综上所述,基于FPGA的DDS信号发生器是一种高效、高精度、高可靠性的信号发生器,可广泛应用于通信、电子、航空、军事等领域。

其实现方法包括选型、编写代码、设计电路板、调试验证和优化扩展等步骤。

- 1 -。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

收稿日期:2009-03-01

作者简介:胡坤(1972-),男,安徽滁州人。

硕士,讲师,研究方向:自动控制。

1引言

目前测控通信设备所配备的信号源大多只能产生单通道射频信号,且信号的调制方式、调制数据、信噪比等参数调整十分有限,只能部分满足现有设备的指标测试及功能检查要求;信号源体积较大、

机动性差,使用不够灵活方便;同类型的测控通信设备在性能检测时使用各自的信号源,测试结果不利于相互分析比较其性能的优劣。

为此,设计一套体积小、调制方式、调制数据码率、码型、信号功率、信噪比等参数可自由设置的信号发生器具有很强的实用性和现实意义。

DDS (直接数字频率合成器)因其性能稳定、易于实现各种调制方式、使用灵活等特点,能产生各种调制方式的中低频信号;FPGA (现场可编程门阵列)技术因其强大的在线可编程性,以及器件规模的增加,成本的降低,在电子通信领域的应用不断扩大,已经成为大多数电子产品

内部不可或缺的重要组成部分。

对FPGA 芯片和DDS 芯片进行有机结合,合理划分其实现的功能,即可设计实现小型化的多功能信号产生器。

2AD9959芯片简介

ADI 公司推出的新型四路直接数字频率合成器件AD9959允许单独编程多达四路同步输出。

ADI 的完整DDS 解决方案采用片内高性能DAC (数模转换)把基准频率转换成有极精密频率控制的正弦波。

如果需要增加通路,

AD 9959可以进行菊花链连接。

器件具有极低的功耗,每个通道最大功耗小于165mW 。

AD9959每一路都集成了有极好宽带和窄带SFDR (杂散抑制)性能的高速10位DAC 。

每路可单独编程的通路提供14位相位分辨率,32位频率分辨率和10位幅度控制。

器件还支持直接或线性扫描调制,各通路绝缘大于60dB 。

系统时钟高达500MHZ ,输出最高正弦波频率达200M HZ 。

AD9959内部集成了倍频时钟单元(最高可实现20倍时钟频率),这样芯片外部时钟可采用较低频率,有效降低电路板设计难度。

四通道均有独立的频率、相位、幅度控制寄存器,可通过数字接口SCLK 、CS 、SDIO 方便地进行控制。

3双通道信号产生器设计

基于DDS 与FPGA 的信号产生器设计与实现

胡

坤

(安徽职业技术学院,安徽合肥230051)

摘

要:采用四通道D D S 芯片及FPG A 器件,设计了多种参数均可自由设置的双通道信号产

生器。

阐述了信号产生器的主要组成及工作原理,给出了FPG A 实现后的V H D L 原理框图及具体应用实例,解决了现有设备检修检测手段不足的问题。

关键词:D D S 技术;信号产生器;FPG A 技术中图分类号:TN74

文献标识码:A

文章编号:1672-2868(2009)03-0032-03

2009年第11卷第3期

总第96期

巢湖学院学报Joumal of Chaohu College

No.3.,Vol.11.2009General Serial No.96

32

3.1系统组成及工作原理

双通道信号产生器的主要组成及工作原理框图如图1所示。

FPGA选用Xilinx(赛灵思)公司生产的低成本FPGA芯片X3CS200,主

要完成调制数据的产生(包括数据码型、数据速率、调制数据格式等参数的控制)、配置DDS芯片AD9959的工作方式,以及驱动七段数码管等用户接口的功能;四通道DDS芯片AD9959即在FPGA的控制下产生所需调制形式、载波频率、信号幅度的中低频信号;合路器选用Mini公司生产的ADP2-1器件,两个合路器分别将两路DDS输出的中低频信号合成一路输出,其中进入合路器的信号一路产生噪声(用高码率直接序列扩频信号模拟),一路为有用信号。

通过控制噪声和信号的输出功率,即可实现信噪比可变的功能;在输出中低频信号的同时,由FPGA直接将基带调制数据

PCM1、PCM2输出,这样即可产生四路信号输出,从而满足不同的需求。

图1信号产生器主要组成及工作原理框图

3.2控制AD9959的方法

FPGA与AD9959的连接关系图如图2所示,FPGA和DDS本身的外围电路可参考文献[1]。

图2FPGA与DDS电路连接图

图中,M odel_sel接地,选择外部晶振提供参考时钟的工作模式,Cs接地,用信号线Sdio_0、sclk、Io_update对AD9959进行配置,采用串行配置模式,其配置时序图如图3所示。

图3AD9959串行配置时序图

配置数据在sclk的上升沿写入DDS寄存器,sclk的最高频率可达200MHZ。

每次配置时,首先写入DDS寄存器的地址,紧接着写入寄存器的值。

写完配置后,Io_update的上升沿触发DDS的寄存器控制字工作。

除串行配置模式外,AD9959还支持2bit、4bit并行配置模式,以进一步提高配置速率。

下面只给出频率控制字的计算方法,其他参数的配置参见文献[1]。

频率字的计算公式为:f

=F×f s

232

(1)

式中,f

为DDS输出频率,F为频率字,f

s

为DDS的系统时钟。

由式(1)可知,系统时钟fs为500MHz时,频率分辨率可达0.1164Hz。

3.3信号产生器控制程序设计

信号产生器控制程序为FPGA程序。

FPGA 程序设计采用VHDL语言,开发环境为ISE7.0,综合工具为XST7.0,仿真工具为M odelsimSE6. 0。

其综合后的RTL(寄存器传输级逻辑)顶层原理图如图4所示。

图4信号产生器VHDL程序顶层RTL原理图

图中clk_produce模块将输入40M Hz时钟信号分频成20MHz、5MHz和毫秒时钟信号供其他模块使用;pcm_produce模块产生调制数据pcm1、pcm2和噪声调制数据noise1、noise2,送至AD9959_config模块产生中频信号;AD9959_config模块是程序的核心模块,完成对AD9959芯片所有参数的控制,通过DDS接口信号送至AD9959相应的控制信号管脚;

33

user_interface模块则完成按键功能以及LED、七段数码管的显示功能,实时显示当前信号状态。

4应用实例

由于该信号产生器产生的信号种类多、体积小、使用方便,因而在设备指标测试、检修检测等方面得到了较为广泛的应用。

图5为利用该信号产生器测试某型号遥测设备分集接收机性能的测试框图。

分集接收机主要完成对输入的左、右旋160MHz中频FM信号分集接收功能,采用最大比分集接收技术以提高在信号衰落时的接收机性能。

测试该功能需产生两路载波相位差可变、功率比可变的中频调制信号。

目前设备所配备的信号源或仿真器均无法产生满足该要求的信号,利用本文所设计的信号产生器即可产生所需信号,从而对分集接收机整体性能进行测试。

由于该信号产生器产生的载波频率可在200MHz以下任意设置,故可改变载波频率,在图中测试点①、②、③、④分别进行测试。

这不仅可测试接收机性能,在接收机发生故障时也可十分方便地对设备的故障进行定位隔离。

图5分集接收机性能测试框图

5结束语

利用灵活的FPGA器件及多通道DDS器件设计的多功能多通道信号产生器,具有体积小、信号通道多、信号种类多等一系列优点,可很好地解决现有设备检修检测手段不足的问题。

同时,由于FPGA的可重复在线可编程功能,十分有利于信号产生器功能的多次开发、升级,以适应未来设备的测试需要。

目前,该信号产生器已成功应用于遥测设备的检修检测中,取得了良好的效果。

参考文献:

[1]Analog Devices,Inc,4-Channel500MSPS DDS with10-Bit DAC。

AD9959,,2005.

[2]沈允春.扩频技术[M].北京:国防工业出版社,2005.

[3]王诚,薛小刚.FPGA/CPLD设计工具XILINXISE使用详解[M].北京:人民邮电出版社,2005.

DESIGN AND IMPLEMENTATION OF THE SIGNAL

GENERATOR BASED ON DDS AND EPGA

HU Kun

(Anhui Vocational and Technical College,Hefei Anhui230051)

Abstract:By adopting DDS chips and FPGA devices,design a kind of flexible multi-parameter dual-channel signal generator,expatiate its main components and working principles,present the VHDL working principium,as well as its specific application instances after the realization of FPGA,and solve the insufficience of the existing equipment overhaul measures. Key words:DDS technology;signal generator;FPGA technology

责任编辑:宏彬

34。