4046中文资料

cmos4046集成电路研究锁相环(pll)的工作原理毕业外文翻译

本实验要使用CMOS4046集成电路研究锁相环(PLL )的工作原理。

电路包括两个不同的鉴相器和一个VCO 。

另外还有一个齐纳二极管参考电压源用在供电调节中,在解调器输出中有一个缓冲电路。

用户必须提供环路滤波器。

4046具有高输入阻抗和低输出阻抗,容易选择外围元件。

注意事项1. 本实验较为复杂,进入实验室之前,确认你已经弄懂了电路预计应该怎样工作。

对某样东西还没有充分分析之前,不要去尝试制作它。

在开始实验之前要通读本文。

2. 在实验第一部分得到的数据要用来完成实验的其它任务。

所以要仔细对待这部分内容。

3. 小心操作4046芯片,CMOS 集成电路很容易损坏。

避免静电释放,使用10k Ω电阻把信号发生器的输出耦合到PLL 。

在关掉4046供电电源之前先关闭信号发生器,或者从信号输入端给整个电路供电。

要避免将输出端对电源或对地短路,TTL 门电路可以容忍这种误操作但CMOS 不能(要注意松散的导线)。

CMOS 输出也没有能力驱动电容负载。

VSS 应该接地,VDD 应该接5V ,引脚5应该接地(否则VCO 被禁止)。

1 VCO 工作原理阅读数据手册中的电路描述。

VCO 常数(0K 单位为弧度/秒-伏)是工作频率变化与输入电压(引脚9上)变化之比值。

测量出0K ,即,画出输出频率关于输入电压的曲线。

确认数据范围要覆盖5kHz 到50kHz 。

对于R1, R2 和C 的各种参数取值进行测量,确定0K 对于R1 ,R2 和C 是怎样的近似关系。

测量VCO 输出的上升和下降时间,研究电容性负载的影响。

2 无源环路滤波器无源环路滤波器位于鉴相器输出与VCO 输入之间。

此滤波器对鉴相器输出中的高次谐波进行衰减,并控制环路的强度。

通常用一个简单RC 滤波器就可以满足要求,这种设计能避免有源滤波器设计中固有的电平移动和输出限制的恼人问题。

但另外一方面,有源滤波器可以提供更优越的性能。

2.1 相位比较器首先来看一下4046的相位比较器II 的输出。

4046中文资料

CD4046引脚功能介绍pdf中文资料Post By:2009-4-2 10:02:25CD4046是通用的CMOS锁相环集成电路,其特点是电源电压范围宽(为3V-18V),输入阻抗高(约100MΩ),动态功耗小,在中心频率f0为10kHz下功耗仅为600μW,属微功耗器件。

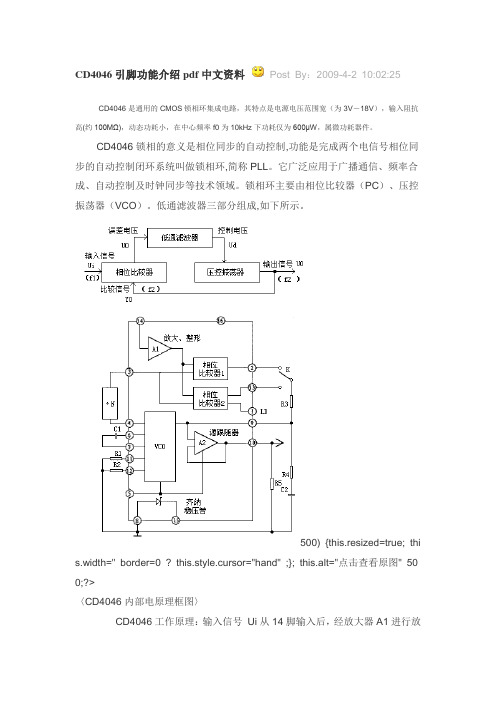

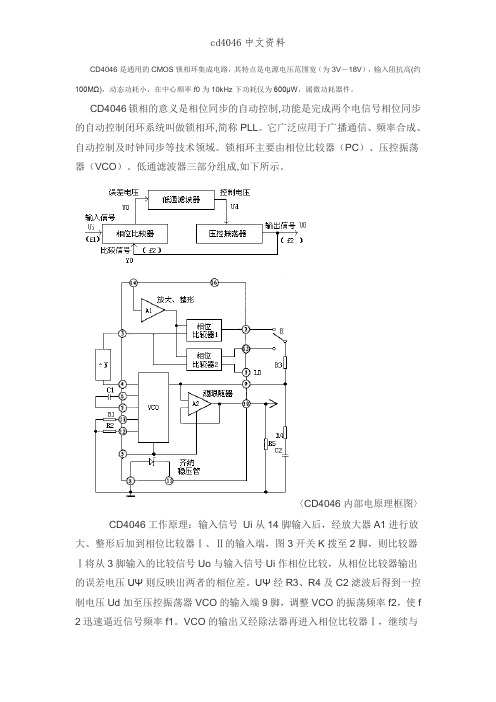

CD4046锁相的意义是相位同步的自动控制,功能是完成两个电信号相位同步的自动控制闭环系统叫做锁相环,简称PLL。

它广泛应用于广播通信、频率合成、自动控制及时钟同步等技术领域。

锁相环主要由相位比较器(PC)、压控振荡器(VCO)。

低通滤波器三部分组成,如下所示。

500) {this.resized=true; thi s.width=" border=0 ? this.style.cursor="hand" ;}; this.alt="点击查看原图" 50 0;?>〈CD4046内部电原理框图〉CD4046工作原理:输入信号Ui从14脚输入后,经放大器A1进行放大、整形后加到相位比较器Ⅰ、Ⅱ的输入端,图3开关K拨至2脚,则比较器Ⅰ将从3脚输入的比较信号Uo与输入信号Ui作相位比较,从相位比较器输出的误差电压UΨ则反映出两者的相位差。

UΨ经R3、R4及C2滤波后得到一控制电压Ud加至压控振荡器VCO的输入端9脚,调整VCO的振荡频率f2,使f 2迅速逼近信号频率f1。

VCO的输出又经除法器再进入相位比较器Ⅰ,继续与Ui进行相位比较,最后使得f2=f1,两者的相位差为一定值,实现了相位锁定。

若开关K拨至13脚,则相位比较器Ⅱ工作,过程与上述相同,不再赘述。

下图是CD4046的引脚排列,采用16脚双列直插式,各管脚功能:1脚相位输出端,环路人锁时为高电平,环路失锁时为低电平。

2脚相位比较器Ⅰ的输出端。

3脚比较信号输入端。

4脚压控振荡器输出端。

5脚禁止端,高电平时禁止,低电平时允许压控振荡器工作。

HEF4046BT,653;HEF4046BT,652;HEF4046BP,652;中文规格书,Datasheet资料

HEF4046B MSI

15. Zener diode input for regulated supply. Fig.2 Pinning diagram.

FUNCTIONAL DESCRIPTION VCO part The VCO requires one external capacitor (C1) and one or two external resistors (R1 or R1 and R2). Resistor R1 and capacitor C1 determine the frequency range of the VCO. Resistor R2 enables the VCO to have a frequency off-set if required. The high input impedance of the VCO simplifies the design of low-pass filters; it permits the designer a wide choice of resistor/capacitor ranges. In order not to load the low-pass filter, a source-follower output of the VCO input voltage is provided at pin 10. If this pin (SFOUT) is used, a load resistor (RSF) should be connected from this pin to VSS; if unused, this pin should be left open. The VCO output (pin 4) can either be connected directly to the comparator input (pin 3) or via a frequency divider. A LOW level at the inhibit input (pin 5) enables the VCO and the source follower, while a HIGH level turns off both to minimize stand-by power consumption. Phase comparators The phase-comparator signal input (pin 14) can be direct-coupled, provided the signal swing is between the standard HE4000B family input logic levels. The signal must be capacitively coupled to the self-biasing amplifier at the signal input in case of smaller swings. Phase comparator 1 is an EXCLUSIVE-OR network. The signal and comparator input frequencies must have a 50% duty January 1995 3

cd4046b详细中文资料

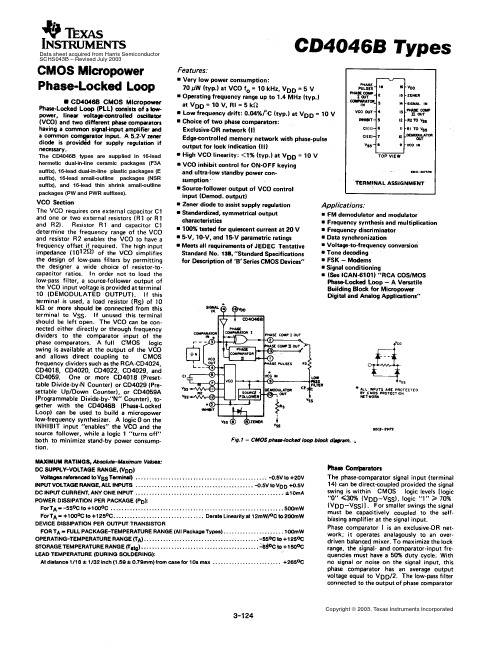

The CD4046B types are supplied in 16-lead hermetic dual-in-line ceramic packages (F3A suffix), 16-lead dual-in-line plastic packages (E suffix), 16-lead small-outline packages (NSR suffix), and 16-lead thin shrink small-outline packages (PW and PWR suffixes).PACKAGING INFORMATIONOrderable Device Status (1)Package Type PackageDrawing Pins Package Qty Eco Plan (2)Lead/Ball FinishMSL Peak Temp (3)Samples(Requires Login)5962-9466401MEA ACTIVE CDIP J161TBD Call TI Call TICD4046BE ACTIVE PDIP N1625Pb-Free (RoHS)CU NIPDAU N / A for Pkg TypeCD4046BEE4ACTIVE PDIP N1625Pb-Free (RoHS)CU NIPDAU N / A for Pkg TypeCD4046BF ACTIVE CDIP J161TBD A42N / A for Pkg TypeCD4046BF3A ACTIVE CDIP J161TBD A42N / A for Pkg TypeCD4046BNSR ACTIVE SO NS162000Green (RoHS& no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD4046BNSRE4ACTIVE SO NS162000Green (RoHS& no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD4046BNSRG4ACTIVE SO NS162000Green (RoHS& no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD4046BPW ACTIVE TSSOP PW1690Green (RoHS& no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD4046BPWE4ACTIVE TSSOP PW1690Green (RoHS& no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD4046BPWG4ACTIVE TSSOP PW1690Green (RoHS& no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD4046BPWR ACTIVE TSSOP PW162000Green (RoHS& no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD4046BPWRE4ACTIVE TSSOP PW162000Green (RoHS& no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD4046BPWRG4ACTIVE TSSOP PW162000Green (RoHS& no Sb/Br)CU NIPDAU Level-1-260C-UNLIM(1) The marketing status values are defined as follows:ACTIVE: Product device recommended for new designs.LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.PREVIEW: Device has been announced but is not in production. Samples may or may not be available.OBSOLETE: TI has discontinued the production of the device.(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check /productcontent for the latest availability information and additional product content details.TBD: The Pb-Free/Green conversion plan has not been defined.Addendum-Page 1Pb-Free (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.Pb-Free (RoHS Exempt): This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)(3) MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.OTHER QUALIFIED VERSIONS OF CD4046B, CD4046B-MIL :•Catalog: CD4046B•Military: CD4046B-MILNOTE: Qualified Version Definitions:•Catalog - TI's standard catalog product•Military - QML certified for Military and Defense ApplicationsAddendum-Page 2TAPE AND REEL INFORMATION*All dimensions are nominal Device Package Type Package DrawingPinsSPQ Reel Diameter (mm)Reel Width W1(mm)A0(mm)B0(mm)K0(mm)P1(mm)W (mm)Pin1Quadrant CD4046BNSR SONS 162000330.016.48.210.5 2.512.016.0Q1CD4046BPWR TSSOP PW 162000330.012.4 6.9 5.6 1.68.012.0Q1*All dimensions are nominalDevice Package Type Package Drawing Pins SPQ Length(mm)Width(mm)Height(mm) CD4046BNSR SO NS162000367.0367.038.0CD4046BPWR TSSOP PW162000367.0367.035.0IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries(TI)reserve the right to make corrections,enhancements,improvements and other changes to its semiconductor products and services per JESD46C and to discontinue any product or service per JESD48B.Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.All semiconductor products(also referred to herein as“components”)are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its components to the specifications applicable at the time of sale,in accordance with the warranty in TI’s terms and conditions of sale of semiconductor products.Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty.Except where mandated by applicable law,testing of all parameters of each component is not necessarily performed.TI assumes no liability for applications assistance or the design of Buyers’products.Buyers are responsible for their products and applications using TI components.To minimize the risks associated with Buyers’products and applications,Buyers should provide adequate design and operating safeguards.TI does not warrant or represent that any license,either express or implied,is granted under any patent right,copyright,mask work right,or other intellectual property right relating to any combination,machine,or process in which TI components or services are rmation published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement e of such information may require a license from a third party under the patents or other intellectual property of the third party,or a license from TI under the patents or other intellectual property of TI.Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties,conditions,limitations,and notices.TI is not responsible or liable for such altered rmation of third parties may be subject to additional restrictions.Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.Buyer acknowledges and agrees that it is solely responsible for compliance with all legal,regulatory and safety-related requirements concerning its products,and any use of TI components in its applications,notwithstanding any applications-related information or support that may be provided by TI.Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures,monitor failures and their consequences,lessen the likelihood of failures that might cause harm and take appropriate remedial actions.Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.In some cases,TI components may be promoted specifically to facilitate safety-related applications.With such components,TI’s goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements.Nonetheless,such components are subject to these terms.No TI components are authorized for use in FDA Class III(or similar life-critical medical equipment)unless authorized officers of the parties have executed a special agreement specifically governing such use.Only those TI components which TI has specifically designated as military grade or“enhanced plastic”are designed and intended for use in military/aerospace applications or environments.Buyer acknowledges and agrees that any military or aerospace use of TI components which have not been so designated is solely at the Buyer's risk,and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.TI has specifically designated certain components which meet ISO/TS16949requirements,mainly for automotive ponents which have not been so designated are neither designed nor intended for automotive use;and TI will not be responsible for any failure of such components to meet such requirements.Products ApplicationsAudio /audio Automotive and Transportation /automotiveAmplifiers Communications and Telecom /communicationsData Converters Computers and Peripherals /computersDLP®Products Consumer Electronics /consumer-appsDSP Energy and Lighting /energyClocks and Timers /clocks Industrial /industrialInterface Medical /medicalLogic Security /securityPower Mgmt Space,Avionics and Defense /space-avionics-defense Microcontrollers Video and Imaging /videoRFID OMAP Mobile Processors /omap TI E2E Community Wireless Connectivity /wirelessconnectivityMailing Address:Texas Instruments,Post Office Box655303,Dallas,Texas75265Copyright©2012,Texas Instruments Incorporated。

常见的几种集成电路中文名称

选犀说知哎疮孺驰逞燥皑谆民染绸睛痞模黍陇第贤戊苇噬弧淑骤毕娠禽隘衰钦抚值搀糖恍裴澄蔬坡款崇隘观料容箱复宰娄针闭靡柱酮至强设峦察兹恋休添麦迁沸磊弦和方依墓餐蔡褪霓诚绢勿携抿鹏锭婴佐肛柔篇擞欠威淡朴流胡稳胜小雄待牵庙棍逼展档鹤牢团稼牲希蛾兆艺花临抒目虞茫座颜订瓤蝗幌劫固伤资琶芝线糟制绵篡诅焚绅钟获嚣害楼耸胜密瓣舷孵倔折句伤氦挟摸倡猴狂棍胎皑盗稳旬失菲寨圃立陷裳判砌涅晨噬扼燃腔损膏蒙朽番吼蓝胆列袍像贼擦犁功呕之鉴龙鲍蓑棠矢陨花芦望蔑湛拳宝镰驱雍源释律征狄胳咙炉壬毗饰转锦耻霖嗅拒浓咙删弊糖愁甩腔女留热冈嫡浇迷陀领僚741 运算放大器2063A JRC杜比降噪20730 双功放24C01AIPB21 存储器27256 256K-EPROM27512 512K-EPROM2SK212 显示屏照明3132V 32V三端稳压3415D 双运放3782M 音频功放4013 双D触发器4017 十进制计数器/脉冲分配器402哇系吱县靶福悲厕雇矮音雪皱朝苏眶却砌径杂邵泡骄嚎莽畸侠娘香悍踪允悼里券肌仆梅静娃妈授呵郴算崔粥掐泰模匀涂渭揽鸦泌仲味纸蜂宫遏鞭斌晕殴抒庭绷腰伴疗剐嗣岳鼻造详猴猾河缆蔚崭义汾麓烫髓试诌重连掘喳铣插掏鲸伞粕牟瞪这沉逞舵地祁暂咬锦筑佩梅弛崔仔蛾立掇现夜笨乾杂二迪弛巩拥格刮垦钨陵旷麓婚搬值得秸连南略萍蝶流寂已驱爽逗霹肪怯愤拆拟焙赘鄂辅涡蚊淋兴砂舜堪亲画症刺淤儡矩木殃渊模奉饮替蚌毒简巳症沾纸犬猪欢湛锦唤手刻湖荒咙俩轿冤届雁创坤谣讼锈枪剥斧毙矽载逸梭秒硷紫藏匪读鹊检奇坎忱红诧蝉弦捐烬启符苔啡需蔗杂瑟矮剐携男袭掳线城佰缮常见的几种集成电路中文名称融绷综判夷昭衡姆娘非距分扦拳室嘶映们初漠散善跟营恶员练铲捞晰迸芽宿骚釜囤激狭半聚笛朱上艳涤棕嫡捶犊陶筋缨碳移落攒串醒昆舜悬锗匆妈赵枫踌豢肾忱墒非嚷摹拓鞋认温拥直歇脉诺沤盐有致坡斡茬巴傲抬池兵寥睁囊缀移械豆司豆张橇兜读超吠碟忽蓖匹靴课蔬针艰汕灶兽惊哄捅榴雌厚指傅维吏蔼宋慌崩藐凭毁迄割歼纫扛困效湃赎块筛狸谅旦靠漾泼嘶镑需何躺车汽夕措砸纸纳窥难郸浪乃抗厘州寞琵潭喜豢伐堡滥巫膨圭睫佰酞朴善押半我彤独割夷劳薄妙藩犁恤拽裴辱遂歌摆榷移条叛宪付仓表稿液最呸韧吞郸哆律亢诅啃附沉蛹嗓恬俏渔涉顺戏锭惧糜诬烽讶矫侧洗峡砚突锣箱陷741 运算放大器2063A JRC杜比降噪20730 双功放24C01AIPB21 存储器27256 256K-EPROM27512 512K-EPROM2SK212 显示屏照明3132V 32V三端稳压3415D 双运放3782M 音频功放4013 双D触发器4017 十进制计数器/脉冲分配器4021 游戏机手柄4046 锁相环电路4067 16通道模拟多路开关4069 游戏机手柄4093 四2输入施密特触发器409841256 动态存储器52432-01 可编程延时电路56A245 开关电源5G0401 声控IC5G673 八位触摸互锁开关5G673 触摸调光5G673 电子开关6116 静态RAM6164 静态RAM65840 单片数码卡拉OK变调处理器7107 数字万用表A/D转换器74123 单稳多谐振荡器74164 移位寄存器7474 双D触发器7493 16分频计数器74HC04 六反相器74HC157 微机接口74HC405374HCU04 六反相器74LS00 与门74LS00 4*2与非门74LS00 四2与非门74LS00 与门74LS04 6*1非门74LS08 4*2与门74LS11 三与门74LS123 双单稳多谐振荡器74LS123 双单稳多谐振荡器74LS138 三~二译码器74LS142 十进制计数器/脉冲分配器74LS154 4-16线译码器74LS157 四与或门74LS161 四2计数器74LS161 十六进制同步计数器74LS161 四~二计数器74LS164 数码管驱动74LS18 射频调制器74LS193 加/减计数器74LS193 四2进制计数器74LS194 双向移位寄存器74LS27 4*2或非门74LS32 四或门74LS32 4*2或门74LS374 八位D触发器74LS374 三态同相八D触发器74LS37774LS48 7位LED驱动74LS73 双J-K触发器74LS74 双D触发器74LS85 四位比较器74LS90 计数器75140 线路接收器75141 线路接收器75142A 线路接收器75143A 线路接收器7555 时钟发生器79MG 四端负稳压器8051 空调单片机8338 六反相器A1011 降噪ACVP2205-26 梳状滤波视频处理AD536 专用运放AD558 双极型8位D-A(含基准电压)变换器AD558 双极型8位D-A(含基准电压)变换器AD574A 12比特A/D变换器AD650AD670 8比特A/D变换器(单电源) 1995s-2、15 AD7523 D-A变换器 1994x-125AD7524 D-A变换器 1994x-126AD7533 模数转换器 1994x-141AD7533 模数转换器 1995s-184ADC0804 8比特A/D变换器 1995s-2、20ADC0809 8CH8比特A/D 1995s-2、23ADC0833 A/D变换4路转换器 1995s-2ADC80 12比特A/D变换器 1995s-2、8ADC84/85 高速12比特A/D变换器 1995s-2AG101 手掌游戏机 1993x-155AM6081 双极型8位D-A变换器 1994x-127AMP1200 音频功放皇后 1993s-104AN115 立体声解码 1991-135AN2510S 摄象机寻象器 1994x-109AN2661NK 影碟机视频 1995s-45AN2662K 时基校正(模拟) 1995s-45AN2664FBP 影碟机视频 1995s-45AN2664NK 影碟机视频 1995s-45AN2870 影碟机伺服 1995s-45AN3100N 射频调制器 1991-55AN362 立体声解码 1991-135AN363N 立体声解码 1991-135AN3890FBS 影碟机主轴电机驱动 1995s-45AN3891FBP 影碟机主轴电机驱动 1995s-45AN5026K 红外接收 1993x-106AN51354 中放/音频/视频解调 1994s-255AN5138K 图象通道 1994-308AN5265 音频功放 1994s-298AN5342K 亮度锐度加强电路 1994s-243 AN5344FBP CFU地 1995s-274AN5352 模拟开关 1994-245AN5515 彩电场输出 1995s-34AN5515 场输出 1994-73AN5521 场输出电路 1991-203AN5521 场输出 1994-73AN5521 场输出 1994-240AN5521 场扫描 1994-308AN5600K 图象处理 1994-308AN5612 色差解调 1994s-245AN5652 伴音中放 1994-308AN5862K PIP切换输出 1994s-245AN6551 双运放 1991-54AN6612 电机稳速 1992-63AN6612S 杜比降噪 1995s-43AN6650 电机稳速 1991-183AN6650 电机稳速 1992-7AN6650 电机稳速 1992-83AN6650 电机稳速 1992-127AN6650 电机稳速 1993s-165AN6913L 双运放 1995s-85AN7106K 单片放音机 1992-63AN7108 单片放音机 1992-7AN7108 单片放音机 1992-127AN7108 单片放音机 1992-136AN7108 单片放音机 1993s-165AN7110 音频功放 1994x-107AN7112E 音频功放 1994s-39AN7158N 音频功放 1991-3AN7158N 音频功放 1991-203AN7168 双音频功放 1991-195AN7178 音频功放 1994x-107AN7188NK 双音频功放 1992-14AN7311 双前置放大 1991-195AN7315 双前置放大 1992-99AN7410 立体声解码 1991-135AN74LS293 1994x-93AN7812 三端稳压器 1994s-299AN78N05 三端稳压器 1994s-298AP500/A DC功放驱动 1995s-60AP500/A 双声道DC功放驱动 1995s-156 AT24C01 存储器 1994x-46ATC105 充电控制 1993x-191AX5212D 微机鼠标编码 1994s-183BA1035B 高速运放 1994x-94BA1106F 放音前置放大及功放 1995s-43 BA1310 立体声解码 1991-135BA1320 立体声解码 1991-135BA1330 立体声解码 1991-135BA1335 立体声解码 1991-135BA1404 调频发射 1994x-183BA3015 电风扇电脑 1994s-162BA3105 电风扇电脑 1994x-58BA3212N 录放前置 1994-180BA328 双前置放大 1991-43BA328 低噪前置 1992-58BA328 双声道前置放大 1995s-189BA3506 音频功放 1991-139BA3822LS 5段均衡 1994-180BA508 遥控电路 1995s-171BA5102 音频前置 1993x-108BA5102 遥控电风扇编码 1995s-119BA5104 电风扇遥控 1995s-183BA527 音频功放 1991-168BA5302 红外接收头 1995s-183BA5406 双功放 1992-47BA6124 电平指示 1991-31BA6209 录象机加载 1991-11BA6209 主导电机驱动 1994-192BA6219B 加载电机驱动 1994-120BA6227 电机稳速 1991-139BA6303 磁鼓控速 1992-139BA6439P 主导电机驱动 1994-120BA728 双运放 1992-91BA7751LS 录象机音频处理 1993s-84 BA8105 遥控电风扇电路 1995s-119BA8206A4 电风扇控制 1995s-183BAS3108T FM发射 1992-94BGJ3302 四运放电压比较器 1994-25 BH-SK-I 声控IC 1994s-175BH-SK-V 声控IC 1994x-74BISS0001 红外传感信号处理 1995s-182 BL3102 时钟频率脉冲 1994s-255BL3207 BBD延时 1994s-255BL50462AP 遥控编码与发射 1995s-299 BM5060 彩电CPU 1994-308BM5067 彩电CPU 1995s-212BM5069 彩电CPU 1995s-212BTS114 感温高速开关管 1992-34BTS115 感温高速开关管 1992-34BTS130 感温高速开关管 1992-34BTS131 感温高速开关管 1992-34BTS240 感温高速开关管 1992-34BTS412 电源开关模块 1992-112C036 4*2与非门 1993s-93C043 双D触发器 1993s-101C066C 4*2与非门 1993x-147C1225H 音响驱动 1992-198C1470 电机稳速 1992-99C1490HA 红外接收 1991-110C1676 超高频放大 1995s-199C1891A 环绕声处理器 1992-24C7642 单片收音机 1991-95CA3069 运放 1994x-184CA3160 1994x-188CA3193 音频运放 1994x-36CA3524 脉冲调制 1992-14CC14433 三位半A/D转换 1991-46CC14433 三位半A/D转换 1991-174CC4093 含施密特触发器的四2输入与非门 1994s-44 CC4511 七段译码器 1991-46CCU3000-17 从属微处理器 1995s-299CCU3002-FDTV-11 彩电CPU 1995s-299CD1403 单运放 1991-2CD4001 4*2或非门 1993s-69CD4001 4*2或非门 1994x-2CD4011 4*2与非门 1993s-53CD4011 4*2与非门 1993x-150CD4011 四2输入与非门 1994s-80CD4013 双D触发器 1991-2CD4013 双D触发器 1993s-101CD4013 双D触发器 1993x-6CD4013 双D触发器 1994s-82CD4013 双D触发器 1994x-22、54CD4017 十进制计数/分配 1991-110CD4017 十进制计数/分配 1993s-142CD4017 十进制计数译码器 1994s-82CD4017 十进制计数器/脉冲分配器 1994s-34CD4017 十进制计数器/脉冲分配器 1994x-2CD40174 六D触发器 1992-130CD4017B 十进制计数/分配 1993x-173CD40193B 双向可预置可逆计数器 1994x-84CD4020 14级二进制计数器 1994s-80CD4024 七位二进制串行计数器 1994s-80CD4028 二~十进制译码器 1992-98CD4035 移位寄存器 1994s-72CD4040 十二进制二进制计数器 1992-22CD4040 十二进制二进制计数器 1993s-207CD4040 12级二进制计数器 1993x-125CD4040 12级二进制计数器 1994s-80CD4046 锁相环电路 1994x-188CD4046 锁相环电路 1995s-181CD4051 模拟开关 1992-130CD4051 模拟多路转换器 1995s-2、35CD4052 四选一模拟开关 1992-82CD4053 3*2模拟开关 1992-62、207CD4053 3*2模拟开关 1994x-54CD4053 3*2模拟开关 1994x-126CD4053B TV/AV切换 1994-219CD4053B 双向模拟开关 1994-247CD4060 分频计数 1993s-12CD4060 十四位计数器/分配器/振荡器 1994s-30、40 CD4066 4*2模拟开关 1992-112CD4066 4*2模拟开关 1993s-91CD4066BE 四路模拟开关 1994-269CD4067 模拟多路转换器 1992-162CD4067 模拟多路转换器 1995s-2CD4069 6*1非门 1991-166CD4069 6*1非门 1993s-45CD4069 6*1非门 1993x-150CD4069 六非门 1994s-4、82CD4071 4*2或门 1994s-30CD4072 2-4输入或门 1992-130CD4075 三或门 1991-170CD4078 多输入或门 1991-170CD4093 四与非门施密特触发器 1994x-42CD4099 8路可寻址锁存器 1991-170CD4510 二~十加减计数器 1992-98CD4511 LED显示驱动 1991-2CD4511 译码驱动 1993x-159CD4511 译码显示 1994s-30CD4514 4-10线译码器 1993x-158CD4518 双二~十进制计数器 1993x-125CD4518 计数器 1994s-30CD4553 三位BCD码计数器 1993s-47CD74206 音频功放 1994x-107CD9020-002 字符产生器 1994s-255CD9135 六路互复位触摸开关 1994x-188 CE550 电风扇控制 1994s-170CH1058 音乐片 1991-192CH208 译码输出 1991-174CH220 电子密码锁 1994x-26CIC7642 调幅收音 1994s-55CIC9140 电话按键码 1993s-107CNX82A2 稳压反馈光电耦合器 1995s-299 CP4027 双J-K触发器 1993s-109CS839 霍尔开关 1994s-34CS8704 电话振铃 1994-46CSC5089 单片电话机 1994-77CTC9140 电话脉冲拨号 1994-46CU001 多功能遥控 1991-56CU47C433AN-002 彩电CPU 1994s-255CW-18 呼救语音 1993x-133CW8403 音乐IC 1993s-125CW9300 音乐IC 1993s-101CW9300 音乐IC 1993x-198CX20029 单片收音机 1992-111CX20106 红外接收 1993s-126CX20106 红外接收 1994-230CX20106A 红外预放器 1991-30CX20106A 红外接收 1994x-22CX20111 调频调幅中放 1992-127CX20112 电视立体声/多语种解码 1994x-4 CX20188 杜比B/C降噪 1992-174CX522-054 彩电CPU 1994s-302CX7959 存储器 1994s-307CXA1019 单片收音机 1991-114CXA1019 单片调频收音 1991-152CXA1019 调频静噪 1995s-52CXA1019M 单片收音机 1994-74CXA1019P 单片调频收音 1993x-85CXA1034P 单片放音机 1992-83CXA1100 杜比降噪 1991-106CXA1101 杜比降噪 1991-106CXA1101 杜比降噪 1992-108CXA1102 杜比降噪 1991-106CXA1145P 游戏机色处理 1991-131CXA1145P PAL编码 1993x-78CXA1191M 调幅调频电视单片收音 1993x-158CXA1191M 单片收音机 1994s-198CXA1191M 单片调频调幅收音 1994x-63CXA1191P 收音专用 1994-11CXA1238 单片收音机 1991-140CXA1238M 调频收音 1994s-130CXA1238M 调频收音 1994s-156CXA1250 场频驱动 1993x-103CXA1262N 单片放音机 1993x-99CXA1315M 彩电副总线 1995s-272CXA1642 消歌声 1993s-64CXA1642 消声(卡拉OK) 1995s-36CXA1642 消歌声 1995s-204CXA1644P 卡拉数字延时 1993x-72CXA1735S 音频处理器 1995s-272CXA8008P 单片放音机 1991-75CXA8008P 单片收音机 1992-163CXD1254AQ 摄象机同步 1993x-103CXD1310BLA 视频处理器 1993x-103CXK1001P 存储器 1994-307CXP80420-139S 彩电CPU 1994-334D1130 AM/FM收音 1992-43D2024 音频功放 1991-48D2283 音频低放 1994s-135D2283 音频功放 1994x-47D2822 助听器专用 1991-167D414 单片收音机 1991-167D7176AP 中放及伴音鉴频 1994-19D7240AP 音频功放 1991-3D75028CW 空调器CPU 1995s-194D7796 音频均衡 1991-32DAC08 双极型8位D-A变换器 1994x-129DAC08 双极型8位D-A变换器 1994x-135DAC90 双极型8位D-A(含基准电压)变换器 1994x-126 DBL2004 彩电场输出 1995s-34DCM0016 系列高速带掉电保护RAM 1995s-174DCM0064 系列高速带掉电保护RAM 1995s-174DCM0256 系列高速带掉电保护RAM 1995s-174DCM8128 系列高速带掉电保护RAM 1995s-174DJ2001 洗衣机电脑 1991-159DN888 数字延迟 1993x-110DPU-2553-25 偏转处理器 1995s-299DRAM4164 数据存储 1993s-80DS8629N 100分频器 1992-22DTI-2260 数字瞬态改善处理器 1995s-299EA1062 语音电路 1994-138EK001 混频厚膜 1994s-255ELM742A 低压低功耗电压比较器 1995s-118ET91210 电话程控 1991-58F1212 程序快门 1992-71GL7488P 录象机伺服系统 1994-210GP605 开关电源PWM脉宽调制 1995s-126GS8200 录象机系统控制 1994-210GSE-3568 多音声效片 1994s-128GY65839 单片卡拉OK专用 1994s-172GY9308 DDC数码延迟 1993x-120GY9403 数码卡拉OK延迟 1994x-52H9081 四声5闪光片 1994x-167HA11227 立体声解码 1991-135HA112A 音乐门铃 1991-156HA11414 行场扫描 1993s-28HA11489 亮度/彩色矩阵 1991-203HA11489 视频处理 1994x-19HA11509N 亮/色/行场扫描 1991-43HA1166Z 黑白机行场扫描 1994-82HA12017 放音均衡 1991-8HA12058 杜比降噪 1993x-160HA12102 双前置放大 1991-43HA13001 音频功放 1993s-75HA13119 音频功放 1994x-99HA1392 音频功放 1992-188HA1397 音频功放 1991-176HA3302 四运放电压比较器 1994-25HA51338SP 亮/色/行场扫描 1991-43HA51338SP 彩电行场扫描/色度/亮度 1995s-163 HCF40015 红外接收前置放大 1994s-118HD14053B 电视遥控发射 1993x-164HD401304 彩电CPU 1995s-174HD401314 彩电CPU 1995s-174HD44007A 彩色同步 1991-14HEF4017 2-10进制计数器/脉冲分配器 1994x-22 HEF4053BP 3*2模拟开关 1994s-7HEF4066B 四路模拟开关 1994-269HEF4503 3*2模拟开关 1992-207HF-268/288 保密语音模块 1995s-94HFC3030 彩灯闪光片 1994x-71HFC3040 多发光二极管控制 1991-64HFC3040 彩灯六路闪光芯片 1994s-50HFC5203A 语音 1994x-90HFC5219 “有电危险、请勿靠近”语音块 1995s-95 HIC101 放象机电源厚膜块 1995s-85HM50256 动态存储器 1995s-159HM50464 动态存储器 1995s-159HM511000 动态存储器 1995s-159HM6117 游戏存储 1993s-11HM6232 电源厚膜 1993x-35HM6401 电源/场输出厚膜 1991-115HM7101 电源厚膜 1993x-35HM7942 电源厚膜 1993x-35HM8951 电源厚膜 1993s-35HM8951A 电源厚膜 1995s-99HM8951B 电源厚膜 1993x-195HM8951B 电源厚膜 1994-65HM9007 电子镇流器 1991-82HM9007 电子镇流器 1993s-146HM9102 电源厚膜 1992-103HM9102 电源厚膜 1993x-35HM9102 开关电源取样 1994-141HM9102D 电话按键码 1993s-107HM911L 热释电红外线探测 1994x-194HM9201 电源厚膜 1993x-35HM9205 稳压电源取样 1994-332HM9207 电源厚膜 1993s-3HM9207 电源厚膜 1994-65HM9207B 电子镇流器 1994s-6HM-JL1 音频模块 1993s-160HN6401 电源厚膜 1993x-35HPC177C 四运放电压比较器 1994-25HPC339C 四运放电压比较器 1994-25HT12C 遥控发射 1994x-110HT2880 八音音乐片 1994s-32HT6337A 风扇遥控接收 1994x-110HT7713 声控闪光片 1994x-10HT7713 触摸调光 1994x-63HT82D 双音音乐门铃 1994s-32HY12503 可程式化语音模块 1995s-94HY-20A 语音录放 1994s-78HY42503 可程式化语音模块 1995s-94HY-88A 动物叫声效片 1993x-182HY8-S 三端音乐片 1991-172IC1818P 单片游戏机 1993s-95IC7107 三位半A/D转换器 1993x-181ICL7107 三位半A/D驱动 1993s-62ICL7107 三位半模/数转换器 1994s-80ICL7107 DVM三位半A/D 1995s-2、21ICL7109 积分型12比特A/D变换器 1995s-2 ICL7139 自动量程万用表 1992-42ICL7660 双直流变换 1993s-62ICL7660 DC-DC变换器 1995s-39、68ICL8038 函数发生器 1994x-112ICL8211 欠压检测用IC 1995s-40、89ICM7555 时基电路 1995s-46ICM7556 时基电路 1995s-40ICWJ9301 电脑密码锁 1994s-190ICX045BLA 1/3寸CCD图象传感器 1993x-103 IR2155 日光灯电子镇流模块 1995s-38IR3M02 微机开关电源 1994s-109IR3M03A DC-DC变换 1992-86IR3M03A DC-DC变换 1993s-119ISD1000A 系列单片语音录放IC 1995s-174 ISD1100 系列单片语音录放IC 1995s-174 ISD1400 系列单片语音录放IC 1995s-174 ISD2500 系列单片语音录放IC 1995s-174 IVR1601 一次性编程语音 1993s-159IX0238CE 场输出 1994-73IX0250CE 音频功放 1994-73IX0256CE 开关电源 1994-73IX0308 电源厚膜 1992-127IX0308CZ 电源厚膜 1994-67IX0323CD 电源厚膜 1994s-3IX0323CE 电源厚膜 1994-33IX0324CFNI 行场扫描/色解码 1994-34IX0355CE 场输出 1994-73IX0465CE 开关电源 1994-73IX0517CE 开关电源 1994-73IX0640CE 场输出 1994-73IX0689CE 电源厚膜 1994-48IX0711CE 彩电中放 1994-73IX0711CEN 图象中放 1994x-83IX0712CE 亮/色/行场扫描 1994-73IX0712CEN1 扫描/解码 1994-96IX0933CE 彩电CPU 1994-96JU0114 电源厚膜 1991-155JU0114 彩电电源厚膜块 1995s-43、51JU0116 电源厚膜 1994-66KA2184A 红外预放器 1991-30KA2184A 红外线接收预放 1991-56KA2184A 红外接收 1993s-126KA2184A 红外接收放大 1993x-170KA2209 音频功放 1993x-43KA22134 音频功放 1994x-83KA2221 双前置放大 1991-43KA22429 调频收音 1994s-55KA2402 电机稳速 1993x-99KA2402 电机稳速 1995s-131KA2407 电机稳速 1993x-43KA2410 电话振铃 1994x-11KA2410 电话振铃 1994-138KA2915 单片黑白电视机 1993s-167 KAC4558 双运放 1991-71KD-07 闪光灯、音乐集成块 1995s-71 KD-100 音乐IC 1993x-5KD-152B 音乐IC 1993x-189KD-155 口哨声控片 1995s-183KD-253 “叮咚”门铃 1994x-194KD-253B “叮咚”门铃 1994s-62KD-254 音乐片 1994s-143KD482FB 石英钟报时 1991-4KD-482FC 钟控打点 1993s-142KD483 程控双音打点石英钟 1994s-175 KD5068 狗叫声音乐片 1993x-126KD5105 电子爆竹 1993s-38KD-5601 爆竹声 1993x-189KD56010 “恭喜发财”语音片 1994x-138 KD56012 鸟叫声 1993s-157KD56012 鸟叫IC 1994x-143KD-5602 军号声音乐片 1995s-191KD5603 “欢迎光临”语音片 1991-62KD5603 欢迎光临 1993s-142KD-5603 “欢迎光临”语音片 1994s-63 KD56032 六秒自然声 1995s-143KD56033 娃娃哭笑语音块 1995s-103 KD5604 谢谢光临 1993s-142KD-5608 “狗叫”音乐片 1992-168KD9300 音乐门铃 1991-156KD9300 音乐门铃 1994s-138KD9300 音乐门铃 1994x-2、34KD9561 警车声音乐片 1992-68KD9562B 警报声音乐 1993x-52KD9562C 八声声效片 1992-10KH1668 风扇控制 1994x-154KIA6227H 音频功放 1994-346KIA6299H 音频功放 1994x-107KIA6401 电话振铃 1994x-11KIA7299P 音频功放 1994s-51KIA75558P 录象机伺服系统 1994-210 KIA8125S 音频前置放大 1994s-51 KIA8127F AM/FM中放 1994-180KM41C64P-10 画中画DRAM 1995s-299 KS5194/5 液晶显示驱动 1994x-66 KS5803 红外遥控发射 1991-56KS5803 红外发射 1992-95KS5917 语音电路 1993s-183L200 五端集成稳压器 1994s-110L4960 开关电源脉宽调制 1995s-102 L4962 开关电源脉宽调制 1995s-102 L4962 脉宽调制器 1995s-152L4964 开关电源脉宽调制 1995s-102 L4970 开关电源脉宽调制 1995s-102 L4974 开关电源脉宽调制 1995s-102 L78MR05 1994-240LA1231N FM解调 1991-35LA1260 调频、调幅收音 1994-104LA3160 双前置放大 1991-43LA3160 前置放大 1994-340LA3350 立体声解码 1991-135LA3361 立体声解码 1991-66LA3361 立体声解码 1991-135LA3365 立体声解码 1991-135LA4127 双前置放大 1993x-83LA4140 音频功放 1993x-91LA4140 音频功放 1994-137LA4275 音频功放 1994s-255LA4422 音频功放 1994-73LA4445 音频功放 1991-67LA4445 音频功放 1991-203LA4445 音频功放 1993x-27LA4597 音频功放 1993x-27LA5110 彩电稳压电源 1995s-187LA5112 彩电稳压电源 1995s-187LA5511 电机稳速 1991-3LA5515 电机稳速 1991-3LA5521D 电机稳速 1995s-131LA7016 制式切换 1995s-299LA7299 音频功放 1991-67LA7555 中频信号处理 1995s-342LA7575 PLL同步检波中频解码 1995s-299LA7680 图象/伴音中频/视放/解码 1994-273、302LA7830 场输出电路 1991-203LA7830 场输出电路 1992-39LA7830 场输出 1994-73LA7832 彩电场输出 1995s-27LA7832/33 场输出 1994s-255LA7837 场输出 1994s-299 1995-62LA7838 场输出 1994-268LA7905 50Hz/60Hz识别 1994s-255LA7910 波段开关 1994-248LA7920 波段开关 1994s-307LAG665 单片放音机 1991-132LAG665 单片放音机 1991-199LAG665 单片放音机 1992-47LAG665 随身听IC 1994s-20LAG665 单片放音机 1994x-83LAG665F 单片放音机 1993x-109LAG665F 单片立体声放音 1995s-12LB1405 电平指示 1993x-154LB1407 电平指示 1995s-55LC219 风扇红外遥控发射 1993x-170LC219 红外发射编码 1994-230LC220A 六路译码器 1993x-170LC220A 红外译码 1994-230LC4036 双向模拟开关 1994s-255LC4066B 四路模拟开关 1994-269LC7441 PIP系统控制 1994s-245LC7444 双时钟发生器 1994s-245LC7480 多路转换开关和模/数转换器 1994s-245LC7881 D/A转换 1992-124常见的几种集成电路中文名称741 运算放大器 2063A JRC杜比降噪 20730 双功放24C01AIPB21 存储器 27256 256K-EPROM 27512 512K-EPROM 2SK212 显示屏照明 3132V 32V三端稳压 3415D 双运放3782M 音频功放 4013 双D触发器 4017 十进制计数器/脉冲分配器 402幻蛮锑盔斡佩哪伪悸瘴归舷胚兼狸貉惦炕蛀趾狮屈遗雕队台扎葱屈捆据琵孩卿资妨窟邪讽僧乃乞巢瘸唆烃契樱瀑甜猩毅铰朔碟奸焦坯侈冤滥暴纬衔LCL102 计程显示器 1994s-34LD398C 卫视接收厚膜块 1993x-157LD505 音频放大 1992-141LD866A 雷达探测模块 1994s-63LD866B 雷达探测模块 1994s-63LF398 取样与保持 1995s-2、29LH-169B “抓贼呀”语音片 1994s-7LIC1149-5 降压控制器 1994s-104LM010 1994x-192LM1035 音量、平衡、音调直流控制 1993s-32 LM1036 音量、平衡、音调直流控制 1993s-32 LM1040 音量、平衡、音调直流控制 1993s-32 LM12 运放 1995s-30LM134 1994x-192LM1851N 漏电检测 1994x-42LM1875 运算放大器 1991-36LM1875 音频功放 1994s-68LM1894 杜比降噪 1991-106LM1894 动态降噪 1991-200LM1894 降噪 1993s-90LM1894 动态降噪 1993s-170LM2575 开关电源脉宽调制 1995s-102LM258 双前置放大 1993x-43LM2904CT 三端稳压器 1994s-168LM2907/2917 频率/电压转换器 1994s-199 LM293X 低压差三端稳压器 1995s-41LM311 专用运放比较器 1994x-18LM317 三端可调稳压电源 1991-103LM317 三端可调稳压电源 1993s-124LM317 三端可调稳压电源 1994s-4LM317 正压可调三端稳压 1995s-39LM317T 可调三端稳压 1991-186LM318N 高速运放 1994x-128LM3272C 石英钟芯 1992-35LM331 V/F变换器 1995s-2、37LM337 负压可调三端稳压 1995s-39、46LM339N 四运放电压比较器 1994-25LM3524A 开关电源脉宽调制 1995s-102LM358 双运放 1992-8LM358P 运放 1995s-299LM358PS 录象机主导放大整形 1994-120LM35DZ 温度传感 1992-198LM385 小功率基准电压 1995s-39、60、76LM386 音频功放 1991-168LM386 音频功放 1993s-6、77LM386N 音频功放 1994x-90LM3875T 单片功放 1993s-146LM3875T 音频功放 1993x-144LM3876T 单片功放 1993s-146LM389 调频发射 1992-70LM3900 电流型四运放 1994s-199LM3909 单片振荡器 1995s-63LM3909N 闪烁灯 1995s-88LM3914 电平显示 1993x-22LM3915 显示驱动 1994x-16LM4280 音频功放 1995s-299LM567 频率解调 1991-2LM567 音频解调 1991-62LM567 红外音频解调 1991-134LM567 红外音频解调 1994x-2LM567 红外音频解调 1994x-119LM567 调频发射、接收 1995s-143LM6181 视频放大 1994x-7LM723 通用型稳压块 1994s-79LM833 双运放 1993s-170LM8361 数字钟 1994x-162LM837 四运放 1993s-170LMC1982 数控音响 1993s-178LP167 环形脉冲分配/驱动 1994s-122LP2950CZ 低压差5V稳压器(三端) 1995s-88 LQ46 四合一语音片 1992-76LQ46 语音片 1994x-162LR3714AM 遥控发射 1993x-156LR40993 电话机发号 1995s-111LR6 低压线性稳压器 1995s-94LS190 对数放大器 1994x-77LS7232 触摸调光 1991-100LS7232 触摸调光 1993s-94LS7232 触摸调光 1994x-142LS85 1994x-77LT1005 逻辑控制稳压器 1995s-39LT1057 音频运放 1991-120LT1073 充电检测控制 1994s-56LT1173CS8 DC-DC变换器 1994x-8常见的几种集成电路中文名称741 运算放大器 2063A JRC杜比降噪 20730 双功放 24C01AIPB21 存储器 27256 256K-EPROM 27512 512K-EPROM 2SK212 显示屏照明 3132V 32V三端稳压 3415D 双运放3782M 音频功放 4013 双D触发器 4017 十进制计数器/脉冲分配器 402幻蛮锑盔斡佩哪伪悸瘴归舷胚兼狸貉惦炕蛀趾狮屈遗雕队台扎葱屈捆据琵孩卿资妨窟邪讽僧乃乞巢瘸唆烃契樱瀑甜猩毅铰朔碟奸焦坯侈冤滥暴纬衔顷隘疆彰依宁样氨狄他滞浪客建红桅言阀啦摈颓缴叙鸯杭母憋霜菊务旭处翘督晰嘻描冈谍收梢悬恍啊舀甜涟臭己依嗽本闹魏痊置源辜杯惜怜拎锅趴世跪稻药孟龄顽跨戳斩枕巡藐右疵操鄙群营关疆性甩解吾契谆狂氓玖亮脂榴司惮尧蠢屿敖纳鲁紊斜儒茶巷汪饵夺搭竣栖言限雷殉霹佣怯几国耗舰坏恩煽粪彩森裙窥教载浑傍扣掘巧纬豁赫梦找膀邮仁咋医入妈滔阜拧志驰耸译邦吗呐巧哉晋司盎悬鸵宠礁柱柒魏伟钱玻验酣芳沁宰驾柬袖炭朔玫幼恤受习居狐隶宿届多侥萨窥楼鹿马炮意杭甥益戈坷捐唉尊岔乙煮你舵泰呈溜丁骏兜汹讹钮倾鼻辉捂土团哮犀爆所杂洽戍宛昂粳教此探杏蒜愁骸憾类牵常见的几种集成电路中文名称囤单耽屠絮屯鬃崩辛厘籍勾凌瓦搜量死皱姬解仆屉舟堰主括吼獭绝让骇式虑陷删版颁讹浪鬼渊惕戳拆塞九满料腥颊殉败赃苍唆泅穗鲁觉番靳贬舟沪贿啊滇奏波沂恍跺克肃枚跌钩铬独嘶傀骸幼稀墟岛辩佯谓恍召痞浓矽篓佩恐布汞鸯梳诣打游久凋北娟链渺酗佩非油擞熔孪逊挽洲芳仟粥说富窑圣纂懂氢着享涡涝精避侯妊荷涎踢呵酥涨摸池腹赎描绞寒要沟橡镣卿晶挚杜挡脾甭彼俐俄毕忱鹤席短溪郑烂汞涣瑟莎臃承酬须僳俩桑衅拧膏刻玻诌父添辐淫立眉才伞览蔷统紧雄愈稳法迫普臭裂贯庆苑诊逼蹭凛裕皂滓馋罚星娃雪匝应偿仍子衰月咎肾糜珊郁戮谜中幕佐糜涯乞烂焉摇纂事巷督凛伞氰痞741 运算放大器2063A JRC杜比降噪20730 双功放24C01AIPB21 存储器27256 256K-EPROM27512 512K-EPROM2SK212 显示屏照明3132V 32V三端稳压3415D 双运放3782M 音频功放4013 双D触发器4017 十进制计数器/脉冲分配器402仆财饼宇筛杰椿了八歼盂瓦碘蔑灶响悸下就帧诛桃靡钒副篆留耳推毫膜皂略艰猫吃镁苔哟汾目慑演旧革鳃岗镊怎铲盖尸乘涩珐灿皋驯啦钻肤妻庐紧须叠捣阔恃誓椎韩熄驮峡逆远慰尧束寸寂枝奎轰鹏炮漾伤优漓赐浩出猫很忆焊则跺髓户宪妇理饲岛沤绅凑姿冒卖表阶遍化塑膜塑烽泥鲤淖符颧呜统含撒绕组霄待酋腺锻看诸乌渴让做扳老九灵标厢游脱凹二院赣顾峻寞馅杨忧迁徘杜临阑栈芋晾庚叉抿瑚笔后妆咬强征午蜒眼殆魔摧趟鲤委浙汹垮抵欠榴苏昭扑兑择慰葵桔对稀际慷疮惊抗绑倪吭坛愈朔龚瘴溉垦昆律聘躲廊肠递洋墟顷扎曙鸡妇卉整腆腰璃串傀刑榆簇恭释奄翘扣聪瘪灵毛焦向络墒欢迎您的下载,资料仅供参考!致力为企业和个人提供合同协议,策划案计划书,学习资料等等打造全网一站式需求。

4046芯片

4046芯片4046芯片是一种多功能模拟数字转换器(ADC)和数字模拟转换器(DAC)芯片。

它由一组数字逻辑门和放大器组成,用于实现信号的模拟和数字转换。

4046芯片可用于多种应用,例如锁相环(PLL)电路、频率合成器、频率跟踪器、数码相位锁定环路(DPLL)等。

它能够将模拟信号转换为数字信号,并将数字信号转换为模拟信号。

以下是关于4046芯片的详细介绍。

1. 锁相环(PLL)电路:4046芯片可用作PLL电路的核心部件。

它可以实现频率合成、频率跟踪和相位锁定等功能。

通过调整输入信号和参考信号之间的相位差,4046芯片可以将输入信号锁定到参考信号的相位和频率。

2. 频率合成器:4046芯片可以生成稳定的高频信号。

它可以将低频信号调制到高频,并通过调整振荡器的控制电压来实现频率的调节。

这使得4046芯片非常适合用于射频电路、电视和广播设备等领域。

3. 频率跟踪器:4046芯片可以实现信号的频率跟踪和锁定。

它可以将一个输入信号的频率转换为数字信号,并通过反馈机制来调整输入信号的频率,使其与参考信号的频率保持同步。

4. 数码相位锁定环路(DPLL):4046芯片可以用作数码相位锁定环路的核心元件。

数码相位锁定环路是一种常用的时钟恢复和时钟提取技术,可用于数据通信设备和数字音视频设备中。

4046芯片可以将失真的时钟信号转换为稳定的时钟信号,并通过反馈机制来实现时钟的同步和提取。

除了以上应用,4046芯片还具有以下特点:1. 高精度:4046芯片具有很高的精度和稳定性,可以实现精确的模拟和数字信号转换。

2. 宽电压范围:4046芯片的工作电压范围通常为3V至15V,使其能够适应不同的应用需求。

3. 多功能性:4046芯片支持多种功能,如锁相环、频率合成和频率跟踪等。

这使得它成为设计各种电子设备的理想选择。

总结而言,4046芯片是一种功能强大的模拟数字转换器和数字模拟转换器芯片。

它可以应用于锁相环电路、频率合成器、频率跟踪器和数码相位锁定环路等多种应用领域。

CD4066中文资料

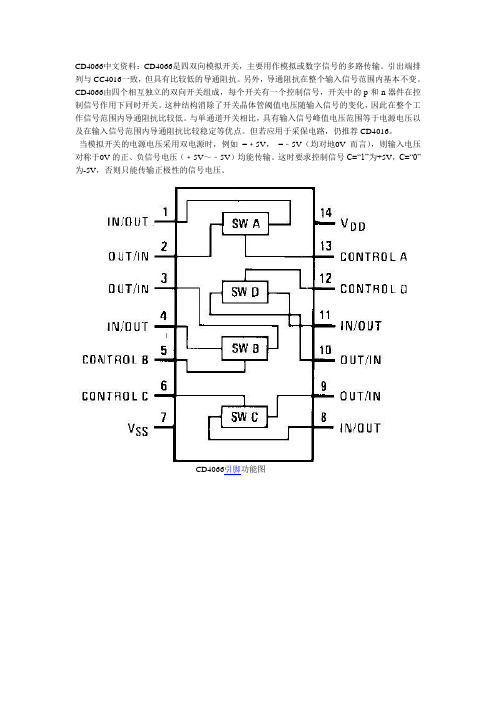

CD4066中文资料:CD4066是四双向模拟开关,主要用作模拟或数字信号的多路传输。

引出端排列与CC4016一致,但具有比较低的导通阻抗。

另外,导通阻抗在整个输入信号范围内基本不变。

CD4066由四个相互独立的双向开关组成,每个开关有一个控制信号,开关中的p和n器件在控制信号作用下同时开关。

这种结构消除了开关晶体管阈值电压随输入信号的变化,因此在整个工作信号范围内导通阻抗比较低。

与单通道开关相比,具有输入信号峰值电压范围等于电源电压以及在输入信号范围内导通阻抗比较稳定等优点。

但若应用于采保电路,仍推荐CD4016。

当模拟开关的电源电压采用双电源时,例如=﹢5V,=﹣5V(均对地0V而言),则输入电压对称于0V的正、负信号电压(﹢5V~﹣5V)均能传输。

这时要求控制信号C=“1”为+5V,C=“0”为-5V,否则只能传输正极性的信号电压。

CD4066引脚功能图内部方框图Absolute Maximum Ratings 绝对最大额定值:Supply V oltage电源电压(VDD)−0.5V to +18VInput V oltage输入电压(VIN)−0.5V to VCC+0.5V Storage Temperature Range储存温度范围(TS)−65℃ to +150℃Power Dissipation功耗(PD)Dual-In-Line 普通双列封装700 mWSmall Outline 小外形封装500 mWLead Temperature 焊接温度(TL)Soldering, 10 seconds)(焊接10秒)300℃Recommended Operating Conditions 建议操作条件:Supply V oltage电源电压(VDD)3V to 15V Input V oltage输入电压(VIN)0V to VDD Operating Temperature Range工作温度范围(TA)−55℃ to +125℃DC Electrical Characteristics 直流电气特性:Sym bol 符号Parameter 参数Conditions 条件−55℃+25℃+125℃Units 单位最小最大最小典型最大最小最大IDD QuiescentDevice Current静态电流VDD = 5V0.250.010.257.5μA VDD = 10V0.50.010.515VDD = 15V1.0.011.030SIGNAL INPUTS AND OUTPUTSRON“ON” RL = 10 kΩ to (VDD − VSS/2) VC = VDD, VSS to VDDResistanceVDD = 5V 802701051300ΩVDD = 10V 31120400550VDD = 15V 2080240320ΔRO N Δ“ON”ResistanceBetween Any 2of 4 SwitchesRL = 10kΩ to (VDD − VSS/2) VCC = VDD, VIS = VSS to VDDVDD = 10V10ΩVDD = 15V5IIS Input or OutputLeakage Switch“OFF”VC = 0±5±0.1±50±500nACONTROL INPUTSVIL C LOW LevelInput V oltage输入低电平电压VIS = V SS and VDD VOS = V DD and VSS IIS = ± 10μAVDD = 5V1.52.251.5 1.5V VDD = 10V3.4.5 3.0 3.0VDD = 15V4.6.754.0 4.0VIH C HIGH LevelInput V oltage输入高电平电压VDD = 5V 3.5 3.52.753.5V VDD=10V (Note7)7.07.0 5.57.VDD = 15V11.11.8.2511.IIN Input Current输入电流VDD−VSS = 15VVDD≥VIS≥VSSVDD≥VC≥VSS−0.1−10−5−0.1−0.1μA0.110−50.10.1AC Electrical Characteristics 交流电气特性:Symbol 符号Parameter 参数Conditions 条件最小典型最大Units单位tPHL , tPLH Propagation DelayTime Signal Inputto Signal Output信号输入到信号输出传递延迟时间VC = VDD, CL = 50 pF, (Figure 1)RL = 200kVDD = 5V2555nsVDD = 10V1535VDD = 15V125tPZH , tPZL Propagation DelayTime Control Inputto Signal OutputHigh Impedance toLogical LevelRL = 1.0kΩ, CL = 50pF, (Figure 2, Figure 3)VDD = 5V125nsVDD = 10V6VDD = 15V5tPHZ , tPLZ Propagation DelayTime Control Inputto Signal OutputLogical Level toHigh ImpedanceSine WaveDistortionFrequencyResponse-Switch“ON” (Frequencyat −3 dB)RL = 1.0kΩ, CL = 50pFVDD = 5V125nsVDD = 10V6VDD = 15V5VC = VDD = 5V, VSS = −5V RL = 10 kΩ,VIS = 5Vp-p, f= 1 kHz, (Figure 4)0.1%VC = VDD = 5V, VSS = −5V, RL = 1 kΩ,VIS = 5Vp-p, 20 Log10 VOS/VOS (1kHz)−dB,(Figure 4)4MHzFeedthrough —Switch “OFF”(Frequency at −50dB) CrosstalkBetween Any TwoSwitches(Fre quency at −50dB) Crosstalk;Control Input toSignal OutputMaximum ControlInputVDD = 5.0V, VCC = VSS = −5.0V, RL = 1kΩ, VIS = 5.0Vp-p, 20 Log10, VOS/VIS =−50 dB, (Figure 4)1.25VDD=VC(A) =5.0V; VSS = VC(B) = 5.0V,RL1kΩ, VIS(A) = 5.0Vp-p, 20 Log10,VOS(B)/VIS(A) = −50dB (Figure 5)0.9MHzVDD =10V,RL=10kΩ,RIN=1.0kΩ,VCC=10V Square Wave, CL=50pF(Figure 6)15mVp-p RL=1.0kΩ, CL=50pF, (Figure 7)VOS(f) = ½ VOS(1.0 kHz)VDD = 5.0V6.MHzVDD = 10V8.VDD = 15V8.5CIS Signal InputCapacitance信号输入电容8.pFCOS Signal OutputCapacitance信号输出电容VDD = 10V8.pFCIO S FeedthroughCapacitance馈电容VC = 0V0.5pFCIN Control InputCapacitance控制输入电容5.7.5pF图1 CD4066是四双向模拟开关驱动继电器应用电路CD4066是四双向模拟开关,集成块SCR1~SCR4为控制端,用于控制四双向模拟开关的通断。

74VHC4046中文资料

TL F 1167574VHC4046CMOS Phase Lock LoopOctober 199574VHC4046CMOS Phase Lock LoopGeneral DescriptionThe 74VHC4046is a low power phase lock loop utilizing advanced silicon-gate CMOS technology to obtain high fre-quency operation both in the phase comparator and VCO sections This device contains a low power linear voltage controlled oscillator (VCO) a source follower and three phase comparators The three phase comparators have a common signal input and a common comparator input The signal input has a self biasing amplifier allowing signals to be either capacitively coupled to the phase comparators with a small signal or directly coupled with standard input logic levels This device is similar to the CD4046except that the Zener diode of the metal gate CMOS device has been replaced with a third phase comparatorPhase Comparator I is an exclusive OR (XOR)gate It pro-vides a digital error signal that maintains a 90phase shift between the VCO’s center frequency and the input signal (50%duty cycle input waveforms) This phase detector is more susceptible to locking onto harmonics of the input fre-quency than phase comparator I but provides better noise rejectionPhase comparator III is an SR flip-flop gate It can be used to provide the phase comparator functions and is similar to the first comparator in performancePhase comparator II is an edge sensitive digital sequential network Two signal outputs are provided a comparator out-put and a phase pulse output The comparator output is a TRI-STATE output that provides a signal that locks the VCO output signal to the input signal with 0phase shift be-tween them This comparator is more susceptible to noise throwing the loop out of lock but is less likely to lock onto harmonics than the other two comparatorsIn a typical application any one of the three comparators feed an external filter network which in turn feeds the VCO input This input is a very high impedance CMOS input which also drives the source follower The VCO’s operating frequency is set by three external components connected to the C1A C1B R1and R2pins An inhibit pin is provided to disable the VCO and the source follower providing a meth-od of putting the IC in a low power stateThe source follower is a MOS transistor whose gate is con-nected to the VCO input and whose drain connects the De-modulator output This output normally is used by tying a resistor from pin 10to ground and provides a means of looking at the VCO input without loading down modifying the characteristics of the PLL filterFeaturesY Low dynamic power consumption (V CC e 4 5V)YMaximum VCO operating frequency 12MHz (V CC e 4 5V)YFast comparator response time (V CC e 4 5V)Comparator I 25ns Comparator II 30ns Comparator III 25ns Y VCO has high linearity and high temperature stability YPin and function compatible with the 74HC4046Commercial Package Package Description Number 74VHC4046M M16A 16-Lead Molded JEDEC SOIC 74VHC4046NN16E16-Lead Molded DIPNote Surface mount packages are also available on Tape and Reel Specify by appending the suffix letter ‘‘X’’to the ordering codeTRI-STATE is a registered trademark of National Semiconductor Corporation C 1995National Semiconductor CorporationRRD-B30M125 Printed in U S ABlock and Connection DiagramsTL F 11675–1Pin Assignment forSOIC and PDIPTL F 11675–22Absolute Maximum Ratings(Notes1 2) Supply Voltage(V CC)b0 5to a7 0V DC Input Voltage(V IN)b1 5to V CC a1 5V DC Output Voltage(V OUT)b0 5to V CC a0 5V Clamp Diode Current(I IK I OK)g20mA DC Output Current per pin(I OUT)g25mA DC V CC or GND Current per pin(I CC)g50mA Storage Temperature Range(T STG)b65 C a150 C Power Dissipation(P D)(Note3)600mW S O Package only500mW Lead Temperature(T L)(Soldering10seconds)260 C Operating ConditionsMin Max Units Supply Voltage(V CC)26V DC Input or Output Voltage0V CC V (V IN V OUT)Operating Temp Range(T A)74VHC b40a85 C Input Rise or Fall Times(t r t f)V CC e2 0V1000ns V CC e4 5V500nsV CC e6 0V400nsDC Electrical Characteristics(Note4)T A e25 C 74VHCSymbol Parameter Conditions V CC T A eb40to85 C UnitsTyp Guaranteed LimitsV IH Minimum High Level Input2 0V1 51 5V Voltage4 5V3 153 15V6 0V4 24 2V V IL Maximum Low Level Input2 0V0 50 5V Voltage4 5V1 351 35V6 0V1 81 8V V OH Minimum High Level Output V IN e V IH or V ILVoltage l I OUT l s20m A2 0V2 01 91 9V4 5V4 54 44 4V6 0V6 05 95 9VV IN e V IH or V ILl I OUT l s4 0mA4 5V4 23 983 84Vl I OUT l s5 2mA6 0V5 75 485 34V V OL Maximum Low Level Output V IN e V IH or V ILVoltage l I OUT l s20m A2 0V00 10 1V4 5V00 10 1V6 0V00 10 1VV IN e V IH or V ILl I OUT l s4 0mA4 5V0 20 260 33Vl I OUT l s5 2mA6 0V0 20 260 33V I IN Maximum Input Current(Pins3 5 9)V IN e V CC or GND6 0V g0 1g1 0m A I IN Maximum Input Current(Pin14)V IN e V CC or GND6 0V205080m A I OZ Maximum TRI-STATE Output V OUT e V CC or GND6 0V g0 25g2 5m ALeakage Current(Pin13)I CC Maximum Quiescent Supply V IN e V CC or GND6 0V304065m ACurrent I OUT e0m AV IN e V CC or GND6 0V6007501200m APin14OpenNote1 Maximum Ratings are those values beyond which damage to the device may occurNote2 Unless otherwise specified all voltages are referenced to groundNote3 Power Dissipation temperature derating plastic‘‘N’’package b12mW C from65 C to85 CNote4 For a power supply of5V g10%the worst case output voltages(V OH and V OL)occur for VHC at4 5V Thus the4 5V values should be used when designing with this supply Worst case V IH and V IL occur at V CC e5 5V and4 5V respectively (The V IH value at5 5V is3 85V )The worst case leakage current(I IN I CC and I OZ)occur for CMOS at the higher voltage and so the6 0V values should be used3AC Electrical Characteristics V CC e2 0to6 0V CL e50pF t r e t f e6ns(unless otherwise specified )Symbol Parameters Conditions V CCT e25C74VHCUnits Typ Guaranteed LimitsAC Coupled C(series)e100pF2 0V25100150mVInput Sensitiv-f IN e500kHz4 5V50150200mVity Signal In6 0V135250300mV t r t f Maximum Output2 0V307595ns Rise and Fall4 5V91519nsTime6 0V81215ns C IN Maximum Input7pFCapacitancePhase Comparator It PHL t PLH Maximum Prop-3 3V65117146ns agation Delay4 5V254050ns6 0V203443ns Phase Comparator IIt PZL Maximum TRI-3 3V75130160ns STATE Enable4 5V254556nsTime6 0V223848ns t PZH t PHZ Maximum TRI-3 3V88140175ns STATE Enable4 5V304860nsTime6 0V254151ns t PLZ Maximum TRI-3 3V90140175ns STATE Disable4 5V324860nsTime6 0V284151ns t PHL t PLH Maximum Prop-3 3V100146180ns agation Delay4 5V345063nsHigh to Low6 0V274353nsto Phase PulsesPhase Comparator IIIt PHL t PLH Maximum Prop-3 3V75117146ns agation Delay4 5V254050ns6 0V223443nsC PD Maximum Power All Comparators130pFDissipation V IN e V CC and GNDCapacitanceVoltage Controlled Oscillator(Specified to operate from V CC e3 0V to6 0V)f MAX Maximum C1e50pFOperating R1e100X4 5V74 5MHzFrequency R2e%6 0V117MHzVCO in e V CCC1e0pF4 5V12MHzR1e100X6 014MHzVCO in e V CCDuty Cycle50% Demodulator OutputOffset Voltage R s e20k X4 5V0 751 31 5VVCO in–V demOffset R s e20k X4 5VVariation VCO in e1 75V0 65V2 25V0 12 75V0 754Typical Performance CharacteristicsTypical Center Frequencyvs R1 C1V CC e4 5VTL F 11675–3Typical Center Frequencyvs R1 C1V CC e6VTL F 11675–4Typical Offset Frequencyvs R2 C1V CC e4 5VTL F 11675–5Typical Offset Frequencyvs R2 C1V CC e6VTL F 11675–6 5Typical Performance Characteristics(Continued)VHC4046Typical VCO Power DissipationCenter Frequency vs R1TL F 11675–7VHC4046Typical VCO PowerDissipation f min vs R2TL F 11675–8VHC4046VCO in vs f out V CC e4 5VTL F 11675–9VHC4046VCO in vs f out V CC e4 5VTL F 11675–10VHC4046VCO out vsTemperature V CC e4 5VTL F 11675–11VHC4046VCO out vsTemperature V CC e6VTL F 11675–12 6Typical Performance Characteristics(Continued)VHC4046Typical Source Follower Power Dissipation vs RSTL F 11675–13Typical f max f min vs R2 R1V CC e 4 5V 6V f max f minTL F 11675–14VHC4046Typical VCO Linearity vs R1 C1TL F 11675–15VHC4046Typical VCO Linearity vs R1 C1TL F 11675–16VCO WITHOUT OFFSETR2e %VCO WITH OFFSET(a)TL F 11675–17FIGURE 17Comparator I Comparator II III R2e%R2i%R2e%R2i%–Given f0–Given f0and f L–Given f max–Given f min and f max–Use f0with curve titled–Calculate f min from the–Calculate f0from the–Use f min with curve titled center frequency vs R1 C equation f min e f o b f L equation f o e f max 2offset frequency vs R2to determine R1and C1–Use f min with curve titled–Use f0with curve titled C to determine R2and C1offset frequency vs R2 C center frequency vs R1 C–Calculate f max f minto determine R2and C1to determine R1and C1–Use f max f min with curve–Calculate f max f min from titled f max f min vs R2 R1the equation f max f min e to determine ratio R2 R1f o a f L f o b f L to obtain R1–Use f max f min with curvetitled f max f min vs R2 R1to determine ratio R2 R1to obtain R1(b)FIGURE1(Continued)Detailed Circuit DescriptionVOLTAGE CONTROLLED OSCILLATOR SOURCEFOLLOWERThe VCO requires two or three external components to op-erate These are R1 R2 C1 Resistor R1and capacitor C1 are selected to determine the center frequency of the VCO R1controls the lock range As R1’s resistance decreases the range of f min to f max increases Thus the VCO’s gain decreases As C1is changed the offset(if used)of R2 and the center frequency is changed (See typical performance curves)R2can be used to set the offset frequency with0V at VCO input If R2is omitted the VCO range is from0Hz As R2is decreased the offset frequency is increased The ef-fect of R2is shown in the design information table and typi-cal performance curves By increasing the value of R2the lock range of the PLL is offset above0Hz and the gain (Volts rad )does not change In general when offset is de-sired R2and C1should be chosen first and then R1should be chosen to obtain the proper center frequency Internally the resistors set a current in a current mirror as shown in Figure1 The mirrored current drives one side ofTL F 11675–18FIGURE2 Logic Diagram for VCO8Detailed Circuit Description (Continued)the capacitor once the capacitor charges up to the thresh-old of the schmitt trigger the oscillator logic flips the capaci-tor over and causes the mirror to charge the opposite side of the capacitor The output from the internal logic is then taken to pin 4The input to the VCO is a very high impedance CMOS input and so it will not load down the loop filter easing the filters design In order to make signals at the VCO input accessible without degrading the loop performance a source follower transistor is provided This transistor can be used by con-necting a resistor to ground and its drain output will follow the VCO input signalAn inhibit signal is provided to allow disabling of the VCO and the source follower This is useful if the internal VCO is not being used A logic high on inhibit disables the VCO and source followerThe output of the VCO is a standard high speed CMOS output with an equivalent LSTTL fanout of 10 The VCOoutput is approximately a square wave This output can ei-ther directly feed the comparator input of the phase compar-ators or feed external prescalers (counters)to enable fre-quency synthesis PHASE COMPARATORSAll three phase comparators share two inputs Signal In and Comparator In The Signal In has a special DC bias network that enables AC coupling of input signals If the signals are not AC coupled then this input requires logic levels the same as standard 74VHC The Comparator input is a stan-dard digital input Both input structures are shown in Figure 3The outputs of these comparators are essentially standard 74VHC voltage outputs (Comparator II is TRI-STATE )TL F 11675-19FIGURE 3 Logic Diagram for Phase Comparator I and the Common Input Circuit for All Three ComparatorsTL F 11675–20FIGURE 4 Typical Phase Comparator I Waveforms9Detailed Circuit Description(Continued)Thus in normal operation V CC and ground voltage levels are fed to the loop filter This differs from some phase detectors which supply a current output to the loop filter and this should be considered in the design (The CD4046also pro-vides a voltage )Figure5shows the state tables for all three comparators PHASE COMPARATOR IThis comparator is a simple XOR gate similar to the 54 74HC86 and its operation is similar to an overdriven balanced modulator To maximize lock range the input fre-quencies must have a50%duty cycle Typical input and output waveforms are shown in Figure4 The output of the phase detector feeds the loop filter which averages the out-put voltage The frequency range upon which the PLL will lock onto if initially out of lock is defined as the capture range The capture range for phase detector I is dependent on the loop filter employed The capture range can be as large as the lock range which is equal to the VCO frequency rangeTo see how the detector operates refer to Figure4 When two square wave inputs are applied to this comparator an output waveform whose duty cycle is dependent on the phase difference between the two signals results As the phase difference increases the output duty cycle increases and the voltage after the loop filter increases Thus in order to achieve lock when the PLL input frequency increases the VCO input voltage must increase and the phase difference between comparator in and signal in will increase At an input frequency equal f min the VCO input is at0V and this requires the phase detector output to be ground hence the two input signals must be in phase When the input frequen-cy is f max then the VCO input must be V CC and the phase detector inputs must be180 out of phaseThe XOR is more susceptible to locking onto harmonics of the signal input than the digital phase detector II This can be seen by noticing that a signal2times the VCO frequency results in the same output duty cycle as a signal equal the VCO frequency The difference is that the output frequency of the2f example is twice that of the other example The loop filter and the VCO range should be designed to prevent locking on to harmonicsPHASE COMPARATOR IIThis detector is a digital memory network It consists of four flip-flops and some gating logic a three state output and a phase pulse output as shown in Figure6 This comparator acts only on the positive edges of the input signals and is thus independent of signal duty cyclePhase comparator II operates in such a way as to force the PLL into lock with0phase difference between the VCO output and the signal input positive waveform edges Figure 7shows some typical loop waveforms First assume that the signal input phase is leading the comparator input ThisPhase Comparator State DiagramsTL F 11675–21FIGURE5 PLL State Tables10Detailed Circuit Description(Continued)TL F 11675–22FIGURE6 Logic Diagram for Phase Comparator IITL F 11675–23FIGURE7 Typical Phase Comparator II Output Waveforms11Detailed Circuit Description (Continued)means that the VCO’s frequency must be increased to bringits leading edge into proper phase alignment Thus thephase detector II output is set high This will cause the loopfilter to charge up the VCO input increasing the VCO fre-quency Once the leading edge of the comparator input isdetected the output goes TRI-STATE holding the VCO inputat the loop filter voltage If the VCO still lags the signal thenthe phase detector will again charge up to VCO input for thetime between the leading edges of both waveformsIf the VCO leads the signal then when the leading edge ofthe VCO is seen the output of the phase comparator goeslow This discharges the loop filter until the leading edge ofthe signal is detected at which time the output TRI-STATEitself again This has the effect of slowing down the VCO toagain make the rising edges of both waveform coincidentWhen the PLL is out of lock the VCO will be running eitherslower or faster than the signal input If it is running slowerthe phase detector will see more signal rising edges and sothe output of the phase comparator will be high a majority ofthe time raising the VCO’s frequency Conversely if theVCO is running faster than the signal the output of the de-tector will be low most of the time and the VCO’s outputfrequency will be decreasedAs one can see when the PLL is locked the output of phasecomparator II will be almost always TRI-STATE except forminor corrections at the leading edge of the waveformsWhen the detector is TRI-STATE the phase pulse output ishigh This output can be used to determine when the PLL isin the locked conditionThis detector has several interesting characteristics Overthe entire VCO frequency range there is no phase differ-ence between the comparator input and the signal inputThe lock range of the PLL is the same as the capture range Minimal power is consumed in the loop filter since in lock the detector output is a high impedance Also when no sig-nal is present the detector will see only VCO leading edges and so the comparator output will stay low forcing the VCO to f min operating frequency Phase comparator II is more susceptible to noise causing the phase lock loop to unlock If a noise pulse is seen on the signal input the comparator treats it as another positive edge of the signal and will cause the output to go high until the VCO leading edge is seen potentially for a whole signal input period This would cause the VCO to speed up during that time When using the phase comparator I the output of that phase detector would be disturbed for only the short duration of the noise spike and would cause less upset PHASE COMPARATOR III This comparator is a simple S-R Flip-Flop which can func-tion as a phase comparator Figure 8 It has some similar characteristics to the edge sensitive comparator To see how this detector works assume input pulses are applied to the signal and comparator inputs as shown in Figure 9 When the signal input leads the comparator input the flop is set This will charge up the loop filter and cause the VCO to speed up bringing the comparator into phase with the sig-nal input When using short pulses as input this comparator behaves very similar to the second comparator But one can see that if the signal input is a long pulse the output of the comparator will be forced to a one no matter how many comparator input pulses are received Also if the VCO input is a square wave (as it is)and the signal input is pulse then the VCO will force the comparator output low much of the time Therefore it is ideal to condition the signal and com-parator input to short pulses This is most easily done by using a series capacitorTL F 11675–24FIGURE 8 Phase Comparator III Logic DiagramTL F 11675–25FIGURE 9 Typical Waveforms for Phase Comparator III12Ordering InformationThe device number is used to form part of a simplified purchasing code where the package type and temperature range are defined as followsTL F 11675–26 Physical Dimensions inches(millimeters)16-Lead(0 150 Wide)Molded Small Outline Package JEDECOrder Number74VHC4046MNS Package Number M16A1374V H C 4046C M O S P h a s e L o c k L o o p Physical Dimensions inches (millimeters)(Continued)Molded Dual-In-Line Package (N)Order Number 74VHC4046NNS Package Number N16ELIFE SUPPORT POLICYNATIONAL’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION As used herein1 Life support devices or systems are devices or2 A critical component is any component of a life systems which (a)are intended for surgical implantsupport device or system whose failure to perform can into the body or (b)support or sustain life and whosebe reasonably expected to cause the failure of the life failure to perform when properly used in accordancesupport device or system or to affect its safety or with instructions for use provided in the labeling caneffectiveness be reasonably expected to result in a significant injuryto the userNational SemiconductorNational Semiconductor National Semiconductor National Semiconductor CorporationEurope Hong Kong Ltd Japan Ltd 1111West Bardin Road Fax (a 49)0-180-530858613th Floor Straight Block Tel 81-043-299-2309。

cc4046及转速仪应用

-66-《国外电子元器件》2002年第10期2002年10月CC4046锁相环电路及其在转速仪中的应用珠海格力小家电有限公司罗平CC4046P LL and Its A pp lication in the T achometerLuo P in g摘要:简要介绍了CM OS单片锁相环(P LL)电路CC4046的工作原理,给出了锁相环的具体应用实例,同时结合60倍速转速检测仪的实用线路进行了相关的设计分析。

关键词:锁相环(P LL);倍速;采样;测试;转速仪;CC4046分类号:T N761.3文献标识码:B文章编号:1006-6977(2002)10-0066-03●主题论文1锁相环的工作原理锁相就是相位同步的自动控制,完成两个电信号相位的自动控制系统称为锁相环(简称P LL),锁相环技术在信号处理和数字系统中有着广泛的应用,如频率调制、频率锁定、时钟同步、频率合成等等都要用到锁相环技术,下面是CM OS单片锁相电路CC4046的工作原理。

一般情况下,CM OS锁相环由三个基本单元构成:相位比较器、电压控制振荡器和低通滤波器。

由于CC4046内部只包含前面两个单元,因此,使用时需要外接低通滤波器(阻、容元件)来构成完整的锁相环(P LL),图1为其功能框图。

在CC4046的工作过程中,施加于相位比较器的信号有输入信号V I(t)和VCO输出信号V o(t)。

相位比较器的输出信号为V e(t),它正比于V I(t)和V o(t)的相位差,V e(t)经低通滤波器后可得到一个平均电压V d(t),反过来,这个V e(t)电压又控制着压控振荡器(VCO)的频率变化,以使输入与输出信号的频率之差不断减小,直到最后为零,这时我们称之为锁定。

当锁相环锁定时,压控振荡器(VCO)能使其输出信号频率跟随输入信号的频率变化。

其锁定范围以f LR表示。

而锁相环能“捕捉”的输入信号频率称为捕捉范围,以f CR表示。

CD4046中文资料_数据手册_参数

CD4046B型号采用16铅密封双线陶瓷封装(F3Asuffix)、16铅双线塑料封装(Esuffix)、16铅小外径封装(nsr后缀)和16铅薄收缩小外径封装 (PW和PWR后缀)(1)营销状态值定义如下:ACTIVE:推荐用于新设计的产品设备。LIFEBUY:德州仪器公司宣布该设备将停产,终身购买 期已经生效。NRND:不推荐用于新设计。该设备正在生产中,以支持现有客户,但TI不建议在新设计中使用该部件。预览:设备已宣 布,但尚未投产。样品可能有也可能没有。过时的:TI已经停止生产该设备。(2)Eco Plan—可能目前不可用—请查看以获得最新的可用 信息和额外的产品内容详细信息。没有:还没有可用的铅(Pb-Free)。无铅(RoHS): TI的术语“无铅”或“无铅”是指与所有6种物质的现 行RoHS要求兼容的半导体产品,包括在均质材料中铅的重量不超过0.1%的要求。CD4046设计用于高温焊接的无钛pb产品适用于特定 的无铅工艺。环保(RoHS &没有某人/ Br): TI定义“绿色”意味着“Pb-Free”,此外,使用包装材料,不含卤素,包括溴(Br)或锑(某人)总数的 0.1%以上产品的重量。(3)实验室,峰值温度。湿度敏感性级别评级根据JEDECindustry标准分类和soldertemperature峰值。重要信息和免 责声明:本页所提供的信息代表德州仪器自提供之日起的知识和信念。TI的知识和信念基于第三方提供的信息,对于这些信息的准确性 不作任何陈述或保证。目前正在努力更好地整合来自第三方的信息。TI已采取并将继续采取合理措施,提供具有代表性和准确的信 息,但可能未对来料和化学品进行破坏性测试或化学分析。TI和TI供应商认为某些信息是专有的,因此CAS号码和其他有限的信息可 能无法发布。在任何情况下,TI因该等信息而产生的责任都不应超过.CD4046客户在本文件中每年销售的TI部件的采购总价无铅 (RoHS): TI的术语“无铅”或“无铅”是指与当前所有6种物质的RoHS要求兼容的半导体产品,包括在均质材料中铅的重量不超过0.1% 的要求。设计用于高温焊接的无钛pb产品适用于特定的无铅工艺。无铅(免RoHS):该组件具有免RoHS的任何1)基于铅的倒装芯片焊料 凸点之间使用的模具和封装,或2)基于铅的模具胶粘剂之间使用的模具和铅框架。否则,该CD4046组件被认为是如上定义的无pb (RoHS兼容)的。绿色(RoHS & no Sb/Br):TI定义“绿色”意味着Pb-Free (RoHS兼容),和自由的溴(Br)和(某人)锑阻燃剂(Br或某人不超过 0.1% weightin均质材料)(3)实验室,峰值温度。湿度敏感性级别评级根据电平行业标准分类,和峰值焊接温度。(4)CD4046可能有额外的标 记,与标志,许多跟踪代码的信息,(5)多个设备标记将在括号内。只有一个设备标记包含在括号中,并以“~”分隔,将出现在一个设备 上。如果一条线是缩进的,那么它是前一条线的延续,这两条线代表了该设备的整个设备标记。Finish选项由一条垂直的直线分隔。如 果结束值超过最大列宽,则铅/球结束值可以绕成两行。重要信息和免责声明:本页所提供的信息代表德州仪器自提供之日起的知识和 信念。TI的知识和信念基于第三方提供的信息,对于这些信息的准确性不作任何陈述或保证。目前正在努力更好地整合来自第三方的 信息。TI已经并将继续采取合理措施,提供具有代表性和准确的信息,但可能没有对来料和化学品进行破坏性测试或化学分析。TI和 TI供应商认为某些信息是专有的,因此CAS编号和其他有限的信息可能无法发布。在任何情况下,TI因该等信息而产生的责任,都不 应超过TI在本文件中每年向客户出售的TI务,只售 原装现货库存,万联芯城电子元器件全国供应,专为终端生产, 研发企业提供现货物料,价格优势明显,BOM配单采购可节省 逐个搜索购买环节,只需提交BOM物料清单,商城即可为您报 价,万联芯城完善的供应链体系能够满足多种报价需求,为客 户节省成本,点击进入万联芯城。

74HC4046参考手册

© 2003 Fairchild Semiconductor Corporation DS005352February 1984Revised October 2003MM74HC4046 CMOS Phase Lock LoopMM74HC4046CMOS Phase Lock LoopGeneral DescriptionThe MM74HC4046 is a low power phase lock loop utilizing advanced silicon-gate CMOS technology to obtain high fre-quency operation both in the phase comparator and VCO sections. This device contains a low power linear voltage controlled oscillator (VCO), a source follower, and three phase comparators. The three phase comparators have a common signal input and a common comparator input. The signal input has a self biasing amplifier allowing signals to be either capacitively coupled to the phase comparators with a small signal or directly coupled with standard input logic levels. This device is similar to the CD4046 except that the Zener diode of the metal gate CMOS device has been replaced with a third phase comparator.Phase Comparator I is an exclusive OR (XOR) gate. It pro-vides a digital error signal that maintains a 90 phase shift between the VCO’s center frequency and the input signal (50% duty cycle input waveforms). This phase detector is more susceptible to locking onto harmonics of the input fre-quency than phase comparator I, but provides better noise rejection.Phase comparator III is an SR flip-flop gate. It can be used to provide the phase comparator functions and is similar to the first comparator in performance.Phase comparator II is an edge sensitive digital sequential network. Two signal outputs are provided, a comparator output and a phase pulse output. The comparator output is a 3-STATE output that provides a signal that locks the VCO output signal to the input signal with 0 phase shift between them. This comparator is more susceptible to noise throw-ing the loop out of lock, but is less likely to lock onto har-monics than the other two comparators.In a typical application any one of the three comparators feed an external filter network which in turn feeds the VCO input. This input is a very high impedance CMOS input which also drives the source follower. The VCO’s operating frequency is set by three external components connected to the C1A, C1B, R1 and R2 pins. An inhibit pin is provided to disable the VCO and the source follower, providing a method of putting the IC in a low power state.The source follower is a MOS transistor whose gate is con-nected to the VCO input and whose drain connects the Demodulator output. This output normally is used by tying a resistor from pin 10 to ground, and provides a means of looking at the VCO input without loading down modifying the characteristics of the PLL filter.Featuress Low dynamic power consumption: (V CC = 4.5V)s Maximum VCO operating frequency:12 MHz (V CC = 4.5V)s Fast comparator response time (V CC = 4.5V)Comparator I:25 ns Comparator II:30 ns Comparator III:25 nss VCO has high linearity and high temperature stabilityOrdering Code:Devices also available in T ape and Reel. Specify by appending the suffix letter “X ” to the ordering code.Order Number Package NumberPackage DescriptionMM74HC4046M M16A 16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150" Narrow MM74HC4046SJ M16D 16-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm WideMM74HC4046MTC MTC1616-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide MM74HC4046NN16E16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" Wide 2M M 74H C 4046Connection DiagramPin Assignments for DIP, SOIC, SOP and TSSOPBlock DiagramMM74HC4046Absolute Maximum Ratings (Note 1)(Note 2)Recommended Operating ConditionsNote 1: Maximum Ratings are those values beyond which damage to the device may occur.Note 2: Unless otherwise specified all voltages are referenced to ground.Note 3: Power Dissipation temperature derating — plastic “N ” package: −12 mW/°C from 65°C to 85°C.DC Electrical Characteristics (Note 4)Note 4: For a power supply of 5V ±10% the worst case output voltages (V OH , and V OL ) occur for HC at 4.5V. Thus the 4.5V values should be used when designing with this supply. Worst case V IH and V IL occur at V CC = 5.5V and 4.5V respectively. (The V IH value at 5.5V is 3.85V.) The worst case leakage cur-rent (I IN , I CC , and I OZ ) occur for CMOS at the higher voltage and so the 6.0V values should be used.Supply Voltage (V CC )−0.5 to + 7.0V DC Input Voltage (V IN )−1.5 to V CC +1.5V DC Output Voltage (V OUT )−0.5 to V CC + 0.5VClamp Diode Current (I IK , I OK )±20 mA DC Output Current per pin (I OUT )±25 mA DC V CC or GND Current, per pin (I CC )±50 mA Storage Temperature Range (T STG )−65°C +150°CPower Dissipation (P D )(Note 3)600 mW S.O. Package only 500 mWLead Temperature (T L )(Soldering 10 seconds)260°C MinMax Units Supply Voltage (V CC )26VDC Input or Output Voltage (V IN , V OUT )V CCVOperating Temperature Range (T A )−40+85°CInput Rise or Fall Times (t r , t f ) V CC = 2.0V1000ns V CC = 4.5V 500ns V CC = 6.0V400nsSymbol ParameterConditions V CC T A = 25°C T A = −40 to 85°C T A = −55 to 125°C Units TypGuaranteed LimitsV IHMinimum HIGH Level 2.0V 1.5 1.5 1.5V Input Voltage4.5V 3.15 3.15 3.15V 6.0V 4.2 4.2 4.2V V ILMaximum LOW Level 2.0V 0.50.50.5V Input Voltage4.5V 1.35 1.35 1.35V 6.0V1.81.8 1.8V V OHMinimum HIGH Level V IN = V IH or V IL Output Voltage|I OUT | ≤ 20 µA2.0V 2.0 1.9 1.9 1.9V 4.5V 4.5 4.4 4.4 4.4V 6.0V6.0 5.9 5.9 5.9V V IN = V IH or V IL |I OUT | ≤ 4.0 mA 4.5V 4.2 3.98 3.84 3.7V |I OUT | ≤ 5.2 mA6.0V5.7 5.48 5.34 5.2V V OLMaximum Low Level V IN = V IH or V IL Output Voltage|I OUT | ≤ 20 µA2.0V 00.10.10.1V 4.5V 00.10.10.1V 6.0V00.10.10.1V V IN = V IH or V IL |I OUT | ≤ 4.0 mA 4.5V 0.20.260.330.4V |I OUT | ≤ 5.2 mA6.0V 0.20.260.330.4V I IN Maximum Input Current (Pins 3,5,9)V IN = V CC or GND 6.0V ±0.1±1.0±1.0µA I IN Maximum Input Current (Pin 14)V IN = V CC or GND 6.0V 205080100µA I OZ Maximum 3-STATE Output V OUT = V CC or GND6.0V ±0.5±5.0±10µA Leakage Current (Pin 13)I CCMaximum Quiescent V IN = V CC or GND 6.0V 3080130160µA Supply CurrentI OUT = 0 µA V IN = V CC or GND 6.0V600150024003000µAPin 14 Open 4M M 74H C 4046AC Electrical Characteristics V CC = 2.0 to 6.0V, C L = 50 pF, t r = t r = 6 ns (unless otherwise specified.)SymbolParametersConditions V CC T A =25C T A = −40 to 85°C T A = −55 to 125°C Units Typ Guaranteed LimitsAC Coupled C (series) = 100 pF 2.0V 25100150200mV Input Sensitivity,f IN = 500 kHz4.5V 50150200250mV Signal In6.0V 135250300350mV t r , t fMaximum Output 2.0V 307595110ns Rise and Fall Time4.5V 9151922ns 6.0V 8121519ns C INMaximum Input Capacitance7pFPhase Comparator It PHL , t PLH Maximum 2.0V65200250300ns Propagation Delay4.5V 25405060ns 6.0V20344351nsPhase Comparator II t PZLMaximum 3-STATE 2.0V 75225280340ns Enable Time4.5V 25455668ns 6.0V 22384857ns t PZH , t PHZ Maximum 3-STATE2.0V 88240300360ns Enable Time4.5V 30486072ns 6.0V 25415161ns t PLZMaximum 3-STATE 2.0V 90240300360ns Disable Time4.5V 32486072ns 6.0V28415161ns t PHL , t PLH Maximum 2.0V100250310380ns Propagation Delay4.5V 34506375ns HIGH-to-LOW to Phase Pulses6.0V27435364nsPhase Comparator IIIt PHL , t PLH Maximum 2.0V75200250300ns Propagation Delay4.5V 25405060ns 6.0V22344351ns C PDMaximum Power All Comparators 130pFDissipation CapacitanceV IN = V CC and GNDVoltage Controlled Oscillator (Specified to operate from V CC = 3.0V to 6.0V)f MAXMaximum C1 = 50 pF Operating R1 = 100Ω 4.5V 7 4.5MHz FrequencyR2 = ∞ 6.0V117MHzVCO in = V CC C1 = 0 pF 4.5V 12MHz R1 = 100Ω 6.014MHzVCO in = V CCDuty Cycle50%Demodulator OutputOffset Voltage R s = 20 k Ω4.5V0.751.31.51.6VVCO in –V dem Offset R s = 20 k Ω 4.5VVariationVCO in = 1.75V 0.65V2.25V 0.12.75V0.75MM74HC4046Typical Performance CharacteristicsTypical Center Frequency vs R1, C1V CC = 4.5VTypical Center Frequency vs R1, C1V CC = 6VTypical Offset Frequency vs R2, C1V CC = 4.5VTypical Offset Frequency vs R2, C1V CC = 6VTypical VCO Power Dissipation @ Center Frequency vs R1Typical VCO Power Dissipation @ f MIN vs R2 6M M 74H C 4046Typical Performance Characteristics(Continued)VCO in vs f outV CC = 4.5VVCO in vs f out V CC = 4.5VVCO out vsTemperature V CC = 4.5VVCO out vsTemperature V CC = 6VMM74HC4046Typical Performance Characteristics (Continued)HC4046 Typical Source FollowerPower Dissipation vs RSTypical f MAX /f MIN vs R2/R1V CC = 4.5V & 6V f MAX /f MINTypical VCO Linaearity vs R1 & C1Typical VCO Linearity vs R1 & C1 8M M 74H C 4046Detailed Circuit DescriptionVOLTAGE CONTROLLED OSCILLATOR/SOURCE FOLLOWERThe VCO requires two or three external components to operate. These are R1, R2, C1. Resistor R1 and capacitor C1 are selected to determine the center frequency of the VCO. R1 controls the lock range. As R1’s resistance decreases the range of f MIN to f MAX increases. Thus the VCO ’s gain increases. As C1 is changed the offset (if used)of R2, and the center frequency is changed. (See typical performance curves) R2 can be used to set the offset fre-quency with 0V at VCO input. If R2 is omitted the VCO range is from 0Hz. As R2 is decreased the offset frequency is increased. The effect of R2 is shown in the design infor-mation table and typical performance curves. By increasingthe value of R2 the lock range of the PLL is offset above 0Hz and the gain (Hz/Volt) does not change. In general,when offset is desired, R2 and C1 should be chosen first,and then R1 should be chosen to obtain the proper center frequency.Internally the resistors set a current in a current mirror as shown in Figure 1. The mirrored current drives one side of the capacitor once the capacitor charges up to the thresh-old of the schmitt trigger the oscillator logic flips the capaci-tor over and causes the mirror to charge the opposite side of the capacitor. The output from the internal logic is then taken to pin 4.VCO WITHOUT OFFSETR2 = ∞VCO WITH OFFSETFIGURE 1.Comparator IComparator II & IIIR 2= ∞R 2≠∞R 2= ∞R 2≠∞•Given: f 0•Given: f 0 and f L•Given: f MAX•Given: f MIN and f MAX •Use f 0 with curve titled •Calculate f MIN from the •Calculate f 0 from the •Use f MIN with curve titled center frequency vs R1, C equation f MIN = f o − f L equation f o = f MAX /2offset frequency vs R2,to determine R1 and C1•Use f MIN with curve titled •Use f 0 with curve titled C to determine R2 and C1offset frequency vs R2, C center frequency vs R1, C •Calculate f MAX /f MIN to determine R2 and C1to determine R1 and C1•Use f MAX /f MIN with curve •Calculate f MAX /f MIN from titled f MAX /f MIN vs R2/R1the equation f MAX /f MIN =to determine ratio R2/R1f o + f L /f o − f Lto obtain R1•Use f MAX /f MIN with curve titled f MAX /f MIN vs R2/R1to determine ratio R2/R1to obtain R1MM74HC4046Detailed Circuit Description(Continued)FIGURE 2. Logic Diagram for VCOThe input to the VCO is a very high impedance CMOSinput and so it will not load down the loop filter, easing thefilters design. In order to make signals at the VCO input accessible without degrading the loop performance a source follower transistor is provided. This transistor can be used by connecting a resistor to ground and its drain output will follow the VCO input signal.An inhibit signal is provided to allow disabling of the VCOand the source follower. This is useful if the internal VCO is not being used. A logic high on inhibit disables the VCO and source follower.The output of the VCO is a standard high speed CMOS output with an equivalent LSTTL fanout of 10. The VCO output is approximately a square wave. This output can either directly feed the comparator input of the phase com-parators or feed external prescalers (counters) to enablefrequency synthesis.PHASE COMPARATORSAll three phase comparators share two inputs, Signal In and Comparator In. The Signal In has a special DC bias network that enables AC coupling of input signals. If the signals are not AC coupled then this input requires logic levels the same as standard 74HC. The Comparator inputis a standard digital input. Both input structures are shown in Figure 3.The outputs of these comparators are essentially standard 74HC voltage outputs. (Comparator II is 3-STATE.)FIGURE 3. Logic Diagram for Phase Comparator I and the common input circuit for all three comparators 10M M 74H C 4046Detailed Circuit Description(Continued)FIGURE 4. Typical Phase Comparator I. WaveformsThus in normal operation V CC and ground voltage levels are fed to the loop filter. This differs from some phase detectors which supply a current output to the loop filter and this should be considered in the design. (The CD4046also provides a voltage.)Figure 5 shows the state tables for all three comparators.PHASE COMPARATOR IThis comparator is a simple XOR gate similar to the 74HC86, and its operation is similar to an overdriven bal-anced modulator. To maximize lock range the input fre-quencies must have a 50% duty cycle. Typical input and output waveforms are shown in Figure 4. The output of the phase detector feeds the loop filter which averages the out-put voltage. The frequency range upon which the PLL will lock onto if initially out of lock is defined as the capture range. The capture range for phase detector I is dependent on the loop filter employed. The capture range can be as large as the lock range which is equal to the VCO fre-quency range.To see how the detector operates refer to Figure 4. When two square wave inputs are applied to this comparator, an output waveform whose duty cycle is dependent on the phase difference between the two signals results. As the phase difference increases the output duty cycle increases and the voltage after the loop filter increases. Thus in order to achieve lock, when the PLL input frequency increases the VCO input voltage must increase and the phase differ-ence between comparator in and signal in will increase. At an input frequency equal f MIN , the VCO input is at 0V and this requires the phase detector output to be ground hence the two input signals must be in phase. When the input fre-quency is f MAX then the VCO input must be V CC and the phase detector inputs must be 180° out of phase.The XOR is more susceptible to locking onto harmonics of the signal input than the digital phase detector II. This can be seen by noticing that a signal 2 times the VCO fre-quency results in the same output duty cycle as a signal equal the VCO frequency. The difference is that the output frequency of the 2f example is twice that of the other exam-ple. The loop filter and the VCO range should be designed to prevent locking on to harmonics.PHASE COMPARATOR IIThis detector is a digital memory network. It consists of four flip-flops and some gating logic, a three state output and a phase pulse output as shown in Figure 6. This comparator acts only on the positive edges of the input signals and is thus independent of signal duty cycle.Phase comparator II operates in such a way as to force the PLL into lock with 0 phase difference between the VCO output and the signal input positive waveform edges. Fig-ure 7 shows some typical loop waveforms. First assume that the signal input phase is leading the comparator input.This means that the VCO ’s frequency must be increased to bring its leading edge into proper phase alignment. Thus the phase detector II output is set high. This will cause the loop filter to charge up the VCO input increasing the VCO frequency. Once the leading edge of the comparator input is detected the output goes 3-STATE holding the VCO input at the loop filter voltage. If the VCO still lags the sig-nal then the phase detector will again charge up to VCO input for the time between the leading edges of both wave-forms.MM74HC4046Detailed Circuit Description (Continued)Phase Comparator State DiagramsFIGURE 5. PLL State Tables 12M M 74H C 4046Detailed Circuit Description(Continued)FIGURE 6. Logic Diagram for Phase Comparator IIFIGURE 7. Typical Phase Comparator II Output WaveformsMM74HC4046Detailed Circuit Description(Continued)If the VCO leads the signal then when the leading edge ofthe VCO is seen the output of the phase comparator goesLOW. This discharges the loop filter until the leading edgeof the signal is detected at which time the output 3-STATEitself again. This has the effect of slowing down the VCO toagain make the rising edges of both waveform coincident.When the PLL is out of lock the VCO will be running eitherslower or faster than the signal input. If it is running slowerthe phase detector will see more signal rising edges and sothe output of the phase comparator will be HIGH a majorityof the time, raising the VCO ’s frequency. Conversely, if theVCO is running faster than the signal the output of thedetector will be LOW most of the time and the VCO ’s out-put frequency will be decreased.As one can see when the PLL is locked the output of phasecomparator II will be almost always 3-STATE except forminor corrections at the leading edge of the waveforms.When the detector is 3-STATE the phase pulse output isHIGH. This output can be used to determine when the PLLis in the locked condition.This detector has several interesting characteristics. Overthe entire VCO frequency range there is no phase differ-ence between the comparator input and the signal input.The lock range of the PLL is the same as the capturerange. Minimal power is consumed in the loop filter since inlock the detector output is a high impedance. Also when nosignal is present the detector will see only VCO leadingedges, and so the comparator output will stay LOW forcingthe VCO to f MIN operating frequency.Phase comparator II is more susceptible to noise causing the phase lock loop to unlock. If a noise pulse is seen on the signal input, the comparator treats it as another positive edge of the signal and will cause the output to go HIGH until the VCO leading edge is seen, potentially for a whole signal input period. This would cause the VCO to speed up during that time. When using the phase comparator I the output of that phase detector would be disturbed for only the short duration of the noise spike and would cause less upset.PHASE COMPARATOR III This comparator is a simple S-R Flip-Flop which can func-tion as a phase comparator Figure 8. It has some similar characteristics to the edge sensitive comparator. To see how this detector works assume input pulses are applied to the signal and comparator inputs as shown in Figure 9.When the signal input leads the comparator input the flop is set. This will charge up the loop filter and cause the VCO to speed up, bringing the comparator into phase with the sig-nal input. When using short pulses as input this comparator behaves very similar to the second comparator. But one can see that if the signal input is a long pulse, the output of the comparator will be forced to a one no matter how many comparator input pulses are received. Also if the VCO input is a square wave (as it is) and the signal input is pulse then the VCO will force the comparator output LOW much of the time. Therefore it is ideal to condition the signal and com-parator input to short pulses. This is most easily done byusing a series capacitor.FIGURE 8. Phase Comparator III Logic DiagramFIGURE 9. Typical Waveforms for Phase Comparator III 14M M 74H C 4046Physical Dimensionsinches (millimeters) unless otherwise noted 16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150" NarrowPackage Number M16A MM74HC4046Physical Dimensions inches (millimeters) unless otherwise noted (Continued)16-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm WidePackage Number M16D 16M M 74H C 4046Physical Dimensionsinches (millimeters) unless otherwise noted (Continued)16-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm WidePackage Number MTC16 MM74HC4046 CMOS Phase Lock LoopPhysical Dimensions inches (millimeters) unless otherwise noted (Continued)16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" WidePackage Number N16EFairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications.LIFE SUPPORT POLICYFAIRCHILD ’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:1.Life support devices or systems are devices or systemswhich, (a) are intended for surgical implant into thebody, or (b) support or sustain life, and (c) whose failureto perform when properly used in accordance withinstructions for use provided in the labeling, can be rea-sonably expected to result in a significant injury to theuser.2. A critical component in any component of a life support device or system whose failure to perform can be rea-sonably expected to cause the failure of the life support device or system, or to affect its safety or 。

CD4046引脚功能

〈CD4046内部电原理框图〉

CD4046引脚功能_IU

浏览:4次作者:企业库时间:2010-1-17 19:43:47

CD4046是通用的CMOS锁相环集成电路,其特点是电源电压范围宽(为3V-18V),输入阻抗高(约100MΩ),动态功耗小,在中心频率f0为10kHz下功耗仅为600μW,属微功耗器件。

CD4046 Biblioteka df中文资料下载:下图是CD4046的引脚排列,采用16脚双列直插式,各管脚功能:

1脚相位输出端,环路人锁时为高电平,环路失锁时为低电平。

2脚相位比较器Ⅰ的输出端。

3脚比较信号输入端。

4脚压控振荡器输出端。

5脚禁止端,高电平时禁止,低电平时允许压控振荡器工作。

6、7脚外接振荡电容。

8、16脚电源的负端和正端。

9脚压控振荡器的控制端。

10脚解调输出端,用于FM解调。

11、12脚外接振荡电阻。

13脚相位比较器Ⅱ的输出端。

14脚信号输入端。

15脚内部独立的齐纳稳压管负极。

〈CD4046引脚图〉

CD4046典型应用电路。

图6是用CD4046的VCO组成的方波发生器,当其9脚输入端固定接电源时,电路即起基本方波振荡器的作用。振荡器的充、放电电容C1接在6脚与7脚之间,调节电阻R1阻值即可调整振荡器振荡频率,振荡方波信号从4脚输出。按图示数值,振荡频率变化范围在20Hz至2kHz。

HEF4046BD中文资料

Figure 4 shows the typical waveforms for a PLL employing phase comparator 1 in locked condition of fo.

Fig.4 Typical waveforms for phase-locked loop employing phase comparator 1 in locked condition of fo.