AN5367FB中文资料

AD536中文资料

公司地址:深圳市福田区中航路鼎诚国际大厦2505 联系电话:0755-82724670 传真:0755-82728158 E-mail:service@ QQ:2355719478 COPYRIGHT 2005-2015 深圳成德广营科技有限公司 ()ALL RIGHTS RESERVED

–VS 4 NC 5 CAV 6 NC 7 dB 8

BUF 9 10

NC NC NC NC COM

AD536A

SQUARER DIVIDER

BUF BUF NC IOUT RL OUT IN NC = NO CONNECT

PRODUCT HIGHLIGHTS

1. The AD536A computes the true root-mean-square level of a complex ac (or ac plus dc) input signal and gives an equivalent dc output level. The true rms value of a waveform is a more useful quantity than the average rectified value since it relates directly to the power of the signal. The rms value of a statistical signal also relates to its standard deviation. 2. The crest factor of a waveform is the ratio of the peak signal swing to the rms value. The crest factor compensation scheme of the AD536A allows measurement of highly complex signals with wide dynamic range. 3. The only external component required to perform measurements to the fully specified accuracy is the capacitor which sets the averaging period. The value of this capacitor determines the low frequency ac accuracy, ripple level and settling time. 4. The AD536A will operate equally well from split supplies or a single supply with total supply levels from 5 to 36 volts. The one milliampere quiescent supply current makes the device well-suited for a wide variety of remote controllers and battery powered instruments. 5. The AD536A directly replaces the AD536 and provides improved bandwidth and temperature drift specifications.

三星电容编码识别

三星电容编码识别之老阳三干创作你看盘子的料号如下比较:CL 03 B 104 K Q 8 N N N C1 2 3 4 5 6 7 8 9 10 111 系列编码:CL=积层陶瓷电容2 尺寸编码03=0201(0603) 21=0805(2012) 42=1808(4520)05=0402(1005) 31=1206(3216) 43=1812(4532)10=0603(1608) 32=1210(3225) 55=2220(5750)14=0504(1410) 01=0306(0816) 12=0508(1220)3 介质I类 II类C=C0G S=S2H L=S2LP=P2H T=T2HR=R2H U=U2JA=X5R F=Y5VB=X7R X=X6S4 容量电容容量用三位数暗示,前面两位为有效数字,第三位为有效数字后"O"的位数如:104 = 1 00000 (单元pF)如果中间一位为R 则暗示"."5 电容的误差:B=±0.1pf F=±1pf±1% K=±10%C=±0.25pf G=±2% M=±20%D=±0.5pf? J=±5% Z=+80/-20%6 额定电压R=4V O =16V B =50V E = 250V I = 1000VQ=6.3V A =25V C=100V G = 500V J = 2000VP =10V L =35V D =200V H = 630V K= 3000V7 厚度:5=0.50毫米 C=0.85毫米 F=1.25毫米 J=2.50毫米 V=2.50毫米8=0.80毫米 D=1.00毫米 H=1.60毫米 L=3.20毫米8 内电极A=惯例产物钯/银/镍屏蔽/锡 100%N=惯例产物镍/铜/镍屏蔽/锡 100%G=惯例产物铜/铜/镍屏蔽/锡 100%L=低正面产物镍/铜/镍屏蔽/锡 100%9 产物编码A =阵列(2-元素) L =LICCB =阵列(4-元素) N =惯例P =自动 C=高频10 特殊编码11 包装编码B=散装 O=纸版箱料带,10英寸料盘 E=压花纸版箱,7英寸料盘P=散装箱 D=纸版箱料带,13英寸料盘(10000ea) F=压花纸版箱,13英寸料盘C=纸版箱料带,7英寸料盘 L=纸版箱料带,13英寸料盘(15,000ea) S=压花纸版箱,10英寸料盘。

三端稳压器的参数介绍

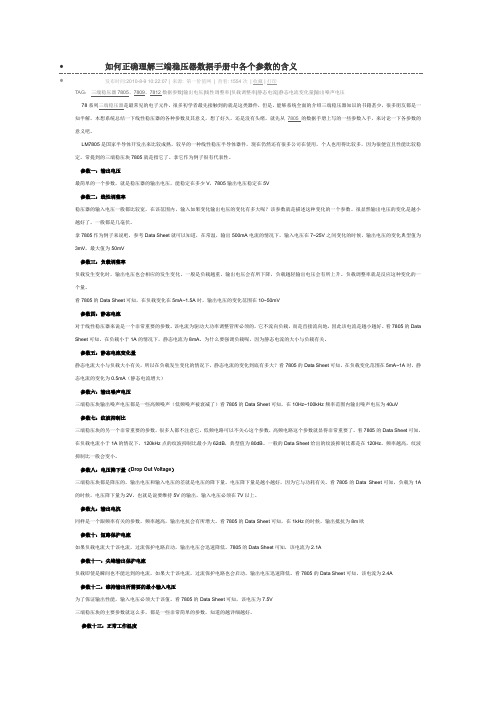

∙如何正确理解三端稳压器数据手册中各个参数的含义∙发布时间:2010-8-9 10:22:07 | 来源: 第一价值网| 查看: 1554次| 收藏 | 打印TAG:三端稳压器7805、7809、7812数据参数|输出电压|线性调整率|负载调整率|静态电流|静态电流变化量|输出噪声电压78系列三端稳压器是最常见的电子元件,很多初学者最先接触到的就是这类器件,但是,能够系统全面的介绍三端稳压器知识的书籍甚少,很多朋友都是一知半解,本想系统总结一下线性稳压器的各种参数及其意义,想了好久,还是没有头绪,就先从7805的数据手册上写的一些参数入手,来讨论一下各参数的意义吧。

LM7805是国家半导体开发出来比较成熟,较早的一种线性稳压半导体器件,现在仍然还有很多公司在使用,个人也用得比较多,因为很便宜且性能比较稳定。

常提到的三端稳压块7805就是指它了。

拿它作为例子很有代表性。

参数一:输出电压最简单的一个参数,就是稳压器的输出电压,能稳定在多少V,7805输出电压稳定在5V参数二:线性调整率稳压器的输入电压一般都比较宽,在该范围内,输入如果变化输出电压的变化有多大呢?该参数就是描述这种变化的一个参数。

很显然输出电压的变化是越小越好了,一般都是几毫伏。

拿7805作为例子来说吧,参考Data Sheet就可以知道,在常温,输出500mA电流的情况下,输入电压在7~25V之间变化的时候,输出电压的变化典型值为3mV,最大值为50mV参数三:负载调整率负载发生变化时,输出电压也会相应的发生变化,一般是负载越重,输出电压会有所下降,负载越轻输出电压会有所上升。

负载调整率就是反应这种变化的一个量。

看7805的Data Sheet可知,在负载变化在5mA~1.5A时,输出电压的变化范围在10~50mV参数四:静态电流对于线性稳压器来说是一个非常重要的参数。

该电流为驱动大功率调整管所必须的,它不流向负载,而是直接流向地,因此该电流是越小越好。

彩电常用存储器引脚功能一览表

型号脚号引脚功能应用电路(或脚位排列)备注1供电+5V2擦除、写入电源一30V 3擦除、写入电源一30V 4音量、对比度数据5测试端6时钟信号输入7~9存储器工作模式选择10片选(低电平时本芯片被选中工作)12地址输入、数据输入/输出11、14空脚13地1片选信号输入(低电平有效)2同步时钟信号输入3数据输入、地址输入(二者复用)4数据输出5地6振荡端(用内部电路时,此端开路或接VCC)8电源(+5V)1电源(+5V)2擦、写电源(一30V)3、510、1l 空脚4片选信号输入(低电平有效)6时钟输入7、8、9存储器工作模式选择12地址输入、数据输入/输出13地14测试端(未用)1~3地址、数据输入端4电源(+5V)5地6空脚7检测输入8存储参考电压发生器电源9擦写电源(一28V)10复位脉冲输入11测试12读写控制13~16数据输出线17地址、数据输入端18电源(一般不用)1电源(+5v)2空脚3地14片选输入控制端5~7工作方式选择输入8地29地址输入、数据输入/输出MNl2C25D本IC属电可改(擦)写只读存储器,有20×16位的存储矩阵。

工作电压4.5~6.5V。

10万次擦写周期,断电后数据保存时间大于10年。

本IC属电可擦可改写只读存储器,其存储容量为512位。

当存储器改写1万次后,信息仍可保存10年若改写10万次后,信息只能保存1年。

彩电常用存储器引脚功能一览表说明:彩电常用只读存储器(ROM)主要包括可编程序只读存储器(PROM)和电可改(擦)写只读存储器(EAROM or E2ROM or E2PROM)。

它们的最大特点是写入的程序(或数据)在断电后能保存几十年时间,同时又可根据用户需要用电或紫外线(指PROM)或电信号(指EAROM or E2PROM)进行清除和重写(即拷贝)。

MNl228M58655PCXKl011PCX7959本IC属是电可擦可改写只读存储器,其存储容量为64×16=1024位。

CHI MEI PA-765B E56070 元件说明书

•Component •元件UL file numberUL档案号Part number型号Remark备注Vendor供应商•FRONT CASE•前身E56070 PA-765B CHI MEI•TOP CASE•上身E56070 PA-765B CHI MEI•BOTTOM CASE•下身E56070 PA-765B CHI MEI•Batterycompartment•电池箱E207780 PC945(GG) QMFZ2 SABIC JAPAN L L C•Transformercover•火牛上盖E50075 LV2250V TEIJIN•TransformerHousing 火牛下盖E50075 LV2250V TEIJIN•Aux foam pad•Aux盖E257267 E50A-60 ZHI JIN•Side plate•侧盖E56070 PA-765B CHI MEI•Battery BayRubber Cover•电池箱盖E257267 E50A-60 ZHI JIN•batterydoors•电池盖E56070 PA-765B CHI MEI•AAA batterycover•3A 电池门E56070 PA-765B CHI MEI•Light guide•导光片E54705 CL PMMA SUMIPEX•Frontcontrolpanel 显示压件E248280 PC+ABS Jacobson•Strainrelief•线卡E107293 6P-4 晋煜•Power cord •电源线E137516 SJTW ZJCZ 利源電業製品廠有限公司LEE YUEN ELECTRICAL MFY LTD. E143681 LY-13B ELBZ7•Lead wire •引线E244721 UL 1007 20AWGL=330mmAVLV2 惠州市远达电业五金制品有限公司HUI ZHOU YUEN DA ELECTRONIC & HARDWARECO.,LTDE329541 UL 1007 18AWGVH3.96-H-2PVH3.96-TL=186mmZPFW2 深圳艾格科技有限公司Shenzhen Aiger Technology Co.,LtdE330646 UL 1007#24 XH-TXH-4P L=140mmAVLV2 深圳市展旺连接器有限公司Shen Zhen Zhan Wang Linker CO.,LTDE330646 UL 1007#24 XH-TXH-2P L=260mmAVLV2E330646 UL 2547#28 PH-TPH-3P L=260mmAVLV2E330646 UL 2547#28 PH-TPH-3P L=220mmAVLV2E330646 UL 1185 22AWG XH-T XH-2P L=150mmAVLV2•Integralfuse •保险丝E340427 SFC0800A(800mA/250V FastActing Glass TubeFuse)JDYX 瑞卓电子(东莞)有限公司Dongguan Reomax Electronics Co., LTD•Fuse Holder •保险丝座E239034 H3(10A/250V)IZLT2 惠州市海牛電子有限公司HUIZHOU HINEW ELECTRIC APPLIANCE CO.,LTD.变压器材料清單/ MATERIAL LISTNO. MATERIAL DESCRIPTION Ul file MANUFACTURERS / SUPPLIERS1. 膠芯/Bobbin 最小0.71mm厚尼龍66 101(r9)一層minimum 0.71mm thick PA66101(r9) one layerUL:E41938 杜邦/E I Dupont De Nemours & Co Inc2 膠套/Shroud 最小0.50mm厚尼龍66 101(r9)一層minimum 0.50mm thick PA66101(r9) one layerUL:E41938 杜邦/E I Dupont De Nemours & Co Inc3 初級線圈PrimaryWinding 聚氨酯漆包線MW75C(130℃) 或Polyurethane Wire,MW75C(130℃)UL:E258125 河源天裕電子塑膠有限公司He Yuan Sky Wealth Electronic And PlasticCo Ltd.4 初級跨線絕緣Pri. windingcrossoverinsulation CT25聚脂膠紙/CT-25 Polyestertape厚度:0.05mm*2 層/Thickness:0.05mm*2 layersUL:E165111 靖江亞華壓敏黏膠有限公司Jingjiang Yahua Pressure Sensitive Glue COLTD5 溫度保險Thermal Fuse Type: A4-F130 Deg.C ( 250V/2A)UL:E140847 雅寶電子有限公司/Aupo Electronics Inc.6 初級引線Primary Leads UL-1672 AWG #22 VW-1 300V105Deg.CUL:E191230UL:E189674UL:E211048UL:E214859恒輝(香港)發展有限公司Ever Bright (Hongkong) development CompanyLimited.深圳东聚Shenzhen Dong Ju Wire & CableCo.,Ltd.琦富瑞Qifurui Electronics co阳泰氟电线电缆YANGTAI WIRE & CABLE CO LTD7 初級引線Primary Leads 聚氨酯漆包線MW75C(130℃) 或Polyurethane Wire,MW75C(130℃)or聚氨酯漆包線MW79C(155℃)Polyurethane Wire,MW79C(155℃)UL:E258125UL:E201757河源天裕電子塑膠有限公司He Yuan Sky Wealth Electronic And PlasticCo Ltd.太平洋電線電纜深圳公司Pacific ElectricWire&Cable(shenzhen)Co.,Ltd.8 次級引線SecondaryLeads UL-1015 AWG #20 VW-1 600V105Deg.CUL:E191230UL:E189674UL:E211048UL:E214859恒輝(香港)發展有限公司Ever Bright(Hongkong) development Company Limited.深圳东聚Shenzhen Dong Ju Wire & CableCo.,Ltd.琦富瑞Qifurui Electronics co阳泰氟电线电缆YANGTAI WIRE & CABLE CO LTD9 次級引線SecondaryLeads CT25聚脂膠紙/CT-25 Polyestertape厚度:0.05mm*3 層/UL:E165111 靖江亞華壓敏黏膠有限公司Jingjiang Yahua Pressure Sensitive Glue COLTD.Thickness:0.05mm*3 layers聚酯膠片型號:MYLAR EL21 0.25mm厚PET film Type:MYLAR EL21 0.25mmThickUL:E93687 杜邦帝人/ Dupont Teijin Films U S L P10 外層絕緣Outinsulation CT25聚脂膠紙/CT-25 Polyestertape厚度:0.05mm*3 層/Thickness:0.05mm*3 layers聚酯膠片型號:MYLAR EL21 0.25mm厚PET film Type:MYLAR EL21 0.25mmThickUL:E165111UL:E93687靖江亞華壓敏黏膠有限公司Jingjiang Yahua Pressure Sensitive Glue COLTD.杜邦帝人/ Dupont Teijin Films U S L P11 鐵芯片LaminationCore EI-57 硅鋼片(H18 黑) 片厚0.50,疊厚35.3+/-0.5mmEI-57 silicon steel sheet(H18black), thickness:0.50mm,depth thickness:35.3+/-0.5mmN/A 東莞東駿電器有限公司Dongguan Dongjun Electrical Appliances Co.,Ltd.12 安裝架/Bracket 冷軋板鍍鋅Cold rolled Steel with Zinc-coatedN/A 東莞駿豐五金製品廠Dongguan JunFeng MetalManufactory13 屏蔽殼/Endbell 冷軋板鍍鋅Cold rolled Steel with Zinc-coatedN/A 東莞駿豐五金製品廠Dongguan JunFeng MetalManufactory14 次級連接器Secondaryconnector Housing: JS-1121-02 & Terminal:JS-1121-THousing: A3963H-2P & Terminal:A3963-TPUL: E113875UL: E326732喬訊電子有限公司Chyao shiunn electronicIndustrial Ltd.長江連接器有限公司ChangJiang Connectors CoLtd15 浸漬/Impregnation Insulating Varnish/絕緣油Type: 8562/C, class FUL:E200154 恒昌化學塗料公司HANG CHEUNG PETROCHEMICALLTD。

AD536(CN)(中文需参看英文图表)

RMS to DC转换AD536A功能:有效值到直流电平装换高精度激光微调技术0.2%最大误差(AD536AX)0.5%最大误差(AD536AJ)宽响应能力:能够计算AC和DC信号的RMS450KHz带宽:Vrms>100mV2MHz带宽:Vrms>1V信号的波峰因数当误差为1%时为7dB输出有60dB范围低功耗:1.2mA静态电流单、双端均可用整体集成电路-55℃ to 125℃(AD536AS)产品描述AD536A是一款RMS到直流转换的整体集成电路,它优于混合式或组合式的电路。

AD536A直接计算输入波形的RMS值,包括AC和DC组件。

有一个波峰因数补偿表,可以使波峰系数达到7的测量值只有1%的误差。

本器件能测量300K 带宽大于100mV的信号,误差在3dB范围内。

AD536A有一项重要的新功能,能够将rms电平转换成dB值输出。

信号rms的对数输出到独立的管脚进行dB转换,其范围有60dB。

利用一个外部的参考电流,用户能够很方便地设置0dB电平,能计算输入的任何0.1到2Vrms波形。

AD536A在晶圆级采用激光校准对输入输出补偿,正负波形平衡,7Vrms满量程精度。

因此,无需外部调整,即可达到额定精度。

输入输出均有完全保护,输入电平可超出供电电平。

输入连接失去供电不会损坏芯片。

输出有短路保护。

AD536A商用产品分两个精度级别(A,K)温度范围(0℃ to 70℃)和另一个超范围级别(S)温度范围-55℃ to 125℃。

AD536AK有最大±2mV±0.2%的读取误差,而AD536AJ和AD536AS有±5mV±0.5%的最大误差。

所有三种都可用14-DIP 或10to100脚金属封装。

AD536AS也有20脚无铅陶瓷封装。

产品特点1、AD536A计算输入的复合AC信号输出等效直流电平。

计算信号的rms值比信号电平均值更有用,因为rms反映了信号的功率,还反映了信号的标准偏差。

常用稳压二极管技术参数及老型号代换

常用稳压二极管技术参数及老型号代换型号最大功耗 (mW) 稳定电压(V) 电流(mA) 代换型号国产稳压管日立稳压管HZ4B2 500 3.8 4.0 5 2CW102 2CW21 4B2HZ4C1 500 4.0 4.2 5 2CW102 2CW21 4C1HZ6 500 5.5 5.8 5 2CW103 2CW21A 6B1HZ6A 500 5.2 5.7 5 2CW103 2CW21AHZ6C3 500 6 6.4 5 2CW104 2CW21B 6C3HZ7 500 6.9 7.2 5 2CW105 2CW21CHZ7A 500 6.3 6.9 5 2CW105 2CW21CHZ7B 500 6.7 7.3 5 2CW105 2CW21CHZ9A 500 7.7 8.5 5 2CW106 2CW21DHZ9CTA 500 8.9 9.7 5 2CW107 2CW21EHZ11 500 9.5 11.9 5 2CW109 2CW21GHZ12 500 11.6 14.3 5 2CW111 2CW21HHZ12B 500 12.4 13.4 5 2CW111 2CW21HHZ12B2 500 12.6 13.1 5 2CW111 2CW21H 12B2HZ18Y 500 16.5 18.5 5 2CW113 2CW21JHZ20-1 500 18.86 19.44 2 2CW114 2CW21KHZ27 500 27.2 28.6 2 2CW117 2CW21L 27-3HZT33-02 400 31 33.5 5 2CW119 2CW21MRD2.0E(B) 500 1.88 2.12 20 2CW100 2CW21P 2B1RD2.7E 400 2.5 2.93 20 2CW101 2CW21SRD3.9EL1 500 3.7 4 20 2CW102 2CW21 4B2RD5.6EN1 500 5.2 5.5 20 2CW103 2CW21A 6A1RD5.6EN3 500 5.6 5.9 20 2CW104 2CW21B 6B2RD5.6EL2 500 5.5 5.7 20 2CW103 2CW21A 6B1RD6.2E(B) 500 5.88 6.6 20 2CW104 2CW21BRD7.5E(B) 500 7.0 7.9 20 2CW105 2CW21CRD10EN3 500 9.7 10.0 20 2CW108 2CW21F 11A2RD11E(B) 500 10.1 11.8 15 2CW109 2CW21GRD12E 500 11.74 12.35 10 2CW110 2CW21H 12A1RD12F 1000 11.19 11.77 20 2CW109 2CW21GRD13EN1 500 12 12.7 10 2CW110 2CW21H 12A3RD15EL2 500 13.8 14.6 15 2CW112 2CW21J 12C3RD24E 400 22 25 10 2CW116 2CW21H 24-1RD24F 400 24 28 10 2CW117 2CW21LRD36EL1 500 32 34 15 2CW119 2CW21M 33-2RD57E 500 48 54 10 1DS55-1805Z5.1Y 500 4.94 5.20 2CW103 2CW21A 5C205Z5.6Z 500 5.61 5.91 2CW104 2CW21B 6B205Z6.2Y 500 5.96 6.27 41 2CW104 2CW21B 6C205Z7.5Y 500 7.07 7.45 34 2CW105 2CW21C05Z7.5Z 500 7.3 7.7 34 2CW105 2CW21C 7C205Z9.1Y 500 8.9 9.3 30 2CW107 2CW21E 9C105Z12 500 11.13 12.35 21 2CW110 2CW21H05Z12Z 500 12.0 12.6 20 2CW110 2CW21H 12A305Z13X 500 12.11 12.75 19 2CW110 2CW21H 12A305Z13Z 500 13.5 14.1 18 2CW111 2CW21H 12C205Z13Y 500 12.55 13.21 19 2CW111 2CW21H 12B205Z15 500 14.4 15.0 17 2CW112 2CW21J 15-205Z15Y 500 13.89 14.62 17 2CW111 2CW21H 12C305Z18 500 16.5 18.5 14 2CW113 2CW21J05Z18Y 500 16.82 17.70 14 2CW113 2CW21J 18-1EQA01-11B 500 10.1 11.8 15 2CW109 2CW21GEQA01-12Z 500 11.2 13.1 15 2CW110 2CW21HEQA02-07B 400 6.66 7.01 20 2CW105 2CW21C 7A3EQA02-25A 500 24 25.5 2CW116 2CW21L 24-3TVSQA106SB 500 5.88 6.6 20 2CW104 2CW21BTVSQA111SB 500 10.4 11.6 10 2CW109 2CW21GTVSQA111SE 500 11 11.5 10 2CW109 2CW21G 11C2MA1130 1000 12.4 14.1 5 2CW111 2CW21HMA1330 500 31 35 25 2CW120 2CW21NM4030 500 2.9 3 5 2CW101 2CW21SuPC574JAG 200 31 35 25 2CW120 2CW21NRIMV 135 160 ZDW591N708 0.25 5.6 40 BWA54、2CW28-5.6V1N709 0.25 6.2 40 2CW55/B、BWA55/E1N710 0.25 6.8 36 2CW55A、2CW105-6.8V1N711 0.25 7.5 30 2CW56A、2CW28-7.5V、2CW106-7.5V 1N712 0.25 8.2 30 2CW57/B、2CW106-8.2V1N713 0.25 9.1 27 2CW58A/B、2CW741N714 0.25 10 25 2CW18、2CW59/A/B1N715 0.25 11 20 2CW76、2DW12F.BS31-121N716 0.25 12 20 2CW61/A、2CW77/A1N717 0.25 13 18 2CW62/A、2DW12G1N718 0.25 15 16 2CW112-15V、2CW78/A1N719 0.25 16 15 2CW63/A/B、2DW12H1N720 0.25 18 13 2CW20B、2CW64/B、2CW64-18 1N721 0.25 20 12 2CW65-20、2DW12I、BWA651N722 0.25 22 11 2CW20C、2DW12J1N723 0.25 24 10 WCW116、2DW13A1N724 0.25 27 9 2CW20D、2CW68、BWA68/D1N725 0.40 30 13 2CW119-30V1N726 0.40 33 12 2CW120-33V1N727 0.40 36 11 2CW120-36V1N728 0.40 39 10 2CW121-39V1N748 0.50 3.8~4.0 125 HZ4B21N752 0.50 5.2~5.7 80 HZ6A1N753 0.50 5.8~6.1 80 2CW1321N754 0.5 6.3~6.8 70 H27A1N755 0.50 7.1~7.3 65 HZ7.5EB1N757 0.50 8.9~9.3 52 HZ9C1N962 0.50 9.5~11 45 2CW1371N963 0.50 11~11.5 40 2CW138、HZ12A-21N964 0.50 12~12.5 40 HZ12C-2、MA1130TA1N969 0.50 21~22.5 20 RD245B1N4240A 1 10 100 2CW108-10V、2CW109、2DW5 1N4724A 1 12 76 2DW6A、2CW110-12V1N4728 1 3.3 270 2CW101-3V31N4729 1 3.6 252 2CW101-3V61N4729A 1 3.6 252 2CW101-3V61N4730A 1 3.9 234 2CW102-3V91N4731 1 4.3 217 2CW102-4V31N4731A 1 4.3 217 2CW102-4V31N4732/A 1 4.7 193 2CW102-4V71N4733/A 1 5.1 179 2CW103-5V11N4734/A 1 5.6 162 2CW103-5V61N4735/A 1 6.2 146 1W6V2、2CW104-6V21N4736/A 1 6.8 138 1W6V8、2CW104-6V81N4737/A 1 7.5 121 1W7V5、2CW105-7V51N4738/A 1 8.2 110 1W8V2、2CW106-8V21N4739/A 1 9.1 100 1W9V1、2CW107-9V11N4740/A 1 10 91 2CW286-10V、B563-101N4741/A 1 11 83 2CW109-11V、2DW61N4742/A 1 12 76 2CW110-12V、2DW6A1N4743/A 1 13 69 2CW111-13V、2DW6B、BWC114D 1N4744/A 1 15 57 2CW112-15V、2DW6D1N4745/A 1 16 51 2CW112-16V、2DW6E1N4746/A 1 18 50 2CW113-18V、1W18V1N4747/A 1 20 45 2CW114-20V、BWC115E1N4748/A 1 22 41 2CW115-22V、1W22V1N4749/A 1 24 38 2CW116-24V、1W24V1N4750/A 1 27 34 2CW117-27V、1W27V1N4751/A 1 30 30 2CW118-30V、1W30V、2DW19F 1N4752/A 1 33 27 2CW119-33V、1W33V1N4753 0.5 36 13 2CW120-36V、1/2W36V1N4754 0.5 39 12 2CW121-39V、1/2W39V1N4755 0.5 43 12 2CW122-43V、1/2W43V1N4756 0.5 47 10 2CW122-47V、1/2W47V1N4757 0.5 51 9 2CW123-51V、1/2W51V1N4758 0.5 56 8 2CW124-56V、1/2W56V1N4759 0.5 62 8 2CW124-62V、1/2W62V1N4760 0.5 68 7 2CW125-68V、1/2W68V1N4761 0.5 75 6.7 2CW126-75V、1/2W75V1N4762 0.5 82 6 2CW126-82V、1/2W82V1N4763 0.5 91 5.6 2CW127-91V、1/2W91V1N4764 0.5 100 5 2CW128-100V、1/2W100V1N5226/A 0.5 3.3 138 2CW51-3V3、2CW52261N5227/A/B 0.5 3.6 126 2CW51-3V6、2CW52271N5228/A/B 0.5 3.9 115 2CW52-3V9、2CW52281N5229/A/B 0.5 4.3 106 2CW52-4V3、2CW52291N5230/A/B 0.5 4.7 97 2CW53-4V7、2CW52301N5231/A/B 0.5 5.1 89 2CW53-5V1、2CW52311N5232/A/B 0.5 5.6 81 2CW103-5.6、2CW52321N5233/A/B 0.5 6 76 2CW104-6V、2CW52331N5234/A/B 0.5 6.2 73 2CW104-6.2V、2CW52341N5235/A/B 0.5 6.8 67 2CW105-6.8V、2CW5235型号稳压值(V) 稳定电流 (MA) 功率(mW) 型号稳压值(V) 稳定电流 (MA) 功率(mW) MA1030 3 5 400 MA2180 18 20 1000MA1033 3.3 5 400 MA2200 20 20 1000MA1036 3.6 5 400 MA2220 22 10 1000MA1039 3.9 5 400 MA2240 24 10 1000MA1043 4.3 5 400 MA2270 27 5 1000MA1047 4.7 5 400 MA2300 30 5 1000MA1051 5.1 5 400 MA2330 33 5 1000MA1056 5.6 5 400 MA2360 36 5 1000MA1062 6.2 5 400 MA3047 4.7 5 150MA1068 6.8 5 400 MA3051 5.1 5 150MA1075 7.5 5 400 MA3056 5.6 5 150MA1082 8.2 5 400 MA3062 6.2 5 150MA1091 9.1 5 400 MA3082 8.2 5 150MA1100 10 5 400 MA3091 9.1 5 150MA1110 11 5 400 MA3100 10 5 150MA1114 11.4 10 400 MA3110 11 5 150MA1120 12 5 400 MA3120 12 5 150MA1130 13 5 400 MA3130 13 5 150MA1140 14 5 400 MA3150 15 5 150MA1150 15 5 400 MA3160 16 5 150MA1160 16 5 400 MA3180 18 5 150MA1180 18 5 400 MA3200 20 5 150MA1200 20 5 400 MA3220 22 5 150MA1220 22 5 400 MA3240 24 5 150MA1240 24 5 400 MA3270 27 2 150MA1270 27 2 400 MA3300 30 2 150MA1300 30 2 400 MA3330 33 2 150MA1330 33 2 400 MA3360 36 2 150MA1360 36 2 400 MA4030 3 5 370MA2051 5.1 40 1000 MA4033 3.3 5 370MA2056 5.6 40 1000 MA4036 3.6 5 370MA2062 6.2 40 1000 MA4039 3.9 5 370 MA2068 6.8 40 1000 MA4043 4.3 5 370 MA2075 7.5 40 1000 MA4047 4.7 5 370 MA2082 8.2 40 1000 MA4051 5.1 5 370 MA2091 9.1 40 1000 MA4056 5.6 5 370 MA2100 10 40 1000 MA4062 6.2 5 370 MA2110 11 5 1000 MA4068 6.8 5 370MA2120 12 5 1000 MA4075 7.5 5 370MA2130 13 5 1000 MA4082 8.2 5 370MA2150 15 5 1000 MA4091 9.1 5 370MA2160 16 5 1000 MA4100 10 5 370MA4110 11 5 370 BZX55C6V8 6.8 5 500 MA4120 12 5 370 BZX55C7V5 7.5 5 500 MA4130 13 5 370 BZX55C8V2 8.2 5 500 MA4140 14 5 370 BZX55C9V1 9.1 5 500 MA4150 15 5 370 BZX55C10 10 5 500MA4160 16 5 370 BZX55C11 11 5 500MA4180 18 5 370 BZX55C12 12 5 500MA4200 20 5 370 BZX55C13 13 5 500MA4220 22 5 370 BZX55C15 15 5 500MA4240 24 5 370 BZX55C16 16 5 500MA4270 27 2 370 BZX55C18 18 5 500MA4300 30 2 370 BZX55C20 20 5 500MA4330 33 2 370 BZX55C22 22 5 500MA4360 36 2 370 BZX55C24 24 5 500MA5047 4.7 5 500 BZX55C27 27 5 500 MA5051 5.1 5 500 BZX55C30 30 5 500 MA5056 5.6 5 500 BZX55C33 33 5 500 MA5062 6.2 5 500 BZX55C36 36 5 500 MA5068 6.8 5 500 BZX55C39 39 5 500 MA5075 7.5 5 500 BZX55C43 43 2.5 500 MA5082 8.2 5 500 BZX55C47 47 2.5 500 MA5091 9.1 5 500 BZX55C51 51 2.5 500 MA5100 10 5 500 BZX55C56 56 2.5 500 MA5110 11 5 500 BZX55C62 62 2.5 500 MA5120 12 5 500 BZX85C2V7 2.7 80 1300 MA5130 13 5 500 BZX85C3V0 3.0 80 1300MA5160 16 5 500 BZX85C3V6 3.6 70 1300MA5180 18 5 500 BZX85C3V9 3.9 60 1300MA5200 20 5 500 BZX85C4V3 4.3 50 1300MA5240 24 5 500 BZX85C4V7 4.7 45 1300 BZX55C2V4 2.4 5 500 BZX85C5V1 5.1 45 1300 BZX55C2V7 2.7 5 500 BZX85C5V6 5.6 45 1300 BZX55C3V0 3.0 5 500 BZX85C6V2 6.2 35 1300 BZX55C3V3 3.3 5 500 BZX85C6V8 6.8 35 1300 BZX55C3V6 3.6 5 500 BZX85C7V5 7.5 35 1300 BZX55C3V9 3.9 5 500 BZX85C8V2 8.2 25 1300BZX55C4V3 4.3 5 500 BZX85C9V1 9.1 25 1300 BZX55C4V7 4.7 5 500 BZX85C10 10 25 1300 BZX55C5V1 5.1 5 500 BZX85C11 11 20 1300 BZX55C5V6 5.6 5 500 BZX85C12 12 20 1300 BZX55C6V2 6.2 5 500 BZX85C13 13 20 1300 BZX85C15 15 15 1300 BZX79A9V1 9.1 5 400 BZX85C16 16 15 1300 BZX79A10 10 5 400 BZX85C18 18 15 1300 BZX79A11 11 5 400 BZX85C20 20 10 1300 BZX79A12 12 5 400 BZX85C22 22 10 1300 BZX79A13 13 5 400 BZX85C24 24 10 1300 BZX79A15 15 5 400 BZX85C27 27 8 1300 BZX79A16 16 5 400BZX85C30 30 8 1300 BZX79A18 18 5 400BZX85C33 33 8 1300 BZX79A20 20 5 400BZX85C36 36 8 1300 BZX79A22 22 5 400BZX85C39 39 6 1300 BZX79A24 24 5 400BZX85C43 43 6 1300 BZX79A27 27 2 400BZX85C47 47 4 1300 BZX79A30 30 2 400BZX85C51 51 4 1300 BZX79A33 33 2 400BZX85C56 56 4 1300 BZX79A36 36 2 400BZX85C62 62 4 1300 BZX79A39 39 2 400BZX55C68 68 2.5 500 BZX79A43 43 2 400 BZX55C75 75 2.5 500 BZX79A47 47 2 400 BZX55C82 82 2.5 500 BZX79A51 51 2 400 BZX55C91 91 1 500 BZX79A56 56 2 400BZX55C110 110 1 500 BZX79A68 68 2 400BZX55C120 120 1 500 BZX79A75 75 2 400BZX55C130 130 1 500 BZX79C2V4 2.4 5 500BZX55C150 150 1 500 BZX79C2V7 2.7 5 500BZX55C160 160 1 500 BZX79C3V0 3.0 5 500BZX55C180 180 1 500 BZX79C3V3 3.3 5 500BZX55C200 200 1 500 BZX79C3V6 3.6 5 500BZX79A2V4 2.4 5 400 BZX79C3V9 3.9 5 500BZX79A2V7 2.7 5 400 BZX79C4V3 4.3 5 500BZX79A3V0 3.0 5 400 BZX79C4V7 4.7 5 500BZX79A3V3 3.3 5 400 BZX79C5V1 5.1 5 500BZX79A3V6 3.6 5 400 BZX79C5V6 5.6 5 500BZX79A3V9 3.9 5 400 BZX79C6V2 6.2 5 500BZX79A4V3 4.3 5 400 BZX79C6V8 6.8 5 500BZX79A4V7 4.7 5 400 BZX79C7V5 7.5 5 500BZX79A5V1 5.1 5 400 BZX79C8V2 8.2 5 500BZX79A5V6 5.6 5 400 BZX79C9V1 9.1 5 500BZX79A6V2 6.2 5 400 BZX79C10 10 5 500BZX79A6V8 6.8 5 400 BZX79C11 11 5 500BZX79A7V5 7.5 5 400 BZX79C12 12 5 500BZX79A8V2 8.2 5 400 BZX79C13 13 5 500整流二极管:整流二极管是面接触型的,多采用硅材料构成。

MAX536AEWE中文资料

Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Microprocessor-Controlled Systems

________________Functional Diagram

SDO LDAC

DGND

VDD

AGND

VSS TP REFAB

DECODE CONTROL

INPUT REG A

DAC REG A

16-BIT SHIFT REGISTER

PARAMETER

SYMBOL

CONDITIONS

1N5400-1N5408 1A 75V标准恢复型二极管数据手册说明书

1N5400 thru 1N54081N5404 and 1N5406 are Preferred DevicesAxial-Lead Standard Recovery RectifiersLead mounted standard recovery rectifiers are designed for use in power supplies and other applications having need of a device with the following features:Features•High Current to Small Size•High Surge Current Capability•Low Forward V oltage Drop•V oid−Free Economical Plastic Package•Available in V olume Quantities•Plastic Meets UL 94 V−0 for Flammability•These are Pb−Free DevicesMechanical Characteristics:•Case: Epoxy, Molded•Weight: 1.1 Gram (Approximately)•Finish: All External Surfaces Corrosion Resistant and Terminal Leads are Readily Solderable•Lead and Mounting Surface Temperature for Soldering Purposes: 260°C Max. for 10 Seconds•Polarity: Cathode Indicated by Polarity Band*For additional information on our Pb−Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.STANDARD RECOVERYRECTIFIERS50−1000 VOLTS3.0 AMPERESAXIAL LEADCASE 267−05STYLE 1Preferred devices are recommended choices for future use and best overall value.A= Assembly Location1N540x= Device Numberx= 0, 1, 2, 4, 6, 7 or 8YY= YearWW= Work WeekG= Pb−Free PackageMARKING DIAGRAMA1N540xYYWW GGSee detailed ordering and shipping information on page 5 of this data sheet.ORDERING INFORMATION(Note: Microdot may be in either location)MAXIMUM RATINGSRating Symbol1N54001N54011N54021N54041N54061N54071N5408UnitPeak Repetitive Reverse Voltage Working Peak Reverse Voltage DC Blocking Voltage V RRMV RWMV R501002004006008001000VNon−repetitive Peak Reverse Voltage V RSM10020030052580010001200V Average Rectified Forward Current(Single Phase Resistive Load,1/2 in. Leads, T L = 105°C)I O 3.0ANon−repetitive Peak Surge Current(8 ms Single Half−Sine−Wave)I FSM200 (one cycle)AOperating and Storage Junction Temperature Range T JT stg−65 to +150−65 to +175°CStresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.THERMAL CHARACTERISTICSCharacteristic Symbol Typ Unit Thermal Resistance, Junction−to−Ambient (PC Board Mount, 1/2 in. Leads)R q JA53°C/W ELECTRICAL CHARACTERISTICSCharacteristic Symbol Min Typ Max Unit Forward Voltage (I F = 3.0 A, T A = 25°C)v F−− 1.0VReverse Current (Rated DC Voltage) T A = 25°CT A = 100°C I R−−−−1050m ARatings at 25°C ambient temperature unless otherwise specified.60 Hz resistive or inductive loads.For capacitive load, derate current by 20%.NOTE 1 — AMBIENT MOUNTING DATAFigure 1. Forward Voltagev F, INSTANTANEOUS VOLTAGE (V), I N S T A N T A N E O U S F O R W A R D C U R R E N T (A M P S )F Figure 2. Maximum Nonrepetitive Surge CurrentFigure 3. Maximum Current Derating, Lead,Various Lengthsi 40020030040NUMBER OF CYCLES5060708090100Figure 4. Maximum Current Derating, Ambient, PCBoard MountingT A, AMBIENT TEMPERATURE (°C)T L, LEAD TEMPERATURE (°C)I F S M , P E A K H A L F W A V E C U R R E N T (A )Figure 5. Forward Power Dissipation3456789101614121086420I F(AV), AVERAGE FORWARD CURRENT (A)P F (A V ), A V E R A G E P O W E R D I S S I P A T I O N (W )12I F (A V ), A V E R A G E F O R W A R D C U R R E N T (A )123456ORDERING INFORMATIONDevice Package Shipping†1N5400G Axial Lead*500 Units/Box1N5400RLG Axial Lead*1200/Tape & Reel1N5401G Axial Lead*500 Units/Box1N5401RLG Axial Lead*1200/Tape & Reel1N5402G Axial Lead*500 Units/Box1N5402RLG Axial Lead*1200/Tape & Reel1N5404G Axial Lead*500 Units/Box1N5404RLG Axial Lead*1200/Tape & Reel1N5406G Axial Lead*500 Units/Box1N5406RLG Axial Lead*1200/Tape & Reel1N5407G Axial Lead*500 Units/Box1N5407RLG Axial Lead*1200/Tape & Reel1N5408G Axial Lead*500 Units/Box1N5408RLG Axial Lead*1200/Tape & Reel†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.*This package is inherently Pb−Free.PACKAGE DIMENSIONSAXIAL LEAD CASE 267−05ISSUE GNOTES:1.DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.2.CONTROLLING DIMENSION: INCH.STYLE 1:PIN 1.CATHODE (POLARITY BAND)2.ANODEDIMMIN MAX MIN MAX MILLIMETERSINCHES A 0.2870.3747.309.50B 0.1890.209 4.80 5.30D 0.0470.051 1.20 1.30K1.000---25.40---ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages.“Typical” parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates,and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.PUBLICATION ORDERING INFORMATION。

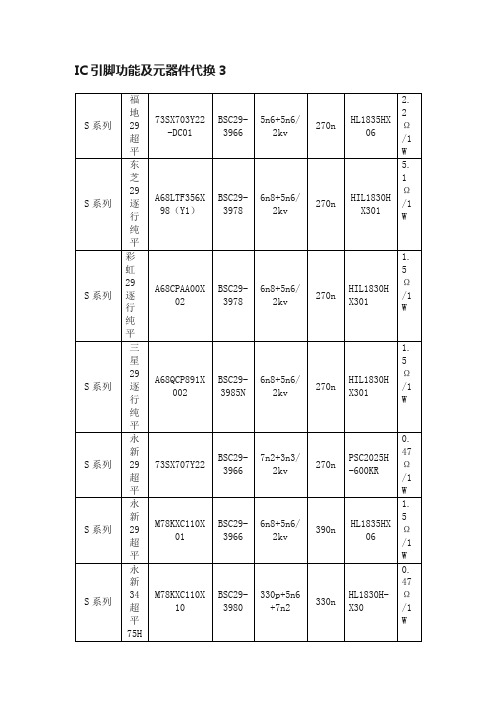

IC引脚功能及元器件代换3

HIL1830HX301

5.1Ω/1W

S系列

彩虹29逐行纯平

A68CPAA00X02

BSC29-3978

6n8+5n6/2kv

270n

HIL1830HX301

1.5Ω/1W

S系列

三星29逐行纯平

A68QCP891X002

BSC29-3985N

6n8+5n6/2kv

270n

HIL1830HX301

0.39Uf

HL1830-X14

1.5Ω/1W

J系列

赛格日立21

A51JSY63X13(C)

粗

BSC25-3368K

5n6+4n7+330p

0.39Uf

HL1830-X14

1.5Ω/1W

J系列

华飞21

A51EHW135X96

粗

BSC25-3368K

5n6+4n7+330p

0.39Uf

HL1830-X14

29永新超平

73SX707Y22-DC01

BSC29-3927

6n8+7n2/2kv

330n

HL1830

3.9Ω/1W

A系列

29永新超平

73SX707Y22-DC02

BSC29-3910A

6n8+6n8/2kv

330n

HL1830

2Ω/1W

A系列

29华飞超平

A68ESF004X111

BSC29-3910A

纯平

A51LVV896X-12

粗

BSC24-3031*

6n8+5n6+180n

ZMM5237B中文资料(SynSemi)中文数据手册「EasyDatasheet - 矽搜」

还是I .齐纳阻抗测量是在两个点,以确防护

在击穿曲线和锋利膝盖消除不稳定单位

(2)有效规定,电极被防护持在环境温度

(3)标准齐纳电压容差

± 5%容差.

典型 体温 系数

VZ(%/ °C)

-0.075 -0.070 -0.065 -0.060 -0.055 ±0.030 ±0.030 +0.038 +0.038 +0.045 +0.050 +0.058 +0.062 +0.065 +0.068 +0.075 +0.076 +0.077 +0.079 +0.082 +0.082 +0.083 +0.084 +0.085 +0.086 +0.086 +0.087 +0.088 +0.089 +0.090 +0.091 +0.091 +0.092 +0.093 +0.094 +0.095 +0.095 +0.096 +0.096 +0.097 +0.098 +0.097 +0.098

电气特性

等级25

°C环境温度,除非另有specifie

额定齐纳

Test

电压

(3)

当前

Type

V Z @ I ZT

IZT

(V)

(mA)

最大齐纳

阻抗

(1)

ZZT @ IZT IZK Z=ZK0.2@5mA

(Ω)

(Ω)

最大反向 泄漏电流

IR @ V R

(μA)

AN7805中文资料

Input

Output

Starter

Voltage Reference

+ Error Amp. −

R2 Thermal Protection

R1 2

Common

8.70±0.30

4.20±0.25 3.80±0.25

12.5±0.2 17.0±0.2 26.1±0.2 29.0±0.3

8.7±0.2

(13.6)

2.54 2.54

0.45 +0.2 –0.0 (2.0) (2.5)

10.5±0.3

HSIP003-P-0000

AN78xxF series

10.50±0.30 φ5.30 (4.30) (1.73) φ3.10±0.10

Unit: mm

2.77±0.30

16.70±0.30

17.00±0.25

元器件交易网

Voltage Regulators

AN78xx/AN78xxF Series

3-pin positive output voltage regulator (1 A type)

I Overview

The AN78xx series and the AN78xxF series are 3pin, fixed positive output type monolithic voltage regulators. Stabilized fixed output voltage is obtained from unstable DC input voltage without using any external components. 11 types of fixed output voltage are available; 5V, 6V, 7V, 8V, 9V, 10V, 12V, 15V, 18V, 20V, and 24V. They can be used widely in power circuits with current capacity of up to 1A. AN78xx series

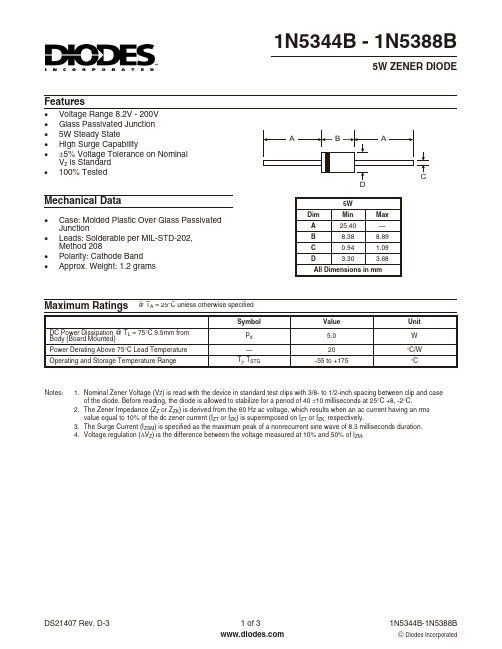

1N5347B中文资料

·Voltage Range 8.2V - 200V ·Glass Passivated Junction ·5W Steady State·High Surge Capability·±5% Voltage Tolerance on Nominal V Z is Standard ·100% Tested1N5344B - 1N5388B5W ZENER DIODENotes:1.Nominal Zener Voltage (V Z ) is read with the device in standard test clips with 3/8- to 1/2-inch spacing between clip and case of the diode. Before reading, the diode is allowed to stabilize for a period of 40 ±10 milliseconds at 25°C +8, -2°C.2.The Zener Impedance (Z Zor Z ZK ) is derived from the 60 Hz ac voltage, which results when an ac current having an rmsvalue equal to 10% of the dc zener current (I ZT or I ZK ) is superimposed on I ZT or I ZK, respectively.3.The Surge Current (I ZSM ) is specified as the maximum peak of a nonrecurrent sine wave of 8.3 milliseconds duration.4.Voltage regulation (D V Z ) is the difference between the voltage measured at 10% and 50% of I ZM .Maximum Ratings@ T A= 25°C unless otherwise specifiedFeaturesMechanical Data·Case: Molded Plastic Over Glass Passivated Junction·Leads: Solderable per MIL-STD-202,Method 208·Polarity: Cathode Band ·Approx. Weight: 1.2 gramsElectrical Characteristics@ T A = 25°C unless otherwise specifiedV F = 1.2V max at I F = 1.0A all types.Suffix ‘B’ denotes 5% tolerance which is standard.11010010000.11.010100V ,REVERSE VOLTAGE (V)R Fig.1, Typ.Capacitance vs.Reverse VoltageC ,C A P A C I T A N C E (p F )j123456255075100125150175200T LEAD TEMPERATURE 9.5mm FROM BODY (ºC)L,Fig.3,Power Derating CurveP ,P O W E R D I S S I P A T I O N (W )d 1.0101001000I ,ZENER CURRENT (mA)ZT Fig.2,Typ.Zener Impedance vs.Zener CurrentZ ,Z E N E R I M P E D A N C E (W )Z T。

5357芯片手册

PRODUCT SPECIFICATION

8

200904

CHINAIC SEMICONDUCTOR

■ 时序表

CJC5357

图 3 MCLK,LRCK,SCLK 时序图

PRODUCT SPECIFICATION

图 4 音频接口时序图 9

200904

CHINAIC SEMICONDUCTOR

CJC5357

注意 11:SCLK 上升沿不能和 LRCK 变化沿发生在同一时间。 注意 12:使 PDN 的引脚处于 L 时,能使 CJC5357 Reset. 注意 13:这个周期是从 PDN 脚为 H 时到 LRCK 上升沿的时间。

-20 -20

150

64fs 50

4233 4051

Hz

%

20

ns

35

ns

ns 1/fs 1/fs

共模电压输出引脚,VA/2

ADC 的偏置电压输入

模拟地引脚

模拟电源引脚,2.7~3.6V

数字电源引脚, 2.7~3.6V

数字地引脚

音频串行数据输出引脚 掉电状态下输出“L”

fs输出数据

输出通道时钟引脚

掉电状态下在主模式中输出“L”

主时钟输入引脚

音频串行数据时钟引脚

掉电状态下在主模式中输出“L”

掉电模式设置引脚 “H”:上电,“L”:掉电

模式 0 1

DIF pin L H

SDTO

LRCK

24bit,MSB justified

H/L

24bit,I2S compatibel

L/H

表 3:音频接口格式

SCLK ≥48fs or 32fs ≥48fs or 32fs

SI5367B-B-GQ资料

Preliminary Rev. 0.3 3/07Copyright © 2007 by Silicon Laboratories Si5367This information applies to a product under development. Its characteristics and specifications are subject to change without notice.Si5367µP-P R O G R A M M A B L E P R E C I S I O N C L O C K M U L T I P L I E RDescriptionThe Si5367 is a low jitter, precision clock multiplier for applications requiring clock multiplication without jitter attenuation. The Si5367 accepts four clock inputs ranging from 10 to 707MHz and generates five frequency-multiplied clock outputs ranging from 10 to 945MHz and select frequencies to 1.4GHz. The device provides virtually any frequency translation combination across this operating range. The outputs are divided down separately from a common source. The Si5367 input clock frequency and clock multiplication ratio are programmable through an I 2C or SPI interface. The Si5367 is based on Silicon Laboratories' 3rd-generation DSPLL ® technology, which provides any-rate frequency synthesis in a highly integrated PLL solution that eliminates the need for external VCXO and loop filter components. The DSPLL loop bandwidth is digitally programmable, providing jitter performance optimization at the application level. Operating from a single 1.8 or 2.5V supply, the Si5367 is ideal for providing clock multiplication in high performance timing applications.ApplicationsSONET/SDH OC-48/OC-192 line cards GbE/10GbE, 1/2/4/8/10GFC line cards ITU G.709 and custom FEC line cards Wireless basestations Data converter clocking xDSLSONET/SDH + PDH clock synthesisTest and measurementFeaturesGenerates any frequency from 10 to 945MHz and select frequencies to 1.4GHz from an input frequency of 10 to 710MHzLow jitter clock outputs w/jitter generation as low as 0.6ps rms (50 kHz–80 MHz)Integrated loop filter with selectable loop bandwidth (30 kHz to 1.3 MHz)Four clock inputs w/manual or automatically controlled hitless switchingFive clock outputs with selectable signal format (LVPECL, LVDS, CML, CMOS)Support for ITU G.709 FEC ratios (255/238, 255/237, 255/236) LOS alarm outputsDigitally-controlled output phase adjustI 2C or SPI programmable settingsOn-chip voltage regulator for 1.8 or 2.5V ±10% operationSmall size: 14x 14mm 100-pin TQFP Pb-free, RoHS compliantP R E L I M I N A R Y D A TA S H E E TSi53672Preliminary Rev. 0.3Table 1. Performance Specifications(V DD=1.8 or 2.5V ±10%, T A=–40 to 85 ºC)Parameter Symbol Test Condition Min Typ Max Unit Temperature Range T A–402585ºC Supply Voltage V DD 2.25 2.5 2.75V1.62 1.8 1.98V Supply Current I DD f OUT = 622.08 MHzAll CKOUTs enabledLVPECL format output—394435mAOnly CKOUT1 enabled—253284mAf OUT = 19.44 MHzAll CKOUTs enabledCMOS format output—278321mAOnly CKOUT1 enabled—229261mATristate/Sleep Mode—TBD TBD mAInput Clock Frequency (CKIN1, CKIN2, CKIN3, CKIN4)CK F Input frequency and clockmultiplication ratio determinedby programming device PLLdividers. Consult Silicon Labo-ratories configuration softwareDSPLL sim or Any-Rate Preci-sion Clock Family ReferenceManual at /tim-ing to determine PLL dividersettings for a given input fre-quency/clock multiplicationratio combination.10—707.35MHzOutput Clock Frequency (CKOUT1, CKOUT2, CKOUT3, CKOUT4, CKOUT5)CK OF109701213———94511341417MHzInput Clocks (CKIN1, CKIN2, CKIN3, CKIN4)Differential Voltage Swing CKN DPP0.25— 1.9V PP Common Mode Voltage CKN VCM 1.8V ±10%0.9— 1.4V2.5V ±10% 1.0— 1.7V Rise/Fall Time CKN TRF20–80%——11ns Duty Cycle CKN DC Whichever is less40—60%50—ns Output Clocks (CKOUT1, CKOUT2, CKOUT3, CKOUT4, CKOUT5)Common Mode V OCM LVPECL100Ω loadline-to-line V DD–1.42—V DD–1.25VDifferential Output Swing V OD 1.1— 1.9V Single Ended OutputSwingV SE0.5—0.93VNote: For a more comprehensive listing of device specifications, please consult the Silicon Laboratories Any-Rate Precision Clock Family Reference Manual. This document can be downloaded from /timing.Si5367Preliminary Rev. 0.33Rise/Fall Time CKO TRF 20–80%230350ps Duty Cycle CKO DC 45—55%PLL Performance Jitter GenerationJ GENf OUT = 622.08 MHz,LVPECL output format 50kHz–80MHz —0.6TBD ps rms12kHz–20MHz —0.6TBD ps rms 800Hz–80MHz—TBD TBD ps rms Jitter Transfer J PK —0.050.1dB Phase NoiseCKO PNf OUT = 622.08 MHz 100 Hz offset—TBD TBD dBc/Hz 1 kHz offset —TBD TBD dBc/Hz 10 kHz offset —TBD TBD dBc/Hz 100 kHz offset —TBD TBD dBc/Hz 1 MHz offset—TBD TBD dBc/Hz Subharmonic Noise SP SUBH Phase Noise @ 100kHz Offset —TBD TBD dBc Spurious Noise SP SPURMax spur @ n x F3(n > 1, n x F3 < 100MHz)—TBDTBDdBcPackageThermal Resistance Junction to AmbientθJAStill Air —40—ºC/WTable 2. Absolute Maximum RatingsParameterSymbol Value Unit DC Supply Voltage V DD –0.5 to 2.75V LVCMOS Input VoltageV DIG –0.3 to (V DD + 0.3)V Operating Junction Temperature T JCT –55 to 150ºC Storage Temperature RangeT STG–55 to 150ºC ESD HBM Tolerance (100 pF, 1.5k Ω)2kV ESD MM Tolerance 200VLatch-Up ToleranceJESD78 CompliantNote:Permanent device damage may occur if the Absolute Maximum Ratings are exceeded. Functional operation should berestricted to the conditions as specified in the operation sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods of time may affect device reliability.Table 1. Performance Specifications (Continued)(V DD =1.8 or 2.5V ±10%, T A =–40 to 85 ºC)ParameterSymbol Test ConditionMin Typ Max Unit Note: For a more comprehensive listing of device specifications, please consult the Silicon Laboratories Any-Rate PrecisionClock Family Reference Manual. This document can be downloaded from /timing .Si53674Preliminary Rev. 0.3Si5367Preliminary Rev. 0.35Figure 2.Si5367 Typical Application Circuit (IC Control Mode)Figure 3.Si5367 Typical Application Circuit (SPI Control Mode)Si53676Preliminary Rev. 0.31. Functional DescriptionThe Si5367 is a low jitter, precision clock multiplier for applications requiring clock multiplication without jitter attenuation. The Si5367 accepts four clock inputs ranging from 10 to 707MHz and generates five frequency-multiplied clock outputs ranging from 10 to 945MHz and select frequencies to 1.4GHz. The device provides virtually any frequency translation combination across this operating range. Independent dividers are available for every input clock and output clock, so the Si5367 can accept input clocks at different frequencies and it can generate output clocks at different frequencies. The Si5367 input clock frequency and clock multiplication ratio are programmable through an I2C or SPI interface. Silicon Laboratories offers a PC-based software utility, DSPLL sim, that can be used to determine the optimum PLL divider settings for a given input frequency/clock multiplication ratio combination that minimizes phase noise and power consumption. This utility can be downloaded from /timing.The Si5367 is based on Silicon Laboratories' 3rd-generation DSPLL® technology, which provides any-rate frequency synthesis in a highly integrated PLL solution that eliminates the need for external VCXO and loop filter components. The Si5367 PLL loop bandwidth is digitally programmable and supports a range from 30kHz to 1.3MHz. The DSPLL sim software utility can be used to calculate valid loop bandwidth settings for a given input clock frequency/clock multiplication ratio. The Si5367 monitors all input clocks for loss-of-signal and provides a LOS alarm when it detects missing pulses on its inputs.In the case when the input clocks enter alarm conditions, the PLL will freeze the DCO output frequency near its last value to maintain operation with an internal state close to the last valid operating state. The Si5367 has five differential clock outputs. The signal format of the clock outputs is programmable to support LVPECL, LVDS, CML, or CMOS loads. If not required, unused clock outputs can be powered down to minimize power consumption. The phase difference between the selected input clock and the output clocks is adjustable in 200ps increments for system skew control. In addition, the phase of each output clock may be adjusted in relation to the other output clocks. The resolution varies from 800ps to 2.2ns depending on the PLL divider settings. Consult the DSPLL sim configuration software to determine the phase offset resolution for a given input clock/clock multiplication ratio combination. For system-level debugging, a bypass mode is available which drives the output clock directly from the input clock, bypassing the internal DSPLL. The device is powered by a single 1.8 or 2.5V supply.1.1. Further DocumentationConsult the Silicon Laboratories Any-Rate Precision Clock Family Reference Manual (FRM) for more detailed information about the Si5367. The FRM can be downloaded from /timing.Silicon Laboratories has developed a PC-based software utility called DSPLL sim to simplify device configuration, including frequency planning and loop bandwidth selection. This utility can be downloaded from /timing.Si5367Preliminary Rev. 0.372. Pin Descriptions: Si5367Table 3. Si5367 Pin DescriptionsPin #Pin NameI/OSignal LevelDescription1, 2, 4, 17, 20, 22, 23, 24, 25, 37, 47, 48, 49, 50, 51, 52, 53, 54, 55, 56, 66, 67, 72, 73, 74, 75, 80, 85, 95NCNo Connect.These pins must be left unconnected for normal opera-tion.3RST I LVCMOSExternal Reset.Active low input that performs external hardware reset of device. Resets all internal logic to a known state and forces the device registers to their default value. Clock outputs are tristated during reset. After rising edge of RST signal, the device will perform an internal self-cali-bration.This pin has a weak pull-up.Note:Internal register names are indicated by underlined italics, e.g. INT_PIN . See Si5368 Register Map.Si53678Preliminary Rev. 0.35, 6, 15, 27, 32, 42, 62, 63, 76, 79, 81, 84, 86, 89, 91, 94, 96,99, 100V DDVddSupplyV DD .The device operates from a 1.8 or 2.5V supply. Bypass capacitors should be associated with the following V DD pins:Pins Bypass Cap 5, 60.1 µF 150.1 µF 270.1 µF 62, 630.1 µF 76, 79 1.0 µF 81, 840.1 µF 86, 890.1 µF 91, 940.1 µF 96, 99, 1000.1 µF 7, 8, 14, 16, 18, 19, 21, 26, 28, 31, 33, 36, 38, 41, 43, 46, 64,65GND GND SupplyGround.This pin must be connected to system ground. Minimize the ground path impedance for optimal performance.9C1B O LVCMOSCKIN1 Invalid Indicator.This pin performs the CK1_BAD function ifCK1_BAD_PIN =1 and is tristated if CK1_BAD_PIN =0. Active polarity is controlled by CK_BAD_POL .0=No alarm on CKIN1.1=Alarm on CKIN1.10C2B O LVCMOSCKIN2 Invalid Indicator.This pin performs the CK2_BAD function ifCK2_BAD_PIN =1 and is tristated if CK2_BAD_PIN =0. Active polarity is controlled by CK_BAD_POL .0=No alarm on CKIN2.1=Alarm on CKIN2.11C3B O LVCMOSCKIN3 Invalid Indicator.This pin performs the CK3_BAD function ifCK3_BAD_PIN =1 and is tristated if CK3_BAD_PIN =0. Active polarity is controlled by CK_BAD_POL .0=No alarm on CKIN3.1=Alarm on CKIN3.Table 3. Si5367 Pin Descriptions (Continued)Pin #Pin Name I/O Signal Level DescriptionNote:Internal register names are indicated by underlined italics, e.g. INT_PIN . See Si5368 Register Map.Si5367Preliminary Rev. 0.3912INT_ALMOLVCMOSInterrupt/Alarm Output Indicator.This pin functions as a maskable interrupt output with active polarity controlled by the INT_POL register bit. The INT output function can be turned off by setting INT_PIN =0. If the ALRMOUT function is desired instead on this pin, set ALRMOUT_PIN =1 and INT_PIN =0.0=ALRMOUT not active.1=ALRMOUT active.The active polarity is controlled by CK_BAD_POL . If no function is selected, the pin tristates.1357CS0_C3A CS1_C4AI/O LVCMOSInput Clock Select/CKIN3 or CKIN4 Active Clock Indi-cator.If manual clock selection is chosen, and ifCKSEL_PIN =1, the CKSEL pins control clock selection and the CKSEL_REG bits are ignored.If CKSEL_PIN =0,the CKSEL_REG register bits control this function and these inputs tristate. If these pins are not functioning as the CS[1:0] inputs and auto clock selection is enabled, then they serve as the CKIN_n active clock indicator.0=CKIN3 (CKIN4) is not the active input clock1=CKIN3 (CKIN4) is currently the active input to the PLLThe CKn_ACTV_REG bit always reflects the active clock status for CKIN_n. If CKn_ACTV_PIN =1, this status will also be reflected on the CnA pin with active polarity con-trolled by the CK_ACTV_POL bit. IfCKn_ACTV_PIN =0, this output tristates.This pin has a weak pull-down.2930CKIN4+CKIN4–IMULTIClock Input 4.Differential clock input. This input can also be driven with a single-ended signal. CKIN4 serves as the frame sync input associated with the CKIN2 clock when CK_CONFIG_REG =1.3435CKIN2+CKIN2–I MULTIClock Input 2.Differential input clock. This input can also be driven with a single-ended signal.Table 3. Si5367 Pin Descriptions (Continued)Pin #Pin Name I/O Signal Level DescriptionNote:Internal register names are indicated by underlined italics, e.g. INT_PIN . See Si5368 Register Map.CS[1:0]Active Input Clock00CKIN101CKIN210CKIN311CKIN4Si536710Preliminary Rev. 0.33940CKIN3+CKIN3–I MULTI Clock Input 3.Differential clock input. This input can also be driven witha single-ended signal. CKIN3 serves as the frame syncinput associated with the CKIN1 clock whenCK_CONFIG_REG=1.4445CKIN1+CKIN1–I MULTI Clock Input 1.Differential clock input. This input can also be driven witha single-ended signal.58C1A O LVCMOS CKIN1 Active Clock Indicator.This pin serves as the CKIN1 active clock indicator. TheCK1_ACTV_REG bit always reflects the active clock sta-tus for CKIN1. If CK1_ACTV_PIN=1, this status willalso be reflected on the C1A pin with active polarity con-trolled by the CK_ACTV_POL bit. IfCK1_ACTV_PIN=0, this output tristates.59C2A O LVCMOS CKIN2 Active Clock Indicator.This pin serves as the CKIN2 active clock indicator. TheCK2_ACTV_REG bit always reflects the active clock sta-tus for CKIN_2. If CK2_ACTV_PIN=1, this status willalso be reflected on the C2A pin with active polarity con-trolled by the CK_ACTV_POL bit. IfCK2_ACTV_PIN=0, this output tristates.60SCL I LVCMOS Serial Clock.This pin functions as the serial port clock input for bothSPI and I2C modes.This pin has a weak pull-down.61SDA_SDO I/O LVCMOS Serial Data.In I2C microprocessor control mode (CMODE=0), thispin functions as the bidirectional serial data port.In SPImicroprocessor control mode (CMODE=1), this pinfunctions as the serial data output.6869A0A1I LVCMOS Serial Port Address.In I2C control mode (CMODE=0), these pins function ashardware controlled address bits.In SPI control mode (CMODE=1), these pins areignored.This pin has a weak pull-down.70A2_SS I LVCMOS Serial Port Address/Slave Select.In I2C microprocessor control mode (CMODE=0), thispin functions as a hardware controlled address bit.In SPI microprocessor control mode (CMODE=1), thispin functions as the slave select input.This pin has a weak pull-down.Table 3. Si5367 Pin Descriptions (Continued)Pin #Pin Name I/O Signal Level DescriptionNote:Internal register names are indicated by underlined italics, e.g. INT_PIN. See Si5368 Register Map.71SDIILVCMOSSerial Data In.In SPI microprocessor control mode (CMODE =1), this pin functions as the serial data input.In I 2C microprocessor control mode (CMODE =0), this pin is ignored.This pin has a weak pull-down.7778CKOUT3+ CKOUT3–O MULTIClock Output 3.Differential clock output. Output signal format is selected by SFOUT3_REG register bits. Output is differential for LVPECL, LVDS, and CML compatible modes. For CMOS format, both output pins drive identical single-ended clock outputs.8283CKOUT1–CKOUT1+O MULTIClock Output 1.Differential clock output. Output signal format is selected by SFOUT1_REG register bits. Output is differential for LVPECL, LVDS, and CML compatible modes. For CMOS format, both output pins drive identical single-ended clock outputs.8788CKOUT5–CKOUT5+O MULTIClock Output 5.Differential clock output. Output signal format is selected by SFOUT5_REG register bits. Output is differential for LVPECL, LVDS, and CML compatible modes. For CMOS format, both output pins drive identical single-ended clock outputs.90CMODE I 3-LevelControl Mode.Selects I 2C or SPI control mode for the device.0=I 2C Control Mode.1=SPI Control Mode.9293CKOUT2+CKOUT2–O MULTIClock Output 2.Differential clock output. Output signal format is selected by SFOUT2_REG register bits. Output is differential for LVPECL, LVDS, and CML compatible modes. For CMOS format, both output pins drive identical single-ended clock outputs.9798CKOUT4–CKOUT4+O MULTIClock Output 4.Differential clock output. Output signal format is selected by SFOUT4_REG register bits. Output is differential for LVPECL, LVDS, and CML compatible modes. For CMOS format, both output pins drive identical single-ended clock outputs.GND PAD GND PAD GND SupplyGround Pad.The ground pad must provide a low thermal and electri-cal impedance to a ground plane.Table 3. Si5367 Pin Descriptions (Continued)Pin #Pin Name I/O Signal Level DescriptionNote:Internal register names are indicated by underlined italics, e.g. INT_PIN . See Si5368 Register Map.3. Ordering GuideOrdering Part NumberOutput ClockFrequency RangePackage Temperature RangeSi5367A-B-GQ10–945MHz970–1134MHz1.213–1.417GHz100-Pin 14x14mm TQFP–40 to 85°CSi5367B-B-GQ10–808MHz100-Pin 14x14mm TQFP–40 to 85°C Si5367C-B-GQ10–346MHz100-Pin 14x14mm TQFP–40 to 85°C4. Package Outline: 100-Pin TQFPFigure4 illustrates the package details for the Si5367. Table4 lists the values for the dimensions shown in the illustration.Table 4. 100-Pin Package Diagram DimensionsDimension Min Nom Max Dimension Min Nom Max A—— 1.20E16.00 BSC.A10.05—0.15E114.00 BSC.A20.95 1.00 1.05E2 3.85 4.00 4.15b0.170.220.27L0.450.600.75c0.09—0.20aaa——0.20D16.00 BSC.bbb——0.20D114.00 c——0.08D2 3.85 4.00 4.15ddd——0.08e0.50BSC.θ0º 3.5º7ºNotes:1.All dimensions shown are in millimeters (mm) unless otherwise noted.2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.3. This package outline conforms to JEDEC MS-026, variant AED-HD.4. Recommended card reflow profile is per the JEDEC/IPC J-STD-020C specification for Small BodyComponents.5. Recommended PCB LayoutTable 5. PCB Land Pattern DimensionsDimension MIN MAXe0.50BSC.E15.40 REF.D15.40 REF.E2 3.90 4.10D2 3.90 4.10GE13.90—GD13.90—X—0.30Y 1.50REF.ZE—16.90ZD—16.90R10.15 REFR2— 1.00Notes (General):1.All dimensions shown are in millimeters (mm) unless otherwise noted.2. Dimensioning and Tolerancing is per the ANSI Y14.5M-1994 specification.3. This Land Pattern Design is based on IPC-7351 guidelines.4. All dimensions shown are at Maximum Material Condition (MMC). Least Material Condition(LMC) is calculated based on a Fabrication Allowance of 0.05mm.Notes (Solder Mask Design):1.All metal pads are to be non-solder mask defined (NSMD). Clearance between the soldermask and the metal pad is to be 60 µm minimum, all the way around the pad.Notes (Stencil Design):1. A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should beused to assure good solder paste release.2. The stencil thickness should be 0.125mm (5 mils).3. The ratio of stencil aperture to land pad size should be 1:1 for the perimeter pads.4. A 4x4 array of 0.80mm square openings on 1.05mm pitch should be used for the centerground pad.Notes (Card Assembly):1. A No-Clean, Type-3 solder paste is recommended.2. The recommended card reflow profile is per the JEDEC/IPC J-STD-020C specification forSmall Body Components.D OCUMENT C HANGE L ISTRevision 0.1 to Revision 0.2Changed LVTTL to LVCMOS in Table2, “Absolute Maximum Ratings,” on page3.Updated “2. Pin Descriptions: Si5367”.Changed FSOUT (pins 87 and 88) to CLKOUT5.Changed FS_ALIGN (pin 21) control pin to GND.Changed pin 16 to ground.Revision 0.2 to Revision 0.3Removed references to latency control, INC, and DEC pins.Updated block diagram on page 1.Added Figure1, “Typical Phase Noise Plot,” on page 4.Updated “2. Pin Descriptions: Si5367”.Changed font of register names to underlined italics.Updated "3. Ordering Guide" on page 12.Added “5. Recommended PCB Layout”.N OTES:C ONTACT I NFORMATIONSilicon Laboratories Inc.400 West Cesar ChavezAustin, TX 78701Tel: 1+(512) 416-8500Fax: 1+(512) 416-9669Toll Free: 1+(877) 444-3032Email: Clockinfo@Internet: The information in this document is believed to be accurate in all respects at the time of publication but is subject to change without notice. Silicon Laboratories assumes no responsibility for errors and omissions, and disclaims responsibility for any consequences resulting from the use of information included herein. Additionally, Silicon Laboratories assumes no responsibility for the functioning of undescribed features or parameters. Silicon Laboratories reserves the right to make changes without further notice. Silicon Laboratories makes no warranty, rep-resentation or guarantee regarding the suitability of its products for any particular purpose, nor does Silicon Laboratories assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation conse-quential or incidental damages. Silicon Laboratories products are not designed, intended, or authorized for use in applications intended to support or sustain life, or for any other application in which the failure of the Silicon Laboratories product could create a situation where per-sonal injury or death may occur. Should Buyer purchase or use Silicon Laboratories products for any such unintended or unauthorized ap-plication, Buyer shall indemnify and hold Silicon Laboratories harmless against all claims and damages.Silicon Laboratories, Silicon Labs, and DSPLL are trademarks of Silicon Laboratories Inc.Other products or brandnames mentioned herein are trademarks or registered trademarks of their respective holders.。

AK5366资料

(1) Pin Compatibility

Pin 26 Pin 34

AK5365 ALC CTRL

AK5366 TVDD

I2C

(2) Software Compatibility

Addr

00H 01H 02H 03H 04H 05H 06H 07H 08H 09H 0AH 0BH 0CH 0DH

I

Test 4 Pin This pin should be connected to AVSS.

I Lch Analog Input 1 Pin

I Lch Feedback Resistor Input Pin

O Lch Feedback Resistor Output Pin

I Lch IPGA Input Pin

D4

0 0 0 LTM0 IPGL4 IPGR4 ALC REF4 ATTL7 ATTR4 PHL4 PHL12 PHR4 PHR12

D3

0 0 DIF ZTM1 IPGL3 IPGR3 FR REF3 ATTL7 ATTR3 PHL3 PHL11 PHR3 PHR11

D2

MCKPD SEL2 CKS1 ZTM0 IPGL2 IPGR2 LMTH REF2 ATTL7 ATTR2 PHL2 PHL10 PHR2 PHR10

: Changing points from AK5365’s register.

MS0309-E-00 -4-

2004/05

ASAHI KASEI

PIN/FUNCTION

No. Pin Name 1 LIN5

2 TEST1

3 LIN4

4 TEST2

CZ5368B资料

ELECTRICAL CHARACTERISTICS: (TA=25°C), VF=1.2V MAX @ IF=1.0A FOR ALL TYPES.

Maximum Zener Type No. Voltage VZ @ IZT MIN Volts CZ5342B CZ5343B CZ5344B CZ5345B CZ5346B CZ5347B CZ5348B CZ5349B CZ5350B CZ5351B CZ5352B CZ5353B CZ5354B CZ5355B CZ5356B CZ5357B CZ5358B CZ5359B CZ5360B CZ5361B CZ5362B CZ5363B CZ5364B CZ5365B 6.460 7.125 7.790 8.265 8.645 9.500 10.45 11.40 12.35 13.30 14.25 15.20 16.15 17.10 18.05 19.00 20.90 22.80 23.75 25.65 26.60 28.50 31.35 34.20 NOM Volts 6.8 7.5 8.2 8.7 9.1 10 11 12 13 14 15 16 17 18 19 20 22 24 25 27 28 30 33 36 MAX Volts 7.140 7.875 8.610 9.135 9.555 10.50 11.55 12.60 13.65 14.70 15.75 16.80 17.85 18.90 19.95 21.00 23.10 25.20 26.25 28.35 29.40 31.50 34.65 37.80 Test Current IZT mA 175 175 150 150 150 125 125 100 100 100 75 75 70 65 65 65 50 50 50 50 50 40 40 30 Zener Impedance ZZT@IZT Ω 1.0 1.5 1.5 2.0 2.0 2.0 2.5 2.5 2.5 2.5 2.5 2.5 2.5 2.5 3.0 3.0 3.5 3.5 4.0 5.0 6.0 8.0 10 11 ZZK @ IZK Ω 200 200 200 200 150 125 125 125 100 75 75 75 75 75 75 75 75 100 110 120 130 140 150 160 mA 1.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0 Maximum Reverse Current IR µA 100 100 100 100 7.5 5.0 5.0 2.0 1.0 1.0 1.0 1.0 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 @ VR Volts 5.2 5.7 6.2 6.6 6.9 7.6 8.4 9.1 9.9 10.6 11.5 12.2 12.9 13.7 14.4 15.2 16.7 18.2 19.0 20.6 21.2 22.8 25.1 27.4 Maximum Surge Current (Note 1) ir A 11.5 10.7 10.0 7.5 9.2 8.6 8.0 7.5 7.0 6.7 6.3 6.00 5.8 5.5 5.3 5.1 4.7 4.4 4.3 4.1 3.9 3.7 3.5 3.3 Maximum Voltage Regulation (Note 2) ∆VZ Volts 0.25 0.25 0.20 0.20 0.22 0.22 0.25 0.25 0.25 0.25 0.25 0.30 0.35 0.40 0.40 0.40 0.45 0.55 0.55 0.60 0.60 0.60 0.65 0.65 IZM mA 700 630 580 545 520 475 430 395 365 340 315 295 280 264 250 237 216 198 190 176 170 158 144 132 CZ5342B CZ5343B CZ5344B CZ5345B CZ5346B CZ5347B CZ5348B CZ5349B CZ5350B CZ5351B CZ5352B CZ5353B CZ5354B CZ5355B CZ5356B CZ5357B CZ5358B CZ5359B CZ5360B CZ5361B CZ5362B CZ5363B CZ5364B CZ5365B Maximum Regulator Current Marking Code

某电子--全新IC手册d

STV8203……………………………

STV8223……………………………

STV9306……………………………

STV9379……………………………

TA1218AN……………………………

TA1219AN……………………………

TA1275AZ……………………………

TA1316………………………………

TDA2461………………………………

TDA2549………………………………

TDA2616………………………………

TDA3653………………………………

TDA3857………………………………

TDA4555………………………………

TDA4661………………………………

TDA4665………………………………

STR-F6653…………………………

STR-S6309…………………………

STR-S6709…………………………

STV2116……………………………

STV2180……………………………

STV2246……………………………

STV2248……………………………

STV5111……………………………

STV5112……………………………

MSM541222……………………………

MSP3310………………………………

MTV880…………………………………

NJM2192………………………………

NJM2700………………………………

NN5199…………………………………

NV320P…………………………………

OM8361…………………………………

41

2.6

主流步进驱动IC选型指南

主流步进驱动IC选型指南特点点评:1. TB6600作为东芝最新的大功率驱动IC,拥有最大50V@5A驱动能力,最高16细分,适用于部分86及全系列57步进电机,芯片自带欠压、过流、短路保护,而且自带5V逻辑电源,和LV8727并列为目前最高性价比的大功率驱动IC。

2. TB6560AHQ无疑是目前应用最多最广泛的步进驱动IC,适用于57及以下步进电机,由于出货量大所以价格便宜,且现货充足。

3. TB62209是最成熟的表贴式步进驱动IC之一,也曾经是性价比最高的42系列步进驱动芯片,但正逐渐被LV8731所取代。

4. LV8726是三洋针对于大中华区特别设计的一款驱动IC,电压高达60V,因为是外接Mosfet所以电流可以达到10A,最大128细分,且具有目前所有主流驱动IC的功能,目前还在内部测试中,预计今年下半年可以面市。

5. LV8727是三洋已经批量供货的最大功率驱动IC,前身是三洋给国内某公司定制的THB8128,三洋被安森美收购后将此IC做了工艺升级并小幅改善了封装方式,拥有最大********驱动能力,虽然稍逊于东芝的TB6600,但此IC细分数高达128,除了常用的保护功能外,还带有自动半流功能,价格也与TB6600相当,因此和TB6600并列为最高性价比大功率驱动IC。

6. LV8729是目前性价比最高的高细分表贴驱动IC,前身是三洋给国内某公司定制的THB6128,三洋被安森美收购后同样将此IC做了工艺升级,且大幅改善了封装和管脚排列方式,适用于部分57、全系列42及以下电机。

7. LV8731是三洋推出的非常成功的一款马达驱动IC,被誉为同级别中最高性价比,原本三洋的策略是剑指东芝的TB62209,但经过测试我们发现参数和驱动能力完全超越后者,已经和Allegro最成熟的A3977同一水准,且凭借新的工艺、多重保护以及自带逻辑5V,使得A3977也只能望尘莫及。

因此在2A以内电流的应用中,如果没有高细分的要求,LV8731是最好的选择。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

BL det.

SC out

36

35

34

33

32

31

30

29

28

27

VCCREF VCC1 (9 V)

37 38 39 40 41 42 43 44 45 46 47 48

25

FSC

C in

24

Limiter R out

2 3 4 5 6 7 8 9

Vertical signal clamp pin

ea s

Pl

M Di ain sc te on na tin nc ue e/ d

P clamp 22 21 20 19 18 17 16 15 14 13

Chroma

23

RGB

G out B out YS

DAC1 (V height

Y in

Video

APL det. SCL

H out

SDA

I2C

GND (main) FBP in

M Di ain sc te on na tin nc ue e/ d

Zener maximum current SW circuit gain 5 GSW fSW CT f = 1 MHz, 0.7 V[p-p] 4.9 −3 5.9 6.9 Frequency characteristics Crosstalk Attenuation amount at 7 MHz with f = 1 MHz as reference f = 1 MHz, input signal 0.7 V[p-p], sine wave −1.3 −50 6 Clamp current I1 , I46 , Sink current of each input pin, when I48 applying 3 V to pin 1, pin 46 and pin 48 10 0 14 Total gain GTOTAL Gain dispersion from each input to output V41 VCC: Typ., input pin voltage measurement Input 2 V[p-p] stair steps −19 1.1

ea s

Storage temperature

e

*1

vi

Operating ambient temperature

*1

si

at io n.

Unit V mA mW °C °C mA 3

SDB00014BEB

AN5367FB

I Electrical Characteristics at Ta = 25°C

SDB00014BEB

or m

Killer out

L det. filter

H VCC (6.2 V)

H AFC1

at io n.

BLK in

AN5367FB

I Pin Descriptions (continued)

Pin No. 21 22 23 24 25 26 27 B output pin G output pin R output pin Output limiter pin Chroma oscillator pin Spot killer pin Description Pin No. 35 36 37 38 39 40 41 Description Black level detection filter pin Chroma signal input pin VCC1 reference voltage pin (9.6 V) Power supply pin (VCC1: 9 V) Capacitor pin for Y clamp DAC output pin 2

ICs for TV

AN5367FB

NTSC video, chroma, and deflection signal processing circuit

I Overview

The AN5367FB is an IC to demodulate the NTSC composite signal. It is possible to control the all functions by the I2C bus. The use of flat package allows a space saving in sets design.

or m

QFP048-P-1212B

at io n.

0.1±0.1

0.15 – 0.05

(1.0)

0° to 10° 0.5±0.2

Publication date: December 2001

SDB00014BEB

1

AN5367FB

I Block Diagram

Killer filter ABL/ACL Spot killer 26 APC filter OSD-G in OSD-R in OSD-B in BL start

Parameter SW and power supply Circuit current 1 (ICC1) (9 V system) Circuit current 2 (ICC2) (5 V system) 9.6 V reference voltage Operating resistance I38 I47 V37 R37 IVD No signal input, I14 = 8 mA, VCC1 = 9 V,VCC2 = 5 V No signal input, I14 = 8 mA, VCC1 = 9 V,VCC2 = 5 V I37 = 2.4 mA I37 = 1.0 mA to 5.0 mA Largest possible sink current 28 18 9.0 0 36 23 9.6 11 43 28 10.2 30 mA mA V Ω mA dB dB dB µA % Symbol Conditions Min Typ Max Unit

Pl

ea s

e

vi

si

tf o ht llow tp in :// g pa U na RL so a ni bo c. u ne t l t/s ate c/ st en in f

• Luminance signal processing • Incorporating 3.58 MHz trap • Black side gradation control is possible by black expansion circuit • Adopting delay line aperture control • Color signal processing • Incorporating band-pass filter • Incorporating ACC filter • Deflection signal processing • Stable sync. signal generation by the use of double AFC circuit and countdown circuit • Vertical directional screen position is adjustable • Others • Incorporating 3-input composite signal changeover SW • DAC output for adjusting sound volume and screen height

or m

ABL/ACL input pin

47

Power supply pin (VCC2: 5 V)

VCC

Supply current

ICC

Power dissipation *2

I Recommended Operating Range

Parameter Supply voltage Symbol VCC1 VCC2 Supply current I14 I37 Unit V

Sync.

VCC2 (5 V)

SW

Vscriptions

Pin No. 1

Video signal input pin 1

vi

si

Description

e

Video signal output pin

10

2

tf 5 V in ol ht low H in 6 tp in 7 down ref. :// Hold g pa U 8 det. out na L R GND (Jungle) so L a 9 10 niV out bo c. 11u X-ray ne t l at 12 H OSC t/s c/ est en in f

Pl

Note) *1 : Except for the operating ambient temperature and storage temperature, all ratings are for Ta = 25°C. *2 : The power dissipation shown is the value for Ta = 70°C.

I Absolute Maximum Ratings

Parameter Supply voltage

tf o ht llow tp in :// g pa U na RL so a ni bo c. u ne t l t/s ate c/ st en in f

Symbol Rating 9.9 5.5 47 31 13 5 VCC1 (38) VCC3 (47) I38 I47 I14 I37 PD 775 Topr Tstg −20 to +70 −55 to +150 Range 8.55 to 9.45 4.75 to 5.25 6.0 to 12 1.0 to 4.5