AON4803中文资料

MAX5033AUSA+中文资料

1

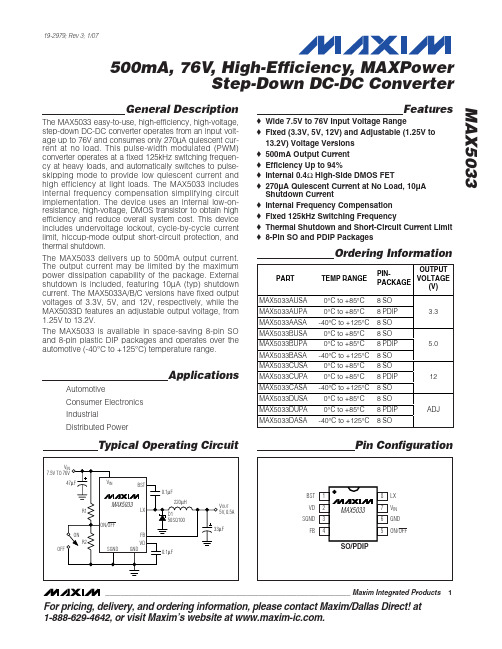

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at 1-888-629-4642, or visit Maxim’s website at .

220µH VOUT 5V, 0.5A 33µF

1 2 3 4

8

LX VIN GND ON/OFF

MAX5033

R1 ON/OFF ON R2 OFF SGND GND FB VD 0.1µF LX

VD SGND FB

D1 50SQ100

MAX5033___________________________________________________________ Maxim Integrated Products

元器件交易网

500mA, 76V, High-Efficiency, MAXPower Step-Down DC-DC Converter MAX5033

ABSOLUTE MAXIMUM RATINGS

(Voltages referenced to GND, unless otherwise specified.) VIN .........................................................................-0.3V to +80V SGND ....................................................................-0.3V to +0.3V LX.................................................................-0.8V to (VIN + 0.3V) BST ...............................................................-0.3V to (VIN + 10V) BST (transient < 100ns) ................................-0.3V to (VIN + 15V) BST to LX................................................................-0.3V to +10V BST to LX (transient < 100ns) ................................-0.3V to +15V ON/OFF ........................................................-0.3V to (VIN + 0.3V) VD...........................................................................-0.3V to +12V FB MAX5033A/MAX5033B/MAX5033C ...................-0.3V to +15V MAX5033D .........................................................-0.3V to +12V VOUT Short-Circuit Duration (VIN ≤ 40V)........................Indefinite VD Short-Circuit Duration ..............................................Indefinite Continuous Power Dissipation (TA = +70°C) 8-Pin PDIP (derate 9.1mW/°C above +70°C)...............727mW 8-Pin SO (derate 5.9mW/°C above +70°C)..................471mW Operating Temperature Range MAX5033_U_ _ ...................................................0°C to +85°C MAX5033_A_ _ ..............................................-40°C to +125°C Storage Temperature Range .............................-65°C to +150°C Junction Temperature ......................................................+150°C Lead Temperature (soldering, 10s) .................................+300°C

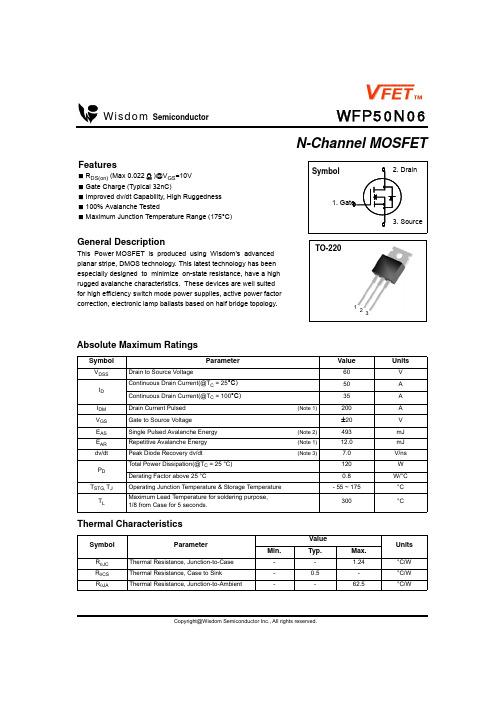

WFP50N06中文资料

ID, Drain Current [A]

102

101 175℃ 25℃

100 2

-55℃

※ Notes :

1. VDS = 30V 2. 250µ s Pulse Test

4

6

8

10

VGS, Gate-Source Voltage [V]

Figure 2. Transfer Characteristics

12

10

VDS = 30V

VDS = 48V 8

6

4

2

※ Note : ID = 50A

0

0

5

10

15

20

25

30

35

QG, Total Gate Charge [nC]

Figure 6. Gate Charge Characteristics

Capacitance [pF]

元器件交易网

※ Notes : 1. VGS = 0 V 2. f = 1 MHz

100

101

VDS, Drain-Source Voltage [V]

Figure 5. Capacitance Characteristics

VGS, Gate-Source Voltage [V]

IDR, Reverse Drain Current [A]

Min. -

Typ. 50 70

Max. 50 200 1.5 -

Unit.

A V emiconductor Inc., All rights reserved.

元器件交易网

Typical Characteristics

ID, Drain Current [A]

ET80960JA3V252中文资料

80960JA/JF/JD/JS/JC/JT 3.3 V Embedded 32-Bit MicroprocessorDatasheetProduct Featuress Code Compatible with all 80960Jx ProcessorssHigh-Performance Embedded Architecture —One Instruction/Clock Execution —Core Clock Rate is:1x the Bus Clock for 80960JA/JF/JS 2x the Bus Clock for 80960JD/JC 3x the Bus Clock for 80960JT —Load/Store Programming Model —Sixteen 32-Bit Global Registers—Sixteen 32-Bit Local Registers (8 sets)—Nine Addressing Modes—User/Supervisor Protection Model sTwo-Way Set Associative Instruction Cache—80960JA - 2Kbyte —80960JF/JD - 4Kbyte —80960JS/JC/JT - 16Kbyte —Programmable Cache-Locking MechanismsDirect Mapped Data Cache —80960JA - 1Kbyte —80960JF/JD - 2Kbyte —80960JS/JC/JT - 4Kbyte —Write Through Operation sOn-Chip Stack Frame Cache—Seven Register Sets May Be Saved —Automatic Allocation on Call/Return —0-7 Frames Reserved for High-Priority InterruptssOn-Chip Data RAM—1Kbyte Critical Variable Storage —Single-Cycle Access s3.3V Supply Voltage —5V Tolerant Inputs—TTL Compatible Outputs sHigh Bandwidth Burst Bus—32-Bit Multiplexed Address/Data—Programmable Memory Configuration —Selectable 8-, 16-, 32-Bit Bus Widths —Supports Unaligned Accesses—Big or Little Endian Byte Ordering sHigh-Speed Interrupt Controller —31 Programmable Priorities —Eight Maskable Pins plus NMI#—Up to 240 Vectors in Expanded Mode sTwo On-Chip Timers—Independent 32-Bit Counting —Clock Prescaling by 1, 2, 4 or 8—Internal Interrupt Sources s Halt Mode for Low Powers IEEE 1149.1 (JTAG) Boundary Scan Compatibility sPackages—132-Lead Pin Grid Array (PGA)—132-Lead Plastic Quad Flat Pack (PQFP)—196-Ball Mini Plastic Ball Grid Array (MPBGA)Order Number: 273159-006August 2004INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL’S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, life sustaining applications.Intel may make changes to specifications and product descriptions at any time, without notice.Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.The 80960JA/JF/JD/JS/JC/JT 3.3 V Embedded 32-Bit Microprocessor may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling1-800-548-4725 or by visiting Intel’s website at .AlertVIEW, AnyPoint, AppChoice, BoardWatch, BunnyPeople, CablePort, Celeron, Chips, CT Connect, CT Media, Dialogic, DM3, EtherExpress, ETOX, FlashFile, i386, i486, i960, iCOMP, InstantIP, Intel, Intel logo, Intel386, Intel486, Intel740, IntelDX2, IntelDX4, IntelSX2, Intel Create & Share, Intel GigaBlade, Intel InBusiness, Intel Inside, Intel Inside logo, Intel NetBurst, Intel NetMerge, Intel NetStructure, Intel Play, Intel Play logo, Intel SingleDriver, Intel SpeedStep, Intel StrataFlash, Intel TeamStation, Intel Xeon, Intel XScale, IPLink, Itanium, LANDesk, LanRover, MCS, MMX, MMX logo, Optimizer logo, OverDrive, Paragon, PC Dads, PC Parents, PDCharm, Pentium, Pentium II Xeon, Pentium III Xeon, Performance at Your Command, RemoteExpress, Shiva, SmartDie, Solutions960, Sound Mark, StorageExpress, The Computer Inside., The Journey Inside, TokenExpress, Trillium, VoiceBrick, Vtune, and Xircom are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.*Other names and brands may be claimed as the property of others.Copyright © Intel Corporation, 2002, 2004Contents Contents1.0Introduction (7)2.080960Jx Overview (9)2.180960 Processor Core (10)2.2Burst Bus (11)2.3Timer Unit (11)2.4Priority Interrupt Controller (11)2.5Instruction Set Summary (12)2.6Faults and Debugging (12)2.7Low Power Operation (12)2.8Test Features (12)2.9Memory-Mapped Control Registers (13)2.10Data Types and Memory Addressing Modes (13)3.0Packaging Information (15)3.1Available Processors and Packages (15)3.2Pin Descriptions (16)3.2.1Functional Pin Definitions (16)3.2.280960Jx 132-Lead PGA Pinout (23)3.2.380960Jx 132-Lead PQFP Pinout (27)3.2.480960Jx 196-Ball MPBGA Pinout (30)4.0Electrical Specifications (35)4.1Absolute Maximum Ratings (35)4.2Operating Conditions (35)4.3Connection Recommendations (36)4.4VCC5 Pin Requirements (VDIFF) (36)4.5VCCPLL Pin Requirements (37)4.6 D.C. Specifications (38)4.7 A.C. Specifications (42)4.7.1 A.C. Test Conditions and Derating Curves (45)4.7.1.1Output Delay or Hold vs. Load Capacitance (46)4.7.1.2T LX vs. AD Bus Load Capacitance (47)4.7.1.3ICC Active vs. Frequency (49)4.7.2 A.C. Timing Waveforms (53)5.0Device Identification (59)5.180960JS/JC/JT Device Identification Register (60)5.280960JD Device Identification Register (61)5.380960JA/JF Device Identification Register (62)6.0Thermal Specifications (63)6.1Thermal Management Accessories (68)6.1.1Heatsinks (68)7.0Bus Functional Waveforms (69)7.1Basic Bus States (79)7.2Boundary-Scan Register (80)ContentsFigures180960Jx Microprocessor Package Options (7)280960Jx Block Diagram (10)3132-Lead Pin Grid Array Top View-Pins Facing Down (23)4132-Lead Pin Grid Array Bottom View-Pins Facing Up (24)5132-Lead PQFP - Top View (27)6196-Ball Mini Plastic Ball Grid Array Top View-Balls Facing Down (30)7196-Ball Mini Plastic Ball Grid Array Bottom View-Balls Facing Up (31)8VCC5 Current-Limiting Resistor (36)9VCCPLL Lowpass Filter (37)10 A.C. Test Load (45)11Output Delay or Hold vs. Load Capacitance–80960JS/JC/JT (3.3 V Signals) (46)12Output Delay or Hold vs. Load Capacitance–80960JS/JC/JT (5V Signals) (46)13Output Delay or Hold vs. Load Capacitance–80960JA/JF/JD (47)14T LX vs. AD Bus Load Capacitance–80960JS/JC/JT (3.3V Signals) (47)15T LX vs. AD Bus Load Capacitance–80960JS/JC/JT (5V Signals) (48)16T LX vs. AD Bus Load Capacitance–80960JA/JF/JD (48)17I CC Active (Power Supply) vs. Frequency–80960JA/JF (49)1880960JA/JF I CC Active (Thermal) vs. Frequency (49)1980960JD I CC Active (Power Supply) vs. Frequency (50)2080960JD I CC Active (Thermal) vs. Frequency (50)2180960JC I CC Active (Power Supply) vs. Frequency (51)2280960JC I CC Active (Thermal) vs. Frequency (51)2380960JS I CC Active (Power Supply) vs. Frequency (52)2480960JS I CC Active (Thermal) vs. Frequency (52)25CLKIN Waveform (53)26T OV1 Output Delay Waveform (53)27T OF Output Float Waveform (54)28T IS1 and T IH1 Input Setup and Hold Waveform (54)29T IS2 and T IH2 Input Setup and Hold Waveform (54)30T IS3 and T IH3 Input Setup and Hold Waveform (55)31T IS4 and T IH4 Input Setup and Hold Waveform (55)32T LX, T LXL and T LXA Relative Timings Waveform (56)33DT/R# and DEN# Timings Waveform (56)34TCK Waveform (57)35T BSIS1 and T BSIH1 Input Setup and Hold Waveforms (57)36T BSOV1 and T BSOF1 Output Delay and Output Float Waveform (57)37T BSOV2 and T BSOF2 Output Delay and Output Float Waveform (58)38T BSIS2 and T BSIH2 Input Setup and Hold Waveform (58)3980960JS/JC/JT Device Identification Register Fields (60)4080960JD Device Identification Register Fields (61)4180960JA/JF Device Identification Register Fields (62)42Non-Burst Read and Write Transactions Without Wait States, 32-Bit Bus (69)43Burst Read and Write Transactions Without Wait States, 32-Bit Bus (70)44Burst Write Transactions With 2,1,1,1 Wait States, 32-Bit Bus (71)45Burst Read and Write Transactions Without Wait States, 8-Bit Bus (72)46Burst Read and Write Transactions With 1, 0 Wait Statesand Extra Tr State on Read, 16-Bit Bus (73)47Double Word Read Bus Request, Misaligned One Byte FromQuad Word Boundary, 32-Bit Bus, Little Endian (74)Contents 48HOLD/HOLDA Waveform For Bus Arbitration (75)49Cold Reset Waveform (76)50Warm Reset Waveform (77)51Entering the ONCE State (78)52Bus States with Arbitration (80)53Summary of Aligned and Unaligned Accesses (32-Bit Bus) (84)54Summary of Aligned and Unaligned Accesses (32-Bit Bus) (Continued) (85)Tables180960Jx 3.3-V Microprocessor Family (7)280960Jx Instruction Set (14)380960Jx Processors Available in 132-Pin PGA Package (15)480960Jx Processors Available in 132-Pin PQFP Package (15)580960Jx Processors Available in Extended Temperature (16)680960Jx Processors Available in 196-Ball MPBGA Package (16)7Pin Description Nomenclature (17)8Pin Description—External Bus Signals (18)9Pin Description—Processor Control Signals, Test Signals, and Power (21)10Pin Description—Interrupt Unit Signals (22)11132-Lead PGA Pinout—In Signal Order (25)12132-Lead PGA Pinout—In Pin Order (26)13132-Lead PQFP Pinout—In Signal Order (28)14132-Lead PQFP Pinout—In Pin Order (29)15196-Ball MPBGA Pinout—In Signal Order (32)16196-Ball MPBGA Pinout—In Pin Order (33)17Absolute Maximum Ratings (35)1880960Jx Operating Conditions (35)19VDIFF Parameters (37)2080960Jx D.C. Characteristics (38)2180960Jx I CC Characteristics (39)2280960Jx A.C. Characteristics (42)23Note Definitions for Table 22, 80960Jx AC Characteristics (45)2480960Jx Device Type and Stepping Reference (59)2580960JS/JC/JT Device ID Register Field Definitions (60)2680960JS/JC/JT Device ID Model Types (60)2780960JD Device ID Field Definitions (61)2880960JD Device ID Model Types (61)2980960JA/JF Device ID Field Definitions (62)3080960JA/JF Device ID Model Types (62)31Thermal Resistance for q CA and q JC Reference Table (63)32Maximum Ambient Temperature Reference Table (63)33132-Lead PGA Package Thermal Characteristics (64)3480960JA/JF/JD 196-Ball MPBGA Package Thermal Characteristics (64)3580960JS/JC/JT 196-Ball MPBGA Package Thermal Characteristics (65)36132-Lead PQFP Package Thermal Characteristics (65)37Maximum T A at Various Airflows in °C (80960JT) (66)38Maximum T A at Various Airflows in °C (80960JC) (66)39Maximum T A at Various Airflows in °C (80960JD) (67)40Maximum T A at Various Airflows in °C (80960JS) (67)41Maximum T A at Various Airflows in °C (80960JA/JF) (68)Contents42Boundary-Scan Register—Bit Order (81)43Natural Boundaries for Load and Store Accesses (81)44Summary of Byte Load and Store Accesses (82)45Summary of Short Word Load and Store Accesses (82)46Summary of n-Word Load and Store Accesses (n = 1, 2, 3, 4) (83)Revision HistoryDate Revision DescriptionSeptember 2002005Removed reference to A80960JF-16 from Table 3 on page15. Removed reference to NG80960JC-40, NG80960JC-33, NG80960JS-16,and NG80960JF-16 from Table 4 on page15.Removed reference to GD80960JC-40, GD80960JC-33, and 80960JS-16 in Table 6 on page16.Removed reference to 80960JC-40, 80960JC-33, 80960JS-16, and 80960JF-16 in Table 18 on page35.Removed reference to 80960JC-40, 80960JC-33, 80960JS-16, and 80960JF-16 from Table 21 on page39.Removed reference to 80960JC-40, 80960JC-33, 80960JS-16 and 80960JF-16 from Table 22 on page42.September 1999004Added new extended temp device offerings. See Table 5 on page16. Removed PGA package availability from JS/JC/JT processors. Changed AC timing parameter T OV1 (min) for extended temp devices only.See Table 22 on page42.June 1999003Merged the 80960JS/JC datasheet information into this datasheet (previously named 80960JA/JF/JD/JT 3.3V Embedded 32-Bit Microprocessor datasheet).Updated I CC values for the 80960JS/JC/JT processors. Increased TIH1 specification for the 80960JS/JC/JT processors. Updated MPBGA thermal specifications.December 1998002Corrected orientation of MPBGA package diagrams (Figure 6 on page30 and Figure 7 on page31).Added Figure 11 on page46,Figure 12 on page46,Figure 14 on page47, and Figure 15 on page48 to distinguish 80960JT 3.3-V and 5-V signal derating curves from the 80960JA/JF/JD derating curves.March 1998001This datasheet supersedes revisions to the following 80960Jx datasheets: #273109 (JT), #272971-002 (JD), and #276146-001 (JA/JF). In addition to combining the documents into one, the following content was changed: Figure 1 on page7: Added MPBGA package to diagram.Section 3.2.4, “80960Jx 196-Ball MPBGA Pinout” on page30: Added new Figures 6 and 7, Tables 10, 11 and 13.Figure 16 on page48: Added with the note that follows the figure.August 2004006To address the fact that many of the package prefix variables have changed, all package prefix variables in this document are now indicated with an "x".80960JA/JF/JD/JS/JC/JT 3.3 V Embedded 32-Bit Microprocessor1.0IntroductionThis document contains information for the 80960Jx microprocessors, including electrical characteristics and package pinout information. Detailed functional descriptions, other than parametric performance, are published in the i960® Jx Microprocessor Developer’s Manual(272483) and may be viewed online at /design/i960/Techinfo/80960JX/.Throughout this datasheet, references to ‘80960Jx’ indicate features that apply to the 3.3-V Jx processors only:Figure 1. 80960Jx Microprocessor Package Optionsi960®iM©19xxx80960JXXXXXXXXX SS132-Pin PQFPTable 1. 80960Jx 3.3-V Microprocessor FamilyProcessor Voltage Instruction Cache Data Cache Core Clock80960JA 3.3 V (5 V Tolerant) 2 Kbyte 1 Kbyte 1x 80960JF 3.3 V (5 V Tolerant) 4 Kbyte 2 Kbyte 1x 80960JD 3.3 V (5 V Tolerant) 4 Kbyte 2 Kbyte 2x 80960JS 3.3 V (5 V Tolerant)16 Kbyte 4 Kbyte 1x 80960JC 3.3 V (5 V Tolerant)16 Kbyte 4 Kbyte 2x 80960JT3.3 V (5 V Tolerant)16 Kbyte4 Kbyte3xNOTE: To address the fact that many of the package prefix variables have changed, all package prefix variables in this document are now indicated with an "x".This page intentionally left blank.80960JA/JF/JD/JS/JC/JT 3.3 V Embedded 32-Bit Microprocessor 2.080960Jx OverviewThe 80960Jx processor offers high performance to cost-sensitive 32-bit embedded applications.The 80960Jx is object code compatible with the 80960 core architecture and is capable of sustainedexecution at the rate of one instruction per clock. This processor’s features include generousinstruction cache, data cache, and data RAM. It also boasts a fast interrupt mechanism anddual-programmable timer units.The 80960Jx processor’s clock multiplication operates the processor core at two or three times thebus clock rate to improve execution performance without increasing the complexity of boarddesigns.Memory subsystems for cost-sensitive embedded applications often impose substantial wait statepenalties. The 80960Jx integrates considerable storage resources on-chip to decouple CPUexecution from the external bus.The 80960Jx rapidly allocates and de-allocates local register sets during context switches. Theprocessor must flush a register set to the stack only when it saves more than seven sets to its localregister cache.A 32-bit multiplexed burst bus provides a high-speed interface to system memory and I/O. A fullcomplement of control signals simplifies the connection of the 80960Jx to external components.The user programs physical and logical memory attributes through memory-mapped controlregisters (MMRs), an extension not found on the i960® Kx, Sx or Cx processors. Physical andlogical configuration registers enable the processor to operate with all combinations of bus widthand data object alignment. The processor supports a homogeneous byte ordering model.This processor integrates two important peripherals: a timer unit and an interrupt controller. Theseand other hardware resources are programmed through memory-mapped control registers, anextension to the familiar i960 processor architecture.The timer unit (TU) offers two independent 32-bit timers for use as real-time system clocks andgeneral-purpose system timing. These operate in either single-shot or auto-reload mode and maygenerate interrupts.The interrupt controller unit (ICU) provides a flexible, low-latency means for requesting interrupts.The ICU provides full programmability of up to 240 interrupt sources into 31 priority levels. TheICU takes advantage of a cached priority table and optional routine caching to minimize interruptlatency. Clock doubling on the 80960JD/JC processors reduces interrupt latency by 40% comparedto the 80960JA/JF, and clock tripling on the 80960JT reduces interrupt latency by 20% comparedto the 80960JD/JC. Local registers may be dedicated to high-priority interrupts to further reducelatency. Acting independently from the core, the ICU compares the priorities of posted interruptswith the current process priority, off-loading this task from the core. The ICU also supports theintegrated timer interrupts.The 80960Jx features a Halt mode designed to support applications where low power consumptionis critical. The halt instruction shuts down instruction execution, resulting in a power savings of upto 90 percent.The 80960Jx’s testability features, including ONCE (On-Circuit Emulation) mode and BoundaryScan (JTAG), provide a powerful environment for design debug and fault diagnosis.80960JA/JF/JD/JS/JC/JT 3.3 V Embedded 32-Bit MicroprocessorThe Solutions960® program features a wide variety of development tools which support the i960 processor family. Many of these tools are developed by partner companies; some are developed by Intel, such as profile-driven optimizing compilers. For more information on these products, contact your local Intel representative.2.180960 Processor CoreThe 80960Jx family is a scalar implementation of the 80960 core architecture. Intel designed this processor core as a very high performance device that is also cost-effective. Factors that contribute to the core ’s performance include:•Core operates at the bus speed with the 80960JA/JF/JS•Core operates at two or three times the bus speed with the 80960JD/JC and 80960JT,respectively•Single-clock execution of most instructions •Independent Multiply/Divide Unit•Efficient instruction pipeline minimizes pipeline break latency•Register and resource scoreboarding allow overlapped instruction execution •128-bit register bus speeds local register caching •Two-way set associative, integrated instruction cache •Direct-mapped, integrated data cache•1-Kbyte integrated data RAM delivers zero wait state program dataFigure 2. 80960Jx Block DiagramProgrammable Interrupt Controller Control Address/Instruction SequencerPhysical Region Configuration Interrupt Port1K Data RAMMemory Interface Execution Multiply UnitDivide UnitMemory-Mapped Register InterfaceData BusGlobal / Local Register FileSRC2DESTSRC1addressControleffective ConstantsGenerationUnitAddress 32-bit Address 32-bit DataBus Request Queuesand Two 32-BitTimers8-SetLocal Register CacheS R C 1S R C 2D E S TPLL, Clocks,Power MgmtBoundary Scan ControllerTAP 5CLKINS R C 1S R C 2D E S TS R C 1D E S T93232-bit buses address / data21Instruction Cache 80960JA - 2K 80960JF/JD - 4K80960JS/JC/JT - 16KDirect Mapped Data Cache 80960JA - 1K 80960JF/JD - 2K 80960JS/JC/JT -1283 Independent 32-Bit SRC1, SRC2, and DEST BusesBus Control Unit80960JA/JF/JD/JS/JC/JT 3.3 V Embedded 32-Bit Microprocessor2.2Burst BusA 32-bit high-performance Bus Controller Unit (BCU) interfaces the 80960Jx to external memoryand peripherals. The BCU fetches instructions and transfers data at the rate of up to four 32-bitwords per six clock cycles. The external address/data bus is multiplexed.Users may configure the 80960Jx’s bus controller to match an application’s fundamental memoryorganization. Physical bus width is register-programmed for up to eight regions. Byte ordering anddata caching are programmed through a group of logical memory templates and a defaults register.The BCU’s features include:•Multiplexed external bus to minimize pin count•32-, 16-, and 8-bit bus widths to simplify I/O interfaces•External ready control for address-to-data, data-to-data and data-to-next-address wait state types•Support for big or little endian byte ordering to facilitate the porting of existing program code•Unaligned bus accesses performed transparently•Three-deep load/store queue to decouple the bus from the coreUpon reset, the 80960Jx conducts an internal self-test. Then, before executing its first instruction, itperforms an external bus confidence test by performing a checksum on the first words of theinitialization boot record (IBR).2.3Timer UnitThe timer unit (TU) contains two independent 32-bit timers that are capable of counting at severalclock rates and generating interrupts. Each is programmed by use of the TU registers. Thesememory-mapped registers are addressable on 32-bit boundaries. The timers have a single-shotmode and auto-reload capabilities for continuous operation. Each timer has an independentinterrupt request to the 80960Jx’s interrupt controller. The TU may generate a fault whenunauthorized writes from user mode are detected. Clock prescaling is supported.2.4Priority Interrupt ControllerA programmable interrupt controller manages up to 240 external sources through an 8-bit externalinterrupt port. Alternatively, the interrupt inputs may be configured for individual edge- or level-triggered inputs. The interrupt unit (IU) also accepts interrupts from the two on-chip timer channelsand a single Non-Maskable Interrupt (NMI#) pin. Interrupts are serviced according to their prioritylevels relative to the current process priority.Low interrupt latency is critical to many embedded applications. As part of its highly flexibleinterrupt mechanism, the 80960Jx exploits several techniques to minimize latency:•Interrupt vectors and interrupt handler routines may be reserved on-chip.•Register frames for high-priority interrupt handlers may be cached on-chip.•The interrupt stack may be placed in cacheable memory space.•Interrupt microcode executes at two or three times the bus frequency for the 80960JD/JC and 80960JT, respectively.80960JA/JF/JD/JS/JC/JT 3.3 V Embedded 32-Bit Microprocessor2.5Instruction Set SummaryThe 80960Jx adds several new instructions to the i960 processor core architecture. The newinstructions are:•Conditional Move•Conditional Add•Conditional Subtract•Byte Swap•Halt•Cache Control•Interrupt ControlTable 2 identifies the instructions that the 80960Jx supports. Refer to the i960® Jx MicroprocessorDeveloper’s Manual (272483) for a detailed description of each instruction.2.6Faults and DebuggingThe 80960Jx employs a comprehensive fault model. The processor responds to faults by makingimplicit calls to a fault handling routine. Specific information collected for each fault allows thefault handler to diagnose exceptions and recover appropriately.The processor also has built-in debug capabilities. In software, the 80960Jx may be configured todetect as many as seven different trace event types. Alternatively, mark and fmark instructionsmay generate trace events explicitly in the instruction stream. Hardware breakpoint registers arealso available to trap on execution and data addresses.2.7Low Power OperationIntel fabricates the 80960Jx using an advanced sub-micron manufacturing process. The processor’ssub-micron topology provides the circuit density for optimal cache size and high operating speedswhile dissipating modest power. The processor also uses dynamic power management to turn offclocks to unused circuits.Users may program the 80960Jx to enter Halt mode for maximum power savings. In Halt mode,the processor core stops completely while the integrated peripherals continue to function, reducingoverall power requirements up to 90 percent. Processor execution resumes from internally orexternally generated interrupts.2.8Test FeaturesThe 80960Jx incorporates numerous features that enhance the user’s ability to test both theprocessor and the system to which it is attached. These features include ONCE (On-CircuitEmulation) mode and Boundary Scan (JTAG).80960JA/JF/JD/JS/JC/JT 3.3 V Embedded 32-Bit Microprocessor The 80960Jx provides testability features compatible with IEEE Standard Test Access Port andBoundary Scan Architecture (IEEE Std. 1149.1).One of the boundary scan instructions, HIGHZ, forces the processor to float all its output pins(ONCE mode). ONCE mode may also be initiated at reset without using the boundary scanmechanism.ONCE mode is useful for board-level testing. This feature allows a mounted 80960Jx toelectrically “remove” itself from a circuit board. This allows for system-level testing in which aremote tester, such as an in-circuit emulator, may exercise the processor system.The provided test logic does not interfere with component or circuit board behavior and ensuresthat components function correctly, connections between various components are correct, andvarious components interact correctly on the printed circuit board.The JTAG Boundary Scan feature is an attractive alternative to conventional “bed-of-nails” testing.It may examine connections that might otherwise be inaccessible to a test system.2.9Memory-Mapped Control RegistersThe 80960Jx, although compliant with the i960 processor core, has the added advantage ofmemory-mapped, internal control registers not found on the i960 Kx, Sx or Cx processors. Theseregisters give software the interface to easily read and modify internal control registers.Each of these registers is accessed as a memory-mapped, 32-bit register. Access is accomplishedthrough regular memory-format instructions. The processor ensures that these accesses do notgenerate external bus cycles.2.10Data Types and Memory Addressing ModesAs with all i960 processors, the 80960Jx instruction set supports several data types and formats:•Bit•Bit fields•Integer (8-, 16-, 32-, 64-bit)•Ordinal (8-, 16-, 32-, 64-bit unsigned integers)•Triple word (96 bits)•Quad word (128 bits)The 80960Jx provides a full set of addressing modes for C and assembly programming:•Two Absolute modes•Five Register Indirect modes•Index with displacement•IP with displacement。

ULN2003 ULN2003A中文资料

0.25 1 μs

Propagation delay time, hightPHL to low-level output 传播延迟时 See Figure 9

间,从高到低输出

0.25 1 μs

High-level output voltage after VS=50V, IO≈300mA, See

间,从高到低输出

See Figure 9

1 10 μs

High-level output voltage after VS=50V, IO≈300mA,

VOH switching 输出高电平电压

See Figure 10

VS–500

mV

图一 ULN2001A 内部电路图

图二 ULN2002A 内部电路图

2 70℃

VI=6V

Off state input current 关 VCE=50V,TA=70℃

闭状态下输入电流

3 IC=500μA,

50

Input current 输入电流 4 VI = 17 V

Clamp reverse current

VR=50V, TA=70℃

反向钳位电流

7 VR = 50 V

ULQ200xA

–20℃ to 70℃ –40℃ to 85℃

Lead temperature 1.6mm(1/16inch)from case for 10 seconds 260℃

Storage temperature range, Tstg 储存温度范围

–65℃ to 150℃

D package Package thermal impedance, θJA 封装热阻(see

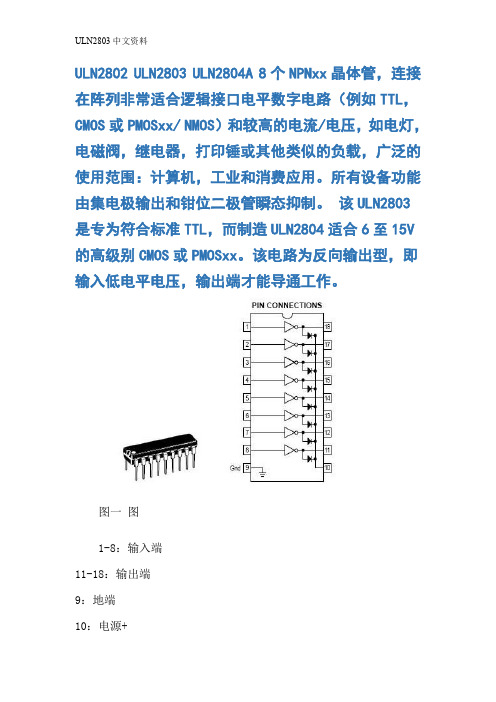

ULN2803中文资料

ULN2802 ULN2803 ULN2804A 8个NPNxx晶体管,连接在阵列非常适合逻辑接口电平数字电路(例如TTL,CMOS或PMOSxx/ NMOS)和较高的电流/电压,如电灯,电磁阀,继电器,打印锤或其他类似的负载,广泛的使用范围:计算机,工业和消费应用。

所有设备功能由集电极输出和钳位二极管瞬态抑制。

该ULN2803

是专为符合标准TTL,而制造ULN2804适合6至15V 的高级别CMOS或PMOSxx。

该电路为反向输出型,即输入低电平电压,输出端才能导通工作。

图一图

1-8:输入端

11-18:输出端

9:地端

10:电源+

图二 ULN2803内部电路图(1/8单元)图二 ULN2804内部电路图(1/8单元)

MAXIMUM RATINGS (TA = 25℃ and rating apply to any one device in the

package, unless otherwise noted.)最大额定值

订购信息

ELECTRICAL CHARACTERISTICS (TA = 25℃, unless otherwise noted)电气特性:

测试图:

图1 图2

图3 图4

图5 图6

图7

图四封装图

应用电路图:

图五步进电机驱动器

图六二相步进电机驱动器

图七 LED发光二极管驱动器电路。

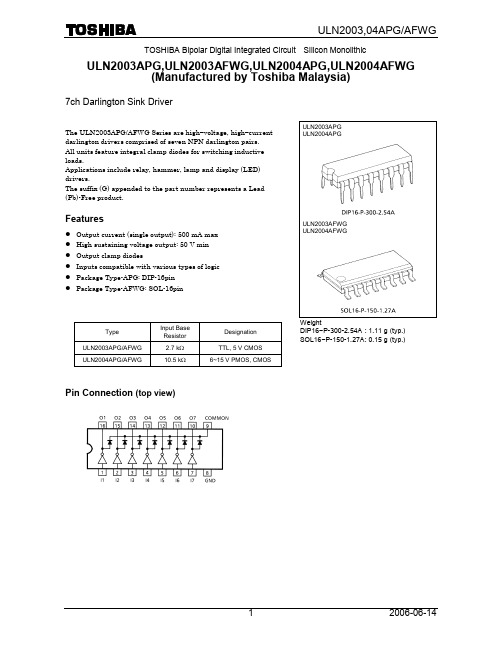

ULN2003APG中文资料

Output current

Input voltage

Clamp diode reverse voltage

Clamp diode forward current

Power dissipation

APG AFWG

Operating temperature

Storage temperature

VCE (SUS) IOUT VIN VR IF

ULN2004APG/AFWG

Note: The input and output parasitic diodes cannot be used as clamp diodes.

Absolute Maximum Ratings (Ta = 25°C)

Characteristic

Symbol

Output sustaining voltage

ULN2003APG ULN2004APG

ULN2003AFWG ULN2004AFWG

Type ULN2003APG/AFWG ULN2004APG/AFWG

Input Base Resistor

2.7 kΩ

10.5 kΩ

Designation TTL, 5 V CMOS 6~15 V PMOS, CMOS

Input Condition

Type Number ULN2003A ULN2004A

R1

VIH

0

3V

0

8V

Note 3: CL includes probe and jig capacitance.

Precautions for Using

This IC does not include built-in protection circuits for excess current or overvoltage. If this IC is subjected to excess current or overvoltage, it may be destroyed. Hence, the utmost care must be taken when systems which incorporate this IC are designed. Utmost care is necessary in the design of the output line, COMMON and GND line since IC may be destroyed due to short−circuit between outputs, air contamination fault, or fault by improper grounding.

AN13300A资料

7 8

Note) *:

Supply current Power dissipation

ICC PD

mA W

Expect for the operating ambient temperature and storage temperature , all ratings are for Ta = 25°C.

DATA SHEET

Part No. Package Code No.

AN13300A

*SOP022 - P - 0375C

SEMICONDUCTOR COMPANY MATSUSHITA ELECTRIC INDUSTRIAL CO., LTD.

Publication date: January 2005

2003 SEP

SDF00039AEB

1

AN13300A Contents

Features …………………………………………………………………………………………………………… 3 Applications ………………………………………………………………………………………………………… 3 Package ……………………………………………………………………………………………………………. 3 Block Diagram ………………………………………………………………………………………………………. 4 Pin Descriptions …………………………………………………………………………………………………… 4 Absolute Maximum Ratings ………………………………………………………………………………………. 5 Operating Supply Voltage Range ………………………………………………………………………………. 5

项目管理术语中英文对照

项目管理术语中英文对照2011-03-18 13:55:12ACWP Actual Cost of Work Performed 已执行工作实际成本AD Activity Description 工作描述ADM Arrow Diagramming Method 箭线图示解法AF Actual Finish Date 实际完成日期AOA Activity-On-Arrow 双代号网络图AON Activity-On-Node 单代号网络图AS Actual Start Date 实际开始日期BAC Budget At Completion 在完成时的预算BCWP Budgeted Cost of work Performed 已执行工作预算成本BCWS Budgeted Cost of work Scheduled 计划完成工作预算成本CCB Change Control Board 变更控制委员会CPFF Cost Plus Fixed Fee 成本加固定费用(合同)CPIF Cost Plus Incentive Fee 成本加奖励费用(合同)CPI Cost Performance Index 成本执行指数CPM Critical Path Method 关键线路法CV Cost Variance 成本偏差DD Data Date 数据日期DU Duration 持续时间,工期EAC Estimate At Completion 在完成时的估算EF Early Finish date 最早完成日期ES Early Start date 最早开始日期ETC Estimate (or Estimated) To Complete 到完成时的估算EV Earned Value 挣值法FF Free Float or Finish-to-Finish 自由时差,或完成到完成关系FFP Firm Fixed Price 完全固定总价合同FPIF Fixed Price Incentive Fee 固定价加奖励费用FS Finish-to-Start 完成到开始关系GERT Graphical Evaluation and Review Technique 图示评审技术IFB Invitation For Bid 邀标LF Late Finish Date 最晚完成日期LOE Level of Effort 投入水平LS Late Start date 最晚开始日期MPM Modern Project Management 现代项目管理OBS Organization(al) Breakdown Structure 组织分解结构PC Percent Complete 完成百分比PDM Precedence Diagramming Method 优先图示法PERT Program Evaluation and Review Technique 计划评审技术PF Planned Finish date 计划完成日期PM Project Management or Project Manager 项目管理或项目经理PMBOK Project Management Body of Knowledge 项目管理知识体系PMP Project Management Professional 项目管理专业人员PS Planned Start date 计划开始日期QA Quality Assurance 质量保障QC Quality Control 质量控制RAM Responsibility Assignment Matrix 责任分配矩阵RDU Remaining DUration 剩余工期RFP Request For Proposal 请求建议书RFQ Request For Quotation 请求报价单SF Scheduled Finish date or Start-to-Finish 计划完成日期或开始到完成关系SOW Statement of Work 工作说明SPI Schedule Performance Index 进度执行指数SS Scheduled Start date or Start-to-Start 计划开始日期或开始到开始关系SV Schedule Variance 进度偏差TC Target Completion date 目标完成日期TF Total Float or Target Finish date 总时差,或目标完成日期TS Target Start date 目标开始日期TQM Total Quality Management 全面质量管理WBS Work Breakdown Structure 工作分解结构定义这里定义的许多词,在词典的定义中具有更广泛的意义,在某些情况下具有不同的意义。

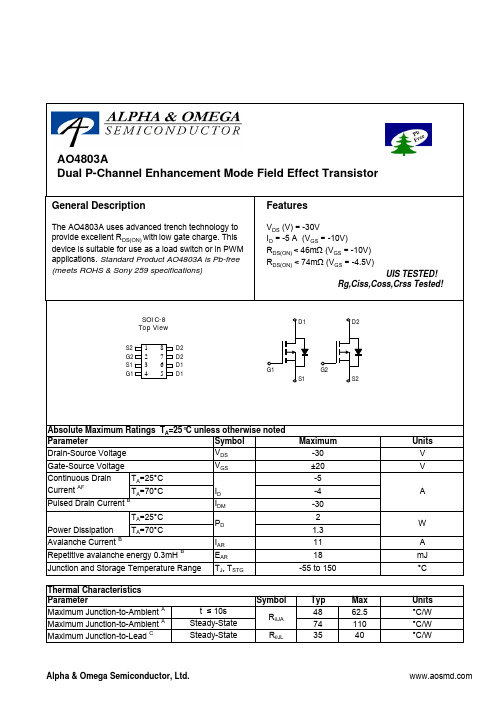

AON6403L中文资料

63 18

79 22

95 26

nC nC

Qgd

Gate Drain Charge

20

33

46

nC

tD(on)

Turn-On DelayTime

13

ns

tr

Turn-On Rise Time

VGS=-10V, VDS=-15V,

18

ns

tD(off)

Turn-Off DelayTime

RL=0.75Ω, RGEN=3Ω

EAR

TC=25°C Power Dissipation B TC=100°C

PD

TA=25°C Power Dissipation A TA=70°C

PDSM

Junction and Storage Temperature Range

TJ, TSTG

Maximum -30 ±20 -85 -67 -280 -21 -17 -72 259 83 33 2.3 1.4

0.8

0 25 50 75 100 125 150 175

Temperature (°C)

0

Figure 4: On-Resistance vs. Junction Tem18perature

(Note E)

RDS(ON) (mΩ)

9

8

ID=-20A

7

6

5

125°C

4

3

2

25°C

1

2

4

6

8

10

-VGS (Volts) Figure 5: On-Resistance vs. Gate-Source Voltage

Rev 1: January 2009

LM4863中文资料

LM4863Dual 2.2W Audio Amplifier Plus Stereo Headphone FunctionGeneral DescriptionThe LM4863is a dual bridge-connected audio power ampli-fier which,when connected to a 5V supply,will deliver 2.2W to a 4Ωload (Note 1)or 2.5W to a 3Ωload (Note 2)with less than 1.0%THD+N.In addition,the headphone input pin al-lows the amplifiers to operate in single-ended mode to drive stereo headphones.Boomer audio power amplifiers were designed specifically to provide high quality output power from a surface mount package while requiring few external components.To sim-plify audio system design,the LM4863combines dual bridge speaker amplifiers and stereo headphone amplifiers on one chip.The LM4863features an externally controlled,low-power consumption shutdown mode,a stereo headphone amplifier mode,and thermal shutdown protection.It also utilizes cir-cuitry to reduce “clicks and pops”during device turn-on.Note 1:An LM4863MTE which has been properly mounted to the circuit board will deliver 2.2W into 4Ω.The other package options for the LM4863will deliver 1.1W into 8Ω.See the Application Information section for LM4863MTE usage information.Note 2:An LM4863MTE which has been properly mounted to the circuit board and forced-air cooled will deliver 2.5W into 3Ω.Key Specificationsn P O at 1%THD+Ninto 3Ω(LM4863MTE) 2.5W(typ)into 4Ω(LM4863MTE) 2.2W(typ)into 8Ω(LM4863)1.1W(typ)n Single-ended mode -THD+N at 75mW into 32Ω0.5%(max)n Shutdown current0.7µA(typ)Featuresn Stereo headphone amplifier mode n “Click and pop”suppression circuitry n Unity-gain stablen Thermal shutdown protection circuitrynExposed-DAP TSSOP ,TSSOP ,SOIC and DIP packaging availableApplicationsn Multimedia monitorsn Portable and desktop computers n Portable televisionsTypical ApplicationBoomer ®is a registered trademark of National Semiconductor Corporation.DS012881-1*Refer to the section Proper Selection of External Components,for a detailed discussion of C B size.FIGURE 1.Typical Audio Amplifier Application CircuitOctober 1999LM4863Dual 2.2W Audio Amplifier Plus Stereo Headphone Function©1999National Semiconductor Corporation Connection DiagramsDS012881-28Top ViewOrder Number LM4863M,LM4863N See NS Package Number M16B for SO See NS Package Number N16A for DIPDS012881-2Top ViewOrder Number LM4863MTESee NS Package Number MXA20A for Exposed-DAP TSSOPL M 4863 2Absolute Maximum Ratings(Note4)If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.Supply Voltage 6.0V Storage Temperature−65˚C to+150˚C Input Voltage−0.3V to V DD+0.3V Power Dissipation(Note10)Internally limited ESD Susceptibility(Note11)2000V ESD Susceptibility(Note12)200V Junction Temperature150˚C Solder InformationSmall Outline PackageVapor Phase(60sec.)215˚C Infrared(15sec.)220˚C See AN-450“Surface Mounting and their Effects onProduct Reliablilty”for other methods of soldering surfacemount devices.Thermal ResistanceθJC(typ)—M16B20˚C/W θJA(typ)—M16B80˚C/W θJC(typ)—N16A20˚C/W θJA(typ)—N16A63˚C/W θJC(typ)—MTC2020˚C/W θJA(typ)—MTC2080˚C/W θJC(typ)—MXA20A2˚C/W θJA(typ)—MXA20A41˚C/W(Note7)θJA(typ)—MXA20A51˚C/W(Note5)θJA(typ)—MXA20A90˚C/W(Note6) Operating RatingsTemperature RangeT MIN≤T A≤T MAX−40˚C≤T A≤85˚C Supply Voltage 2.0V≤V DD≤5.5VElectrical Characteristics for Entire IC(Notes3,4)The following specifications apply for V DD=5V unless otherwise noted.Limits apply for T A=25˚C.Symbol Parameter Conditions LM4863Units(Limits)Typical Limit(Note13)(Note14)V DD Supply Voltage2V(min)5.5V(max)I DD Quiescent Power Supply Current V IN=0V,I O=0A(Note15),HP-IN=0V11.520mA(max)6mA(min)V IN=0V,I O=0A(Note15),HP-IN=4V 5.8mAI SD Shutdown Current V PIN1=V DD0.72µA(min) V IH Headphone High Input Voltage4V(min) V IL Headphone Low Input Voltage0.8V(max)Electrical Characteristics for Bridged-Mode Operation(Notes3,4)The following specifications apply for V DD=5V unless otherwise specified.Limits apply for T A=25˚C.Symbol Parameter Conditions LM4863Units(Limits)Typical Limit(Note 13)(Note 14)V OS Output Offset Voltage V IN=0V550mV(max) P O Output Power(Note9)THD=1%,f=1kHzLM4863MTE,R L=3Ω(Note7)2.5WLM4863MTE,R L=4Ω(Note8) 2.2WLM4863,R L=8Ω 1.1 1.0W(min)THD+N=10%,f=1kHzLM4863MTE,R L=3Ω(Note7) 3.2WLM4863MTE,R L=4Ω(Note8) 2.7LM4863,R L=8Ω 1.5WTHD+N=1%,f=1kHz,R L=32Ω0.34W THD+N Total Harmonic Distortion+Noise20Hz≤f≤20kHz,A VD=2LM4863MTE,R L=4Ω,P O=2W0.3LM4863,R L=8Ω,P O=1W0.3%PSRR Power Supply Rejection Ratio V DD=5V,V RIPPLE=200mV RMS,R L=8Ω,C B=1.0µF 67dBLM48633Electrical Characteristics for Bridged-Mode Operation (Notes 3,4)(Continued)The following specifications apply for V DD =5V unless otherwise specified.Limits apply for T A =25˚C.SymbolParameterConditionsLM4863Units (Limits)Typical Limit (Note 13)(Note 14)X TALK Channel Separation f =1kHz,C B =1.0µF90dB SNRSignal To Noise Ratio V DD =5V,P O =1.1W,R L =8Ω98dBElectrical Characteristics for Single-Ended Operation (Notes 3,4)The following specifications apply for V DD =5V unless otherwise specified.Limits apply for T A =25˚C.SymbolParameterConditionsLM4863Units (Limits)Typical Limit (Note 13)(Note 14)V OS Output Offset Voltage V IN =0V550mV (max)P OOutput PowerTHD =0.5%,f =1kHz,R L =32Ω8575mW (min)THD+N =1%,f =1kHz,R L =8Ω340mW THD+N =10%,f =1kHz,R L =8Ω440mW THD+N Total Harmonic Distortion+Noise A V =−1,P O =75mW,20Hz ≤f ≤20kHz,R L =32Ω0.2%PSRR Power Supply Rejection Ratio C B =1.0µF,V RIPPLE =200mV RMS ,f =1kHz52dB X TALK Channel Separation f =1kHz,C B =1.0µF60dB SNRSignal To Noise RatioV DD =5V,P O =340mW,R L =8Ω95dB Note 3:All voltages are measured with respect to the ground pins,2,7,and 15,unless otherwise specified.Note 4:Absolute Maximum Ratings indicate limits beyond which damage to the device may occur.Operating Ratings indicate conditions for which the device is func-tional,but do not guarantee specific performance limits.Electrical Characteristics state DC and AC electrical specifications under particular test conditions which guar-antee specific performance limits.This assumes that the device is within the Operating Ratings.Specifications are not guaranteed for parameters where no limit is given,however,the typical value is a good indication of device performance.Note 5:The θJA given is for an MXA20A package whose exposed-DAP is soldered to an exposed 2in 2piece of 1ounce printed circuit board copper.Note 6:The θJA given is for an MXA20A package whose exposed-DAP is not soldered to any copper.Note 7:When driving 3Ωloads from a 5V supply,the LM4863MTE must be mounted to the circuit board and forced-air cooled (450linear-feet per minute).Note 8:When driving 4Ωloads from a 5V supply,the LM4863MTE must be mounted to the circuit board.Note 9:Output power is measured at the device terminals.Note 10:The maximum power dissipation must be derated at elevated temperatures and is dictated by T JMAX ,θJA ,and the ambient temperature T A .The maximum allowable power dissipation is P DMAX =(T JMAX −T A )/θJA .For the LM4863,T JMAX =150˚C.For the θJA s for different packages,please see the Application Informa-tion section or the Absolute Maximum Ratings section.Note 11:Human body model,100pF discharged through a 1.5k Ωresistor.Note 12:Machine model,220pF–240pF discharged through all pins.Note 13:Typicals are measured at 25˚C and represent the parametric norm.Note 14:Limits are guaranteed to National’s AOQL (Average Outgoing Quality Level).Note 15:The quiescent power supply current depends on the offset voltage when a practical load is connected to the amplifier.Truth Table for Logic InputsSHUTDOWNHP-IN LM4863MODELow Low Bridged Low High Single-Ended High Low LM4863Shutdown HighHighLM4863ShutdownL M 4863 4External Components Description(Figure 1)Components Functional Description1.R i Inverting input resistance which sets the closed-loop gain in conjunction with R f .This resistor also forms a high pass filter with C i at f c =1/(2πR i C i ).2.C iInput coupling capacitor which blocks the DC voltage at the amplifier’s input terminals.Also creates ahighpass filter with R i at f c =1/(2πR i C i ).Refer to the section,Proper Selection of External Components ,for an explanation of how to determine the value of C i .3.R f Feedback resistance which sets the closed-loop gain in conjunction with R i .4.C s Supply bypass capacitor which provides power supply filtering.Refer to the Power Supply Bypassing section for information concerning proper placement and selection of the supply bypass capacitor.5.C BBypass pin capacitor which provides half-supply filtering.Refer to the section,Proper Selection of External Components ,for information concerning proper placement and selection of C B .Typical Performance Characteristics MTE Specific CharacteristicsNote 16:These curves show the thermal dissipation ability of the LM4863MTE at different ambient temperatures given these conditions:500LFPM +JEDEC board:The part is soldered to a 1S2P 20-lead exposed-DAP TSSOP test board with 500linear feet per minute of forced-air flow across it.Board information -copper dimensions:74x74mm,copper coverage:100%(buried layer)and 12%(top/bottom layers),16vias under the exposed-DAP .500LFPM +2.5in 2:The part is soldered to a 2.5in 2,1oz.copper plane with 500linear feet per minute of forced-air flow across it.2.5in 2:The part is soldered to a 2.5in 2,1oz.copper plane.Not Attached:The part is not soldered down and is not forced-air cooled.LM4863MTETHD+N vs Output PowerDS012881-97LM4863MTETHD+N vs FrequencyDS012881-99LM4863MTETHD+N vs Output PowerDS012881-96LM4863MTETHD+N vs FrequencyDS012881-98LM4863MTEPower Dissipation vs Power OutputDS012881-90LM4863MTE (Note 16)Power Derating CurveDS012881-95LM48635Non-MTE Specific CharacteristicsTHD+N vs FrequencyDS012881-3THD+N vs FrequencyDS012881-4THD+N vs FrequencyDS012881-5THD+N vs Output Power DS012881-6THD+N vs Output Power DS012881-7THD+N vs Output PowerDS012881-8THD+N vs Output Power DS012881-87THD+N vs Frequency DS012881-89THD+N vs Output PowerDS012881-88Output Power vs Load ResistanceDS012881-84Power Dissipation vs Supply VoltageDS012881-85L M 4863 6Non-MTE Specific Characteristics(Continued)Output Power vs Supply VoltageDS012881-9Output Power vs Supply VoltageDS012881-10Output Power vs Supply VoltageDS012881-11Output Power vs Load Resistance DS012881-12Output Power vs Load Resistance DS012881-13Power Dissipation vs Output PowerDS012881-14Dropout Voltage vs Supply VoltageDS012881-15Power Derating CurveDS012881-16Power Dissipation vs Output PowerDS012881-17Noise Floor DS012881-18Channel Separation DS012881-19Channel SeparationDS012881-20LM48637Non-MTE Specific Characteristics(Continued)Application InformationEXPOSED-DAP MOUNTING CONSIDERATIONSThe exposed-DAP must be connected to ground.The exposed-DAP package of the LM4863MTE requires special attention to thermal design.If thermal design issues are not properly addressed,an LM4863MTE driving 4Ωwill go into thermal shutdown.The exposed-DAP on the bottom of the LM4863MTE should be soldered down to a copper pad on the circuit board.Heat is conducted away from the exposed-DAP by a copper plane.If the copper plane is not on the top surface of the cir-cuit board,8to 10vias of 0.013inches or smaller in diameter should be used to thermally couple the exposed-DAP to the plane.For good thermal conduction,the vias must be plated-through and solder-filled.The copper plane used to conduct heat away from the exposed-DAP should be as large as pratical.If the plane is on the same side of the circuit board as the exposed-DAP ,2.5in 2is the minimum for 5V operation into 4Ω.If the heat sink plane is buried or not on the same side as the exposed-DAP ,5in 2is the minimum for 5V operation into 4Ω.If the am-bient temperature is higher than 25˚C,a larger copper plane or forced-air cooling will be required to keep the LM4863MTE junction temperature below the thermal shut-down temperature (150˚C).See the power derating curve for the LM4863MTE for derating information.The LM4863MTE requires forced-air cooling when operating into 3Ω.With the part attached to 2.5in 2of exposed copper,with a 3Ωload,and with an ambient temperature of 25˚C,450linear-feet per minute kept the part out of thermal shut-down.In higher ambient temperatures,higher airflow rates and/or larger copper areas will be required to keep the part out of thermal shutdown.See DEMOBOARD CIRCUIT LAYOUT for an example of an exposed-DAP TSSOP circuit board layout.3Ω&4ΩLAYOUT CONSIDERATIONSWith low impedance loads,the output power at the loads is heavily dependent on trace resistance from the output pins of the LM4863.Traces from the output of the LM4863MTE to the load or load connectors should be as wide as practical.Any resistance in the output traces will reduce the power de-livered to the load.For example,with a 4Ωload and 0.1Ωof trace resistance in each output,output power at the load drops from 2.2W to 2.0WOutput power is also dependent on supply regulation.To keep the supply voltage from sagging under full output power conditions,the supply traces should be as wide as practical.BRIDGE CONFIGURATION EXPLANATIONAs shown in Figure 1,the LM4863has two pairs of opera-tional amplifiers internally,allowing for a few different ampli-fier configurations.The first amplifier’s gain is externally con-figurable,while the second amplifier is internally fixed in a unity-gain,inverting configuration.The closed-loop gain of the first amplifier is set by selecting the ratio of R f to R i while the second amplifier’s gain is fixed by the two internal 20k Ωresistors.Figure 1shows that the output of amplifier one serves as the input to amplifier two which results in both am-plifiers producing signals identical in magnitude,but out of phase 180˚.Consequently,the differential gain for each channel of the IC isA VD =2*(R f /R i )By driving the load differentially through outputs +OutA and −OutA or +OutB and −OutB,an amplifier configuration com-monly referred to as “bridged mode”is established.Bridged mode operation is different from the classical single-ended amplifier configuration where one side of its load is con-nected to ground.A bridge amplifier design has a few distinct advantages over the single-ended configuration,as it provides differential drive to the load,thus doubling the output swing for a speci-fied supply voltage.Four times the output power is possible as compared to a single-ended amplifier under the same conditions.This increase in attainable output power as-sumes that the amplifier is not current limited or clipped.In order to choose an amplifier’s closed-loop gain without caus-ing excessive clipping,please refer to the Audio Power Am-plifier Design section.A bridge configuration,such as the one used in LM4863,also creates a second advantage over single-ended amplifi-ers.Since the differential outputs,+OutA,−OutA,+OutB,and −OutB,are biased at half-supply,no net DC voltage ex-ists across the load.This eliminates the need for an output coupling capacitor which is required in a single supply,single-ended amplifier configuration.If an output coupling capacitor is not used in a single-ended configuration,the half-supply bias across the load would result in both in-creased internal IC power dissipation as well as permanent loudspeaker damage.Power Supply Rejection RatioDS012881-21Open LoopFrequency ResponseDS012881-22Supply Current vs Supply Voltage 8Application Information(Continued)POWER DISSIPATIONWhether the power amplifier is bridged or single-ended, power dissipation is a major concern when designing the amplifier.Equation1states the maximum power dissipation point for a single-ended amplifier operating at a given supply voltage and driving a specified load.P DMAX=(V DD)2/(2π2R L):Single-Ended(1) However,a direct consequence of the increased power de-livered to the load by a bridge amplifier is an increase in in-ternal power dissipation.Equation2states the maximum power dissipation point for a bridge amplifier operating at the same given conditions.P DMAX=4*(V DD)2/(2π2R L):Bridge Mode(2) Since the LM4863is a dual channel power amplifier,the maximum internal power dissipation is2times that of Equa-tion1or Equation2depending on the mode of operation. Even with this substantial increase in power dissipation,the LM4863does not require heatsinking.The power dissipation from Equation2,assuming a5V power supply and an8Ωload,must not be greater than the power dissipation that re-sults from Equation3:P DMAX=(T JMAX−T A)/θJA(3) For packages M16A and MTA20,θJA=80˚C/W,and for package N16A,θJA=63˚C/W.T JMAX=150˚C for the LM4863.Depending on the ambient temperature,T A,of the system surroundings,Equation3can be used to find the maximum internal power dissipation supported by the IC packaging.If the result of Equation2is greater than that of Equation3,then either the supply voltage must be de-creased,the load impedance increased,or the ambient tem-perature reduced.For the typical application of a5V power supply,with an8Ωbridged load,the maximum ambient tem-perature possible without violating the maximum junction temperature is approximately48˚C provided that device op-eration is around the maximum power dissipation point and assuming surface mount packaging.Internal power dissipa-tion is a function of output power.If typical operation is not around the maximum power dissipation point,the ambient temperature can be increased.Refer to the Typical Perfor-mance Characteristics curves for power dissipation infor-mation for different output powers.POWER SUPPLY BYPASSINGAs with any power amplifier,proper supply bypassing is criti-cal for low noise performance and high power supply rejec-tion.The capacitor location on both the bypass and power supply pins should be as close to the device as possible.The effect of a larger half supply bypass capacitor is improved PSRR due to increased half-supply stability.Typical applica-tions employ a5V regulator with10µF and a0.1µF bypass capacitors which aid in supply filtering.This does not elimi-nate the need for bypassing the supply nodes of the LM4863.The selection of bypass capacitors,especially C B, is thus dependent upon desired PSRR requirements,click and pop performance as explained in the section,Proper Selection of External Components,system cost,and size constraints.SHUTDOWN FUNCTIONIn order to reduce power consumption while not in use,the LM4863contains a shutdown pin to externally turn off the amplifier’s bias circuitry.This shutdown feature turns the am-plifier off when a logic high is placed on the shutdown pin.The trigger point between a logic low and logic high level istypically half supply.It is best to switch between ground andthe supply V DD to provide maximum device performance.Byswitching the shutdown pin to V DD,the LM4863supply cur-rent draw will be minimized in idle mode.While the devicewill be disabled with shutdown pin voltages less than V DD,the idle current may be greater than the typical value of0.7µA.In either case,the shutdown pin should be tied to adefinite voltage to avoid unwanted state changes.In many applications,a microcontroller or microprocessoroutput is used to control the shutdown circuitry which pro-vides a quick,smooth transition into shutdown.Another solu-tion is to use a single-pole,single-throw switch in conjunctionwith an external pull-up resistor.When the switch is closed,the shutdown pin is connected to ground and enables theamplifier.If the switch is open,then the external pull-up re-sistor will disable the LM4863.This scheme guarantees thatthe shutdown pin will not float,thus preventing unwantedstate changes.HP-IN FUNCTIONThe LM4863possesses a headphone control pin that turnsoff the amplifiers which drive+OutA and+OutB so thatsingle-ended operation can occur and a bridged connectedload is muted.Quiescent current consumption is reducedwhen the IC is in this single-ended mode.Figure2shows the implementation of the LM4863’s head-phone control function using a single-supply headphone am-plifier.The voltage divider of R1and R2sets the voltage atthe HP-IN pin(pin16)to be approximately50mV when thereare no headphones plugged into the system.This logic-lowvoltage at the HP-IN pin enables the LM4863and places it inbridged mode operation.Resistor R4limits the amount ofcurrent flowing out of the HP-IN pin when the voltage at thatpin goes below ground resulting from the music coming fromthe headphone amplifier.The output coupling capacitors pro-tect the headphones by blocking the amplifier’s half supplyDC voltage.When there are no headphones plugged into the system andthe IC is in bridged mode configuration,both loads are es-sentially at a0V DC potential.Since the HP-IN threshold isset at4V,even in an ideal situation,the output swing cannotcause a false single-ended trigger.When a set of headphones are plugged into the system,thecontact pin of the headphone jack is disconnected from thesignal pin,interrupting the voltage divider set up by resistorsR1and R2.Resistor R1then pulls up the HP-IN pin,en-abling the headphone function.This disables the secondside of the amplifier thus muting the bridged speakers.Theamplifier then drives the headphones,whose impedance isin parallel with resistors R2and R3.Resistors R2and R3have negligible effect on output drive capability since thetypical impedance of headphones are32Ω.Also shown inFigure2are the electrical connections for the headphonejack and plug.A3-wire plug consists of a Tip,Ring andSleave,where the Tip and Ring are signal carrying conduc-tors and the Sleave is the common ground return.One con-trol pin contact for each headphone jack is sufficient to indi-cate to control inputs that the user has inserted a plug into ajack and that another mode of operation is desired.The LM4863can be used to drive both a pair of bridged8Ωspeakers and a pair of32Ωheadphones without using theHP-IN pin.In this case the HP-IN would not be connected tothe headphone jack but to a microprocessor or a switch.Byenabling the HP-IN pin,the8Ωspeakers can be muted.LM48639Application Information(Continued)PROPER SELECTION OF EXTERNAL COMPONENTS Proper selection of external components in applications us-ing integrated power amplifiers is critical to optimize device and system performance.While the LM4863is tolerant to avariety of external component combinations,consideration to component values must be used to maximize overall sys-tem quality.The LM4863is unity-gain stable,giving the designer maxi-mum system performance.The LM4863should be used in low gain configurations to minimize THD+N values,and maximize the signal to noise ratio.Low gain configurations require large input signals to obtain a given output power.In-put signals equal to or greater than 1Vrms are available from sources such as audio codecs.Please refer to the sec-tion,Audio Power Amplifier Design ,for a more complete explanation of proper gain selection.Besides gain,one of the major considerations is the closed-loop bandwidth of the amplifier.To a large extent,the bandwidth is dictated by the choice of external components shown in Figure 1.The input coupling capacitor,C i ,forms a first order high pass filter which limits low frequency re-sponse.This value should be chosen based on needed fre-quency response for a few distinct reasons.CLICK AND POP CIRCUITRYThe LM4863contains circuitry to minimize turn-on transients or “clicks and pops”.In this case,turn-on refers to either power supply turn-on or the device coming out of shutdown mode.When the device is turning on,the amplifiers are inter-nally configured as unity gain buffers.An internal current source ramps up the voltage of the bypass pin.Both the in-puts and outputs ideally track the voltage at the bypass pin.The device will remain in buffer mode until the bypass pin has reached its half supply voltage,1/2V DD .As soon as the bypass node is stable,the device will become fully opera-tional,where the gain is set by the external resistors.Although the bypass pin current source cannot be modified,the size of C B can be changed to alter the device turn-on time and the amount of “clicks and pops”.By increasing amount of turn-on pop can be reduced.However,the tradeoff for using a larger bypass capacitor is an increase in turn-on time for this device.There is a linear relationship be-tween the size of C B and the turn-on time.Here are some typical turn-on times for a given C B :C B T ON 0.01µF 20ms 0.1µF 200ms 0.22µF 420ms 0.47µF 840ms 1.0µF2SecIn order eliminate “clicks and pops”,all capacitors must be discharged before turn-on.Rapid on/off switching of the de-vice or the shutdown function may cause the “click and pop”circuitry to not operate fully,resulting in increased “click and pop”noise.In a single-ended configuration,the output cou-pling capacitor,C O ,is of particular concern.This capacitor discharges through the internal 20k Ωresistors.Depending on the size of C O ,the time constant can be relatively large.To reduce transients in single-ended mode,an external 1k Ω–5k Ωresistor can be placed in parallel with the internal 20k Ωresistor.The tradeoff for using this resistor is an in-crease in quiescent current.The value of C I will also reflect turn-on pops.Clearly,a cer-tain size for C I is needed to couple in low frequencies without excessive attenuation.But in many cases,the speakers used in portable systems,whether integral or external,have little ability to reproduce signals below 100Hz to 150Hz.In this case,using a large input and output capacitor may not increase system performance.In most cases,choosing a small value of C I in the range of 0.1µF to 0.33µF),along with C B equal to 1.0µF should produce a virtually clickless and popless turn-on.In cases where C I is larger than 0.33µF,it may be advantageous to increase the value of C B .Again,it should be understood that increasing the value of C B will reduce the “clicks and pops”at the expense of a longer device turn-on time.DS012881-24FIGURE 2.Headphone CircuitL M 486310Application Information(Continued)NO-LOAD DESIGN CONSIDERATIONSIf the outputs of the LM4863have a load higher than10kΩ,the LM4863may show a small oscillation at high output lev-els.To prevent this oscillation,place5kΩresistors from thepower outputs to ground.AUDIO POWER AMPLIFIER DESIGNDesign a1W/8ΩBridged Audio AmplifierGiven:Power Output:1WrmsLoad Impedance:8ΩInput Level:1VrmsInput Impedance:20kΩBandwidth:100Hz−20kHz±0.25dBA designer must first determine the minimum supply rail toobtain the specified output power.By extrapolating from theOutput Power vs Supply Voltage graphs in the Typical Per-formance Characteristics section,the supply rail can beeasily found.A second way to determine the minimum sup-ply rail is to calculate the required V opeak using Equation3and add the dropout ing this method,the mini-mum supply voltage would be(V opeak+(2*V od)),where V odis extrapolated from the Dropout Voltage vs Supply Voltagecurve in the Typical Performance Characteristics section.(4)Using the Output Power vs Supply Voltage graph for an8Ωload,the minimum supply rail is3.9V.But since5V is a stan-dard supply voltage in most applications,it is chosen for thesupply rail.Extra supply voltage creates headroom that al-lows the LM4863to reproduce peaks in excess of1W with-out producing audible distortion.At this time,the designermust make sure that the power supply choice along with theoutput impedance does not violate the conditions explainedin the Power Dissipation section.Once the power dissipation equations have been addressed,the required differential gain can be determined from Equa-tion4.(5)R f/R i=A VD/2(6)From equation4,the minimum A VD is2.83;use A VD=3Since the desired input impedance was20kΩ,and with aA VD of3,a ratio of1.5:1of R f to R i results in an allocation ofR i=20kΩand R f=30kΩ.The final design step is to ad-dress the bandwidth requirements which must be stated as apair of−3dB frequency points.Five times away from a polegives0.17dB down from passband response,which is betterthan the required±0.25dB specified.f L=100Hz/5=20Hzf H=20kHz x5=100kHzAs stated in the External Components section,R i in con-junction with C i create a highpass filter.C i≥1/(2π*20kΩ*20Hz)=0.397µF;use0.33µFThe high frequency pole is determined by the product of thedesired high frequency pole,f H,and the differential gain,AVD.With a A VD=3and f H=100kHz,the resulting GBWP=150kHz which is much smaller than the LM4863GBWP of3.5MHz.This figure displays that if a designer has a need todesign an amplifier with a higher differential gain,theLM4863can still be used without running into bandwidthproblems.DEMOBOARD CIRCUIT LAYOUTThe demoboard circuit layout is provided here as an ex-ample of a circuit using the LM4863.If an LM4863MTE isused with this layout,the exposed-DAP is soldered down tothe copper pad beneath the part.Heat is conducted awayfrom the part by the two large copper pads in the upper cor-ners of the demoboard.This demoboard provides enough heat dissipation ability toallow an LM4863MTE to output2.2W into4Ωat25˚C.DS012881-94All LayersDS012881-93Silk Screen LayerLM486311。

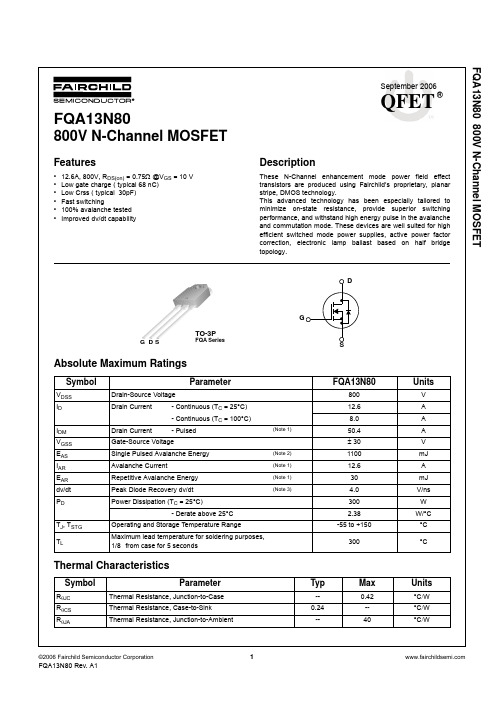

FQA13N80_06中文资料

BVDSS

Drain-Source Breakdown Voltage

VGS = 0 V, ID = 250 µA

800

∆BVDSS/ ∆TJ

Breakdown Voltage Temperature Coefficient ID = 250 µA, Referenced to 25°C

--

IDSS

30

35

40

45

ID, Drain Current [A]

Figure 5. Capacitance Characteristics

Capacitance [pF]

5000 4500 4000 3500 3000 2500 2000 1500 1000 500

0 10-1

Ciss = Cgs + Cgd (Cds = shorted) Coss = Cds + Cgd Crss = Cgd

ns

230

ns

88

nC

--

nC

--

nC

12.6

A

50.4

A

1.4

V

--

ns

--

µC

2

FQA13N80 Rev. A1

元器件交易网

FQA13N80 800V N-Channel MOSFET

Typical Performance Characteristics

(Note 4, 5)

--

Drain-Source Diode Characteristics and Maximum Ratings

IS

Maximum Continuous Drain-Source Diode Forward Current

ULN2003应用电路及中文资料

ULN2003应用电路及中文资料ULN2000、ULN2800是高压大电流达林顿晶体管阵列系列产品,具有电流增益高、工作电压高、温度范围宽、带负载能力强等特点,适应于各类要求高速大功率驱动的系统。

ULN2003A电路是美国Texas Instruments公司和Sprague公司开发的高压大电流达林顿晶体管阵列电路,文中介绍了它的电路构成、特征参数及典型应用。

功率电子电路大多要求具有大电流输出能力,以便于驱动各种类型的负载。

功率驱动电路是功率电子设备输出电路的一个重要组成部分。

在大型仪器仪表系统中,经常要用到伺服电机、步进电机、各种电磁阀、泵等驱动电压高且功率较大的器件。

ULN2000、ULN2800高压大电流达林顿晶体管阵列系列产品就属于这类可控大功率器件,由于这类器件功能强、应用范围语广。

因此,许多公司都生产高压大电流达林顿晶体管阵列产品,从而形成了各种系列产品,ULN2000、ULN2800系列就是美国Texas Instruments公司、美国Sprague公司开发的高压大电流达林顿晶体管阵列产品。

它们的系列型号分类如表1所列,生产2000、2800高压大电流达林顿晶体管阵列系列产品的公司与型号对照表如表2所列。

在上述系列产品中,ULN2000系列能够同时驱动7组高压大电流负载,ULN2800系列则能够同时驱动8组高压大电流负载。

美国Texas Instruments 公司、美国Sprague公司生产的ULN2003A由7组达林顿晶体管阵列和相应的电阻网络以及钳位二极管网络构成,具有同时驱动7组负载的能力,为单片双极型大功率高速集成电路。

以下介绍该电路的构成、性能特征、电参数以及典型应用。

2000、2800高压大电流达林顿晶体管阵列系列中的其它产品的性能特性与应用可参考ULN2003A。

ULN200A电路具有以下特点:●电流增益高(大于1000);●带负载能力强(输出电流大于500mA);●温度范围宽(-40~85℃);●工作电压高(大于50V)。

ML4803用于开关电源设计中的技巧

ML4803用于开关电源设计中的技巧漳州师范学院高级实验师 张国金ML4803是目前国际上PFC/PWM 复合控制器居领先地位的厂家美国MLCRO-LINEAR(微线性公司)的产品,它是一种体积小、效率高、节省空间的开关电源控制器,用于校正功率因数及控制调节开关电源,只需要很低的启动电流和工作电流。

功率因数校正器可使用较小容量和较便宜的高压储能电容器,降低了输电线的负荷及功率开关管MOSFET 的应力,从而使开关稳压电源完全符合IEC1000-3-2的规格。

ML4803的PFC部分使用升压型DC-DC变换器来完成这一任务,变换器输入是全波整流的交流电网电压,在经桥式整流器时没有进行滤波,所以升压变换器的输入电压两倍于电网频率,变化范围从零伏到交流输入的峰值,然后再返回零。

通过迫使升压变换器同时满足两个条件,就能确保变换器从供电网流入的电流,能匹配瞬时的电网电压。

条件之一是升压变换器的输出电压必须设置在高于电网电压的峰值,常用值是385V DC 。

另一条件是变换器应在任何瞬间的电网输入电流,必须与电网电压成比例。

ML4803的PFC升压变换拓扑控制模式是电流平均型,所以不需要斜率补偿。

1 ML4803引脚功能简介一芯片上,仅有8个引出脚,如图1所示。

引脚功能如下: PFC OUT和PWM OUT:是大电流功率驱动器,能提供A 1±峰值电流直接驱动功率MOSFET栅极。

当V CC 低于欠压锁定门限电平时,两种输出均自行维持在低电平。

I LIMIT :该脚接在原边的PWM电流检测电阻器式电流互感器,它为PWM级提供逐个脉冲电流限制,并为PWM级的电流型控制提供峰值电流型反馈通路。

电流斜坡在内部偏移1.2V,然后与光耦反馈电压比较,以设置PWM的占空比。

图1 ML4803引脚图 V EAO :该脚提供反馈通路,使PFC的输出调节在设定的数值上,它接到PFC输出电压的可调电阻器上,并由反馈补偿网络分流。

AON7403中文资料

SymbolTyp Max 30406075R θJC 4 4.5°C/WThermal Characteristics ParameterUnits Maximum Junction-to-Ambient A t ≤ 10s R θJA °C/W °C/W Maximum Junction-to-Case DSteady-StateMaximum Junction-to-Ambient A Steady-State AON7403Pin 1SymbolMin TypMaxUnits BV DSS -30V -1T J =55°C-5I GSS ±100nA V GS(th)-1.7-2.2-3V I D(ON)-80A1418T J =125°C20252636g FS 21S V SD -0.7-1V I S-3A C iss 11301400pF C oss 240pF C rss 155pF R g5.88ΩQ g 1824nC Q gs 5.5nC Q gd 3.3nC t D(on)8.7ns t r 8.5ns t D(off)18ns t f 7ns t rr 1216ns Q rr26nC 150COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS ARE NOT AUTHORIZED. AOS DOES NOT ASSUME ANY LIABILITY ARISING OUT OF SUCH APPLICATIONS OR USES OF ITS PRODUCTS. AOS RESERVES THE RIGHT TO IMPROVE PRODUCT DESIGN,FUNCTIONS AND RELIABILITY WITHOUT NOTICE.Drain-Source Breakdown Voltage On state drain currentI D =-250µA, V GS =0V V GS =-10V, V DS =-5V V DS =-30V, V GS =0VV DS =0V, V GS = ±25V Zero Gate Voltage Drain Current Gate-Body leakage current I DSS µA Body Diode Reverse Recovery Charge I F =-8A, dI/dt=500A/µsBody Diode Reverse Recovery TimeV GS =-10V, I D =-8AReverse Transfer Capacitance I F =-8A, dI/dt=500A/µsGate Threshold Voltage V DS =V GS I D =-250µA Electrical Characteristics (T J =25°C unless otherwise noted)STATIC PARAMETERS ParameterConditions V GS =-4.5V, I D =-6AI S =-1A,V GS =0V V DS =-5V, I D =-10ATurn-On Rise Time Turn-Off DelayTime V GS =-10V, V DS =-15V, R L =1.8Ω, R GEN =3ΩTurn-Off Fall TimeTurn-On DelayTime Gate Source Charge Gate resistanceV GS =0V, V DS =0V, f=1MHzTotal Gate Charge V GS =-10V, V DS =-15V, I D =-8AGate Drain Charge SWITCHING PARAMETERS Maximum Body-Diode Continuous CurrentOutput Capacitance DYNAMIC PARAMETERS R DS(ON)m ΩV GS =0V, V DS =-15V, f=1MHz Input Capacitance Static Drain-Source On-ResistanceForward TransconductanceDiode Forward Voltage A: The value of R θJA is measured with the device in a still air environment with T A =25°C. The power dissipation P DSM and current rating I DSM are based on T J(MAX)=150°C, using steady state junction-to-ambient thermal resistance.B. The power dissipation P D is based on T J(MAX)=150°C, using junction-to-case thermal resistance, and is more useful in setting the upper dissipation limit for cases where additional heatsinking is used.C: Repetitive rating, pulse width limited by junction temperature T J(MAX)=150°C.D. The R θJA is the sum of the thermal impedence from junction to case R θJC and case to ambient.E. The static characteristics in Figures 1 to 6 are obtained using <300 µs pulses, duty cycle 0.5% max.F. These tests are performed with the device mounted on 1 in 2FR-4 board with 2oz. Copper, in a still air environment with T A =25°C. The SOA curve provides a single pulse rating.G. The maximum current rating is limited by bond-wires. Rev0: Jun 2008AON7403。

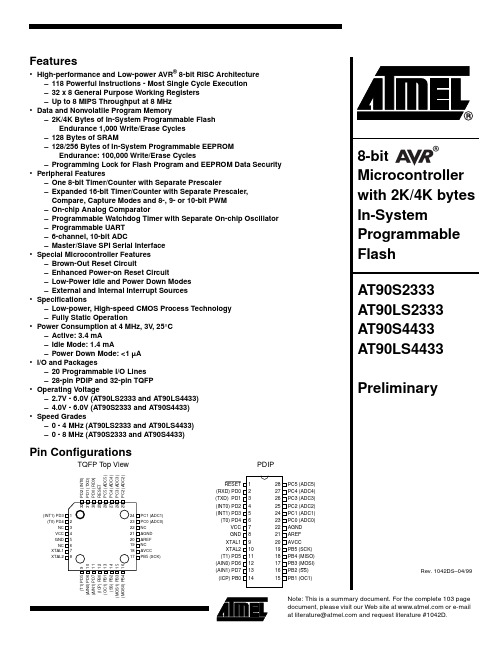

AT90LS4433中文资料