TB4005中文资料

常规生化复合定值质控品((正常正常水平))

1 SD

2.3 2.3 2.3 2.3 4.4 4.5 4.5 4.5 2.7 2.7 2.7 2.7 4.3 4.3 4.3 4.3 2.6 2.6 2.6 2.6 1.1 1.1 1.1 1.1 1.1 1.1 1.1 1.1 1.5 1.6 1.6 1.6 1.5 1.5 1.5 1.5 0.08 0.08 0.08 0.08 0.12 0.12 0.12 0.12

参考值

45.6 46.1 46.1 46.1 87.3 90.9 90.9 90.9 53.1 53.4 53.4 53.4 85.6 85.9 85.9 85.9 51.3 51.0 51.0 51.0 15.3 15.0 15.0 15.0 14.5 14.8 14.8 14.8 20.6 20.7 20.7 20.7 20.5 20.6 20.6 20.6 2.18 2.21 2.21 2.21 2.59 2.60 2.60 2.60

1

重氮盐 重氮盐法

BS-2002 BS-3003 BS-3804 BS-1201

BS-4806 BS-8007 BS-20008 BS-4005 BS-4806 BS-8007 BS-20008 BS-400

5

TB

钒酸盐氧化法

BS-2002 BS-3003 BS-3804 BS-120

1

Ca

偶氮胂 III 法

6

AST

IFCC 法

BS-2002 BS-3003 BS-3804 BS-1201

重氮盐 重氮盐法

BS-200

2

BS-3003 BS-3804 BS-1201

BS-8007 BS-20008 BS-4005 BS-4806 BS-8007 BS-20008 BS-400

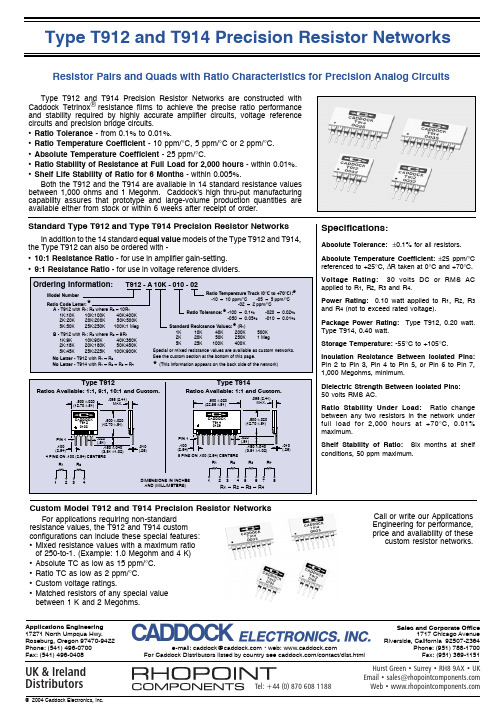

T912-B500K-001-10中文资料

® resistance films to achieve the precise ratio performance Caddock Tetrinox® MG 650 Caddock Tetrinox resistance films to achieve thesource precise ratio performance ® resistance and stability required by highly accurate amplifier circuits, reference Caddock's Micronox films are the ofvoltage Preconditioning for Power and Voltage Ratings and stability required by highly accurate amplifier circuits, reference and stability required by highly accurate amplifier circuits,voltage voltage reference MG 655 Now with Extended Resistance Range to 10,000 Megohms and Additional Models circuits a

foxboro工程师手册

I/A’s系统维护手册(工程师手册)编制:何卫兵上海福克斯波罗有限公司二零零二年元月第一章系统概述本手册为上海福克斯波罗有限公司DCS系统I/A维护手册,并作为I/A’s 培训手册的补充。

用户可以结合两本手册来进行系统操作、软件组态及系统维护。

必要时还应参考随机的原版资料及福克斯波罗公司提供的中文培训手册。

本手册针对福克斯波罗制造的I/A’S,采用Solaris 2.5.1操作系统和I/A’s 6.2.1版本应用软件。

整个系统为一个节点,在冗余的节点总线DNBI上挂有:●三台工程师站AW5101、AW5102、AW5103该站作为工程师站,内置256M内存及8GB硬盘,AW5102外挂一台喷墨打印机(电缆长度15米),AW5103配有和MIS系统通讯用的第二以太网卡。

该工作站安放在工程师站内,与I/A机柜(位于电子间)之间的通讯电缆长度为30米。

●四台操作员站WP5101、WP5103、WP5104、WP5105该站内置128M内存及8GB硬盘,并各配有一个21”的CRT。

该工作站安放在主控室内与I/A机柜(位于电子间)之间的通讯电缆长度为30米。

●一台操作员站WP5102该站作为大屏幕操作站,内置128M内存及8GB硬盘,除配有一个21”的CRT外。

还配有一台用于显示大屏幕的以太网卡。

该工作站安放在主控室内,与I/A机柜(位于电子间)之间的通讯电缆长度为30米。

●十一对容错台控制处理站CP4001、CP4002、CP4003、CP4004、CP4005、CP4006、CP4007、CP4008、CP4009、CP4010、CP4011此容错型控制处理站CP40BFT,用于实现DCS系统的数据采集及控制。

该控制处理器安放在电子间内。

现场由十八个装有现场总线组件FBM的现场机柜、十个安装DCS系统辅助装置(包括冗余的24VDC电源、交流继电器、直流继电器、SIMENSE交流接触器、以及相应的I/O端子)的继电器柜、一个DCS系统220VAC配电柜共同构成。

BT152B-400R,118;BT152B-600R,118;BT152B-800R,118;中文规格书,Datasheet资料

BT152B series ThyristorsThyristors BT152B seriesGENERAL DESCRIPTIONQUICK REFERENCE DATAGlass passivated thyristors in a plastic SYMBOL PARAMETERMAX.MAX.MAX.UNIT envelope suitable for surface mounting,intended for use in BT152B-400R 600R 800R applications requiring high V DRM ,Repetitive peak off-state 450650800V bidirectional blocking voltage V RRM voltagescapability and high thermal cycling I T(AV)Average on-state current 131313A performance.Typical applications I T(RMS)RMS on-state current202020A include motor control,industrial and I TSMNon-repetitive peak on-state 200200200Adomestic lighting,heating and static currentswitching.PINNING - SOT404PIN CONFIGURATIONSYMBOLPIN DESCRIPTION 1cathode 2anode 3gate mbanodeLIMITING VALUESLimiting values in accordance with the Absolute Maximum System (IEC 134).SYMBOL PARAMETERCONDITIONSMIN.MAX.UNIT -400R -600R -800R V DRM Repetitive peak off-state -45016501800V voltagesI T(AV)Average on-state current half sine wave; T mb ≤ 103 ˚C -13A I T(RMS)RMS on-state current all conduction angles-20A I TSMNon-repetitive peak half sine wave; T j = 25 ˚C prior to on-state currentsurge t = 10 ms -200A t = 8.3 ms -220A I 2t I 2t for fusingt = 10 ms-200A 2s dI T /dt Repetitive rate of rise of I TM = 50 A; I G = 0.2 A;-200A/μs on-state current after dI G /dt = 0.2 A/μs triggeringI GM Peak gate current -5A V GM Peak gate voltage-5V V RGM Peak reverse gate voltage -5V P GM Peak gate power -20W P G(AV)Average gate power over any 20 ms period -0.5W T stg Storage temperature -40150˚C T jOperating junction -125˚Ctemperature1 Although not recommended, off-state voltages up to 800V may be applied without damage, but the thyristor may switch to the on-state. The rate of rise of current should not exceed 15 A/μs.Thyristors BT152B seriesTHERMAL RESISTANCESSYMBOL PARAMETERCONDITIONSMIN.TYP.MAX.UNIT R th j-mb Thermal resistance-- 1.1K/W junction to mounting base R th j-aThermal resistance minimum footprint, FR4 board -55-K/Wjunction to ambientSTATIC CHARACTERISTICST j = 25 ˚C unless otherwise stated SYMBOL PARAMETER CONDITIONSMIN.TYP.MAX.UNIT I GT Gate trigger current V D = 12 V; I T = 0.1 A -332mA I L Latching current V D = 12 V; I GT = 0.1 A -2580mA I H Holding current V D = 12 V; I GT = 0.1 A -1560mA V T On-state voltage I T = 40 A- 1.4 1.75V V GT Gate trigger voltage V D = 12 V; I T = 0.1 A-0.6 1.5V V D = V DRM(max); I T = 0.1 A; T j = 125 ˚C 0.250.4-V I D , I ROff-state leakage currentV D = V DRM(max); V R = V RRM(max); T j = 125 ˚C-0.21.0mADYNAMIC CHARACTERISTICST j = 25 ˚C unless otherwise stated SYMBOL PARAMETER CONDITIONSMIN.TYP.MAX.UNIT dV D /dt Critical rate of rise of V DM = 67% V DRM(max); T j = 125 ˚C;200300-V/μs off-state voltageexponential waveform gate open circuit t gt Gate controlled turn-on V D = V DRM(max); I G = 0.1 A; dI G /dt = 5 A/μs;-2-μs timeI TM = 40 At qCircuit commutated V D = 67% V DRM(max); T j = 125 ˚C;-70-μsturn-off timeI TM = 50 A; V R = 25 V; dI TM /dt = 30 A/μs;dV D /dt = 50 V/μs; R GK = 100 ΩThyristors BT152B seriesThyristors BT152B seriesThyristors BT152B seriesMECHANICAL DATANotes1. Epoxy meets UL94 V0 at 1/8".MOUNTING INSTRUCTIONS1. Plastic meets UL94 V0 at 1/8".Legal informationDATA SHEET STATUSNotes1.Please consult the most recently issued document before initiating or completing a design.2.The product status of device(s) described in this document may have changed since this document was publishedand may differ in case of multiple devices. The latest product status information is available on the Internet at URL . DOCUMENT STATUS (1)PRODUCT STATUS (2)DEFINITIONObjective data sheet Development This document contains data from the objective specification for product development.Preliminary data sheet Qualification This document contains data from the preliminary specification. Product data sheet ProductionThis document contains the product specification.DEFINITIONSProduct specification ⎯ The information and data provided in a Product data sheet shall define the specification of the product as agreed between NXP Semiconductors and its customer, unless NXPSemiconductors and customer have explicitly agreed otherwise in writing. In no event however, shall an agreement be valid in which the NXP Semiconductors product is deemed to offer functions and qualities beyond those described in the Product data sheet.DISCLAIMERSLimited warranty and liability ⎯ Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give anyrepresentations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information.In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or reworkcharges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors’aggregate and cumulative liability towards customer for the products described herein shall be limited inaccordance with the Terms and conditions of commercial sale of NXP Semiconductors.Right to make changes ⎯ NXP Semiconductors reserves the right to make changes to informationpublished in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.Suitability for use ⎯ NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severeproperty or environmental damage. NXP Semiconductors accepts no liability for inclusion and/or use of NXP Semiconductors products in such equipment orapplications and therefore such inclusion and/or use is at the customer’s own risk.Applications ⎯ Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification. Customers are responsible for the design and operation of their applications and products using NXPSemiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer’s sole responsibility to determine whether the NXPSemiconductors product is suitable and fit for thecustomer’s applications and products planned, as well as for the planned application and use of customer’s third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.Legal informationNXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer’s applications or products, or the application or use by customer’s third party customer(s). Customer is responsible for doing all necessary testing for the customer’s applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer’s third partycustomer(s). NXP does not accept any liability in this respect.Limiting values ⎯ Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC 60134) will cause permanent damage to the device. Limiting values are stress ratings only and (proper) operation of the device at these or any other conditions above those given in the Recommended operating conditions section (if present) or theCharacteristics sections of this document is not warranted. Constant or repeated exposure to limiting values will permanently and irreversibly affect the quality and reliability of the device.Terms and conditions of commercial sale ⎯ NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at /profile/terms, unless otherwiseagreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. NXP Semiconductors hereby expressly objects to applying the customer’s general terms and conditions with regard to the purchase of NXP Semiconductors products by customer.No offer to sell or license ⎯ Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.Export control ⎯ This document as well as the item(s) described herein may be subject to export controlregulations. Export might require a prior authorization from national authorities.Quick reference data ⎯ The Quick reference data is an extract of the product data given in the Limiting values and Characteristics sections of this document, and as such is not complete, exhaustive or legally binding.Non-automotive qualified products ⎯ Unless this data sheet expressly states that this specific NXPSemiconductors product is automotive qualified, the product is not suitable for automotive use. It is neither qualified nor tested in accordance with automotive testing or application requirements. NXP Semiconductors accepts no liability for inclusion and/or use of non-automotive qualified products in automotive equipment or applications.In the event that customer uses the product for design-in and use in automotive applications to automotivespecifications and standards, customer (a) shall use the product without NXP Semiconductors’ warranty of the product for such automotive applications, use and specifications, and (b) whenever customer uses the product for automotive applications beyond NXPSemiconductors’ specifications such use shall be solely at customer’s own risk, and (c) customer fully indemnifies NXP Semiconductors for any liability, damages or failed product claims resulting from customer design and use of the product for automotive applications beyond NXP Semiconductors’ standard warranty and NXP Semiconductors’ product specifications.Contact informationFor additional information please visit: For sales offices addresses send e-mail to: salesaddresses@Customer notificationThis data sheet was changed to reflect the new company name NXP Semiconductors, including new legal definitions and disclaimers. No changes were made to the content, except for the legal definitions and disclaimers. © NXP B.V. 2011All rights are reserved. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner.The information presented in this document does not form part of any quotation or contract, is believed to be accurate and reliable and may be changed without notice. No liability will be accepted by the publisher for any consequence of its use. Publication thereof does not convey nor imply any license under patent- or other industrial or intellectual property rights.Printed in The Netherlands分销商库存信息:NXPBT152B-400R,118BT152B-600R,118BT152B-800R,118。

TPS40021中文资料

乐器价格表

350

2454

虎丘牌5211香红木3.5寸中胡(配盒)

把

2200

2455

虎丘牌香红木3.5寸铜轸中胡(配盒)

把

2200

2474

敦煌牌90A酸枝木八角筒木轸中胡(配盒)

把

1800

2475

敦煌牌90C酸枝木前方后圆木轸中胡(配盒)

把

2800

胡琴配件

售价

2700

苏式二胡腰托(用于南方二胡)

只

30

2607

2225

虎丘牌T525红木本色二胡(配高级盒)

把

2650

2228

虎丘牌5128-1五级黑檀专业二胡(配高级盒)

把

2650

2216

虎丘牌5131特选红木专业二胡(配高级盒)

把

2850

2219

虎丘牌5133特选紫檀二胡(配高级盒)

把

3800

2240

虎丘牌5135特选紫檀专业二胡(配高级盒)

把

3300

2220

把

820

2400

虎丘牌5602白木板(梆)胡(纸盒)

把

250

2401

虎丘牌5603仿红木板(梆)胡(纸盒)

把

350

2404

虎丘牌5611花梨木板(梆)胡(配盒)

把

430

2409

虎丘牌5621红木专业板(梆)胡(配盒)

把

800

2406

敦煌牌62B酸枝木铜轸板(梆)胡(配盒)

把

680

2408

敦煌牌61A花梨木木轸板(梆)胡(纸盒)

台

350

2804

永美YM6100电子琴((61键)

T912-B500K-002-02中文资料

® resistance films to achieve the precise ratio performance Caddock Tetrinox® MG 650 Caddock Tetrinox resistance films to achieve thesource precise ratio performance ® resistance and stability required by highly accurate amplifier circuits, reference Caddock's Micronox films are the ofvoltage Preconditioning for Power and Voltage Ratings and stability required by highly accurate amplifier circuits, reference and stability required by highly accurate amplifier circuits,voltage voltage reference MG 655 Now with Extended Resistance Range to 10,000 Megohms and Additional Models circuits and precision bridge circuits. the Type

AD404M324VBB-5中文资料

ASCEND Semiconductor 4Mx4 EDO Data sheetDescriptionThe device CMOS Dynamic RAM organized as 4,194,304 words x 4 bits with extended data out access mode. It is fabricated with an advanced submicron CMOS technology and designed to operate from a single 3.3V oniy power supply. Low voltage operation is more suitable to be used on battery backup, portable elec-tronic application. lt is packaged in JEDEC standard 26/24-pin plastic SOJ or TSOP(II).Features• Single 3.3V(%) only power supply • High speed t RAC acess time: 50/60ns • Low power dissipation- Active mode : 432/396 mW (Mas) - Standby mode: 0.54 mW (Mas)• Extended - data - out(EDO) page mode access • I/O level: CMOS level (Vcc = 3.3V)• 2048 refresh cycle in 32 ms(Std.) or 128 ms(S-version)• 4 refresh modesh: - RAS only refresh- CAS - before - RAS refresh - Hidden refresh - Self-refresh(S-version)10±Pin Name FunctionA0-A10Address inputs- Row address - Column address - Refresh address DQ1~DQ4Data-in / data-out RAS Row address strobe CAS Column address strobe WE Write enable OE Output enable Vcc Power (+ 3.3V)VssGroundVCC 1DQ12DQ23DQ34DQ45VCC6891011 NC 12 WE 13A0 A117 A218 A319VSS RAS CAS OE A8A7A6A5A4VSSAD404M42VSPin Description Pin Configuration21222324 2526151416 A1026/24-PIN 300mil Plastic SOJA9VCC 1DQ12DQ23DQ34DQ45VCC6891011 NC 12 WE 13A0 A117 A218 A319VSS RAS CAS OE A8A7 A6A5 A4VSSAD404M42VT212223242526151416 A1026/24-PIN 300mil Plastic TSOP (ll)A9A0-A10A0-A10A0-A10WECASNO. 2 CLOCK GENERATORCOLUMN ADDRESS BUFFERS (11)REFRESH CONTROLLERREFRESH COUNTERBUFFERS (11)ADDRESS ROW NO. 1 CLOCK GENERATORA0RASA1A2A3A4A5A6A7A8CONTROLLOGICDATA-IN BUFFERDATA-OUT BUFFEROEDQ1.DQ4.COLUMN DECODER2048SENSE AMPLIFIERSI/O GATING2048x42048x2048x4MEMORY ARRAY2048R O W D E C O D E RVcc VssBlock DiagramA9A10TRUTH TABLENotes: 1. EARLY WRITE only.FUNCTIONRASCAS WE OE ADDRESSESDQ SNotesROW COL STANDBY H X X X X High-Z READL L H L ROW COL Data-Out WRITE: (EARLY WRITE )L L L X ROW COL Data-lnREAD WRITE L L ROW COL Data-Out,Data-ln EDO-PAGE-MODE READ1st Cycle L H L ROW COL Data-Out 2nd CycleL H L n/a COL Data-Out EDO-PAGE MODE WRITE1st CycleL L X ROW COL Data-In 2nd Cycle L L Xn/a COL Data-InEDO-PAGE-MODEREAD-WRITE 1st Cycle L ROW COL Data-Out, Data-In 2nd Cycle L n/a COL Data-Out, Data-In HIDDEN REFRESHREAD L H L ROW COL Data-Out WRITEL L X ROW COL Data-In 1RAS-ONLY REFRESH L H X X ROW n/a High-Z CBR REFRESHLHXXXHigh-ZH X →H L →L H →H L →H L →H L →H L →H L →H L →L H →H L →H L →L H→L H L →→L H L→→H L→Absolute Maximum RatingsRecommended DC Operating ConditionsCapacitanceTa = 25°C, V CC = 3.3V%, f = 1MHz Note: 1. Capacitance measured with effective capacitance measuring method. 2. RAS, CAS = V IH to disable Dout.ParameterSymbol Value Unit Voltage on any pin relative to Vss V T -0.5 to + 4.6V Supply voltage relative to Vss V CC -0.5 to + 4.6V Short circuit output current I OUT 50mA Power dissipation P D 1.0WOperating temperature T OPT 0 to + 70°C Storage temperatureT STG-55 to + 125°CParameter/Condition Symbol3.3 Volt VersionUnitMinTyp MaxSupply VoltageV CC 3.0 3.33.6V Input High Voltage, all inputs V IH 2.0-V CC + 0.3V Input Low Voltage, all inputsV IL-0.3-0.8VParameterSymbol Typ Max Unit Note Input capacitance (Address)C I1 -5pF 1Input capacitance (RAS, CAS, OE, WE)C I2-7pF 1Output capacitance(Data-in, Data-out)C I/O-7pF1, 210±DC Characteristics :(T a = 0 to 70°C, V CC = + 3.3V%, V SS = 0V)Parameter Symbol Test Conditions AD404M42V Unit Notes-5-6Min Max Min MaxOperating current I CC1RAS cyclingCAS, cyclingt RC = min-120-110mA1, 2Standby Current LowpowerS-versionI CC2LVTTL interfaceRAS, CAS = V IHDout = High-Z-0.5-0.5mACMOS interfaceRAS, -0.2VDout = High-Z-0.15-0.15mAStandardpowerversionLVTTL interfaceRAS, CAS = V IHDout = High-Z-2-2mACMOS interfaceRAS,-0.2VDout = High-Z-0.5-0.5mARAS- only refresh current I CC3RAS cycling, CAS = V IHt RC = min-120-110mA1, 2 EDO page mode current I CC4t PC = min-90-80mA1, 3CAS- before- RAS refresh current I CC5t RC = minRAS, CAS cycling-120-110mA1, 2Self- refresh current (S-Version)I CC8 - 550 - 55010±CAS V CC≥CAS V CC≥t RASS100µs≥µADC Characteristics :(T a = 0 to 70°C , V CC = +3.3V %, V SS = 0V)Notes:1. I CC is specified as an average current. It depends on output loading condition and cycle rate when the device is selected. I CC max is specified at the output open condition.2. Address can be changed once or less while RAS = V IL .3. For I CC4, address can be changed once or less within one EDO page mode cycle time.Parameter Symbol Test Conditions AD404M42VUnitNotes-5-6Min MaxMin MaxInput leakage current I LI + 0.3V -55-55Output leakage current I LO + 0.3V Dout = Disable -55-55Output high Voltage V OH I OH = -2mA 2.4- 2.4-V Output low voltage V OLI OL = +2mA-0.4-0.4V10±0V Vin V CC ≤≤µA 0V Vout V CC ≤≤µAAC Characteristics(T a = 0 to + 70°C , V cc = 3.3V %, V ss = 0V) *1, *2, *3, *4Test conditions• Output load: one TTL Load and 100pF (V CC = 3.3V %)• Input timing reference levels:V IH = 2.0V, V IL = 0.8V (V CC = 3.3V %)• Output timing reference levels:V OH = 2.0V, V OL = 0.8V10±10±10±Read, Write, Read- Modify- Write and Refresh Cycles (Common Parameters)ParameterSymbol AD404M42V UnitNotes-5-6Min MaxMin MaxRandom read or write cycle time t RC 84-104-ns RAS precharge timet RP 30-40-ns CAS precharge time in normal mode t CPN 10-10-ns RAS pulse width t RAS 50100006010000ns 5CAS pulse width t CAS 8100001010000ns 6Row address setup time t ASR 0-0-ns Row address hold time t RAH 8-10-ns Column address setup time t ASC 0-0-ns 7Column address hold time t CAH 8-10-ns RAS to CAS delay timet RCD 12371445ns 8RAS to column address delay time t RAD 10251230ns 9Column address to RAS lead time t RAL 25-30-ns RAS hold time t RSH 8-10-ns CAS hold timet CSH 38-40-ns CAS to RAS precharge time t CRP 5-5-ns 10OE to Din delay time t OED 12-15-ns Transition time (rise and fall)t T 150150ns 11Refresh periodt REF -32-32ms Refresh period (S- Version)t REF -128-128ms CAS to output in Low- Z t CLZ 0-0-ns CAS delay time from Din t DZC 0-0-ns OE delay time from Dint DZO-0-nsRead CycleWrite Cycle Parameter SymbolAD404M42V Unit Notes-5-6Min Max Min MaxAccess time from RAS t RAC-50-60ns12 Access time from CAS t CAC-14-15ns13, 14 Access time from column address t AA-25-30ns14, 15 Access time from OE t OEA-12-15nsRead command setup time t RCS0-0-ns7 Read command hold time to CAS t RCH0-0-ns10, 16 Read command hold time to RAS t RRH0-0-ns16 Output buffer turn-off time t OFF012015ns17 Output buffer turn-off time from OE t OEZ012015ns17Parameter SymbolAD404M42V Unit Notes -5-6Min Max Min MaxWrite command setup time t WCS0-0-ns7, 18 Write command hold time t WCH8-10-nsWrite command pulse width t WP8-10-nsWrite command to RAS lead time t RWL13-15-nsWrite command to CAS lead time t CWL8-10-nsData-in setup time t DS0-0-ns19 Data-in hold time t DH8-10-ns19 WE to Data-in delay t WED10-10-nsRead- Modify- Write CycleRefresh Cycle Parameter SymbolAD404M42V Unit Notes-5-6Min Max Min MaxRead-modify- write cycle time t RWC108-133-nsRAS to WE delay time t RWD64-77-ns18 CAS to WE dealy time t CWD26-32-ns18 Column address to WE delay time t AWD39-47-ns18 OE hold time from WE t OEH8-10-nsParameter SymbolAD404M42VUnit Notes -5-6Min Max Min MaxCAS setup time (CBR refresh) t CSR5-5-nsCAS hold time (CBR refresh)t CHR8-10-ns10 RAS precharge to CAS hold time t RPC5-5-ns7 RAS pulse width (self refresh)t RASS100-100-RAS precharge time (self refresh)t RPS90-110-nsCAS hold time (CBR self refresh)t CHS-50--50-nsWE setup time t WSR0-0-nsWE hold time t WHR10-10-nsµsEDO Page Mode CycleEDO Page Mode Read Modify Write CycleParameterSymbol AD404M42VUnit Notes-5-6Min MaxMin MaxEDO page mode cycle timet PC 20-25-ns EDO page mode CAS precharge time t CP 10-10-ns EDO page mode RAS pulse width t RASP 5010560105ns 20Access time from CAS precharge t CPA -30-35ns 10, 14RAS hold time from CAS precharge t CPRH 30-35-ns OE high hold time from CAS high t OEHC 5-5-ns OE high pulse widtht OEP 10-10-ns Data output hold time after CAS low t COH 5-5-ns Output disable delay from WEt WHZ 310310ns WE pulse width for output disable whenCAS hight WPZ7-7-nsParameterSymbol AD404M42V Unit Notes -5-6Min MaxMin MaxEDO page mode read- modify- write cycle CAS precharge to WE delay timet CPW 45-55-ns 10EDO page mode read- modify- write cycle timet PRWC56-68-nsNotes :1. AC measurements assume t T = 2ns.2. An initial pause of 100 is required after power up, and it followed by a minimum of eightinitialization cycles (RAS - only refresh cycle or CAS - before - RAS refresh cycle). If the internal refresh counter is used, a minimun of eight CAS - before - RAS refresh cycles are required.3. In delayed write or read-modify-write cycles, OE must disable output buffer prior to applying data to the device.4. All the V CC and V SS pins shall be supplied with the same voltages.5. t RAS (min) = t RWD (min)+t RWL (min)+t T in read-modify-write cycle.6. t CAS (min) = t CWD (min)+t CWL (min)+t T in read-modify-write cycle.7. t ASC (min), t RCS (min), t WCS (min), and t RPC are determined by the falling edge of CAS .8. t RCD (max) is specified as a reference point only, and t RAC (max) can be met with the t RCD (max) limit.Otherwise, t RAC is controlled exclusively by t CAC if t RCD is greater than the specified t RCD (max) limit. 9. t RAD (max) is specified as a reference point only, and t RAC (max) can be met with the t RAD (max) limit.Otherwise, t RAC is controlled exclusively by t AA if t RAD is greater than the specified t RAD (max) limit. 10. t CRP , t CHR , t RCH , t CPA and t CPW are determined by the rising edge of CAS .11. V IH (min) and V IL (max) are reference levels for measuring timing or input signals. Therefore, transitiontime is measured between V IH and V IL .12. Assumes that t RCD tRCD (max) and t RAD t RAD (max). If t RCD or t RAD is greater than the maximum recommended value shown in this table, t RAC exceeds the value shown. 13. Assumes that (max) and (max).14. Access time is determined by the maximum of t AA , t CAC , t CPA . 15. Assumes that (max) and (max). 16. Either t RCH or t RRH must be satisfied for a read cycle.17. t OFF (max) and t OEZ (max) define the time at which the output achieves the open circuit condition (highimpedance). t OFF is determined by the later rising edge of RAS or CAS.18. t WCS , t RWD , t CWD , and t AWD are not restrictive operating parameters. They are included in the datasheet as electrical characteristics only. If (min), the cycle is an early write cycle and the data out will remain open circuit (high impedance) throughout the entire cycle. If (min),(min), (min) and (min), the cycle is a read-modify-write and the data output will contain data read from the selected cell. If neither of the above sets of conditions is satisfied, the condition of the data output (at access time) is indeterminate.19. These parameters are referenced to CAS separately in an early write cycle and to WE edge in adelayed write or a read-modify-write cycle.20. t RASP defines RAS pulse width in EDO page mode cycles.µs ≤≤t RCD t RCD ≥t RADt RAD ≤t RCD t RCD ≤t RAD t RAD ≥t WCS t WCS ≥t RWD t RWD ≥t CWDt CWD ≥t AWD t AWD ≥t CPW t CPW≥Timing Waveforms• Read Cyclet RC t RASt RPtCRPtCPNtRRHtRCHt OEZ t OFF tOEA tCACt AAtRACt CLZD OUTtRCS t ASR tRAH tASC tCAH tRAD t RALtCAStRSH tRCDt TtCSHRASCASADDRESSWEDQ1~DQ4Note : = don’t care OEt OFFRowColumn= Invalid Dout•Early Write CycletRC t RASt RPt WCHt DSt DHt WCS t RALtCAStRSH tRCDt TtCSHRASCASWEDQ1~DQ4tCRPtASRtRAH tASCtCAH ADDRESSColumnRowtCPND INtRADt RAL• Delayed Write CycletRC t RASt RPt RWL t RCSt CAStRSH tRCDt TtCSHRASCAStASR tRAH tCAHADDRESSColumnRow tASC D INDQ1~DQ4WEtCRPtCPNt DHt DSt OEHt OEDOEt DSOPENt WPt CWL• Read - Modify - Write CycletRWC t RASt RPtRWDt WPtRADtRWL tCAStCWL tRCDt TtCPNRASCASWEtCRP t ASRtRAHtASCtCAHADDRESS Column RowDQ1~DQ4t DHt DSOEtRCStAWD tCWD D INt OEDt OEHt OEZt OEA t CAC t RACt AADQ1~DQ4D OUTOPENtDZCtDZO• EDO Page Mode Read CycletRASPtCPRHt RCStCAStRSH tRCDt OEAtCSHRASCAStASRtRAHtCAHADDRESStCASWEtCRPt CPOEDQ1~DQ4OPENtOEPD OUT 1t PCt CPtCAStCPNtCRPtRADtCAHtASCt ASCtCAHt ASCt RAL Row Column 1t OEAt OEHCtRRH tRCHt RACt AAt AAt AA t CPA t CPA t OEZt OFFt OFFt CACt OEZt CAC t CACt COHD OUT NWE OE Column 2Column N Rowt RPD OUT 2• EDO Page Mode Early Write CycletRASPtRPt WCSt CAStRSH tRCDRASCAStASRtRAHtCAHADDRESStCASWEt CPDQ1~DQ4t PCt CPt CAStCPNtCRP tCAH tASCtASC tCAH tASC Row Column 1t DS WE Column 2Column Nt WCH t WCS t WCH t WCS t WCHt DH t DS t DH t DS t DHD IN 1D IN 2D IN Nt TtCSH• EDO Page Mode Read-Early-Write Cyclet RASPtCPRHt RCStCAStRSH tRCDt OEAtCSHRASCAStASRtRAHtCAHADDRESStCASWEtCRPt CPOEDQ1~DQ4OPENtWEDt PCt CPtCAStCPNtCRPtRADtRAHtASCt ASCtCAHt ASCt RAL Row Column 1tWCStRCHt RACt AAt AAt CPA t DHt WHZt CACt CACt COHWE OE Column 2Column N Rowt RPt CAL tWCHDataDoutput 2Data Input NDataDoutput 1t DStCSH• EDO Page Mode Read-Modify-Write Cyclet RASPt CPRHt RCStCASt WP RASCASt ASRtRAHtCAHADDRESSt CASWEtRCDCPDQ1~DQ4tPRWCt CPtCAStCRPtRADtCAHtASCt ASCtCAH tASC Row Column 1tRWLtRCSt OEDt DZOt CAC WE OEt RPt RAL D OUT 2D OUT ND OUT 1tTt Column NColumn 2Column 1tRWD tAWD tCWDtCWLtRCStCWDtAWD tCPW tCWL tCPW tAWD tCWDtCWL t OEDt OEDt OEHt OEHt OEHt CAC t CAC t OEA t AAt RACt OEZt OEAt AA t CPAt OEZt OEAt AA t CPAt OEZ t DSt DHt WP t DSt DHt WP t DSt DHOPENOPENOPEN D IN 1D IN ND IN 2DQ1~DQ4t DZCt DZOt DZCt DZCt DZO• Read Cycle with WE Controlled Disablet WPZt RCStCAStRCDt TtCSHRASCASt ASRtRAHtCAHADDRESSColumnRow tASCD DQ1~DQ4WEt OEZt DSt WHZOEt RCH t OEA t CACt AAt RACt CLZOUTtRADRASADDRESSt RC t CRPt ASRt RAHt Tt RPCROWt OFFCAS t RASt RPOPENt CRPDQ1~DQ4RASt CSRt WSRt RPt T t RPCt OFFCAS t RASt RPOPENt CRPDQ1~DQ4t RPCt CHRt RASt RPt RCt RCt CHRt CSRt WHRt WSRt WHRWECAS-Before-RAS Refresh CycleRASWEt RPCt OFFt CSRt CHSt WSRCASt RASS t RPSOPENDQ1~DQ4t WHRHigh lmpedance• Hidden Refresh Cyclet RPt RASRASt RCDt CRPADDRESSWEt CHRt CASt RSHt RAHt ASRt ASCt CAHt RAL ROW t RCHt OEZCASDQ1~DQ4t Tt RCSD t RASt RASt RPt RPt RC t RCt RCt RADt RRHt OFF t OFFt OEA t CACt AAt RACCOlumnOUTOE(READ)(REFRESH)(REFRESH)Ordering informationAD404M42VSA-5• AD• Ascend Memory Product • 40 • Device Type• 4M4 • Density and Organization • 2• Refresh Rate, 2: 2K Refresh • V• T: 5V, V: 3.3V• S • Package Type (S : SOJ, T : TSOP II)• A• Version• 5• Speed (5: 50 ns, 6: 60 ns)Part Number Access time PackageAD404M42VSA-5AD404M42VSA-6AD404M42VTA-5AD404M42VTA-650 ns 60 ns 50 ns 60 ns300mil 26/24-Pin Plastic SOJTSOP IIPackaging information • 300 mil, 26/24-Pin Plastic SOJ• 300 mil, 26/24-Pin TSOP II。

TDA2050-TB5-T中文资料

UNISONIC TECHNOLOGIES CO., LTDTDA2050 LINEAR INTEGRATED CIRCUIT32W HI-FI AUDIO POWER AMPLIFIERDESCRIPTIONThe UTC TDA2050 is a monolithic integrated circuit with high power capability and is designed to use as an class AB audio amplifier. It can deliver typically 50W music power into 4Ω load over 1 sec at V S =22.5V, f = 1KHz.The device is most suitable for both Hi-Fi and high class TV sets on the strength of its high supply voltage and very low harmonic and crossover distortion.FEATURES* High output power (50W Music Power IEC 268.3 Rules) * High operating supply voltage (50V) * Single or split supply operations * Very low distortion* Short circuit protection (OUT to GND) * Thermal shutdown*Pb-free plating product number: TDA2050LORDERING INFORMATIONOrdering Number Normal Lead Free Plating Package PackingTDA2050-TB5-T TDA2050L-TB5-TTO-220BTubePIN CONFIGURATION*TAB CONNECTED TO PIN 3OUTPUT +V S -V SINVERTING INPUT NON INVERTING INPUTBLOCK DIAGRAMABSOLUTE MAXIMUM RATINGSPARAMETER SYMBOL RATINGS UNITSupply Voltage V S ±25 V Input Voltage V IN V SDifferential Input Voltage V IN(DIFF) ±15℃ Output Peak Current (internally limited) I OUT 5℃ Power Dissipation T C = 75℃ P D 25 WJunction Temperature T J +125℃ Storage Temperature T STG -40 ~ +150 ℃ Note:1.Absolute maximum ratings are those values beyond which the device could be permanently damaged.Absolute maximum ratings are stress ratings only and functional device operation is not implied.2.The device is guaranteed to meet performance specification within 0℃~70℃ operating temperature range and assured by design from –40℃~85℃.THERMAL DATAPARAMETERSYMBOLRATINGS UNITThermal Resistance junction-case θJC3 ℃/WELECTRICAL CHARACTERISTICS(Refer to the Test Circuit, V S = ±18V, Ta = 25℃, f = 1 kHz, unless otherwise specified.)PARAMETER SYMBOL TEST CONDITIONS MIN TYP MAX UNITSupply Voltage V S ±4.5 ±25VQuiescent Drain Current I DV S = ±4.5VV S = ±25V18 21 50 90 mA Input Bias Current I B V S = ±22V 0.4 0.5µA Input Offset Voltage V IN(OS) V S = ±22V ±15mV Input Offset Current I IN(OS) V S = ±22V ±200nAD = 0.5%R L = 4ΩR L = 8Ω R L = 8Ω, V S = ±22V24 22 27 18 25 RMS Output PowerD = 10%R L = 4ΩR L = 8Ω R L = 8Ω, V S = ±22V 35 22 32Music Power IEC268.3 RULES P O D = 10%, T = 1s, V S = ±22.5V, R L = 4Ω50 W R L = 4Ω f = 1kHz, P O = 0.1 ~ 24W f = 100Hz ~ 10kHz, P O = 0.1 ~ 18W 0.03 0.50.5Total Harmonic Distortion THD R L = 8Ω, V S = ±22V f = 1kHz, P O = 0.1 ~ 20W f = 100Hz ~ 10kHz, P O = 0.1 ~ 15W 0.02 0.5%Slew Rate SR 5 8 V/µs Open Loop Voltage Gain G V 80 dB Closed Loop Voltage Gain G V 30 30.5 31 dB Power Bandwidth (-3dB) B W R L = 4Ω, V IN = 200mV 20 ~ 80000 HzTotal Input Noise e NCurve AB = 22Hz ~ 22kHz4 5 10 µV Input Resistance (pin 1) R IN 500 k ΩSupply Voltage Rejection SVR R S = 22K Ω, f =100Hz, V RIPPLE =0.5Vrms 45 dBP O = 28W, R L = 4Ω 65Efficiency η P O = 25W, R L = 8Ω, V S = ±22V 67%TYPICAL APPLICATION CIRCUITFOR SPLIT SUPPLY APPLICATION SUGGESTIONSR LV INFigure.1 Split Supply Typical Application CircuitThe following table demonstrates the recommended values of the external components are those shown on above circuit. Different values can be used.RECOMMENDED VALUECOMPONENT PURPOSETYPICAL LARGER SMALLERR1 Input Impedance 22k ΩIncrease of Input Impedance Decrease of InputImpedanceR2 Feedback Resistor 680Ω Decrease of Gain* Increase of Gain R3 22k Ω Increase of Gain Decrease of Gain* R4 Frequency Stability 2.2Ω Danger of Oscillations C1 Input Decoupling DC 1µF Higher Low-frequency cut-offC2Inverting Input DCDecoupling22µF Increase of Switch ON/OFF Noise Higher Low-frequency cut-off C3, C4 Supply Voltage Bypass 100nF Danger of Oscillations C5, C6 Supply Voltage Bypass 220µF Danger of Oscillations C7 Frequency Stability 0.47µF Danger of Oscillations* The gain must be higher than 24dBTYPICAL APPLICATION CIRCUIT(CONT.)FOR SINGLE SUPPLY APPLICATION SUGGESTIONSR L C21000μFFigure.2 Single Supply Typical Application CircuitThe following table demonstrates the recommended values of the external components are those shown on above circuit. Different values can be used.RECOMMENDED VALUECOMPONENT PURPOSETYPICAL LARGER SMALLER R1, R2, R3 Biasing Resistor 22kΩR4 FeedbackResistor22kΩIncrease of Gain Decrease of Gain*R5 680ΩDecrease of Gain*Increase of GainR6 FrequencyStability 2.2ΩDanger of OscillationsC1 Input Decoupling DC 2.2µF Higher Low-frequency cut-offC2 Supply VoltageRejection100µFWorse Turn-off TransientWorse Turn-on DelayC3 Supply Voltage Bypass1000µF Danger of Oscillations Worse of Turn-off TransientC4 Inverting Input DCDecoupling22µFIncrease of Switch ON/OFFHigher Low-frequency cut-offC5 Supply Voltage Bypass100nF Danger of OscillationsC6 FrequencyStability 0.47µF Danger of Oscillations C7 Output DC Decoupling1000µF Higher Low-frequency cut-off * The gain must be higher than 24dBNOTE: If the supply voltage is lower than 40V and the load is 8Ω(or more), a lower value of C2(i.e. 22µF) can be used.C7 can be larger than 1000µF only if the supply voltage does not exceed 40V.TYPICAL CHARACTERISTICS (Split Supply Test Circuit, unless otherwise specified )P O (W )V S (V)152025301050Output Power vs. Supply VoltageP O (W )V S(V)15202530105Output Power vs. Supply VoltageI D (m A )V S (V)35404550302520Quiescent Current vs. Supply Voltage P D (W )P O (W)152********Total Power Dissipation and Efficiencyvs. Output Power 55m (%)3530405060201007080P D (W )P O (W)12162024840Total Power Dissipation and Efficiencyvs. Output Power m (%)2830405060201007080354040603540。

各类2020年垂直盘PMR区分和最新叠瓦盘SMR及其性能参数表

2020年各类最新叠Brand Series Market Model SMR/PMR CapacityRPMDisk/HeadSeagate Barracuda Desktop ST500DM009PMR500 GB72001/1 Seagate Barracuda Desktop ST1000DM010PMR 1 TB72001/2 Seagate Barracuda Desktop ST2000DM005SMR 2 TB54001/2 Seagate Barracuda Desktop ST2000DM006PMR 2 TB72003/6 Seagate Barracuda Desktop ST2000DM007PMR 2 TB72002/4 Seagate Barracuda Desktop ST2000DM008SMR 2 TB72001/2 Seagate Barracuda Desktop ST3000DM007SMR 3 TB54002/3 Seagate Barracuda Desktop ST4000DM004SMR 4 TB54002/4 Seagate Barracuda Desktop ST6000DM003SMR 6 TB54003/6 Seagate Barracuda Desktop ST8000DM004SMR8 TB54004/8 Seagate Barracuda Pro Enthusiast ST2000DM009PMR 2 TB72002/4 Seagate Barracuda Pro Enthusiast ST4000DM006PMR 4 TB72004/7 Seagate Barracuda Pro Enthusiast ST6000DM004PMR 6 TB72006/12 Seagate Barracuda Pro Enthusiast ST8000DM005PMR8 TB72006/12 Seagate Barracuda Pro Enthusiast ST8000DM0004PMR8 TB72007/14 Seagate Barracuda Pro Enthusiast ST10000DM001PMR+TDMR10 TB72008/13 Seagate Barracuda Pro Enthusiast ST10000DM0004PMR10 TB72007/14 Seagate Barracuda Pro Enthusiast ST12000DM001PMR+TDMR12 TB72008/15 Seagate Barracuda Pro Enthusiast ST12000DM0007PMR12 TB72008/16 Seagate Barracuda Pro Enthusiast ST14000DM001PMR+TDMR14 TB72008/16 Seagate IronWolf NAS ST1000VN002PMR 1 TB59001/2 Seagate IronWolf NAS ST2000VN004PMR 2 TB59002/4 Seagate IronWolf NAS ST3000VN007PMR 3 TB59003/6 Seagate IronWolf NAS ST4000VN008PMR 4 TB59003/6 Seagate IronWolf NAS ST6000VN001PMR 6 TB54004/8Seagate IronWolf NAS ST6000VN0033PMR 6 TB72005/10 Seagate IronWolf NAS ST8000VN004PMR8 TB72005/10 Seagate IronWolf NAS ST8000VN0022PMR8 TB72006/12 Seagate IronWolf NAS ST10000VN0004PMR10 TB72008/16 Seagate IronWolf NAS ST10000VN0008PMR+TDMR10 TB72008/13 Seagate IronWolf NAS ST12000VN0007PMR12 TB72008/16 Seagate IronWolf NAS ST12000VN0008PMR+TDMR12 TB72008/15 Seagate IronWolf NAS ST14000VN0008PMR+TDMR14 TB72008/16 Seagate IronWolf NAS ST14000VN0008PMR+TDMR14 TB72009/18 Seagate IronWolf NAS ST16000VN001PMR+TDMR16 TB72009/18Seagate IronWolf Pro EnterpriseNASST2000NE0025PMR 2 TB72002/4Seagate IronWolf Pro EnterpriseNASST4000NE0025PMR 4 TB72004/7Seagate IronWolf Pro EnterpriseNASST4000NE001PMR 4 TB72003/6Seagate IronWolf Pro EnterpriseNASST6000NE0021PMR 6 TB72006/12Seagate IronWolf Pro EnterpriseNASST6000NE0023PMR 6 TB72006/12Seagate IronWolf Pro EnterpriseNASST6000NE000PMR 6 TB72004/8Seagate IronWolf Pro EnterpriseNASST8000NE0021PMR8 TB72006/12Seagate IronWolf Pro EnterpriseNASST8000NE001PMR8 TB72005/10Seagate IronWolf Pro EnterpriseNASST8000NE0004PMR8 TB72007/14Seagate IronWolf Pro EnterpriseNASST10000NE0004PMR10 TB72007/14Seagate IronWolf Pro EnterpriseNASST10000NE0004PMR10 TB72008/16Seagate IronWolf Pro EnterpriseNASST10000NE0008PMR+TDMR10 TB72008/13Seagate IronWolf Pro EnterpriseNASST12000NE0007PMR12 TB72008/16Seagate IronWolf Pro EnterpriseNASST12000NE0008PMR+TDMR12 TB72008/15Seagate IronWolf Pro EnterpriseNASST14000NE0008PMR+TDMR14 TB72008/16Seagate IronWolf Pro EnterpriseNASST14000NE0008PMR+TDMR14 TB72009/18Seagate IronWolf Pro EnterpriseNASST16000NE000PMR+TDMR16 TB72009/18Seagate SkyHawk Surveillance ST1000VX005PMR 1 TB59001/2 Seagate SkyHawk Surveillance ST2000VX008PMR 2 TB59002/4 Seagate SkyHawk Surveillance ST2000VX012SMR 2 TB54001/2 Seagate SkyHawk Surveillance ST2000VX015SMR 2 TB54001/2 Seagate SkyHawk Surveillance ST2000VP001SMR 2 TB54001/2 Seagate SkyHawk Surveillance ST3000VX009SMR 3 TB54002/4 Seagate SkyHawk Surveillance ST3000VX010PMR 3 TB59003/6 Seagate SkyHawk Surveillance ST4000VX005SMR 4 TB54002/4 Seagate SkyHawk Surveillance ST4000VX013SMR 4 TB54002/4 Seagate SkyHawk Surveillance ST4000VX007PMR 4 TB59003/6 Seagate SkyHawk Surveillance ST4000VP001SMR 4 TB54002/4 Seagate SkyHawk Surveillance ST6000VX001SMR 6 TB54004/8 Seagate SkyHawk Surveillance ST6000VP001SMR 6 TB54004/8 Seagate SkyHawk Surveillance ST6000VP000SMR 6 TB54004/8 Seagate SkyHawk Surveillance ST6000VX0023PMR 6 TB72005/10 Seagate SkyHawk Surveillance ST8000VX002SMR8 TB54004/8 Seagate SkyHawk Surveillance ST8000VX008SMR8 TB54004/8 Seagate SkyHawk Surveillance ST8000VP001SMR8 TB54004/8 Seagate SkyHawk Surveillance ST8000VX0022PMR8 TB72006/12 Seagate SkyHawk Surveillance ST8000VX004PMR8 TB72005/10 Seagate SkyHawk AI AI Surveillance ST6000VE000PMR 6 TB72004/8 Seagate SkyHawk AI AI Surveillance ST8000VE000PMR8 TB72005/10 Seagate SkyHawk AI AI Surveillance ST8000VE0004PMR8 TB72007/14 Seagate SkyHawk AI AI Surveillance ST10000VE0004PMR10 TB72007/14 Seagate SkyHawk AI AI Surveillance ST10000VE0008PMR+TDMR10 TB72008/13 Seagate SkyHawk AI AI Surveillance ST12000VE0008PMR+TDMR12 TB72008/15 Seagate SkyHawk AI AI Surveillance ST12000VE0008PMR+TDMR12 TB72009/16Seagate SkyHawk AI AI Surveillance ST14000VE0008PMR+TDMR14 TB72008/16 Seagate SkyHawk AI AI Surveillance ST14000VE0008PMR+TDMR14 TB72009/18 Seagate SkyHawk AI AI Surveillance ST16000VE000PMR+TDMR16 TB72009/18 Seagate Exos 5E8Enterprise ST8000AS0003SMR8 TB59804/8 Seagate Exos 7E2Enterprise ST1000NM0008PMR 1 TB72002/2 Seagate Exos 7E2Enterprise ST2000NM0008PMR 2 TB72002/4 Seagate Exos 7E8 512n Enterprise ST1000NM000A PMR 1 TB72002/2 Seagate Exos 7E8 512n Enterprise ST2000NM000A PMR 2 TB72002/3 Seagate Exos 7E8 512n Enterprise ST3000NM000A PMR 3 TB72003/6 Seagate Exos 7E8 512n Enterprise ST4000NM000A PMR 4 TB72003/6 Seagate Exos 7E8 512n Enterprise ST6000NM002A PMR 6 TB72005/10 Seagate Exos 7E8 512e Enterprise ST2000NM001A PMR 2 TB72002/3 Seagate Exos 7E8 512e Enterprise ST4000NM002A PMR 4 TB72003/6 Seagate Exos 7E8 512e Enterprise ST6000NM021A PMR 6 TB72004/8 Seagate Exos 7E8 512e Enterprise ST8000NM000A PMR8 TB72005/10 Seagate Exos 7E8 4Kn Enterprise ST2000NM002A PMR 2 TB72002/3 Seagate Exos 7E8 4Kn Enterprise ST4000NM001A PMR 4 TB72003/6 Seagate Exos 7E8 4Kn Enterprise ST6000NM022A PMR 6 TB72004/8 Seagate Exos 7E8 4Kn Enterprise ST8000NM002A PMR8 TB72005/10 Seagate Exos X10 512e Enterprise ST8000NM0206PMR8 TB72007/14 Seagate Exos X10 4Kn Enterprise ST8000NM0136PMR8 TB72007/14 Seagate Exos X10 512e Hyperscale ST8000NM0016PMR8 TB72007/14 Seagate Exos X10 4Kn Hyperscale ST8000NM0006PMR8 TB72007/14 Seagate Exos X10 512e Enterprise ST10000NM0086PMR10 TB72007/14 Seagate Exos X10 4Kn Enterprise ST10000NM0146PMR10 TB72007/14 Seagate Exos X10 512e Hyperscale ST10000NM0016PMR10 TB72007/14 Seagate Exos X10 4Kn Hyperscale ST10000NM0006PMR10 TB72007/14Seagate Exos X12Enterprise ST12000NM0007PMR12 TB72008/16 Seagate Exos X14Enterprise ST10000NM0478PMR+TDMR10 TB72008/13 Seagate Exos X14Enterprise ST12000NM0008PMR+TDMR12 TB72008/15 Seagate Exos X14Enterprise ST14000NM0008PMR+TDMR14 TB72008/16 Seagate Exos X16 512e Hyperscale ST10000NM001G PMR+TDMR10 TB72009/14 Seagate Exos X16 512e Hyperscale ST12000NM001G PMR+TDMR12 TB72009/16 Seagate Exos X16 512e Hyperscale ST14000NM001G PMR+TDMR14 TB72009/16 Seagate Exos X16 512e Hyperscale ST16000NM001G PMR+TDMR16 TB72009/18 Seagate Exos X16 4Kn Hyperscale ST10000NM009G PMR+TDMR10 TB72009/14 Seagate Exos X16 4Kn Hyperscale ST12000NM007G PMR+TDMR12 TB72009/16 Seagate Exos X16 4Kn Hyperscale ST14000NM010G PMR+TDMR14 TB72009/16 Seagate Exos X16 4Kn Hyperscale ST16000NM008G PMR+TDMR16 TB72009/18 WD Blue Desktop WD5000AZLX PMR500 GB72001/2 WD Blue Desktop WD5000AZRZ PMR500 GB54001/2 WD Blue Desktop WD10EZEX PMR 1 TB72001/2 WD Blue Desktop WD10EZRZ PMR 1 TB54001/2 WD Blue Desktop WD20EZRZ PMR 2 TB54002/4 WD Blue Desktop WD20EZAZ SMR 2 TB54001/2 WD Blue Desktop WD30EZRZ PMR 3 TB54003/6 WD Blue Desktop WD40EZRZ PMR 4 TB54003/6 WD Blue Desktop WD60EZRZ PMR 6 TB54005/6 WD Blue Desktop WD60EZAZ SMR 6 TB54003/6 WD Black Enthusiast WD5003AZEX PMR500 GB72001/1 WD Black Enthusiast WD1003FZEX PMR 1 TB72001/2 WD Black Enthusiast WD2003FZEX PMR 2 TB72003/6 WD Black Enthusiast WD4004FZWZ PMR 4 TB72005/10 WD Black Enthusiast WD4005FZBX PMR 4 TB72005/10 WD Black Enthusiast WD6002FZWZ PMR 6 TB72005/10 WD Black Enthusiast WD6003FZBZ PMR 6 TB72005/10 WD Red NAS WD10EFRX PMR 1 TB54001/2 WD Red NAS WD20EFRX PMR 2 TB54002/4 WD Red NAS WD20EFAX SMR 2 TB54001/2 WD Red NAS WD30EFRX PMR 3 TB54003/6 WD Red NAS WD30EFAX SMR 3 TB54002/3 WD Red NAS WD40EFRX PMR 4 TB54004/8 WD Red NAS WD40EFAX SMR 4 TB54002/4 WD Red NAS WD60EFRX PMR 6 TB54005/10 WD Red NAS WD60EFAX SMR 6 TB54003/6 WD Red NAS WD80EFAX PMR8 TB54005/10 WD Red NAS WD100EFAX PMR10 TB54007/14 WD Red NAS WD101EFAX PMR10 TB54006/12 WD Red NAS WD120EFAX PMR12 TB54008/16WD Red NAS WD140EFFX PMR+TDMR14 TB54009/18 WD Red Pro Enterprise WD2002FFSX PMR 2 TB72002/4 WD Red Pro Enterprise WD4003FFBX PMR 4 TB72003/6 WD Red Pro Enterprise WD6003FFBX PMR 6 TB72004/8 WD Red Pro Enterprise WD8003FFBX PMR8 TB72005/10 WD Red Pro Enterprise WD101KFBX PMR10 TB72007/14 WD Red Pro Enterprise WD102KFBX PMR10 TB72006/12 WD Red Pro Enterprise WD121KFBX PMR12 TB72008/16 WD Red Pro Enterprise WD141KFGX PMR+TDMR14 TB72009/18 WD Purple Surveillance WD10PURZ PMR 1 TB54001/2 WD Purple Surveillance WD20PURZ PMR 2 TB54002/4 WD Purple Surveillance WD30PURZ PMR 3 TB54003/6 WD Purple Surveillance WD40PURZ PMR 4 TB54004/8 WD Purple Surveillance WD60PURZ PMR 6 TB54005/10 WD Purple AI Surveillance WD82PURZ PMR8 TB72005/10 WD Purple AI Surveillance WD101PURZ PMR10 TB72007/14 WD Purple AI Surveillance WD102PURZ PMR10 TB72006/12 WD Purple AI Surveillance WD121PURZ PMR12 TB72008/16 WD Purple AI Surveillance WD140PURZ PMR+TDMR14 TB72009/18 WD Gold Enterprise WD1005FBYZ PMR 1 TB72001/2 WD Gold Enterprise WD2005FBYZ PMR 2 TB72002/4 WD Gold Enterprise WD4003FRYZ PMR 4 TB72003/6 WD Gold Enterprise WD6003FRYZ PMR 6 TB72004/8 WD Gold Enterprise WD8004FRYZ PMR8 TB72005/10 WD Gold Enterprise WD102KRYZ PMR10 TB72006/12 WD Gold Enterprise WD121KRYZ PMR12 TB72008/16 WD Gold Enterprise WD141KRYZ PMR+TDMR14 TB72009/18 Ultrastar DC HA210Enterprise HUS722T1TALE604PMR 1 TB72001/2 Ultrastar DC HA210Enterprise HUS722T2TALE604PMR 2 TB72002/4 Ultrastar DC HC310 512n Enterprise HUS726T4TALA6L4PMR 4 TB72003/6 Ultrastar DC HC310 4Kn Enterprise HUS726T4TALE6L4PMR 4 TB72003/6 Ultrastar DC HC310 512n Enterprise HUS726T6TALA6L4PMR 6 TB72004/8 Ultrastar DC HC310 4Kn Enterprise HUS726T6TALE6L4PMR 6 TB72004/8 Ultrastar DC HC320Enterprise HUS728T8TALE6L4PMR8 TB72005/10 Ultrastar DC HC330Enterprise WUS721010ALE6L4PMR10 TB72006/12 Ultrastar DC HC510 512e Enterprise HUH721008ALE604PMR8 TB72007/14 Ultrastar DC HC510 4Kn Enterprise HUH721008ALN604PMR8 TB72007/14 Ultrastar DC HC510 512e Enterprise HUH721010ALE604PMR10 TB72007/14 Ultrastar DC HC510 4Kn Enterprise HUH721010ALN604PMR10 TB72007/14 Ultrastar DC HC520 512e Enterprise HUH721212ALE604PMR12 TB72008/16 Ultrastar DC HC520 4Kn Enterprise HUH721212ALN604PMR12 TB72008/16 Ultrastar DC HC530Enterprise WUH721414ALE604PMR+TDMR14 TB72009/18 Ultrastar DC HC620 512e Enterprise HSH721414ALE6M4SMR14 TB72008/16 Ultrastar DC HC620 4Kn Enterprise HSH721414ALN6M SMR14 TB72008/16 Ultrastar DC HC620 512e Enterprise HSH721415ALE6M4SMR15 TB72008/16 Ultrastar DC HC620 4Kn Enterprise HSH721415ALN6M SMR15 TB72008/16 Toshiba P300Desktop HDWD105PMR500 GB72001/1 Toshiba P300Desktop HDWD110PMR 1 TB72001/2 Toshiba P300Desktop HDWD120PMR 2 TB72002/4 Toshiba P300Desktop HDWD130PMR 3 TB72003/6 Toshiba P300Desktop HDWD240SMR 4 TB54002/4 Toshiba P300Desktop HDWD260SMR 6 TB54003/6Toshiba X300Enthusiast HDWE140PMR 4 TB72004/8 Toshiba X300Enthusiast HDWE150PMR 5 TB72005/10 Toshiba X300Enthusiast HDWE160PMR 6 TB72006/12 Toshiba X300Enthusiast HDWE180PMR8 TB72006/12 Toshiba X300Enthusiast HDWR11A PMR10 TB72007/14 Toshiba X300Enthusiast HDWR21C PMR12 TB72008/16 Toshiba X300Enthusiast HDWR21E PMR14 TB72009/18 Toshiba N300NAS HDWQ140PMR 4 TB72004/8 Toshiba N300NAS HDWN160PMR 6 TB72006/12 Toshiba N300NAS HDWN180PMR8 TB72006/12 Toshiba N300NAS HDWG11A PMR10 TB72007/14 Toshiba N300NAS HDWG21C PMR12 TB72008/16 Toshiba N300NAS HDWG21E PMR14 TB72009/18 Toshiba V300Video Stream HDWU105PMR500 GB57001/1 Toshiba V300Video Stream HDWU110PMR 1 TB57001/2 Toshiba V300Video Stream HDWU120PMR 2 TB57002/4 Toshiba V300Video Stream HDWU130PMR 3 TB59403/6 Toshiba S300Surveillance HDWT140PMR 4 TB54004/8 Toshiba S300Surveillance HDWT240SMR 4 TB54002/4 Toshiba S300Surveillance HDWT150PMR 5 TB54005/10 Toshiba S300Surveillance HDWT360PMR 6 TB72006/12 Toshiba S300Surveillance HDWT380PMR8 TB72006/12 Toshiba S300Surveillance HDWT31A PMR10 TB72007/14 Toshiba MG04ACA-N Enterprise MG04ACA100N PMR 1 TB72001/2 Toshiba MG04ACA-N Enterprise MG04ACA200N PMR 2 TB72002/4 Toshiba MG04ACA-N Enterprise MG04ACA400N PMR 4 TB72004/8 Toshiba MG04ACA 4Kn Enterprise MG04ACA200A PMR 2 TB72002/4 Toshiba MG04ACA 512e Enterprise MG04ACA200E PMR 2 TB72002/4 Toshiba MG04ACA 4Kn Enterprise MG04ACA300A PMR 3 TB72003/6 Toshiba MG04ACA 512e Enterprise MG04ACA300E PMR 3 TB72003/6 Toshiba MG04ACA 4Kn Enterprise MG04ACA400A PMR 4 TB72004/8 Toshiba MG04ACA 512e Enterprise MG04ACA400E PMR 4 TB72004/8 Toshiba MG04ACA 4Kn Enterprise MG04ACA500A PMR 5 TB72005/10 Toshiba MG04ACA 512e Enterprise MG04ACA500E PMR 5 TB72005/10 Toshiba MG04ACA 4Kn Enterprise MG04ACA50DA PMR 5 TB72006/10 Toshiba MG04ACA 512e Enterprise MG04ACA50DE PMR 5 TB72006/10 Toshiba MG04ACA 4Kn Enterprise MG04ACA600A PMR 6 TB72006/12 Toshiba MG04ACA 512e Enterprise MG04ACA600E PMR 6 TB72006/12 Toshiba MG05ACA 4Kn Enterprise MG05ACA800A PMR8 TB72006/12 Toshiba MG05ACA 512e Enterprise MG05ACA800E PMR8 TB72006/12 Toshiba MG06ACA 4Kn Enterprise MG06ACA600A PMR 6 TB72005/10 Toshiba MG06ACA 512e Enterprise MG06ACA600E PMR 6 TB72005/10 Toshiba MG06ACA 4Kn Enterprise MG06ACA800A PMR8 TB72006/12 Toshiba MG06ACA 512e Enterprise MG06ACA800E PMR8 TB72006/12 Toshiba MG06ACA 4Kn Enterprise MG06ACA10TA PMR10 TB72007/14 Toshiba MG06ACA 512e Enterprise MG06ACA10TE PMR10 TB72007/14 Toshiba MG07ACA 4Kn Enterprise MG07ACA12TA PMR12 TB72008/16 Toshiba MG07ACA 512n Enterprise MG07ACA12TE PMR12 TB72008/16 Toshiba MG07ACA 4Kn Enterprise MG07ACA14TA PMR14 TB72009/18 Toshiba MG07ACA 512n Enterprise MG07ACA14TE PMR14 TB72009/18 Toshiba MG08ACA 4Kn Enterprise MG08ACA16TA PMR+TDMR16 TB72009/18 Toshiba MG08ACA 512n Enterprise MG08ACA16TE PMR+TDMR16 TB72009/18最新叠瓦盘SMR和垂直盘PMR区分及其性能参数表Cap./Disk Density Cache Speed Helium/AirL/ULCycleWorkloadPower-OnPower Op1 TB625 Gb/in²32 MB210 MB/s Air30000055 TB/Y 2400hrs/Y5.3 W1 TB625 Gb/in²64 MB210 MB/s Air30000055 TB/Y 2400hrs/Y5.3 W2 TB1203 Gb/in²256MB190 MB/s Air30000055 TB/Y2400hrs/Y3.7 W1 TB625 Gb/in²64 MB210 MB/s Air30000055 TB/Y 2400hrs/Y8 W1 TB625 Gb/in²64 MB210 MB/s Air30000055 TB/Y 2400hrs/Y8 W2 TB1188 Gb/in²256MB220 MB/s Air30000055 TB/Y2400hrs/Y5.1 W2 TB1203 Gb/in²256MB185 MB/s Air30000055 TB/Y2400hrs/Y3.7 W2 TB1203 Gb/in²256MB190 MB/s Air30000055 TB/Y2400hrs/Y3.7 W2 TB1203 Gb/in²256MB185 MB/s Air30000055 TB/Y2400hrs/Y5.3 W2 TB1203 Gb/in²256MB190 MB/s Air30000055 TB/Y2400hrs/Y5.3 W1 TB651 Gb/in²128MB195 MB/s Air600000180 TB/Y8760hrs/Y6.7 W1.33 TB732 Gb/in²128MB214 MB/s Air600000180 TB/Y8760hrs/Y6.7 W1.33 TB732 Gb/in²256MB214 MB/s Air600000180 TB/Y8760hrs/Y9.0 W1.33 TB732 Gb/in²256MB214 MB/s Air600000180 TB/Y8760hrs/Y9.0 W1.43 TB867 Gb/in²256MB220 MB/s Helium300000300 TB/Y8760hrs/Y6.8 W1.75 TB1058 Gb/in²256MB250 MB/s Helium300000300 TB/Y8760hrs/Y6.9 W1.43 TB867 Gb/in²256MB220 MB/s Helium300000300 TB/Y8760hrs/Y7.8 W1.75 TB1058 Gb/in²256MB250 MB/s Helium300000300 TB/Y8760hrs/Y6.9 W1.5 TB923 Gb/in²256MB250 MB/s Helium300000300 TB/Y8760hrs/Y7.8 W1.75 TB1058 Gb/in²256MB250 MB/s Helium300000300 TB/Y8760hrs/Y6.9 W1 TB625 Gb/in²64 MB180 MB/s Air600000180 TB/Y 8760hrs/Y3.76 W1 TB613 Gb/in²64 MB180 MB/s Air600000180 TB/Y 8760hrs/Y4.3 W1 TB613 Gb/in²64 MB180 MB/s Air600000180 TB/Y 8760hrs/Y4.8 W1.33 TB810 Gb/in²64 MB180 MB/s Air600000180 TB/Y 8760hrs/Y4.8 W1.5 TB900 Gb/in²256MB190 MB/s Air600000180 TB/Y8760hrs/Y5.3 W1.33 TB732 Gb/in²256MB210 MB/s Air600000180 TB/Y8760hrs/Y8.1 W1.6 TB930 Gb/in²256MB210 MB/s Air600000180 TB/Y8760hrs/Y8.8 W1.33 TB732 Gb/in²256MB210 MB/s Air600000180 TB/Y8760hrs/Y8.8 W1.5 TB923 Gb/in²256MB210 MB/s Helium600000180 TB/Y8760hrs/Y7.8 W1.75 TB1058 Gb/in²256MB220 MB/s Helium600000180 TB/Y8760hrs/Y7.8 W1.5 TB923 Gb/in²256MB210 MB/s Helium600000180 TB/Y8760hrs/Y7.8 W1.75 TB1058 Gb/in²256MB220 MB/s Helium600000180 TB/Y8760hrs/Y7.8 W1.75 TB1058 Gb/in²256MB220 MB/s Helium600000180 TB/Y8760hrs/Y7.8 W1.78 TB1028 Gb/in²256MB210 MB/s Helium600000180 TB/Y8760hrs/Y7.3 W1.78 TB1028 Gb/in²256MB210 MB/s Helium600000180 TB/Y8760hrs/Y7.3 W1 TB651 Gb/in²128MB195 MB/s Air600000300 TB/Y8760hrs/Y6.5 W1.33 TB732 Gb/in²128MB214 MB/s Air600000300 TB/Y8760hrs/Y8.5 W1.6 TB930 Gb/in²256MB214 MB/s Air600000300 TB/Y8760hrs/Y9.0 W1.33 TB732 Gb/in²256MB214 MB/s Air600000300 TB/Y8760hrs/Y8.1 W1.33 TB732 Gb/in²256MB214 MB/s Air600000300 TB/Y8760hrs/Y8.1 W1.6 TB930 Gb/in²256MB214 MB/s Air600000300 TB/Y8760hrs/Y8.1 W1.33 TB732 Gb/in²256MB214 MB/s Air600000300 TB/Y8760hrs/Y8.78 W1.6 TB930 Gb/in²256MB214 MB/s Air600000300 TB/Y8760hrs/Y9.2 W1.43 TB867 Gb/in²256MB214 MB/s Helium600000300 TB/Y8760hrs/Y7.4 W1.43 TB867 Gb/in²256MB214 MB/s Helium600000300 TB/Y8760hrs/Y7.8 W1.5 TB923 Gb/in²256MB250 MB/s Helium600000300 TB/Y8760hrs/Y7.8 W1.75 TB1058 Gb/in²256MB250 MB/s Helium600000300 TB/Y8760hrs/Y7.8 W1.5 TB923 Gb/in²256MB250 MB/s Helium600000300 TB/Y8760hrs/Y7.8 W1.75 TB1058 Gb/in²256MB250 MB/s Helium600000300 TB/Y8760hrs/Y7.6 W1.75 TB1058 Gb/in²256MB250 MB/s Helium600000300 TB/Y8760hrs/Y7.9 W1.78 TB1028 Gb/in²256MB255 MB/s Helium600000300 TB/Y8760hrs/Y7.6 W1.78 TB1028 Gb/in²256MB255 MB/s Helium600000300 TB/Y8760hrs/Y7.6 W1 TB625 Gb/in²64 MB180 MB/s Air300000180 TB/Y 8760hrs/Y5.6 W1 TB613 Gb/in²64 MB180 MB/s Air300000180 TB/Y 8760hrs/Y5.6 W2 TB1186 Gb/in²256MB180 MB/s Air600000180 TB/Y8760hrs/Y2 TB1186 Gb/in²256MB180 MB/s Air600000180 TB/Y8760hrs/Y2 TB1186 Gb/in²256MB180 MB/s Air600000180 TB/Y8760hrs/Y1.5 TB900 Gb/in²256MB180 MB/s Air600000180 TB/Y8760hrs/Y3.5 W1 TB613 Gb/in²64 MB180 MB/s Air300000180 TB/Y 8760hrs/Y5.6 W2 TB1186 Gb/in²256MB180 MB/s Air600000180 TB/Y8760hrs/Y2 TB1186 Gb/in²256MB180 MB/s Air600000180 TB/Y8760hrs/Y1.33 TB810 Gb/in²64 MB180 MB/s Air300000180 TB/Y 8760hrs/Y5.5 W2 TB1186 Gb/in²256MB180 MB/s Air600000180 TB/Y8760hrs/Y1.5 TB900 Gb/in²256MB180 MB/s Air600000180 TB/Y8760hrs/Y5.0 W1.5 TB900 Gb/in²256MB180 MB/s Air600000180 TB/Y8760hrs/Y5.0 W1.5 TB900 Gb/in²256MB180 MB/s Air600000180 TB/Y8760hrs/Y5.0 W1.33 TB732 Gb/in²256MB210 MB/s Air300000180 TB/Y8760hrs/Y9.0 W2 TB1186 Gb/in²256MB180 MB/s Air600000180 TB/Y8760hrs/Y2 TB1186 Gb/in²256MB180 MB/s Air600000180 TB/Y8760hrs/Y2 TB1186 Gb/in²256MB180 MB/s Air600000180 TB/Y8760hrs/Y1.33 TB732 Gb/in²256MB210 MB/s Air300000180 TB/Y8760hrs/Y9.0 W1.6 TB930 Gb/in²256MB210 MB/s Air300000180 TB/Y8760hrs/Y8.73 W1.6 TB930 Gb/in²256MB235 MB/s Air300000550 TB/Y8760hrs/Y1.6 TB930 Gb/in²256MB235 MB/s Air300000550 TB/Y8760hrs/Y8.73 W1.43 TB867 Gb/in²256MB235 MB/s Helium300000550 TB/Y8760hrs/Y7.2 W1.43 TB867 Gb/in²256MB235 MB/s Helium300000550 TB/Y8760hrs/Y7.2 W1.75 TB1058 Gb/in²256MB250 MB/s Helium300000550 TB/Y8760hrs/Y6.9 W1.75 TB1058 Gb/in²256MB250 MB/s Helium300000550 TB/Y8760hrs/Y6.9 W1.78 TB1028 Gb/in²256MB250 MB/s Helium300000550 TB/Y8760hrs/Y6.71 W1.75 TB1058 Gb/in²256MB250 MB/s Helium300000550 TB/Y8760hrs/Y6.9 W1.78 TB1028 Gb/in²256MB250 MB/s Helium300000550 TB/Y8760hrs/Y6.71 W1.78 TB1028 Gb/in²256MB250 MB/s Helium300000550 TB/Y8760hrs/Y6.71 W2 TB1203 Gb/in²256MB190 MB/s Air300000180 TB/Y8760hrs/Y5.3 W1 TB651 Gb/in²128MB185 MB/s Air600000550 TB/Y8760hrs/Y7.0 W1 TB651 Gb/in²128MB185 MB/s Air600000550 TB/Y8760hrs/Y7.0 W1.33 TB732 Gb/in²256MB225 MB/s Air600000550 TB/Y8760hrs/Y9.91 W1.33 TB732 Gb/in²256MB225 MB/s Air600000550 TB/Y8760hrs/Y9.91 W1.33 TB732 Gb/in²256MB225 MB/s Air600000550 TB/Y8760hrs/Y10.77 W1.33 TB732 Gb/in²256MB225 MB/s Air600000550 TB/Y8760hrs/Y10.77 W1.33 TB732 Gb/in²256MB225 MB/s Air600000550 TB/Y8760hrs/Y12.91 W1.6 TB930 Gb/in²256MB226 MB/s Air600000550 TB/Y8760hrs/Y9.83 W1.6 TB930 Gb/in²256MB226 MB/s Air600000550 TB/Y8760hrs/Y10.89 W1.6 TB930 Gb/in²256MB226 MB/s Air600000550 TB/Y8760hrs/Y11.67 W1.6 TB930 Gb/in²256MB249 MB/s Air600000550 TB/Y8760hrs/Y12.81 W1.6 TB930 Gb/in²256MB226 MB/s Air600000550 TB/Y8760hrs/Y9.83 W1.6 TB930 Gb/in²256MB226 MB/s Air600000550 TB/Y8760hrs/Y10.89 W1.6 TB930 Gb/in²256MB226 MB/s Air600000550 TB/Y8760hrs/Y11.67 W1.6 TB930 Gb/in²256MB249 MB/s Air600000550 TB/Y8760hrs/Y12.81 W1.43 TB867 Gb/in²256MB249 MB/s Helium600000550 TB/Y8760hrs/Y8.4 W1.43 TB867 Gb/in²256MB249 MB/s Helium600000550 TB/Y8760hrs/Y8.4 W1.43 TB867 Gb/in²256MB249 MB/s Helium600000550 TB/Y8760hrs/Y8.4 W1.43 TB867 Gb/in²256MB249 MB/s Helium600000550 TB/Y8760hrs/Y8.4 W1.43 TB867 Gb/in²256MB249 MB/s Helium600000550 TB/Y8760hrs/Y8.4 W1.43 TB867 Gb/in²256MB249 MB/s Helium600000550 TB/Y8760hrs/Y8.4 W1.43 TB867 Gb/in²256MB249 MB/s Helium600000550 TB/Y8760hrs/Y8.4 W1.43 TB867 Gb/in²256MB249 MB/s Helium600000550 TB/Y8760hrs/Y8.4 W1.5 TB923 Gb/in²256MB261 MB/s Helium600000550 TB/Y8760hrs/Y7.8 W1.75 TB1058 Gb/in²256MB245 MB/s Helium600000550 TB/Y8760hrs/Y9.8 W1.75 TB1058 Gb/in²256MB245 MB/s Helium600000550 TB/Y8760hrs/Y10 W1.75 TB1058 Gb/in²256MB261 MB/s Helium600000550 TB/Y8760hrs/Y10 W1.78 TB1028 Gb/in²256MB245 MB/s Helium600000550 TB/Y8760hrs/Y9.5 W1.78 TB1028 Gb/in²256MB245 MB/s Helium600000550 TB/Y8760hrs/Y9.5 W1.78 TB1028 Gb/in²256MB245 MB/s Helium600000550 TB/Y8760hrs/Y10 W1.78 TB1028 Gb/in²256MB261 MB/s Helium600000550 TB/Y8760hrs/Y10 W1.78 TB1028 Gb/in²256MB245 MB/s Helium600000550 TB/Y8760hrs/Y9.5 W1.78 TB1028 Gb/in²256MB245 MB/s Helium600000550 TB/Y8760hrs/Y9.5 W1.78 TB1028 Gb/in²256MB245 MB/s Helium600000550 TB/Y8760hrs/Y10 W1.78 TB1028 Gb/in²256MB261 MB/s Helium600000550 TB/Y8760hrs/Y10 W500 GB32 MB150 MB/s Air300000 3.3 W 500 GB64 MB150 MB/s Air300000 3.3 W 1 TB64 MB150 MB/s Air300000 6.8 W 1 TB64 MB150 MB/s Air300000 3.3 W1 TB64 MB147 MB/s Air300000 4.1 W2 TB256180 MB/s Air300000 4.1 W 1 TB64 MB147 MB/s Air300000 4.1 W 1.33 TB64 MB175 MB/s Air300000 4.5 W1.2 TB64 MB170 MB/s Air300000 5.3 W2 TB256180 MB/s Air300000 4.8 W 1 TB64 MB150 MB/s Air300000 6.8 W 1 TB64 MB150 MB/s Air300000 6.8 W 667 GB64 MB164 MB/s Air3000009.5 W 800 GB128128 MB/s Air3000009.1 W 800 GB256256 MB/s Air3000009.1 W 1.2 TB128227 MB/s Air3000009.1 W 1.2 TB256227 MB/s Air3000009.1 W 1 TB64 MB144 MB/s Air600000180 TB/Y 3.3 W1 TB64 MB147 MB/s Air600000180 TB/Y 4.1 W2 TB256180 MB/s Air600000180 TB/Y 4.1 W1 TB64 MB147 MB/s Air600000180 TB/Y 4.1 W2 TB256180 MB/s Air600000180 TB/Y 4.8 W1 TB64 MB150 MB/s Air600000180 TB/Y 4.5 W2 TB256180 MB/s Air600000180 TB/Y 4.8 W1.2 TB64 MB175 MB/s Air600000180 TB/Y 5.3 W2 TB256180 MB/s Air600000180 TB/Y 4.8 W 1.6 TB256198 MB/s Air600000180 TB/Y8.8 W 1.43 TB256210 MB/s Helium600000180 TB/Y 5.7 W 1.67 TB256215 MB/s Air600000180 TB/Y8.4 W 1.5 TB256196 MB/s Helium600000180 TB/Y 6.3 W1.56 TB512210 MB/s Helium600000180 TB/Y 6.5 W 1 TB64 MB164 MB/s Air600000300 TB/Y7.8 W 1.33 TB256217 MB/s Air600000300 TB/Y7.2 W 1.5 TB256238 MB/s Air600000300 TB/Y7.2 W 1.6 TB256235 MB/s Air600000300 TB/Y8.8 W 1.43 TB256240 MB/s Helium600000300 TB/Y 5.7 W 1.67 TB256265 MB/s Air600000300 TB/Y8.4 W 1.5 TB256240 MB/s Helium600000300 TB/Y 6.0 W 1.56 TB512255 MB/s Helium600000300 TB/Y 6.2 W 1 TB64 MB110 MB/s Air300000180 TB/Y 3.3 W 1 TB64 MB145 MB/s Air300000180 TB/Y 4.4 W 1 TB64 MB145 MB/s Air300000180 TB/Y 4.4 W 1 TB64 MB150 MB/s Air300000180 TB/Y 5.1 W 1.2 TB64 MB175 MB/s Air300000180 TB/Y 5.3 W 1.6 TB256245 MB/s Air300000360 TB/Y8.6 W 1.43 TB256245 MB/s Helium300000360 TB/Y 6.3 W 1.67 TB256265 MB/s Air300000360 TB/Y9.0 W 1.5 TB256245 MB/s Helium300000360 TB/Y 6.6 W 1.56 TB512255 MB/s Helium300000360 TB/Y 6.0 W 1 TB128184 MB/s Air6000008.1 W 1 TB128200 MB/s Air6000008.1 W 1.33 TB256255 MB/s Air6000007.0 W 1.5 TB256255 MB/s Air6000007.0 W 1.6 TB256255 MB/s Air6000008.8 W 1.67 TB256262 MB/s Air6000009.2 W 1.5 TB256255 MB/s Helium600000 6.9 W 1.56 TB512267 MB/s Helium600000 6.0 W 1 TB128184 MB/s Air6000008.1 W 1 TB128200 MB/s Air6000008.1 W 1.33 TB256255 MB/s Air6000007.0 W 1.33 TB256255 MB/s Air6000007.0 W 1.5 TB256255 MB/s Air6000007.0 W 1.5 TB256255 MB/s Air6000007.0 W 1.6 TB256255 MB/s Air6000008.8 W 1.67 TB256262 MB/s Air6000009.2 W 1.13 TB256249 MB/s Helium600000 6.8 W 1.13 TB256249 MB/s Helium600000 6.8 W 1.43 TB256249 MB/s Helium600000 6.8 W 1.43 TB256249 MB/s Helium600000 6.8 W 1.5 TB256255 MB/s Helium600000 6.9 W 1.5 TB256255 MB/s Helium600000 6.9 W 1.56 TB512267 MB/s Helium600000 6.0 W 1.75 TB512255 MB/s Helium600000 6.4 W 1.75 TB512255 MB/s Helium600000 6.4 W 1.86 TB512255 MB/s Helium600000 6.4 W 1.86 TB512255 MB/s Helium600000 6.4 W 1 TB64 MB Air300000 6.4 W 1 TB64 MB Air300000 6.4 W 1 TB64 MB Air300000 5.8 W 1 TB64 MB Air300000 6.4 W2 TB 128MB185 MB/s Air60000055 TB/Y2400hrs/Y4.11 W2 TB 128MB185 MB/s Air60000055 TB/Y2400hrs/Y4.46 W。

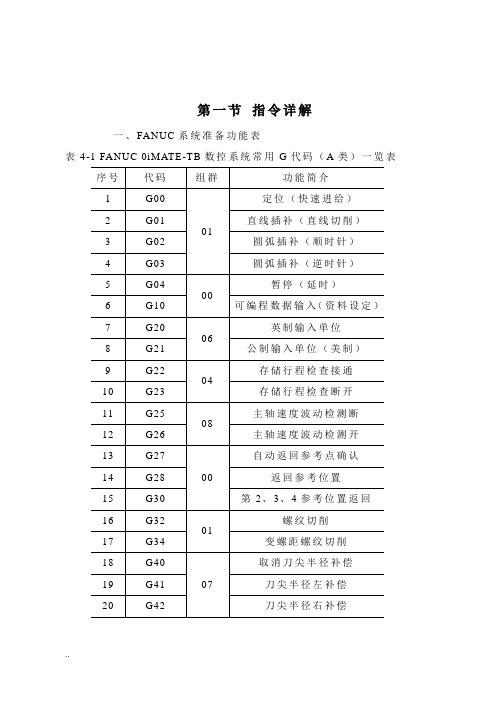

发那科数控系统的编程与操作

第一节指令详解一、FANUC系统准备功能表表4-1 FANUC 0iMATE-TB数控系统常用G代码(A类)一览表..数控车床编程与操作- 102 - 102二、FANUC 0i MATE-TB编程规则1.小数点编程:在本系统中输入的任何坐标字(包括X、Z、I、K、U、W、R等)在其数值后须加小数点。

即X100须记作X100.0。

否则系统认为所坐标字数值为100×0.001mm=0.1mm。

2.绝对方式与增量方式:FANUC-0T数控车系统中用U或W表示增量方式。

在程序段出现U即表示X方向的增量值,出现W即表示Z方向的增量值。

同时允许绝对方式与增量混合编程。

注意与使用G90和G91表示增量的系统有所区别。

3.进给功能:系统默认进给方式为转进给。

4.程序名的指定:本系统程序名采用字母O后跟四位数字的格式。

子程序文件名遵循同样的命名规则。

通常在程序开始指定文件名。

程序结束须加M30或M02指令。

5.G指令简写模式:系统支持G指令简写模式。

三、常用准备功能代码详解1.直线插补(G01)格式:G01 X(U)Z(W) F说明:基本用法与其它各系统相同。

此处主要介绍G01指令用于回转体类工件的台阶和端面交接处实现自动倒圆角或直角。

⑴圆角自动过渡:——格式:G01 X R FG01 Z R F——说明:X轴向Z轴过渡倒圆(凸弧)R值为负,Z轴向X轴过渡倒圆(凹弧)R值为正。

..数控车床编程与操作- 104 - 104——程序示例:O4001 N10 T0101N20 G0 X0 Z1. S500 M03 N30 G1Z0 F0.2 N40 G1 X20. R-5. N50 G1 Z-25. R3. N60 G1 X30.5 N70 G28 X120. Z100. N80 M30⑵ 直角自动过渡:——程式:G01 X C FG01 Z C F——说明:倒直角用指令C ,其符号设置规则同倒圆角。

——程序示例: O4002N10 T0101N20 G0 X0 Z1. S500 M03 N30 G1Z0 F0.2 N40 G1 X20. C-2. N50 G1 Z-25. R3. N60 G1 X30.5 N70 G28 X120. Z100. N80 M30提示:自动过渡倒直角和圆角指令在用于精加工编程时会带来方便,但要注意符号的正负要准确,否则会发生不正确的动作。

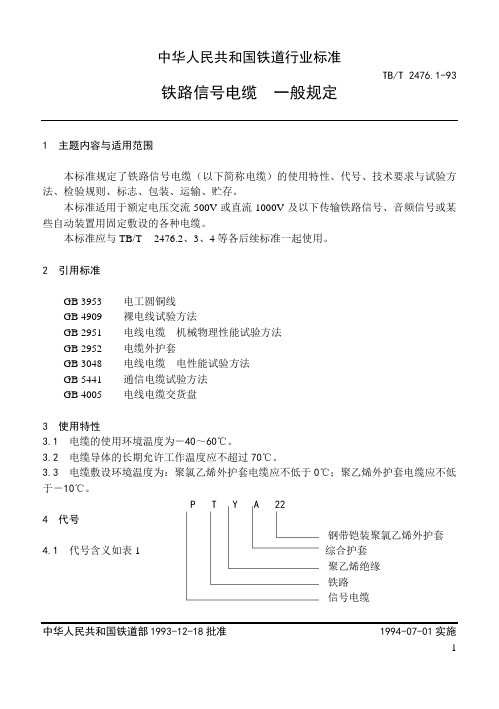

铁路信号电缆 一般规定

序号

项目

单位

指标

试验方法

换算公式

1

1.1

1.2

直流电阻20℃时

每根导体直流电阻不大于

工作线对导体电阻不平衡不大于

Ω

23.5

0.02

GB3048.4

L/1000

2

绝缘电阻不小于

MΩ

3000

GB3048.6

1000/L

3

3.1

3.2

3.3

电容

对线组工作电容不大于

星形四线组工作电容不大于

任一绝缘线芯对连接到地

PTY22 37×1.0 TB/T 2476.2

5技术要求与试验方法

5.1导体

导体应采用符合GB 3953规定的软圆铜线,其标称直径为1.0mm,试验方法应符合GB4909.2规定。

5.2绝缘

5.2.1绝缘应采用聚乙烯塑料,并制成红、绿、白、蓝四种颜色。

5.2.2绝缘标称厚度为0.6mm,允许偏差为±0.1mm,试验方法应符合GB2951.2规定。

四芯电缆ea1、ea2Байду номын сангаас标为最大值

PF

330

1300

GB5441.3

L/500

6

6.1

6.2

绝缘耐压50Hz 2min

线芯间

线芯对其余线芯接地

V

1000

1800

GB3048.8

注:工作线对导体电阻不平衡,即星形四线组工作线对的两根导体的电阻之差与其电阻之和的比值。

5.7电缆的机械物理特性除应符合本标准第5.5条的规定外,应进行低温卷绕或低温拉伸试验,试验温度为-15±2℃,其技术要求和试验方法应符合GB2951.12或GB2951.13的规定。

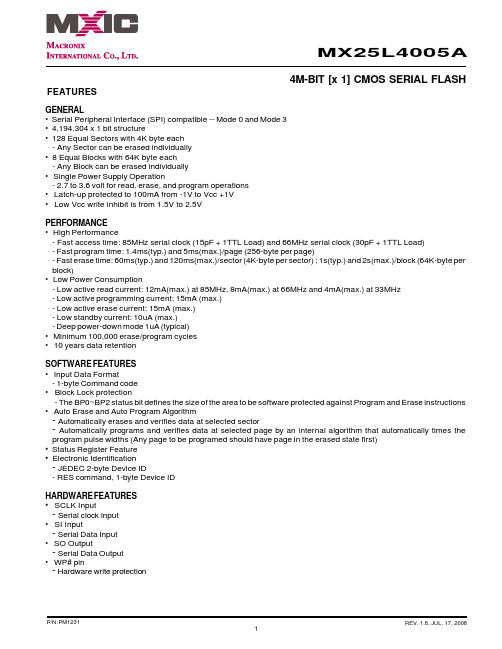

MX25L4005AM2C-12G中文资料