一个框架时序逻辑程序设计语言

VHDL5套试卷标准答案

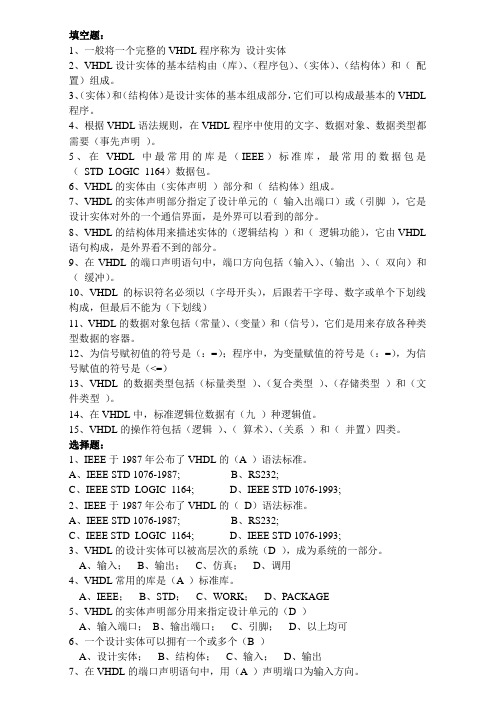

填空题:1、一般将一个完整的VHDL程序称为设计实体2、VHDL设计实体的基本结构由(库)、(程序包)、(实体)、(结构体)和(配置)组成。

3、(实体)和(结构体)是设计实体的基本组成部分,它们可以构成最基本的VHDL 程序。

4、根据VHDL语法规则,在VHDL程序中使用的文字、数据对象、数据类型都需要(事先声明)。

5、在VHDL中最常用的库是(IEEE)标准库,最常用的数据包是(STD_LOGIC_1164)数据包。

6、VHDL的实体由(实体声明)部分和(结构体)组成。

7、VHDL的实体声明部分指定了设计单元的(输入出端口)或(引脚),它是设计实体对外的一个通信界面,是外界可以看到的部分。

8、VHDL的结构体用来描述实体的(逻辑结构)和(逻辑功能),它由VHDL 语句构成,是外界看不到的部分。

9、在VHDL的端口声明语句中,端口方向包括(输入)、(输出)、(双向)和(缓冲)。

10、VHDL的标识符名必须以(字母开头),后跟若干字母、数字或单个下划线构成,但最后不能为(下划线)11、VHDL的数据对象包括(常量)、(变量)和(信号),它们是用来存放各种类型数据的容器。

12、为信号赋初值的符号是(:=);程序中,为变量赋值的符号是(:=),为信号赋值的符号是(<=)13、VHDL的数据类型包括(标量类型)、(复合类型)、(存储类型)和(文件类型)。

14、在VHDL中,标准逻辑位数据有(九)种逻辑值。

15、VHDL的操作符包括(逻辑)、(算术)、(关系)和(并置)四类。

选择题:1、IEEE于1987年公布了VHDL的(A)语法标准。

A、IEEE STD 1076-1987;B、RS232;C、IEEE STD_LOGIC_1164;D、IEEE STD 1076-1993;2、IEEE于1987年公布了VHDL的(D)语法标准。

A、IEEE STD 1076-1987;B、RS232;C、IEEE STD_LOGIC_1164;D、IEEE STD 1076-1993;3、VHDL的设计实体可以被高层次的系统(D ),成为系统的一部分。

第1节 组合逻辑和时序逻辑

第1节组合逻辑和时序逻辑来源:/book/09-03/8331410070307.html通过前面各章的学习可知,Verilog HDL语言分为面向综合和面向仿真两大类语句,且可综合语句远少于仿真语句,读者可能会有可综合设计相对简单的感觉。

然而事实刚好与此相反,这是因为:首先,可综合设计是用来构建硬件平台的,因此对设计的指标要求很高,包括资源、频率和功耗,这都需要通过代码来体现;其次,在实际开发中要利用基本Verilog HDL语句完成种类繁多的硬件开发,给设计人员带来了很大的挑战。

所有的仿真语句只是为了可综合设计的验证而存在。

为了让读者深入地理解可综合设计、灵活运用已学内容,本章将可综合设计中的基本知识点和难点提取出来,融入Verilog HDL语法以及开发工具等诸多方面,以深入浅出的方式向读者说明设计中的难点本质。

8.1 组合逻辑和时序逻辑数字电路根据逻辑功能的不同特点,可以分成两大类,一类叫组合逻辑电路(简称组合电路),另一类叫做时序逻辑电路(简称时序电路)。

掌握组合逻辑和时序逻辑的区分手段与实现方法是数字系统设计的基本要求。

8.1.1 组合逻辑设计1.组合逻辑概念组合逻辑是Verilog HDL设计中的一个重要组成部分。

从电路本质上讲,组合逻辑电路的特点是输出信号只是当前时刻输入信号的函数,与其他时刻的输入状态无关。

无存储电路,也没有反馈电路,其典型结构如图8-1所示。

从电路行为上看,其特征就是输出信号的变化仅仅与输入信号的电平有关,不涉及对信号跳变沿的处理。

尽管组合电路在功能上千差万别,可是其分析方法却有很多相似之处。

给定逻辑电路后,得到其输入与输出的直接表达式,将输入组合全部带入表达式中计算得到输出结果,并以真值表的形式表达出来,最后根据真值表说明电路功能。

组合逻辑电路的设计就是在给定逻辑功能的前提下,通过某种设计渠道,得到满足功能要求且最简单的逻辑电路。

基于HDL 语言和EDA 工具的组合逻辑电路的设计流程如图8-2 所示。

程序设计语言与程序设计方法ppt课件

建模

采用UML等建模工具,对系统进 行可视化建模,包括类图、时序 图、用例图等,以便于理解和沟 通。

设计

根据需求和模型,进行系统架构 设计、数据库设计、界面设计等 ,制定详细的设计文档。

编码、测试与调试阶段方法论

编码

采用合适的编程语言和开发工具,按照设计 文档进行编码实现,注意代码风格和注释规 范。

功能强大

Python语言内置了丰富的库和模块,支持多种编程任务。

Python语言特点与应用领域

• 跨平台性:Python语言可以在多种操作系统上运 行,具有良好的跨平台性。

Python语言特点与应用领域

01

Web开发

Python语言在Web开发领域有 广泛应用,如Django、Flask等 框架。

2

定期召开项目会议,分享进展和遇到的问题

3

使用团队协作工具,提高沟通效率和协作效果

THANKS FOR WATCHING

感谢您的观看

结构化控制结构

使用顺序、选择和循环三种基本控制结构,简化 程序逻辑。

面向对象程序设计方法

类与对象

通过定义类来封装数据和操作,创建对象来实现具体功能。

继承与多态

利用继承实现代码重用,通过多态实现灵活的程序设计。

封装与信息隐藏

将数据与操作封装在类中,隐藏内部实现细节,提高程序安全性 。

敏捷开发方法与DevOps理念

01

03 02

成功项目案例剖析及经验借鉴

高质量的代码编写和测试 经验借鉴 重视团队建设和沟通协作能力的培养

成功项目案例剖析及经验借鉴

制定详细的项目计划和时间表,确保 按时交付

注重代码质量和测试,提高系统的稳 定性和可靠性

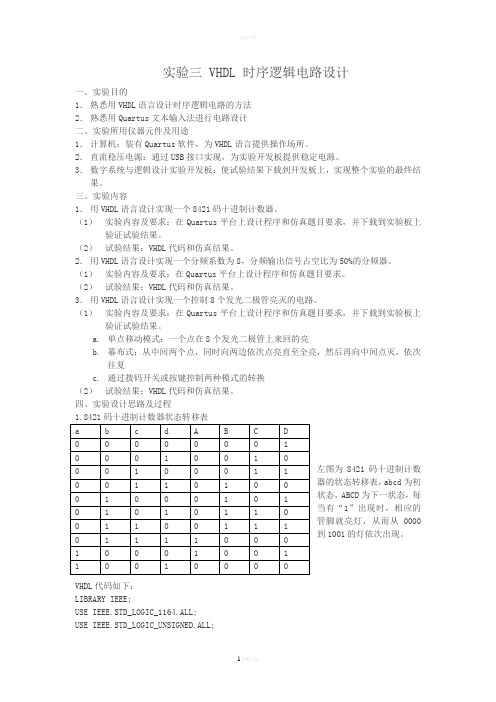

实验三-VHDL时序逻辑电路设计

实验三 VHDL 时序逻辑电路设计一、实验目的1.熟悉用VHDL语言设计时序逻辑电路的方法2.熟悉用Quartus文本输入法进行电路设计二、实验所用仪器元件及用途1.计算机:装有Quartus软件,为VHDL语言提供操作场所。

2.直流稳压电源:通过USB接口实现,为实验开发板提供稳定电源。

3.数字系统与逻辑设计实验开发板:使试验结果下载到开发板上,实现整个实验的最终结果。

三、实验内容1.用VHDL语言设计实现一个8421码十进制计数器。

(1)实验内容及要求:在Quartus平台上设计程序和仿真题目要求,并下载到实验板上验证试验结果。

(2)试验结果:VHDL代码和仿真结果。

2.用VHDL语言设计实现一个分频系数为8,分频输出信号占空比为50%的分频器。

(1)实验内容及要求:在Quartus平台上设计程序和仿真题目要求。

(2)试验结果:VHDL代码和仿真结果。

3.用VHDL语言设计实现一个控制8个发光二极管亮灭的电路。

(1)实验内容及要求:在Quartus平台上设计程序和仿真题目要求,并下载到实验板上验证试验结果。

a.单点移动模式:一个点在8个发光二极管上来回的亮b.幕布式:从中间两个点,同时向两边依次点亮直至全亮,然后再向中间点灭,依次往复c.通过拨码开关或按键控制两种模式的转换(2)试验结果:VHDL代码和仿真结果。

四、实验设计思路及过程1.8421码十进制计数器状态转移表左图为8421码十进制计数器的状态转移表,abcd为初状态,ABCD为下一状态,每当有“1”出现时,相应的管脚就亮灯,从而从0000到1001的灯依次出现。

VHDL代码如下:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY count12 ISPORT(clk,clear:IN STD_LOGIC;q :OUT STD_LOGIC_VECTOR(3 DOWNTO 0);END count12;ARCHITECTURE a OF count12 ISSIGNAL q_temp:ATD_LOGIC_VECTOR(3 DOWNTO 0);BEGINPROCESS(clk)BEGINIF(clk'event and clk='1') THENIF clear='0' THENq_temp<="0000";ELSIF q_temp="1011"THENq_temp<="0000";ELSEq_temp<=q_temp+1;END IF;END IF;END PROCESS;q<=q_temp;END a;2.分频系数为8,输出占空比为50%的分频器的设计左图为八分频器(占空比50%)的状态转移图,其中abc为原状态,ABC为下一状态。

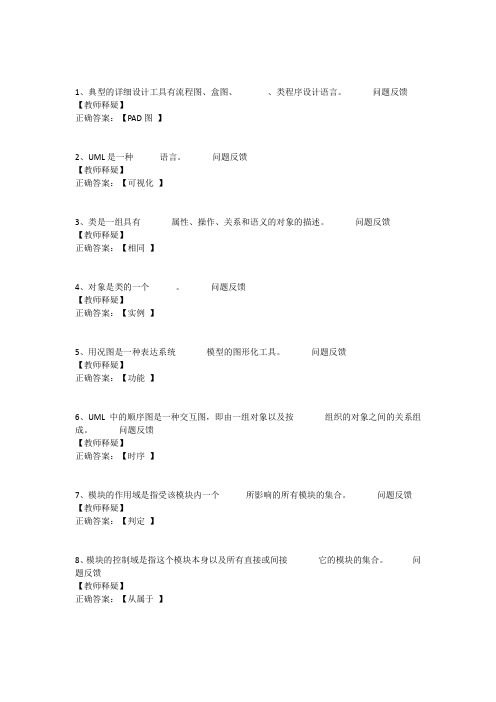

软件工程(简答题)

1、典型的详细设计工具有流程图、盒图、、类程序设计语言。

问题反馈【教师释疑】正确答案:【PAD图】2、UML是一种语言。

问题反馈【教师释疑】正确答案:【可视化】3、类是一组具有属性、操作、关系和语义的对象的描述。

问题反馈【教师释疑】正确答案:【相同】4、对象是类的一个。

问题反馈【教师释疑】正确答案:【实例】5、用况图是一种表达系统模型的图形化工具。

问题反馈【教师释疑】正确答案:【功能】6、UML中的顺序图是一种交互图,即由一组对象以及按组织的对象之间的关系组成。

问题反馈【教师释疑】正确答案:【时序】7、模块的作用域是指受该模块内一个所影响的所有模块的集合。

问题反馈【教师释疑】正确答案:【判定】8、模块的控制域是指这个模块本身以及所有直接或间接它的模块的集合。

问题反馈【教师释疑】正确答案:【从属于】9、在数据流图中引入数据源和数据潭这两个术语的目的是为了表示系统的,可以使用它们和相关数据流来定义系统的。

问题反馈【教师释疑】正确答案:【环境|边界】10、模块结构图是系统的一个高层蓝图,允许设计人员在较高的层次上进行抽象思维。

模块结构图可用和两种形式来表示。

问题反馈【教师释疑】正确答案:【层次图|HIPO图】11、在设计模块结构图时要基于原则来设计模块。

问题反馈【教师释疑】正确答案:【高内聚低耦合】12、在进行总体结构设计时,人们通过长期的软件开发实践,总结出一些实现模块“高内聚低耦合”的启发式规则,对初始的模块结构图进行精化,其中一条规则是“尽力使模块的在其控制域之内”。

问题反馈【教师释疑】正确答案:【作用域】13、在进行总体结构设计时,人们通过长期的软件开发实践,总结出一些实现模块“高内聚低耦合”的启发式规则,对初始的模块结构图进行精化,其中一条规则是“力求深度、宽度、扇出和扇入”。

问题反馈【教师释疑】正确答案:【适中】14、在进行总体结构设计时,人们通过长期的软件开发实践,总结出一些实现模块“高内聚低耦合”的启发式规则,对初始的模块结构图进行精化,其中一条规则是“改进软件结构,提高模块的”。

verilog hdl应用程序设计实例精讲

verilog hdl应用程序设计实例精讲网上现在有很多关于verilog hdl应用程序设计的资料,但是并没有一个很系统和全面的教程来帮助初学者快速入门。

本文就verilog hdl应用程序设计实例进行了精讲,从基本概念到应用实例一步一步地回答了初学者的问题,帮助大家理解verilog hdl的设计和应用。

一、verilog hdl的基本概念Verilog HDL是一种硬件描述语言,用于描述数字系统,包括逻辑电路、集成电路等等。

它既可以进行仿真验证,也可以直接生成硬件电路。

简单来说,verilog hdl就是一种用来描述数字系统的语言。

1.1 模块与实例化在verilog hdl中,模块是最基本的设计单元,每个模块包含一个或多个端口和内部逻辑电路。

模块可以包含其他模块,这被称为实例化。

实例化可以理解为创建一个模块的实例,并根据实例进行连接。

1.2 端口和内部信号模块的端口是与其他模块或外部电路连接的接口,可以是输入、输出或双向。

内部信号是模块内部产生和使用的信号,只在模块内部可见。

1.3 组合逻辑与时序逻辑组合逻辑是指只有输入信号改变时才会改变输出信号的逻辑电路,而时序逻辑是指输出信号的改变还受到时钟信号的控制。

在verilog hdl中,可以使用逻辑门、逻辑运算符和条件语句来实现组合逻辑和时序逻辑。

二、verilog hdl应用程序设计实例接下来,我们通过一些实例来展示verilog hdl的应用程序设计。

2.1 4位全加器我们首先来实现一个4位全加器。

全加器是用来实现两个二进制数的加法的电路,它能够实现两个输入和一个进位的相加操作,输出结果和进位。

在verilog hdl 中,可以使用逻辑运算符和条件语句来实现全加器。

2.2 4位加法器我们可以使用四个全加器来实现一个4位加法器。

加法器是用来实现两个二进制数的加法的电路,它能够实现多位的相加操作,输出结果和进位。

2.3 4位计数器计数器是一种能够实现计数功能的电路,它能够根据时钟信号进行计数,并在达到一定数值时输出特定信号。

asic 设计流程

asic 设计流程ASIC(Application Specific Integrated Circuit)是指专门为特定应用领域设计的集成电路。

ASIC设计流程指的是将一个特定的应用需求转化为ASIC电路的设计和制造过程。

本文将详细介绍ASIC设计流程的各个阶段和关键步骤。

一、需求分析阶段在ASIC设计流程中,首先需要进行需求分析。

这个阶段主要包括对应用需求的详细了解和分析,明确需要实现的功能和性能指标。

同时,还需要考虑制约因素,如成本、功耗、集成度等。

在需求分析阶段,设计团队与应用领域的专家密切合作,进行系统级的设计和规划。

他们会通过调研市场、分析竞争产品等手段,明确应用需求,并制定相应的设计目标。

二、架构设计阶段在需求分析阶段完成后,接下来是架构设计阶段。

在这个阶段,设计团队将根据需求分析的结果,确定ASIC的整体架构和功能划分。

架构设计阶段的关键是找到合适的功能模块,并确定它们之间的接口和通信方式。

通过模块化的设计思想,可以提高设计的可重用性和可维护性,并且方便后续的验证和仿真工作。

三、RTL设计阶段在架构设计阶段确定了ASIC的整体框架后,接下来是RTL (Register Transfer Level)设计阶段。

在这个阶段,设计团队将使用硬件描述语言(如Verilog、VHDL)来描述和实现ASIC的功能模块。

RTL设计阶段的关键是将功能模块转化为硬件逻辑电路。

设计团队需要仔细考虑时序和逻辑的优化,以提高电路的性能和功耗。

同时,还需要进行功能仿真和时序约束等工作,确保设计的正确性和可靠性。

四、综合与布局布线阶段在RTL设计阶段完成后,接下来是综合与布局布线阶段。

在这个阶段,设计团队将进行逻辑综合、布局和布线等工作,将RTL描述的电路转化为物理电路。

综合是将RTL描述的电路转化为门级网表电路的过程。

在综合过程中,设计团队需要进行逻辑优化和面积约束等工作,以提高电路的性能和集成度。

布局和布线是将门级网表电路映射到实际的芯片布局上的过程。

时序逻辑实验报告

实验报告姓名:陈生文学号:1053305048班级:电气二班一、课程设计要求1011序列发生器的设计实现设计内容:1)进行需求分析,确定总体框架;2)画出逻辑电路图; 3)对设计电路进行仿真; 设计要求:1)设计一个1011序列发生器;二、1011序列发生器分析之1011序列发生器序列信号是一组串行周期性的二进制码。

能够产生一组或多组序列信号的电路称为序列信号发生器。

序列信号发生器通常由移位寄存器或计数器构成,我采用的是移位寄存器序列信号发生器。

它由移位寄存器和组合逻辑输出网络两个部分组成,序列码从组合逻辑输出网络输出。

设计过程分为两步:首先根据序列码的长度M选择适合的移位寄存器,状态可以自定;按寄存器的状态转移关系和序列码的要求设计组合输出网络。

我采用这种方法的原因是可以通过并行送数进行初始化,因此这种结构对于输出序列的更改比较方便,有重复利用性,只要产生的序列长度相等即可。

程序源Entity sheji isPort ( X : in STD_LOGIC; clk : in STD_LOGI C; Z : out STD_LOGIC; );end mimasuo_sheji;architecture Behavioral ofsheji issignal state : STD_LOGIC_VECTOR(1 DOWNTO 0) := "00";signal next_state : STD_LOGIC_VECTOR(1 DOWNTO 0) :="00"; beginprocess(state,clk)beginstate <= next_state;if(clk'event and clk='1' )then case state iswhen"00" => if(c ='1')thennext_state <= "01";Z <= '0'; elsenext_state <= "00";Z <= '0';end if; when"01" => if(c='1')thennext_state <= "01";Z <= '0'; elsenext_state <= "10";Z <= '0'; end if; when"10" => if(c='1')thennext_state <= "11";Z <= '0'; elsenext_state <= "10"; Z<= '0'; end if;when"11" => if(c='1')thennext_state <= "01";Z <= '1'; elsenext_state <= "10"; Z <= '0'; end; end case; end if;end process; end Behavioral;仿真波形序列发生器波形。

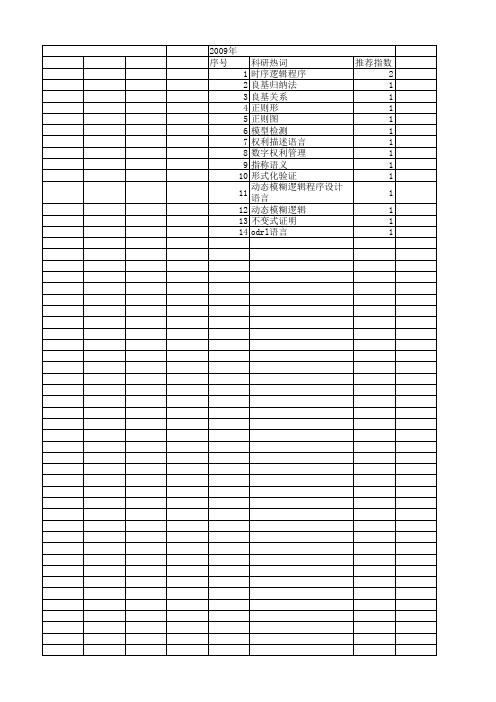

【计算机科学】_逻辑程序语言_期刊发文热词逐年推荐_20140725

2013年 序号 1 2 3 4 5

2013年 科研热词 量子力学 模态逻辑 模型检测 多agent系统 可能世界 推荐指数 1 1 1 1 1

2009年 序号 1 2 3 4 5 6 7 8 9 10 11 12 13 14

科研热词 推荐指数 时序逻辑程序 2 良基归纳法 1 良基关系 1 正则形 1 正则图 1 模型检测 1 权利描述语言 1 数字权利管理 1 指称语义 1 形式化验证 1 动态模糊逻辑程序设计语言 1 动态模糊逻辑 1 不变式证明 1 odrl5 6 7 8 9 10 goedel编译器 11 g(o)del编译器 12 datalog语言

科研热词 类型推断 多态处理 逻辑程序 程序调用 数字版权保护 可满足性检测 决策问题 xml

推荐指数 3 3 1 1 1 1 1 1 1 1 1 1

2011年 序号 1 2 3 4 5 6 7 8

科研热词 逻辑程序设计 赋值 程序 延迟计算 剪枝算子 一阶动态逻辑 web服务模型本体 web服务

推荐指数 1 1 1 1 1 1 1 1

2012年 序号 1 2 3 4 5 6 7

科研热词 静态分析 模型检测 模型抽取 查询语言 形式化验证 代码查询技术 socket

推荐指数 1 1 1 1 1 1 1

verilog语言及程序设计

verilog语言及程序设计Verilog语言及程序设计什么是Verilog语言?Verilog是一种硬件描述语言(HDL),用于描述数字系统的行为和结构。

它最初是由Gateway Design Automation公司(现在是Cadenza Design Automation公司的一部分)于1984年开发的,用于模拟和验证集成电路设计。

Verilog不仅可以用于模拟和验证电路设计,还可以用于编写可综合的硬件描述。

可综合的硬件描述可以通过合成工具转换成实际的硬件电路,在FPGA(现场可编程门阵列)和ASIC(应用特定集成电路)中实现。

Verilog的应用领域Verilog广泛应用于数字系统的设计、验证和实现。

它可以用于设计各种数字电路,包括处理器、存储器、通信接口、数字信号处理器等。

Verilog还被用于编写可综合的程序,用于验证电路设计的正确性。

Verilog的基本语法Verilog语言的基本语法与C语言类似,包括模块定义、端口声明、信号声明、组合逻辑、时序逻辑等。

下面是一个简单的Verilog模块的例子:verilogmodule MyModule (input wire clk,input wire rst,input wire in_data,output wire out_data);reg [7:0] reg1;always (posedge clk or posedge rst) beginif (rst)reg1 <= 8'b0;elsereg1 <= reg1 + in_data;endassign out_data = reg1;endmodule上面的例子定义了一个名为`MyModule`的Verilog模块,有4个端口:`clk`(时钟),`rst`(复位),`in_data`(输入数据),`out_data`(输出数据)。

其中的`reg1`是一个8位的寄存器,使用时序逻辑进行更新。

常用的基本电路模块的建模与设计

并单独就加法器和乘法器,作为数字通信系统

的重要部件进行建模与设计。

3.2 基本组合逻辑电路的VHDL的模型与

设计

❖ 数字逻辑电路可分为两类。一类逻辑电路的输 出只与当时输入的逻辑值有关,而与输入的历 史情况无关,这种逻辑电路称为组合逻辑电路 (Combinational Logic Circuit)。另一类逻辑 电路的输出不仅与电路当时输入的逻辑值有关, 而且与电路以前输入过的逻辑值有关,这种逻 辑电路称为时序逻辑电路(Sequential Logic Circuit)。

❖ 其模型基础是由数字逻辑符号表示的电路模型, 而 对 于 RTL 级 的 基 本 门 的 VDHL 描 述 , 非 常 简 单,只需用VHDL语言简单描述门的特性。对

于较复杂的基本电路模块,例如二进制计数器 的VHDL建模,是在其行为功能的基础上,建 立一个流程图模型,其对应的VHDL编程以流

程图为路线进行,既便于编程,又便于程序分 析。本章将首先介绍门电路的VHDL编程描述,

1. 模型

与非门的模型图如图3-5所示。

图3-5 与非门模型

其布尔代数模型为:

c ab

用VHDL语言描述为:c<=not (a and b)。

(3-3)

2.程序设计

在这里,设实体名为nand1,表示一个与非门,当然也可以用其它命名。其 VHDL编程如下:

library ieee; use ieee.std_logic_1164.all; entity nand1 is port(a,b: in std_logic;c: out std_logic);――定义输入端口为a,b;输出端口为c end entity nand1; architecture one of nand1 is begin c<=not (a and b);――“二与非”逻辑描述 end architecture one;

实验五时序逻辑电路实验报告

实验五时序逻辑电路实验报告一、实验目的1.了解时序逻辑电路的基本原理和设计方法。

2.掌握时序逻辑电路的设计方法。

3.运用Verilog语言进行时序逻辑电路的设计和仿真。

二、实验原理时序逻辑电路是指在电路中引入记忆元件(如触发器、计数器等),通过电路中的时钟信号和输入信号来控制电路的输出。

时序逻辑电路的输出不仅与当前输入有关,还与之前输入和输出的状态有关,因此对于时序逻辑电路的设计,需要考虑时钟信号的频率、输入信号的变化及当前状态之间的关系。

三、实验内容本次实验通过使用Verilog语言设计和仿真下列时序逻辑电路。

1.设计一个10进制累加器模块,实现对输入信号进行累加并输出,并在仿真中验证结果的正确性。

2.设计一个4位二进制计数器模块,实现对输入时钟信号的计数,并在仿真中验证结果的正确性。

3.设计一个4位带加载/清零控制功能的二进制计数器模块,实现对输入时钟信号的计数,并在仿真中验证结果的正确性。

四、实验步骤1.根据实验原理和要求,利用Verilog语言设计10进制累加器模块。

在设计中需要注意时钟的频率和输入信号的变化。

2.编译并运行仿真程序,验证设计的10进制累加器模块的正确性。

3.在设计时钟频率和输入信号变化的基础上,设计4位二进制计数器模块。

4.编译并运行仿真程序,验证设计的4位二进制计数器模块的正确性。

5.在设计4位二进制计数器模块的基础上,引入加载/清零控制功能,设计一个4位带加载/清零控制功能的二进制计数器模块。

6.编译并运行仿真程序,验证设计的带加载/清零控制功能的二进制计数器模块的正确性。

7.总结实验结果,撰写实验报告。

五、实验结果与分析1.经过验证实验,10进制累加器模块能够正确实现对输入信号的累加并输出正确的结果。

2.经过验证实验,4位二进制计数器模块能够正确实现对输入时钟信号的计数,并输出正确的计数结果。

3.经过验证实验,带加载/清零控制功能的二进制计数器模块能够正确实现对输入时钟信号的计数,并在加载或清零信号的控制下实现加载或清零操作。

框架投影时序逻辑程序设计语言中的指针

J0UR NAL 0F XI AN UNI DI VER S TY I

De . 0 8 c2 0

Vo . 5 NO 6 13 .

框 架 投 影 时序 逻 辑 程 序 设 计语 言 中 的指 针

Te u awhc safa n r jcinTe o a gcp o rmmig ln u g .I e tn st ePrjcin mp r ih i r migP oeto mp rl Lo i r g a n a g a e t xe d h oe t o

Te o a g c n g v s o ma d fn t n o p i t r r f r n e n d r f r n e a e o n me mp r lLo i a d ie f r l e iii s f o n e s e e e c a d e e e e c b s d n a o c n t n s n h n b s f t e fa p r t r a d mii l mo e i e t e i lme tn y i o sa t ,a d t e y u e o h r me o e a o n n ma d lg v s h mp e n i g wa n

王 小 兵 , 段 振 华

( 西安 电子 科 技 大 学 计 算理 论 与技 术研 究 所 , 西 西安 陕 707) 10 1

摘 要 :针 对 框 架 投 影 时序 逻 辑 程 序 设 计 语 言 F a dT mp r , 出 了 一种 形 式 化指 针 及 其 实现 的 新 方 rme e u a提 法. 方 法扩 展 了投 影 时 序逻 辑 , 于 名 字 常量 给 出 了 指 针 g用 和 反 引 用 的形 式 化 定 义 , 该 基 l 再使 用 框 架 操

VERILOGHDL语言基础

VERILOGHDL语⾔基础第1节 Verilog HDL语⾔简介Verilog HDL语⾔简介Verilog HDL和VHDL是⽬前世界上最流⾏的两种硬件描述语⾔(HDL:Hardware Description Language),均为IEEE标准,被⼴泛地应⽤于基于可编程逻辑器件的项⽬开发。

⼆者都是在20世纪80年代中期开发出来的,前者由Gateway Design Automation公司(该公司于1989年被Cadence公司收购)开发,后者由美国军⽅研发。

HDL语⾔以⽂本形式来描述数字系统硬件结构和⾏为,是⼀种⽤形式化⽅法来描述数字电路和系统的语⾔,可以从上层到下层来逐层描述⾃⼰的设计思想。

即⽤⼀系列分层次的模块来表⽰复杂的数字系统,并逐层进⾏验证仿真,再把具体的模块组合由综合⼯具转化成门级⽹表,接下去再利⽤布局布线⼯具把⽹表转化为具体电路结构的实现。

⽬前,这种⾃顶向下的⽅法已被⼴泛使⽤。

概括地讲,HDL语⾔包含以下主要特征:* HDL语⾔既包含⼀些⾼级程序设计语⾔的结构形式,同时也兼顾描述硬件线路连接的具体结构。

* 通过使⽤结构级⾏为描述,可以在不同的抽象层次描述设计。

HDL语⾔采⽤⾃顶向下的数字电路设计⽅法,主要包括3个领域5个抽象层次。

* HDL语⾔是并⾏处理的,具有同⼀时刻执⾏多任务的能⼒。

这和⼀般⾼级设计语⾔(例如C 语⾔等)串⾏执⾏的特征是不同的。

* HDL语⾔具有时序的概念。

⼀般的⾼级编程语⾔是没有时序概念的,但在硬件电路中从输⼊到输出总是有延时存在的,为了描述这⼀特征,需要引⼊时延的概念。

HDL语⾔不仅可以描述硬件电路的功能,还可以描述电路的时序。

2.1.1 Verilog HDL语⾔的历史1983年,Gateway Design Automation(GDA)硬件描述语⾔公司的Philip Moorby⾸创了Verilog HDL。

后来Moorby成为Verilog HDL-XL的主要设计者和Cadence公司的第⼀合伙⼈。

【国家自然科学基金】_时序逻辑语言_基金支持热词逐年推荐_【万方软件创新助手】_20140731

科研热词 推荐指数 软件体系结构 4 时序逻辑 4 描述 3 求精 2 模型检测 2 xyz/e 2 uml 2 面向方面软件设计 1 面向方面体系结构描述语言 1 面向对象程序设计 1 非确定自动机 1 随机实时时序逻辑 1 银行atm系统 1 软件体系描述语言 1 解释器 1 自动机 1 统一建模语言 1 正则形 1 模糊时间petri网 1 模型检验 1 模型提取 1 框架 1 时序逻辑语言 1 形式验证 1 形式化方法 1 工厂自动化系统 1 实时系统 1 安全性 1 双向交换自动机 1 公理系统 1 xyz/adl 1 psl(property specification language) 1 1 fl(foundation language) 1 atm系统 1 ansi-c 1

2011年 序号 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32

2011年 科研热词 推荐指数 模型检测 3 xyz/adl 2 mil-std-1553b 2 ip核 2 fpga 2 软件体系结构 1 行为时序逻辑 1 网络服务组合 1 网络服务描述语言(wsdl) 1 统一框架 1 统一建模语言 1 精化检验 1 程序规范 1 电梯控制系统 1 求精 1 有限状态自动机(fsa) 1 时间自动机 1 描述 1 扩展tempura语言 1 总线接收器 1 总线发送器 1 形式化验证 1 形式化方法 1 度量区时序逻辑 1 实时时序逻辑 1 基于迁移的扩展时间bchi自动机 1 区间模型 1 区间时序逻辑 1 动作时序逻辑(tla) 1 xyz/re 1 web服务组合 1 tableau方法 1

实验三_VHDL时序逻辑电路设计

实验三实验三 VHDL VHDL VHDL 时序逻辑电路设计时序逻辑电路设计 一、实验目的一、实验目的1. 熟悉用VHDL 语言设计时序逻辑电路的方法语言设计时序逻辑电路的方法 2. 熟悉用Quartus 文本输入法进行电路设计文本输入法进行电路设计 二、实验所用仪器元件及用途二、实验所用仪器元件及用途 1. 计算机:装有Quartus 软件,为VHDL 语言提供操作场所。

语言提供操作场所。

2. 直流稳压电源:通过USB 接口实现,为实验开发板提供稳定电源。

接口实现,为实验开发板提供稳定电源。

3. 数字系统与逻辑设计实验开发板:使试验结果下载到开发板上,实现整个实验的最终结果。

果。

三、实验内容三、实验内容 1. 用VHDL 语言设计实现一个8421码十进制计数器。

码十进制计数器。

(1) 实验内容及要求:在Quartus 平台上设计程序和仿真题目要求,并下载到实验板上验证试验结果。

验证试验结果。

(2) 试验结果:VHDL 代码和仿真结果。

代码和仿真结果。

2. 用VHDL 语言设计实现一个分频系数为8,分频输出信号占空比为50%的分频器。

的分频器。

(1) 实验内容及要求:在Quartus 平台上设计程序和仿真题目要求。

平台上设计程序和仿真题目要求。

(2) 试验结果:VHDL 代码和仿真结果。

代码和仿真结果。

3. 用VHDL 语言设计实现一个控制8个发光二极管亮灭的电路。

个发光二极管亮灭的电路。

(1) 实验内容及要求:在Quartus 平台上设计程序和仿真题目要求,并下载到实验板上验证试验结果。

验证试验结果。

a. 单点移动模式:一个点在8个发光二极管上来回的亮个发光二极管上来回的亮b. 幕布式:从中间两个点,同时向两边依次点亮直至全亮,然后再向中间点灭,依次往复往复c. 通过拨码开关或按键控制两种模式的转换通过拨码开关或按键控制两种模式的转换 (2) 试验结果:VHDL 代码和仿真结果。

框架时序逻辑语言MSVL中面向对象机制的实现

框 架 时 序逻 辑 语 言 MS VL 中 面 向对 象机 制 的实 现

王 小 兵 , 段 振 华

(. 西安 电 子科 技 大 学 计 算 理 论 与技 术 研 究 所 , 西 西 安 7 0 7 ;2 西 安 电子 科 技 大 学 综技 术 国 家重 点 实验 室 , 西 西 安 7 0 7 ;3 陕 1 0 1 .武 汉 大 学 软 件 工 程 国 家 重 点 实验 室 , 湖

f a e e p r ll g c l n u g S r m d t m o a o i a g a e M VL

W A N G i — i g .D UA N e — X ao b n ・一 Zh n hua

( .Re e r h I s .o o 1 s a c n t f C mp t g Th o y,Xi i n U n v , Xi n 7 0 7 ui e r n da i . ’ 1 0 1,Ch n ; 2 a ia .Te h o o y a d c n lg n

St t y La a e Ke b. o nt g a e r c e w o ks X i a U n v., Xia 71 071, Chi f I e r t d Se vie N t r , din i ’n 0 na; 3. St t Ke ae y Iab.ofSo t a e Eng. fw r ,W uha n v. W u n 4 07 nU i , ha 30 2,Chi na)

t e fa d t mp r l o i a g a e M S h r me e o a g cl n u g VL i d fn d,wh c n l d s s me t c n q e u h a e f a l s e i e ih i cu e o e h i u s s c sn w r me

计算机研究生语言

计算机研究生语言计算机研究生语言是指在计算机科学与技术领域中,研究生所需要掌握和使用的语言。

这些语言包括程序设计语言、领域特定语言、模型描述语言等。

程序设计语言是计算机研究生必须掌握的基本工具。

常见的程序设计语言有C、C++、Java、Python等。

这些语言具有不同的特点和用途,研究生需要根据具体的需求来选择合适的语言。

例如,C 语言适用于系统编程和底层开发,Java适用于跨平台应用开发,Python适用于数据分析和人工智能等领域。

领域特定语言是指在特定领域中使用的语言。

这些语言通常针对某一特定问题领域进行了优化,使得问题的表达更加简洁和直观。

例如,MATLAB是一种适用于科学计算和工程应用的领域特定语言,R是一种适用于统计分析和数据可视化的领域特定语言。

研究生在特定的领域中,需要掌握并熟练运用相应的领域特定语言。

模型描述语言是一种用于描述和分析计算机系统和软件模型的语言。

这些语言通常用于建立系统模型、进行性能分析和验证等。

常见的模型描述语言有UML、Petri网、时序逻辑等。

研究生需要学习和掌握这些模型描述语言,以便能够进行系统建模和分析。

除了上述的语言,计算机研究生还需要掌握一些其他的语言和工具。

例如,Linux命令行工具是计算机研究生必备的工具之一,研究生需要学习和掌握Linux系统的基本命令,以便能够进行系统管理和开发工作。

另外,研究生还需要学习和使用一些常见的开发工具和框架,如Git、Docker、TensorFlow等。

总结起来,计算机研究生语言包括程序设计语言、领域特定语言、模型描述语言以及其他相关的工具和语言。

研究生在学习和研究过程中,需要根据具体的需求来选择和使用合适的语言和工具。

通过掌握这些语言和工具,研究生能够更好地进行计算机科学与技术领域的研究和开发工作。

程序流程使用的表达工具

程序流程使用的表达工具1. 概述在软件开发过程中,程序流程使用的表达工具是非常重要的。

它们可以帮助开发人员清晰地描述程序的流程逻辑,便于团队内部沟通和代码的编写。

本文将介绍几种常用的程序流程表达工具,包括流程图、伪代码和时序图。

2. 流程图流程图是一种图形化的工具,用于表示程序的流程控制。

它由流程符号和箭头组成,通过不同的符号和箭头来表示不同的逻辑和控制结构。

流程图可以清晰地展示程序的控制流程,包括条件判断、循环和函数调用等。

下面是流程图的一些常用符号:•开始/结束符号:用于标识程序的开始和结束。

•输入/输出符号:表示程序的输入和输出操作。

•运算符号:表示程序的计算和逻辑运算。

•条件判断符号:表示程序的条件判断,如if语句。

•循环符号:表示程序的循环结构,如while循环和for循环。

流程图能够直观地展示程序的逻辑结构,便于开发人员理解和修改代码。

它还可以用于文档编写和代码审查,提高团队的协作效率。

3. 伪代码伪代码是一种类似于编程语言的记述语言,用于描述程序的逻辑流程。

它不是一种具体的编程语言,而是一种近似自然语言的描述方式。

伪代码往往采用简单的语法规则,以易于理解和写作为特点。

下面是一个使用伪代码描述循环的例子:while (条件为真) do执行语句1执行语句2end while伪代码可以清晰地表达程序的逻辑结构,更加直观地描述算法和逻辑。

它可以作为程序设计的一种框架,帮助开发人员更好地组织和编写代码。

伪代码还可以用于算法的描述和优化,方便进行代码的实现和测试。

4. 时序图时序图是一种用于描述对象之间消息交互顺序的图形工具。

它主要用于描述程序的执行过程,展示程序中不同对象之间的交互流程。

时序图由对象(用矩形表示)和消息(用箭头表示)组成,通过不同的对象和消息之间的序列图来表示程序的执行过程。

下面是一个简单的时序图示例:对象A->对象B: 消息1对象B->对象C: 消息2对象C->对象A: 消息3时序图能够清晰地展示程序的执行流程和对象之间的交互。

软件开发术语

软件开发术语⼀、结构化程序设计 结构化程序设计是以模块功能和详细处理过程设计为主的⼀种传统的程序设计思想,通常采⽤⾃顶向下、逐步求精的⽅式进⾏。

在结构化程序设计中,任何程序都可以由顺序、选择、循环三种基本结构构成。

结构化程序采⽤模块化设计思想来实现,基本思路是把程序要解决的总⽬标分解为若⼲个简单的⼩⽬标来处理,再进⼀步分解为具体的任务项来实现,在模块化的程序设计中,应尽量做到模块之间的⾼内聚、低耦合。

⼆、⾯向对象的基本概念 (1)对象:是要研究的任何事务,可以是⾃然界的任何事物。

对像由数据和作⽤于数据的操作构成⼀个独⽴整体,从程序设计者来看,对象是⼀个程序模块,从⽤户来看,对象可以提供⽤户所希望的⾏为。

(2)类:类是⼀组有相同数据和相同操作对象的定义,⼀个类包含的⽅法和数据描述⼀组对象的共同属性和⾏为。

类是在对象之上的抽象,对象则是类的具体化,是类的实例。

⾯向对象的程序设计语⾔通过类库来代替传统的函数库。

(3)消息和⽅法:对象之间进⾏通信的机制叫作消息。

(4)软件复⽤ 软件复⽤是指在两次或多次不同的软件开发过程中重复使⽤相同或相拟软件元素的过程,软件元素包括程序代码、测试⽤例、设计⽂档、设计过程、需求分析⽂档甚⾄领域知识。

根据复⽤跨越的问题领域,软件复⽤可分为垂直式复⽤和⽔平式复⽤。

垂直式复⽤:指在⼀类具有较多公共性的应⽤领域之间进⾏软件重⽤,⼤多数软件组织采⽤这种重⽤形式。

⽔平式复⽤:重⽤不同应⽤领域中的软件元素,例如数据结构、分类算法、⼈机界⾯构件等,标准函数库属于⽔平式重⽤。

三、⾯向对象的主要特征 (1)继承性 继承性是⼦类⾃动共享⽗类的数据结构和⽅法的⼀种机制。

在类层次中,若⼦类只继承⼀个⽗类的数据结构和⽅法,则称为单重继承,若⼦类继承多个⽗类的结构和⽅法,则称为多重继承。

(2)多态性 多态性是指相同的操作、函数或过程可作⽤于多种不同类型的对象上,对象收到同⼀个消息可以产⽣不同的结果,这种现象称为多态性。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

A Framed Temporal Logic Programming Language

Zhenhua Duan Computer School Xidian U niversity Xi an 710071 P.R.China zhhduan@ Maciej Koutny Department of Computing Science U niversity of N ewcastle upon T yne N ewcastle upon T yne N E 1 7RU, U.K. M aciej.Koutny @

1

_______________________________________________________________________________ 中国科技论文在线

2

interval over which it is executed. In particular, the sequence of processes, p1 , . . . , pm and process q may terminate at different time points. Although the communication between processes is still based on shared variables, the communication and synchronization only take place at the rendezvous points (global states), otherwise they are executed independently. The new projection operator also enables the specification of program execution using different time scales. Another problem that must be dealt with in temporal logic programming is that of communication between concurrent processes. Some models of concurrency involve shared (programming) variables, some involve synchronous message passing (e.g. CCS [8] and CSP [9]), and some involve asynchronous channels. In temporal logic programming languages, such as XYZ/E [5, 6], Tempura [4], METAMET [1] and TOKIO [2], the communication between parallel components is based on shared variables. Similarly as many concurrent programming languages [10], to synchronize communication between parallel processes in a concurrent program with the shared variable model (e.g., when solving the mutual exclusion problem), a synchronization construct, await(c) or some equivalent is required. The meaning of await(c) is simple: it changes no variables, but waits until the condition c becomes true, at which point it terminates. In a sequential program, an await statement is useless, since if c is currently false it will remain so forever. However, within a concurrent program this statement makes perfect sense since another process, acting in parallel, may cause c to become true. Defining await(c) is difficult without some kind of a framing construct. However, there is a problem which is caused by the fact that in temporal logic the values of variables are not inherited automatically from one state to another. Yet, to implement await(c), one requires some kind of indefinite stability, since one cannot know at the point of use how long the waiting will last. At the same time one must also allow variables to change, so that an external process can modify the Boolean parameter and it can eventually become true. Framing is concerned with how the value of a variable can be carried from one state to the next. In [11], a framing technique in temporal logic programming was introduced by means of an explicit operator, frame(x). The new construct was interpreted within minimal model semantics. This allows one to specify the framing status of variables throughout an interval in a flexible manner, and to define await(c) in an easy way. It should be noted that introducing the framing operator destroys the monotonicity and leads to a default logic [12]–[14]. Therefore, negation by default has to be used to manipulate the framing operator. In this paper, we formalize a framed concurrent temporal logic programming language, FTLL, under the projection temporal logic framework, PTL, a variant of interval temporal logic. An interpreter [11], written in SICSTUS Prolog, has been developed for a subset of FTLL using the framing technique presented here. The paper is organized as follows. The next section presents some fundamental aspects of the underlying PTL logic. In Section 3, the framing technique is discussed. Section 4 describes the framed programming language FTLL, and Section 5 provides two examples of FTLL programs. Conclusions are drawn in Section 6.

∗ Support by the National Natural Science Foundation of China under Grant No.60373103, the SRFDP Grant 20030701015 and the Grant SYSKF0407 from Lab. Computer Science, ISCAS.

∗

Abstract We discuss the projection temporal logic (PTL), based on a primitive projection operator, prj . A framing technique is also presented, using which a synchronization operator, await, is defined within the underlying logic. A framed temporal logic programming language (FTLL) is presented. To illustrate how to use both the language and framing technique, some examples are given. Keywords: Temporal logic, Temporal logic programming, Frame, Projection, Concurrency