WED3EG6418S-D4中文资料

MEMORY存储芯片TMS32C6414TBGLZWA8中文规格书

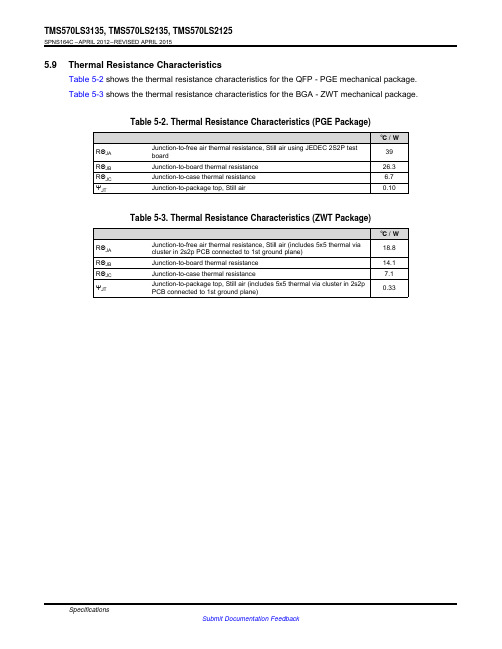

TMS570LS3135,TMS570LS2135,TMS570LS2125SPNS164C–APRIL2012–REVISED APRIL20155.9Thermal Resistance CharacteristicsTable5-2shows the thermal resistance characteristics for the QFP-PGE mechanical package.Table5-3shows the thermal resistance characteristics for the BGA-ZWT mechanical package.Table5-2.Thermal Resistance Characteristics(PGE Package)°C/WJunction-to-free air thermal resistance,Still air using JEDEC2S2P testRΘJA39boardRΘJB Junction-to-board thermal resistance26.3RΘJC Junction-to-case thermal resistance 6.7ΨJT Junction-to-package top,Still air0.10Table5-3.Thermal Resistance Characteristics(ZWT Package)°C/WJunction-to-free air thermal resistance,Still air(includes5x5thermal viaRΘJA18.8cluster in2s2p PCB connected to1st ground plane)RΘJB Junction-to-board thermal resistance14.1RΘJC Junction-to-case thermal resistance7.1Junction-to-package top,Still air(includes5x5thermal via cluster in2s2pΨJT0.33PCB connected to1st ground plane)SpecificationsTMS570LS3135,TMS570LS2135,TMS570LS2125SPNS164C–APRIL2012–REVISED APRIL2015 5.10Output Buffer Drive StrengthsTable5-4.Output Buffer Drive StrengthsLOW-LEVEL OUTPUT CURRENT,I OL for V I=V OLmaxor SIGNALSHIGH-LEVEL OUTPUT CURRENT,I OH for V I=V OHminFRAYTX2,FRAYTX1,FRAYTXEN1,FRAYTXEN2,MIBSPI5CLK,MIBSPI5SOMI[0],MIBSPI5SOMI[1],MIBSPI5SOMI[2],MIBSPI5SOMI[3],MIBSPI5SIMO[0],MIBSPI5SIMO[1],MIBSPI5SIMO[2],MIBSPI5SIMO[3],8mA TMS,TDI,TDO,RTCK,SPI4CLK,SPI4SIMO,SPI4SOMI,nERROR,N2HET2[1],N2HET2[3],All EMIF Outputs and I/Os,All ETM OutputsMIBSPI3SOMI,MIBSPI3SIMO,MIBSPI3CLK,MIBSPI1SIMO,MIBSPI1SOMI,MIBSPI1CLK, 4mAnRSTAD1EVT,CAN1RX,CAN1TX,CAN2RX,CAN2TX,CAN3RX,CAN3TX,DMM_CLK,DMM_DATA[0],DMM_DATA[1],DMM_nENA,DMM_SYNC,GIOA[0-7],GIOB[0-7],LINRX,LINTX,2mA zero-dominantMIBSPI1NCS[0],MIBSPI1NCS[1-3],MIBSPI1NENA,MIBSPI3NCS[0-3],MIBSPI3NENA,MIBSPI5NCS[0-3],MIBSPI5NENA,N2HET1[0-31],N2HET2[0],N2HET2[2],N2HET2[4],N2HET2[5],N2HET2[6],N2HET2[7],N2HET2[8],N2HET2[9],N2HET2[10],N2HET2[11],N2HET2[12],N2HET2[13],N2HET2[14],N2HET2[15],N2HET2[16],N2HET2[18],SPI2NCS[0],SPI2NENA,SPI4NCS[0],SPI4NENAECLK,selectable8mA/2mA SPI2CLK,SPI2SIMO,SPI2SOMIThe default output buffer drive strength is8mA for these signals.Table5-5.Selectable8mA/2mA ControlSIGNAL CONTROL BIT ADDRESS8mA2mAECLK SYSPC10[0]0xFFFF FF7801SPI2CLK SPI2PC9[9](1)0xFFF7F66801SPI2SIMO SPI2PC9[10](1)0xFFF7F66801SPI2SOMI SPI2PC9[11](1)0xFFF7F66801(1)Either SPI2PC9[11]or SPI2PC9[24]can change the output strength of the SPI2SOMI pin.In case of a32-bit write where these two bitsdiffer,SPI2PC9[11]determines the drive strength.SpecificationsTMS570LS3135,TMS570LS2135,TMS570LS2125SPNS164C–APRIL2012–REVISED APRIL20155.11Input TimingsFigure5-2.TTL-Level InputsTable5-6.Timing Requirements for Inputs(1)MIN MAX UNIT t pw Input minimum pulse width t c(VCLK)+10(2)ns(1)t c(VCLK)=peripheral VBUS clock cycle time=1/f(VCLK)(2)The timing shown in Figure5-2is only valid for pins used in GPIO mode.5.12Output TimingsTable5-7.Switching Characteristics for Output Timings versus Load Capacitance(C L)PARAMETER MIN MAX UNITCL=15pF 2.5CL=50pF4Rise time,t r nsCL=100pF7.2CL=150pF12.5 8mA low EMI pins(see Table5-4)CL=15pF 2.5CL=50pF4Fall time,t f nsCL=100pF7.2CL=150pF12.5CL=15pF 5.6CL=50pF10.4Rise time,t r nsCL=100pF16.8CL=150pF23.2 4mA low EMI pins(see Table5-4)CL=15pF 5.6CL=50pF10.4Fall time,t f nsCL=100pF16.8CL=150pF23.2 2mA-z low EMI pins CL=15pF8(see Table5-4)CL=50pF15Rise time,t r nsCL=100pF23CL=150pF33CL=15pF8CL=50pF15Fall time,t f nsCL=100pF23CL=150pF33 Specifications。

12864中文资料

12864液晶名称含义12864是128*64点阵液晶模块的点阵数简称,业界约定俗成的简称。

基本参数液晶屏类型 STN FSTN模块显示效果:黄绿底黑字蓝底白字白底黑字视角6点钟12点钟驱动方式 1/64 DUTY 1/9 BIAS背光LED白色LED黄绿色控制器KS0108或兼容ST7920 T6963C数据总线 8 位并口/6800 方式串口温度特性工作温度:-20℃~+70℃ 储藏温度:-30℃~+80℃点阵格式 128 x 64基本用途:该点阵的屏显成本相对较低,适用于各类仪器,小型设备的显示领域。

基本用途:该点阵的屏显成本相对较低,适用于各类仪器,小型设备的显示领域。

液晶模组使用注意事项1 当您在你的产品设计中使用本液晶模组,注意液晶的视角与你的产品用途相一致。

2 液晶屏是玻璃为基础的,跌落或与硬物撞击会引起液晶屏破裂或粉碎。

尤其是边角处。

3 尽管在液晶表面的偏振片有抑制反光的表层,应当小心不要划伤表面,一般推荐在液晶表面采用透明塑胶材料的保护屏。

4 如果液晶模组储藏在低于规定的温度以下,液晶材料会凝结而性能恶化。

如果液晶模组储藏在高于规定的温度以上,液晶材料的分子排列方向会转变为液态,可能无法恢复到原来的状态。

超出温度和湿度范围,会引起偏振片剥落或起泡。

因此,液晶模组应储藏在规定的温度范围。

5 如液晶表面遇口水或滴水,应立即擦除,避免长时间过后引起色彩变化或留下污点。

水蒸气会引起ITO电极腐蚀。

6 如果需要清洁液晶屏表面,应该用棉或软布轻快地擦拭,仍不能清除时,呵气之后再擦拭。

7 液晶模组的驱动应遵照规定的额定指标,避免故障及永久损坏。

对液晶材料施加直流电压,会引起液晶材料迅速恶化,应该确保提供交流波形的M信号的连续应用。

特别是,在电源开关时应遵照供电顺序,避免驱动锁存及直流直接加至液晶屏。

8 机械注意事项:a) 液晶模组是在高精度下调试安装的。

避免外力撞击,不要对其改变或修改。

b) 不要篡改金属框的任何突出部分。

MEMORY存储芯片TMS320C6414TZLZ中文规格书

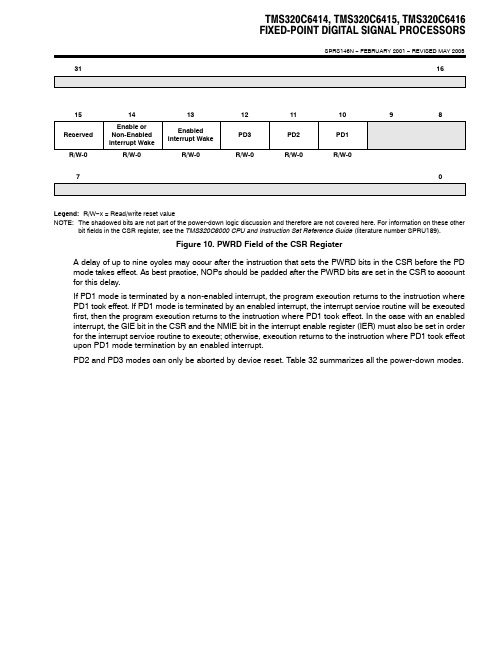

TMS320C6414, TMS320C6415, TMS320C6416FIXED-POINT DIGITAL SIGNAL PROCESSORSSPRS146N − FEBRUARY 2001 − REVISED MAY 2005 bootmodeThe C6414/15/16 device resets using the active-low signal RESET. While RESET is low, the device is held in reset and is initialized to the prescribed reset state. Refer to reset timing for reset timing characteristics and states of device pins during reset. The release of RESET starts the processor running with the prescribed device configuration and boot mode.The C6414/C6415/C6416 has three types of boot modes:D Host bootIf host boot is selected, upon release of RESET, the CPU is internally “stalled” while the remainder of the device is released. During this period, an external host can initialize the CPU’s memory space as necessary through the host interface, including internal configuration registers, such as those that control the EMIF or other peripherals. For the C6414 device, the HPI peripheral is used for host boot. For the C6415/C6416 device, the HPI peripheral is used for host boot if PCI_EN = 0, and the PCI peripheral is used for host boot if PCI_EN = 1. Once the host is finished with all necessary initialization, it must set the DSPINT bit in the HPIC register to complete the boot process. This transition causes the boot configuration logic to bring the CPU out of the “stalled” state. The CPU then begins execution from address 0. The DSPINT condition is not latched by the CPU, because it occurs while the CPU is still internally “stalled”. Also, DSPINT brings the CPU out of the “stalled” state only if the host boot process is selected. All memory may be written to and read by the host. This allows for the host to verify what it sends to the DSP if required. After the CPU is out of the “stalled” state, the CPU needs to clear the DSPINT, otherwise, no more DSPINTs can be received.D EMIF boot (using default ROM timings)Upon the release of RESET, the 1K-Byte ROM code located in the beginning of CE1 is copied to address 0 by the EDMA using the default ROM timings, while the CPU is internally “stalled”. The data should be stored in the endian format that the system is using. In this case, the EMIF automatically assembles consecutive 8-bit bytes to form the 32-bit instruction words to be copied. The transfer is automatically done by the EDMA as a single-frame block transfer from the ROM to address 0. After completion of the block transfer, the CPU is released from the “stalled” state and starts running from address 0.D No bootWith no boot, the CPU begins direct execution from the memory located at address 0. Note: operation is undefined if invalid code is located at address 0.resetA hardware reset (RESET) is required to place the DSP into a known good state out of power-up. The RESETsignal can be asserted (pulled low) prior to ramping the core and I/O voltages or after the core and I/O voltages have reached their proper operating conditions. As a best practice, reset should be held low during power-up.Prior to deasserting RESET (low-to-high transition), the core and I/O voltages should be at their proper operating conditions and CLKIN should also be running at the correct frequency.TMS320C6414, TMS320C6415, TMS320C6416FIXED-POINT DIGITAL SIGNAL PROCESSORSSPRS146N − FEBRUARY 2001 − REVISED MAY 2005absolute maximum ratings over operating case temperature range (unless otherwise noted)†Supply voltage ranges:CV DD (see Note 1)− 0.3 V to 1.8 V . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . DV DD (see Note 1)−0.3 V to 4 V . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Input voltage ranges:(except PCI), V I −0.3 V to 4 V . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . (PCI), V IP [C6415 and C6416 only]−0.5 V to DV DD + 0.5 V . . . . . . . . . . . . . . . . . . . . . Output voltage ranges:(except PCI), V O −0.3 V to 4 V . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . (PCI), V OP [C6415 and C6416 only]−0.5 V to DV DD + 0.5 V . . . . . . . . . . . . . . . . . . . . Operating case temperature ranges, T C :(default)0_C to 90_C . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . (A version) [A-5E0, A-6E3]−40_C to105_C . . . . . . . . . . . . . . . . . . . Storage temperature range, T stg −65_C to 150_C . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . †Stresses beyond those listed under “absolute maximum ratings” may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under “recommended operating conditions” is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.NOTE 1:All voltage values are with respect to V SS .recommended operating conditions MINNOM MAX UNIT CV DDSupply voltage, Core (-5E0 device)‡ 1.14 1.2 1.26V CV DDSupply voltage, Core (A-5E0 device)‡ 1.19 1.25 1.31V CV DDSupply voltage, Core (-6E3, A-6E3, -7E3 devices)‡ 1.36 1.4 1.44V DV DDSupply voltage, I/O 3.14 3.3 3.46V V SSSupply ground 000V V IHHigh-level input voltage (except PCI)2V V ILLow-level input voltage (except PCI)0.8V V IPInput voltage (PCI) [C6415 and C6416 only]−0.5DV DD + 0.5V V IHPHigh-level input voltage (PCI) [C6415 and C6416 only]0.5DV DD DV DD + 0.5V V ILPLow-level input voltage (PCI) [C6415 and C6416 only]−0.50.3DV DD V V OSMaximum voltage during overshoot/undershoot −1.0§ 4.3§V Operating case tem-Default 090_C T COperating case tem perature A version (C6414/15/16GLZA-5E0 and GLZA-6E3 only)–40105_C ‡Future variants of the C641x DSPs may operate at voltages ranging from 0.9 V to 1.4 V to provide a range of system power/performance options.TI highly recommends that users design-in a supply that can handle multiple voltages within this range (i.e., 1.2 V, 1.25 V, 1.3 V, 1.35 V, 1.4 V with ± 3% tolerances) by implementing simple board changes such as reference resistor values or input pin configuration modifications. Examples of such supplies include the PT4660, PT5500, PT5520, PT6440, and PT6930 series from Power Trends, a subsidiary of T exas Instruments. Not incorporating a flexible supply may limit the system’s ability to easily adapt to future versions of C641x devices.§The absolute maximum ratings should not be exceeded for more than 30% of the cycle period.。

(完整word版)12864中文字库说明书ST7920

12864C-1液晶中文显示模块(一)概述 (3)(一)(二)外形尺寸1 方框图 (3)2 外型尺寸图 (4)(二)(三)模块的接口 (4)(三)(四)硬件说明 (5)(五) 指令说明 (7)(四)(五)读写操作时序 (8)(五)(六)交流参数 (11)(六)(七)软件初始化过程 (12)(七)(八)应用举例 (13)(八)(九)附录1半宽字符表 (20)2 汉字字符表 (21)一、概述12864C-1是一种具有4位/8位并行、2线或3线串行多种接口方式,内部含有国标一级、二级简体中文字库的点阵图形液晶显示模块;其显示分辨率为128×64, 内置8192个16*16点汉字,和128个16*8点ASCII字符集.利用该模块灵活的接口方式和简单、方便的操作指令,可构成全中文人机交互图形界面。

可以显示8×4行16×16点阵的汉字. 也可完成图形显示.低电压低功耗是其又一显著特点。

由该模块构成的液晶显示方案与同类型的图形点阵液晶显示模块相比,不论硬件电路结构或显示程序都要简洁得多,且该模块的价格也略低于相同点阵的图形液晶模块。

基本特性:●●低电源电压(VDD:+3.0--+5.5V)●●显示分辨率:128×64点●●内置汉字字库,提供8192个16×16点阵汉字(简繁体可选)●●内置 128个16×8点阵字符●●2MHZ时钟频率●●显示方式:STN、半透、正显●●驱动方式:1/32DUTY,1/5BIAS●●视角方向:6点●●背光方式:侧部高亮白色LED,功耗仅为普通LED的1/5—1/10●●通讯方式:串行、并口可选●●内置DC-DC转换电路,无需外加负压●●无需片选信号,简化软件设计●●工作温度: 0℃ - +55℃ ,存储温度: -20℃ - +60℃二、方框图3、外形尺寸图三、模块接口说明*注释1:如在实际应用中仅使用串口通讯模式,可将PSB接固定低电平,也可以将模块上的J8和“GND”用焊锡短接。

计算机硬件指标

显存容量决定了显示芯片能处理的数据量。除显存频率和位宽外,影响显卡性能的一个非常重要的指标就是显存的容量。从理论上讲,显存容量越大,显卡性能就越好。

⑵显示器的性能参数

显示器作为最重要的输出设备,其性能好坏直接影响到用户的使用和身体健康。根据显示器成像原理,可分为CRT显示器、LCD(液晶)显示器和等离子显示器(PD),目前用户常用的是CRT显示器和LCD(液晶)显示器。

BIOS惠普68CPC Ver. F.02

制造日期06/09/2011

内存:

DIMM 0:海力士DDR3 1333MHz 2GB

制造日期2010年01月

型号AD HMT125S6BFR8C-H9 N0

序列号:BD43B222

DIMM 3:金士顿DDR3 1333MHz 2GB

制造日期2011年04月

CPU的接口是指CPU与主板插槽接触的部位。

⑹制造工艺

CPU的制造工艺一般是指CPU内部主要电子元件之间所间隔的距离,其单位通常为nm(纳米),生产工艺越先进,连接线越细,CPU内部功耗和发热量越小,其集成度越高。

主板:

⑴主板的结构

主板上的主要结构元素有以下几点:

①主板的接口

目前大多数主板的接口一般有IDE接口、SATA接口、软驱接口等。

④可扩充性

主板的扩充能力主要体现在有足够的扩展槽、内存插槽、CPU插槽及硬盘、光驱接口、USB接口等。

内存:

内存的主要性能参数有容量、工作电压、存取时间、工作频率、数据宽度等。

⑴容量

计算机中内存容量越大,计算机运行速度也就越快。但内存容量的增加受到主板芯片支持能力和内存插槽数量的制约。因此在扩充内存容量时,要了解所使用的主板所支持的最大内存容量和空闲的内存插槽数量。

W3HG128M64EEUXXXD4MG资料

W3HG128M64EEU-D4ADVANCED*White Electronic Designs1GB – 128Mx64 DDR2 SDRAM UNBUFFERED, SO-DIMMDESCRIPTIONThe W3HG128M64EEU is a 128Mx64 Double Data Rate2 SDRAM memory module based on 1Gb DDR2 SDRAM components. The module consists of eight 128Mx8, in FBGA package mounted on a 200 pin SO-DI MM FR4 substrate.* T his product is under development, is not qualifi ed or characterized and is subject to change or cancellation without notice.NOTE: C onsult factory for availability of:• Vendor source control options • Industrial temperature optionFEATURES200-pin, Small-Outline DIMM (SO-DIMM), RawCard "B" Fast data transfer rates: PC2-6400*, PC2-5300*,PC2-4200 and PC2-3200 Utilizes 800*, 667*, 533 and 400 Mb/s DDR2SDRAM components V CC = V CCQ = 1.8V ± 0.1V V CCSPD = 1.7V to 3.6VJEDEC standard 1.8V I/O (SSTL_18-compatible) Differential data strobe (DQS, DQS#) option Four-bit prefetch architectureDLL to align DQ and DQS transitions with CK Multiple internal device banks for concurrentoperation Supports duplicate output strobe (RDQS/RDQS#) Programmable CAS# latency (CL): 3, 4, 5* and 6* Adjustable data-output drive strength On-Die Termination (ODT)Posted CAS# latency: 0, 1, 2, 3 and 4 Serial Presence Detect (SPD) with EEPROM 64ms: 8,192 cycle refresh Gold edge contacts Single Rank RoHS Compliant JEDEC Package option• 200 Pin (SO-D IMM)• PCB – 29.20mm (1.150") TYPOPERATING FREQUENCIESPC2-6400*PC2-5300*PC2-4200PC2-3200Clock Speed 400MHz 333MHz 266MHz 200MHz CL-t RCD -t RP6-6-65-5-54-4-43-3-3* Consult factory for availabilityW3HG128M64EEU-D4ADVANCEDWhite Electronic DesignsPIN NAMESSYMBOLDESCRIPTION A0 - A13Address inputODT0On-Die Termination CK0, CK0#Differential Clock Inputs CK1, CK1#Differential Clock inputs CKE0Clock Enable input CS0#Chip selectRAS#, CAS#, WE#Command Inputs BA0 - BA2Bank Address Inputs DM0 - DM7Input Data Mask DQ0 - DQ63Data Input/Output DQS0 - DQS7DQS0#-DQS7#Data StrobeSCL Serial Clock for Presence Detect SA0-SA1Presence Detect Address Inputs SDA Serial Presence Detect Data V CC Power SupplyV REF SSTL_18 reference voltage V SS GroundV CCSPD Serial EEPROM Power Supply NCNo ConnectPIN CONFIGURATIONPIN#SYMBOL PIN#SYMBOL PIN#SYMBOL PIN#SYMBOL1V REF51DQS2101A1151DQ422V SS 52DM2102A0152DQ463V SS53V SS 103V CC 153DQ434DQ454V SS 104V CC 154DQ475DQ055DQ18105A10/AP 155V SS 6DQ556DQ22106BA1156V SS 7DQ157DQ19107BA0157DQ488V SS 58DQ23108RAS#158DQ529V SS 59V SS 109WE#159DQ4910DM060V SS 110CS0#160DQ5311DQS0#61DQ24111V CC 161V SS 12V SS 62DQ28112V CC 162V SS 13DQS063DQ25113CAS#163NC 14DQ664DQ29114ODT0164CK115V SS65V SS 115NC 165V SS 16DQ766V SS 116A13166CK1#17DQ267DM3117V CC 167DQS6#18V SS 68DQS3#118V CC 168V SS 19DQ369NC 119NC 169DQS620DQ1270DQS3120NC 170DM621V SS 71V SS 121V SS 171V SS 22DQ1372V SS 122V SS 172V SS 23DQ873DQ26123DQ32173DQ5024V SS74DQ30124DQ36174DQ5425DQ975DQ27125DQ33175DQ5126DM176DQ31126DQ37176DQ5527V SS 77V SS 127V SS 177V SS 28V SS 78V SS 128V SS 178V SS 29DQS1#79CKE0129DQS4#179DQ5630CK080NC 130DM4180DQ6031DQS181V CC 131DQS4181DQ5732CK0#82V CC 132V SS 182DQ6133V SS 83NC 133V SS 183V SS 34V SS 84NC 134DQ38184V SS 35DQ1085BA2135DQ34185DM736DQ1486NC 136DQ39186DQS7#37DQ1187V CC137DQ35187V SS 38DQ1588V CC 138V SS 188DQS739V SS 89A12139V SS 189DQ5840V SS 90A11140DQ44190V SS 41V SS 91A9141DQ40191DQ5942V SS 92A7142DQ45192DQ6243DQ1693A8143DQ41193V SS 44DQ2094A6144V SS 194DQ6345DQ1795V CC 145V SS 195SDA 46DQ2196V CC 146DQS5#196V SS 47V SS 97A5147DM5197SCL 48V SS 98A4148DQS5198SA049DQS2#99A3149V SS 199V CCSPD 50NC 100A2150V SS 200SA1White Electronic DesignsW3HG128M64EEU-D4ADVANCED FUNCTIONAL BLOCK DIAGRAMW3HG128M64EEU-D4ADVANCEDWhite Electronic DesignsRECOMMENDED DC OPERATING CONDITIONSAll voltages referenced to V SSParameter Symbol Min Max Units Notes Supply VoltageV CC 1.7 1.9V -I/O Reference VoltageV REF 0.49 x V CC 0.51 x V CC V 1I/O Termination Voltage (system)V TT V REF - 40V REF + 40mV 2NOTE:1. V REF is expected to equal V CCQ /2 of the transmitting device and to track variations in the DC level of the same. Peak-to-peak noise (non-common mode) on V REF may not exceed±1 percent of the DC value. Peak-to-peak AC noise on V REF may not exceed ±2 percent of V REF (DC). This measurement is to be taken at the nearest V REF bypass capacitor.2. V TT is not applied directly to the device. V TT is a system supply for signal termination resistors, is expected to be set equalto V REF and must track variations in the DC level of V REF .ABSOLUTE MAXIMUM DC CHARACTERISTICSSymbol ParameterMin Max Units V CC V CC Supply Voltage Relative to V SS -0.5 2.3V V IN , V OUT Voltage on any Pin Relative to V SS -0.5 2.3V T STG Storage Temperature-55100°C T CASE DDR2 SDRAM Device Operating Temperature*085°C T OPR Operating Temperature (Ambient)065°C I IInput Leakage Current; Any input 0V ≤ V IN ≤ V CC ; V REF input 0V ≤ V IN ≤0.95V; (All other pins not under test = 0V)Command/Address, RAS#, CAS#, WE# S#, CKE-4040µACK, CK#-2020DM-55I OZ Output Leakage Current; 0V ≤ V OUT ≤ V CC Q; DQs and ODT are disabledDQ, DQS, DQS#-55µA I VREFV REF Leakage Current; V REF = Valid V REF level-1616µA* T CASE specifi es as the temperature at the top center of the memory devices.CAPACITANCET A = 25°C, f = 100MHz, V CC = 1.8V, V REF = V SSParameterSymbol Max Unit Input Capacitance (A0-A12)C IN135pF Input Capacitance (RAS#,CAS#,WE#)C IN235pF Input Capacitance (CKE0)C IN331pF Input Capacitance (CK0, CK0#)C IN415pF Input Capacitance (CS0#)C IN531pF Input Capacitance (DQS0#-DQS17#)C IN66pF Input Capacitance (BA0-BA1)C IN735pF Data input/output Capacitance (DQ0-DQ63)C OUT 6pFNOTE:* These capacitance values are based on worst case component values in conjunction with the circuit boards associated parasitic net capacitance.W3HG128M64EEU-D4ADVANCED White Electronic DesignsDDR2 I CC SPECIFICATIONS AND CONDITIONSDDR2 SDRAM components onlyV CC = +1.8V ± 0.1VParameter Symbol Condition806665534403Units Operating one devicebank active-precharge current;I CC0t CK = t CK (I CC), t RC = t RC (I CC), t RAS = t RAS MIN (I CC); CKE is HIGH, CS# isHIGH between valid commands; Address bus inputs are SWITCHING;Data bus inputs are SWITCHING.TBD800640640mAOperating one devicebank active-read-precharge current;I CC1I OUT = 0mA; BL = 4, CL = CL(I CC), AL = 0; t CK = t CK (I CC), t RC = t RC (I CC),t RAS = t RAS MIN (I CC), t RCD = t RCD (I CC); CKE is HIGH, CS# is HIGHbetween valid commands; Address bus inputs are SWITCHING; Datapattern is same as I CC4W.TBD1,160760760mAPrecharge power-down current;I CC2PAll device banks idle; t CK = t CK (I CC); CKE is LOW; Other control andaddress bus inputs are STABLE; Data bus inputs are FLOATING.TBD564040mAPrecharge quiet standby current;I CC2QAll device banks idle; t CK = t CK (I CC); CKE is HIGH, CS# is HIGH; Othercontrol and address bus inputs are STABLE; Data bus inputs areFLOATING.TBD480328280mAPrecharge standby current;I CC2NAll device banks idle; t CK = t CK (I CC); CKE is HIGH, CS# is HIGH; Othercontrol and address bus inputs are SWITCHING; Data bus inputs areSWITCHING.TBD520360280mAActive power-down current;I CC3PAll device banks open; t CK = t CK (I CC); CKE is LOW;Other control and address bus inputs are STABLE;Data bus inputs are FLOATING.Fast PDN ExitMR[12] = 0TBD320240200mASlow PDN ExitMR[12] = 1TBD808080mAActive standby current;I CC3N All device banks open; t CK = t CK(I CC), t RAS = t RAS MAX (I CC), t RP = t RP(I CC);CKE is HIGH, CS# is HIGH between valid commands; Other control andaddress bus inputs are SWITCHING; Data bus inputs are SWITCHING.TBD560400320mAOperating burst write current;I CC4WAll device banks open, Continuous burst writes; BL = 4, CL = CL (I CC),AL = 0; t CK = t CK (I CC), t RAS = t RAS MAX (I CC), t RP = t RP (I CC); CKE isHIGH, CS# is HIGH between valid commands; Address bus inputs areSWITCHING; Data bus inputs are SWITCHING.TBD1,4401,040960mAOperating burst read current;I CC4RAll device banks open, Continuous burst reads, I OUT = 0mA; BL = 4, CL= CL (I CC), AL = 0; t CK = t CK (I CC), t RAS = t RAS MAX (I CC), t RP = t RP (I CC);CKE is HIGH, CS# is HIGH between valid commands; Address businputs are SWITCHING; Data bus inputs are SWITCHING.TBD1,6401,1601,080mABurst refresh current;I CC5t CK = t CK (I CC); Refresh command at every t RFC (I CC) interval; CKEis HIGH, CS# is HIGH between valid commands; Other control andaddress bus inputs are SWITCHING; Data bus inputs are SWITCHING.TBD2,1602,0001,920mASelf refresh current;I CC6CK and CK# at 0V; CKE ≤ 0.2V; Other control and address bus inputsare FLOATING; Data bus inputs are FLOATING.TBD564040mAOperating device bank interleave read current; I CC7All device banks interleaving reads, I OUT= 0mA; BL = 4, CL = CL (I CC),AL = t RCD (I CC)-1 x t CK (I CC); t CK = t CK (I CC), t RC = t RC(I CC), t RRD = t RRD(I CC),t RCD = t RCD(I CC); CKE is HIGH, CS# is HIGH between valid commands;Address bus inputs are STABLE during DESELECTs; Data bus inputsare SWITCHINGTBD2,7202,3602,360mANote:• I CC specifi cation is based on MICRON components. Other DRAM manufacturers specifi cation may be different.W3HG128M64EEU-D4ADVANCEDWhite Electronic DesignsAC OPERATING CONDITIONSV CC = +1.8V ±0.1VC l o c kAC Characteristics Symbol806665534403Units NotesParameterMinMaxMin Max Min Max Min Max Clock cycle timeCL = 6t CK (6)3,0008,000------ps CL = 5t CK (5)3,0008,0003,0008,000----ps 16, 22, 36, 38CL = 4t CK (4)3,0008,0003,7508,0003,7508,0005,0008,000ps CL = 3tCK (3)--5,0008,0005,0008,0005,0008,000psCK high-level width tCH AVG 0.480.520.480.520.480.520.480.52t CK 45CK low-level width tCL AVG0.480.520.480.520.480.520.480.52tCKHalf clock periodtHP MIN (t CH,t CL)MIN (t CH,t CL)MIN (t CH,t CL)MIN (t CH,t CL)ps46C l o c k (A b s o l u t e )Absolute tCk tCK abstCKAVG+(MIN)+tJITPER (MIN)tCKAVG+(MAX)+t JITPER (MAX)tCKAVG+(MIN)+t JITPER (MIN)tCKAVG+(MAX)+t JITPER (MAX)tCKAVG+(MIN)+t JITPER (MIN)tCKAVG+(MAX)+t JITPER (MAX)tCKAVG+(MIN)+t JITPER (MIN)tCKAVG+(MAX)+tJITPER (MAX)psAbsolute CK high-level widthtCH abstCKAVG (MIN)*t CH AVG+t JIT DTY(MIN)tCKAVG (MAX)*t CH AVG+t JIT DTY(MAX)tCKAVG (MIN)*t CH AVG+t JIT DTY(MIN)tCKAVG (MAX)*t CH AVG+t JIT DTY(MAX)tCKAVG (MIN)*t CH AVG+t JIT DTY(MIN)tCKAVG (MAX)*t CH AVG+t JIT DTY(MAX)tCKAVG (MIN)*t CH AVG+t JIT DTY(MIN)tCKAVG (MAX)*t CHAVG+t JIT DTY(MAX)psAbsolute CK low-level widthtCL abstCKAVG (MIN)*tCLAVG(MIN)+t JIT DTY(MIN)t CKAVG (MAX)*tCLAVG (MAX)+t JIT DTY(MIN)t CKAVG (MIN)*t CLAVG (MIN)+t JIT DTY(MIN)t CKAVG (MAX)*t CLAVG (MAX)+t JIT DTY(MIN)t CKAVG (MIN)*t CLAVG (MIN)+t JIT DTY(MIN)t CKAVG (MAX)*t CLAVG (MAX)+t JIT DTY(MIN)t CKAVG(MIN)*t CLAVG(MIN)+tJIT DTY(MIN)tCKAVG(MAX)*t CLAVG(MAX)+t JITDTY(MIN)psC l o c k j i t t e rClock jitter - period tJIT PER-125125-125125-125125-125125ps 39Clock jitter - half period tJIT DUTY -125125-125125-125125-150150ps 40Clock jitter - cycle to cycle tJIT CC250250250250ps 41Cumulative jitter error, 2 cycles t ERR 2per -175175-175175-175175-175175ps 42Cumulative jitter error, 3 cycles t ERR 3per -225225-225225-225225-225225ps 42Cumulative jitter error, 4 cycles t ERR 4per -250250-250250-250250-250250ps 42Cumulative jitter error, 5cycles t ERR 5per-250250-250250-250250-250250ps 42, 48Cumulative jitter error, 6-10 cycles t ERR 6-10per -350350-350350-350350-350350ps 42, 48Cumulative jitter error, 11-50 cyclest ERR 11-50per -450450-450450-450450-450450ps42Note:• AC specifi cation is based on MICRON components. Other DRAM manufactures specifi cation may be different.W3HG128M64EEU-D4ADVANCEDWhite Electronic DesignsAC OPERATING CONDITIONS (continued)V CC = +1.8V ±0.1VD a t aAC Characteristics Symbol806665534403Units Notes ParameterMin Max Min Max Min Max Min Max tQHS-340-340-400-450ps 47DQ output access time from CK/CK#tAC -450+450-450+450-500+500-600+600ps 43Data-out high-impedance window from CK/CK#tHZtAC (MAX)tAC (MAX)tAC (MAX)tAC (MAX)ps 8, 9, 43Data-out low-impedance window from CK/CK#tLZ1tAC (MIN)tAC (MAX)tAC (MIN)tAC (MAX)tAC (MIN)tAC (MAX)tAC (MIN)tAC (MAX)ps 8, 10, 43Data-out low-impedance window from CK/CK#tLZ 22*t AC(MIN)tAC (MAX)2*t AC(MIN)tAC (MAX)2*t AC(MIN)tAC (MAX)2*t AC(MIN)tAC (MAX)ps 8, 10, 43DQ and DM input setup time relative to DQS tDS a300300350400ps 7, 15,19DQ and DM input hold time relative to DQS tDH a 300300350400ps 7, 15, 19DQ and DM input setup time relative to DQS tDS b100100100150ps 7, 15, 19DQ and DM input hold time relative to DQS tDH b175175225275ps7, 15,19DQ and DM input pulse width (for each input)t DIPW0.350.350.350.35tCK37Data hold skew factortQHS340340400450ps 47DQ–DQS hold, DQS to fi rst DQ to go nonvalid, per accesstQHtHP-tQHStHP-tQHStHP-tQHStHP-tQHSps 15, 17, 47Data valid output window (DVW)t DVWt QH - tDQSQ t QH - tDQSQ t QH - tDQSQ t QH- tDQSQns15, 17D a t a S t r o b eDQS input high pulse width t DQSH 0.350.350.350.35t CK 37DQS input low pulse widthtDQSL0.350.350.350.35tCK37DQS output access time from CK/CK#t DQSCK -400+400-400+400-450+450-500+500ps40DQS falling edge to CK rising – setup time t DSS 0.20.20.20.2t CK 37DQS falling edge from CK rising – hold timetDSH0.20.20.20.2tCK37Note:• AC specifi cation is based on MICRON components. Other DRAM manufactures specifi cation may be different.W3HG128M64EEU-D4ADVANCEDWhite Electronic DesignsAC OPERATING CONDITIONS (continued)V CC = +1.8V ±0.1VD a t a S t r o b eAC Characteristics Symbol806665534403Units Notes ParameterMinMax MinMax MinMax MinMax DQS–DQ skew, DQS to last DQ valid, per group, per accesstDQSQ 240240300350ps15, 17DQS read preamble tRPRE 0.9 1.10.9 1.10.9 1.10.9 1.1tCK33, 37, 43DQS read postamble t RPST0.40.60.40.60.40.60.40.6tCK33, 34, 37, 43DQS write preamble setup time tWPRE S 0000ps12, 13,DQS write preamble tWPRE 0.350.350.250.25tCK 37DQS write postambletWPST 0.40.60.40.60.40.60.40.6t CK 11, 37Positive DQS latching edge to associated clock edge tDQSS- 0.25 0.25- 0.25 0.25- 0.25 0.25- 0.25 0.25tCK 37Write command to fi rst DQS latching transition WL-tDQSSWL+tDQSSWL-tDQSSWL+tDQSSWL-tDQSSWL+tDQSSWL-tDQSSWL+tDQSStCK C o m m a n d a n d A d d r e s sAddress and control input pulse width for each input t IPW0.60.60.60.6tCK37Address and control input setup time t IS a 400400500600ps 6, 19Address and control input hold time tIH a 400400500600ps 6, 19Address and control input setup time t IS b200200250350ps6, 19Address and control input hold time tIH b2752753754756, 19CAS# to CAS# command delayt CCD2222tCK37ACTIVE to ACTIVE (same bank) command tRC54555555ns 31, 37ACTIVE bank a to ACTIVE bank b command t RRD (x8)7.57.57.57.5ns 25, 37ACTIVE to READ or WRITE delay tRCD 12151515ns 37Four Bank Activate period tFAW(x8)37.537.537.537.5ns28, 37ACTIVE to PRECHARGE command tRAS 4070,0004070,0004070,0004070,000ns 18, 31,37Internal READ to precharge command delay tRTP 7.57.57.57.5ns 21, 25. 37Write recovery timet WR15151515ns 25, 37Auto precharge write recovery + precharge time tDALtWR + tRPtWR + tRPtWR + tRPtWR + tRPns 20Internal WRITE to READ command delay t WTR 7.57.57.510ns 25, 37PRECHARGE command period tRP12151515ns 29, 37PRECHARGE ALL command period t RPAtRP + tCKtRP + tCKtRP + tCKtRP + tCKns29LOAD MODE command cycle timet MRD 2222tCK37Note:• AC specifi cation is based on MICRON components. Other DRAM manufactures specifi cation may be different.W3HG128M64EEU-D4ADVANCEDWhite Electronic DesignsAC OPERATING CONDITIONS (continued)V CC = +1.8V ±0.1VAC Characteristics Symbol806665534403Units Notes ParameterMinMaxMinMaxMinMaxMinMaxR e f r e s hCKE low to CK,CK# uncertainty tDELAYtIS + tCK + tIH tIS + tCK + tIH tIS + tCK + tIH tIS + tCK + tIHns 26REFRESH to ACTIVE or REFRESH to REFRESH command intervaltRFC 127.570,000127.570,000127.570,000127.570,000ns 14, 37Average periodic refresh interval (commercial)tREFI 7.87.87.87.8µs 14, 37Average periodic refresh interval (industrial)tREFI IT 3.9 3.93.93.9µs 14, 37S e l f R e f r e s hExit self refresh to non-READ command tXSNR t RFC(MIN) + 10t RFC(MIN) + 10t RFC(MIN) + 10t RFC(MIN) + 10nsExit self refresh to READ command tXSRD200200200200tCK37Exit self refresh timing reference tISXR t IS t ISt ISt ISps 6, 27O D TODT turn-on delay t AOND 22222222tCK37ODT turn-on tAOND tAC (MIN)tAC (MAX) + 700)t AC (MIN)tAC (MAX) + 700)t AC (MIN)tAC (MAX) + 1,000)t AC (MIN)tAC (MAX) + 1,000)ps23, 43ODT turn-off delay tAOFD2.52.52.52.52.52.52.52.5tCK35, 37ODT turn-off tAOFtAC (MIN)tAC (MAX + 600)t AC (MIN)tAC (MAX + 600)t AC (MIN)tAC (MAX + 600)t AC (MIN)tAC (MAX + 600)ps 24, 44ODT turn-on (power-down mode)t AONPDtAC (MIN) + 2,000 2 x tCK +tAC (MAX) + 1,000t AC (MIN) + 2,000 2 x tCK +t AC (MAX) + 1,000t AC (MIN) + 2,000 2 x tCK +t AC (MAX) + 1,000t AC (MIN) + 2,0002 x tCK +tAC (MAX)+ 1,000psODT turn-off (power-down mode)t AOFPDtAC (MIN)+ 2,000 2.5 xtCK +tAC (MAX) + 1,000tAC (MIN)+ 2,000 2.5 xtCK +tAC (MAX) + 1,000tAC (MIN)+ 2,000 2.5 xtCK +tAC (MAX) + 1,000tAC (MIN)+ 2,000 2.5 xtCK +tAC (MAX)+ 1,000psODT to power-down entry latency tANPD 3333t CK 37ODT power-down exit latency tAXPD8888tCK37ODT enable from MRS command tMOD 12121212ns37, 49P o w e r D o w nExit active power-down to READ command, MR[bit12=0]t XARD2222tCK37Exit active power-down to READ command, MR[bit12=1]tXARDS 7 - AL 7 - AL 6 - AL 6 - AL 37Exit precharge power-down to any non-READ command.t XP 2222t CK 37CKE minimum high/low timetCKE3333tCK32, 37Note:• AC specifi cation is based on MICRON components. Other DRAM manufactures specifi cations may be different.W3HG128M64EEU-D4ADVANCED* White Electronic DesignsNotes:1. All voltages referenced to VSS.2. Tests for AC timing, I CC, and electrical AC and DC characteristics may be conductedat nominal reference / supply voltage levels, but the related specifi cations anddevice operation are guaranteed for the full voltage range specifi ed. ODT is disabled for all measurements that are not ODT-specifi c.3. Outputs measured with equivalent load:4. AC timing and I CC tests may use a V IL-to-V IH swing of up to 1.0V in the testenvironment and parameter specifi cations are guaranteed for the specifi ed AC input levels under normal use conditions. The slew rate for the input signals used to test the device is 1.0V/ns for signals in the range between V IL (AC) and V IH (AC). Slew rates less than 1.0V/ns require the timing parameters to be derated as specifi ed.5. The AC and DC input level specifi cations are as defi ned in the SSTL_18 standard(i.e., the receiver will effectively switch as a result of the signal crossing the AC inputlevel and will remain in that state as long as the signal does not ring back above [below] the DC input LOW [HIGH] level).6. There are two sets of values listed for Command/Address: t ISa, t IHa and t ISb, t IHb. Thet ISa, t IHa values (for reference only) are equivalent to the baseline values of t ISb, t IHb at V REF when the slew rate is 1V/ns. The baseline values, t ISb, t IHb, are the JEDEC defi ned values, referenced from the logic trip points. t ISb is referenced from V IH (AC) for a rising signal and V IL (AC) for a falling signal, while t IHb is referenced from V IL (DC) for a rising signal and V IH (DC) for a falling signal. If the Command/Address slew rate is not equal to 1 V/ns, then the baseline values must be derated.7. The values listed are for the differential DQS strobe (DQS and DQS#) with adifferential slew rate of 2 V/ns (1 V/ns for each signal). There are two sets of values listed: t DSa. t DHa and t DSb, t DHb. The t DSa, t DHa values (for reference only) are equivalent to the baseline values of t DSb, t DHb at V REF when the slew rate is 2V/ns, differentially. The baseline values, t DSb, t DHb, are the JEDEC-defi ned values, referenced from the logic trip points. t DSb is referenced from V IH (AC) for a rising signal and V IL (AC) for a falling signal, while t DSb is referenced from V IL (DC) for a rising signal and V IH (DC) for a falling signal. If the differential DQS slew rate is not equal to 2 V/ns, then the baseline values must be derated. If the DQS differential strobe feature is not enabled, then the DQS strobe is single-ended, the baseline values not applicable, and timing is not referenced to the logic trip points. Single-ended DQS data timing is referenced to DQS crossing V REF.8. t HZ and t LZ transitions occur in the same access time windows as valid datatransitions. These parameters are not referenced to a specifi c voltage level, butspecify when the device output is no longer driving (t HZ) or begins driving (t LZ).9. This maximum value is derived from the referenced test load. t HZ (MAX) will prevailover t DQSCK (MAX) + t RPST (MAX) condition.10. t LZ (MIN) will prevail over a t DQSCK (MIN) + t RPRE (MAX) condition11. The intent of the "Don’t Care" state after completion of the postamble is the DQS-driven signal should either be high, low or High-Z and that any signal transitionwithin the input switching region must follow valid input requirements. That is if DQS transitions high (above V IH DC(min) then it must not transition low (below V IH(DC) prior to t DQSH(min).12. This is not a device limit. The device will operate with a negative value, but systemperformance could be degraded due to bus turnaround.13. It is recommended that DQS be valid (HIGH or LOW) on or before the WRITEcommand. The case shown (DQS going from High-Z to logic LOW) applies when no WRITEs were previously in progress on the bus. If a previous WRITE was inprogress, DQS could be HIGH during this time, depending on t DQSS.14. The refresh period is 64ms (commercial) or 32ms (industrial). This equates to anaverage refresh rate of 7.8125µs (commercial) or 3.9607µs (industrial). However, a REFRESH command must be asserted at least once every 70.3µs or t RFC (MAX).To ensure all rows of all banks are properly refreshed, 8,192 REFRESH commands must be issued every 64ms.15. Referenced to each output group: x4 = DQS with DQ0–DQ3; x8 = DQS withDQ0–DQ7; x16 = LDQS with DQ0–DQ7; and UDQS with DQ8–DQ15.16. CK and CK# input slew rate is referenced at 1 V/ns (2 V/ns if measureddifferentially).17. The data valid window is derived by achieving other specifi cations - t HP. (t CK/2),t DQSQ, and t QH (t QH = t HP - t QHS). The data valid window derates in directproportion to the clock duty cycle and a practical data valid window can be derived.18. READs and WRITEs with auto precharge are allowed to be issued beforet RAS(MIN) is satisfi ed since t RAS lockout feature is supported in DDR2 SDRAM.19. V IL/V IH DDR2 overshoot/undershoot.20. t DAL = (nWR) + (t RP/t CK). Each of these terms, if not already an integer, should berounded up to the next integer. t CK refers to the application clock period; nWR refers with t WR programmed to four clocks would have t DAL = 4 + (15ns/3.75ns) clocks =4 + (4) clocks = 8 clocks.21. The minimum internal READ to PRECHARGE time. This is the time from the last4-bit prefetch begins to when the PRECHARGE command can be issued. A 4-bit prefetch is when the READ command internally latches the READ so that data will output CL later. This parameter is only applicable when t RTP/(2x t CK) > 1, such as frequencies faster than 533 MHz when tRTP = 7.5ns. If tRTP/ (2x t CK) ≤ 1, then equation AL + BL/2 applies. tRAS (MIN) also has to be satisfi ed as well. The DDR2 SDRAM will automatically delay the internal PRECHARGE command until t RAS(MIN) has been satisfi ed.22. Operating frequency is only allowed to change during self refresh mode, prechargepower-down mode, and system reset condition.23. t DAL = (nWR) + (t RP/t CK): For each of the terms above, if not already an integer,round to the next highest integer. t CK refers to the application clock period;AC Operation Condition Notes: nWR refers to the t WR parameter stored in theMR[11,10,9]. Example: For -533Mb/s at t CK = 3.75 ns with t WR programmed to four clocks. t DAL = 4 + (15 ns/3.75 ns) clocks = 4 +(4) clocks = 8 clocks.24. ODT turn-off time t AOF (MIN) is when the device starts to turn off ODT resistance.ODT turn off time t AOF (MAX) is when the bus is in high-Z. Both are measured from t AOFD.25. This parameter has a two clock minimum requirement at any t CK.26. t DELAY is calculated from t IS + t CK + t IH so that CKE registration LOW isguaranteed prior to CK, CK# being removed in a system RESET condition.27. t ISXR is equal to t IS and is used for CKE setup time during self refresh exit.28. No more than 4 bank ACTIVE commands may be issued in a given t FAW(min)period. t RRD(min) restriction still applies. The t FAW(min) parameter applies to all 8 bank DDR2 devices, regardless of the number of banks already open or closed. 29. t RPA timing applies when the PRECHARGE(ALL) command is issued, regardlessof the number of banks already open or closed. If a single-bank PRECHARGEcommand is issued, t RP timing applies. t RPA(MIN) applies to all 8-bank DDR2devices.30. Value is minimum pulse width, not the number of clock registrations.31. This is applicable to Read cycles only. Write cycles generally require additional timedue to t WR during auto precharge.32. t CKE (MIN) of 3 clocks means CKE must be registered on three consecutivepositive clock edges. CKE must remain at the valid input level the entire time it takes to achieve the 3 clocks of registration. Thus, after any CKE transition, CKE may not transition from its valid level during the time period of t IS + 2 x t CK + t IH.33. This parameter is not referenced to a specifi c voltage level, but specifi ed when thedevice output is no longer driving (t RPST) or beginning to drive (t RPRE).34. When DQS is used single-ended, the minimum limit is reduced by 100ps.35. The half-clock of t AOFD's 2.5 t CK assumes a 50/50 clock duty cycle. This half-clockvalue must be derated by the amount of half-clock duty cycle error. For example, if the clock duty cycle was 47/53, t AOFD would actually be 2.5 - 0.03, or 2.47 for t AOF (MIN) and 2.5 + 0.03 or 2.53 for t AOF (MAX).36. The clock’s t CK AVG is the average clock over any 200 consecutive clocks and。

MEMORY存储芯片MT48G4M32LFFC-10IT中文规格书

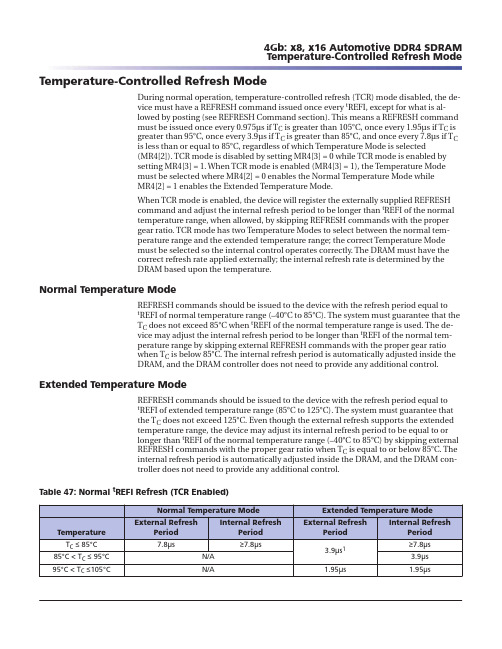

Temperature-Controlled Refresh ModeDuring normal operation, temperature-controlled refresh (TCR) mode disabled, the de-vice must have a REFRESH command issued once every t REFI, except for what is al-lowed by posting (see REFRESH Command section). This means a REFRESH commandmust be issued once every 0.975μs if T C is greater than 105°C, once every 1.95μs if T C isgreater than 95°C, once every 3.9μs if T C is greater than 85°C, and once every 7.8μs if T Cis less than or equal to 85°C, regardless of which Temperature Mode is selected(MR4[2]). TCR mode is disabled by setting MR4[3] = 0 while TCR mode is enabled bysetting MR4[3] = 1. When TCR mode is enabled (MR4[3] = 1), the Temperature Modemust be selected where MR4[2] = 0 enables the Normal Temperature Mode whileMR4[2] = 1 enables the Extended Temperature Mode.When TCR mode is enabled, the device will register the externally supplied REFRESHcommand and adjust the internal refresh period to be longer than t REFI of the normaltemperature range, when allowed, by skipping REFRESH commands with the propergear ratio. TCR mode has two Temperature Modes to select between the normal tem-perature range and the extended temperature range; the correct Temperature Modemust be selected so the internal control operates correctly. The DRAM must have thecorrect refresh rate applied externally; the internal refresh rate is determined by theDRAM based upon the temperature.Normal Temperature ModeREFRESH commands should be issued to the device with the refresh period equal tot REFI of normal temperature range (–40°C to 85°C). The system must guarantee that theT C does not exceed 85°C when t REFI of the normal temperature range is used. The de-vice may adjust the internal refresh period to be longer than t REFI of the normal tem-perature range by skipping external REFRESH commands with the proper gear ratiowhen T C is below 85°C. The internal refresh period is automatically adjusted inside theDRAM, and the DRAM controller does not need to provide any additional control. Extended Temperature ModeREFRESH commands should be issued to the device with the refresh period equal tot REFI of extended temperature range (85°C to 125°C). The system must guarantee thatthe T C does not exceed 125°C. Even though the external refresh supports the extendedtemperature range, the device may adjust its internal refresh period to be equal to orlonger than t REFI of the normal temperature range (–40°C to 85°C) by skipping externalREFRESH commands with the proper gear ratio when T C is equal to or below 85°C. Theinternal refresh period is automatically adjusted inside the DRAM, and the DRAM con-troller does not need to provide any additional control.Table 47: Normal t REFI Refresh (TCR Enabled)Fine Granularity Refresh ModeMode Register and Command Truth TableThe REFRESH cycle time (t RFC) and the average refresh interval (t REFI) can be pro-grammed by the MRS command. The appropriate setting in the mode register will set asingle set of REFRESH cycle times and average refresh interval for the device (fixedmode), or allow the dynamic selection of one of two sets of REFRESH cycle times andaverage refresh interval for the device (on-the-fly mode [OTF]). OTF mode must be ena-bled by MRS before any OTF REFRESH command can be issued.Table 48: MRS DefinitionThere are two types of OTF modes (1x/2x and 1x/4x modes) that are selectable by pro-gramming the appropriate values into the mode register. When either of the two OTFmodes is selected, the device evaluates the BG0 bit when a REFRESH command is is-sued, and depending on the status of BG0, it dynamically switches its internal refreshconfiguration between 1x and 2x (or 1x and 4x) modes, and then executes the corre-sponding REFRESH operation.Table 49: REFRESH Command Truth Tablet REFI and t RFC ParametersThe default refresh rate mode is fixed 1x mode where REFRESH commands should beissued with the normal rate; that is, t REFI1 = t REFI(base) (for T C≤ 85°C), and the dura-tion of each REFRESH command is the normal REFRESH cycle time (t RFC1). In 2xmode (either fixed 2x or OTF 2x mode), REFRESH commands should be issued to thedevice at the double frequency (t REFI2 = t REFI(base)/2) of the normal refresh rate. In 4xmode, the REFRESH command rate should be quadrupled (t REFI4 = t REFI(base)/4). PerFigure 84: TCR Mode Example1Controller85°C T C 95°C T C 85°C REFRESHExternal t REFI3.9μs Internal t REFI 3.9μs Internal t REFI 7.8μs REFRESH REFRESH REFRESH REFRESH REFRESH REFRESHREFRESH REFRESHREFRESH REFRESH REFRESH REFRESH REFRESH REFRESH REFRESH REFRESH REFRESH Note: 1.TCR enabled with Extended Temperature Mode selected.。

W3EG6466S-BD4中文资料

White Electronic DesignsW3EG6466S-AD4-BD4PRELIMINARY*512MB – 2x32Mx64 DDR SDRAM UNBUFFERED, w/PLLDESCRIPTIONThe W3EG 6466S is a 2x32Mx64 Double Data Rate SDRAM memory module based on 512Mb DDR SDRAM components. The module consists of sixteen 32Mx8 components as eight 64Mx8 stacked DDR SDRAMs in 66 pin TSOP packages mounted on a 200 pin FR4 substrate.Synchronous design allows precise cycle control with the use of system clock. Data I/O transactions are possible on both edges and Burst Lengths allow the same device to be useful for a variety of high bandwidth, high performance memory system applications.* T his product is under development, is not qualifi ed or characterized and is subject to change without notice.FEATURESDDR200, DDR266 and DDR333• JEDEC design specifi cations Double-data-rate architecture Bi-directional data strobes (DQS) Differential clock inputs (CK & CK#) Programmable Read Latency 2,2.5 (clock) Programmable Burst Length (2,4,8)Programmable Burst type (sequential & interleave) Edge aligned data output, center aligned data input Auto and self refresh Serial presence detect Dual RankPower supply: 2.5V ± 0.20VJEDEC standard 200 pin SO-DIMM package• Package height options: AD4: 35.5mm (1.38") BD4: 31.75mm (1.25")NOTE: C onsult factory for availability of:• RoHS compliant products • Vendor source control options • Industrial temperature optionOPERATING FREQUENCIESDDR333 @CL=2.5DDR266 @CL=2DDR266 @CL=2.5DDR200 @CL=2Clock Speed 166MHz 133MHz 133MHz 100MHz CL-t RCD -t RP2.5-3-32-2-22.5-3-32-2-2White Electronic DesignsW3EG6466S-AD4-BD4PRELIMINARYPIN NAMESA0 – A12A CC ress input (Multiplexed)BA0-BA1Bank Select A CC ress DQ0-DQ63Data Input/OutputDQS0-DQS7Data Strobe Input/Output CK0Clock Input CK0#Clock inputCKE0-CKE1Clock Enable input CS0#-CS1#Chip select Input RAS#Row A CC ress Strobe CAS#Column A CC ress Strobe WE#Write Enable DQM0-DQM7Data-In Mask V CC Power Supply V SS GroundV REF Power Supply for Reference V CCSPD Serial EEPROM Power Supply SDA Serial data I/O SCL Serial clockSA0-SA2A CC ress in EEPROM V CCID V CC Identifi cation Flag NCNo Connect* Not UsedPIN CONFIGURATIONPin Symbol Pin Symbol Pin Symbol Pin Symbol 1V REF 51V SS 101A9151DQ422V REF 52V SS 102A8152DQ463V SS 53DQ19103V SS 153DQ434V SS 54DQ23104V SS 154DQ475DQ055DQ24105A7155V CC 6DQ456DQ28106A6156V CC 7DQ157V CC 107A5157V CC 8DQ558V CC 108A4158NC 9V CC 59DQ25109A3159V SS 10V CC 60DQ29110A2160NC 11DQS061DQS3111A1161V SS 12DQM062DQM3112A0162V SS 13DQ263V SS 113V CC 163DQ4814DQ664V SS 114V CC 164DQ5215V SS 65DQ26115A10/AP 165DQ4916V SS 66DQ30116BA1166DQ5317DQ367DQ27117BA0167V CC 18DQ768DQ31118RAS#168V CC 19DQ869V CC 119WE#169DQS620DQ1270V CC 120CAS#170DQM621V CC 71NC 121CS0#171DQ5022V CC 72NC 122CS1#172DQ5423DQ973NC 123NC 173V SS 24DQ1374NC 124NC 174V SS 25DQS175V SS 125V SS 175DQ5126DQM176V SS 126V SS 176DQ5527V SS 77DQS8127DQ32177DQ5628V SS 78DQM8128DQ36178DQ6029DQ1079NC 129DQ33179V CC 30DQ1480NC 130DQ37180V CC 31DQ1181V CC 131V CC 181DQ5732DQ1582V CC 132V CC 182DQ6133V CC 83NC 133DQS4183DQS734V CC 84NC 134DQM4184DQM735CK085NC 135DQ34185V SS 36V CC 86NC 136DQ38186V SS 37CK0#87V SS 137V SS 187DQ5838V SS 88V SS 138V SS 188DQ6239V SS 89NC 139DQ35189DQ5940V SS 90V SS 140DQ39190DQ6341DQ1691NC 141DQ40191V CC 42DQ2092V CC 142DQ44192V CC 43DQ1793V CC 143V CC 193SDA 44DQ2194V CC 144V CC 194SA045V CC 95CKE1145DQ41195SCL 46V CC 96CKE0146DQ45196SA147DQS297NC 147DQS5197V CCSPD 48DQM298NC 148DQM5198SA249DQ1899A12149V SS 199V CCID 50DQ22100A11150V SS200NCWhite Electronic Designs W3EG6466S-AD4-BD4PRELIMINARY FUNCTIONAL BLOCK DIAGRAMWhite Electronic DesignsW3EG6466S-AD4-BD4PRELIMINARYABSOLUTE MAXIMUM RATINGSParameterSymbol Value Units Voltage on any pin relative to V SS V IN , V OUT -0.5 to 3.6V Voltage on V CC supply relative to V SS V CC , V CCQ -1.0 to 3.6V Storage Temperature T STG -55 to +150°C Power Dissipation P D 16W Short Circuit CurrentI OS50mANote:Permanent device damage may occur if "ABSOLUTE MAXIMUM RATINGS" are exceeded. Functional operation should be restricted to recommended operating condition.Exposure to higher than recommended voltage for extended periods of time could affect device reliability.DC CHARACTERISTICS0°C ≤ T A ≤ 70°C, V CC = 2.5V ± 0.2VCAPACITANCET A = 25°C, f = 1MHz, V CC = 3.3V, V REF =1.4V ± 200mVParameter Symbol Min Max Unit Supply Voltage V CC 2.3 2.7V Supply Voltage V CCQ 2.3 2.7V Reference Voltage V REF V CCQ/2 - 50mV V CCQ/2 + 50mV V Termination Voltage V TT V REF - 0.04V REF + 0.04V Input High Voltage V IH V REF + 0.15V CCQ + 0.3V Input Low Voltage V IL -0.3V REF - 0.15V Output High Voltage V OH V TT + 0.76—V Output Low VoltageV OL—V TT - 0.76VParameterSymbol Max Unit Input Capacitance (A0-A12)C IN150pF Input Capacitance (RAS#, CAS#, WE#)C IN250pF Input Capacitance (CKE0, CKE1)C IN326pF Input Capacitance (CK0,CK0#)C IN4 5.5pF Input Capacitance (CS0#, CS1#)C IN526pF Input Capacitance (DQM0-DQM8)C IN613pF Input Capacitance (BA0-BA1)C IN750pF Data input/output capacitance (DQ0-DQ63)(DQS)C OUT13pFWhite Electronic Designs W3EG6466S-AD4-BD4PRELIMINARYI DD SPECIFICATIONS AND TEST CONDITIONS0°C ≤ T A ≤ 70°C, V CCQ = 2.5V ±0.2V, V CC = 2.5V ±0.2VDDR333@CL=2.5DDR266@CL=2, 2.5DDR200@CL=2 Parameter Symbol Conditions Max Max Max UnitsOperating Current I DD0One device bank; Active - Precharge;t RC=t RC(MIN); t CK=t CK(MIN); DQ,DM and DQSinputs changing once per clock cycle; Addressand control inputs changing once every twocycles.160014401360mAOperating Current I DD1One device bank; Active-Read-Precharge;Burst = 2; t RC=t RC(MIN);t CK=t CK(MIN); Iout =0mA; Address and control inputs changingonce per clock cycle.180016401560mAPrecharge Power-Down Standby Current I DD2PAll device banks idle; Power- down mode;t CK=t CK(MIN); CKE=(low)484848mAIdle Standby Current I DD2F CS# = High; All device banks idle;t CK=t CK(MIN); CKE = high; Address and othercontrol inputs changing once per clock cycle.Vin = Vref for DQ, DQS and DM.400320320mAActive Power-Down Standby Current I DD3POne device bank active; Power-down mode;t CK(MIN); CKE=(low)560480480mAActive Standby Current I DD3N CS# = High; CKE = High; One devicebank; Active-Precharge; t RC=t RAS(MAX);t CK=t CK(MIN); DQ, DM and DQS inputschanging twice per clock cycle; Address andother control inputs changing once per clockcycle.880720720mAOperating Current I DD4R Burst = 2; Reads; Continous burst; Onedevice bank active;Address and control inputschanging once per clock cycle; t CK=t CK(MIN);Iout = 0mA.216018401840mAOperating Current I DD4W Burst = 2; Writes; Continous burst; Onedevice bank active; Address and control inputschanging once per clock cycle; t CK=t CK(MIN);DQ,DM and DQS inputs changing twice perclock cycle.216018001800mAAuto Refresh Current I DD5t RC=t RC(MIN)224020002000mA Self Refresh Current I DD6CKE ≤ 0.2V484848mAOperating Current I DD7A Four bank interleaving Reads (BL=4) with autoprecharge with t RC=t RC (MIN); t CK=t CK(MIN);Address and control inputs change onlyduring Active Read or Write commands.312029602720mA* For DDR333 consult factoryWhite Electronic Designs W3EG6466S-AD4-BD4PRELIMINARYI DD1 : OPERATING CURRENT : ONE BANK1. Typical Case : V CC=2.5V, T=25°C2. Worst Case : V CC=2.7V, T=10°C3. Only one bank is accessed with t RC (min), BurstMode, Address and Control inputs on NOP edgeare changing once per clock cycle. I OUT = 0mA4. Timing Patterns :• DDR200 (100 MHz, CL=2) : t CK=10ns, CL2, BL=4, t RCD=2*t CK, t RAS=5*t CKRead : A0 N R0 N N P0 N A0 N - repeat thesame timing with random address changing;50% of data changing at every burst• DDR266 (133MHz, CL=2.5) : t CK=7.5ns,CL=2.5, BL=4, t RCD=3*t CK, t RC=9*t CK, t RAS=5*t CKRead : A0 N N R0 N P0 N N N A0 N - repeatthe same timing with random addresschanging; 50% of data changing at every burst • DDR266 (133MHz, CL=2) : t CK=7.5ns, CL=2, BL=4, t RCD=3*t CK, t RC=9*t CK, t RAS=5*t CKRead : A0 N N R0 N P0 N N N A0 N - repeatthe same timing with random addresschanging; 50% of data changing at every burst • DDR333 (166MHz, CL=2.5) : t CK=6ns, BL=4, t RCD=10*t CK, t RAS=7*t CKRead : A0 N N R0 N P0 N N N A0 N - repeatthe same timing with random addresschanging; 50% of data changing at every burst I DD7A : OPERATING CURRENT : FOUR BANKS1. Typical Case : V CC=2.5V, T=25°C2. Worst Case : V CC=2.7V, T=10°C3. Four banks are being interleaved with t RC (min),Burst Mode, Address and Control inputs on NOPedge are not changing. Iout=0mA4. Timing Patterns :• DDR200 (100 MHz, CL=2) : t CK=10ns, CL2, BL=4, t RRD=2*t CK, t RCD=3*t CK, Read withAutoprechargeRead : A0 N A1 R0 A2 R1 A3 R2 A0 R3 A1 R0- repeat the same timing with random addresschanging; 100% of data changing at everyburst• DDR266 (133MHz, CL=2.5) : t CK=7.5ns,CL=2.5, BL=4, t RRD=3*t CK, t RCD=3*t CKRead with AutoprechargeRead : A0 N A1 R0 A2 R1 A3 R2 N R3 A0 NA1 R0 - repeat the same timing with randomaddress changing; 100% of data changing atevery burst• DDR266 (133MHz, CL=2) : t CK=7.5ns, CL2=2, BL=4, t RRD=2*t CK, t RCD=2*t CKRead : A0 N A1 R0 A2 R1 A3 R2 N R3 A0 NA1 R0 - repeat the same timing with randomaddress changing; 100% of data changing atevery burst• DDR333 (166MHz, CL=2.5) : t CK=6ns,BL=4, t RRD=3*t CK, t RCD=3*t CK, Read withAutoprechargeRead : A0 N A1 R0 A2 R1 A3 R2 N R3 A0 NA1 R0 - repeat the same timing with randomaddress changing; 100% of data changing atevery burstDETAILED TEST CONDITIONS FOR DDR SDRAM I DD1 & I DD7ALegend : A = Activate, R = Read, W = Write, P = Precharge, N = NOPA (0-3) = Activate Bank 0-3R (0-3) = Read Bank 0-3White Electronic Designs W3EG6466S-AD4-BD4PRELIMINARYDDR SDRAM COMPONENT ELECTRICAL CHARACTERISTICS AND RECOMMENDED ACOPERATING CONDITIONSAC CHARACTERISTICS335262265/202UNITS NOTES PARAMETER SYMBOL MIN MAX MIN MAX MIN MAXAccess window of DQs from CK/CK#t AC-0.70+0.70-0.75+0.75-0.75+0.75nsCK high-level width t CH0.450.550.450.550.450.55t CK26 CK low-level width t CL0.450.550.450.550.450.55t CK26 Clock cycle time CL = 2.5t CK (2.5)6137.5137.513ns39, 44CL = 2t CK (2)7.5137.5137.5/1013ns39, 44 DQ and DM input hold time relative to DQS t DH0.450.50.5ns23, 27 DQ and DM input setup time relative to DQS t DS0.450.50.5ns23, 27 DQ and DM input pulse width (for each input)t DIPW 1.75 1.75 1.75ns27 Access window of DQS from CK/CK#t DQSCK-0.60+0.60-0.75+0.75-0.75+0.75nsDQS input high pulse width t DQSH0.350.350.35t CKDQS input low pulse width t DQSL0.350.350.35t CKDQS-DQ skew, DQS to last DQ valid, per group, per access t DQSQ0.40.50.5ns22, 23 Write command to fi rst DQS latching transition t DQSS0.75 1.250.75 1.250.75 1.25t CKDQS falling edge to CK rising - setup time t DSS0.200.200.20t CKDQS falling edge from CK rising - hold time t DSH0.200.200.20t CKHalf clock period t HP t CH,t CL t CH,t CL t CH,t CL ns8 Data-out high-impedance window from CK/CK#t HZ+0.70+0.75+0.75ns16, 36 Data-out low-impedance window from CK/CK#t LZ-0.70-0.75-0.75ns16, 36 Address and control input hold time (fast slew rate)t IHF0.750.900.90ns12 Address and control input setup time (fast slew rate)t ISF0.750.90.900ns12 Address and control input hold time (slow slew rate)t IHS0.811ns12 Address and control input setup time (slow slew rate)t ISS0.811ns12 Address and Control input pulse width (for each input)t IPW 2.2 2.2 2.2nsLOAD MODE REGISTER command cycle time t MRD121515nsWhite Electronic Designs W3EG6466S-AD4-BD4PRELIMINARYDDR SDRAM COMPONENT ELECTRICAL CHARACTERISTICS AND RECOMMENDED ACOPERATING CONDITIONS (Continued)AC CHARACTERISTICS335262265/202UNITS NOTES PARAMETER SYMBOL MIN MAX MIN MAX MIN MAXDQ-DQS hold, DQS to fi rst DQ to go non-valid, per access t QH t HP - t QHS t HP - t QHS t HP - t QHS ns22, 23 Data hold skew factor t QHS0.750.750.75nsACTIVE to PRECHARGE command t RAS4270,00040120,00040120,000ns31, 47 ACTIVE to READ with Auto precharge command t RAP151520nsACTIVE to ACTIVE/AUTO REFRESH command period t RC606065nsAUTO REFRESH command period t RFC727575ns42 ACTIVE to READ or WRITE delay t RCD151520ns PRECHARGE command period t RP151520nsDQS read preamble t RPRE0.9 1.10.9 1.10.9 1.1t CK37 DQS read postamble t RPST0.40.60.40.60.40.6t CK37 ACTIVE bank a to ACTIVE bank b command t RRD121515nsDQS write preamble t WPRE0.250.250.25t CKDQS write preamble setup time t WPRES000ns18, 19 DQS write postamble t WPST0.40.60.40.60.40.6t CK17 Write recovery time t WR151515nsInternal WRITE to READ command delay t WTR111t CKData valid output window NA t QH -t DQSQ t QH -t DQSQ t QH -t DQSQ ns22 REFRESH to REFRESH command interval t REFC70.370.370.3µs21 Average periodic refresh interval t REFI7.87.87.8µs21 Terminating voltage delay to VDD t VTD000nsExit SELF REFRESH to non-READ command t XSNR757575nsExit SELF REFRESH to READ command t XSRD200200200t CKWhite Electronic Designs W3EG6466S-AD4-BD4PRELIMINARY Notes1. All voltages referenced to V SS.2. Tests for AC timing, I DD, and electrical AC and DC characteristics may be conductedat nominal reference/supply voltage levels, but the related specifi cations and device operation are guaranteed for the full voltage range specifi ed.3. Outputs measured with equivalent load:Output(V OUT)4. AC timing and I DD tests may use a V IL-to-V IH swing of up to 1.5V in the testenvironment, but input timing is still referenced to V REF (or to the crossing point for CK/CK#), and parameter specifi cations are guaranteed for the specifi ed AC input levels under normal use conditions. The mini-mum slew rate for the input signals used to test the device is 1V/ns in the range between V IL(AC) and V IH(AC).5. The AC and DC input level specifi cations are as defi ned in the SSTL_2 Standard(i.e., the receiver will effectively switch as a result of the signal crossing the ACinput level, and will remain in that state as long as the signal does not ring backabove [below] the DC input LOW [HIGH] level).6. V REF is expected to equal V CCQ/2 of the transmitting device and to track variationsin the DC level of the same. Peak-to-peak noise (non-common mode) on V REF may not exceed ±2 percent of the DC value. Thus, from V CCQ/2, V REF is allowed ±25mV for DC error and an additional ±25mV for AC noise. This measurement is to betaken at the nearest V REF bypass capacitor.7. V TT is not applied directly to the device. V TT is a system supply for signal terminationresistors, is expected to be set equal to V REF and must track variations in the DC level of V REF.8. I DD is dependent on output loading and cycle rates. Specifi ed values are obtainedwith mini-mum cycle time at CL = 2 for 262, 263, and 202, CL = 2.5 for 335 and 265 with the outputs open.9. Enables on-chip refresh and address counters.10. I DD specifi cations are tested after the device is properly initialized, and is averagedat the defi ned cycle rate.11. This parameter is sampled. V CC = +2.5V ±0.2V, V CCQ = +2.5V ±0.2V, V REF = V SS, f= 100 MHz, = 25°C, V OUT(DC) = V CCQ/2, V OUT (peak to peak) T A = 0.2V. DM input is grouped with I/O pins, refl ecting the fact that they are matched in loading.12. For slew rates less than 1 V/ns and greater than or equal to 0.5 V/ns. If slew rateis less than 0.5 V/ns, timing must be derated: t IS has an additional 50ps per each 100mV/ns reduction in slew rate from 500mV/ns, while t IH is unaffected. If slew rate exceeds 4.5 V/ns, functionality is uncertain. For 335, slew rates must be ≥ 0.5 V/ns.13. The CK/CK# input reference level (for timing referenced to CK/CK#) is the point atwhich CK and CK# cross; the input reference level for signals other than CK/CK# is V REF.14. Inputs are not recognized as valid until V REF stabilizes. Exception: during the periodbefore V REF stabilizes, CKE < 0.3 x V CCQ is recognized as LOW.15. The output timing reference level, as measured at the timing reference pointindicated in Note 3, is V TT.16. t HZ and t LZ transitions occur in the same access time windows as valid datatransitions. These parameters are not referenced to a specifi c voltage level, butspecify when the device output is no longer driving (HZ) or begins driving (LZ).17. The intent of the Don’t Care state after completion of the postamble is the DQS-driven signal should either be high, low, or high-Z and that any signal transitionwithin the input switching region must follow valid input requirements. That is, ifDQS transitions high (above V IH DC (MIN) then it must not transition low (below V IH DC) prior to t DQSH (MIN).18. This is not a device limit. The device will operate with a negative value, but systemperformance could be degraded due to bus turnaround.19. It is recommended that DQS be valid (HIGH or LOW) on or before the WRITEcommand. The case shown (DQS going from High-Z to logic LOW) applies when no WRITEs were previously in progress on the bus. If a previous WRITE was in progress, DQS could be HIGH during this time, depending on t DQSS.20. MIN (t RC or t RFC) for I DD measurements is the smallest multiple of t CK that meetsthe minimum absolute Value for the respective parameter. t RAS (MAX) for I DDmeasurements is the largest multiple of t CK that meets the maximum absolute value for t RAS.21. The refresh period 64ms. This equates to an aver-age refresh rate of 7.8125µs.However, an AUTO REFRESH command must be asserted at least once every70.3µs; burst refreshing or posting by the DRAM controller greater than eightrefresh cycles is not allowed.22. The valid data window is derived by achieving other specifi cations: t HP (t CK/2), t DQSQ,and t QH (t QH = t HP - t QHS). The data valid window derates directly porportional with the clock duty cycle and a practical data valid window can be derived. The clock is allowed a maximum duty cycle variation of 45/55, beyond which functionality is uncertain. Figure 8, Derating Data Valid Window, shows derating curves for duty cycles ranging between 50/50 and 45/55.23. Each byte lane has a corresponding DQS.24. This limit is actually a nominal value and does not result in a fail value. CKE isHIGH during REFRESH command period (t RFC [MIN]) else CKE is LOW (i.e., during standby).25. To maintain a valid level, the transitioning edge of the input must:a. S ustain a constant slew rate from the current AC level through to the target AClevel, V IL(AC) or V IH(AC).b. R each at least the target AC level.After the AC target level is reached, continueto maintain at least the target DC level, V IL(DC) or V IH(DC).26. JEDEC specifi es CK and CK# input slew rate must be ≥ 1V/ns (2V/ns differentially).27. DQ and DM input slew rates must not deviate from DQS by more than 10 percent.If the DQ/ DM/DQS slew rate is less than 0.5V/ns, timing must be derated: 50ps must be added to t DS and t DH for each 100mv/ns reduction in slew rate. If slew rate exceeds 4V/ns, functionality is uncertain. For 335, slew rates must be ≥ 0.5 V/ns.28. V CC must not vary more than 4 percent if CKE is not active while any bank is active.29. The clock is allowed up to ±150ps of jitter. Each timing parameter is allowed to varyby the same amount.30. t HP min is the lesser of t CL minimum and t CH minimum actually applied to the deviceCK and CK# inputs, collectively during bank active.31. READs and WRITEs with auto precharge are not allowed to be issued untilt RAS(MIN) can be satisfi ed prior to the internal precharge command being issued. 32. Any positive glitch must be less than 1/3 of the clock and not more than +400mV or2.9V, whichever is less. Any negative glitch must be less than 1/3 of the clock cycleand not exceed either -300mV or 2.2V, whichever is more positive.White Electronic Designs W3EG6466S-AD4-BD4PRELIMINARY33. The voltage levels used are derived from a mini-mum V CC level and the referencedtest load. In practice, the voltage levels obtained from a properly terminated bus will provide signifi cantly different voltage values.34. V IH overshoot: V IH (MAX) = V CCQ + 1.5V for a pulse width ≤ 3ns and the pulse widthcan not be greater than 1/3 of the cycle rate. V IL undershoot: V IL (MIN) = -1.5V for a pulse width ≤ 3ns and the pulse width can not be greater than 1/3 of the cycle rate.35. V CC and V CCQ must track each other.36. t HZ (MAX) will prevail over t DQSCK (MAX) + t RPST (MAX) condition. t LZ (MIN) willprevail over t DQSCK (MIN) + t RPRE (MAX) condition.37. t RPST end point and t RPRE begin point are not referenced to a specifi c voltage levelbut specify when the device output is no longer driving (t RPST), or begins driving(t RPRE).38. During Initialization, V CCQ, V TT, and V REF must be equal to or less than V CC + 0.3V.Alternatively, V TT may be 1.35V maximum during power up, even if V CC/V CCQ are0.0V, provided a minimum of 42 0 of series resistance is used between the V TTsupply and the input pin.39. The current part operates below the slowest JEDEC operating frequency of 83MHz. As such, future die may not refl ect this option.40. Random addressing changing and 50 percent of data changing at every transfer.41. Random addressing changing and 100 percent of data changing at every transfer.42. CKE must be active (high) during the entire time a refresh command is executed.That is, from the time the AUTO REFRESH command is registered, CKE must be active at each rising clock edge, until tREF later.43. I DD2N specifi es the DQ, DQS, and DM to be driven to a valid high or low logic level.I DD2Q is similar to I DD2F except I DD2Q specifi es the address and control inputs toremain stable. Although I DD2F, I DD2N, and I DD2Q are similar, I DD2F is “worst case.”44. Whenever the operating frequency is altered, not including jitter, the DLL is requiredto be reset. This is followed by 200 clock cycles.45. Leakage number refl ects the worst case leakage possible through the module pin,not what each memory device contributes.46. When an input signal is HIGH or LOW, it is defi ned as a steady state logic HIGH orLOW.47. The 335 speed grade will operate with t RAS (MIN) = 40ns and t RAS (MAX) =120,000ns at any slower frequency.White Electronic DesignsW3EG6466S-AD4-BD4PRELIMINARYPACKAGE DIMENSIONS FOR AD4ORDERING INFORMATION FOR AD4Part Number SpeedHeight*W3EG6466S335AD4166MHz/333Mbps, CL=2.535.5 (1.38)W3EG6466S262AD4133MHz/266Mbps, CL=235.5 (1.38)W3EG6466S265AD4133MHz/266Mbps, CL=2.535.5 (1.38)W3EG6466S202AD4100MHz/200Mbps, CL=235.5 (1.38)NOTES:• Consult Factory for availability of RoHS compliant products. (G = RoHS Compliant) • V endor specifi c part numbers are used to provide memory components source control. The place holder for this is shown as lower case “x” in the part numbers above and is tobe replaced with the respective vendors code. Consult factory for qualifi ed sourcing options. (M = Micron, S = Samsung & consult factory for others) • Consult factory for availability of industrial temperature (-40°C to 85°C) option* ALL DIMENSIONS ARE IN MILIMETERS AND (INCHES)White Electronic DesignsW3EG6466S-AD4-BD4PRELIMINARYPACKAGE DIMENSIONS FOR BD4ORDERING INFORMATION FOR BD4Part Number SpeedHeight*W3EG6466S335BD4166MHz/333Mbps, CL=2.531.75 (1.25)W3EG6466S262BD4133MHz/266Mbps, CL=231.75 (1.25)W3EG6466S265BD4133MHz/266Mbps, CL=2.531.75 (1.25)W3EG6466S202BD4100MHz/200Mbps, CL=231.75 (1.25)NOTES:• Consult Factory for availability of RoHS compliant products. (G = RoHS Compliant) • V endor specifi c part numbers are used to provide memory components source control. The place holder for this is shown as lower case “x” in the part numbers above and is tobe replaced with the respective vendors code. Consult factory for qualifi ed sourcing options. (M = Micron, S = Samsung & consult factory for others) • Consult factory for availability of industrial temperature (-40°C to 85°C) option* ALL DIMENSIONS ARE IN MILIMETERS AND (INCHES)White Electronic Designs W3EG6466S-AD4-BD4PRELIMINARYDocument Title512MB – 64Mx64 DDR SDRAM UNBUFFERED, w/PLLRevision HistoryRev #History Release Date StatusRev A Created7-21-02Advanced8-04Preliminary Rev 00.1 Upated I DD specs.0.2 Added AD4 and BD4 package options0.3 Added document title page0.4 Removed "ED" from part number0.5 Moved from advanced to preliminary11-04Preliminary Rev 1 1.0 Upated I DD and CAP specs.1.1 Added AC specs1-05Preliminary Rev 2 2.1 Added lead-free and RoHS notes2.2 Added source control notes2.3 Added industrial temperature options。

配置

100台

电脑型号 X86 兼容 台式电脑

操作系统 Windows XP 专业版 32位 SP3 ( DirectX 9.0c )

处理器 AMD Athlon(速龙) II X4 640பைடு நூலகம்四核

主板 华硕 M4A87T PLUS (ATI RX780/RX790(AMD 770/870) 芯片组)

50台

电脑型号 X86 兼容 台式电脑

操作系统 Windows XP 专业版 32位 SP3 ( DirectX 9.0c )

处理器 AMD Athlon(速龙) II X4 640 四核

主板 华硕 M4A87T PLUS (ATI RX780/RX790(AMD 770/870) 芯片组)

内存 2 GB ( 宇瞻 DDR2 800MHz )

显卡 Nvidia Geforce 9600 GT ( 512 MB / 七彩虹 )

显示器 瀚视奇 HSD2275 Hanns.G HH241 ( 23.4 英寸 ) (钢化玻璃)

声卡 瑞昱 ALC662 @ 英特尔 ICH10 高保真音频

网卡 瑞昱 RTL8168E PCI-E Gigabit Ethernet NIC / 华硕

内存制造日期 宇瞻 2011 年 10 月

主板制造日期 华硕 2011 年 05 月 31 日

显卡制造日期 镭风 2011 年 05 月 09 日

显示器制造日期 HannsG 2011 年 09 月

电脑型号 精英 P43T-A2 台式电脑

操作系统 Windows XP 专业版 32位 SP3 ( DirectX 9.0c )

W78E58中文

W78E58B规格书8位微控制器目录:1.概述 (3)2.特性 (3)3.管脚配置 (4)4.管脚描述 (5)5.方块图 (7)6.功能描述 (8)6.1 RAM (8)6.2 定时器0,1,2 (8)6.3 时钟 (9)6.4 晶体振荡器 (9)6.5 外部时钟 (9)6.6 电源管理 (9)6.7 减少EMI辐射 (9)6.8 复位 (9)6.9 I/O口4 (11)6.10 INT2/INT3 (12)6.11 P4口基地址寄存器 (14)6.12 在线编程(ISP)模式 (15)6.13 在线编程控制寄存器(CHPCON) (17)6.14 F04KBOOT 模式(从LDROM启动) (18)7.保密位 (22)7.1 锁止位 (22)禁止 (22)7.2 MOVC7.3 加密 (22)8.电气特性 (23)8.1 绝对最大额定值 (23)8.2 DC特性 (23)出版日期: December 22, 20048.3 AC特性 (25)8.3.1时钟输入波形 (25)8.3.2程序读取周期 (26)8.3.3数据读取周期 (26)8.3.4数据写周期 (27)8.3.5端口访问周期 (27)9.时序波形图 (28)9.1 程序读取周期 (28)9.2 数据读周期 (28)9.3 数据写周期 (29)9.4 端口访问周期 (29)10.典型应用电路 (30)10.1 扩展的外部程序存储器和石英晶体 (30)10.2 扩展的外部程序存储器和振荡器 (31)11.封装尺寸 (32)11.1 DIP40 (32)11.2 44 管脚PLCC (33)11.3 44 管脚PQFP (34)12.应用指南 (35)12.1 ISP 软件编程示例: (35)13.文件版本描述 (42)1. 概述W78E58B是具有带ISP功能的Flash EPROM的低功耗8位微控制器;ISP功能的Flash EPROM可用于固件升级。

专业音频处理器 2X4 3X6 4X8(Dante 可选)使用说明书

使用说明书V1.2专业音频处理器2X4/3X6/4X8(Dante可选)目录第1章简介---------------------------------------------3第2章技术参数--------------------------------------------3第3章功能结构---------------------------------------------5第4章上位机软件简介----------------------------------------7第5章软件安装----------------------------------------------7第6章软件界面说明------------------------------------------9第7章功能界面介绍------------------------------------------14第1章简介DAP是数字音频处理的简称,DAP系列产品是一种可以实现多种DSP功能的专业音箱处理器,本系列产品集成压缩器、限幅器、分频器、延时器、均衡器、混音矩阵,可以通过精美直观的Mconsole软件快速地进行调试和监控,为专业音响扩音系统的构建和操作提供了广阔的操作空间。

D4表示配置了4路Dante 网络音频输入和输出接口的功能。

应用场合▲演艺厅▲体育场馆▲专业演出▲礼堂▲多功能厅▲会议系统功能特点▲96k24BIT采样率▲输入7段PEQ,输出7段PEQ,高低通滤波器▲全通滤波器AIIpass▲可配置Dante网络数字音频输入输出▲USB免驱自动连接软件,支持RS232中控控制,支持TCPIP有线和无线控制▲支持手机APP无线控制▲支持多台机器组网联调,远程监控第2章技术参数第3章功能结构前面板过载指示灯0dBu输入信号电平灯-24dBu输入信号电平灯输入编辑与静音灯限幅状态灯0dBu输出信号电平灯-24dBu输出信号电平灯输出编辑与静音灯后面板机器尺寸图上翻键下翻键菜单键回车键旁通键退出键频率Q 值增益输入:长按编辑/短按静音输出:长按编辑/短按静音USB (B 型)连接口液晶显示屏4通道卡侬母输入8通道卡侬公输出电源开关保险丝盒电源插座Dante 接口(可选)TCP/IP 控制网口RS232接口3.1LCD 显示屏功能菜单LCD菜单主界面1、设备名称:用户可以通过控制软件或下位机自定义修改名称。

SAMSUNG SDRAM 64Mb H-die (x4, x8, x16) 数据手册