基于FPGA中I 2C总线模块的情确懈统

基于FPGA的I 2C总线设计

G inUnv ri f l t nc eh oo , ul a g i 4 4 C ia ul iesyo e r i T c n lg G inGu n x 0 , hn ) i t E co y i 51 0

程 。通过对 S A 1 的初 始化验 证 了该方 案 的正 确性 。 A 71 3

关键 词: C总线 ; P A 有 限状 态机 。 P FG ;

中图分类 号 : N9 91 文献标 识码 : 文章编 号 :0 2 5 6 (0 1 9 0 4 — 2 T 2 .l A 10 — 5 1 1) — 0 0 0 2 0

摘 要: 以 I 线协议 为根 据 , 出一种 采 用 F G , z c总 提 P A 通过有 限状 态机 来模 拟 实现 I 。 c总线接 口的方法 。 主

要 内容 包括 简述 I c总线 的原 理 ;介 绍用 FG P A中有 限状 态机 开发 I c总线模 块 时 的设 计 思 想和 实现 过

时钟 线 为低 电平 时 允许 数据 线 的 电平 状 态变化 。 才 总 线 的数 据 传输 由主器 件 控脉 冲 , 数 据 线 上 产 生 寻 址 信 号 、 始 信 号 、 止 在 起 停

讯 的 串行 传输 总线 , 由串行时 钟线 S L和 串行 数据 它 C 线 S A完成 全 双工数 据 传送 。I D 2 C总线 最 主要 的优点

0 引 言

I C总 线 是 P ip 公 司 开 发 的 一 种 用 于 : 间 通 hl s i 芑片

用 时 ,D 和 S L都必 须保 持 高 电平状 态 ,只有关 闭 SA C I 2 C总线 时才使 S L箝 位在 低 电平 。F C C总 线数 据传输 时。在 时钟高 电平期 间数 据 线上 必 须保 持有 稳定 的逻 辑 电平 状态, 电平 为数 据 1 电平为 数据 0 高 , 低 。只有在

《2024年基于FPGA的PCIE总线接口和光纤通信模块设计》范文

《基于FPGA的PCIE总线接口和光纤通信模块设计》篇一一、引言随着信息技术的飞速发展,数据传输的速度和效率成为了系统性能的关键因素。

FPGA(现场可编程门阵列)以其高度的可定制性和并行处理能力,在高速数据传输和处理领域得到了广泛应用。

本文将详细介绍基于FPGA的PCIE总线接口和光纤通信模块设计,探讨其设计原理、实现方法和应用前景。

二、PCIE总线接口设计1. 设计原理PCIE(Peripheral Component Interconnect Express)总线是一种高速串行计算机扩展总线标准,具有高带宽、低延迟、支持即插即用等特点。

FPGA作为PCIE设备的核心控制器,需要设计相应的接口电路以实现与主机的通信。

2. 实现方法在FPGA中,PCIE总线接口的设计主要包括物理层设计、数据链路层设计和事务层设计。

物理层设计负责信号的收发和电气特性的匹配;数据链路层设计负责数据的封装、解封和流控制;事务层设计则负责处理数据传输过程中的各种事务请求。

3. 优势与挑战PCIE总线接口的设计具有高带宽、低延迟、可扩展性强等优势,能够满足高速数据传输的需求。

然而,设计过程中也面临着诸如信号完整性、电磁兼容性、时序约束等挑战。

需要通过合理的电路设计和严格的时序分析来确保系统的稳定性和性能。

三、光纤通信模块设计1. 设计原理光纤通信模块利用光信号在光纤中传输信息,具有传输距离远、传输速度快、抗干扰能力强等优点。

在FPGA系统中,光纤通信模块负责与外部设备进行高速数据传输。

2. 实现方法光纤通信模块的设计包括光模块和电模块两部分。

光模块负责将电信号转换为光信号,并通过光纤进行传输;电模块则负责将光信号转换为电信号,并与FPGA进行通信。

在FPGA中,需要设计相应的接口电路和协议栈来实现与光纤通信模块的通信。

3. 关键技术光纤通信模块设计的关键技术包括光模块的选择与配置、电模块的电路设计、光纤传输协议的制定等。

AD9883A基于FPGA的I 2C初始化模块设计

前 提 。其 初 始 化 过 程 依 靠 A 98 A 的 S A( 7脚 ) ] D 83 D 5 和 S L 5 ) 引脚 进行 , C (6脚 两 时序 符 合 I 总 线 的 时 序 标 准 。 C

对 A 8 3 芯 片可 以使用 单 片 机或 者 由F GA产 生 IC 时 D9 8 A P 序 进行 配 置 , 面 分别 介 绍 这些 方 法 , 详 细 介绍 在 实 际 工 下 并 程 中采 用 的 基于 F GA 的 IC配 置 模块 。 P

摘 要

F GA 的 IC 配 置模 块 , Qu ru I 件 中进 行 了 IC 总 线主 从 模 式 下的 仿 真 , 用 其 内嵌 逻 辑 软 分析 P 。 在 at sI软 并

仪 Sg aTa l in l p I完 成 了 硬 件 调 试 。

关键词

F GA IC 总 线 AD9 8 A IC初 始 化 P 83

引 言

在 现 代 电 子 系统 中 , 为 数 众 多 的 I 需 要 进 行 相 互 有 C

线 S A 出现 由高 电平 向低 电平 的 变 化 , 于 启 动 IC 总 D 用 线, 准备 开始 传 送 数 据 。

② 停 止 信 号 。 在 时 钟 信 号 S L为 高 电平 期 间 , 据 C 数

2 采用 单 片 机 进 行初 始 化

一

方 面 , 直 接 采 用 带 有 IC总 线 接 口 的 单 片 机 对 可

AD9 8 A 进 行 初 始 化 , P ip 公 司 的 P 9 P 3 A1 83 如 hl s i 8 L C9 2 。

它 是 一 款 单 片 封 装 的 微 控 制 器 , 合 于 许 多 要 求 高 集 成 适

FPGA有限状态机模拟I 2C总线设计

S A 11adS A 11i V r gH L F ayt i iu tnudrm s rsv ur s a dn。 n A 71 A 72 n cl D . i l mn s l o ne ae—l ei Q aul WS oe ad n i o nl i g m a i t a n t I

d b  ̄ n y SgaTp!o ad aeW o pe dsces l . eu gb inla I n hrw r a cm lt ucsf l s e uy

Ke r sIC b ;F GA; S Vei g HDL;nt l a o y wo d : u 2 s P F M; ro l i i i tn i azi

的 7位地址码 ) l 和 位读写方 向标 志位 ; 通讯 停

b s。该总线具有接 口线少、 u) 通讯效率高等特点。 在进行 F G P A设计时 , 经常需要和外围提供 P C 接 口的芯片通信 ,虽然市场上有专用 I 总线接 口 ℃ 芯片 , 但是地址可选范围小 、 能指标 固定 、 性 功能单 使用不方便 。 根据 I 2 C总线的电气特性及其通讯

Hale Waihona Puke Ab ta tAc odn o r b s c mmu ia o rtc l ti a e to u e ein o h - b s b S b b sr c : c r ig t - u o c nc t n poo o , h s p p ri r d c d d sg fte r i n C u y P M u d s

o F GA. I n P t many n ld s he r il icu e t bi nto u t n f h c aa tr d 0 F d i rd ci o te h rceh c f C b s te e in d a a d _ o u , h d sg ie s n l _ l

基于FPGA的I 2C总线接口设计

计 算 机 应 用

? mp tr, lat n , ue a i i o op c o

.

. = 自动化技术与应用>O6 20年第 2 糟第 4 5 期

基 于 F G 的 1C总 线 接 口设 计 PA 2

吕炎军 ,王泽 勇

( 西南交通大学 光电工程研究所 ,四川 成都 603 ) 10 1

计 算 机 应 用

3 omD trAo lat s ue oi i c on

3 1 2 块 设 计 与 实现 C模

31 模块结构设计 .

4 仿 真 验证

本文在 Moe i E6 0 dl m S . 环境下对 i S 2 c总线接 口时序 进行 仿

真, 为了验证 l 2 C总线接 V模块的读/ I 写操作, 我们还得编写信

要 回应一个应答信号 。数据传 送完毕 , 主节 点器件 发 出终止信

起始信号 s在 S L 高电平 时 , : C为 数据线 S A出现 由高 电平 D

收 稿 日期 :0 一l —2 2 2 6

号结束 整个 过程 。

维普资讯

< 自动化技术与应用>06 20 年第 2 卷第 4 5 期

时钟脉冲对应于一个字节的 8 位数据传送。脉冲高电平期间数

据串行转送 , 电平 期 间为数据 准 备 , 低 允许 总线上 数据 电平 变

换。

能 。本文结合现行 的研究 项 目, 用 v 0 D 利 l H L在 FG g P A上设

计实现 i 2 C总线接 口功能 。

应答信号 A I 总线 上第 9 时钟 脉冲对应 于应 答位 , :C 2 个 相

数据位传送 : I 在 2 C总线启动后或应 答信号后 的第 1 8 个

基于I 2C总线的CPU温度监控系统

1 1C主设 备 首 先 启 动 一 次 写 周 期 , 据 线 上 的 )2 数 第一 个 字节将 被 默认 地写 入地 址 寄存器 。

2 在 第二 个 数据 周 期 , ) 主设 备 将 控 制命 令 写 入 配

置寄 存器 。

3 A T4 1开始工 作 , 集 本 地 或 远程 温度 值 并 ) D 76 采

第4卷 2

第 4期

航 空 计 算 技 术

Ae o a tc lCo ut c i u r n u ia mp i Te hn q e ng

V0 _ l42 No. 4

21 02年 7月

J 12 1 u. 0 2

基 于 I C总 线 的 C U温 度 监 控 系 统 2 P

图 1 A T 4 1内部 结 构 图 D 76

从 设 备 反 馈 应 答 信 号 A K, 接 到 应 答 信 号 后 , 设 C 再 主

8 J l 9

S A f O j A A A A A 州 I 』 ×I ×J 0J 1 2 3 4 5 6I 7 D I A A1I 2I 3l 4I 5I 6J × x D D I I l I R D I D D D D D

存 于温度 寄存 器 中。 4 温度寄存 器与温度 界限寄存器 中的值进 行 比较 。 ) 5 如 果温 度超 过 阈值则 产 生报 警信 号 A E T ) LR 。 6 IC主设 备 通 过 读 取 A T 4 1设 备 地 址/ 空 ) D 76 清

过 1C总 线 , 成 C U与 A T4 1的互 联 , 2 完 P D 76 实现 处 理

木

。

.

c  ̄ P u

1

川门 皿 不

21 0 2年 7月

基于FPGA的I2C总线控制器设计

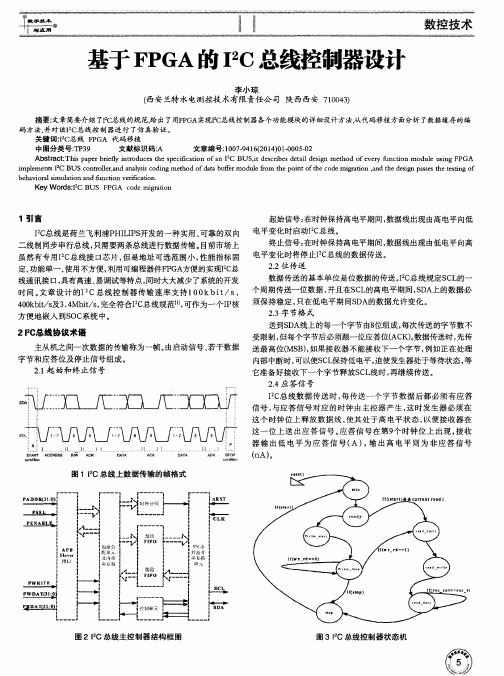

2 F C 总线协议术语

送到S D A线上 的每一个字节 由8 位组成 , 每次传送 的字节数不

受 限制 , 但每个字节后必须跟一位应答位( AC K) 。 数据传送时 , 先传 主从机之 间一 次数 据的传输称为一帧 。 由启动信号 、 若干数据 送最高 位( MS B ) , 如果接收器 不能接收下一个字节 , 例如 正在处理 字 节和应答位 及停止信号组 成。 内部 中断时 , 可 以使S C L 保持低 电平 , 迫使发生器处于等待状态 , 等

i mp l e me n t s I 2 C BU S c on t r o l l e r , a nd a n a l y s i s c o d i n g me t h od ofd a t a b uf f e r mo d u l e f r o m t he p o i n t o ft he c o d e mi g r a i t on , a n d t he d e s i n g p a s s e s t he t e s in t g o f b e h a vi o r  ̄s i mu la io t n a nd f u nc io t n ve if r ic a i t on .

数 控 技 术

黯

基于 F P G A的 I 2 C总线控制器设计

李 小 琼

( 西安 兰特水电测控技术有限责任公 司 陕西西安 7 1 0 0 4 3 )

摘要: 文章 简要介绍 了F C 总线的规范, 给出了用F P G A实现l a C 总线控制器各个功能模块的详细设计方法, 从代码移植方面分析了数据缓存的编

Ab s t r ac t : Th i s p a p e r b r i e nv i n t r o d uc e s t h e s p e c i ic f a t i o n of a n 1 2 C BU S . i t de s c r i b e s d e t a i l d e s i g n me t h od o f e ve r y f u nc io t n m od u l e us i ng FPGA

I2C verilog (非常详细的i2c学习心得)

图 4. AT24C02/4/8/16 字节写入帧格式

启 动 SDA线 S 1 0 1 0 X X X 应 答 应 S 1 0 答 1 0 X X X 应 答 非 P 应 答 控制字节 写 读 EEPROM存储单元 指定地址(n) 启 动 控制字节 数据(n) 停 止

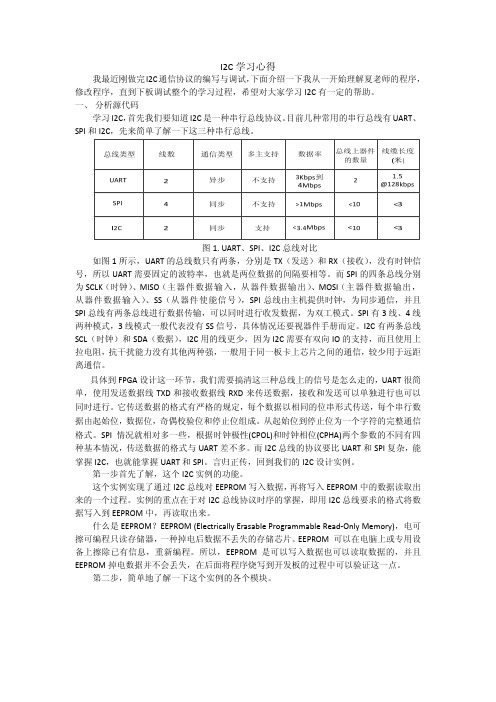

( 1)总线非忙状态( A 段) :数据线 SDA 和 时钟线 SCL 都保持高电平。 ( 2)启动数据传输( B 段) :当时钟线( SCL)为高电平状态时,数据线( SDA)由 高电平变为低电平的下降沿被认为是 “ 启动 ”信号。只有出现 “ 启动 ”信号后,其它的命令 才有效。 ( 3)停止数据传输( C 段) :当时钟线( SCL)为高电平状态时,数据线( SDA)由 低电平变为高电平的上升沿被认为是 “ 停止 ”信号。随着 “停在 ” 信号出现,所有的外部操 作都结束。 ( 4)数据有效( D 段) :在出现 “启动 ”信号以后,在时钟线( SCL)为高电平状态时 数据线是稳定的,这时数据线的状态就要传送的数据。数据线( SDA )上的数据的改变 必须在时钟线为低电平期间完成, 每位数据占用一个时钟脉冲。 每个数传输都是由 “启动 ” 信号开始,结束于 “停止 ”信号。 ( 5)应答信号:每个正在接收数据的从机 EEPROM 在接到一个字节的数据后,通 常需要发出一个应答信号。而每个正在发送数据的 EEPROM 在发出一个字节的数据后, 通常需要接收一个应答信号。 EEPROM 读写控制器必须产生一个与这个应答位相联系的 额外的时钟脉冲。在 EEPROM 的读操作中, EEPROM 读写控制器对 EEPROM 完成的最 后一个字节产生一个高的应答位,这叫做非应答信号,随后给 EEPROM 一个结束信号。 第四步,理解各个模块的代码。 首先介绍核心模块——EEPROM_WR 模块,这个模块就干一件事,严格控制 SDA 与 SCL 总线上的信号, 使其满足 I2C 总线时序要求。 这里要用到状态机来控制 SDA 与 SCL 上的信号, 所以难点就在于对状态机的编写。因为 EP2C8‐2010 开发板采用的 EEPROM 是 AT24C02, 所以该状态机控制的 SCL 与 SDA 时序就要满足 AT24C02 的写入和读取格式。图 4、5 分别 是 AT24C02/4/8/16 字节写入帧格式和读指定地址存储单元的数据帧格式,简单分析一下字 节写入格式,如图 4 所示:第 1 位启动信号,接下来的第 2‐9 位是控制字节写入,其中 2‐5 位是固定的机器码 1010,6‐8 位是页地址,第 10 位是 EEPROM 给出的应答信号 0,第 11‐18 位是存储单元地址,19 位是 EEPROM 给出的应答信号 0,第 20‐27 位是写入的数据,28 位 应答信号,29 位停止信号。而 AT24C02/4/8/16 的字节读取格式也是大同小异,先写入控制 字和存储地址, 然后是启动信号与控制字节信号, 这时, 控制字节的第 8 位变为了 1 (读取) , 最后读取数据,并且在读取完毕后,主机将 SDA 拉高作为非应答信号。最后是停止位。 可能有人还是对这种字节写入与读取格式不明白, 其实这种格式是别人定好的, 我们所 需要的就是要让 SDA 与 SCL 的信号满足这种格式要求即可,下面我们来看夏老师的 EEPROM_WR 程序。

基于FPGA的I2C SLAVE模式总线的设计方案

基于FPGA的I2C SLAVE模式总线的设计方案

0 引言

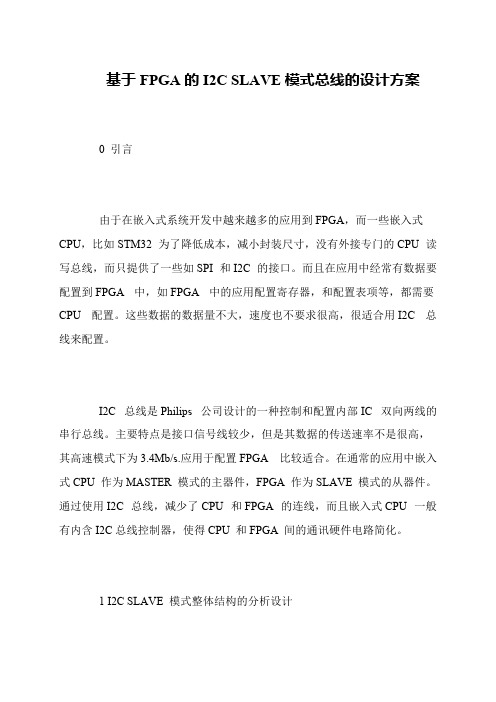

由于在嵌入式系统开发中越来越多的应用到FPGA,而一些嵌入式CPU,比如STM32 为了降低成本,减小封装尺寸,没有外接专门的CPU 读写总线,而只提供了一些如SPI 和I2C 的接口。

而且在应用中经常有数据要配置到FPGA 中,如FPGA 中的应用配置寄存器,和配置表项等,都需要CPU 配置。

这些数据的数据量不大,速度也不要求很高,很适合用I2C 总线来配置。

I2C 总线是Philips 公司设计的一种控制和配置内部IC 双向两线的串行总线。

主要特点是接口信号线较少,但是其数据的传送速率不是很高,其高速模式下为3.4Mb/s.应用于配置FPGA 比较适合。

在通常的应用中嵌入式CPU 作为MASTER 模式的主器件,FPGA 作为SLAVE 模式的从器件。

通过使用I2C 总线,减少了CPU 和FPGA 的连线,而且嵌入式CPU 一般有内含I2C总线控制器,使得CPU 和FPGA 间的通讯硬件电路简化。

1 I2C SLAVE 模式整体结构的分析设计。

i平方c总线的工作原理

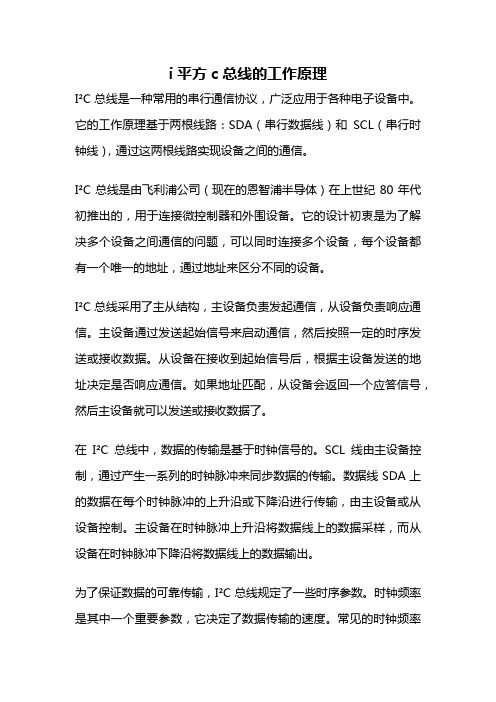

i平方c总线的工作原理I²C总线是一种常用的串行通信协议,广泛应用于各种电子设备中。

它的工作原理基于两根线路:SDA(串行数据线)和SCL(串行时钟线),通过这两根线路实现设备之间的通信。

I²C总线是由飞利浦公司(现在的恩智浦半导体)在上世纪80年代初推出的,用于连接微控制器和外围设备。

它的设计初衷是为了解决多个设备之间通信的问题,可以同时连接多个设备,每个设备都有一个唯一的地址,通过地址来区分不同的设备。

I²C总线采用了主从结构,主设备负责发起通信,从设备负责响应通信。

主设备通过发送起始信号来启动通信,然后按照一定的时序发送或接收数据。

从设备在接收到起始信号后,根据主设备发送的地址决定是否响应通信。

如果地址匹配,从设备会返回一个应答信号,然后主设备就可以发送或接收数据了。

在I²C总线中,数据的传输是基于时钟信号的。

SCL线由主设备控制,通过产生一系列的时钟脉冲来同步数据的传输。

数据线SDA上的数据在每个时钟脉冲的上升沿或下降沿进行传输,由主设备或从设备控制。

主设备在时钟脉冲上升沿将数据线上的数据采样,而从设备在时钟脉冲下降沿将数据线上的数据输出。

为了保证数据的可靠传输,I²C总线规定了一些时序参数。

时钟频率是其中一个重要参数,它决定了数据传输的速度。

常见的时钟频率有100kHz和400kHz,也有更高的频率。

时钟频率越高,数据传输速度越快,但也会增加传输的误差。

I²C总线还定义了起始信号和停止信号。

起始信号由主设备产生,表示通信开始。

停止信号也由主设备产生,表示通信结束。

起始信号和停止信号的产生都是通过控制SDA线上的电平变化来实现的。

总的来说,I²C总线的工作原理是通过主设备产生起始信号,然后按照一定的时序发送或接收数据,最后由主设备产生停止信号来完成通信。

通过SDA线和SCL线的协作,实现了设备之间的串行通信。

这种通信方式简单灵活,并且可以同时连接多个设备,因此在很多电子设备中得到了广泛应用。

一种状态优化的I 2C总线主控制器的FPGA设计

.

r gse o n sa o td t o to tt r n i o e itrc u twa d pe o c n r lsae ta st n,a d t e fe i e sr c u e o h h f r gse su e o sm— i n h xbl tu t r ft e s i e itrwa s d t i l t

中图分 类号 : N 7 T 4

文献标识 码 : A

文章 编 号 :0 5— 4 0 2 1 ) 6—0 3 0 1 0 9 9 (0 0 0 7 8— 4

IC Itr ne rt i ut 是 由 P ip公 司 推 (ne— t a dCr i I g e c ) hl i

送信 息 , 根据 地址 识 别 每个 器 件 。每 个 器件 都 有 并

r aie h 2 u aa c mmun c t n e lz st e I b s d t o C iai o

.

,

ad n

K e o ds F y w r : PGA ;I C b s u ;Ve io rlg HDL ;sae o t ie tt pi z d m

( 桂林 电子 科 技 大 学 信 息 与 通 信 学 院 , 西 桂 林 5 10 ) 广 4 0 4

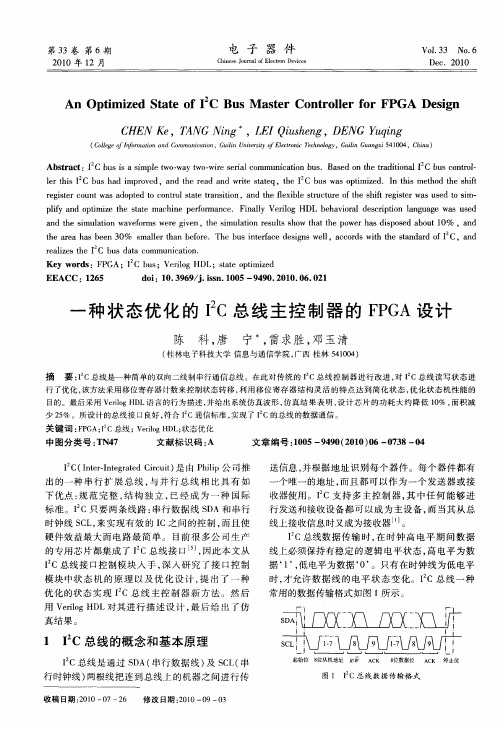

摘 要 : C总线是一种简单的双向二线制串行通信总线。在此对传统的 I 1 2 2 C总线控制器进行改进, 1 对 2 C总线读写状态进

行 了优 化 , 方法 采 用 移 位 寄 存 器 计 数 来 控 制状 态转 移 , 用 移 位 寄 存 器 结 构 灵 活 的 特 点 达 到 简 化 状 态 , 化 状 态 机 性 能 的 该 利 优

目的。最后采用 V ro L语言的行为描述 , ei gHD l 并给 出系统仿真波形 , 真结果表 明 , 仿 设计 芯片 的功耗 大约降低 1% , 0 面积减 少 2 % 。所设计的总线接 口良好 , 合 I 5 符 C通信标准 , 实现 了 iC的总线 的数据通信 。 2

基于FPGA的I 2C控制器设计

以 太 网控 制 技 术 和 A I 计 ; 蔚 (9 1 )女 , 士研 究 生 , SC设 付 18 一 , 硕 研究 方 向为 工 业 以太 网控 制 技 术 和 A I SC设 计 ; 王 平 (93 ) 男 , 士 , 授 , 士 生 导 师 , 究 方 向为 工 业 以太 网及 网 络 控 制 技术 、 线 控 制 网络 及 其 应 用 、 能 16一 , 博 教 博 研 无 智

1 l 总 线 介 绍 ℃

I 总线 是 P IIS公 司开 发 的 一 种 简 单 、 2 C H LP 双

作 者简 介 : 夏 ( 9 2 ) 男 , 士研 究 生 , 究 方 向 为工 业 控 制 和 现 场 总线 ; 渝 ( 9 2 )男 , 士 研 究 生 , 究 方 向为 工 业 杨 18一 , 硕 研 金 18 一 , 硕 研

b r o o c r u h o y Ve i g t a r o t te c mmu i ain w t P M h c a h n ef c f P l y n c t i EE RO o h w ih h s t e i tra e o C.Usn d l i . o e - ig Mo esm60 t mu

De i n o n f IC Co t o lr Ba e n FPGA sg f a Ki d o Z n r le s d o

Y ANG a JN Yu, U W e , ANG Pn Xi ,I F iW ig

( olg fAuo t n, h n qn iest fP ssa d T lc mmu iain , h n qn 0 0 5 C ia) C l e o tmai C o g ig Unvri o ot n ee o e o y nc t s C o g ig4 0 6 , hn o

基于FPGA视频采集中的I2C总线设计与实现

基于FPGA视频采集中的I2C总线设计与实现作者:潘利明王惠平刘春风来源:《现代电子技术》2010年第08期摘要:随着编码理论和多媒体网络应用的发展,图像和视频压缩编码JPEG2000系统应用得到逐步推广。

在此从视频采集中总线的特点、协议入手,着重对总线设计及实现方法进行介绍。

基于视频采集芯片SAA7111,提出采用VHDL语言来模拟实现总线接口的方法,并将其嵌入到FPGA中。

实验仿真结果证明数据是正确、稳定、可靠的,具有一定的可借鉴性。

关键词:FPGA; 视频采集总线; SAA7111中图分类号:TP336文献标识码:A文章编号:1004-373X(2010)08-0080-03PAN Li---(1.College of Electronic Science and Engineering, National University of Defence Technology, Changsha 410073, China;2.Qinghai University, Xining 810016, China)Abstract:With development of the coding theory and multimedia network application, the application of the image and video compression coding JPEG2000 system have been extendeded emphatically.Based on the videoVHDL language, and embed it into FPGA is proposed. The simulation results show that the data is correct stable and reliable.随着科学技术的发展和现代战争条件的变化,传统图像信号提供的单一服务已远远不能满足现代战争的需要。

基于FPGA的I~2C控制器的实现及其在音频编解码中应用

& ’ 总线 控 制 器 的 设 计采 用 () *+,-. 语 言描 述 O 本 文 给 出 了 & "’ 控 制 器 写 数 据 代码 O读 数 据 与 其 类似 ! 输 入 ’ U‘’ R 是 & "’ 控 制 器 的 时 钟输 入 O 在 对 & "’ 控制 器 进 行例 化 时O需 要 提 供一 个 满 足 & "’ 标 准 的时 钟 ! 控制 器 每 次 传 输 "\ 位 数据 O前 % 位 是 从 设备 地 址 ZU2a Vb2]]WO接 下 来 % 位 是 从 设 备 的 寄 存器 地 址 Z^cb2]]WO最 后 % 位 是 数据 ! 3 4%567 的 &"’ 通信 数 据 格 式 中 有 5 位 寄存 器 地 址和 d 位数 据 O与 &"’ 控 制 器 的 数 据格 式 定 义 不 一致 O 实 际 传输 时OZ^cb2]]W 的 高 5 位 为 寄 存器 地 址O 最 后 一 位 是 d 位 数 据 最 高 位 ! 本设 计 中 O&"’ 控 制 器使 用 66 个时 钟 周 期 完 成一 次 传 输 "\ 位 数据 ! 第 7 个 时 钟 周期 用 于 初始 化 控 制器 O 第 "O6 个 周期 用 于 启 动传 输 O 第 \e6$ 个 周 期用 于 传 输数 据S 其 中 包括 "\ 位 数 据 和 6 个 2’ RT O最 后 6 个 周 期 用 以

2@=<* ;A<B CD ) E;<; <*;F=G +<+F . G)AD;F+=G - H & "’ =)*+;, @: = += ;F;,I J)E +F <D+= ;* <+A,)8 @ I ()*+,- . <D;< += D;*EK;*) ,;F.: ;.) +F ;A<+- F ,)(),8 & "’ @ := A- F<* -,,)* += ;AD+)()E -F / 012 L1+( +F . A- FH+.:*) &0 ’-* ) ;@ -: < ;:E +- )F A- E) ;F E E)A- E) &’ 3 4%5 67M2AA- *E+F . <- E)=+.F H,-K! N *- .*;G= ;*) E)@: ..+F. ;FE N*)A)E+F . )G: ,;<-* O <D) * )=: ,< += ;AA-* E+F. K+<D * )P:)=< - H & "’ =)*+;, @ := ;.*))G)F <M C D) N* -.* ;G += =IF <D)=+J)E! @;AQ )G: ,;<-* ;F E E -KF ,- ;E )E +F 9: ;*<: = && >M$M R)I K- *E=B /012 ()* +,-. & "’ @: = 3 4% 567

基于FPGA的片内多址I 2C总线控制器设计

微 电子通信 控 制 领 域 以及 S C( 上 系 统 ) O 片 中 广 泛采用 IC总线作 为控 制 总线 。

IC总线 (ne C B S 是 P ip 公 司 推 出 的 ItrI U ) hl s i

ห้องสมุดไป่ตู้

芯片 间串行 通讯 总线 , 以两 根 线 实 现完 整 的 全双 它 工 同步数据 传输 , 初为 电视 机调 频 电路而设 计 , 最 目

t n f h u i s o e s b—u i sn rlg HD o t nt u i g Ve i L.T e s lt n r s l h wst a a r e l ta s e d s o h i ai e u t s o ti c n wo k w l a p e mu o s h t

itg a ig.W e frtd s rb h u da n as a d ta s s in fr a f1 b s t e r s n h ne rt n s e c e t e f n me tl n n miso o i i r m to 2 C u h n we p e e tt e , oe v r—altu t r fo rd sg sn e T p —Do t o . W e as k e a ir llv ld s rp lsr cu e o u e in u ig t o h wn meh d lo ma e b h v o a e e e c i —

维普资讯

第 5期 20 07年 l O月

微

处

理

机

No 5 .

M1 CROP ROC S RS ES O

Oc . 2 o t .O 7

基于I 2C总线的单片机系统设计与虚拟仿真

di1 .9 9 ji n 17 —14 .0 0 0 . 2 o:0 3 6 /.s . 6 1 0 1 2 1 .4 0 3 s

量 麦旦

基 于 IC 总线 的 单 片机 系统 设 计 与虚 拟 仿 真 2

黄 鑫 王玉林 谢 , , 静

( .格 林概念 科技有 限公 司 , 圳 5 8 0 ; .南华大学 机械 工程 学院 。 阳 4 10 ) 1 深 10 0 2 衡 2 0 1

摘要 :目前 , S l系列、 TME 8 MC 5 A L 9系列、8 0 6 HC 5系列等单片 机应 用 很 广 . 他 们 均 没 有 1C 总 线 接 口 , 制 了在 这 些 系 统 中使 用 具 有 但 2 限 IC总线接 口器件的应用。本 文介绍 了基于 IC总线 的 A/ 2 2 D转换 的 接 口电路 设 计 与 编程 。 P oes仿 真 环 境 下 建 立 单 片 机 系 统 电 路模 在 rt u 型, 实现 了基于 IC总线的 A D转换测试过程的虚拟仿真。 2 /

O C: S 外部时钟输入端 , 内部时钟输 出端 ; E T: X 内部 、 外部 时钟选择线 , 使用 内部时钟时 E T接地 ; X A N 模拟信号地 ; G D: A U :/ O T D A转换输出端 ; V E 基准电源端 。 R F: .

(.G l o cp eh ooyC ,Ld, hn hn5 80 C ia 1 ei C ne tT c nlg o t S ez e 10 0, hn ; n

bu ne ac sit f e.1 t g te u e o h s y tm swi 2 bu nef e i i h s f e es se t 1C sit r min t h ac

fpga 的i2c通信实现方案

fpga 的i2c通信实现方案下载温馨提示:该文档是我店铺精心编制而成,希望大家下载以后,能够帮助大家解决实际的问题。

文档下载后可定制随意修改,请根据实际需要进行相应的调整和使用,谢谢!并且,本店铺为大家提供各种各样类型的实用资料,如教育随笔、日记赏析、句子摘抄、古诗大全、经典美文、话题作文、工作总结、词语解析、文案摘录、其他资料等等,如想了解不同资料格式和写法,敬请关注!Download tips: This document is carefully compiled by theeditor.I hope that after you download them,they can help yousolve practical problems. The document can be customized andmodified after downloading,please adjust and use it according toactual needs, thank you!In addition, our shop provides you with various types ofpractical materials,such as educational essays, diaryappreciation,sentence excerpts,ancient poems,classic articles,topic composition,work summary,word parsing,copy excerpts,other materials and so on,want to know different data formats andwriting methods,please pay attention!FPGA实现I2C通信的详细方案一、引言Field-Programmable Gate Array(FPGA)是一种可编程逻辑器件,具有高度灵活性和并行处理能力。

基于FPGA的I~2C接口设计

个信号后 。 等待受控单元发 出一个应答信号 。 C P U接 收到应答信号后 , 根据实际情况作出是否继续传递信号 的判断。若未收到应答信号 , 则 判断为受控单元出现故 障 数据传输信号 : 发送数据 的芯片在 S C L脉冲控 制下 在 S D A上 串 行输出数据信号 . S D A只能在 S C L为低 电平期间改变状态 , 在S C L为 高 电平期间应保持稳定

2 总线 的构 成 及 信 号 类 型

I 2 C总线是由数 据线 S D A和 时钟 S C L 构 成的串行总线 . 可发送和 接收数据 。在 C P U与被控 I c 之间、 I c与 I c之间进行双 向传送 , 最高 传送 速率 1 0 0 k b p s 。各种被控制 电路均并 联在这条总线上 . 但就像 电 话机一样 只有拨通各 自的号码才能工作 . 所 以每个 电路和模块都有唯 的地址 , 在信息 的传输过程 中, P C总线 上并接的每一模块 电路 既是 主控 器( 或被控器 ) . 又是发 送器 ( 或接 收器 ) , 这取决于 它所要完成 的 功能 。C P U发出的控制信号分 为地址码 和控制量两部分 , 地址码用来 选址 , 即接通需要控制 的电路 , 确定控制 的种类 : 控制量决定该调整 的 类别 ( 如对 比度 、 亮度等 ) 及需要调整的量。 这样 . 各控制 电路虽然挂在 同一条总线上 . 却彼此独立 . 互不相关 I 2 C总线 在传送数据过程 中共有三种类 型信 号 , 它们分别是 : 开始 信号 、 结束信号和应答信号 。 开始信号 : S C L 为高 电平时 . S D A由高电平 向低 电平跳变 . 开始传 送数据 。 结束信号 : S C L 为低 电平时 . S D A由低 电平 向高电平跳变 . 结束传 送数据。 应答信号 :接收数据的 I c在接收到 8 b i t 数据 后 .向发送 数据的 I c 发 出特定 的低 电平脉 冲, 表示 已收到数据。C P U向受控单元发出一

I2C总线的光电隔离措施及电路原理分析

I2C总线的光电隔离措施及电路原理分析I2C总线是一种常用的串行通信协议,用于连接微控制器、传感器和其他外设。

由于I2C总线是一个双线制的通信协议,其中的数据线和时钟线是共用的,这就导致了在一些特定场景下存在干扰和数据传输不可靠的问题。

为了解决这些问题,可以采取一些光电隔离措施及电路原理来提高I2C总线的可靠性和抗干扰性。

一、光电隔离措施1.光电耦合器光电耦合器是一种可以实现光电隔离的器件,它包括一个发光二极管和一个光敏电阻(或光敏三极管)。

在I2C总线上,可以将发光二极管连接到主设备的SDA和SCL线上,然后将光敏电阻连接到从设备的SDA和SCL线上。

这样,当主设备将数据或时钟信号传输到从设备时,光电耦合器会将信号转换为光信号,并通过光传导到从设备的SDA和SCL线上,从而实现光电隔离。

2.光耦光耦是一种包含光电二极管和光敏三极管的器件,可以实现光电隔离。

在I2C总线上,可以使用光耦将主设备和从设备之间的SDA和SCL线进行隔离。

将主设备的SDA和SCL线连接到光电二极管的阳极和阴极上,然后将光敏三极管的集电极和发射极分别连接到从设备的SDA和SCL线上。

当主设备将数据或时钟信号传输到从设备时,光耦会将信号通过光传导到从设备的SDA和SCL线上,从而实现光电隔离。

1.使用电阻器提高抗干扰性在进行I2C总线的光电隔离时,可以采用电阻器来提高总线的抗干扰性。

将电阻器连接到总线上可以起到限流的作用,使总线的驱动能力得到提升,从而改善总线的干扰抗性。

此外,使用电阻器可以改善总线的匹配阻抗,提高信号的传输质量。

2.增加滤波电容在I2C总线的光电隔离电路中,可以增加适当的滤波电容来抑制干扰信号。

滤波电容可以起到滤波器的作用,将高频噪声滤除,提高总线的信号质量。

在I2C总线的主设备和从设备之间加入适当的电容,可以阻止外界噪声对总线信号的干扰。

3.使用保护器件为了保护I2C总线免受过电流、过电压和ESD的影响,可以在总线的主设备和从设备之间插入保护器件。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

S DA必须 置0 ,产生 应答 信号 ,才 能继 续 工作 ,如果 L 6 有应 M7 没 答 ,数 据传送 将停 止 。图1 为读和 写 的时序 。

扫 描 显 示和报

警 蜂 鸣

键Hale Waihona Puke T 可编程逻辑器件 ( P A 及 I F G ) ℃总线接 口

可 。 总 线

L 6 M7

X 3 。 0 开发板对系统进行了 证, C S1 0 5 验 最后给 出了 可行的 电路扩展方法。 关键词: G M7 C F A L 6 I 总线 P 2

1 引言

I 总线是 P i p ̄ 推 出的芯 片间 串行传输 总线 ,它 以两根 2 C hl s i 连 线 实现 了完善 的全 双 工 同步数 据 传送 ,可 以方 便 地构 成 多机 系 统 和 外 围器 件扩 展 系 统 。I 总 线 采 用 了 器件 地址 的硬 件 设 置方 2 C 法 ,通过 软 件寻 址 完全 避免 了 器件 的片 选线 寻址 方 法 ,从而 使硬 件 系统 可以 进行 简 单灵 活的 扩展 。由于 具有 严格 完 整 的规范 与 独 立 的系统 结构 ,I 总 线器 件的 编程操 作变 得更加 简便 。F G 是 2 C P A 现场 可 编程 门阵 列 的简 称 ,在 电子 设计 领域 有广 泛应 用 ,从CP U 到 简单 的逻 辑 门 电路 , 它几乎 能完 成 任何数 字 器 件的 功能 。所 以 与 其他 器件 相 比 ,F GA 有 很多优 点 。() P 在 反 复的设 计 P 具 1 F GA 修 改过 程 中 只需 改变 编程 文件 ,这为 设计 人 员提 供 了很 大的 灵活 性 。() 2 由于F G P A几乎 能 实现 各种 数 字 电路 的功 能 ,非 常有 利于 电路 的 扩展 。因此 F G P A被 众多 设 计人 员视 为 逻辑 解 决 方案 的首 选 。这 也是  ̄F G E P A中能方 便完成 托 总 线接 口设计 的原 因。 般 的温 度 实时 显示 电路 都是 首先 由传 感 器采集 温 度信 号的 模 拟 量 ,再 通过 放 大 电路 ,A D转换 器 ,输 出数 字 量 。这 种 系统 / 由分立 元 件和 通用 集 成 电路组 成 ,抗 干扰 能 力差 ,精 度 低 。那 么 如果把这一过程通过集成电路来实现 ,可靠性和精确性会有很大 提 高 。L 6 M7 实现 了这一 功能 ,并 配以I 串行 总 线接 口,再加 上 2 c L 6 工作 范 围是 从一52 15 ,满 足 了现实 生活 中决大 多数 M7 的 5 X ̄ 2 E 情 况 ,使它用 起来 非常方 便 。

I技 术 与 应 用 T

统

刘鹏 唐 山开滦赵 各庄矿 业有 限公 司洗煤 厂 河北唐 山 0 30 6 10 摘要: 本文首先介 绍了 测温集成电路LM7的器件结构、 6 器件性 质、 数据 传输方式、 用方法, 使 然后对基于F G 中 2总线模块 的精确 测温系统的 P A I C 硬件组成进行 了 详细说明。 此系统利 用 P 实现 了 F GA 精确 的温度测量, 显示输 出和报警功 能。 文章重点介 绍了 接 口 块电路和控 制原理 , I c 模 利用GR _

沿被 称为 “ 开始 ”信号 ,数 据传输 开始 。

2 、器件介绍

L 6是 由数字 温度 传感 器 、温 度窗 口比较器 和I M7 C串行 总线 接 口组 成 的集 成 电路 。它 的输 出( ) 温 度超 过 可 编程 窗 口温 I 在 NT 度时被激活 ,温度超限警报输 出(-RI - ) TC T A 在温度超过可编程的 危险极限温度时有效Ⅲ。当L 6 M7 的串行总线工作时 ,L 6 位 M7 有7 片选 ( 受控 )地 址 ,片 选地 址 中的高 5 设 为 “0 1 ” ,另外 低 位 10 0 2 分配 给管脚 A 、A ,并通 过A 、A1 地或 接+Vs 置 “” 位 0 1 0 接 来 0 或置 “ ” 。所 以通 过改 变A 、A1 1 0 ,一路 串行 总线可 以最 多为4 个 L 6 M7 提供 传输 Ⅲ 。 L 6 M7 内部 共 有 5 1 位寄 存 器 ,分 别存 储 实 时温 度 数 据 , 个 6 迟 滞 温 度 ( h s)数 据 ,下 限 温 度 ( l w)数 据 ,上 限 温 度 T yt To ( hg )数据 ,危险极限温度 (— I )数据 ,1 位寄存 T ih T CR T 个8 器 ,用来 设 置状 态 字 ,另一 个 8 寄 存 器用 来存 储 寄 存 器地 址 , 位 每个 寄 存 器都 可通过 F G I P A ̄ 用I ] C串行总 线 进行 编程 ,改 变数 据 值 。除指 示寄 存 器外 的其 他寄 存 器的 地址 由8 位组 成 ,前5 全为 位 0 ,后3 位的表 示不 同寄 存器 ,表 1 明 了在指示 寄 存器 中 ,不 同寄 说 存 器的 地址 。

II 蟠 K T

f I

圈 2 统 框 图 系

3 .系统硬件组成

如 图 2 示 ,系 统 由控 制 系统 ,温 度采 集 系 统 ,显 示 和 报 所 警系统 ,键盘组成 。F GA P 把L 6 M7 采集的温度数据 ̄ l 端 、 l fNT TCR TA 的状 态送 至显 示和 报警 蜂 鸣 系统 ,因为 L 6 实时 - I-端 M7 的 温度 数据 寄存 器 内的 数据 是 自动 实时 更新 的 ,这 就使 系统 达 到 了 实时 显示 和监测 的 目的 。键盘 输入 ,利 用F G P A编程 ,改 变L 6 M7 中寄存器的数值 ,使其在不同的温度情况下使用。在系统的硬件 中,最为重要的 ,也是本设计的关键点是F GA中的I 总线接 口 P 2 C 模块 。I 总 线传输 的数 据 是 串行 进 出的 ,并且 具有 严格 的规 范 , 2 C 这就 要求 接 口模 块既 满足 时序 要 求 ,又能 实现 串行数 据转 换 为 并 行数据 的功 能 。 31 双 向二线 制总 线协议 定义 ( 图1 . 如 )嘲【: 3 】 () 1总线 非忙 状 态 ( 段 ) :该 段内 的数 据 线(DA) 钟 线 A s 和时 (C ) S L 都保持 高 电平 。 () 数据传 输 (段 ) :当时钟 线(C ) 2开始 B S L 为 高 电平 状态 时 ,数 据线 (DA 由高 电平变 为 低 电平 时下 降 S )