MAX5842中文资料

UCN5841中文资料

Output Voltage, VCE (5841) . . . . . . . . . . . . . . . . . . . . . . 50 V (5842) . . . . . . . . . . . . . . . . . . . . . . 80 V

SUB

1

POWER GROUND

9

Dwg. FP-013-2

A5841SLW & A5842SLW

POWER GROUND

1

SUB

CLOCK 2 CLK

SERIAL DATA IN

3

GROUND 4

LOGIC SUPPLY 5 VDD

SERIAL DATA OUT

6

STROBE 7 ST

OUTPUT ENABLE

5 LOGIC SUPPLY

SERIAL-PARALLEL SHIFT REGISTER

6

SERIAL DATA OUT

LATCHES

7 STROBE

8

OUTPUT ENABLE (ACTIVE LOW)

MOS

BIPOLAR

18

17

16

15

14

13

12

11

10

OUT 1 OUT 2 OUT 3 OUT 4 OUT 5 OUT 6 OUT 7 OUT 8 K

PD . . . . . . . . . . . . . . . . . . . See Graph Operating Temperature Range,

TA . . . . . . . . . . . . . . . . -20°C to +85°C Storage Temperature Range,

YAV 8AD PRO 24位高精度串口多功能采集卡技术手册DAM7452

YAV8AD PRO高精度串口采集卡技术手册V1801武汉亚为电子科技有限公司DAM7452关于本手册为亚为推出的YAV8AD PRO数据采集卡的用户手册,主要内容包括功能概述、8路模拟量输入功能、8路IO功能、应用实例、性能测试、注意事项及故障排除等。

说明序号版本号编写人编写日期支持对象应用时间特别说明1 1.0郑先科2014.05YA V8AD PRO采集卡2 2.0郑先科2016.01YA V8AD PRO采集卡3 3.0郑先科2017.01YA V8AD PRO采集卡2017.01适用于RS232\485\WiFi\GPRS ZIGBEE\蓝牙\433M无线4 4.0李雪2017.08YA V8AD PRO采集卡2017.08目录0.快速上手 (1)产品包装内容 (1)应用软件 (1)接口定义 (1)通信 (2)1.产品概述 (2)技术指标 (2)⏹模拟信号输入 (3)⏹数字信号输入 (4)⏹数字信号输出 (4)⏹通信总线 (4)⏹温度参数 (4)硬件特点 (5)原理框图 (5)机械规格 (6)2.采集卡信号接线 (7)AI模拟量接线 (7)DI数字量接线 (8)DO数字量接线 (9)3.模拟量输入功能 (9)模拟量输入 (9)输入采样原理 (10)输入接线 (10)采样值计算 (11)⏹无符号整型 (11)⏹24位精度采集值的计算方法 (11)⏹模拟量值 (12)4.数字量输入功能 (12)数字量输入原理 (12)DI高低电平/无源触点输入 (13)计数功能输入 (13)测频功能输入 (13)PWM功能输入 (13)5.数字量输出功能 (14)输出原理 (14)DO高低电平输出 (14)PWM测试输出 (14)AO输出 (14)输出接线方式 (15)6.通信协议 (15)串口Modbus通信协议 (15)YA V IOT通信协议 (17)7.应用实例 (19)采集卡连接 (19)软件功能 (20)⏹亚为串口采集卡通用采集平台 (21)8.注意事项及故障排除 (22)注意事项 (22)⏹存储说明 (22)⏹出货清单 (22)⏹质保及售后 (22)⏹特别说明 (22)故障排除 (23)⏹无法正常采集数据 (23)⏹不显示波形 (24)⏹DI测频计数没反应 (24)⏹采集速度不够 (24)⏹软件错误 (24)9.性能测试 (24)安全规范 (24)耐电压范围测试 (25)环境适应性测试 (25)10.文档权利及免责声明 (26)11.联系方式.......................................................................................................................错误!未定义书签。

MAX485中文数据手册资料

MAX485中文资料2009-11-28 14:49MAX485中文资料,MAX485 PDF,DATASHEET,电路图,通讯程序内容介绍:MAX481、MAX483、MAX485、MAX487-MAX491以及MAX1487是用于RS-485与RS-422通信的低功耗收发器,每个器件中都具有一个驱动器和一个接收器。

MAX483、MAX487、MAX488以及MAX489具有限摆率驱动器,可以减小EMI,并降低由不恰当的终端匹配电缆引起的反射,实现最高250kbps 的无差错数据传输。

MAX481、MAX485、MAX490、MAX491、MAX1487的驱动器摆率不受限制,可以实现最高2.5Mbps的传输速率。

这些收发器在驱动器禁用的空载或满载状态下,吸取的电源电流在120(A 至500(A 之间。

另外,MAX481、MAX483与MAX487具有低电流关断模式,仅消耗0.1µA。

所有器件都工作在5V单电源下。

驱动器具有短路电流限制,并可以通过热关断电路将驱动器输出置为高阻状态,防止过度的功率损耗。

接收器输入具有失效保护特性,当输入开路时,可以确保逻辑高电平输出。

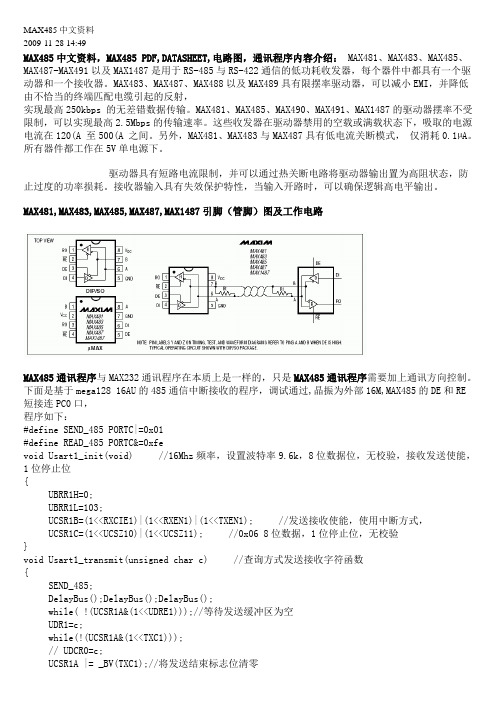

MAX481,MAX483,MAX485,MAX487,MAX1487引脚(管脚)图及工作电路MAX485通讯程序与MAX232通讯程序在本质上是一样的,只是MAX485通讯程序需要加上通讯方向控制。

下面是基于mega128 16AU的485通信中断接收的程序,调试通过,晶振为外部16M,MAX485的DE和RE短接连PC0口,程序如下:#define SEND_485 PORTC|=0x01#define READ_485 PORTC&=0xfevoid Usart1_init(void) //16Mhz频率,设置波特率9.6k,8位数据位,无校验,接收发送使能,1位停止位{UBRR1H=0;UBRR1L=103;UCSR1B=(1<<RXCIE1)|(1<<RXEN1)|(1<<TXEN1); //发送接收使能,使用中断方式,UCSR1C=(1<<UCSZ10)|(1<<UCSZ11); //0x06 8位数据,1位停止位,无校验}void Usart1_transmit(unsigned char c) //查询方式发送接收字符函数{SEND_485;DelayBus();DelayBus();DelayBus();while( !(UCSR1A&(1<<UDRE1)));//等待发送缓冲区为空UDR1=c;while(!(UCSR1A&(1<<TXC1)));// UDCR0=c;UCSR1A |= _BV(TXC1);//将发送结束标志位清零// SET_BIT(UCSR1A,);READ_485;direction++;}SIGNAL(SIG_UART1_RECV)//serial port 1 {if(UCSR1A&(1<<RXC1)){rec1buff=UDR1;rec1_flag=1;。

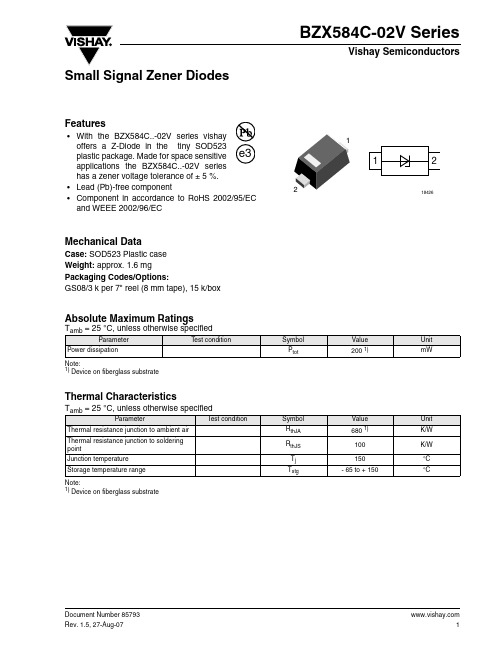

BZX584C2V7-02V中文资料

BZX584C-02V SeriesDocument Number 85793Rev. 1.5, 27-Aug-07Vishay Semiconductors1Small Signal Zener DiodesFeatures•With the BZX584C..-02V series vishay offers a Z-Diode in the tiny SOD523plastic package. Made for space sensitive applications the BZX584C..-02V series has a zener voltage tolerance of ± 5 %. •Lead (Pb)-free component•Component in accordance to RoHS 2002/95/EC and WEEE 2002/96/ECMechanical DataCase: SOD523 Plastic case Weight: approx. 1.6 mgPackaging Codes/Options:GS08/3 k per 7" reel (8 mm tape), 15 k/boxAbsolute Maximum RatingsT amb = 25°C, unless otherwise specifiedNote:1) Device on fiberglass substrateThermal CharacteristicsT amb = 25°C, unless otherwise specifiedNote:1)Device on fiberglass substrateParameterT est conditionSymbol Value Unit Power dissipationP tot200 1)mWParameterTest conditionSymbol Value Unit Thermal resistance junction to ambient air R thJA 680 1)K/W Thermal resistance junction to soldering pointR thJS 100K/W Junction temperature T j 150°C Storage temperature range T stg- 65 to + 150°C 2Document Number 85793Rev. 1.5, 27-Aug-07BZX584C-02V SeriesVishay Semiconductors Electrical CharacteristicsPartnumberMarking CodeZener Voltage Range Dynamic Resistance T est Current Temp. Coefficient of Zener Voltage T est Current Reverse Leakage Current V Z at 5 mAr zj at I ZT1r zj at I ZT2I ZT1αVZ at 5 mA I ZT2I R at V R V ΩmA10-4/°C mAµAVmin max min max BZX584C2V4-02V 2 2.2 2.670 (≤ 100)275 (≤ 600)5- 9.0- 4.01501BZX584C2V7-02V 3 2.5 2.975 (≤ 100)300 (≤ 600)5- 9.0- 4.01201BZX584C3V0-02V 42.83.280 (≤ 95)325 (≤ 600)5- 9.0- 3.01101BZX584C3V3-02V 5 3.1 3.585 (≤ 95)350 (≤ 600)5- 8.0- 3.0151BZX584C3V6-02V 63.4 3.885 (≤ 90)375 (≤ 600)5- 8.0- 3.0151BZX584C3V9-02V 7 3.74.185 (≤ 90)400 (≤ 600)5- 7.0- 3.0131BZX584C4V3-02V 84 4.680 (≤ 90)410 (≤ 600)5- 6.0- 1.0131BZX584C4V7-02V 9 4.4550 (≤ 80)425 (≤ 500)5-5.0+ 2.0132BZX584C5V1-02V 1 4.8 5.440 (≤ 60)400 (≤ 480)5- 3.0+ 4.0122BZX584C5V6-02V 0 5.2615 (≤ 40)80 (≤ 400)5- 2.0+6.0112BZX584C6V2-02V 1 5.8 6.6 6.0 (≤ 10)40 (≤ 150)5- 1.0+ 7.0134BZX584C6V8-02V 2 6.47.2 6.0 (≤ 15)30 (≤ 80)5+ 2.0+ 7.0124BZX584C7V5-02V 377.9 6.0 (≤ 15)30 (≤ 80)5+ 3.0+ 7.0115BZX584C8V2-02V T7.78.7 6.0 (≤ 15)40 (≤ 80)5+ 4.0+ 7.010.75BZX584C9V1-02V S 8.59.6 6.0 (≤ 15)40 (≤ 100)5+ 5.0+ 8.010.56BZX584C10-02V R9.410.68.0 (≤ 20)50 (≤ 150)5+ 5.0+ 8.010.27BZX584C11-02V P 10.411.610 (≤ 20)50 (≤ 150)5+ 5.0+ 9.010.18BZX584C12-02V 711.412.710 (≤ 25)50 (≤ 150)5+ 6.0+ 9.010.18BZX584C13-02V 512.414.110 (≤ 30)50 (≤ 170)5+ 7.0+ 9.010.18BZX584C15-02V 413.815.610 (≤ 30)50 (≤ 200)5+ 7.0+ 9.010.18BZX584C16-02V 15.317.110 (≤ 40)50 (≤ 200)5+ 8.0+ 9.510.050.7 V Znom BZX584C18-02V 16.819.110 (≤ 45)50 (≤ 225)5+ 8.0+ 9.510.050.7 V Znom BZX584C20-02V 18.821.215 (≤ 55)60 (≤ 225)5+ 8.0+ 1010.050.7 V Znom BZX584C22-02V 20.823.320 (≤ 55)60 (≤ 250)5+ 8.0+ 1010.050.7 V Znom BZX584C24-02V 22.825.625 (≤ 70)60 (≤ 250)5+ 8.0+ 1010.050.7 V Znom BZX584C27-02V 25.128.925 (≤ 80)65 (≤ 300)2+ 8.0+ 100.50.050.7 V Znom BZX584C30-02V K283230 (≤ 80)70 (≤ 300)2+ 8.0+ 100.50.050.7 V Znom BZX584C33-02V 313535 (≤ 80)75 (≤ 325)2+ 8.0+ 100.50.050.7 V Znom BZX584C36-02V 343835 (≤ 90)80 (≤ 350)2+ 8.0+ 100.50.050.7 V Znom BZX584C39-02V 374140 (≤ 130)80 (≤ 350)2+ 10+ 120.50.050.7 V Znom BZX584C43-02V 404645 (≤ 150)85 (≤ 375)2+ 10+ 120.50.050.7 V Znom BZX584C47-02V L 445050 (≤ 170)85 (≤ 375)2+ 10+ 120.50.050.7 V Znom BZX584C51-02VM485460 (≤ 180)85 (≤ 400)2+ 10+ 120.50.050.7 V Znom1241579P R1BZX584C-02V SeriesDocument Number 85793Rev. 1.5, 27-Aug-07Vishay Semiconductors3Package Dimensions in millimeters (inches): SOD523 4Document Number 85793Rev. 1.5, 27-Aug-07BZX584C-02V SeriesVishay SemiconductorsOzone Depleting Substances Policy StatementIt is the policy of Vishay Semiconductor GmbH to1.Meet all present and future national and international statutory requirements.2.Regularly and continuously improve the performance of our products, processes, distribution and operatingsystems with respect to their impact on the health and safety of our employees and the public, as well as their impact on the environment.It is particular concern to control or eliminate releases of those substances into the atmosphere which are known as ozone depleting substances (ODSs).The Montreal Protocol (1987) and its London Amendments (1990) intend to severely restrict the use of ODSs and forbid their use within the next ten years. Various national and international initiatives are pressing for an earlier ban on these substances.Vishay Semiconductor GmbH has been able to use its policy of continuous improvements to eliminate the use of ODSs listed in the following documents.1.Annex A, B and list of transitional substances of the Montreal Protocol and the London Amendmentsrespectively2.Class I and II ozone depleting substances in the Clean Air Act Amendments of 1990 by the EnvironmentalProtection Agency (EPA) in the USA3.Council Decision 88/540/EEC and 91/690/EEC Annex A, B and C (transitional substances) respectively. Vishay Semiconductor GmbH can certify that our semiconductors are not manufactured with ozone depleting substances and do not contain such substances.We reserve the right to make changes to improve technical designand may do so without further notice.Parameters can vary in different applications. All operating parameters must be validated for each customer application by the customer. Should the buyer use Vishay Semiconductors products for any unintended or unauthorized application, the buyer shall indemnify Vishay Semiconductors against all claims, costs, damages, and expenses, arising out of, directly or indirectly, any claim of personal damage, injury or death associatedwith such unintended or unauthorized use.Vishay Semiconductor GmbH, P.O.B. 3535, D-74025 Heilbronn, GermanyDocument Number: 91000Revision: 18-Jul-081DisclaimerLegal Disclaimer NoticeVishayAll product specifications and data are subject to change without notice.Vishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively, “Vishay”), disclaim any and all liability for any errors, inaccuracies or incompleteness contained herein or in any other disclosure relating to any product.Vishay disclaims any and all liability arising out of the use or application of any product described herein or of any information provided herein to the maximum extent permitted by law. The product specifications do not expand or otherwise modify Vishay’s terms and conditions of purchase, including but not limited to the warranty expressed therein, which apply to these products.No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of Vishay.The products shown herein are not designed for use in medical, life-saving, or life-sustaining applications unless otherwise expressly indicated. Customers using or selling Vishay products not expressly indicated for use in such applications do so entirely at their own risk and agree to fully indemnify Vishay for any damages arising or resulting from such use or sale. Please contact authorized Vishay personnel to obtain written terms and conditions regarding products designed for such applications.Product names and markings noted herein may be trademarks of their respective owners.元器件交易网。

5841中文资料

I To 3.3 MHz Data-Input Rate

I CMOS, NMOS, TTL Compatible Inputs

I Internal Pull-Up/Pull-Down Resistors

I Low-Power CMOS Logic and Latches,

I High-Voltage Current-Sink Outputs

5 LOGIC SUPPLY

SERIAL-PARALLEL SHIFT REGISTER

6

SERIAL DATA OUT

LATCHES

7 STROBE

8

OUTPUT ENABLE (ACTIVE LOW)

MOS

BIPOLAR

18

17

16

15

14

13

12

11

10

OUT 1 OUT 2 OUT 3 OUT 4 OUT 5 OUT 6 OUT 7 OUT 8 K

TS . . . . . . . . . . . . . . . -55°C to +150°C

†For inductive load applications.

Caution: CMOS devices have input static protection but are susceptible to damage when exposed to extremely high static electrical charges.

SUB

1

POWER GROUND

9

Dwg. FP-013-2

A5841SLW & A5842SLW

POWER GROUND

SG5842

Product Specification

SG5842A/JA PIN CONFIGURATION

GND FB VIN RI

GATE VDD SENSE RT

6

SENSE

Current Sense

Current sense. The sensed voltage is used for peak-current-mode control and cycle-by-cycle current limiting.

7

VDD

Power Supply Power supply. The internal protection circuit disables PWM output if VDD is over-voltage.

ORDERING INFORMATION

Part Number

OTP Latch OVP Latch Frequency Hopping Pb-Free

SG5842JASZ

Yes

Yes

Yes

SG5842JADZ

Yes

Yes

Yes

SG5842ASZ (Preliminary) Yes

Yes

No

SG5842ADZ (Preliminary Yes

Highly Integrated Green-Mode PWM Controller

FEATURES

Green-Mode PWM Controller Low Start-up Current (14µA) Low Operating Current (4mA) Programmable PWM Frequency with Hopping

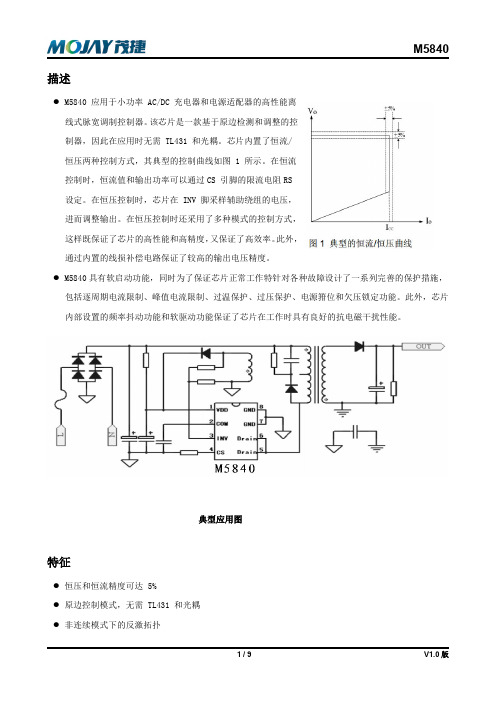

M5840-V2.0规格书(中文)

恒流工作

M5840 的恒压/恒流特征曲线如图 1 所示。M5840 被设计应用于工作在非连续模式下的反激式系统中。

在正常工作时,当 INV 电压低于内部 2.0V 的基准电压好时,系统工作在恒流模式,否则系统工作在恒压

模式。当次级输出电流达到了系统设定的最大电流时,系统就进入恒流模式,并且会引起输出电压的下降。

电气参数 (Ta=25oC, 其余情况会做说明)

(如无特殊说明, VIN=12V(注 1), TA=25℃)

参数

启动电流

工作电流

进入欠压锁定的阈值电压 退出欠压锁定的阈值电压 过压保护的阈值电压 电源箝位电压 内置 MOS 管耐压值 MOS 管导通电阻值 前沿消隐时间 过流保护阈值 过流保护延迟 输入阻抗 软启动时间 正常工作频率 启动频率 频率抖动幅度 误差放大器的输入基准电压 误差放大器的直流增益 线损补偿最大电流 输出低电平

由于 TDemag 与电感的大小成反比,因此,电感 LP 和 FSW 的乘积为一定值,从而限制了最大的输 出功率,避免了系统进入连续工作模式。

电流检测和前沿消隐 M5840 采样功率 MOSFET 上的电流是通过 CS 来实现的。 M5840 不仅设计了逐周期的电流限制,而

且设计了峰值电流限制,最大的峰值电流电压为 0.9V。因此,MOSFET 上最大的峰值电流为:

随着输出电压的下降,反馈电压也跟着下降,芯片内部的 VCO 将

会调整开关的频率,以使输出功率保持和输出电压成正比,其结

果就是使输出电流保持恒定。这就是恒流的原理。在恒流模式下,

无论输出电压如何变化,输出电流为一常数。在作为充电器应用

时,先是恒流充电直到接近电池充饱的状态,随后再进行恒压充

电。在 M5840 中, 恒流值和最大输出功率可以通过外部的限流

MAX1682-MAX1683中文资料

ELECTRICAL CHARACTERISTICS

(VIN = +5.0V, capacitor values from Table 2, TA = 0°C to +85°C, unless otherwise noted. Typical values are at TA = +25°C.) PARAMETER No-Load Supply Current Supply Voltage Range Minimum Operating Voltage Oscillator Frequency Output Resistance Voltage Conversion Efficiency TA = +25°C RLOAD = 10kΩ (Note 2) TA = +25°C IOUT = 5mA IOUT = 0mA, TA = +25°C MAX1682 MAX1683 TA = +25°C TA = 0°C to +85°C 98 99.9 8.4 24.5 CONDITIONS MAX1682 MAX1683 TA = +25°C TA = 0°C to +85°C 2.0 2.1 MIN TYP 110 230 1.7 1.8 1 12 35 20 15.6 45.5 50 65 MAX 145 310 5.5 5.5 UNITS µA V V kHz Ω %

OUTPUT RESISTANCE vs. SUPPLY VOLTAGE

80 OUTPUT RESISTANCE (Ω) 70 60 50 40 30 20 10 1.0 1.5 2.0 2.5 3.0 3.5 4.0 4.5 5.0 5.5 VIN (V) MAX1683, C1 = C2 = 10µF MAX1682, C1 = C2 = 10µF MAX1683, C1 = C2 = 3.3µF

MAX742中文资料

MAX742

CC-

+5V INPUT

+2.0V VREF

R -SENSE

PWM

S -DRIVE

P

-VO

OSC +VO

S +DRIVE

N

PWM

R +SENSE

CC+

________________________________________________________________ Maxim Integrated Products 1

Operating Temperature Ranges MAX742C_ _ .......................................................0°C to +70°C MAX742E_ _ ....................................................-40°C to +85°C MAX742MJP ..................................................-55°C to +125°C

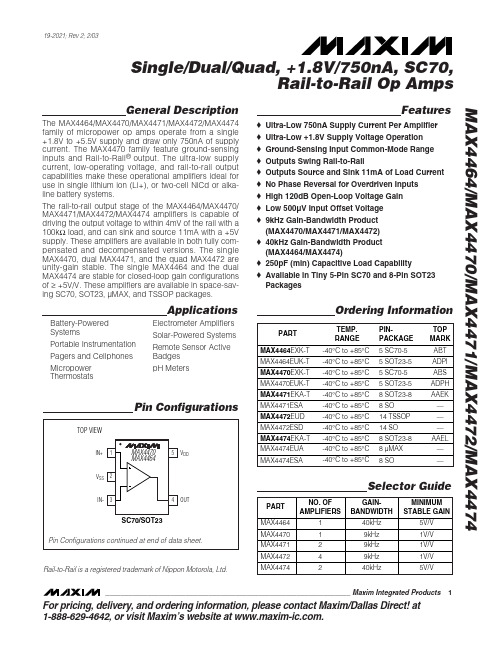

MAX4472中文资料

Features

o Ultra-Low 750nA Supply Current Per Amplifier o Ultra-Low +1.8V Supply Voltage Operatommon-Mode Range o Outputs Swing Rail-to-Rail o Outputs Source and Sink 11mA of Load Current o No Phase Reversal for Overdriven Inputs o High 120dB Open-Loop Voltage Gain o Low 500µV Input Offset Voltage o 9kHz Gain-Bandwidth Product

NPC_SM5842AP

SM5842AP/APTHigh-Class Audio Multi-function Digital FilterOVERVIEWThe SM5842AP/APT is a multi-function digital filter IC, fabricated using NPC’s Molybdenum-gate CMOS process, for digital audio reproduction equip-ment. It features 8-times oversampling (interpola-tion), independent left and right-channel digital deemphasis, and soft muting functions. It accepts 16, 18, 20 or 24-bit input data, and outputs data in 18, 20, 22 or 24-bit format. It operates using either a 384fs or 256fs system clock at sampling frequencies up to 48 kHz + 10% (384fs SM5842AP, 384/256fs SM5842APT).FEATURESFunctionss L/R 2-channel processings8-times oversampling (interpolation)•≤ ±0.00002 dB passband ripple•≥ 117 dB stopband attenuations Digital deemphasis•32/44.1/48 kHz sampling frequency (fs)•2-channel independent ON/OFF controls Soft muting•2-channel independent ON/OFF controls Input data format•2s complement, MSB first-LR alternating, 16/18/20/24-bit serial, trail-ing data-LR alternating, 24-bit serial, leading data-LR simultaneous, 24-bit serial, leading data s Output data format•2s complement, MSB first, LR simultaneous •18/20/22/24-bit serial•BCKO burst (NPC format)s Dither round-up processing•ON (dither rounding)/OFF (normal rounding) controls25-bit internal data lengths Jitter-free function for correct operation in the presence of jitter between the system clock and LRCI clock•ON (jitter-free mode)/OFF (sync mode) control s256fs/384fs system clock selectable•384fs-21.2 MHz maximum frequency (at maximumfs = 55.2 kHz)•256fs-13 MHz maximum frequency (at maximumfs = 50.7 kHz, SM5842AP)-14.2 MHz maximum frequency (at maximumfs = 55.2 kHz, SM5842APT)s Crystal oscillator circuit built-ins TTL-compatible input/outputss 5.0 ± 0.25 V supplys Molybdenum-gate CMOS processs28-pin plastic DIPFilter Configurations Linear phase 3-stage FIR interpolation filter •169-tap 1st stage (fs to 2fs)•29-tap 2nd stage (2fs to 4fs)•17-tap 3rd stage (4fs to 8fs)s Deemphasis filter-IIR filter configuration for accurate gain andphase characteristicss26 × 24-bit parallel multiplier/32-bit accumulator for high precisions Overflow limiter built-in APPLICATIONSs CD playerss DAT playerss PCM systemsPINOUTSM5842AP/APT PACKAGE DIMENSIONSUnit: mm28-pin plastic DIPBLOCK DIAGRAMSM5842AP/APTPIN DESCRIPTIONNumber Name I/O 1 Description1DI/INF2N Ip Data input when INF1N is LOW, and input format select pin 2 when INF1N is HIGH.2BCKI Ip Input bit clock3CKSLNIpOscillator and system clock select input. 384fs when HIGH, and 256fs when LOW.4INF1NIpInput format select pin 1. INF1N and INF2N select the pin functions below.5IW1N/DILIpInput bit length select pin 1 when INF1N is LOW, and left-channel data input when INF1N is HIGH. IW1N and IW2N select the input data length.6XTI I Oscillator input connection 7XTO O Oscillator output connection 8VSS –Ground9CKO O Oscillator output clock. Same frequency as XTI.10IW2N/DIRIpInput bit length select pin 2 when INF2N is LOW, and right-channel data input when INF2N is HIGH. IW1N and IW2N select the input data length as shown in the table for pin 5.11OW1NIpOutput length select bits.12OW2NIp13SYNCN Ip Sync mode select pin. Normal sync mode when LOW, and jitter-free mode when HIGH.14RSTN Ip System reset. Reset operation when LOW, and normal operation when HIGH.15DEMPR Ip Right-channel deemphasis control signal. OFF when LOW, and ON when HIGH.16DEMPRIpLeft-channel deemphasis control signal. OFF when LOW, and ON when HIGH.17FSEL1IpDeemphasis filter select inputs18FSEL2IpINF1NDI/INF2N Input formatPin function selection DI/INF2N IW1N/DIL IW2N/DIR LOW LOW LR alternating, trailing data DIIW1NIW2NLOW HIGH HIGH LOW LR alternating, leading data INF2N DIL DIRHIGHHIGHLR simultaneous, leading dataINF1NIW2N/DIL IW1N/DIR Input bit lengthLOWLOWLOW 24 bits LOW HIGH 20 bits HIGH LOW 18 bits HIGHHIGH 16 bits HIGH××24 bitsOW2N OW1N Output bit lengthLOW LOW 24 bits LOWHIGH 22 bits HIGH LOW 20 bits HIGHHIGH18 bitsFSEL1FSEL2Sampling frequency (fs)LOW LOW 44.1 kHz LOWHIGH 48 kHz HIGH LOW Invalid setting HIGHHIGH32 kHzSM5842AP/APTNumber Name I/O1Description 19MUTER Ip Right-channel mute signal. Muting when HIGH, and normal output when LOW.20MUTEL Ip Left-channel mute signal. Muting when HIGH, and normal output when LOW.21DITHN Ip Dither processing control. ON when LOW, and OFF when HIGH.22VDD– 5 V supply23DOR O Right-channel data output24DOL O Left-channel data output25WCKO O Output word clock26BCKO O Output bit clock27DG O Deglitched output28LRCI Ip Input data sample rate (fs) clock1. I = input, Ip = Input with pull-up resistor, O = outputSM5842AP/APTSPECIFICATIONSAbsolute Maximum RatingsV SS = 0 VRecommended Operating ConditionsV SS = 0 VDC Electrical CharacteristicsV DD = 4.75 to 5.25 V , V SS = 0 V , T a = − 20 to 80 ° CParameterSymbol Rating Unit Supply voltage range V DD − 0.3 to 7.0V Input voltage range V IN − 0.3 to V DD + 0.3V Storage temperature range T stg − 40 to 125 ° C Power dissipation P D 550mW Soldering temperature T sld 255 ° C Soldering timet sld10sParameterSymbol ConditionRating Unit Supply voltage range V DD 4.75 to 5.25V Operating temperature rangeT oprSM5842AP − 20 to 80 ° CSM5842APT− 20 to 70ParameterSymbol ConditionRatingUnit min typ max Current consumption I DD V DD = 5.0 V 11. f SYS = 256fs = 14.2 MHz (CKSLN = LOW), no output load–6080mA XTI HIGH-level input voltage V IH1 0.7V DD ––V XTI LOW-level input voltage V IL1 ––0.3V DD V HIGH-level input voltage 2 2. Pins DI/INF2N, BCKI, CKSLN, INF1N, IW1N/DIL, IW2N/DIR, OW1N, OW2N, SYNCN, RSTN, DEMPR, DEMPL, FSEL1, FSEL2, MUTER, MUTEL,DITHN, LRCIV IH2 2.4––V LOW-level input voltage 2 V IL2 ––0.5V HIGH-level output voltage 3 3. Pins CKO, DOL, DOR, BCKO, WCKO, DGV OH1 I OH = − 0.4 mA 2.5––V LOW-level output voltage 3 V OL1 I OL = 1.6 mA ––0.4V XTO HIGH-level output voltage V OH2 I OH = − 1.0 mA V DD − 0.5––V XTO LOW-level output voltage V OL2 I OL = 1.0 mA ––0.4V XTI HIGH-level input current I LH V IN = V DD –1020µA XTI LOW-level input current I LL1 V IN = 0 V –1020µA LOW-level input current 2 I LL2 V IN = 0 V –1020µA Input leakage current 2I IHV IN = V DD––1.0µASM5842AP/APTAC Electrical CharacteristicsInput Clock (XTI: SM5842AP)Crystal oscillatorfs = 384fs (CKSLN = HIGH): V DD = 4.75 to 5.25 V , V SS = 0 V , T a = − 20 to 80 ° Cfs = 256fs (CKSLN = LOW): V DD = 4.75 to 5.25 V , V SS = 0 V , T a = − 20 to 80 ° CExternal clock inputfs = 384fs (CKSLN = HIGH): V DD = 4.75 to 5.25 V , V SS= 0 V , T a = − 20 to 80 ° Cfs = 256fs (CKSLN = LOW): V DD = 4.75 to 5.25 V , V SS = 0 V , T a = − 20 to 80 ° CParameterSymbol RatingUnit min typ max Oscillator frequencyf OSC2.0–21.2MHzParameterSymbol RatingUnit min typ max Oscillator frequencyfOSC1.0–13.0MHzParameterSymbol RatingUnit min typ max Clock HIGH-level pulsewidth t CWH 20–250ns Clock LOW-level pulsewidth t CWL 20–250ns Clock pulse cycle timet XI47–500nsParameterSymbol RatingUnit min typ max Clock HIGH-level pulsewidth t CWH 35–500ns Clock LOW-level pulsewidth t CWL 35–500ns Clock pulse cycle timet XI76–1000nsInput Clock (XTI: SM5842APT)Crystal oscillatorfs = 384fs (CKSLN = HIGH): V DD = 4.75 to 5.25 V , V SS = 0 V , T a = −20 to 70 °Cfs = 256fs (CKSLN = LOW): V DD = 4.75 to 5.25 V , V SS = 0 V , T a = −20 to 70 °CExternal clock inputfs = 384fs (CKSLN = HIGH): V DD = 4.75 to 5.25 V , V SS = 0 V , T a = −20 to 70 °Cfs = 256fs (CKSLN = LOW): V DD = 4.75 to 5.25 V , V SS = 0 V , T a= −20 to 70 °CParameterSymbol RatingUnit min typ max Oscillator frequencyf OSC2.0–21.2MHzParameterSymbol RatingUnit min typ max Oscillator frequencyf OSC1.0–14.2MHzParameterSymbol RatingUnit min typ max Clock HIGH-level pulsewidth t CWH 20–250ns Clock LOW-level pulsewidth t CWL 20–250ns Clock pulse cycle timet XI47–500nsParameterSymbol RatingUnit min typ max Clock HIGH-level pulsewidth t CWH 30–500ns Clock LOW-level pulsewidth t CWL 30–500ns Clock pulse cycle timet XI70–1000nsSerial input timing (BCKI, DI, DIL, DIR, LRCI)SM5842AP: V DD = 4.75 to 5.25 V, V SS = 0 V, T a = −20 to 80 °C SM5842APT: V DD = 4.75 to 5.25 V, V SS = 0 V, T a = −20 to 70 °COutput timingSM5842AP: V DD = 4.75 to 5.25 V, V SS = 0 V, T a = −20 to 80 °C, C L = 15 pF SM5842APT: V DD = 4.75 to 5.25 V, V SS = 0 V, T a = −20 to 70 °C, C L = 15 pFParameter Symbol ConditionRatingUnit min typ maxXTI to XTO delay t XTO XTI fall to XTO rise3–15ns XTI to CKO delay t CKO XTI fall to CKO fall10–35nsXTI to BCKO delay (CKSLN = HIGH)t sbH XTI fall to BCKO rise20–65ns t sbL XTI fall to BCKO fall20–65XTI to BCKO delay (CKSLN = LOW)t sbH XTI fall to BCKO rise20–65ns t sbL XTI fall to BCKO fall20–65BCKO to DOL, DOR, WCKO delay t bdH BCKO fall to output rise−5–10ns t bdL BCKO fall to output fall−5–10CKO to DOL, DOR, WCKO, DG delay t cdH CKO fall to output rise12–45ns t cdL CKO fall to output fall12–45XTO to DOL, DOR, WCKO, DG delay t xdH XTO rise to output rise15–50ns t xdL XTO rise to output fall15–50Filter Characteristics8-times interpolation filterParameter Rating Passband0 to 0.4535fs Stopband0.5465fs to 7.4535fs Passband ripple≤ ±0.00002 dB Stopband attenuation≥ 117 dB Group delay Fixed8fs filter response with deemphasis OFF8fs filter transition response with deemphasis OFFDeemphasis filterPassband response with deemphasis ON (logarithmic frequency axis)ParameterSampling frequency (fs)32 kHz 44.1 kHz 48 kHz Passband bandwidth (kHz)0 to 14.50 to 20.00 to 21.7Deviation from ideal characteristicAttenuation ≤ ±0.001 dB Phase, θ0 to 1.5°FUNCTIONAL DESCRIPTIONThe basic arithmetic block is shown in figure 1, and the function of each block is described in the follow-ing sections.8-times Oversampling (Interpolation) The interpolation arithmetic block is comprised of 3 cascaded, 2-times FIR interpolation filters, as shown in figure 1.The input signal is sampled at rate fs, and then 8-times oversampling data is output. Sampling noise in the 0.5465fs to 7.4535fs stopband is removed by the interpolation filter.Digital DeemphasisThe digital deemphasis filter has the same construc-tion as analog filters. It is implemented as an IIR fil-ter to faithfully reproduce the gain and phase characteristics of standard analog deemphasis filters. The three sets of filter coefficients for the three fs = 32.0/44.1/48.0 kHz sampling frequencies are selected by FSEL1 and FSEL2 when the sampling frequency is specified, as shown in table 1. Indepen-dent deemphasis for the left and right channel is con-trolled independently by DEMPL and DEMPR, respectively. Digital deemphasis is ON when DEMPL/DEMPR is HIGH, and OFF when DEMPL/DEMPR is LOW.Figure 1. Arithmetic block diagramTable 1. Sampling frequency selectFSEL1FSEL2Sampling frequency (fs)LOW LOW44.1 kHzLOW HIGH48 kHzHIGH LOW Invalid settingHIGH HIGH32 kHzSoft MutingMuting of the left and right channel is controlled independently by MUTEL and MUTER, respec-tively. Muting is ON when MUTEL/MUTER is HIGH, muting is OFF when MUTEL/MUTER is LOW.When MUTEL/MUTER goes HIGH, the attenuation changes smoothly from 0 to −∞ dB in 512/fs, or approximately 11.6 ms when fs = 44.1 kHz. When MUTEL/MUTER goes LOW, muting is released and the attenuation changes smoothly from −∞ to 0 dB, again taking approximately 11.6 ms.When RSTN goes LOW, the DOL and DOR outputs go LOW, immediately muting the output signal. Muting is released and timing is synchronized when RSTN goes HIGH.System Clock (XTI, XTO, CKO, CKSLN)Two system clock frequencies, 384fs and 256fs, can be used. An external clock source can be input on XTI, or a crystal oscillator can be constructed by connecting a crystal between XTI and XTO. The system clock is also buffered and then output on CKO. The system clock frequency selection and the internal clock frequency are shown in table 2.Table 2. System clock frequency selectParameterCKSLNHIGH LOW XTI input clock frequency (f XI = 1/t XI)384fs256fs CKO clock frequency384fs256fs Internal clock frequency (t SYS) 2 × t XI t XIFigure 2. Clock generator circuitAudio Data Input (INF1N, INF2N, IW1N, IW2N, DI, DIL, DIR, BCKI, LRCI) The input data format and several input pin functionsare selected by the state of INF1N and INF2N asshown in table 3.The input data word length is selected by the state of IW1N and IW2N when INF1N is LOW. 24-bit is selected when INF1N is HIGH.Jitter-free Function (SYNCN)The arithmetic circuit and output control timing is derived from the system clock, and is therefore inde-pendent of the input LRCI and BCKI clocks. Accordingly, any jitter in the data input clock (LRCI and BCKI) does not cause jitter in the output. Generally, the internal timing is synchronized to the LRCI input timing after a system reset release, when RSTN goes from LOW to HIGH, on the first LRCI clock start edge. If the input timing and LRCI start edge timing subsequently drift, the input timing is automatically resynchronized when the timing error exceeds a certain value. There are 2 timing error val-ues at which resynchronization occurs, selected by the state of SYNCN.Jitter-free mode (SYNCN = HIGH)When SYNCN is HIGH, the timing error value is ±3/8 × (LRCI clock period). When the difference between the input timing and LRCI start edge posi-tion do not exceed this value, internal timing is not resynchronized and all functions continue to operate normally.Sync mode (SYNCN = LOW)When SYNCN is LOW, the timing error value is ±1× (system clock period), which is a much smaller timing error tolerance than in jitter-free mode. In this mode, the internal timing is guaranteed to follow the LRCI clock timing within this tolerance, making this mode useful for systems constructed from a multiple number of SM5842AP/APT devices.Note that resynchronization affects the internal oper-ation and can generate a momentary click noise out-put.T able 3. Pin function selectINF1N DI/INF2N Input formatPin function selectionDI/INF2N IW1N/DIL IW2N/DIR LOW LOWLR alternating1, trailing data DI IW1N IW2N LOW HIGHHIGH LOW LR alternating, leading dataINF2N DIL DIR HIGH HIGH LR simultaneous2, leading data1. Alternating left-channel and right-channel data input on a single input DI.2. Simultaneous left-channel and right-channel data input on two inputs, DIL and DIR, respectively.T able 4. Input word lengthINF1N IW2N/DIL IW1N/DIR Input word lengthLOW LOW LOW24 bits LOW HIGH22 bits HIGH LOW18 bits HIGH HIGH16 bitsHIGH××24 bitsAudio Data Output (DOL, DOR, BCKO, WCKO, OW20N)The output data is in serial, simultaneous left and right-channel, 2s complement, MSB first, BCKO burst (NPC format) format. The output data word length is selected by the state of OW1N and OW2N as shown in table 5.T able 5. Output word length selectOW1N OW2N Output word lengthLOW LOW24 bitsLOW HIGH22 bitsHIGH LOW20 bitsHIGH HIGH18 bits8fs serial data is output in sync with the falling edge of the internal system clock and BCKO clock. The output timing is determined by CKSLN and the out-put word length. When CKSLN is LOW, the output timing is the same for different output word lengths. Only the number of BCKO bit clock pulses word changes depending on the output word length selected. When CKSLN is HIGH, however, the out-put timing for 24-bit output mode starts 1 bit earlier than for 18/20/22-bit output mode.T able 6. Output timingParameter Symbol CKSLN = HIGH CKSLN = LOW Bit clock rate t B1/192fs1/256fs Data word length t DW24t SYS32t SYSSystem Reset (RSTN)Under normal operating conditions, the SM5842AP/APT does not need to be reset. However, it can be reset when you want to synchronize the LRCI clock and internal operation timing in jitter-free mode.The system is reset by applying a LOW-level pulse on RSTN.The arithmetic and output timing counters are reset on the first LRCI start edge after reset is released, as long as the XTI clock has already stabilized. The LRCI start edge is determined by the state of INF1N and INF2N. When INF1N is LOW or when both INF1N and INF2N are HIGH, the start edge is the rising edge. When INF1N is HIGH and INF2N is LOW, the start edge is the falling edge.When RSTN is LOW, the DOL and DOR outputs are LOW, muting the output signal to an attenuation level of −∞.The power-ON reset pulse can be applied by a microcontroller or, for systems where XTI and LRCI are stable at power-ON, by connecting a capacitor of about 300 pF between RSTN and VSS. For systems that do not use a microcontroller, the capacitor must be chosen such that the XTI and LRCI clocks fully stabilize before RSTN goes from LOW to HIGH.Figure 3. System reset timing and output mutingTIMING DIAGRAMSInput Timing Examples (DIN, BCKI, LRCI)INF1N = LOW, IW1N = IW2N = HIGHFigure 4. LR alternating, trailing data, 16-bit inputData following LSB is ignored. Requires minimum 24 BCKI clock pulses.Figure 5. LR alternating, leading data, 24-bit inputINF1N = INF2N = HIGH.Data following LSB is ignored. Requires minimum 24 BCKI clock pulses.Figure 6. LR simultaneous, leading data, 20-bit inputOutput Timing Examples (DOL, DOR, BCKO, WCKO, DG)The number of output bits is determined by the output bit length selected.Figure 7. 18/20/22-bit output (CKSLN = HIGH)Figure 8. 24-bit output (CKSLN = HIGH)The number of output bits is determined by the output bit length selected.Figure 9. 24-bit output (CKSLN = LOW)Data Input to Output Delay TimingThis is the digital filter arithmetic computation time from the completion of data input at rate fs (t INPUT) on the rising edge of LRCI to the start of data output at rate 8fs (t OUTPUT) on the falling edge of WCKO.T able 7. Output delayCKSLN SYNCN Mode t OUTPUT− t INPUTLOW After reset + sync mode48.625/fs LOW (256fs)HIGH Jitter-free mode48.25/fs − 49.0/fsLOW After reset + sync mode48.75/fs HIGH (384fs)HIGH Jitter-free mode48.375/fs − 49.125/fsFigure 10. Delay timing 1Figure 11. Delay timing 2APPLICATION CIRCUITSInput Interface CircuitsCD decoder (CXD2500Q) connectionDigital audio interface receiver (YM3623B) connectionOutput Interface Circuits20-bit input Σ∆ DAC (SM5864AP) connection 1 384fs512fs20-bit input Σ∆ DAC (SM5864AP) connection 2L/R-channel independent complementary PWM output20-bit input R − 2R DAC (PCM63P) connectionL/R-channel independentNC9714AE1998.2This datasheet has been downloaded from:Free DownloadDaily Updated Database100% Free Datasheet Search Site100% Free IC Replacement Search SiteConvenient Electronic DictionaryFast Search SystemAll Datasheets Cannot Be Modified Without PermissionCopyright © Each Manufacturing Company。

MIC5841YWM TR;MIC5841YWM;MIC5841YN;MIC5841YV;MIC5842YN;中文规格书,Datasheet资料

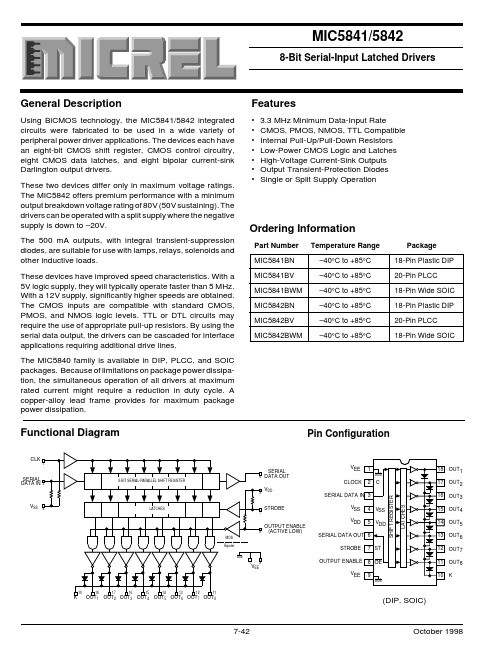

MIC5841/58428-Bit Serial-Input Latched DriversMicrel Inc. • 2180 Fortune Drive • San Jose, CA 95131 • USA • tel +1 (408) 944-0800 • fax + 1 (408) 474-1000 • General DescriptionUsing BiCMOS technology, the MIC5841/5842 integrated circuits were fabricated to be used in a wide variety of peripheral power driver applications. The devices each have an eight-bit CMOS shift register, CMOS control circuitry, eight CMOS data latches, and eight bipolar current-sink Darlington output drivers.These two devices differ only in maximum voltage ratings. The MIC5842 offers premium performance with a minimum output breakdown voltage rating of 80V (50Vsustaining). The drivers can be operated with a split supplywhere the negative supply is down to –20V.The 500mA outputs, with integral transient-suppressiondiodes, are suitable for use with lamps, relays, solenoids and other inductive loads.These devices have improved speed characteristics. With a 5V logic supply, they will typically operate faster than 5 MHz. With a 12V supply, significantly higher speeds are obtained. The CMOS inputs are compatible with standard CMOS, PMOS, and NMOS logic levels. TTL or DTL circuits may require the use of appropriate pull-up resistors. By using the serial data output, the drivers can be cascaded for interface applications requiring additional drive lines.The MIC5840 family is available in DIP, PLCC, and SOIC packages. Because of limitations on package power dissipation, the simultaneous operation of all drivers at maximum rated current might require a reduction in duty cycle. A copper-alloy lead frame provides for maximum package power dissipation.Features• 3.3 MHz Minimum Data-Input Rate • CMOS, PMOS, NMOS, TTL Compatible• Internal Pull-Up/Pull-Down Resistors • Low-Power CMOS Logic and Latches• High-Voltage Current-Sink Outputs• Output Transient-Protection Diodes • Single or Split Supply OperationOrdering InformationPart NumberStandard Pb-Free Temperature RangePackage MIC5841BN MIC5841YN –40ºC to +85ºC 18-Pin Plastic DIP MIC5841BV MIC5841YV –40ºC to +85ºC 20-Pin PLCC MIC5841BWM MIC5841YWM –40ºC to +85ºC 18-Pin Wide SOIC MIC5842BN MIC5842YN –40ºC to +85ºC 18-Pin Plastic DIP MIC5842BV MIC5842YV –40ºC to +85ºC 20-Pin PLCC MIC5842BWM MIC5842YWM–40ºC to +85ºC18-Pin Wide SOICFunctional DiagramSERIAL DATA OUT CLKV S SV DDS T R O B EOUTPUT ENABLE (ACTIVE LOW)87654321Absolute Maximum Ratings (1,2,3)At 25°C Free-Air Temperature and V SS ...................0V Output Voltage, V CE (MIC5841)............................. 50V (MIC5842)..............................80V Output Voltage, V CE(SUS) (MIC5841)(1)..................................35V (MIC5842)........................50V Logic Supply Voltage, V DD .......................................15V VDD with Reference to V EE . (25V)Emitter Supply Voltage, V EE ...................................–20V Input Voltage Range, V IN ...............–0.3V to V DD + 0.3V Continuous Output Current, I OUT .........................500mA Package Power Dissipation, P D (2)........................1.82W Operating Temperature Range, T A .......–55°C to +85°C Storage Temperature Range, T S ........–65°C to +150°CElectrical CharacteristicsAt T A = 25°C V DD = 5V, V SS = V EE = 0V (unless otherwise noted)LimitsCharacteristic Symbol Applicable Devices Test ConditionsMin Max Unit V OUT = 50V50 MIC5841V OUT = 50V, T A = +70ºC100 V OUT = 80V50 Output Leakage CurrentI CEXMIC5842 V OUT = 80V, T A = +70ºC100 µAI OUT = 100mA1.1 I OUT = 200mA1.3 Collector-Emitter Saturation VoltageV CE(SAT) Both I OUT = 350mA, V DD = 7.0V1.6V MIC5841 I OUT = 350mA, L = 2mH35Collector-Emitter Saturation Voltage V CE(SUS)(5)MIC5842 I OUT = 350mA, L = 2mH50V V IN(0) Both0.8V DD = 12V 10.5 V DD = 10V 8.5 Input VoltageV IN(1) BothV DD = 5.0V(4)3.5 V V DD = 12V50 V DD = 10V 50 Input ResistanceR IN Both V DD = 5.0V50k Ω All Drivers ON, V DD = 12V16All Drivers ON, V DD = 10V 14 IDD (ON) Both All Drivers ON, V DD = 5.0V 8.0 All Drivers OFF, V DD = 12V 2.9 All Drivers OFF, V DD = 10V 2.5 Supply CurrentIDD (OFF) BothAll Drivers OFF, V DD = 5.0V1.6 1.6 MIC5841 V R = 50V50 Clamp Diode Leakage Current I R MIC5842 V R = 80V50 µA Clamp Diode Forward VoltageV F Both I F = 350mA2.0 VElectrical CharacteristicsAt T A = –55°C V DD = 5V, V SS = V EE = 0V (unless otherwise noted)LimitsCharacteristic Symbol Test Conditions Min Max Unit Output Leakage CurrentI CEX V OUT = 80V 50 µA I OUT = 100mA 1.3 I OUT = 200mA1.5 Collector-Emitter Saturation VoltageV CE(SAT)I OUT = 350mA, V DD = 7.0V1.8 V V IN(0)0.8 V DD = 12V 10.5 Input VoltageV IN(1)V DD = 5.0V3.5 V V DD = 12V35 V DD = 10V 35 Input ResistanceR IN V DD = 5.0V35k Ω All Drivers ON, V DD = 12V16All Drivers ON, V DD = 10V 14 I DD(ON) All Drivers ON, V DD = 5.0V10 All Drivers OFF, V DD = 12V3.5 Supply CurrentI DD(OFF) All Drivers OFF, V DD = 5.0V2.0mAElectrical CharacteristicsAt T A = +125°C V DD = 5V, V SS = V EE = 0V (unless otherwise noted)LimitsCharacteristic Symbol Test Conditions Min Max Unit Output Leakage CurrentI CEX V OUT = 80V 500 µA I OUT = 100mA 1.3 I OUT = 200mA1.5 Collector-Emitter Saturation VoltageV CE(SAT)I OUT = 350mA, V DD = 7.0V1.8 V V IN(0)0.8 V DD = 12V 10.5 Input VoltageV IN(1)V DD = 5.0V3.5 V V DD = 12V50 V DD = 10V 50 Input ResistanceR IN V DD = 5.0V50 k Ω All Drivers ON, V DD = 12V16 All Drivers ON, V DD = 10V 14 I DD(ON) All Drivers ON, V DD = 5.0V 8 All Drivers OFF, V DD = 12V 2.9 Supply CurrentI DD(OFF)All Drivers OFF, V DD = 5.0V2.1.6 mA MIC5841A V R = 50V1.6 µA Clamp Diode Leakage CurrentI R MIC5842A V R = 80V100Notes :1. For Inductive load applications.2. Derate at the rate of 18.2mW/°C above TA = 25°C (Plastic DIP)3. CMOS devices have input-static protection but are susceptible to damage when exposed to extremely high static electrical charges.4. Operation of these devices with standard TTL may require the use of appropriate pull-up resistors to insure an input logic HIGH.5. Not 100% tested. Guaranteed by design.Timing Conditions(TA = 25°C Logic Levels are V DD and V SS ) V DD = 5V A. Minimum Data Active Time Before Clock Pulse (Data Set-Up Time)...................................................................... 75 ns B. Minimum Data Active Time After Clock Pulse (Data Hold Time) ............................................................................75 ns C. Minimum Data Pulse Width ...................................................................................................................................150 ns D. Minimum Clock Pulse Width...................................................................................................................................150 ns E. Minimum Time Between Clock Activation and Strobe ...........................................................................................300 ns F. Minimum Strobe Pulse Width..................................................................................................................................100 ns G. Typical Time Between Strobe Activation and Output Transition............................................................................500 ns SERIAL DATA present at the input is transferred to the shift register on the logic “0” to logic “1” transition of the CLOCK input pulse. On succeeding CLOCK pulses, the registers shift data information towards the SERIAL DATA OUTPUT. The SERIAL DATA must appear at the input prior to the rising edge of the CLOCK input waveform.Information present at any register is transferred to its respective latch when the STROBE is high (serial-to-parallel conversion). The latches will continue to accept new data as long as the STROBE is held high. Applications where the latches are bypassed (STROBE tied high) will require that the ENABLE input be high during serial data entry. When the ENABLE input is high, all of the output buffers are disabled (OFF) without affecting information stored in the latches or shift register. With the ENABLE input low, the outputs are controlled by the state of the latches.MIC5840 Family Truth TableShift Register Contents Latch Contents Output Contents Serial Data InputClock InputI 1I 2I 3 … I 8Serial Data OutputStrobe InputI 1I 2I 3 … I 8 OutputEnableI 1I 2I 3…I 8H H R1 R2 … R7 R7 L L R1 R2 … R7 R7 X R1 R2 R3 … R8 R8X X X … X X L R1 R2 R3 … R8P1 P2 P3 … P8P8 H P1 P2 P3 … P8 L P1 P2 P3 …P8X X X (X)HH H H …HL = Low Logic Level H = High Logic Level X = Irrelevant P = Present State R = Previous StateTypical Output DriverTypical Input CircuitsMaximum Allowable Duty Cycle (Plastic DIP)V DD = 5.0VMax. Allowable Duty Cycle at Ambient Temperature ofNumber of Outputs ON(I OUT = 200mA V DD = 5.0V)25ºC 40ºC 50ºC 60ºC 70ºC8 85% 72% 64% 55% 46%7 97% 82% 73% 63% 53% 6 100% 96% 85% 73% 62%5 100% 100% 100% 88% 75% 4 100% 100% 100% 100% 93%3 100% 100% 100% 100% 100%2 100% 100% 100% 100% 100%1100% 100% 100% 100% 100%V DD = 12VMax. Allowable Duty Cycle at Ambient Temperature ofNumber of Outputs ON(I OUT = 200mA V DD = 12V)25ºC 40ºC 50ºC 60ºC 70ºC8 80% 68% 60% 52% 44%7 91% 77% 68% 59% 50%6 100% 90% 79% 69% 58% 5 100% 100% 95% 82% 69%4 100% 100% 100% 100% 86%3 100% 100% 100% 100% 100%2 100% 100% 100% 100% 100%1100% 100% 100% 100% 100%Typical ApplicationsRelay/Solenoid Driver MIC5842 MIC5841 Hammer DriverMIC5841 Solenoid Driver with Output Enable MIC5841 Level Shifting Lamp Driver withDarlington Emitters Tied to a Negative SupplyTypical Applications, ContinuedMICREL, INC. 2180 FORTUNE DRIVE SAN JOSE, CA 95131 USATEL +1 (408) 944-0800 FAX +1 (408) 474-1000 WEB http:/The information furnished by Micrel in this data sheet is believed to be accurate and reliable. However, no responsibility is assumed by Micrel for its use. Micrel reserves the right to change circuitry and specifications at any time without notification to the customer.Micrel Products are not designed or authorized for use as components in life support appliances, devices or systems where malfunction of a product can reasonably be expected to result in personal injury. Life support devices or systems are devices or systems that (a) are intended for surgical implant into the body or (b) support or sustain life, and whose failure to perform can be reasonably expected to result in a significant injury to the user. A Purchaser’s use or sale of Micrel Products for use in life support appliances, devices or systems is a Purchaser’s own risk and Purchaser agrees to fullyindemnify Micrel for any damages resulting from such use or sale.© 1998 Micrel, Incorporated.分销商库存信息:MICRELMIC5841YWM TR MIC5841YWM MIC5841YNMIC5841YV MIC5842YN MIC5842YWM MIC5842YV MIC5841YV TR MIC5842YWM TR MIC5842YV TR MIC5841BN MIC5841BWM MIC5841BWM TR MIC5842BN MIC5841BVMIC5841BV TR MIC5842BV MIC5842BV TR MIC5842BWM MIC5842BWMTR。

MAX5222中文资料完整

令中。

Figure 图 3.详细的串行接口时序图

数字输入 数字输入与 CMOS 逻辑兼容。当通过 0.3 ✕ VDD 和 0.7 ✕ VDD 之间的过渡区切换逻辑 输入时,电源电流稍微增加。 微处理器接口 MAX5222 串行接口与 Microwire、SPI 和 QSPI 兼容。对于 SPI,清除 CPOL 和 CPHA 位 (CPOL=0 和 CPHA=0)。cpol=0 将非活动时 钟状态设置为零,CPHA=0 更改 SCLK 下降沿 的数据。此设置允许 SPI 以全时钟速度运行。 如果您的祄 P 上没有串行端口,则可以使用 并行端口的 3 位逐位模拟串行端口操作。只 有在必要时才操作串行时钟,从而使电压输 出处的数字馈通最小化。

工作温度范围…………-40°C 至+85°C

接 地 的 所 有 其 他 插 脚 ( 注 1 ) -0.3V 至 结温…………………………………+150°C

(VDD+0.3V)

储存温度范围……………………-65°C 至

持续功耗(Ta=+70°C)

+150°C

8 针 SOT23(在+70°C 以上减额 8.7mW/° 铅温度(焊接 10s)……………………………

CIN

Note4

10

pF

动态性能

电压输出滑移速率 电压输出稳定时间 数字馈通 和串扰

电源电压范围 电源电流

关机电源电流

SR

CL = 100pF

1

To ± 1⁄2LSB, CL = 100pF

10

All 0s to all 1s

0.25

电源

VDD

2.7

5.5

ALL INPUTS=0 IDD

MAX5432_07中文资料

Operating Temperature Range ...........................-40°C to +85°C Junction Temperature ......................................................+150°C Storage Temperature Range .............................-60°C to +150°C Lead Temperature (soldering, 10s) .................................+300°C

The MAX5432–MAX5435 feature an internal, nonvolatile, electrically erasable programmable read-only memory (EEPROM) that returns the wiper to its previously stored position at power-up. The fast-mode I2C-compatible serial interface allows communication at data rates up to 400kbps, minimizing board space and reducing interconnection complexity. Each device is available with multiple factory-preset I2C addresses (see the Ordering Information/Selector Guide).

CR5842B_中_V1.0

高压启动输入脚,通过启动电阻连接到整流输入电容阳极。

典型应用

EMI Filter

启达科技(香港)有限公司 V1.0

成都启臣微电子有限公司 2/10

CR5842B

结构图

BO

1

HV 8

VTH_BO

VDD 6

Internal supply

LVDD

UVLO

POR

OVP

工作电流

CR5842B 的工作电流为 2mA,这种较低的工作电流和 Burst 模式能够更好的实现效率 的提高与待机功耗的降低,在无负载情况下工作电流进一步降低,保证能够实现超低待机功 耗(50mW 以下)。

软启动

每一次VDD电源启动瞬间,CR5842B芯片内部都将触发软启动功能,即在VDD电压达到 UVLO_OFF以后,在大约4ms时间内,峰值电流从0上升到最大值峰值电流,以减少电源启动 期间功率MOSFET的电压应力。注意:无论何种保护导致的VDD再次启动,都必将触发软 启动功能。

FOSC

PWM工作时频率

高压启动绿色节能反激控制器

测试条件

VDD=2V, HV=100V VDD=18V, HV=500V

最小 典型 最大 单位

2

mA

5 μA

VFB=3V VDD=15V,

VFB=1V

IVDD=10mA

5.0 20.0 μA 2 2.5 mA

0.8 1 mA

13.5 14.5 15.5 V

启达科技(香港)有限公司 V1.0

www.ቤተ መጻሕፍቲ ባይዱ

成都启臣微电子有限公司 7/10

CR5842B

高压启动绿色节能反激控制器

重新充电,但芯片不会重新启动,除非去掉系统电源,且使 VDD 电压下降到 Vth_latch 电 压以下,然后重新供电,系统将重新启动。

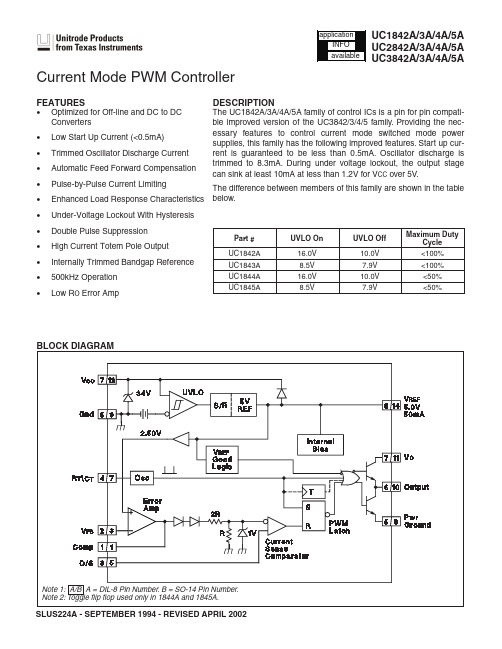

UC5842A资料

UC1842A/3A/4A/5A UC2842A/3A/4A/5A UC3842A/3A/4A/5A•Optimized for Off-line and DC to DC Converters•Low Start Up Current (<0.5mA)•Trimmed Oscillator Discharge Current •Automatic Feed Forward Compensation •Pulse-by-Pulse Current Limiting•Enhanced Load Response Characteristics •Under-Voltage Lockout With Hysteresis •Double Pulse Suppression •High Current Totem Pole Output •Internally Trimmed Bandgap Reference •500kHz Operation •Low R O Error AmpCurrent Mode PWM ControllerThe UC1842A/3A/4A/5A family of control ICs is a pin for pin compati-ble improved version of the UC3842/3/4/5family.Providing the nec-essary features to control current mode switched mode power supplies,this family has the following improved features.Start up cur-rent is guaranteed to be less than 0.5mA.Oscillator discharge is trimmed to 8.3mA.During under voltage lockout,the output stage can sink at least 10mA at less than 1.2V for V CC over 5V .The difference between members of this family are shown in the table below.FEATURESDESCRIPTIONPart #UVLO On UVLO Off Maximum DutyCycleUC1842A 16.0V 10.0V <100%UC1843A 8.5V 7.9V <100%UC1844A 16.0V 10.0V <50%UC1845A8.5V7.9V<50%UC1842A/3A/4A/5A UC2842A/3A/4A/5AUC3842A/3A/4A/5ACONNECTION DIAGRAMSABSOLUTE MAXIMUM RATINGS (Note 1)Note 1.All voltages are with respect to Ground, Pin 5.Currents are positive into, negative out of the specified terminal.Consult Packaging Section of Databook for thermal limitations and con-siderations of packages.Pin numbers refer to DIL package only.Supply Voltage (Low Impedance Source). . . . . . . . . . . . . .30V Supply Voltage (I CC mA). . . . . . . . . . . . . . . . . . . .Self Limiting Output Current. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .±1A Output Energy (Capacitive Load). . . . . . . . . . . . . . . . . . . . .5µJ Analog Inputs (Pins 2, 3). . . . . . . . . . . . . . . . . . .-0.3V to +6.3V Error Amp Output Sink Current . . . . . . . . . . . . . . . . . . . .10mA Power Dissipation at T A ≤25°C (DIL-8). . . . . . . . . . . . . . . .1W Storage Temperature Range. . . . . . . . . . . . . .-65°C to +150°C Lead Temperature (Soldering, 10 Seconds). . . . . . . . . .300°C N/C VREF VCC OUTPUT VCC GND 12345678161514131211N/C N/C N/CRT/CT N/C COMP VFB ISENSE PWRGND N/C109SOIC-WIDE16(TOP VIEW)DW PackagePARAMETERTEST CONDITIONSUC184xA\UC284xA UC384xAUNITSMIN.TYP.MAX.MIN.TYP.MAX.Reference Section Output Voltage T J = 25°C, I O = 1mA 4.955.00 5.05 4.905.00 5.10V Line Regulation 12≤V IN 25V 620620mV Load Regulation 1≤I O ≤20mA 625625mV Temp. Stability(Note 2, Note 7)0.20.40.20.4mV/°C Total Output Variation Line, Load, Temp. 4.95.14.825.18V Output Noise Voltage 10Hz ≤f ≤10kHz T J = 25°C (Note 2)5050µV Long Term Stability T A = 125°C, 1000Hrs. (Note 2)525525mV Output Short Circuit -30-100-180-30-100-180mA Oscillator Section Initial Accuracy T J = 25°C (Note 6)475257475257kHz Voltage Stability 12≤V CC ≤25V0.210.21%Temp. Stability T MIN ≤T A ≤T MAX (Note 2)55%AmplitudeV PIN 4peak to peak (Note 2) 1.7 1.7V Discharge Current T J = 25°C,V PIN 4= 2V (Note 8)7.88.38.87.88.38.8mA V PIN 4= 2V (Note 8)7.58.87.68.8mA Error Amp Section Input VoltageV PIN 1= 2.5V2.45 2.50 2.55 2.42 2.50 2.58V Input Bias Current -0.3-1-0.3-2µA A VOL2≤V O ≤4V65906590dB Unity Gain Bandwidth T J = 25°C (Note 2)0.710.71MHz PSRR12≤V CC ≤25V60706070dB Output Sink Current V PIN 2= 2.7V,V PIN 1= 1.1V 2626mA Output Source Current V PIN 2= 2.3V,V PIN 1= 5V-0.5-0.8-0.5-0.8mA V OUT High V PIN 2= 2.3V,R L = 15k to ground 5656V V OUT LowV PIN 2= 2.7V,R L = 15k to Pin 80.7 1.10.7 1.1V Current Sense Section Gain(Note 3, Note 4) 2.853 3.15 2.853 3.15V/V Maximum Input Signal V PIN 1= 5V (Note 3)0.91 1.10.91 1.1V PSRR12≤V CC ≤25V (Note 3)7070dB Input Bias Current -2-10-2-10µA Delay to Output V PIN 3= 0 to 2V (Note 2)150300150300ns Output Section Output Low Level I SINK = 20mA 0.10.40.10.4V I SINK = 200mA 15 2.215 2.2V Output High Level I SOURCE = 20mA 1313.51313.5V I SOURCE = 200mA1213.51213.5V Rise Time T J = 25°C, C L = 1nF (Note 2)5015050150ns Fall TimeT J = 25°C, C L = 1nF (Note 2)5015050150ns UVLO SaturationV CC = 5V,I SINK = 10mA0.71.20.71.2VELECTRICAL CHARACTERISTICS Unless otherwise stated,these specifications apply for –55°C ≤T A ≤125°C for theUC184xA;–40°C ≤T A ≤125°C for the UC284xAQ;–40°C ≤T A ≤85°C for the UC284xA;0≤T A ≤70°C for the UC384xA;V CC =15V (Note 5);R T =10k;C T =3.3nF;T A =T J ;Pin numbers refer to DIL-8.PARAMETERTEST CONDITIONSUC184xA\UC284xA UC384xAUNITSMIN.TYP.MAX.MIN.TYP.MAX.Under-Voltage Lockout Section Start Threshold x842A/4A 15161714.51617.5V x843A/5A 7.88.49.07.88.49.0V Min. Operation Voltage After x842A/4A 910118.51011.5V Turn On x843A/5A 7.07.68.27.07.68.2V PWM SectionMaximum Duty Cycle x842A/3A 94961009496100%x844A/5A474850474850%Minimum Duty Cycle 00%Total Standby Current Start-Up Current0.30.50.30.5mA Operating Supply Current V PIN 2=V PIN 3= 0V 11171117mA V CC Zener VoltageI CC = 25mA30343034VNote 2:Ensured by design, but not 100% production tested.Note 3:Parameter measured at trip point of latch with V PIN2= 0.Note 4:Gain defined as:A VPIN VPIN =∆∆13;0V PIN 30.8V .Note 5:Adjust V CC above the start threshold before setting at 15V .Note 6:Output frequency equals oscillator frequency for the UC1842A and UC1843A.Output frequency is one half oscillator fre-quency for the UC1844A and UC1845A.Note 7:“Temperature stability, sometimes referred to as average temperature coefficient, is described by the equation:Temp Stability VREF max VREF min TJ max TJ min =−−()()()().V REF (max) and V REF (min) are the maximum & minimum reference volt-age measured over the appropriate temperature range.Note that the extremes in voltage do not necessarily occur at the extremes in temperature.”Note 8:This parameter is measured with R T = 10k to V REF .This contributes approximately 300 A of current to the measurement.The total current flowing into the R T /C pin will be approximately 300 A higher than the measured value.ELECTRICAL CHARACTERISTICS Unless otherwise stated,these specifications apply for –55°C ≤T A ≤125°C for theUC184xA;–40°C ≤T A ≤125°C for the UC284xAQ;–40°C ≤T A ≤85°C for the UC284xA;0≤T A ≤70°C for the UC384xA;V CC =15V (Note 5);R T =10k;C T =3.3nF;T A =T J ;Pin numbers refer to DIL-8.Error Amplifier Open-Loop Frequency ResponseOutput Saturation CharacteristicsUC2842A/3A/4A/5AAPPLICATIONS DATA (cont.)UC2842A/3A/4A/5AUC3842A/3A/4A/5AAPPLICATIONS DATA (cont.)PACKAGING INFORMATIONOrderable Device Status(1)PackageType PackageDrawingPins PackageQtyEco Plan(2)Lead/Ball Finish MSL Peak Temp(3)5962-8670405PA ACTIVE CDIP JG81None A42SNPB Level-NC-NC-NC 5962-8670405VPA ACTIVE CDIP JG81None Call TI Level-NC-NC-NC 5962-8670405VXA ACTIVE LCCC FK201None Call TI Level-NC-NC-NC 5962-8670405XA ACTIVE LCCC FK201None POST-PLATE Level-NC-NC-NC 5962-8670406PA ACTIVE CDIP JG81None A42SNPB Level-NC-NC-NC 5962-8670406VPA ACTIVE CDIP JG81None Call TI Level-NC-NC-NC 5962-8670406VXA ACTIVE LCCC FK201None Call TI Level-NC-NC-NC 5962-8670406XA ACTIVE LCCC FK201None POST-PLATE Level-NC-NC-NC 5962-8670407PA ACTIVE CDIP JG81None A42SNPB Level-NC-NC-NC 5962-8670407VPA ACTIVE CDIP JG81None Call TI Level-NC-NC-NC 5962-8670407VXA ACTIVE LCCC FK201None Call TI Level-NC-NC-NC 5962-8670407XA ACTIVE LCCC FK201None POST-PLATE Level-NC-NC-NC 5962-8670408PA ACTIVE CDIP JG81None A42SNPB Level-NC-NC-NC 5962-8670408VPA ACTIVE CDIP JG81None Call TI Level-NC-NC-NC 5962-8670408VXA ACTIVE LCCC FK201None Call TI Level-NC-NC-NC 5962-8670408XA ACTIVE LCCC FK201None POST-PLATE Level-NC-NC-NC UC1842AJ ACTIVE CDIP JG81None A42SNPB Level-NC-NC-NCUC1842AJ883B ACTIVE CDIP JG81None A42SNPB Level-NC-NC-NCUC1842AJQMLV ACTIVE CDIP JG8None Call TI Call TIUC1842AL883B ACTIVE LCCC FK201None POST-PLATE Level-NC-NC-NCUC1842ALQMLV ACTIVE LCCC FK20None Call TI Call TI UC1843AJ ACTIVE CDIP JG81None A42SNPB Level-NC-NC-NCUC1843AJ883B ACTIVE CDIP JG81None A42SNPB Level-NC-NC-NCUC1843AJQMLV ACTIVE CDIP JG8None Call TI Call TIUC1843AL883B ACTIVE LCCC FK201None POST-PLATE Level-NC-NC-NCUC1843ALQMLV ACTIVE LCCC FK20None Call TI Call TI UC1844AJ ACTIVE CDIP JG81None A42SNPB Level-NC-NC-NCUC1844AJ883B ACTIVE CDIP JG81None A42SNPB Level-NC-NC-NCUC1844AJQMLV ACTIVE CDIP JG8None Call TI Call TIUC1844AL883B ACTIVE LCCC FK201None POST-PLATE Level-NC-NC-NCUC1844ALQMLV ACTIVE LCCC FK20None Call TI Call TI UC1845AJ ACTIVE CDIP JG81None A42SNPB Level-NC-NC-NCUC1845AJ883B ACTIVE CDIP JG81None A42SNPB Level-NC-NC-NCUC1845AJQMLV ACTIVE CDIP JG8None Call TI Call TIUC1845AL883B ACTIVE LCCC FK201None POST-PLATE Level-NC-NC-NCUC1845ALQMLV ACTIVE LCCC FK20None Call TI Call TI UC2842AD ACTIVE SOIC D1450None CU NIPDAU Level-1-220C-UNLIM UC2842AD8ACTIVE SOIC D875None CU NIPDAU Level-1-220C-UNLIM UC2842AD8TR ACTIVE SOIC D82500None CU NIPDAU Level-1-220C-UNLIM UC2842AD8TRG4ACTIVE SOIC D82500None Call TI Call TIUC2842ADTR ACTIVE SOIC D142500None CU NIPDAU Level-1-220C-UNLIM UC2842ADW ACTIVE SOIC DW1640None CU NIPDAU Level-2-220C-1YEAROrderable Device Status(1)PackageType PackageDrawingPins PackageQtyEco Plan(2)Lead/Ball Finish MSL Peak Temp(3)UC2842ADWTR ACTIVE SOIC DW162000None CU NIPDAU Level-2-220C-1YEAR UC2842AJ OBSOLETE CDIP JG8None Call TI Call TIUC2842AN ACTIVE PDIP P850Pb-Free(RoHS)CU SNPB Level-NC-NC-NC UC2843AD ACTIVE SOIC D1450None CU NIPDAU Level-1-220C-UNLIM UC2843AD8ACTIVE SOIC D875None CU NIPDAU Level-1-220C-UNLIM UC2843AD8TR ACTIVE SOIC D82500None CU NIPDAU Level-1-220C-UNLIM UC2843ADTR ACTIVE SOIC D142500None CU NIPDAU Level-1-220C-UNLIM UC2843ADW ACTIVE SOIC DW1640None CU NIPDAU Level-2-220C-1YEAR UC2843ADWTR ACTIVE SOIC DW162000None CU NIPDAU Level-2-220C-1YEAR UC2843AJ OBSOLETE CDIP JG8None Call TI Call TIUC2843AN ACTIVE PDIP P850Pb-Free(RoHS)CU SNPB Level-NC-NC-NC UC2843AQ ACTIVE PLCC FN2046None CU SNPB Level-2-220C-1YEAR UC2844AD ACTIVE SOIC D1450None CU NIPDAU Level-1-220C-UNLIM UC2844AD8ACTIVE SOIC D875None CU NIPDAU Level-1-220C-UNLIM UC2844AD8TR ACTIVE SOIC D82500None CU NIPDAU Level-1-220C-UNLIM UC2844AD8TRG4PREVIEW SOIC D82500None Call TI Call TIUC2844ADTR ACTIVE SOIC D142500None CU NIPDAU Level-1-220C-UNLIM UC2844ADW ACTIVE SOIC DW1640None CU NIPDAU Level-2-220C-1YEAR UC2844ADWTR ACTIVE SOIC DW162000None CU NIPDAU Level-2-220C-1YEAR UC2844AJ ACTIVE CDIP JG81None A42SNPB Level-NC-NC-NC UC2844AN ACTIVE PDIP P850Pb-Free(RoHS)CU SNPB Level-NC-NC-NC UC2844AQD ACTIVE SOIC D1450None Call TI Level-1-220C-UNLIM UC2844AQD8ACTIVE SOIC D875None Call TI Level-1-220C-UNLIM UC2844AQD8R ACTIVE SOIC D82500None Call TI Level-1-220C-UNLIM UC2844AQDR ACTIVE SOIC D142500None Call TI Level-1-220C-UNLIM UC2845AD ACTIVE SOIC D1450None CU NIPDAU Level-1-220C-UNLIM UC2845AD8ACTIVE SOIC D875None CU NIPDAU Level-1-220C-UNLIM UC2845AD8TR ACTIVE SOIC D82500None CU NIPDAU Level-1-220C-UNLIM UC2845AD8TRG4PREVIEW SOIC D82500None Call TI Call TIUC2845ADTR ACTIVE SOIC D142500None CU NIPDAU Level-1-220C-UNLIM UC2845ADW ACTIVE SOIC DW1640None CU NIPDAU Level-2-220C-1YEAR UC2845AN ACTIVE PDIP P850Pb-Free(RoHS)CU SNPB Level-NC-NC-NC UC3842AD ACTIVE SOIC D1450None CU NIPDAU Level-1-220C-UNLIM UC3842AD8ACTIVE SOIC D875None CU NIPDAU Level-1-220C-UNLIM UC3842AD8TR ACTIVE SOIC D82500None CU NIPDAU Level-1-220C-UNLIM UC3842ADTR ACTIVE SOIC D142500None CU NIPDAU Level-1-220C-UNLIM UC3842ADW ACTIVE SOIC DW1640None CU NIPDAU Level-2-220C-1YEAR UC3842ADWTR ACTIVE SOIC DW162000None CU NIPDAU Level-2-220C-1YEAR UC3842AJ ACTIVE CDIP JG81None A42SNPB Level-NC-NC-NC UC3842AN ACTIVE PDIP P850Pb-Free(RoHS)CU SNPB Level-NC-NC-NCOrderable Device Status(1)PackageType PackageDrawingPins PackageQtyEco Plan(2)Lead/Ball Finish MSL Peak Temp(3)UC3842ANG4ACTIVE PDIP P850Green(RoHS&no Sb/Br)CU NIPDAU Level-NA-NA-NAUC3843AD ACTIVE SOIC D1450None CU NIPDAU Level-1-220C-UNLIM UC3843AD8ACTIVE SOIC D875None CU NIPDAU Level-1-220C-UNLIM UC3843AD8G4ACTIVE SOIC D875None Call TI Call TIUC3843AD8TR ACTIVE SOIC D82500None CU NIPDAU Level-1-220C-UNLIM UC3843AD8TRG4ACTIVE SOIC D82500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMUC3843ADG4ACTIVE SOIC D1450Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIM UC3843ADTR ACTIVE SOIC D142500None CU NIPDAU Level-1-220C-UNLIM UC3843AJ ACTIVE CDIP JG81None A42SNPB Level-NC-NC-NCUC3843AN ACTIVE PDIP P850Pb-Free(RoHS)CU SNPB Level-NC-NC-NCUC3843ANG4ACTIVE PDIP P850Green(RoHS&no Sb/Br)CU NIPDAU Level-NA-NA-NA UC3844AD ACTIVE SOIC D1450None CU NIPDAU Level-1-220C-UNLIM UC3844AD8ACTIVE SOIC D875None CU NIPDAU Level-1-220C-UNLIM UC3844AD8TR ACTIVE SOIC D82500None CU NIPDAU Level-1-220C-UNLIM UC3844AD8TRG4ACTIVE SOIC D82500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIM UC3844ADTR ACTIVE SOIC D142500None CU NIPDAU Level-1-220C-UNLIM UC3844ADW ACTIVE SOIC DW1640None CU NIPDAU Level-2-220C-1YEAR UC3844ADWTR ACTIVE SOIC DW162000None CU NIPDAU Level-2-220C-1YEAR UC3844AN ACTIVE PDIP P850Pb-Free(RoHS)CU SNPB Level-NC-NC-NC UC3845AD ACTIVE SOIC D1450None CU NIPDAU Level-1-220C-UNLIM UC3845AD8ACTIVE SOIC D875None CU NIPDAU Level-1-220C-UNLIM UC3845AD8TR ACTIVE SOIC D82500None CU NIPDAU Level-1-220C-UNLIM UC3845ADTR ACTIVE SOIC D142500None CU NIPDAU Level-1-220C-UNLIM UC3845ADW ACTIVE SOIC DW1640None CU NIPDAU Level-2-220C-1YEAR UC3845ADWTR ACTIVE SOIC DW162000None CU NIPDAU Level-2-220C-1YEAR UC3845AJ ACTIVE CDIP JG81None A42SNPB Level-NC-NC-NCUC3845AN ACTIVE PDIP P850Pb-Free(RoHS)CU SNPB Level-NC-NC-NCUC3845ANG4ACTIVE PDIP P850Green(RoHS&no Sb/Br)CU NIPDAU Level-NA-NA-NA(1)The marketing status values are defined as follows:ACTIVE:Product device recommended for new designs.LIFEBUY:TI has announced that the device will be discontinued,and a lifetime-buy period is in effect.NRND:Not recommended for new designs.Device is in production to support existing customers,but TI does not recommend using this part in a new design.PREVIEW:Device has been announced but is not in production.Samples may or may not be available.OBSOLETE:TI has discontinued the production of the device.(2)Eco Plan-May not be currently available-please check /productcontent for the latest availability information and additional product content details.None:Not yet available Lead(Pb-Free).Pb-Free(RoHS):TI's terms"Lead-Free"or"Pb-Free"mean semiconductor products that are compatible with the current RoHS requirementsfor all 6substances,including the requirement that lead not exceed 0.1%by weight in homogeneous materials.Where designed to be soldered at high temperatures,TI Pb-Free products are suitable for use in specified lead-free processes.Green (RoHS &no Sb/Br):TI defines "Green"to mean "Pb-Free"and in addition,uses package materials that do not contain halogens,including bromine (Br)or antimony (Sb)above 0.1%of total product weight.(3)MSL,Peak Temp.--The Moisture Sensitivity Level rating according to the JEDECindustry standard classifications,and peak solder temperature.Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is provided.TI bases its knowledge and belief on information provided by third parties,and makes no representation or warranty as to the accuracy of such information.Efforts are underway to better integrate information from third parties.TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals.TI and TI suppliers consider certain information to be proprietary,and thus CAS numbers and other limited information may not be available for release.In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s)at issue in this document sold by TI to Customer on an annualbasis.PACKAGE OPTION ADDENDUM 10-Mar-2005Addendum-Page 4元器件交易网。

MIC5842中文资料

VDD = 12V VDD = 10V VDD = 5.0V (See Note 4) VDD = 12V VDD = 10V VDD = 5.0V All Drivers ON, VDD = 12V All Drivers ON, VDD = 10V All Drivers ON, VDD = 5.0V All Drivers OFF, VDD = 12V All Drivers OFF, VDD = 10V All Drivers OFF, VDD = 5.0V VR = 50V VR = 80V IF = 350mA

Features

• 3.3 MHz Minimum Data-Input Rate • CMOS, PMOS, NMOS, TTL Compatible • Internal Pull-Up/Pull-Down Resistors • Low-Power CMOS Logic and Latches • High-Voltage Current-Sink Outputs • Output Transient-Protection Diodes • Single or Split Supply Operation

MAX5842LEUB+中文资料

VDD OUTA OUTB OUTC OUTD

µMAX Rail-to-Rail is a registered trademark of Nippon Motorola, Ltd. I2C is a trademark of Philips Corp.

REF

________________________________________________________________ Maxim Integrated Products

TOP VIEW

ADD 1 SCL VDD GND SDA 2 3 4 5 10 OUTD 9 OUTC OUTB OUTA REF

RS SCL RS SDA MAX5842 REF

VDD OUTA OUTB OUTC OUTD

MAX5842

8 7 6

RS SCL RS SDA REF

MAX5842

Features

MAX5842

Ordering Information

PART MAX5842LEUB TEMP RANGE

o o

Applications

Digital Gain and Offset Adjustments Programmable Voltage and Current Sources Programmable Attenuation VCO/Varactor Diode Control Low-Cost Instrumentation Battery-Powered Equipment ATE

ELECTRICAL CHARACTERISTICS

(VDD = +2.7V to +5.5V, GND = 0, VREF = VDD, RL = 5kΩ, CL = 200pF, TA = TMIN to TMAX, unless otherwise noted. Typical values are at VDD = +5V, TA = +25°C.) (Note 1)

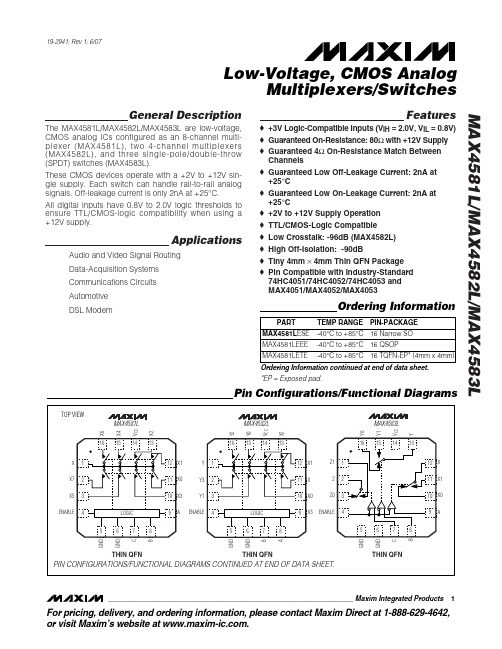

MAX4582LETE中文资料

General DescriptionThe MAX4581L/MAX4582L/MAX4583L are low-voltage,CMOS analog ICs configured as an 8-channel multi-plexer (MAX4581L), two 4-channel multiplexers (MAX4582L), and three single-pole/double-throw (SPDT) switches (MAX4583L).These CMOS devices operate with a +2V to +12V sin-gle supply. Each switch can handle rail-to-rail analog signals. Off-leakage current is only 2nA at +25°C.All digital inputs have 0.8V to 2.0V logic thresholds to ensure TTL/CMOS-logic compatibility when using a +12V supply.ApplicationsAudio and Video Signal Routing Data-Acquisition Systems Communications Circuits Automotive DSL ModemFeatures♦+3V Logic-Compatible Inputs (V IH = 2.0V, V IL = 0.8V)♦Guaranteed On-Resistance: 80Ωwith +12V Supply ♦Guaranteed 4ΩOn-Resistance Match Between Channels♦Guaranteed Low Off-Leakage Current: 2nA at +25°C ♦Guaranteed Low On-Leakage Current: 2nA at +25°C♦+2V to +12V Supply Operation ♦TTL/CMOS-Logic Compatible♦Low Crosstalk: -96dB (MAX4582L)♦High Off-Isolation: -90dB♦Tiny 4mm ×4mm Thin QFN Package ♦Pin Compatible with Industry-Standard 74HC4051/74HC4052/74HC4053 and MAX4051/MAX4052/MAX4053MAX4581L/MAX4582L/MAX4583LLow-Voltage, CMOS AnalogMultiplexers/Switches________________________________________________________________Maxim Integrated Products 1Pin Configurations/Functional DiagramsOrdering Information19-2941; Rev 1; 6/07For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642,or visit Maxim’s website at .Ordering Information continued at end of data sheet.*EP = Exposed pad.M A X 4581L /M A X 4582L /M A X 4583LLow-Voltage, CMOS Analog Multiplexers/Switches 2_______________________________________________________________________________________ABSOLUTE MAXIMUM RATINGSELECTRICAL CHARACTERISTICS(V CC = +12V ±5%, V_H = 2.0V, V_L = 0.8V, T A = T MIN to T MAX , unless otherwise noted. Typical values are at T A = +25°C.) (Notes 2, 3)Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.Note 1:Voltages exceeding V CC or GND on any signal terminal are clamped by internal diodes. Limit forward-diode current to max-imum current rating.(All Voltages Referenced to GND, Unless Otherwise Noted.)V CC .........................................................................-0.3V to +13V Voltage At Any Pin (Note 1)...........(GND - 0.3V) to (V CC + 0.3V)Continuous Current into Any Terminal..............................±20mA Peak Current X_, Y_ or Z_(pulsed at 1ms, 10% duty cycle)..................................±40mA ESD per Method 3015.7..................................................>2000VContinuous Power Dissipation (T A = +70°C)16-Pin Narrow SO (derate 8.7mW/°C above +70°C)...696mW 16-Pin QSOP (derate 8.3mW/°C above +70°C)...........667mW 16-Pin Thin QFN (derate 16.9mW/°C above +70°C).1349mW Operating Temperature Range ...........................-40°C to +85°C Storage Temperature Range.............................-65°C to +150°C Junction Temperature......................................................+150°C Lead Temperature (soldering, 10s).................................+300°CELECTRICAL CHARACTERISTICS (continued)MAX4581L/MAX4582L/MAX4583L Low-Voltage, CMOS Analog Multiplexers/Switches(V CC= +12V ±5%, V_H= 2.0V, V_L= 0.8V, T A= T MIN to T MAX, unless otherwise noted. Typical values are at T A = +25°C.) (Notes 2, 3)1009070608000678910111234512ON-RESISTANCE vs. V COMM A X 4581L /2L /3L t o c 01V COM (V)O N -R E S I S T A N C E (Ω)50403020101009070608000678910111234512ON-RESISTANCE vs. V COMV COM (V)O N -R E S I S T A N C E (Ω)50403020101001010.0001-403550658095110-25-10520125OFF-LEAKAGE CURRENT vs. TEMPERATURETEMPERATURE (°C)O F F -L E A K A G E C UR R E N T (n A )0.10.010.001Typical Operating Characteristics(V CC = 12V, V EN = GND, T A = +25°C, unless otherwise noted.)M A X 4581L /M A X 4582L /M A X 4583LLow-Voltage, CMOS Analog Multiplexers/Switches 4_______________________________________________________________________________________ELECTRICAL CHARACTERISTICS (continued)(V = +12V ±5%, V_= 2.0V, V_= 0.8V, T = T to T , unless otherwise noted. Typical values are at T = +25°C.) (Notes 2, 3)Note 3:The algebraic convention used in this data sheet is where the most negative value is the minimum column.Note 4:ΔR ON = R ON(MAX)- R ON(MIN).Note 5:Flatness is defined as the difference between the maximum and minimum value of on-resistance as measured over the specified analog signal ranges.Note 6:Leakage parameters are 100% tested at the maximum-rated hot operating temperature and guaranteed by design at T A =+25°C.Note 7:Guaranteed by design, not production tested.MAX4581L/MAX4582L/MAX4583LLow-Voltage, CMOS AnalogMultiplexers/Switches_______________________________________________________________________________________51001010.001-403550658095110-25-10520125ON-LEAKAGE CURRENT vs. TEMPERATUREM A X 4581L /2L /3L t o c 04TEMPERATURE (°C)O N -L E A K A G E C U R R E N T (n A )0.10.010214389765100234516789101112CHARGE INJECTION vs. V COMM A X 4581L /2L /3L t o c 05V COM (V)C H A R G E I N J E C T I O N (p C )1000100100.01-403550658095110-25-10520125SUPPLY CURRENT vs. TEMPERATURETEMPERATURE (°C)S U P P L Y C U R R E N T (n A )10.10.10.0001101k 10k100100kTOTAL HARMONIC DISTORTIONvs. FREQUENCY0.001FREQUENCY (Hz)T O T A L H A R M O N I C D I S T O R T I O N (%)0.01FREQUENCY RESPONSEFREQUENCY (MHz)0.0011101000.010.11000G A I N (d B )30-130-110-90-70-50-3010-10P H A S E (D E G R E E S )90-150-120-90-60-3006030SUPPLY CURRENT vs. LOGIC-LEVEL VOLTAGELOGIC-LEVEL VOLTAGE (V)0678910111234512S U P P L Y C U R R E N T (μA )10,0000.00010.0010.010.11101000100M A X 4581L /2L /3L t o c 0900.60.20.41.41.21.00.81.81.62.00234157689101112LOGIC-LEVEL THRESHOLD vs. SUPPLY VOLTAGEM A X 4581L /2L /3L t o c 10SUPPLY VOLTAGE (V)L O G I C -L E V E L T H R E S H O L D (V )Typical Operating Characteristics (continued)(V CC = 12V, V EN = GND, T A = +25°C, unless otherwise noted.)M A X 4581L /M A X 4582L /M A X 4583LLow-Voltage, CMOS Analog Multiplexers/Switches 6_______________________________________________________________________________________in both directions.Detailed Description The MAX4581L/MAX4582L/MAX4583L are low-voltage, CMOS analog ICs that operate from a single supply of +2V to +12V. The MAX4581L is configured as an 8-channel multiplexer, the MAX4582L as two 4-channel multiplexers, and the MAX4583L as three single-pole/double-throw (SPDT) switches. These devices can handle rail-to-rail analog signals with only 2nA of off-leakage current at +25°C.The MAX4581L/MAX4582L/MAX4583L are TTL/CMOS-logic compatible with 0.8V to 2.0V logic thresholds for all digital inputs when operating from a +12V supply.Applications InformationPower-Supply Considerations The MAX4581L/MAX4582L/MAX4583Ls’ construction is typical of most CMOS analog switches. The supply input, V CC, is used to power the internal CMOS switch-es and sets the limit of the analog voltage on any switch. Reverse ESD protection diodes are internally connected between each analog signal pin and both V CC and G ND. If any analog signal exceeds V CC or goes below G ND, one of these diodes conducts. During normal operation, these reverse-biased ESD diodes leak, causing the only current drawn from V CC or GND. Virtually all the analog leakage current comes from the ESD diodes. Although the ESD diodes on a given signal pin are identical, and therefore fairly well balanced, they are reverse biased differently by either V CC or G ND and the analog signal. This means that leakage varies as the analog signal varies. The differ-ence in the two diodes’ leakage to V CC and GND con-stitutes the analog signal-path leakage current. Because there is no connection between the analog signal paths and GND, all analog leakage current flows between each pin and one of the supply terminals, not to the other switch terminal. Because of this, both sides of a given switch can show leakage currents of either the same or opposite polarity.V CC and GND power the internal logic and logic-level translators, and set both the input and output logic lim-its. The logic-level translators convert the logic levels into switched V CC and GND signals to drive the gates of the analog switches. This drive signal is the only connection between the logic supplies (and signals) and the analog supplies. The logic-level thresholds are TTL/CMOS compatible when V CC is +12V.Overvoltage Protection Proper power-supply sequencing is recommended for all CMOS devices. Do not exceed the absolute maxi-mum ratings because stresses beyond the listed rat-ings can cause permanent damage to the devices. Always sequence V CC first, followed by the logic inputs and analog signals.Pin Nomenclature The MAX4581L/MAX4582L/MAX4583L are pin compati-ble with the industry-standard 74HC4051/74HC4052/ 74HC4053 and the MAX4051/MAX4052/MAX4053.*C not present on MAX4582L.Note:Input and output pins are identical and interchangeable. Either may be considered an input or output; signals pass equally well in either direction.MAX4581L/MAX4582L/MAX4583L Low-Voltage, CMOS Analog Multiplexers/Switches _______________________________________________________________________________________7M A X 4581L /M A X 4582L /M A X 4583LLow-Voltage, CMOS Analog Multiplexers/Switches 8_______________________________________________________________________________________Test Circuits/Timing DiagramsFigure 1. Enable Switching TimesMAX4581L/MAX4582L/MAX4583L Low-Voltage, CMOS Analog Multiplexers/Switches Figure 2. Address Transition Time_______________________________________________________________________________________9M A X 4581L /M A X 4582L /M A X 4583LLow-Voltage, CMOS Analog Multiplexers/Switches 10______________________________________________________________________________________Figure 3. Break-Before-Make IntervalFigure 4. Charge InjectionMAX4581L/MAX4582L/MAX4583L Low-Voltage, CMOS Analog Multiplexers/SwitchesFigure 5. NO/COM CapacitanceFigure 6. Off-Isolation, On-Loss, and Crosstalk______________________________________________________________________________________11M A X 4581L /M A X 4582L /M A X 4583LLow-Voltage, CMOS Analog Multiplexers/Switches 12______________________________________________________________________________________Ordering Information (continued)Pin Configurations/Functional Diagrams (continued)Chip InformationTRANSISTOR COUNT: 219PROCESS: CMOS*EP = Exposed pad.____________________Revision HistoryPages changed at Rev 1: 1, 6, 12, 16Package InformationMAX4581L/MAX4582L/MAX4583L Low-Voltage, CMOS Analog Multiplexers/Switches (The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline informationgo to /packages.)M A X 4581L /M A X 4582L /M A X 4583LLow-Voltage, CMOS Analog Multiplexers/Switches 14______________________________________________________________________________________Package Information (continued)(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to /packages .)Package Information (continued)MAX4581L/MAX4582L/MAX4583L Low-Voltage, CMOS Analog Multiplexers/Switches (The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline informationgo to /packages.)M A X 4581L /M A X 4582L /M A X 4583LLow-Voltage, CMOS Analog Multiplexers/Switches Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.16____________________Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600©2007 Maxim Integrated Productsis a registered trademark of Maxim Integrated Products.Package Information (continued)(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to /packages .)。

基于PIC单片机的螺杆空压机控制器

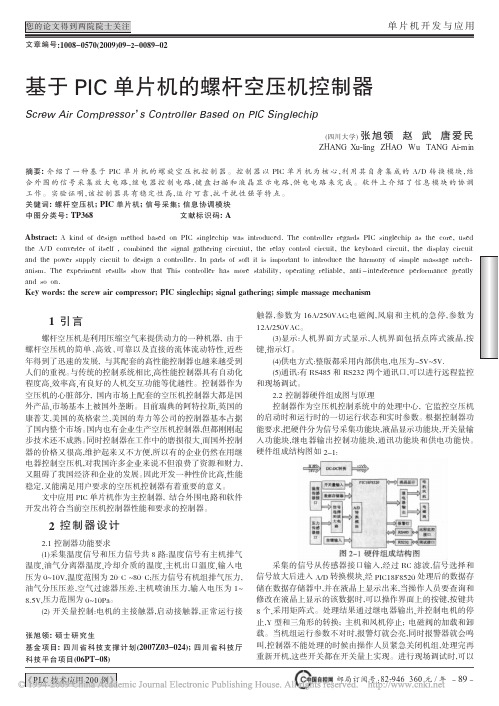

邮局订阅号:82-946360元/年技术创新单片机开发与应用《PLC 技术应用200例》您的论文得到两院院士关注基于PIC 单片机的螺杆空压机控制器Screw Air Compressor ’s Controller Based on PIC Singlechip(四川大学)张旭领赵武唐爱民ZHANG Xu-ling ZHAO Wu TANG Ai-min摘要:介绍了一种基于PIC 单片机的螺旋空压机控制器。

控制器以PIC 单片机为核心,利用其自身集成的A/D 转换模块,结合外围的信号采集放大电路,继电器控制电路,键盘扫描和液晶显示电路,供电电路来完成。

软件上介绍了信息模块的协调工作。

实验证明,该控制器具有稳定性高,运行可靠,抗干扰性强等特点。

关键词:螺杆空压机;PIC 单片机;信号采集;信息协调模块中图分类号:TP368文献标识码:AAbstract:A kind of design method based on PIC singlechip was introduced.The controller regards PIC singlechip as the core,used the A/D converter of itself ,combined the signal gathering circuiut,the relay control circuit,the keyboard circuit,the display circuit and the power supply circuit to design a controller.In parts of soft it is important to introduce the harmony of simple massage mech -anism.The experiment results show that This controller has more stability,operating reliable,anti -interference performance greatly and so on.Key words:the screw air compressor;PIC singlechip;signal gathering;simple massage mechanism文章编号:1008-0570(2009)09-2-0089-021引言螺杆空压机是利用压缩空气来提供动力的一种机器,由于螺杆空压机的简单、高效、可靠以及直接的流体流动特性,近些年得到了迅速的发展,与其配套的高性能控制器也越来越受到人们的重视。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

19-2317; Rev 0; 1/02

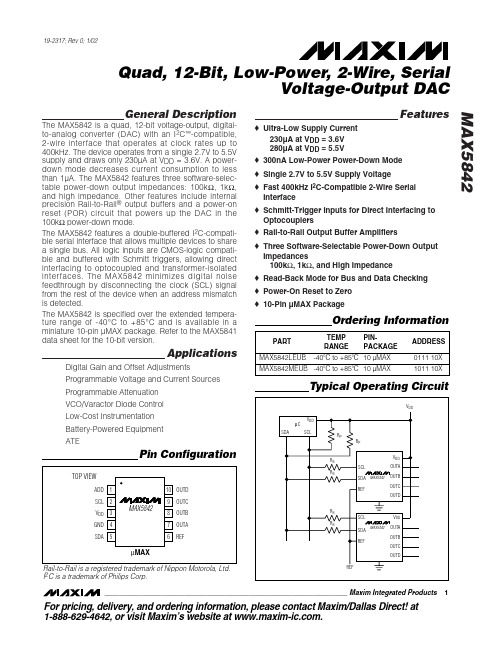

MAX5842

Quad, 12-Bit, Low-Power, 2-Wire, Serial Voltage-Output DAC

General Description

The MAX5842 is a quad, 12-bit voltage-output, digitalto-analog converter (DAC) with an I2C™-compatible, 2-wire interface that operates at clock rates up to 400kHz. The device operates from a single 2.7V to 5.5V supply and draws only 230µA at VDD = 3.6V. A powerdown mode decreases current consumption to less than 1µA. The MAX5842 features three software-selectable power-down output impedances: 100kΩ, 1kΩ, and high impedance. Other features include internal precision Rail-to-Rail® output buffers and a power-on reset (POR) circuit that powers up the DAC in the 100kΩ power-down mode. The MAX5842 features a double-buffered I2C-compatible serial interface that allows multiple devices to share a single bus. All logic inputs are CMOS-logic compatible and buffered with Schmitt triggers, allowing direct interfacing to optocoupled and transformer-isolated interfaces. The MAX5842 minimizes digital noise feedthrough by disconnecting the clock (SCL) signal from the rest of the device when an address mismatch is detected.

MAX5842MEUB -40oC to +85oC 10 µMAX

ADDRESS

0111 10X 1011 10X

Typical Operating Circuit

VDD µC

SDA

SCL

VDD

RP RP

RS

VDD

SCL

OUTA

RS

SDA MAX5842 OUTB

OUTC REF

OUTD

RS

SCL

Features

o Ultra-Low Supply Current 230µA at VDD = 3.6V 280µA at VDD = 5.5V

o 300nA Low-Power Power-Down Mode

o Single 2.7V to 5.5V Supply Voltage o Fast 400kHz I2C-Compatible 2-Wire Serial

The MAX5842 is specified over the extended temperature range of -40°C to +85°C and is available in a miniature 10-pin µMAX package. Refer to the MAX5841 data sheet for the 10-bit version.