并口编程

基于fpga的ad9268的并口读数据的代码

基于fpga的ad9268的并口读数据的代码1. 引言1.1 概述本文基于FPGA设计了一种并口读取数据的方案,该方案可以与AD9268芯片实现接口通信。

通过该方案,我们可以在FPGA平台上高效地读取AD9268芯片采集的数据。

1.2 文章结构本文共分为五个部分进行阐述。

首先,引言部分将介绍文章的背景和目的。

其次,AD9268简介部分将对AD9268芯片及其功能进行介绍,以及FPGA与AD9268之间接口通信的原理和并口读取数据的需求背景。

然后,在基于FPGA的AD9268并口读取数据设计方案中,将详细说明选择和搭建FPGA硬件平台、设计与实现AD9268数据读取流程、优化技术研究等内容。

随后,在实验与结果分析部分,将展示实验环境搭建与参数设置,并对AD9268并口读取数据性能测试结果进行详细分析,并评估优化方法对性能提升的影响。

最后,在结论与展望部分总结研究成果,并提出存在问题与改进方向以及未来发展趋势展望。

1.3 目的本文旨在针对AD9268芯片,并基于FPGA设计一种高效的并口读取数据的方案。

通过深入研究AD9268芯片的功能,对FPGA与AD9268之间的接口通信原理进行分析,并提出一种针对并口读取数据需求背景下的设计方案。

通过实验和结果分析,验证了该方案的可行性,并从优化方法的角度评估了其对性能提升的影响。

最后,总结研究成果,指出存在问题并提出改进方向,并展望了未来在该领域的发展趋势。

2. AD9268简介:2.1 AD9268芯片功能:AD9268是一款高性能、12位模数转换器(ADC)芯片,采用并行接口与FPGA 进行通信。

它具有较高的分辨率和采样速率,并且适用于广泛的模拟输入信号范围。

该芯片内置了功耗优化的电源管理电路,并提供了多种工作模式,以满足不同应用场景的需求。

2.2 FPGA与AD9268接口通信的原理:在FPGA与AD9268之间建立稳定可靠的通信通道是实现并口读取数据的关键。

并口编程器制作全过程

并口编程器制作全过程-以后大家大胆的折腾BIOS吧!!这个教程本来打算在五一期间就做出来的,无奈哥们我五一冒着30度高温去电子市场的时候,人家也停业休息,上周去电子市场把材料买齐,这不,今天趁老婆上班,就窝在家里制作教程喽制作之前的准备:1工具:电烙铁万用表焊锡斜口钳美工刀(工具我就不上相片了)2材料:面包板一块芯片紧锁座一个并口头一个电阻电容若干(参考电路图)PNP(加菲我用的A1015)三极管一个4007三极管三个(用于串联实现将5V降为3.3V).也可直接使用AMS11173.3V稳压管,可直接将5V转换为3.3V(注:并非所有1117芯片都是3.3V稳压管,也有1.8V的,一般芯片上有标明)如下图,当AMS1117(左下角标明是3.3V的稳压管)这次放置时,左边脚为GND(接地,0V),中间脚为3.3V输出,最右边为电源输入(接USB 5V)当用AMS1117取代电路图中三个二级管时,只需将USB 5V接1117最右边脚,将原电路图中3个二极管之后电路接1117中间,1117最左边接地即可。

下面是其它的工具,地上太乱,就放床上拍照了器材:奥林巴斯FE-290 [奥林巴斯数码相机]时间:2011-04-21 06:23:50 快门:1/30 光圈:F/2.7 焦距:4毫米感光度:1253电路图一张:(我那个贴子里面有一个多功能编程器,图纸相对复杂,部分兄弟可能感觉制作起来有点难度,我就示范制作这个25类编程器吧)至此,工具,材料,图纸都已准备就绪了,现在开始正式制作。

用斜口钳将并口头的外壳固定脚修整,将25个针脚重新排位,固定焊接在万用板上器材:奥林巴斯FE-290 [奥林巴斯数码相机]时间:2011-04-23 02:52:28 快门:1/25 光圈:F/2.7 焦距:4毫米感光度:125这张是正面的,固定得还不错吧?上面的那个小贴片的芯片就是1117 3.3V稳压芯片,用它可获得更精确的电压。

C#并口访问

用C#操作IO端口1-用并口控制发光二极管作者: Levent S. 翻译:Aweay为什么要写这篇文章,不可否认,用C#编写这类程序不是非常合适的, 相信来CSDN的很多朋友都能用其他语言轻松编写这样的程序, 不过如果有一天你的.net的项目里有这样的需求, 那么这篇文章或许就适合你了.什么是端口?端口包含了一系列信号线, 通过这个端口CPU可以同其他外部设备交换数据, 比如我们经常见到的Modem,打印机等.通常情况下, 打开的信号是”1”, 关闭的信号是”0”. 并口在同一时间内可以发送8位的数据, 接收5位的数据. 而串口RS-232则只能发送1位数据, 但串口是多向的, 所以在同一时刻既可以发送也可以接收.什么是RS-232RS-232(ANSI/EIA-232标准)是IBM-PC及其兼容机上的串行连接标准。

可用于许多用途,比如连接鼠标、打印机或者Modem,同时也可以接工业仪器仪表。

用于驱动和连线的改进,实际应用中RS-232的传输长度或者速度常常超过标准的值。

RS-232只限于PC串口和设备间点对点的通信。

RS-232串口通信最远距离是50英尺。

\ 1 2 3 4 5 /\ 6 7 8 9 /从计算机连出的线的截面。

RS-232针脚的功能:数据:TXD(pin 3):串口数据输出RXD(pin 2):串口数据输入握手:RTS(pin 7):发送数据请求CTS(pin 8):清除发送DSR(pin 6):数据发送就绪DCD(pin 1):数据载波检测DTR(pin 4):数据终端就绪地线:GND(pin 5):地线其他RI(pin 9):铃声指示RS232 通讯原理? RS485通讯原理?RS-232是串行数据接口标准,最初都是由电子工业协会(EIA)制订并发布的,RS-232在1962年发布,命名为EIA-232-E,作为工业标准,以保证不同厂家产品之间的兼容。

RS-422由RS-232发展而来,它是为弥补RS-232之不足而提出的。

8080并口时序

8080并口时序

8080并口时序是一种用于输入输出数据的接口,常用于计算机与外部

设备之间的数据传输。

在该时序中,CPU与并口之间通过多根数据线,控制线以及时钟线进行数据的传输和控制。

8080并口的时序如下:

1. 起始信号:CPU向并口发送起始信号,表示即将开始进行数据传输。

2. 地址线传输:CPU将需要读取或写入的设备地址信息发送给并口,

以确定目标设备。

3. 控制信号传输:CPU向并口发送控制信号,包括读(Read)和写(Write)信号,用于区分数据的读写操作。

4. 数据线传输:CPU将需要读取或写入的数据通过数据线发送给并口,或者从并口读取数据放入数据线中。

5. 状态确认:并口接收到数据后,通过状态线向CPU发送确认信号,

表示数据已成功传输或接收。

6. 结束信号:数据传输完成后,CPU向并口发送结束信号,表明数据

传输结束。

在8080并口时序中,通过这些步骤可以实现计算机与外部设备之间的

数据传输,从而实现各种输入输出操作。

通过合理的控制和管理,能

够高效地完成数据的读取和写入操作,满足计算机与外部设备之间的

数据交互需求。

stm32并口数据处理方法

stm32并口数据处理方法

STM32并口数据处理方法是指使用STM32芯片的并口接口进行数据处理的方法。

并口接口是一种并行接口,可以同时传输多个数据位,速度快,但是需要使用更多的引脚。

在STM32芯片中,并口接口可以用于连接外部设备,如LCD屏幕、按键等。

在STM32并口数据处理中,首先需要配置并口接口的引脚和模式。

然后可以使用STM32提供的库函数或者自己编写的代码来读取或写

入数据。

对于读取数据,可以使用GPIO端口读取数据,也可以使用

外部中断或DMA等方式。

对于写入数据,可以使用GPIO端口输出数据,也可以使用TIM等定时器输出数据。

在实际应用中,可以根据具体的需求选择不同的数据处理方法。

例如,可以使用GPIO端口进行简单的输入输出操作,也可以使用外

部中断进行多任务处理。

对于需要高速数据传输的应用,可以使用DMA方式进行数据传输。

总之,STM32并口数据处理方法是一种灵活、高效的数据处理方式,可以满足不同的应用需求。

通过对STM32并口接口的深入理解和熟练应用,可以提高开发效率,实现更为复杂的应用功能。

- 1 -。

25针并口VB编程技术

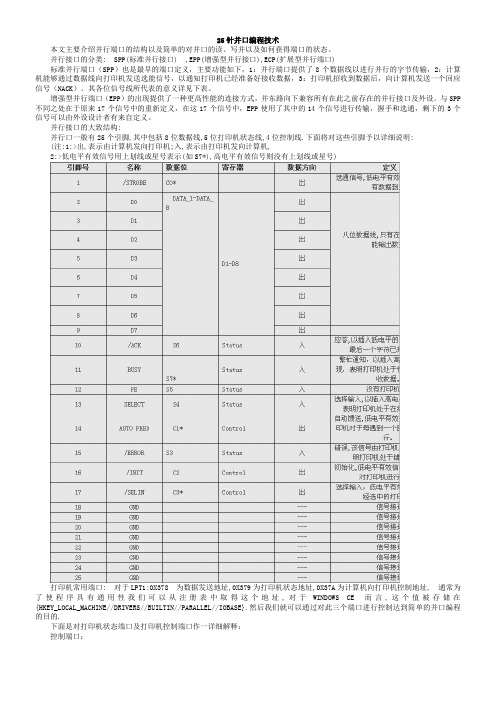

25针并口编程技术本文主要介绍并行端口的结构以及简单的对并口的读、写并以及如何获得端口的状态。

并行接口的分类: SPP(标准并行接口) ,EPP(增强型并行接口),ECP(扩展型并行端口)标准并行端口(SPP)也是最早的端口定义,主要功能如下,1:并行端口提供了8个数据线以进行并行的字节传输,2:计算机能够通过数据线向打印机发送选能信号,以通知打印机已经准备好接收数据,3:打印机招收到数据后,向计算机发送一个回应信号(NACK)。

其各位信号线所代表的意义详见下表。

增强型并行端口(EPP)的出现提供了一种更高性能的连接方式,并东路向下兼容所有在此之前存在的并行接口及外设。

与SPP 不同之处在于原来17个信号中的重新定义,在这17个信号中,EPP使用了其中的14个信号进行传输,握手和选通,剩下的3个信号可以由外设设计者有来自定义。

并行接口的大致结构:并行口一般有25个引脚,其中包括8位数据线,5位打印机状态线,4位控制线.下面将对这些引脚予以详细说明:(注:1:>出,表示由计算机发向打印机;入,表示由打印机发向计算机,2:>低电平有效信号用上划线或星号表示(如S7*),高电平有效信号则没有上划线或星号)打印机常用端口: 对于LPT1:0X378 为数据发送地址,0X379为打印机状态地址,0X37A为计算机向打印机控制地址, 通常为了使程序具有通用性我们可以从注册表中取得这个地址,对于WINDOWS CE 而言,这个值被存储在{HKEY_LOCAL_MACHINE//DRIVERS//BUILTIN//PARALLEL//IOBASE}.然后我们就可以通过对此三个端口进行控制达到简单的并口编程的目的.下面是对打印机状态端口及打印机控制端口作一详细解释:控制端口:这个0x37A计算机控制打印机的地址,可以产生对打印机进行控制的必要信号,可写,两高位(7和8)没什么用,第6位写1表示可以向并口输出数据。

并行接口程序设计

并行接口程序设计本章介绍在Windows 2000/XP下的并行接口的程序设计方法,分析一下目前进行并行接口编程的方法,可以归纳为几种:•DLL直接I/O方式:应用程序通过一个可以进行端口I/O访问的DLL接口软件实现对并行接口的访问,即通过调用第三方DLL接口软件中的I/O端口读写函数实现对并行口的寄存器的读写。

这样的软件很多,像WinIo、Inpout32、TVicPort等;•Active X控件直接I/O方式:通过一个提供Active X控件实现对端口的直接I/O访问,一般控件的方式采用VB编程比较简单。

这样的软件包括Inpout32、TVicPort等;•并行接口专用接口软件:使用这一类软件对并行接口编程要比上2种方法简单,有些软件支持中断。

这样的软件如TVicLPT。

•自己编写驱动程序:直接在VC++环境下通过Windows 2000 DDK或Windows XP DDK编写驱动程序,这是一种最灵活的方法,但编程的难度比较大。

5.1 实现直接I/O方式的软件并行接口的编程在不同的操作系统下采取不同的方法,在DOS和Windows95之前的操作系统下,可以直接对端口进行读写,根据并行接口的不同模式的寄存器进行读写操作就可以完成各种模式的接口编程。

在目前的Windows 2000/XP操作系统下,不能直接对端口寄存器进行访问,这是由于Windows2000/XP对系统底层操作采取了屏蔽的策略,对用户而言,系统变得更为安全,但这却给接口和接口软件开发人员带来了不小的困难,因为只要应用程序中涉及到底层的操作,开发人员就不得不深入到Windows的内核去编写属于系统级的设备驱动程序。

对并行口的读写操作就是如此,由于Windows对系统的保护,应用程序不允许直接I/O操作。

在Windows2000/XP操作系统下,正规的接口程序的编程方法是采取驱动程序的开发方法。

由于驱动程序需要与操作系统最底层进行交互,因此不同的操作系统的底层结构对应不同的设备驱动程序模型。

8255A可编程并行接口实验

实验八8255A可编程并行接口实验一、实验项目用8255A可编程并行接口芯片,重复实验四的内容。

PA口作为显示输出口,PB口作为开关量输入口。

二、实验目的1.了解8255A芯片的结构及编程方法2.掌握通过8255A并行接口读取开关数据的方法三、实验原理设置好8255A各端口的工作模式:三个端口都工作于方式0,PA口作为显示输出口,PB口作为开关量输入口。

四、实验连线8255A的PA0PA7接发光二极管L1L8,PB0PB7接开关K1K8,片选信号CS8255接CS0。

五、实验电路六、程序框图七、参考程序CSEG AT 0000HLJMP START开始置控制字从B通道读入开关状态从A通道输出到发光二极管延时一段时间.23.CSEG AT 4100HPA EQU 0CFA0HPB EQU HPCTL EQU HSTART: MOV DPTR, #PCTL ;置8255A控制字,A、B、C口均工作MOV A, # H ;方式0,A、C口为输出,B口为输入MOVX @DPTR, ALOOP: MOV DPTR, #PB ;从B口读入开关状态值MOVX A,MOV DPTR, #PA ;从A口将状态值输出显示MOVX , AMOV R7, #10H ;延时DEL0: MOV R6, #0FFHDEL1: DJNZ R6,DJNZ R7,LJMP LOOPEND八、问题思考试分析改置8255A控制字,A、B、C口工作方式1,B、C口为输出,A口为输入,可不可以。

.24.。

FPGA的虚拟JTAG技术对并口FLASH快速编程

敬请登录网站在线投稿2018年第2期9F PG A的虚拟J T A G技术对并口F L A S H快速编程丁峰平,陈莉萍(诺基亚上海贝尔股份有限公司,杭州310053)摘要:集成数字电路板上经常有F L A S H器件需要编程,在工厂批量生产中往往要占据较多时间㊂特别是对于挂载在可编程器件(F P G A)的并行接口的F L A S H,使用边界扫描的方法靠移位数据来仿真F L A S H读写时序,从而完成F L A S H 器件编程的方法相当低效费时㊂应用了虚拟J T A G技术后,就不需要进行整个边界引脚的移位处理,可以一次性从J T A G链上加载较大的数据块,再配合并口F L A S H的接口逻辑进行编程,有效地提高了效率㊂关键词:F P G A;边界扫描;虚拟J T A G;并口F L A S H中图分类号:T P311文献标识码:AF a s t P a r a l l e l F L A S H P r o g r a m m i n g B a s e d o n V i r t u a l J T AG i n F P G AD i n g F e n g p i n g,C h e n L i p i n g(N o k i a S h a n g h a i B e l l C o.,L t d.,H a n g z h o u310053,C h i n a)A b s t r a c t:T h e r e i s a l w a y s p a r a l l e l F L A S H t o b e p r o g r a mm e d o n P CB i n f a c t o r y.T h e p r o g r a mm i n g t a k e s m u c h t i m e d u r i n g t h e m a s s p r o d u c t i o n,e s p e c i a l l y f o r F L A S H w h i c h i s m o u n t e d o n t h e p a r a l l e l i n t e r f a c e o f p r o g r a mm a b l e d e v i c e(F P G A).T h e m e t h o d o f u s i n g b o u n d a r y s c a n i s u s e d t o s i m u l a t e F L A S H r e a d a n d w r i t e,w h i c h i m p l e m e n t e d b y b i t s h i f t i n g t h r o u g h a l l t h e b o u n d a r y c e l l s i s c o n s u-m i n g.A f t e r t h e v i r t u a l J T A G t e c h n o l o g y i s a p p l i e d,t h e d i s p l a c e m e n t o f t h e e n t i r e b o u n d a r y p i n i s n o t r e q u i r e d,b e c a u s e t h e v i r t u a l J T A G c o r e c a n r e c e i v e m a s s i v e d a t a f r o m J T A G c h a i n w i t h i n o n e t i m e.A n d p r o g r a mm i n g w i t h t h e i n t e r f a c e l o g i c o f F L A S H,t h e e f f i c i e n c y i s i m p r o v e d.K e y w o r d s:F P G A;B o u n d a r y S c a n;v i r t u a l J T A G;p a r a l l e l F L A S H引言联合测试行动小组(J o i n t T e s t A c t i o n G r o u p,J T A G)边界扫描(B o u n d a r y S c a n)是I E E E1149.1标准,其接口在大量的数字芯片中集成,方便调试和编程㊂集成电路板上一般将各个芯片的J T A G接口串接起来形成菊花链,这样可以通过J T A G工具进行统一的自动化操作㊂F L A S H 存储芯片往往挂载在具有J T A G接口的芯片的总线上,这样在工厂进行大规模生产时,可以通过J T A G链对F L A S H芯片进行编程㊂1J T A G接口简介J T A G接口一般有4个信号,分别为测试数据输入(T D I)㊁测试数据输出(T D O)㊁测试时钟(T C K)㊁测试模式选择(TM S),测试复位信号(T R S T)是可选的㊂TM S㊁T C K连入芯片内部的测试接入端口(T A P),T D I串接到芯片引脚的边界扫描单元(B S)上,这些单元串接后通过T D O连出芯片㊂T A P控制器在T C K触发下通过一系列的TM S信号进行状态机的改变,这些状态包括:C a p t u r e D R(得到当前数据寄存器的内容),S h i f t D R(对数据寄存器进行数据移位,从T D I移入,T D O移出),U p d a t e D R (更新当前数据寄存器的内容),C a p t u r e I R(得到当前数据指令寄存器的内容),S h i f t I R(对指令寄存器进行数据移位,从T D I移入㊁T D O移出),U p d a t e I R(更新当前指令寄存器的内容)㊂I R和D R一起进行边界扫描单元的控制,比如当I R 是全1时,一般对应的功能是测试数据直通输出(通过1比特的移位寄存器B y p a s s R e g i s t e r)㊂还可以控制引脚数据是从内部逻辑得到还是扫描单元得到,扫描单元的数据是从引脚输入还是输出到引脚上,从而实现特定的J T A G 动作(如图1所示)㊂2F L A S H器件的编程集成电路板上的F L A S H器件一般挂载在具有J T A G接口的芯片上,在批量生产中往往需要通过J T A G 烧写一个小的引导程序或数据文件,大小从几十K B到几M B不等㊂传统的边界扫描方式是依次将数据串行移位到芯片10M i c r o c o n t r o l l e r s &E m b e d d e d S ys t e m s 2018年第2期w w w .m e s n e t .c o m .c n图1 T A P 控制器原理框图的扫描单元(B S )里,准备好各个数据线(d a t a)㊁地址线(a d d r e s s )㊁片选线(c s )㊁读写使能线(w r )㊁输出使能(o e)㊁编程使能(AW ),接线如图2所示㊂图2 F L A S H 连接图因为每次移位都需要遍历芯片的所有B S,一次数据的准备需要额外的开销,所以这种方式的编程十分低效,只能用来烧写小块的程序和数据㊂即便这样,这种方式的耗时也不可小觑,以1M B 的数据和有100个引脚的芯片以及有32字节编程块缓存的F L A S H (即有N=32K 字节块,一次性可以编程32字节)为例㊂为方便计算,忽略F L A S H 的命令字,仅仅计算有效字节编程时间㊂一个块编程周期包含片选C S 从高到低,然后写有效信号W E 从高到低,数据有效(可同时),W E从低到高,W E 从高到低,数据有效(可同时),W E 从低到高 最后C S 从低到高㊂J T A G 控制器就需要至少移位K=(2N+3)c yc l e s (对应一个T C K 时钟周期),每次都需要移位T s h i f t =100次㊂假设J T A G 控制器的T C K 时钟为T t c k =20MH z ,那么T c y c l e =50n s ㊂总时间就是:T=KˑT c yc l e ˑT s h i f t =327.695s >5m i n 实际上的引脚会更多,编程命令字的开销也不少,J T A G 工具每批次移位的间隔还有时间,需要更多的编程时间㊂3 虚拟J T A G 简介批量生产的自动化测试需要用到J T A G 接口,而传统的J T A G 编程又比较低效费时,有没有两全其美的方法呢?答案是肯定的,就是可编程器件F P G A 或C P L D (C o m p l e x P r o g r a mm a b l e L o g i c D e v i c e )的虚拟J T A G 技术㊂V i r t u a l J T A G 是A L T E R A (已被I n t e l 收购)公司提出的一个概念,X I L I N X 公司和L A T T I C E 公司也有相对应的提法,具体实现大同小异㊂在可编程器件里面,J T A G T A P 控制器可以作为一个硬核对用户开放,用户可以得到T A P 状态机的各种状态,当然包括T D I ㊁T C K ㊁T D O ,从而可以接管T D I 的数据,自定义返回给T D O 的数据㊂触发用户自定义的J T A G 后级控制器的原理用到了指令寄存器(i n s t r u c t i o n r e gi s t e r )里面的用户数据寄存器(u s e r d a t a r e gi s t e r )㊂当输入特定数据给用户寄存器0和用户寄存器1后,相应的状态指示线发出高电平,J T A G后级控制器就可以知道后面的数据都是输入给它的,就可以对这些数据进行自定义的操作㊁自定义虚拟指令寄存器(V i r t u a l I n s t r u c t i o n R e g i s t e r ,V I R )和虚拟数据寄存器(V i r t u a l D a t a R e g i s t e r ,V D R ),从而完成了虚拟J T A G 的实现,如图3所示㊂4 挂载F P G A 上的F L A S H 的快速编程基于V i r t u a l J T A G 技术,可以自定义后级J T A GT A P 控制器,定义好虚拟数据寄存器(V D R )和虚拟指令寄存器(I R )㊂再移植一个F l a s h M e m o r y Co n t r o l l e r ,由相应的虚拟I R 指令得到擦除㊁读取㊁编程等命令,相应的数据从V D R 得到或保存于V D R ㊂一般的F P G A 有足够的内部存储空间R AM ,所以上位机可以一次性把大容量数据通过虚拟J T A G 传给V D R ,后级的F l a s h C o n t r o l l e r 就可以启动相应的编程序列,从而节省了很多传输和边界移位的开销,极大地提高了F L A S H 的编程效率㊂图4就是一种实现的功能框图㊂敬请登录网站在线投稿 2018年第2期11图3 V i r t u a l J T A G实现原理图图4 虚拟J T A G 快速F L A S H 编程实现框图T A P 控制器里面对V i r t u a l J T A G 的内核进行了封装,导出了三个总线,分别是对下级模块输出的虚拟I R ㊁虚拟D R 以及从下级模块输入的虚拟D R ㊂下级的命令转换模块从输入的V I R 和V D R 得到命令和数据,通过W i s h b o n e 总线转换为F L A S H 控制器的命令和数据,以及得到返回的数据㊂F L A S H 控制器进行对F L A S H 的实际读写操作㊂V I R 定义为4比特位宽,其定义如表1所列㊂还是以1M B 的数据为例,V D R 存储深度为1K B ,表1 V I R V D R 对应关系表V I R 输入V D R 输出V D R (0000)读I D无定义32位宽的F L A S H I D(0001)导入数据1K B y t e 无定义(0010)开始编程无定义无定义(0011)读状态无定义1位宽,1:结束0:忙(0100)读取数据无定义1K BV I R 为4位㊂则一次数据搬运需要移动T s h i f t =1028次,一共需要搬运K=1024次㊂那么总时间为:T=KˑT c yc l e ˑT s h i f t =52.6336s <1m i n 如果V D R 的存储深度变得更大(一般F P G A 里面有足够多的内存),那么时间将更少,最后的瓶颈取决于F L A S H 自身的编程速度㊂结 语在工业4.0时代,对自动化测试的要求是更高效㊁更智能㊂而虚拟J T A G 技术不仅能优化诸如F L A S H 器件的编程效率,也能打通芯片内部逻辑的在线测试,提高了测试的覆盖率和有效性㊂参考文献[1]D r .B e n B e n n e t t s .I E E E 1149.1J T A Ga n d B o u n d a r y Sc a n T u t o r i a l [E B /O L ].[2017-10].h t t ps ://w w w .a s s e t -i n t e r t e c h .c o m /e r e s o u r c e s /i e e e -11491-j t a g -a n d -b o u n d a r y-s c a n -t u t o r i a l .[2]A L T E R A.V i r t u a l J T A G (a l t e r a _v i r t u a l _j t a g)I P C o r e U s e r [E B /O L ].[2017-10].h t t ps ://w w w.a l t e r a .c o m /e n _U S /p d f s /l i te r a t u r e /u g /u g _v i r t u a l jt a g .pd f .丁峰平(硬件工程师),主要研究方向为电信硬件电路㊁F P G A 设计和实现;陈莉萍(项目经理),主要研究方向为电信工程项目组织计划和实现㊂(责任编辑:杨迪娜 收稿日期:2017-10-23) 灵活,最后通过将该方法在一款实际D S P 设计中的应用说明了本方法是可行的㊁有效的㊂参考文献[1]韦祎.基于S ys t e m C 构建多核D S P 软件仿真平台[J ].微电子学与计算机,2016,33(4):8690.[2]彭德生,蒋志翔.基于S ys t e m C 的M I P S 处理器建模与架构[J ].计算机工程与设计,2015,36(4):10151021.[3]陈曦,徐宁仪,周祖成.嵌入式系统虚拟原型平台的S ys t e m C 实现[J ].计算器辅助设计与图形学报,2004,16(8):10701073.[4]K e i n e r t J ,S c h l i c h t e r T ,F a l k J ,e t a l .S y s t e m C o d e s i gn e r a n a u t o m a t i c E S L s y n t h e s i s a p p r o a c h b y d e s i g n s p a c e e x pl o r a -t i o n a n d b e h a v i o r a l s y n t h e s i s f o r s t r e a m i n g a p pl i c a t i o n [C ]//P r o c .o f t h e 45t h A n n u a l D e s i gn A u t o m a t i o n C o n f e r e n c e ,2008:580585.[5]莫寒以,王仁平.32位稀疏树可逆逻辑加法器的V e r i l o g 设计[J ].中国集成电路,2017,30(5):2833.[6]赵地,朱兴华.基于V e r i l o g的模拟前端时序的实现方法[J ].电子科技,2017,30(4):144147.[7]I E E E 16662005.I E E E S t a n d a r d S y s t e m C l a n g u a ge r ef e r -e n c e m a n u a l ,2006.[8]G h e n a s s i a F .T r a n s a c t i o n l e v e l m o d e l i n g w i t h S ys t e m C :T L M c o n c e p t s a n d a p p l i c a t i o n s f o r e m b e d d e d s ys t e m s [M ].B e r l i n :S p r i n ge r ,2005.[9]洪一,方体莲,赵斌等. 魂芯一号 数字信号处理器及其应用[J ].中国科学:信息科学,2015,45(4):574586.(责任编辑:薛士然 收稿日期:2017-11-16)。

并行端口EPP接口编程方法

附图是EPP数据写周期的时序图。

因它的握手信号由硬件完成,整个数据传输过程发生在一个ISA I/O周期内,因而使用EPP传送数据,协调可以获得500KB/S~2MB/S的传输率。

2.2、EPP端口及寄存器EPP 占用并行口基地址+0~+7共8个相邻的I/O映像地址。

基地址+3是EPP的地址口,对它进行I/O操作便产生地址周期;基地址+4是EPP的数据口,对它进行8位I/O读写操作,便产生数据读写周期。

如软件使用16位或32位的I/O操作,则会用到基地址+4~+7映像地址。

对基地址+0~+2的操作与SPP相同,这就保证了与SPP的兼容性。

但由于EPP为双向端口,其寄存器的内容比SPP有所增加(如表2所示)。

新增的位如下:(1)TIMEOUT位:逻辑“1”表示EPP读写操作时发生超时错误;逻辑“0”表示无超时发生。

(2)PCD位(Parallel Control Direction并行口方向控制):在双向传输种,PCD位为“0”时进行写操作;为“1”时进行读操作,8位数据线处于读状态。

2.3、EPP1.9和EPP1.7EPP1.7 是指Xircom 1.7版的提案,Intel在最初的82360 I/O控制器中使用这一协议,而那时IEEE1284标准还没建立起来。

EPP1.7与IEEE1284标准所规定的EPP1.9的区别在于,EPP1.7在读写周期开始时,nDATASTROBE或nADDRSTROBE置位时不考虑nWAIT 信号的状态。

这意味着外设不能通过清nWAIT来推迟一个EPP周期的开始。

因而服从1284标准的外设可以在EPP1.7的主机上工作,而EPP1.7的外设不能在服从1284 标准的主机上工作。

EPP 控制芯片中的看门狗时钟会防止系统锁死。

一般来讲,EPP1.9在读写周期开始10us 后,如果nWAIT仍没有响应,则发生TIMEOUT错误,状态寄存器的第0位TIMEOUT为“1”,EPP周期终止;而EPP1.7则是在EPP读写周期开始10us后仍未结束时,置TIMEOUT为“1”。

可编程并口8255A

例:对B口的PB1和PB0同时置位复位(产生方波) mov dx, 301h ;Port B 端口地址为301h lp:in al, dx or al, 03h out dx, al ;PB1PB0=11 call delay and al, 0fch out dx, al ;PB1PB0=00 call delay jmp lp

• 主要由数据总线缓冲器、读写控制逻辑、 A、B、C三个双向I/O端口及有关控制电 路组成。

– 数据总线缓冲器 三态双向8位缓冲,用于收发数据总线上的 数据 – 读/写控制逻辑 包括RD、WR、CS、A0、A1。控制总线的 开放、关闭和数据的传送方向。

8255A的编程控制字

8255A 共有两个控制字:①方式选择 控制字;②对端口C按位置位/复位控制字。 这两个控制字共用一个地址号。即当 地址线A1A0都为1时就是访问控制字寄存器 的片内地址。而用控制字的D7位来区分是 方式设定控制字,还是对C端口的按位置位 /复位命令。当D7位为1,是方式控制字; 若D7位为0,是对端口C按位置位/复位的 命令。

1、 方式0及其应用

0方式特点

①0 方式是一种基本输入 / 输出工作方式。 通常不用联络信号,或不使用固定的联 络信号,因此,所谓基本I/O方式是指查 询方式传送,也包括无条件传送。这种 方式不能采用中断方式和 CPU 交换数据。 输出锁存,输入有三态缓冲能力而无锁 存功能。

②在0方式下,彼此独立的两个8位和两个4 位并行口,共24根I/O线全部由用户支 配,都能被指定作为输入或者作为输出 用,共有16种不同的使用组态。要特别 强调的是,在0方式下,只能把C口的高4 位为一组或低4位为一组同时输入或输出, 不能再把4位中一部分作输入另一部分作 输出,即4位一起行动。

基于PC机并口编程控制的ISD芯片的语音录写方法

个, 内部地址计数器都将加 1 由此可见 , ID 。 对 S

语音芯片录写后 , 每个语音段 的起始位置一定在某 行 的行首 , O E M标记决定该语音段的结束地址 , 前 后相邻语音段之间可能在存储空间上不一定连续 , 但在地址上具有连续性。因此芯片内部信息段 的地 址获取有两种实现方法。 () 1定时计数法。通过对某段语音的播放 时间 进行计时 , 确定该段 占用 的地址空 间 , 从而在起始 地 址 的基 础上 计算 出结 束 地址 。 由于 ID 50的地 S 26 址分辨率为 10 坞 因此可以利用一个定时器连续 0 , n 产生 10 坞的定时,每 隔 10m 使地址计数器加 0n 0 s

是一种 更 为灵 活 的方法 , C语 言编程 实现 如下 : 其

l pr f dot n ()

E R M存储单元 , PO 划分为 6O个地址单元 , O 每一个 地址单元对应 的存储空间相当于 40k60 80 , 8  ̄0 = 0 B 对应 的录放 时 间是 10m 。 同时 , D器 件 通过 0 s I S E M标记决定各个信息段的结束 , O 并在每一地址 中 均匀的布置了 4个 E M标记定位点 ,O O E M可 以定

地 址位作 为工作 模式 选择 端 。

工作原理如图 1 所示 。 它以 P c机为平台, 预先利用 声卡对需写入 ID语音芯片的多段语音信号进行录 S 音, 并利用语音编辑软件进行优化处理, 分段形成波 此外 , 在样机和产品制造出来之后 , 还要抽样 进行各种试验 ,并对在试验中所 出的故障或问题 , 进行 分 析研究 和采取 措施加 以改进 。最 后对整 机 的 设计和制造作出可靠性的评估 、 鉴定和总结 。

维普资讯

r

芯片烧录的 ICP、ISP、IAP、JTAG 技术小结参考

本文档仅供参考,若有纰漏,欢迎提议改正……芯片烧录的ICP、ISP、IAP、JTAG 技术小结1. MCU传统编程方法最初,单片机使用并口编程,一般要用高压12V、5V,按照数据手册上的操作方式,使能编程引脚,最终是通过I2C或者SPI总线协议,发送相应的指令,进入编程模式,把程序写到MCU程序存储器。

这种方法,往往需要从实际最终产品上取下 MCU,放到编程器上烧录程序。

2. ICP技术ICP 是 In-Circuit Programming(在电路编程)的缩写. 当做为 ICP 编程器时,它事实上完全像一个通用编程器,除了它采用的只需占用 4 个引脚的串行接。

3.ISP技术In-System-Programming 即,在系统编程,烧录程序的时候,直接在系统进行,不需要把MCU取出来。

这种编程方式,需预先写ISP引导代码到MCU的ISP程序区。

上电后,目标MCU从ISP程序区启动并且执行ISP代码来检测是否需要进行ISP操作。

如果需要,目标MCU 将从编程器接收数据,并且使用ISP程序区的相应函数、指令,把数据写入到应用程序区。

ISP过程完成后, MCU将会从应用程序区重新引导来运行新的应用程序代码。

ISP接口如下图,主要有四根线:数据输入、输出,时钟,编程触发,分别对应于单片机的相应接口(由芯片手册得知)。

ISP数据传输符合 SPI协议。

ISP 编程操作是通过不同的指令实现的,以编程使能命令作为其他命令的前导命令,必须首先执行编程使能命令,再执行其他命令。

例如要擦除芯片,首先执行编程使能命令,然后执行芯片擦除命令,这样才能完成操作擦除。

部分指令如下:4. IAP 技术全称“In-ApplicationProgramming”,中文解释为“在程序中编程”。

MCU可以在系统运行中获取新代码并对自己重新编程,即用程序来改变程序。

实现IAP技术的核心是一段预先烧写在单片机内部的IAP程序。

这段程序主要负责与外部的上位机软件进行握手同步,然后将通过外设通信接口将来自于上位机软件的程序数据接收后写入单片机内部指定的闪存区域,然后再跳转执行新写入的程序,最终就达到了程序更新的目的。

并口定义及编程基础简明扼要

1 / 2并口定义及并口编程基础一、接口定义说明电脑的并口,通常是25针. 接口定义如下:功能说明:二、并口编程基础这些引脚,其实就是I/O 口。

而且是可以控制的,以软件的方式,非常简单。

在计算机内部,对应的寄存器如下:0x378是8bit 数据寄存器的地址,对应并口针的顺序是9,8,7,6,5,4,3,2 0x379是状态寄存器,11,10,12,13,15 - - -0x37A 是控制寄存器,- - - 并口中断允许位,17,16,14,1也就是说PC 的0x378可以用来做输入和输出,0x37A 的低4位可以用来输出,0x379是输入。

这样就可以用并口模拟很多时许,比如IIC 、JTAG 、SPI 等等。

注意:上述的寄存器地址是以0x378为基地址的。

如果基地址为0x3F0,那么他们的数据、状态、控制寄存器地址分别为0x3F0、0x3F1、0x3F2。

(基地址缺省的是0x378,也可在BIOS 里重新设置) 输入函数:int inport(int address); address 就是上面的寄存器地址 输出函数:int outport(int address,int value); 无论是DOS 下编程、还是Windows 下,都可用。

三、25针并口具体定义Pin Name Dir Description 1 /STROBE -> Strobe 2 D0 -> Data Bit 0 3 D1 -> Data Bit 1 4 D2 -> Data Bit 2 5 D3 -> Data Bit 3 6 D4 -> Data Bit 4 7 D5 -> Data Bit 5 8 D6 -> Data Bit 6 9 D7 -> Data Bit 7 10 /ACK <- Acknowledge11 BUSY <- Busy12 PE <- Paper End13 SEL <- Select14 /AUTOFD -> Autofeed15 /ERROR <- Error16 /INIT -> Initialize17 /SELIN -> Select In18 GND -- Signal Ground19 GND -- Signal Ground20 GND -- Signal Ground21 GND -- Signal Ground22 GND -- Signal Ground23 GND -- Signal Ground24 GND -- Signal Ground25 GND -- Signal Ground友情提示:范文可能无法思考和涵盖全面,供参考!最好找专业人士起草或审核后使用,感谢您的下载!。

可编程并行接口实验

实验报告课程名称微机原理与接口技术实验项目实验三可编程并行接口实验实验仪器 TPC-USB通用微机接口实验系统系别电子信息工程专业电子信息工程班级/学号学生姓名实验日期2011-5-19成绩_______________________指导教师___________一、实验目的1. 通过实验,掌握8255工作于方式0以及设置A、B、C口为输入或输出口的方法。

2. 掌握数码管数字显示和静态、动态驱动原理及编程设计实现。

二.实验设备1.PC微机系统一套2.TPC-USB通用微机接口实验系统一套三.实验要求1.实验前要作好充分准备,包括程序框图、源程序清单、调试步骤、测试方法、对运行结果的分析等。

2.熟悉与实验有关的系统软件(如编辑程序、汇编程序、连接程序和调试程序等)使用方法。

在程序调试过程中,有意识地了解并掌握TPC-USB通用微机接口实验系统的软硬件环境及使用,掌握程序的调试及运行的方法技巧。

3.实验前仔细阅读理解教材相关章节的相关内容,实验时必须携带教材及实验讲义。

四.实验内容及步骤(一)8255初始化设置和简单输入/输出实验1.实验电路如图1,8255C口接逻辑电平开关K0~K7,A口接LED显示电路L0~L7。

2. 按上述要求对8255进行初始化设置,并编程从8255C口输入数据,再从A口输出。

图1 实验连接参考电路图和流程图之一(二)数码管动态显示驱动设计1. 按图2连接好电路,将8255的A口PA0~PA6分别与七段数码管的段码驱动输入端a~g相连,位码驱动输入端S1,S0接8255 C口的PC1,PC0。

2. 编程从键盘连续输入两个十进制数,分别在两个数码管上显示;编程实现数码管的动态显示驱动。

3.(选作)从键盘连续输入两个任意数:若是ESC键输入,则程序退出运行;若是十六进制数键输入,则在数码管上显示十六进制数;若是上述键之外的输入,则不对数码管显示更新。

【参考提示:请仔细分析、理解“七段数码管”实验之LED1.ASM和LED3.ASM】图2 实验连接参考电路图之二编程提示:1. 8255控制寄存器端口地址为:28BH、A口的地址288H、B口的地址289H、C口的地址28AH2. 实验台上的七段数码管为共阴型,段码采用同相驱动,输入端加高电平,选中的数码管亮,位码加反相驱动器,位码输入端高电平选中。

C#(.Net)配合WQL实现并口读写

C#(.Net)配合WQL实现并⼝读写

最近做开发,要对POS打印机就进⾏编程,说⽩了,也就是⼀个端⼝读写,再根据打印机说明实现⼏个POS指令就OK了,但是遇到了⼀个困难的问题,因为是⽆⼈系统,⼀个打印机打印客户单据,⼀个打印历史单据,这个还不是最要命的,最要命的是⼀个是串⼝的,⼀个是并⼝的,对于串⼝还好办,因为.Net⾥有现成的SerialPort类,可是并⼝就难了。

搜了⼀下⽹上的资料,不外乎两种⽅法。

第⼀种是⽤win32 API来实现。

见

另⼀种⽅式是⽤第三⽅的动态连接库inpout32.dll

两种⽅式,各有优劣。

如果⽤win32 API的话,操作固然⽅便,但是有⼀个死⽳,就是⽆法读并⼝的数据。

如果⽤inpout32呢,到是能读能写,但是并⼝的地址(0x378,0x379,0x37a)并不是⼀个固定值。

参见⽂档

但是客户要求能实时检测打印机状态。

这个问题可是难住了⼀天。

怎么办?让客户⾃⼰到设备管理器⾥去找并⼝基址?MS有点太⼟了。

后来看了⼀些资料,突然发现WQL好像可以实现查找串⼝基址的功能,实验了⼀下,还真实现了,嘿嘿

好了,现在就贴代码

Code。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

信号源

PC PC PC PC

是否在连接 器处倒相 是 是 否 是

引脚: Centronics 1 14 31 36

注: 连接器中没有提供的附加位: 4:中断启用,此位为 1 时,IRQ 从 nAck 送往系统的中断控制器;为 0 时,IRQ 不送

往中断控制器。 5:双向控制端口的方向控制位,此位为 0 时,输出启动;为 1 时,不能输出;控制

获得途 径 网上下载 网上下载 网上下载

网上下载 网上下载

网上下载

三、实用并口编程

1.新建一个基于对话框的 Vc 工程

名称定义为 ParallelExample,参见下图,下一步工程类型选基于对话框.

2、引用基础资源文件

首先,把 WinIo.lib WinIo.h ParallelPort.cpp ParallelPort.h 拷贝到工程目录中,马上就要用到. 再把 WinIo.Dll WinIo.sys 拷贝到工程目录的 Debug 和 Release 目录中,以后工程发布后,这两 个文件要跟随工程一起。

并口控制开发

一、并口介绍(摘自互联网)

并口 SPP 模ቤተ መጻሕፍቲ ባይዱ寄存器定义

数据寄存器(基地址)

位 引脚:D-sub 信号名

02 13 24 35 46 57 68 79

数据位 0 数据位 1 数据位 2 数据位 3 数据位 4 数据位 5 数据位 6 数据位 7

信号源

PC PC PC PC PC PC PC PC

4、并口初始化

双击“初始化”按钮,在弹出的代码中加入程序如下 //在这里初始化并口 if(PaPort.InitPort()==TRUE) {

SetDlgItemText(IDC_EDIT_READ,"并口初始化成功,并口地址:0x378"); } else {

SetDlgItemText(IDC_EDIT_READ,"并口初始化失败!"); } 完成后如下图所示

注:1,2 位未定义。

信号源

外设 外设 外设 外设 外设

是否在连接器 处倒相 否 否 否 否 是

引脚: Centronics 32 13 12 10 11

控制寄存器(基地址+2)

位 引脚:D-sub 信号名

01 1 14 2 16 3 17

nStrobe nAutoLF nInit nSelectIn

“ParallelPort.cpp”文件,加入工程。

工程中引用加入类 如图,打开“ParallelExampleDlg.cpp”,加入#include "ParallelPort.h" //添加

并口类头文件。

定义一个并口类变量 在“ParallelExampleDlg.cpp”文件加入变量 PaPort。

引入 WinIo.lib 点 击 [ 工 程 ]->[ 设 置 ] 在 弹 出 的 对 话 框 中 选 择 [ 连 接 ] 标 签 , 然 后 在

“Link\Object/library modules”中加入 WinIo.lib 完成后如下图.

填加基础资源文件 选择“project\Add To Project\Files”菜单,选择“WinIo.h”、“ParallelPort.h”、

注解:PaPort.InitPort()是并口操作类中的并口初始化函数,传入参数是并口地址,由 于类定义时默认了 0x378 为并口地址,这里可以不用传参数了.如果初始化成功,传回布

尔变量 TRUE,运行一下,应该可以看到并口初始化成功的信息.

5、读数据口

双击“读数据口”按钮,在弹出的代码中加入程序如下 BYTE nPortData=PaPort.ReadData(); //从并口读到数据 CString a,b; GetDlgItemText(IDC_EDIT_READ,b); //获取编辑框中原有的文本 a.Format("\r\n 读到数据口数据:%2.2X",nPortData); b+=a; SetDlgItemText(IDC_EDIT_READ,b); //写入文本到编辑框 完成后如图所示(图 8)

读控制口

IDC_BTN_READCTL

写控制口

IDC_BTN_WRITECTL

读状态口

IDC_BTN_READSTATUS

单引脚操作

IDC_BTN_SIMPLESTITCH

用于显示收到的数据 用于填写要发送的数据 用于初始化并口 用于释放并口所占用的资源 用于读取并口数据总线 用于写并口数据口数据 用于读取并口控制总线 用于写并口控制口数据 用于读并口状态总线 用于引用单个引脚

端口可以读取外部逻辑电平。 6、7:未定义。

详解:上面罗列的是除去电源及地线后可用到的 IO 口,数据口 8 位,由状态寄存器第五位决 定能否输出,状态口共 5 位,控制口共 4 位.一般我们只用到数据口来传输数据.一般来说,并 口基地址是 0x378,也就是数据寄存器的地址,在并口类中默认.明白了这些以后,就可以对 并口进行相应的操作了.

是否在连接器 处倒相 否 否 否 否 否 否 否 否

引脚:Centronics

2 3 4 5 6 7 8 9

注:控制寄存器的第 5 位控制数据位是否能够输出。

状态寄存器(基地址+1)

位 引脚:D-sub 信号名

3 15 4 13 5 12 6 10 7 11

nError Select Paper Out nAck Busy

3、编辑对话框界面

下面在界面中加入八个按钮和两个文本编辑框,完成后如下图

其中,各控件 ID 如下

上面的编辑框 IDC_EDIT_READ

下面的编辑框 IDC_EDIT_WRITE

初始化

IDC_BTN_INIT

关闭释放

IDC_BTN_SHUTDOWN

读数据口

IDC_BTN_READDATA

写数据口

IDC_BTN_WRITEDATA

二、并口编程用到的几个资源文件

文件名

WinIo.sys WinIo.dll WinIo.lib

WinIo.h ParallelPort.cpp

ParallelPort.h

文件类型\介绍

基础并口编程使用文件 动态库:与 WinIo.sys 完成同并口的连接. 静态调用提供的引入库文件:虽然引入库文件和静态库 文件都是以 Lib 为扩展名的,但实际上有本质的区别. 这是 IO 操作的头文件. 这是一个并口操作类:用于同 WinIo 接口,并定义了相关 的操作函数. 虽然这个类用于同 WinIo 的操作接口,但这 个类并不是从 WinIO 派生的,只是一个独立的自定义类. 这是并口类的头文件.