MC-7725_datasheet

OV7725

4.内置IRCUT切换器,使得画质色彩更加清晰,细腻,通透!

技术参数:

OV7725图像板+IRCUT切换

图像传感器(DPS)

1/4"CMOS OV7725彩色摄像机

水平解析度

420线

扫描系统

Progressive Scan

名称ov7725图像板ircut切换图像传感器dps14cmosov7725彩色摄像机水平解析度420扫描系统progressivescan最低照度03lux镜头类型36mm6mm电子快门automaticfrom1601501100000sec

功能特性:

1.提供方案,模块,IRCUT!

2.低照非常度,噪点非常小,白天/夜视效果非常好!

最低照度

0.3 Lux

镜头类型

3.6mm/6mm

电子快门

Automatic from 1/60 (1/50) ~ 1/100,000 Sec.

自动增益控制

Auto

背光补偿

Auto

白平衡

Auto

同步模式

nal

信噪比

More Than 52dB (AGC off)

视频输出

1.0 Vp-p Composite / 75Ω

电源功耗

DC12V, 35mA

工作环境

-10℃~+50℃, RH85% Max.

图像板尺寸

32x32,38X38

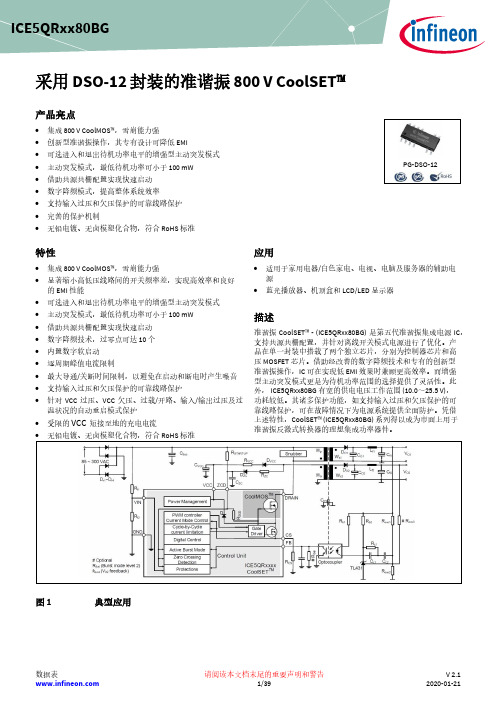

英飞凌 ICE5QRxx80BG 第五代准谐振集成电源IC 数据表

采用 DSO-12 封装的准谐振 800 V CoolSET ™产品亮点• 集成 800 V CoolMOS ™,雪崩能力强 • 创新型准谐振操作,其专有设计可降低 EMI• 可选进入和退出待机功率电平的增强型主动突发模式 • 主动突发模式,最低待机功率可小于 100 mW • 借助共源共栅配置实现快速启动 • 数字降频模式,提高整体系统效率 • 支持输入过压和欠压保护的可靠线路保护 • 完善的保护机制•无铅电镀、无卤模塑化合物,符合 RoHS 标准特性• 集成 800 V CoolMOS ™,雪崩能力强• 显著缩小高低压线路间的开关频率差,实现高效率和良好的 EMI 性能• 可选进入和退出待机功率电平的增强型主动突发模式 • 主动突发模式,最低待机功率可小于 100 mW • 借助共源共栅配置实现快速启动 • 数字降频技术,过零点可达 10 个 • 内置数字软启动 • 逐周期峰值电流限制• 最大导通/关断时间限制,以避免在启动和断电时产生噪音 • 支持输入过压和欠压保护的可靠线路保护•针对 VCC 过压、VCC 欠压、过载/开路、输入/输出过压及过温状况的自动重启模式保护• 受限的 VCC 短接至地的充电电流• 无铅电镀、无卤模塑化合物,符合 RoHS 标准应用• 适用于家用电器/白色家电、电视、电脑及服务器的辅助电源• 蓝光播放器、机顶盒和 LCD/LED 显示器描述准谐振 CoolSET ™ - (ICE5QRxx80BG) 是第五代准谐振集成电源 IC ,支持共源共栅配置,并针对离线开关模式电源进行了优化。

产品在单一封装中搭载了两个独立芯片,分别为控制器芯片和高压 MOSFET 芯片。

借助经改善的数字降频技术和专有的创新型准谐振操作,IC 可在实现低 EMI 效果时兼顾更高效率。

而增强型主动突发模式更是为待机功率范围的选择提供了灵活性。

此外, ICE5QRxx80BG 有宽的供电电压工作范围 (10.0~25.5 V), 功耗较低。

TCS34725 Color Sensor User Manual

TCS34725 Color SensorUser Manual OVERVIEWThis is a color sensor module based on TCS34725, will output RGB data and light intensity through the I2C interface. Its advantages include high sensitivity, wide dynamic range, accurate measuring, etc.SPECIFICATIONWorking voltage: 3.3V/5VController: TCS34725FNIO voltage: 3.3V/5VInterface:I2CDimension:27 x 20(mm)INTERFACEPIN DescriptionVCC 3.3V/5VGND GroundSDA I2C Data InputSCL I2C Clock InputINT Interrupt Output(Open drain output)LED LEDOverview (1)Specification (1)Interface (1)Hardware (3)Controller (3)Communication protocol (3)I2C write (3)I2C Read (4)I2C address (4)How to use (5)Download examples (5)examples (5)Raspberry Pi (5)STM32 (10)Arduino (12)FAQ (14)CONTROLLERTCS34725 is used for color sensing. TCS34725 is an I2C bus-based color light-to-digital converter with IR filter, provides a digital return of red, green , blue (RGB) and clear light sensing values. The high sensitivity, wide dynamic range and IR blocking filter make the TCS34725 an ideal color sensor solution for use under varying lighting conditions and through attenuating materials.COMMUNICATION PROTOCOLI2C bus has two lines, one is data line (SDA) and another is lock line (SDL). There are three kinds of signals when communicating, Start signal, Stop signal and Answer signal.Start signal: When SCL is High, SDA change from High to Low, it start to transmit data Stop signal: When SCL is High, SDA change from Low to High, it stop transmitting. Answer signal: Every time IC send back a certain Low plus to sender after it receives 8 bits data.I2C WRITEWhen working, Raspberry Pi (hereafter named as Master) will first send a Start signal, then send a byte to TCS34725(hereafter named as Slaver), whose first 7bits are address of Slaver and 1 bit write bit. Slave response with Answer signal every time it receives any data. Master send command register address to Slaver, then data of command register. Stop signals is sent to slave to stop communicating.I2C READWhen working, Master will first send a Start signal, then send a byte to Slaver, whose first 7bits are address of Slaver and 1 bit write bit. Slave response with Answer signal every time it receives any data. Master send command register address to Slave. After that, Mater will send a Start signal again, and then send a byte (7bits address and 1bit read bit) to Slaver. Slaver response and send data of the register to Master, master answer as well. Stop signals will be sent to stop communicating.I2C ADDRESSThe I2C device address of TCS34725 is 0x29TCS3472 datasheet page 34Note: 0x29 is 7bit in fact, therefore, when you set the I2C address, you should left-shift one bit, turn it to 0x52HOW TO USEDOWNLOAD EXAMPLESFind and download examples from Waveshare wiki:Extract the 7z you get:Arduino: examples for ArduinoRaspberry Pi: examples for Raspberry Pi(wiringPi, python, bcm2835)EXAMPLESRASPBERRY PIInsert the SD card (Raspbian installed)Copy the Raspberry Pi examples to SD card:Insert SD card to Raspberry Pi and power on, you can find the folder is listed in /bootCopy the examples to /home/pi and change its permission:INSTALL LIBRARIESTo run the examples, you need to first install libraries (wiringPi, bcm2835 and python) and enable I2C interface, otherwise example cannot work properly.BCM2835/mikem/bcm2835/Download the library from bcm2835 libraries and install:Note: The xx is the version number you download, for example, if the version you download is bcm2835-1.52. then the command you should execute is sudo tar zxvf bcm2835-1.52.tar.gzwiringPi libraries:Python libraries:Enable I2C interface:sudo raspi-configReboot Raspberry Pi and check I2C devices:HARDWARE CONNECTIONRUNNING EXAMPLEBCM2835 exampleWiringPi examplepython exampleNote: If you get error information that files are not exist when running BCM2835 or wiringpi example, please execute make command and try again.EXPECTED RESULTThe expected result of three examples are similar, here we take python codes as example:R, G, B value are printed in RGB888 format (DEC), C is light value without processing, RGB565 and RGB888 are HEX data printed in certain format. LUX is light value processed. CT is color temperature. (https:///wiki/Color_temperature) If you want to measure CT, please turn off LED. INT is interrupt, 1: light value is over threshold.You can turn the RGB value to color with tools below:https:///w/upload/5/53/Infrared-Temperature-Sensor-Code.7zSTM32Open STM32 project with Keil uVision5. The example is based on HAL libraries. Development board used is Waveshare XNUCLEO-F103RB, the chip isSTM32F103RBT6. Example uses UART2 (PA2, PA3) to print data, 115200, 8N1. HARDWARE CONNECTIONEXPECTED RESULTThis is the output when testing redYou can turn the RGB value to color with tools below:https:///w/upload/5/53/Infrared-Temperature-Sensor-Code.7zARDUINOThe development board used is Waveshare UNO PLUS(Compatible with Arduino UNO ), set serial monitor to 115200HARDWARE CONNECTIONEXPECTED RESULTThis is the output when testing redYou can turn the RGB value to color with tools below:https:///w/upload/5/53/Infrared-Temperature-Sensor-Code.7z1.Q: Raspberry Pi example initializing failed?A: Please check if you connect sensor correctly, and check i2C device withcommand i2cdetect -y 1Please correct connecting and restart2.Q: What happened when running example by mistake?A: If you find that python or bcm2835 examples cannot work properly afterrunning wiringpi codes, please just restart Raspberry Pi can test again3.Q: Data output are incorrect when using STM32 and Arduino examples?A: Please check if you choose the correct COM port (according to device manager).If all the setting are correct, please exchange RXD and TXD and try again.4.Q: Why the RGB data outputted are all 0A: Please check if you connect device correctly then press reset button5.Q: The RGB data output are all 253?A: The light intensity value is over measure range, you can try to modify the gain parameter in initial codes, or add statementTCS34725_Set_Gain(TCS34725_GAIN_16X))following initialize part.6.Q: Color detect is abnormal after modifying integrate timeA: The integrate time is relate to maximum data of RGB channels. If the color turns darker or lighter after modification, please try to change the brightness of LED 7.Q: Why interrupt cannot be triggered or be triggered all the time after modifyingintegrate timeA: Interrupt is relate to data of Clear channel. Data of Clear channel is influenced by integrate time. When gain is 60:Therefore, you should modify the threshold value if sample rate is fast. And please increase brightness of LED when you set integrate time to 2.4ms.。

OV7725 datasheet

© 2006 OmniVision Technologies, Inc.VarioPixel, OmniVision, and the OmniVision logo are registered trademarks of OmniVision Technologies, Inc.Version 1.0, September 12, 2006OmniPixel2 and CameraChip are trademarks of OmniVision Technologies, Inc.These specifications are subject to change without notice.Advanced Information Preliminary DatasheetOV7725 Color CMOS VGA (640x480) C AMERA C HIP TM SensorO mniision®with OmniPixel2TM TechnologyGeneral DescriptionThe OV7725 C AMERA C HIP ™ image sensor is a low voltage CMOS device that provides the full functionality of a single-chip VGA camera and image processor in a small footprint package. The OV7725 provides full-frame,sub-sampled or windowed 8-bit/10-bit images in a wide range of formats, controlled through the Serial CameraApplications•Cellular and picture phones •Toys•PC Multimedia•Digital still camerasKey SpecificationsOV7725Color CMOS VGA OmniPixel2™C AMERA C HIP™ Sensor OFunctional DescriptionFigure2 shows the functional block diagram of the OV7725 image sensor. The OV7725 includes:•Image Sensor Array (total array of 656 x 488 pixels, with active pixels 640 x 480 in YUV mode)•Analog Signal Processor•A/D Converters•Test Pattern Generator•Digital Signal Processor (DSP)•Image Scaler•Timing Generator2Proprietary to OmniVision Technologies, Inc.Version 1.0, September 12, 2006Functional DescriptionVersion 1.0, September 12, 2006Proprietary to OmniVision Technologies, Inc.3OImage Sensor ArrayThe OV7725 sensor has an image array of 656x 488pixels for a total of 320,128 pixels, of which 640x 480pixels are active (307,200 pixels). Figure 3 shows a cross-section of the image sensor array.Figure 3 Image Sensor ArrayIn addition to the A/D conversion, this block also has the following functions:•Digital Black-Level Calibration (BLC)•Optional U/V channel delay •Additional A/D range controlsIn general, the combination of the A/D Range Multiplier and A/D Range Control sets the A/D range and maximum value to allow the user to adjust the final image brightness as a function of the individual application.Test Pattern GeneratorOL /I OH drive currentthe C AMERA C HIP sensor operation. Refer to OmniVision Technologies Serial Camera Control Bus (SCCB)Specification for detailed usage of the serial control port.4Proprietary to OmniVision Technologies, Inc.Version 1.0, September 12, 2006OV7725Color CMOS VGA OmniPixel2™ C AMERA C HIP ™ SensorOPin DescriptionTable 1Pin DescriptionPin NumberName Pin Type Function/DescriptionA1ADVDD Power ADC power supplyA2RSTB Input System reset input, active lowA3VREFH Reference Reference voltage - connect to ground using a 0.1 µF capacitor A4FSIN Input Frame synchronize input A5SCL Input SCCB serial interface clock input A6D0a a. D[9:0] for 10-bit Raw RGB data (D[9] MSB, D[0] LSB)Output Data output bit[0]B1ADGND Power ADC groundB2VREFN Reference Reference voltage - connect to ground using a 0.1 µF capacitor B3AVDD Power Analog power supply B4AGND Power Analog groundB5SDA I/O SCCB serial interface data I/O B6HREF Output HREF outputC1PWDN Input (0)b b. Input (0) represents an internal pull-down resistor.Power Down Mode Selection0:Normal mode1:Power down mode C6VSYNC Output Vertical sync output D1D5Output Data output bit[5]D6D4Output Data output bit[4]E1D7Output Data output bit[7]E2D1Output Data output bit[1]E3DVDD Power Power supply (+1.8 VDC) for digital logic core E4PCLK Output Pixel clock outputE5DOVDD Power Digital power supply for I/O (1.7V ~ 3.3V)E6D6Output Data output bit[6]F1D9c c. D[9:2] for 8-bit YUV or RGB565/RGB555 (D[9] MSB, D[2] LSB)Output Data output bit[9]F2D3Output Data output bit[3]F3XCLK Input System clock input F4DOGND Power Digital ground F5D2Output Data output bit[2]F6D8OutputData output bit[8]Electrical CharacteristicsVersion 1.0, September 12, 2006Proprietary to OmniVision Technologies, Inc.5OElectrical CharacteristicsNOTE:Exceeding the Absolute Maximum ratings shown above invalidates all AC and DC electrical specifications and may result in permanent device damage.Table 2Operating ConditionsParameterMin Max Operating temperature -20°C +70°C Storage temperature a a.Exceeding the stresses listed may permanently damage the device. This is a stress rating only and functional operation of the sensor at these and any other condition above those indicated in this specification is not implied. Exposure to absolute maximum rating conditions for any extended period may affect reliability.-40°C+125°CTable 3 Absolute Maximum RatingsAmbient Storage Temperature-40ºC to +95ºCSupply Voltages (with respect to Ground)V DD-A4.5 V V DD-C 3 V V DD-IO4.5 VAll Input/Output Voltages (with respect to Ground)-0.3V to V DD-IO +0.5V Lead-free Temperature, Surface-mount process 245ºCTable 4DC Characteristics (-20°C < T A < 70°C)Symbol ParameterConditionMin Typ Max Unit V DD-A DC supply voltage – Analog – 3.0 3.3 3.6V V DD-C DC supply voltage – Digital Core – 1.62 1.8 1.98V V DD-IO DC supply voltage – I/O power – 2.5– 3.3V I DDA Active (Operating) Current See Note a a. V DD-A = 3.3V, V DD-C = 1.8V, V DD-IO = 3.3VI DDA = ∑{I DD-IO + I DD-C + I DD-A }, f CLK = 24MHz at 30 fps YUV output, no I/O loading 10 + 8bb. I DD-C = 10mA, I DD-A = 8mA, without loading mA I DDS-SCCB Standby Current See Note cc. V DD-A = 3.3V, V DD-C = 1.8V, V DD-IO = 3.3VI DDS-SCCB refers to a SCCB-initiated Standby, while I DDS-PWDN refers to a PWDN pin-initiated Standby 1mA I DDS-PWDN Standby Current 1020µA V IH Input voltage HIGH CMOS0.7 x V DD-IOV V IL Input voltage LOW 0.3 x V DD-IOV V OH Output voltage HIGH CMOS0.9 x V DD-IOV V OL Output voltage LOW 0.1 x V DD-IOV I OH Output current HIGH See Note dd. Standard Output Loading = 25pF, 1.2K Ω8mA I OL Output current LOW 15mA I LInput/Output LeakageGND to V DD-IO ± 1µAOV7725Color CMOS VGA OmniPixel2™C AMERA C HIP™ Sensor OTable 5 Functional and AC Characteristics (-20°C < T A < 70°C)Symbol Parameter Min Typ Max Unit Functional CharacteristicsA/D Differential Non-Linearity+ 1/2LSBA/D Integral Non-Linearity+1LSBAGC Range30dBRed/Blue Adjustment Range12dB Inputs (PWDN, CLK, RESET#)f CLK Input Clock Frequency102448MHzt CLK Input Clock Period2142100ns t CLK:DC Clock Duty Cycle455055% t S:RESET Setting time after software/hardware reset1ms t S:REG Settling time for register change (10 frames required)300ms SCCB Timing (see Figure4)f SCL Clock Frequency400KHzt LOW Clock Low Period 1.3μs t HIGH Clock High Period600ns t AA SCL low to Data Out valid100900ns t BUF Bus free time before new START 1.3μs t HD:STA START condition Hold time600ns t SU:STA START condition Setup time600ns t HD:DAT Data-in Hold time0μs t SU:DAT Data-in Setup time100ns t SU:STO STOP condition Setup time600ns t R, t F SCCB Rise/Fall times300ns t DH Data-out Hold time50ns Outputs (VSYNC, HREF, PCLK, and D[9:0] (see Figure5, Figure6, Figure7, and Figure8)t PDV PCLK[↓] to Data-out Valid5ns t SU D[9:0] Setup time15ns t HD D[9:0] Hold time8ns t PHH PCLK[↓] to HREF[↑]05ns t PHL PCLK[↓] to HREF[↓]05nsAC Conditions:• V DD: V DD-C = 1.8V, V DD-A = 3.3V, V DD-IO = 3.3V • Rise/Fall Times: I/O: 5ns, MaximumSCCB: 300ns, Maximum • Input Capacitance: 10pf• Output Loading: 25pF, 1.2KΩ to 3.3V• f CLK: 24MHz6Proprietary to OmniVision Technologies, Inc.Version 1.0, September 12, 2006Timing SpecificationsVersion 1.0, September 12, 2006Proprietary to OmniVision Technologies, Inc.7OTiming SpecificationsFigure 4 SCCB Timing DiagramOV7725Color CMOS VGA OmniPixel2™C AMERA C HIP™ Sensor OFigure 7 QVGA Frame Timing8Proprietary to OmniVision Technologies, Inc.Version 1.0, September 12, 2006Timing SpecificationsVersion 1.0, September 12, 2006Proprietary to OmniVision Technologies, Inc.9OFigure 9 RGB 565 Output Timing DiagramOV7725Color CMOS VGA OmniPixel2™C AMERA C HIP™ Sensor OFigure 11 RGB 444 Output Timing Diagram10Proprietary to OmniVision Technologies, Inc.Version 1.0, September 12, 2006Register Set Table6 provides a list and description of the Device Control registers contained in the OV7725. For all register Enable/Disable bits, ENABLE = 1 and DISABLE = 0. The device slave addresses are 42 for write and 43 for read.Table 6 Device Control Register List (Sheet 1 of 11)Address (Hex)RegisterNameDefault(Hex)R/W Description00GAIN00RW AGC – Gain control gain settingBit[7:0]:AGC[7:0] (see GREEN[7:6] (0x03) for AGC[9:8])•Range: [00] to [FF]01BLUE80RW AWB – Blue channel gain setting •Range: [00] to [FF]02RED80RW AWB – Red channel gain setting •Range: [00] to [FF]03GREEN00RW AWB – Green channel gain setting •Range: [00] to [FF]04COM100RW Common Control 1Bit[7:2]:ReservedBit[1:0]:AGC 2 MSBs, AGC[9:8]05BAVG00RW U/B Average LevelAutomatically updated based on chip output format06GAVG00RW Y/Gb Average LevelAutomatically updated based on chip output format07RAVG00RW V/R Average LevelAutomatically updated based on chip output format08AECH00RW Exposure Value – AEC MSBsBit[7:5]:AEC[15:8] (see register AEC for AEC[7:0]} Automatically updated based on chip output format09COM201RW Common Control 2Bit[7:5]:ReservedBit[4]:Soft sleep modeBit[3:2]:Pixel clock output delay control•Range: [00] to [11]Bit[1:0]:Output drive capability00:1x01:2x10:3x11:4x0A PID77R Product ID Number MSB (Read only) 0B VER21R Product ID Number LSB (Read only)0C COM310RW Common Control 3Bit[7]:Vertical flip image ON/OFF selectionBit[6]:Horizontal mirror image ON/OFF selectionBit[5]:Swap B/R output sequence in RGB output modeBit[4]:Swap Y/UV output sequence in YUV output modeBit[3]:Swap output MSB/LSBBit[2]:Tri-state option for output clock at power-down period 0:Tri-state at this period1:No tri-state at this periodBit[1]:Tri-state option for output data at power-down period 0:Tri-state at this period1:No tri-state at this periodBit[0]:Sensor color bar test pattern output enable0D COM441RW Common Control 4Bit[7:6]:PLL frequency control00:Bypass PLL01:PLL 4x10:PLL 6x11:PLL 8xBit[5:4]:AEC evaluate window00:Full window01:1/2 window10:1/4 window11:Low 2/3 window Bit[3:0]:Reserved0E COM501RW Common Control 5Bit[7]:Auto frame rate control ON/OFF selectionBit[6]:Auto frame rate control speed selectionBit[5:4]:Auto frame rate max rate control00:No reduction of frame rate01:Max reduction to 1/2 frame rate10:Max reduction to 1/4 frame rate11:Max reduction to 1/8 frame rate Bit[3:2]:Auto frame rate active point control00:Add frame when AGC reaches 2x gain01:Add frame when AGC reaches 4x gain10:Add frame when AGC reaches 8x gain11:Add frame when AGC reaches 16x gain Bit[1]:ReservedBit[0]:AEC max step control0:AEC increase step has limit1:No limit to AEC increase step0F COM643RW Common Control 6Bit[7:1]:ReservedBit[0]:Auto window setting ON/OFF selection when format changes(Hex)Name(Hex)R/W Description10AEC40RW Exposure ValueBit[7:0]:AEC[7:0] (see register AECH for AEC[15:8])11CLKRC80RW Internal ClockBit[7]:ReservedBit[6]:Use external clock directly (no clock pre-scale available)Bit[5:0]:Internal clock pre-scalarF(internal clock) = F(input clock)/(Bit[5:0]+1)•Range: [0 0000] to [1 1111]12COM700RW Common Control 7Bit[7]:SCCB Register Reset0:No change1:Resets all registers to default values Bit[6]:Resolution selection0:VGA1:QVGABit[5]:ITU656 protocol ON/OFF selectionBit[4]:ReservedBit[3:2]:RGB output format control00:GBR4:2:201:RGB56510:RGB55511:RGB444Bit[1:0]:Output format control00:YUV01:Processed Bayer RAW10:RGB11:Bayer RAW13COM88F RW Common Control 8Bit[7]:Enable fast AGC/AEC algorithmBit[6]:AEC - Step size limit0:Step size is limited to vertical blank1:Unlimited step sizeBit[5]:Banding filter ON/OFFBit[4]:Enable AEC below banding valueBit[3]:Fine AEC ON/OFF controlBit[2]:AGC EnableBit[1]:AWB EnableBit[0]:AEC Enable(Hex)Name(Hex)R/W Description14COM94A RW Common Control 9Bit[7]:Histogram or average based AEC/AGC selection Bit[6:4]:Automatic Gain Ceiling - maximum AGC value000:2x001:4x010:8x011:16x100:32x10164x110:128x111:Not allowedBit[3]:ReservedBit[2]:Drop VSYNC output of corrupt frameBit[1]:Drop HREF output of corrupt frameBit[0]:Reserved15COM1000RW Common Control 10Bit[7]:Output negative dataBit[6]:HREF changes to HSYNCBit[5]:PCLK output option0:Free running PCLK1:PCLK does not toggle during horizontal blank Bit[4]:PCLK reverseBit[3]:HREF reverseBit[2]:VSYNC option0:VSYNC changes on falling edge of PCLK1:VSYNC changes on rising edge of PCLK Bit[1]:VSYNC negativeBit[0]:Output data range selection0:Full range1:Data from [10] to [F0] (8 MSBs)16RSVD XX–Reserved17HSTART23 (VGA)3F (QVGA)RW Horizontal Sensor Size18HSIZEA0 (VGA)50 (QVGA)RWHorizontal Frame (HREF column) end high 8-bit (low 2bits are atHREF[1:0])19VSTRT07 (VGA)03 (QVGA)RW Vertical Frame (row) start high 8-bit (low 1 bit is at HREF[6])1A VSIZEF0 (VGA)78 (QVGA)RW Vertical Sensor Size1B PSHFT40RW Data Format - Pixel Delay Select (delays timing of the D[9:0] data relative to HREF in pixel units)•Range: [00] (no delay) to [FF] (256 pixel delay which accounts for whole array)1C MIDH7F R Manufacturer ID Byte – High(Read only = 0x7F) 1D MIDL A2R Manufacturer ID Byte – Low(Read only = 0xA2) 1E RSVD XX–Reserved(Hex)Name(Hex)R/W Description1F LAEC00RW Fine AEC Value - defines exposure value less than one line period20COM1110RW Common Control 11Bit[7:2]:ReservedBit[1]:Single frame ON/OFF selection Bit[0]:Single frame transfer trigger21RSVD XX–Reserved22BDBase FF RW Banding Filter Minimum AEC Value23DBStep01RW Banding Filter Maximum Step24AEW75RW AGC/AEC - Stable Operating Region (Upper Limit) 25AEB63RW AGC/AEC - Stable Operating Region (Lower Limit)26VPT D4RW AGC/AEC Fast Mode Operating RegionBit[7:4]:High nibble of upper limit of fast mode control zone Bit[3:0]:High nibble of lower limit of fast mode control zone27RSVD XX–Reserved28REG28??RW Register 28Bit[7:2]:ReservedBit[1]:Frame sync option (in external frame sync mode, set this bit to 1)Bit[0]:Auto frame adjust option0:Always decrease frame rate by 21:Decrease frame rate by inserting dummy verticalsync equal to maximum exposure lines29HOutSize A0 (VGA)50 (QVGA)RW Horizontal Data Output Size MSBs (2 LSBs at register EXHCH[1:0])2A EXHCH00RW Dummy Pixel Insert MSBBit[7:4]: 4 MSB for dummy pixel insert in horizontal direction Bit[3]:ReservedBit[2]:Vertical data output size LSBBit[1:0]:Horizontal data output size 2 LSBs2B EXHCL00RW Dummy Pixel Insert LSB8 LSB for dummy pixel insert in horizontal direction2C VOutSize F0 (VGA)78 (QVGA)RW Vertical Data Output Size MSBs (LSB at register EXHCH[2])2D ADVFL00RW LSB of Insert Dummy Lines in Vertical Direction (1 bit equals 1 line) 2E ADVFH00RW MSB of Insert Dummy Lines in Vertical Direction2F YAVE00RW Y/G Channel Average Value30LumHTh80RW Histogram AEC/AGC Luminance High Level Threshold31LumLTh60RW Histogram AEC/AGC Luminance Low Level Threshold(Hex)Name(Hex)R/W Description32HREF00RW Image Start and Size ControlBit[7]:Mirror image edge alignmentBit[6]:Vertical HREF window start control LSBBit[5:4]:Horizontal HREF window start control LSBsBit[3]:Data output bit shift test pattern ON/OFF control Bit[2]:Vertical sensor size LSBBit[1:0]:Horizontal sensor size 2 LSBs33DM_LNL00RW Dummy Line Low 8 Bits34DM_LNH00RW Dummy Line High 8 Bits35ADoff_B80RW AD Offset Compensation Value for B Channel36ADoff_R80RW AD Offset Compensation Value for R Channel37ADoff_Gb80RW AD Offset Compensation Value for Gb Channel38ADoff_Gr80RW AD Offset Compensation Value for Gr Channel39Off_B80RW Analog Process B Channel Offset Compensation Value 3A Off_R80RW Analog Process R Channel Offset Compensation Value 3B Off_Gb80RW Analog Process Gb Channel Offset Compensation Value 3C Off_Gr80RW Analog Process Gr Channel Offset Compensation Value3D COM1280RW Common Control 12Bit[7:6]:ReservedBit[5:0]:DC offset compensation for analog process3E COM13E2RW Common Control 13Bit[7]:Analog processing channel BLC ON/OFF control Bit[6]:ADC channel BLC ON/OFF controlBit[5:0]:Reserved3F COM141F RW Edge Enhancement AdjustmentBit[7:4]:ReservedBit[3:2]:AD offset compensation optionx0:Use R/Gr channel value for B/Gb01:Use B/Gb channel value for R/Gr11:Use B/Gb/R/Gr channel value independently Bit[1:0]:Analog processing offset compensation optionx0:Use R/Gr channel value for B/Gb01:Use B/Gb channel value for R/Gr11:Use B/Gb/R/Gr channel value independently40COM15C0RW Common Control 15Bit[7:4]:ReservedBit[3]:AD add 128 bit offsetBit[2:0]:Reserved41COM1608RW Common Control 16Bit[7:2]:ReservedBit[1:0]:BLC target 2 LSBs42TGT_B80RW BLC Blue Channel Target Value (Hex)Name(Hex)R/W Description43TGT_R80RW BLC Red Channel Target Value 44TGT_Gb80RW BLC Gb Channel Target Value 45TGT_Gr80RW BLC Gr Channel Target Value46LCC000RW Lens Correction Control 0Bit[7:3]:ReservedBit[2]:Lens correction control select0:R, G, and B channel compensation coefficient isset by registers LCC3 (0x49)1:R, G, and B channel compensation coefficient isset by registers LCC5 (0x4B), LCC3 (0x49), andLCC6 (0x4C), respectivelyBit[1]:ReservedBit[0]:Lens correction enable0:Disable1:Enable47LCC100RW Lens Correction Option 1 – X Coordinate of Lens Correction Center Relative to Array Center48LCC200RW Lens Correction Option 2 – Y Coordinate of Lens Correction Center Relative to Array Center49LCC350–Lens Correction Option 3G channel compensation coefficient when LCC0[2] (0x46) is 1 R, G, and B channel compensation coefficient when LCC0[2] is 04A LCC430–Lens Correction Option 4 – radius of the circular section where no compensation applies4B LCC550RW Lens Correction Option 5 (effective only when LCC0[2] is high) 4C LCC650RW Lens Correction Option 6 (effective only when LCC0[2] is high)4D FixGain00RW Analog Fix Gain AmplifierBit[7:6]:Gb channel fixed gainBit[5:4]:Gr channel fixed gainBit[3:2]: B channel fixed gainBit[1:0]:R channel fixed gain4E AREF0EF RW Sensor Reference Control •Range: [00] to [FF]4F AREF110RW Sensor Reference Current ControlBit[7:4]:Sensor reference current controlBit[3]:Internal regulator ON/OFF selection Bit[2]:ReservedBit[1:0]:Analog reference control50AREF260RW Analog Reference Control •Range: [00] to [FF]51AREF300RW ADC Reference Control •Range: [00] to [FF]52AREF400RW ADC Reference Control •Range: [00] to [FF](Hex)Name(Hex)R/W Description53AREF524RW ADC Reference Control •Range: [00] to [FF]54AREF67A RW Analog Reference Control •Range: [00] to [FF]55AREF7FC RW Analog Reference Control •Range: [00] to [FF]56-5F RSVD XX–Reserved60UFix80RW U Channel Fixed Value Output 61VFix80RW V Channel Fixed Value Output 62AWBb_blk FF RW AWB Option for Advanced AWB63AWB_Ctrl0F0RW AWB Control Byte 0Bit[7]:AWB gain enableBit[6]:AWB calculate enableBit[5]:ReservedBit[4:0]:WBC threshold 264DSP_Ctrl11F RW DSP Control Byte 1Bit[7]:FIFO enable/disable selectionBit[6]:UV adjust function ON/OFF selectionBit[5]:YUV444 to 422 UV channel option selection Bit[4]:Color matrix ON/OFF selectionBit[3]:Interpolation ON/OFF selectionBit[2]:Gamma function ON/OFF selectionBit[1]:Black defect auto correction ON/OFFBit[0]:White defect auto correction ON/OFF65DSP_Ctrl200RW DSP Control Byte 2Bit[7:4]:ReservedBit[3:0]:Scaling control66DSP_Ctrl310RW DSP Control Byte 3Bit[7]:UV output sequence optionBit[6]:ReservedBit[5]:DSP color bar ON/OFF selectionBit[4]:ReservedBit[3]:FIFO power down ON/OFF selectionBit[2]:Scaling module power down control 1Bit[1]:Scaling module power down control 2Bit[0]:Interpolation module power down control67DSP_Ctrl400RW DSP Control Byte 468AWB_bias00RW AWB BLC Level Clip69AWBCtrl15C RW AWB Control 16A AWBCtrl211RW AWB Control 26B AWBCtrl3A2RW AWB Control 36C AWBCtrl401RW AWB Control 4(Hex)Name(Hex)R/W Description6D AWBCtrl550RW AWB Control 56E AWBCtrl680RW AWB Control 66F AWBCtrl780RW AWB Control 770AWBCtrl80F RW AWB Control 871AWBCtrl900RW AWB Control 972AWBCtrl1000RW AWB Control 1073AWBCtrl110F RW AWB Control 1174AWBCtrl120F RW AWB Control 1275AWBCtrl13FF RW AWB Control 1376AWBCtrl14FF RW AWB Control 1477AWBCtrl15FF RW AWB Control 1578AWBCtrl1610RW AWB Control 1679AWBCtrl1770RW AWB Control 177A AWBCtrl1870RW AWB Control 187B AWBCtrl19F0RW AWB Control 197C AWBCtrl20F0RW AWB Control 207D AWBCtrl21F0RW AWB Control 217E GAM10E RW Gamma Curve 1st Segment Input End Point 0x04 Output Value 7F GAM21A RW Gamma Curve 2nd Segment Input End Point 0x08 Output Value 80GAM331RW Gamma Curve 3rd Segment Input End Point 0x10 Output Value 81GAM45A RW Gamma Curve 4th Segment Input End Point 0x20 Output Value 82GAM569RW Gamma Curve 5th Segment Input End Point 0x28 Output Value 83GAM675RW Gamma Curve 6th Segment Input End Point 0x30 Output Value 84GAM77E RW Gamma Curve 7th Segment Input End Point 0x38 Output Value 85GAM888RW Gamma Curve 8th Segment Input End Point 0x40 Output Value 86GAM98F RW Gamma Curve 9th Segment Input End Point 0x48 Output Value 87GAM1096RW Gamma Curve 10th Segment Input End Point 0x50 Output Value 88GAM11A3RW Gamma Curve 11th Segment Input End Point 0x60 Output Value 89GAM12AF RW Gamma Curve 12th Segment Input End Point 0x70 Output Value 8A GAM13C4RW Gamma Curve 13th Segment Input End Point 0x90 Output Value 8B GAM14D7RW Gamma Curve 14th Segment Input End Point 0xB0 Output Value 8C GAM15E8RW Gamma Curve 15th Segment Input End Point 0xD0 Output Value8D SLOP20RW Gamma Curve Highest Segment Slope - calculated as follows: SLOP[7:0] = (0x100 - GAM15[7:0]) x 4/38E DNSTh00RW De-noise Threshold(Hex)Name(Hex)R/W Description8F EDGE000RW Edge Enhancement Control 0Bit[7:5]:ReservedBit[4:0]:Edge enhancement strength control90EDGE108RW Edge Enhancement Control 1Bit[7:4]:ReservedBit[3:0]:Edge enhancement threshold control91DNSOff10RW Auto De-noise Threshold Control92EDGE21F RW Edge Enhancement Strength Low Point Control 93EDGE301RW Edge Enhancement Strength High Point Control 94MTX12C RW Matrix Coefficient 195MTX224RW Matrix Coefficient 296MTX308RW Matrix Coefficient 397MTX414RW Matrix Coefficient 498MTX524RW Matrix Coefficient 599MTX638RW Matrix Coefficient 69A MTX_Ctrl9E RW Matrix ControlBit[7]:Matrix double ON/OFF selection Bit[6]:ReservedBit[5]:Sign bit for MTX6Bit[4]:Sign bit for MTX5Bit[3]:Sign bit for MTX4Bit[2]:Sign bit for MTX3Bit[1]:Sign bit for MTX2Bit[0]:Sign bit for MTX19B BRIGHT00RW Brightness Control9C CNST40RW Contrast Control9D CNST_ctr00RW Contrast Control Center9E UVADJ011RW Auto UV Adjust Control 0Bit[7:4]:Auto UV adjust offset control 4 LSBs Bit[3:0]:Auto UV adjust threshold control9F UVADJ102RW Auto UV Adjust Control 1Bit[7:3]:Auto UV adjust valueBit[2]:ReservedBit[1]:Auto UV adjust stop controlBit[0]:Auto UV adjust offset control MSBA0SCAL000RW Scaling Control 0A1SCAL140RW Scaling Control 1 – for horizontal scaling control A2SCAL240RW Scaling Control 2 – for vertical scaling controlA3FIFOdlyM06RW FIFO Manual Mode Delay ControlA4FIFOdlyA00RW FIFO Auto Mode Delay Control(Hex)Name(Hex)R/W DescriptionRegister SetOA5RSVD XX –ReservedA6SDE 00RW Special Digital Effect Control A7USAT 40RW U Component Saturation Control A8VSAT 40RW V Component Saturation Control A9HUE080RW Hue Control 0AAHUE180RWHue Control 1AB SIGN 06RWSign Bit for Hue and ContrastBit[7:4]:ReservedBit[3:2]:Contrast sign bit Bit[1:0]:Hue sign bitAC DSPAuto FF RWDSP Auto Function ON/OFF ControlBit[7]:AWB auto threshold control Bit[6]:De-noise auto threshold controlBit[5]:Edge enhancement auto strength control Bit[4]:UV adjust auto slope controlBit[3]:Auto scaling factor control (register SCAL0 (0xA0))Bit[2]:Auto scaling factor control (registers SCAL1 (0xA1 and SCAL2 (0xA2))Bit[1:0]:ReservedNOTE: All other registers are factory-reserved. Please contact OmniVision Technologies for reference register settings.Table 6Device Control Register List (Sheet 11 of 11)Address (Hex)Register Name Default (Hex)R/W DescriptionOV7725Color CMOS VGA OmniPixel2™ C AMERA C HIP ™ SensorOPackage SpecificationsThe OV7725 uses a 28-ball Chip Scale Package 2 (CSP2). Refer to Figure 12 for package information, Table 7 for package dimensions and Figure 13 for the array center on the chip.Figure 12 OV7725-CSP2 Package SpecificationsNote: For OVT devices that are lead-free, all part marking letters are lower case. Underlining the last digit of the lot number indicates CSP2 is used.Package SpecificationsOSensor Array CenterFigure 13 OV7725 Sensor Array CenterOV7725Color CMOS VGA OmniPixel2™C AMERA C HIP™ Sensor OChief Ray AngleFigure 14 OV7725 Chief Ray AnglePackage SpecificationsOIR Reflow Ramp Rate Requirements OV7725 Lead-Free Packaged DevicesFigure 15 IR Reflow Ramp Rate RequirementsNote: For OVT devices that are lead-free, all part marking letters are lower caseOV7725Color CMOS VGA OmniPixel2™C AMERA C HIP™ Sensor ONote:•All information shown herein is current as of the revision and publication date. Please refer to the OmniVision web site () to obtain the current versions of alldocumentation.•OmniVision Technologies, Inc. reserves the right to make changes to their products or to discontinue any product or service without further notice (It is advisable to obtain current product documentation prior to placing orders).•Reproduction of information in OmniVision product documentation and specifications is permissible only if reproduction is without alteration and is accompanied by all associatedwarranties, conditions, limitations and notices. In such cases, OmniVision is not responsibleor liable for any information reproduced.•This document is provided with no warranties whatsoever, including any warranty of merchantability, non-infringement, fitness for any particular purpose, or any warrantyotherwise arising out of any proposal, specification or sample. Furthermore, OmniVisionTechnologies, Inc. disclaims all liability, including liability for infringement of any proprietary rights, relating to use of information in this document. No license, expressed or implied, byestoppels or otherwise, to any intellectual property rights is granted herein.•‘OmniVision’, ’VarioPixel’ and the OmniVision logo are registered trademarks of OmniVision Technologies, Inc. ’OmniPixel2’ and ’CameraChip’ are trademarks of OmniVision Technologies, Inc. All other trade, product or service names referenced in this release may be trademarks or registered trademarks of their respective holders. Third-party brands, names, and trademarks are the property of their respective owners.For further information, please feel free to contact OmniVision at info@.OmniVision Technologies, Inc.1341 Orleans DriveSunnyvale, CA USA(408) 542-3000。

MC8755_65 Datasheet rev 1.2

MC8755: 2100 MHz UMTS MC8765: 850/1900 MHz UMTS Power class 3 (+23dBm) MC8755 and MC8765: 850MHz GSM/GPRS/EDGE 900MHz GSM/GPRS/EDGE 1800MHz GSM/GPRS/EDGE 1900MHz GSM/GPRS/EDGE EDGE – Power Class E2 PCS/DCS Power Class 1 GSM – GMSK Power Class 4

AirCard EnabledTM

.Typical download rates of 600-800kbps, peak speeds up to 1.8Mbps* .Uses MSM6275™ chipset from QUALCOMM .MC8755 supports single band UMTS (HSDPA): 2100 MHz .MC8765 supports dual-band UMTS (HSDPA): 850/1900 MHz .Both MC8755 and MC8765 support quadband EDGE/GPRS/GSM: 850/900/1800/1900 MHz .Support third generation (3G) digital cellular standards .Enable rapid development of exceptional highspeed data products .Comprehensive WHQL-certified USB software driver

PCI Express Mini Card Standard

Superior Integration Support

MIC22705YML EV评估板1MHz,7A集成开关高效同步斜坡调压电源MLF和MicroLea

MIC22705YML EV Evaluation Board1MHz, 7A Integrated Switch High-Efficiency Synchronous Buck RegulatorMLF and Micro Lead Frame are registered trademarks of Amkor Technology, Inc.Micrel Inc. • 2180 Fortune Drive • San Jose, CA 95131 • USA • tel +1 (408) 944-0800 • fax + 1 (408) 474-1000 •General DescriptionThe Micrel MIC22705 is a high-efficiency, 7A, integrated switch, synchronous buck (step-down) regulator. The MIC22705 achieves more than 95% efficiency andswitches at 1MHz. The ultra-high speed control loop keepsthe output voltage within regulation even under the extreme transient load swings commonly found in FPGAs and low-voltage ASICs. The output voltage is pre-bias safeand is adjustable down to 0.7V. The MIC22705 offers a full range of sequencing and tracking options. The Enable/Delay (EN/DLY) and Power Good (PG) inputs allow versatile turn-on and turn-off sequencing across multiple devices. The Ramp Control™ (RC) input allows start-up voltage tracking, either directly or ratio-metrically. The MIC22705 is available in a 24-pin 4mm x 4mm MLF ®with a junction operating range from –40°C to +125°C. Data sheets and support documentation are found on the Micrel web site: . RequirementsThe MIC22705YML EV requires a power supply of 2.9V to 5.5V, and a test load. Ensure that the power supply can provide the wattage required for the chosen test load. Theload can be active (electronic load) or passive (resistor).Additionally, monitor the Power Good output (PG) with a multimeter or an oscilloscope if desired.PrecautionsThere is no reverse input protection on this board. When connecting supplies and signals ensure that correct polarities are observed.Getting Started 1. V INSuppliesConnect the V IN supply (2.9V to 5.5V) across the PVIN and PGND terminals. Monitor V IN at the PVIN and PGND terminals with a voltmeter.2. Enable/SHDN Inputs The enable input EN is internally pulled up with a 1µA current source. When external on/off control is desired, install Q1 and R5, and connect a logic level control signal to the SHDN input. When SHDN is high, the output is off, and when SHDN is low, the output is on.3. Monitor Outputs Monitor the output V OUT with a scope or DVM connectedacross the VOUT and PGND terminals. 4. Output LoadConnect a load across the VOUT and PGND terminals. Use an active or passive load.5. Turn On the Power Turn on the power supply and verify that V OUT = 1.8V. Ordering Information Part Number Description MIC22705YML EVEvaluation Board for the MIC22705YMLEV Board FeaturesSee the MIC22705YML datasheet for detailed explanations of these functions.Enable/Delay (EN/DLY)Enable/Delay allows delayed turn on of the MIC22705. Install a capacitor in location C6 to increase the start-up delay of the MIC22705.Shutdown Input (SHDN)SHDN allows enable/disable of the MIC22705 with an external logic signal. To activate the shutdown feature, install components into the locations labeled Q1 and R5 (component recommendations are listed in the Bill of Materials later in this document). With the components installed, force SHDN high to disable the MIC22705, and low to allow the MIC22705 to operate normally.Delay (DELAY)DELAY allows a delayed Power Good output (PG) indication. Install a capacitor in location C8 to increase the Power Good delay timing of the MIC22705. Ramp Control (RC)Ramp control allows slowing the slew rate of the MIC22705 output. Increase the value of capacitor C7 to reduce the slew rate.Power Good Output (PG)Open drain output PG pulls low when the output voltage of the MIC22705 is out of specification. PG is pulled up to V IN by a 47.5kΩ resistor.Switch Voltage (V SW)Test point V SW is provided to monitor the internal switching node. V SW is isolated from the switch node by 49.9Ωresistor R6.Typical CharacteristicsEvaluation Board SchematicBill of MaterialsItem Part Number Manufacturer DescriptionQty. C2012X5R0J226M TDK (1) 08056D226MAT AVX (2) C1, C2, C3, C4GRM21BR60J226ME39L Murata (3) 22µF/6.3V, 0805, Ceramic Capacitor506036D225TAAT2A AVX (2)2.2µF/6.3V, Ceramic Capacitor, X5R, Size 0805 GRM188R7160J225M Murata (3) 2.2µF/6.3V, Ceramic Capacitor, X7R, Size 0805 C5C1608X5R0J225M TDK (1)1C13 GRM188R71H103KA01D Murata (3)10nF, 0603, Ceramic Capacitor 1 Open(VJ0603Y102KXQCW1BC) Vishay (4) 1nF, 0603, Ceramic CapacitorOpen(GRM188R71H102KA01D) Murata (3) 1nF/50V, X7R, 0603, Ceramic Capacitor C7 Open(C1608C0G1H102J) TDK (1) 1nF/50V, COG, 0603, Ceramic Capacitor 1 C6, C8 OpenGRM1555C1H390JZ01D Murata (3) 39pF/50V, COG, 0402, Ceramic Capacitor C9VJ0402A390KXQCW1BCBCComponents (5)39pF /10V, 0402, Ceramic Capacitor 1 C3216X5R0J476M TDK (1)47µF/6.3V, X5R, 1206, Ceramic Capacitor GRM31CR60J476ME19 Murata (3)47µF/6.3V, X5R, 1206, Ceramic Capacitor C10, C11GRM31CC80G476ME19L Murata (3)47µF/4V, X6S, 1206, Ceramic Capacitor 2 VJ0402A101KXQCW1BC Vishay (4) 100pF, 0603, Ceramic CapacitorC12 GRM1555C1H101JZ01D Murata (3) 100pF/50V, COG, 0402, Ceramic Capacitor 1 SPM6530T-1R0M120 TDK (1) 1µH, 12A, size 7x6.5x3mm L1HCP0704-1R0-R Coiltronics (6)1µH, 12A, size 6.8x6.8x4.2mm 1 C IN BA1851A3477MEpcos (7) 470µF/10V, Elect., 8×11.5 1 R1 CRCW06031101FKEYE3 Vishay (4) Resistor, 1.10k, 0603, 1% 1 R2 CRCW04026980FKEYE3 Vishay (4) Resistor, 698Ω, 0603, 1%1 R3 CRCW06034752FKEYE3 Vishay (4) Resistor, 47.5k, 0603, 1% 1 R4 CRCW04022002FKEYE3 Vishay (4)Resistor, 20k, 0402, 1% 1 R5 Open(CRCW06031003FRT1) Vishay (4)Resistor, 100k, 0603, 1%1 R6 CRCW060349R9FKEA Vishay (4)49.9Ω Resistor, 1%, Size 0603 1 R7 CRCW06032R20FKEA Vishay (4) 2.2Ω Resistor, 1%, Size 06031 Open(2N7002E)Q1Open(CMDPM7002A) CentralSemiconductor (8)Signal MOSFET − SOT23-6 1 U1 MIC22705YMLMicrel, Inc.(6)1MHz, 7A Integrated Switch High-EfficiencySynchronous Buck Regulator1Notes:1. TDK: .2. AVX.: .3. Murata: .4. Vishay Tel: .5. BC Components: .6. Coiltronics: .7. Epcos: .8. Central Semiconductor: . 9. Micrel, Inc.: .Evaluation Board PCB LayoutMIC22705 Evaluation Board Top LayerMIC22705 Evaluation Board Top SilkMIC22705 Evaluation Board Mid-Layer 1 (Ground Plane)MIC22705 Evaluation Board Mid-Layer 2MIC22705 Evaluation Board Bottom LayerMIC22705 Evaluation Board Bottom Silk。

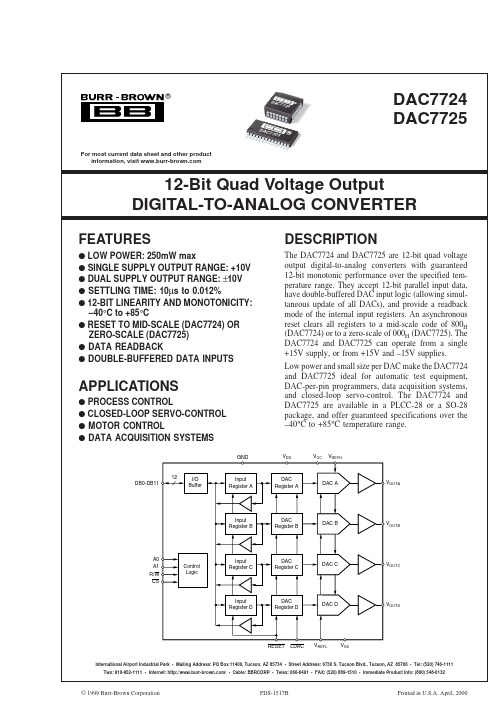

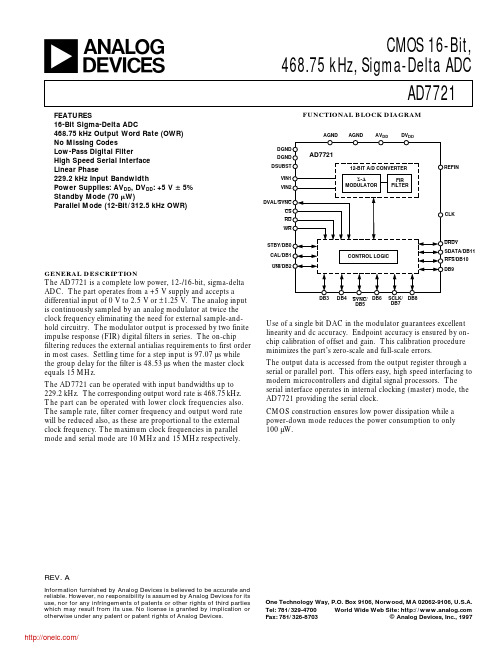

DAC7724

No Oscillation To VSS, VCC, or GND

VREFL ±5

VREFH

T

T

500

±20

–40°C to +85°C q RESET TO MID-SCALE (DAC7724) OR

ZERO-SCALE (DAC7725) q DATA READBACK q DOUBLE-BUFFERED DATA INPUTS

APPLICATIONS

q PROCESS CONTROL q CLOSED-LOOP SERVO-CONTROL q MOTOR CONTROL q DATA ACQUISITION SYSTEMS

+15.75

T

–14.25

–15.75

T

50

6

8.5

–8

–6

T

180

250

TEMPERATURE RANGE Specified Performance

–40

+85

T

±1

LSB(1)

±1

LSB

±1

LSB

Bits

T

LSB

T

ppm/°C

±1

LSB

T

LSB

±1

LSB

T

ppm / V

T

V

T

mA

T

pF

T

mA

T

®

DAC7724, 7725

2

SPECIFICATION (SINGLE SUPPLY)

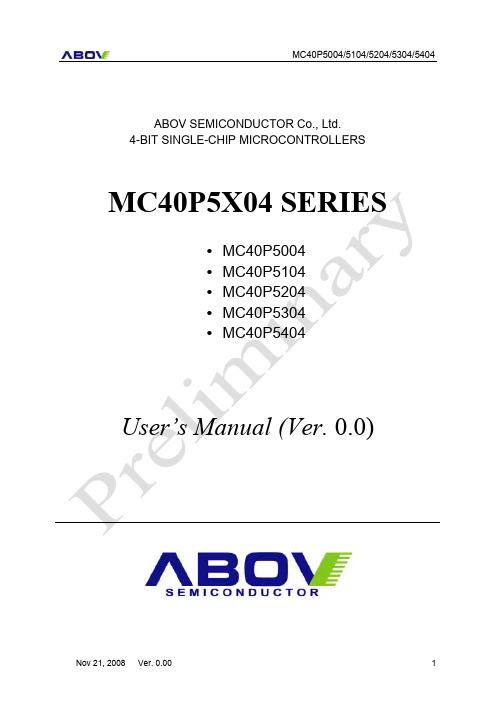

mc40p5004_datasheet_v0.0_090323

ABOV SEMICONDUCTOR Co., Ltd.4-BIT SINGLE-CHIP MICROCONTROLLERS MC40P5X04 SERIES•MC40P5004•MC40P5104•MC40P5204•MC40P5304•MC40P5404 User’s Manual (Ver. 0.0)REVISION HISTORY ( I ) VERSION 1.00 (Nov 21, 2008) This bookREVISION HISTORY ( II )VERSION 1.00 (Nov 21, 2008) This bookVersion 0.00Published by FAE Team2008 ABOV Semiconductor Co., Ltd. All rights reserved.Additional information of this manual may be served by ABOV Semiconductor offices in Korea or Distributors.ABOV Semiconductor reserves the right to make changes to any information here in at any time without notice.The information, diagrams and other data in this manual are correct and reliable; however, ABOV Semiconductor is in no way responsible for any violations of patents or other rights of the third party generated by the use of this manual.Table of Contents1. OVERVIEW (5)1.1 Description (5)1.2 Features (6)1.3 Ordering Information (6)2. BLOCK DIAGRAM (7)2.1 MC40P5004D (20 pin package) (7)2.2 MC40P5104D (20 pin package) (8)2.3 MC40P5204D (24 pin package) (9)2.4 MC40P5304D (24 pin package) (10)2.5 MC40P5404D (20 pin package) (11)3. PIN ASSIGNMENT (12)4. PACKAGE DIAGRAM (14)5. PIN DESCRIPTION (16)5.1 PIN DESCRIPTION (MC40P5004D, 20pins) (16)5.2 PIN DESCRIPTION (MC40P5104D, 20pins) (17)5.3 PIN DESCRIPTION (MC40P5404D, 20pins) (18)6. PORT STRUCTURES (19)7. ELECTRICAL CHARACTERISTICS (21)7.1 Absolute Maximum Ratings (Ta = 25℃) (21)7.2 Recommended Operating Conditions (21)7.3 Electrical characteristics (Ta=25℃, V DD= 3V) (21)8. Architecture (25)8.1 Program Memory (EPROM) (25)8.2 EPROM Address Register (26)8.3 Data memory (RAM) (27)8.4 X-register (X) (28)8.5 Y-register (Y) (28)8.6 Accumulator (Acc) (28)8.7 Arithmetic and Logic Unit (ALU) (28)8.8 State Counter (SC) (28)8.9 Clock Generator (29)8.10 Pulse Generator (30)8.11 Reset Operation (31)8.12 STOP Operation (33)8.13 Port Operation (33)9. Instruction (34)9.1 Instruction Table (35)9.2 DETAILS OF INSTRUCTION SYSTEM (37)9.3 Assembler Macro (48)10. SPGM(Serial Program) (49)10.1 Summary of Protocol (49)11. APPLICATION (53)11.1 Circuit Diagram (53)MC40P5004CMOS SINGLE-CHIP 4-BIT MICROCONTROLLER1. OVERVIEW1.1 DescriptionThe MC40P5x04D series is 4-bit remote control MCU which uses CMOS technology and the 4K bytes EPROM version. This enables transmission code outputs of different configurations, multiple customcode output, and double push key output for easy fabrication. The MC40P5x04D series is suitable for remote control of TV, VCR, FANS, Air-conditioners, Audio Equipments, Toys, Games etc.1.2 Features∙Program memory : 4,096 bytesMTP : 1K * 4, 2K * 2, 4K * 1∙Data memory : 32 × 4 bits∙43 types of instruction set∙ 3 levels of subroutine nesting∙Operating frequency : 2.4MHz ~ 4MHz2. BLOCK DIAGRAM2.1 MC40P5004D (20 pin package)ALUY-reg4 4 444 88 12124 4 44164 6422.2 MC40P5104D (20 pin package)ALUY-reg4 4 444 88 12124 444164 7422.3 MC40P5204D (24 pin package)ALUY-reg4 4 444 88 12124 4 44164 1010422.4 MC40P5304D (24 pin package)ALUY-reg4 4 444 88 12124 4 44164 1010422.5 MC40P5404D (20 pin package)ALUY-reg4 4 444 88 12124 4 44164 6423. PIN ASSIGNMENTFig 3-3 MC40P5204D Pin Assignment(24 PIN)REMDRV : open drain outputVPP : K3 ( PIN No.8) Fig 3-4 MC40P5304D Pin Assignment(24 PIN)REMOUT : Push Pull outputVPP : K3 ( PIN No.8)4. PACKAGE DIAGRAMFig 4-1 20SOP (209MIL)Fig 4-2 20SOP (300MIL)Fig 4-3 24SOP (300MIL)5. PIN DESCRIPTION5.1 PIN DESCRIPTION (MC40P5004D, 20pins)5.2 PIN DESCRIPTION (MC40P5104D, 20pins)5.3 PIN DESCRIPTION (MC40P5404D, 20pins)6. PORT STRUCTURES- Built in feedback-resistor Note: at 24 pins, D0 ~D5 is changed to D0 ~ D9 (MC40P5204D, 24pins) D8, D9 pin is automatically “L” at STOP mode. There is REMDRV at MC40P5204D and REMOUT at MC40P5304D.7. ELECTRICAL CHARACTERISTICS 7.1 Absolute Maximum Ratings (Ta = 25℃)Fig 7-1. I OH1 vs V OH1 Graph (REMOUT Port)Fig 7-2. I vs. V Graph. ( D, R Port )Fig 7-3. I OL1 vs V OL1 Graph (REMOUT Port without built-in Transistor of MC40P5104D and MC40P5304D )Fig 7-4. I OL4 vs. V OL4 Graph ( REMDRV Port with built-in Transistor of MC40P5004D,MC40P5204D and MC40P5404)8. Architecture8.1 Program Memory (EPROM)The MC40P5x04D series can incorporate maximum 4,096 words (4 bank x 64 words x 16 page x 8bits) for program memory. Program counter PC (A0~A5), Page address register (A6~A9) and Bank address register (A10, A11) are used to address the whole area of program memory having an instruction (8bits) to be next executed.The program memory consists of 64 words on each page, and thus each page can hold up to 64 steps ofFig 8-1 Configuration of Program Memory8.2 EPROM Address RegisterThe following registers are used to address the EPROM.ㆍPage address register (PA)Holds EPROM’s page number (0~Fh) and bank address (0 ~ 3h)to be addressed.ㆍPage buffer register (PB)Value of PB is loaded by an LPBI command when newly addressing a page. Then it is shifted into the PAAvailable for addressing word on each page.ㆍStack register (SR)Stores returned-word address in the subroutine call mode.(1) Page address register and page buffer registerAddress one of pages #0 to #15 in the EPROM by the 4-bit binary counter. Unlike the program counter, the page address register is usually unchanged so that the program will repeat on the same page unless a page changing command is issued. To change the page address, take two steps such as (1) writing in the page buffer what page to jump (execution of LPBI) and (2) execution of BR or CAL, because instruction code is of eightbits so that page and word can not be specified at the same time.In case a return instruction (RTN) is executed within the subroutine that has been called In the other page, the page address will be changed at the same time.(2) Program counterThis 6-bit binary counter increments for each fetch to address a word in the currently addressed page having an instruction to be next executed. For easier programming, at turning on the power, the program counter is reset to the zero location. The PA is also set to "0". Then the program counter specifies the next EPROM address in random sequence. When BR, CAL or RTN instructions are decoded, the switches on each step are turned off notFig 8-2 Configuration of Data Memory8.4 X-register (X)X-register is consist of 2bit, X0 is a data pointer of page in the RAM, X1 is only used for selecting of D8~D9 with value of Y-registerTable 8-1 Mapping table between X and Y register8.5 Y-register (Y)Y-register has 4 bits. It operates as a data pointer or a general-purpose register.Y-register specifies and address (a0~a3) in a page of data memory, as well as it is used to specify an output port. Further it is used to specify a mode of carrier signal outputted from the REMOUT port. It can also be treated as a general-purpose register on a program.8.6 Accumulator (Acc)The 4-bit register for holding data and calculation results.8.7 Arithmetic and Logic Unit (ALU)In this unit, 4bits of adder/comparator are connected in parallel as it's main components and they are combined with status latch and status logic (flag.)(1) Operation circuit (ALU)The adder/comparator serves fundamentally for full addition and data comparison. It executes subtraction by making a complement by processing an inversed output of Acc (Acc +1)(2) Status logicThis is to bring an ST, or flag to control the flow of a program. It occurs when a specified instruction is executed in three cases such as overflow or underflow in operation and two inputs unequal.8.8 State Counter (SC)A fundamental machine cycle timing chart is shown below. Every instruction is one byte length. Its execution time is the same. Execution of one instruction takes 48 clocks for fetch cycle and 48clocks for execute cycle (96 clocks in total).Virtually these two cycles proceed simultaneously, and thus it is apparently completed in 48clocks (one machine cycle). Exceptionally BR, CAL and RTN instructions is normal execution time since they change an addressing sequentially. Therefore, the next instruction is prefetched so that its execution is completed within the fetch cycle.Figure 8-4 Oscillator circuit with external capacitor8.10 Pulse GeneratorThe following frequency and duty ratio are selected for carrier signal outputted from the REMOUT port depending on a PMR (Pulse Mode Register) value set in a program.*Default value is “0”* f PUL = Pulse frequency, f OSC = Oscillation frequencyTable 8-2 PMR selection table8.11 Reset OperationMC40P5x04D series have three reset sources. One is a built-in Power-on reset circuit,Another is a built-in Low VDD Detection circuit, the other is the overflow of Watch Dog Timer WDT). All reset operations are internal in the MC40P5x04D series.8.11.1 Built-in Power On Reset CircuitMC40P5x04D series has a built-in Power-on reset circuit consisting of an about 1㏁Resistor and a 3pFreset f osc = 3.64MHzFig8-5 Power –On Reset Circuit and Timing Chart8.11.2 Built-in Low VDD Reset CircuitMC40P5x04D series have a Low VDD detection circuit.If VDD become Reset Voltage of Low VDD Detection circuit at a active status, system reset occur and WDT is cleared.After VDD is increased upper Reset Voltage again, WDT is re-counted and if WDT is overflowed, system reset is released.8.12 STOP OperationStop mode can be achieved by STOP instructions.In stop mode1. Oscillator is stopped, the operating current is low.2. Watch dog timer is reset, D8~D9 output and REMOUT output are "L".3. Part of output pin other than WDT,D0~D3, D8~D9 output and REMOUT output have a value beforecome into stop mode.Stop mode is released when one of K or R input is going to "L".1. State of D0~D7 output and REMOUT output is return to state of before stop mode is achieved.9. InstructionINSTRUCTION FORMATAll of the 43 instruction in MC40P5x04D series is format in two fields of OP code and operand which consist of eight bits. The following formats are available with different types of operands.*FormatⅠAll eight bits are for OP code without operand.*FormatⅡTwo bits are for operand and six bits for OP code. Two bits of operand are used for specifying bits of RAM and X-register (bit 1 and bit 7 are fixed at ″0″)*FormatⅢFour bits are for operand and the others are OP code. Four bits of operand are used for specifying a constant loaded in RAM or Y-register, a comparison value of compare command, or page addressing in ROM.*Format ⅣSix bits are for operand and the others are OP code. Six bits of operand are used for word addressing in the ROM.9.1 Instruction TableThe MC40P5x04D series provides the following 43 basic instructions.*2 Operation is settled by a value of Y-register..9.2 DETAILS OF INSTRUCTION SYSTEMAll 43 basic instructions of the MC40P5X04D Series are one by one described in detail below.Description Form.Each instruction is headlined with its mnemonic symbol according to the instructions table given earlier. Then, for quick reference, it is described with basic items as shown below. After that, detailed comment follows.*Items :- Naming : Full spelling of mnemonic symbol- Status : Check of status function- Format :Categorized into Ⅰto Ⅳ- Operand : Omitted for Format Ⅰ- Function(1) LAYNaming : Load Accumulator from Y-RegisterStatus : SetFormat : IFunction : A ←Y<Comment> Data of four bits in the Y-register is unconditionally transferred to the accumulator. Data in the Y-register is left unchanged.(2) LYANaming : Load Y-register from AccumulatorStatus : SetFormat : IFunction : Y ← A<Comment> Load Y-register from Accumulator(3) LAZNaming : Clear AccumulatorStatus : SetFormat : IFunction : A ←0<Comment> Data in the accumulator is unconditionally reset to zero.(4) LMANaming : Load Memory from AccumulatorStatus : SetFormat : IFunction : M(X,Y) ← A<Comment> Data of four bits from the accumulator is stored in the RAM location addressed by the X-register and Y-register. Such data is left unchanged.(5) LMAIYNaming : Load Memory from Accumulator and Increment Y-RegisterStatus : SetFormat : IFunction : M(X,Y) ←A, Y ←Y+1<Comment> Data of four bits from the accumulator is stored in the RAM location addressed by the X register and Y-register. Such data is left unchanged.(6) LYMNaming : Load Y-Register form MemoryStatus : SetFormat : IFunction : Y ←M(X,Y)<Comment> Data from the RAM location addressed by the X-register and Y-register is loaded into the Y-register. Data in the memory is left unchanged.(7) LAMNaming : Load Accumulator from MemoryStatus : SetFormat : IFunction : A ←M(X,Y)<Comment> Data from the RAM location addressed by the X-register and Y-register is loaded into the Y-register. Data in the memory is left unchanged.(8) XMANaming : Exchanged Memory and AccumulatorStatus : SetFormat : IFunction : M(X,Y) ↔ A<Comment> Data from the memory addressed by X-register and Y-register is exchanged with data from the accumulator. For example, this instruction is useful to fetch a memory word into theaccumulator for operation and store current data from the accumulator into the RAM. Theaccumulator can be restored by another XMA instruction.(9) LYI iNaming : Load Y-Register from ImmediateStatus : SetFormat : ⅢOperand : Constant 0 ≤i ≤15Function : Y ←i<Purpose> To load a constant in Y-register. It is typically used to specify Y-register in a particular RAM word address, to specify the address of a selected output line, to set Y-register forspecifying a carrier signal outputted from OUT port, and to initialize Y-register for loopcontrol. The accumulator can be restored by another XMA instruction.<Comment> Data of four bits from operand of instruction is transferred to the Y-register.(10) LMIIY iNaming : Load Memory from Immediate and Increment Y-RegisterStatus : SetFormat : ⅢOperand : Constant 0 ≤i ≤15Function : M(X,Y) ←i, Y ←Y + 1<Comment> Data of four bits from operand of instruction is stored into the RAM location addressed by the X-register and Y-register. Then data in the Y-register is incremented by one.(11) LXI nNaming : Load X-Register from ImmediateStatus : SetFormat : ⅡOperand : X file address 0 ≤n ≤3Function : X ←n<Comment> A constant is loaded in X-register. It is used to set X-register in an index of desired RAM page. Operand of 1 bit of command is loaded in X-register.(12) SEM nNaming : Set Memory BitStatus : SetFormat : ⅡOperand : Bit address 0 ≤n ≤3Function : M(X,Y,n) ← 1<Comment> Depending on the selection in operand of operand, one of four bits is set as logic 1 in the RAM memory addressed in accordance with the data of the X-register and Y-register.(13) REM nNaming : Reset Memory BitStatus : SetFormat : ⅡOperand : Bit address 0 ≤n ≤3Function : M(X,Y,n) ←0<Comment> Depending on the selection in operand of operand, one of four bits is set as logic 0 in the RAM memory addressed in accordance with the data of the X-register and Y-register.(14) TM nNaming : Test Memory BitStatus : Comparison results to statusFormat : ⅡOperand : Bit address 0 ≤n ≤3Function : M(X,Y,n) ←1?ST ← 1 when M(X,Y,n)=1, ST ←0 when M(X,Y,n)=0<Purpose> A test is made to find if the selected memory bit is logic. 1 Status is set depending on the result.(15) BR aNaming : Branch on status 1Status : Conditional depending on the statusFormat : ⅣOperand : Branch address a (Addr)Function : When ST =1 , PA ←PB, PC ←a(Addr)When ST = 0, PC ←PC + 1, ST ← 1Note : PC indicates the next address in a fixed sequence that is actually pseudo-randomcount.<Purpose> For some programs, normal sequential program execution can be change. A branch is conditionally implemented depending on the status of results obtained by executing theprevious instruction.<Comment> • Branch instruction is always conditional depending on the status.a. If the status is reset (logic 0), a branch instruction is not rightly executed but the nextinstruction of the sequence is executed.b. If the status is set (logic 1), a branch instruction is executed as follows.• Branch is available in two types - short and long. The former is for addressing in thecurrent page and the latter for addressing in the other page. Which type of branch toexecute is decided according to the PB register. To execute a long branch, data of the PBregister should in advance be modified to a desired page address through the LPBIinstruction.(16) CAL aNaming : Subroutine Call on status 1Status : Conditional depending on the statusFormat : ⅣOperand : Subroutine code address a(Addr)Function : When ST =1 , PC ←a(Addr) PA ←PBSR1 ←PC + 1, PSR1 ←PASR2 ←SR1 PSR2 ←PSR1SR3 ←SR2 PSR3 ←PSR2When ST = 0, PC ←PC + 1 PB ←PS ST ← 1Note : PC actually has pseudo-random count against the next instruction.<Comment> • In a program, control is allowed to be transferred to a mutual subroutine. Since a call instruction preserves the return address, it is possible to call the subroutine from differentlocations in a program, and the subroutine can return control accurately to the address that ispreserved by the use of the call return instruction (RTN).Such calling is always conditional depending on the status.a. If the status is reset, call is not executed.b. If the status is set, call is rightly executed.The subroutine stack (SR) of three levels enables a subroutine to be manipulated on threelevels. Besides, a long call (to call another page) can be executed on any level.• For a long call, an LPBI instruction should be executed before the CAL. When LPBI isomitted (and when PA=PB), a short call (calling in the same page) is executed.(17) RTNNaming : Return from SubroutineStatus : SetFormat : ⅠFunction : PC ←SR1 PA, PB ←PSR1SR1 ←SR2 PSR1 ←PSR2SR2 ←SR3 PSR2 ←PSR3SR3 ←SR3 PSR3 ←PSR2ST ←1<Purpose> Control is returned from the called subroutine to the calling program.<Comment> Control is returned to its home routine by transferring to the PC the data of the return address that has been saved in the stack register (SR1). At the same time, data of the pagestack register (PSR1) is transferred to the PA and PB.(18) LPBI iNaming : Load Page Buffer Register from ImmediateStatus : SetFormat : ⅢOperand : ROM page address 0 ≤i ≤15Function : PB ←i<Purpose> A new ROM page address is loaded into the page buffer register (PB). This loading is necessary for a long branch or call instruction.<Comment> The PB register is loaded together with three bits from 4 bit operand.(19) AMNaming : Add Accumulator to Memory and Status 1 on CarryStatus : Carry to statusFormat : ⅠFunction : A ←M(X,Y)+A, ST ←1(when total>15),ST ←0 (when total ≤15)<Comment> Data in the memory location addressed by the X and Y-register is added to data of the accumulator. Results are stored in the accumulator. Carry data as results is transferred tostatus. When the total is more than 15, a carry is caused to put ″1″in the status. Data in thememory is not changed.(20) SMNaming : Subtract Accumulator to Memory and Status 1 Not BorrowStatus : Carry to statusFormat : ⅠFunction : A ←M(X,Y) - A ST ←1(when A ≤M(X,Y))ST ←0(when A > M(X,Y))<Comment> Data of the accumulator is, through a 2`s complemental addition, subtracted from the memory word addressed by the Y-register. Results are stored in the accumulator. If dataof the accumulator is less than or equal to the memory word, the status is set to indicate thata borrow is not caused. If more than the memory word, a borrow occurs to reset the statusto ″0″.(21) IMNaming : Increment Memory and Status 1 on CarryStatus : Carry to statusFormat : ⅠFunction : A ←M(X,Y) + 1 ST ←1(when M(X,Y) ≥15)ST ←0(when M(X,Y) < 15)<Comment> Data of the memory addressed by the X and Y-register fetched. Adding 1 to this word, results are stored in the accumulator. Carry data as results is transferred to the status.When the total is more than 15, the status is set. The memory is left unchanged.(22) DMNaming : Decrement Memory and Status 1 on Not BorrowStatus : Carry to statusFormat : ⅠFunction : A ←M(X,Y) - 1 ST ←1(when M(X,Y) ≥1)ST ←0 (when M(X,Y) = 0)<Comment> Data of the memory addressed by the X and Y-register is fetched, and one is subtracted from this word (addition of Fh)> Results are stored in the accumulator. Carry data asresults is transferred to the status. If the data is more than or equal to one, the status is setto indicate that no borrow is caused. The memory is left unchanged.(23) IANaming : Increment AccumulatorStatus : SetFormat : ⅠFunction : A ←A+1<Comment> Data of the accumulator is incremented by one. Results are returned to the accumulator.A carry is not allowed to have effect upon the status.(24) IYNaming : Increment Y-Register and Status 1 on CarryStatus : Carry to statusFormat : ⅠFunction : Y ←Y + 1 ST ←1 (when Y = 15)ST ←0 (when Y < 15)<Comment> Data of the Y-register is incremented by one and results are returned to the Y-register. Carry data as results is transferred to the status. When the total is more than 15, the status is set.(25) DANaming : Decrement Accumulator and Status 1 on BorrowStatus : Carry to statusFormat : ⅠFunction : A ← A - 1 ST ←1(when A ≥1)ST ←0 (when A = 0)<Comment> Data of the accumulator is decremented by one. As a result (by addition of Fh), if a orrow is caused, the status is reset to ″0″by logic. If the data is more than one, no borrowoccurs and thus the status is set to ″1″.(26) DYNaming : Decrement Y-Register and Status 1 on Not BorrowStatus : Carry to statusFormat : ⅠFunction : Y ←Y -1 ST ←1 (when Y ≥1)ST ←0 (when Y = 0)<Purpose> Data of the Y-register is decremented by one.<Comment> Data of the Y-register is decremented by one by addition of minus 1 (Fh). Carry data as results is transferred to the status. When the results is equal to 15, the status is set toindicate that no borrow has not occurred.(27) EORMNaming : Exclusive or Memory and AccumulatorStatus : SetFormat : ⅠFunction : A ←M(X,Y) + A<Comment> Data of the accumulator is, through a Exclusive OR, subtracted from the memory word addressed by X and Y-register. Results are stored into the accumulator.(28) NEGANaming : Negate Accumulator and Status 1 on ZeroStatus : Carry to statusFormat : ⅠFunction : A ← A + 1 ST ←1(when A = 0)ST ←0 (when A != 0)<Purpose> The 2`s complement of a word in the accumulator is obtained.<Comment> The 2`s complement in the accumulator is calculated by adding one to the 1`s complement in the accumulator. Results are stored into the accumulator. Carry data is transferred to thestatus. When data of the accumulator is zero, a carry is caused to set the status to ″1″.(29) ALEMNaming : Accumulator Less Equal MemoryStatus : Carry to statusFormat : ⅠFunction : A ≤M(X,Y) ST ←1 (when A ≤M(X,Y))ST ←0 (when A > M(X,Y))<Comment> Data of the accumulator is, through a complemental addition, subtracted from data in the memory location addressed by the X and Y-register. Carry data obtained is transferred to thestatus. When the status is ″1″, it indicates that the data of the accumulator is less than orequal to the data of the memory word. Neither of those data is not changed.(30) ALEINaming : Accumulator Less Equal ImmediateStatus : Carry to statusFormat : ⅢFunction : A ≤i ST ←1 (when A ≤i)ST ←0 (when A > i)<Purpose> Data of the accumulator and the constant are arithmetically compared.<Comment> Data of the accumulator is, through a complemental addition, subtracted from the constant that exists in 4bit operand. Carry data obtained is transferred to the status. The status isset when the accumulator value is less than or equal to the constant. Data of theaccumulator is left unchanged.(31) MNEZNaming : Memory Not Equal ZeroStatus : Comparison results to statusFormat : ⅠFunction : M(X,Y) ≠0 ST ←1(when M(X,Y) ≠0)ST ←0 (when M(X,Y) = 0)<Purpose> A memory word is compared with zero.<Comment> Data in the memory addressed by the X and Y-register is logically compared with zero.Comparison data is transferred to the status. Unless it is zero, the status is set.(32) YNEANaming : Y-Register Not Equal AccumulatorStatus : Comparison results to statusFormat : ⅠFunction : Y ≠A ST ←1 (when Y ≠A)ST ←0 (when Y = A)<Purpose> Data of Y-register and accumulator are compared to check if they are not equal.<Comment> Data of the Y-register and accumulator are logically compared. Results are transferred to the status. Unless they are equal, the status is set.(33) YNEINaming : Y-Register Not Equal ImmediateStatus : Comparison results to statusFormat : ⅢOperand : Constant 0 ≤i ≤15Function : Y ≠i ST ←1 (when Y ≠i)ST ←0 (when Y = i)<Comment> The constant of the Y-register is logically compared with 4bit operand. Results aretransferred to the status. Unless the operand is equal to the constant, the status is set.(34) KNEZNaming : K Not Equal ZeroStatus : The status is set only when not equalFormat : ⅠFunction : When K ≠0, ST ←1<Purpose> A test is made to check if K is not zero.<Comment> Data on K are compared with zero. Results are transferred to the status. For input data not equal to zero, the status is set.(35) RNEZNaming : R Not Equal ZeroStatus : The status is set only when not equalFormat : ⅠFunction : When R ≠0, ST ←1<Purpose> A test is made to check if R is not zero.<Comment> Data on R are compared with zero. Results are transferred to the status. For input data not equal to zero, the status is set.(36) LAKNaming : Load Accumulator from KStatus : SetFormat : ⅠFunction : A ←K<Comment> Data on K are transferred to the accumulator(37) LARNaming : Load Accumulator from RStatus : SetFormat : ⅠFunction : A ←R<Comment> Data on R are transferred to the accumulator(38) SONaming : Set Output Register LatchStatus : SetFormat : ⅠFunction : D(Y) ←1 0 ≤Y ≤7REMOUT ←1(PMR=5) Y = 8D0~D9 ←1 (High-Z) Y = 9R(Y) ←1 Ah ≤Y ≤DhR ←1 Y = EhD0~D9, R ←1 Y = Fh<Purpose> A single D output line is set to logic 1, if data of Y-register is between 0 to 7. Carrier frequency comes out from REMOUT port, if data of Y-register is 8.All D output line is set to logic 1, if data of Y-register is 9. It is no operation, if data of Y-register between 10 to 15.When Y is between Ah and Dh, one of R output lines is set at logic 1.When Y is Eh, the output of R is set at logic 1.When Y is Fh, the output D0~D9 and R are set at logic 1.<Comment> Data of Y-register is between 0 to 7, selects appropriate D output.Data of Y-register is 8, selects REMOUT port.Data of Y-register is 9, selects all D port.Data in Y-register, when between Ah and Dh, selects an appropriate R output (R0~R3).Data in Y-register, when it is Eh, selects all of R0~R3.Data in Y-register, when it is Fh, selects all of D0~D9 and R0~R3.(39) RONaming : Reset Output Register LatchStatus : SetFormat : ⅠFunction : D(Y) ←0 0 ≤Y ≤7REMOUT ←0 Y = 8D0~D9 ←0 Y = 9R(Y) ←0 Ah ≤Y ≤DhR ←0 Y = EhD0~D9, R ←0 Y = Fh<Purpose> A single D output line is set to logic 0, if data of Y-register is between 0 to 9.REMOUT port is set to logic 0, if data of Y-register is 9.All D output line is set to logic 0, if data of Y-register is 9.。

P87C552SBAA,512;中文规格书,Datasheet资料

• Two standard 16-bit timer/counters • 256 × 8 RAM, expandable externally to 64k bytes • Capable of producing eight synchronized, timed outputs • A 10-bit ADC with eight multiplexed analog inputs • Fast 8-bit ADC option • Two 8-bit resolution, pulse width modulation outputs • Five 8-bit I/O ports plus one 8-bit input port shared with analog

– OTP/EPROM – 3 bits

• Encryption array – 64 bytes • 4 level priority interrupt • 15 interrupt sources • Full-duplex enhanced UART

– Framing error detection – Automatic address recognition

INTEGRATED CIRCUITS

P87C552 80C51 8-bit microcontroller

8K/256 OTP, 8 channel 10 bit A/D, I2C, PWM, capture/compare, high I/O, low voltage (2.7 V to 5.5 V), low power

Product data

80C51 8-bit microcontroller

8K/256 OTP, 8 channel 10 bit A/D, I2C, PWM, capture/compare, high I/O, low voltage (2.7 V to 5.5 V), low power

MIC45205评估板:26V 6A DC-到-DC电源模块,超轻负载和超速控制是Micrel公司的