基于ZYNQ7000的S波段USB应答机设计

基于ZYNQ-7000开发板的摄像头采集与处理系统实验设计与实现

据 通 过 读 VDMA1 显 示, 将 写 VDMA2 写 入 的 数 据 通 过 读 VDMA2 显 示, 读 VDMA3 显 示 的 是写 VDMA1 写入内存中的数据在 ARM 中实现 边缘检测之后的输出,读 VDMA4 显示的是写 VDMA2 写入内存的数据在 FPGA 中实现边缘检 测之后的输出。虽然读 VDMA3 与读 VDMA4 显 示的均为边缘检测之后的结果,但是两者实现边 缘检测的硬件平台不同,分别为基于 ARM 的软 件算法以及基于 FPGA 的硬件算法。

摘 要:为了充分发挥 ZYNQ-7000 系列嵌入式处理器 FPGA+ARM 异构架构的优势,提出双路 OV5640 驱动实验的设计方案,具体说明如何完成图像处理算法的基于软硬件两种方法的实验设计与 实现,最后通过图像处理运行结果说明该系统为嵌入式教学提供有力支撑。 关键词:ZYNQ-7000 ;协同设计;OV5640 ;双目摄像头

Ⴟପത ས

协议,在相应的时序控制下,依次转换

为 DVI 数据输出到 HDMI 显示器中。

2.2 摄像头驱动 在图 1 中,硬件直接接收来自 OV5640 的视

频流数据输入,需要对摄像头完成相应的时序操 作。由于 Xilinx 公司提供的软核 IP 并没有驱动 OV5640 芯片,因此需要单独编写驱动程序,形 成相应的硬件电路,满足摄像头工作的时序要 求。OV5640 芯片硬件系统如图 2 所示。

:VILS तࠚႁሸແĻ

.x

.y

图 4 Sobel 边缘检测算子

4 图像处理系统运行结果

基于ZYNQ-7000的星载双模卫星导航接收机设计与实现

c h a r a c t e r i s t i c s o f GPS / BDS d u a l -mo d e c o mp a t i bi l i t y ,hi g h p r e c i s i o n a n d hi g h d y n a mi c .Th e o v e r a l l d e s i g n

s y s t e m. A s a t e l l i t e — b o r n e s a t e l l i t e n a v i g a t i o n r e c e i v e r b a s e d o n Z Y N Q 一 7 0 0 0 i S d e s i g n e d . w h i c h h a s t h e

第5 0卷 第 8期

2 0 1 7年 8月

通信技术

Co mmuni c a t i o n s Te c hn o l o g y

V0 1 . 5 0 No. 8 Aug . 2 01 7

d o i : 1 0 . 3 9 6 9 / j . i s s n . 1 0 0 2 - 0 8 0 2 . 2 0 1 7 . 0 8 . 0 4 5

f r a me , c a p t u r e a n d t r a c k i n g d e s i g n , p o s i t i o n i n g V e l o c i t y — me a s u r e me n t a l g o r i t h m a n d i o n o s p h e r i c e r r o r c o r r e c t i o n a r e d e s c r i b e d i n d e t a i l . F i n a l l y . s i mu l a t i o n o n l o w e a r t h - o r b i t s a t e l l i t e i n d i c a t e s t h e f e a s i b i l i t y o f t h e p r o p o s e d s c h e me .Me a n wh i l e , t h e s t a t i s t i c s o n t h e p o s i t i o n i n g e r r o r o f t h e s a t e l l i t e — b o r n e r e c e i v e r

基于Zynq-7000的千兆以太网传输系统设计与实现

第44卷第2期2021年2月核技术NUCLEAR TECHNIQUESV ol.44,No.2February2021基于Zynq-7000的千兆以太网传输系统设计与实现杨振雷刘承敏青先国朱宏亮包超蒋天植喻恒李进罗庭芳袁航单伟(中国核动力研究设计院核反应堆系统设计技术重点实验室成都610213)摘要随着核仪控系统的复杂性、集成度和数据量的不断增加,传统的控制器局域网络(Controller Area Network,CAN)或外围设备互连(Peripheral Component Interconnect,PCI)等数据总线在一定程度上已难以满足数据快速传输需求。

本文基于美国Xilinx公司Zynq-7000型片上系统(System on Chip,SoC)设计和实现了基于用户数据报协议(User Datagram Protocol,UDP)的千兆以太网传输系统。

首先,对UDP千兆以太网传输系统的实现方式进行了详细描述;然后,采用仿真工具ModelSim对系统方案可行性进行了仿真验证;最后,基于Xilinx 的开发板ZC706对系统方案进行了具体实现和功能性能验证。

验证结果表明:UDP传输速度最高可以达870Mbps,能够满足绝大多数核仪控系统的实际传输需求。

关键词Zynq-7000,用户数据报协议,以太网,传输系统中图分类号TL82DOI:10.11889/j.0253-3219.2021.hjs.44.020401Design and implementation of gigabit ethernet transmission system based on Zynq-7000YANG Zhenlei LIU Chengmin QING Xianguo ZHU Hongliang BAO Chao JIANG Tianzhi YU Heng LI Jin LUO Tingfang YUAN Hang SHAN Wei (Science and Technology on Reactor System Design Technology Laboratory,Nuclear Power Institute of China,Chengdu610213,China)Abstract[Background]With the increasing complexity,integration level and data volume of nuclear instrumentation and control system,conventional data buses,such as peripheral component interconnect(PCI)or controller area network(CAN),are difficult to meet the needs of rapid data transmission.[Purpose]This study aims to design and implement a Gigabit Ethernet transmission system based on the Xilinx's Zynq-7000system on chip (SoC)and user datagram protocol(UDP).[Methods]First of all,the system architecture of UDP Gigabit Ethernet transmission system for nuclear instrumentation and control system was introduced in detail.Then the ModelSim toolkit was employed to verify designed system functions by simulation.Finally,the Gigabit Ethernet transmission system was implemented using ZC706development board,and tested by experiment.[Results]Experimental results show that the data transmission speed can reach870Mbps.[Conclusions]The Gigabit Ethernet transmission system can meet the actual transmission requirements of most nuclear instruments and control system.Key words Zynq-7000,User datagram protocol(UDP),Ethernet,Transmission system随着核能行业的快速发展,核仪控系统复杂度逐渐提高,数据传输量也迅速增长,对数据传输提出了较高要求。

基于Zynq-7000平台的字符识别系统研究与实现

单位代码:10293 密级:公开专业学位硕士论文论文题目:基于Zynq-7000平台的字符识别系统研究与实现Research and Implementation of Character Recognition System Based onZynq-7000Thesis Submitted to Nanjing University of Posts and Telecommunications for the Degree ofMaster of EngineeringByWang WeiDongSupervisor: Prof. Zhu WeiPingFebruary 2016南京邮电大学学位论文原创性声明本人声明所呈交的学位论文是我个人在导师指导下进行的研究工作及取得的研究成果。

尽我所知,除了文中特别加以标注和致谢的地方外,论文中不包含其他人已经发表或撰写过的研究成果,也不包含为获得南京邮电大学或其它教育机构的学位或证书而使用过的材料。

与我一同工作的同志对本研究所做的任何贡献均已在论文中作了明确的说明并表示了谢意。

本人学位论文及涉及相关资料若有不实,愿意承担一切相关的法律责任。

研究生签名:_____________ 日期:____________南京邮电大学学位论文使用授权声明本人授权南京邮电大学可以保留并向国家有关部门或机构送交论文的复印件和电子文档;允许论文被查阅和借阅;可以将学位论文的全部或部分内容编入有关数据库进行检索;可以采用影印、缩印或扫描等复制手段保存、汇编本学位论文。

本文电子文档的内容和纸质论文的内容相一致。

论文的公布(包括刊登)授权南京邮电大学研究生院办理。

涉密学位论文在解密后适用本授权书。

研究生签名:____________ 导师签名:____________ 日期:_____________摘要随着机器视觉相关技术不断发展,嵌入式机器视觉相关应用已经渗透到我们日常生活的方方面面,例如自动驾驶汽车、智能化游戏机以及工业流水线中的智能机械臂都是嵌入式机器视觉的具体应用。

基于Zynq-7000的双目相机系统硬件平台设计

基于Z y n q 7000的双目相机系统硬件平台设计*周禹辰,卜凡亮(中国人民公安大学信息技术与网络安全学院,北京102623)*基金项目:国家重点研发计划(2016Y F C 0801005)㊂摘要:目前,仅获取二维图像的单目相机已经不能满足日益严峻的公安视频监控工作㊂本文设计了一款可以为三维图像分析提供硬件平台的双目相机,采用Z y n q 7000芯片作为双目相机系统解决方案㊂通过集成设计工具V i v a d o 编写,添加自定义I P 核(I n t e l l e c t u a l P r o p e r t y co r e ),配置各I P 的端口㊁电平㊁时钟等信息,最后对工程进行综合,生成完整系统文件后导入软件开发工具包编写显示程序㊂系统通过O V 5642双目摄像头实现两幅图像的实时采集和显示㊂测试结果表明,本硬件系统不仅可以显示高清㊁流畅的彩色视频图像,还保证了系统的高性能㊁低功耗㊂关键词:硬件平台;双目相机;Z y n q 7000;O V 5642中图分类号:T P 274.2 文献标识码:AD e s i g n o f H a r d w a r e P l a t f o r m o f B i n o c u l a r C a m e r a S y s t e m B a s e d o n Z y n q-7000Z h o u Y u c h e n ,B u F a n l i a n g(C o l l e g e o f I n f o r m a t i o n T e c h n o l o g y a n d C y b e r S e c u r i t y ,P e o p l e 's P u b l i c S e c u r i t y U n i v e r s i t y o f C h i n a ,B e i j i n g 102623,C h i n a )A b s t r a c t :A t p r e s e n t ,t h e m o n o c u l a r c a m e r a t h a t o n l y a c q u i r e t w o -d i m e n s i o n a l i m a g e s i s n o l o n g e r a b l e t o s a t i s f y t h e i n c r e a s i n g l y se v e r e p u b l i c s e c u r i t y v i d e o s u r v e i l l a n c e w o r k r e q u i r e m e n t s .A b i n o c u l a r c a m e r a t h a t c o u l d p r o v i d e a h a r d w a r e p l a tf o r m f o r 3D i m ag e a n a l ys i s i s d e s i g n e d .T h e Z y n q -7000c h i p i s u s e d a s a b i n o c u l a r c a m e r a s y s t e m s o l u t i o n .W e p r o g r a m a n d a d d c u s t o m I P c o r e s t o c o n f i gu r e t h e p o r t ,e l e c t r i c a l l e v e l ,c l o c k a n d o t h e r i n f o r m a t i o n o f e a c h I P ,a n d s y n t h e s i z e t h e p r o j e c t ,t h e n i m p o r t t h e s o f t w a r e d e v e l o pm e n t k i t a f t e r g e n e r a -t i n g a c o m p l e t e s y s t e m t o w r i t e t h e d i s p l a y p r o g r a m b y i n t e g r a t e d d e s i g n t o o l V i v a d o .T h e s y s t e m w i l l c a p t u r e a n d d i s p l a yt w o r e a l -t i m e i m a g e s t h r o u g h t h e O V 5642b i n o c u l a r c a m e r a .T h e t e s t r e s u l t s s h o w t h a t t h e h a r d w a r e s y s t e m c a n n o t o n l y d i s p l a y h i gh -d e f i n i t i o n ,s m o o t h i m a g e s ,b u t a l s o e n s u r e h i g h p e r f o r m a n c e a n d l o w p o w e r c o n s u m p t i o n o f t h e s ys t e m.K e y wo r d s :h a r d w a r e p l a t f o r m ;b i n o c u l a r c a m e r a ;Z y n q -7000;O V 5642引 言三维视觉成像原理有很多,如双目立体视觉㊁L i gh t C o d i n g 技术㊁T O F (T i m e o f F l i gh t )㊁激光散斑等,但它们有一个共同特点:数据采集量大㊂如L i g h t C o d i n g 技术是用光源照明给被照射物体编上码;T O F 飞行时间原理是通过脉冲调制光源发射红外光,通过反射回传感器的相位差来计算物体到相机的距离㊂这些立体成像技术在处理过程中都会伴随着巨大的数据吞吐量,因此需要性能强大的视频图像处理系统㊂传统的数字信号处理(D i g i t a l S i g-n a l P r o c e s s ,D S P )加处理器芯片(A c o r n R I S C M a c h i n e,A R M )构成的解决方案[1]在处理复杂视频数据时会出现带宽过低㊁数据处理能力较弱等缺点㊂而单纯采用现场可编程门阵列(F i e l d P r o g r a mm a b l e G a t e A r r a y,F P G A )[2]或D S P +F P G A[3-4]作为视频采集处理方案,可发挥其并行数据处理的优势,但是很难在短时间内进行复杂的图像算法处理㊂本文采用Z y n q 7000芯片的A R M+F P G A S o C (S y s t e m -o n -a -C h i p)解决方案,充分发挥F P G A 并行数据处理和A R M 软件开发的优势,运用软硬件协同开发的方法构建出一套三维相机硬件平台,以适应需求日益扩大的公安视频侦察工作㊂1 系统平台总体架构Z y n q 7000芯片由两部分组成:处理系统(P r o c e s s -i n g S y s t e m ,P S )和可编程逻辑(P r o g r a mm a b l e L o gi c ,P L )㊂两部分数据传输采用A X I 4接口协议[5]㊂系统设计框图如图1所示,总体由4大模块组成:图像采集㊁数据缓存㊁图像处理㊁视频显示,所有工作由P S 和P L 协同完成㊂最前端的图像采集在P L 端完成,图像传感器为O V 5642型C MO S 数字图像传感器,采用S C C B 总线配置,且与2总线兼容[6],该图像传感器可传输万像图1 系统设计框图素图像,采用V G A 时序输出图像,数据总线为8位,2个时钟周期传输一个像素,接收端将数据帧拼接成完整视频流数据㊂P L 部分采集到的图像数据通过I P 核A X I V D MA写入D D R 3,该I P 有两个A X I 4S t r e a m 接口,设置P L 端为主设备,用来传输转换格式之后的视频数据,P S 端存储器为从设备,用于接收视频数据㊂主从设备传输接口使用A X I H P 来提供高速数据传输㊂主从端口可并行工作㊂P S 端的处理器可通过A X I L i t e 总线对其内部寄存器进行访问来控制V D MA (V i d e o D i r e c t M e m o r y Ac c e s s )的工作模式,获取V D MA 的工作状态[7]㊂视频图像处理部分由P S 与P L 共同完成,前端P L 通过一些专用I P 核对拍摄到的图像进行预处理,经过格式转换后由A X I V D MA 将图像数据存入D D R ,P S 端根据缓存地址对存储的数据进行调取,后期可根据双目立体视觉匹配技术进行深度图像开发[8]㊂2 双目相机系统硬件平台组成三维相机系统的硬件平台主要包括以下三个部分:A X 7010开发板传输㊁储存㊁处理采集到的图像数据以及实现图像算法;O V 5642双目摄像头模组通过D V P 接口与P L 端实现图像的传输;H D M I 显示器用来显示通过摄像头采集和开发板处理之后的图像㊂2.1 A X 7010开发板本系统使用的开发板是基于X i l i n x Z y n q 7000架构提出的A R M+F P G A 片上系统方案所设计的A X 7010型开发板,Z y n q 7000芯片将双核C o r t e x A 9处理器与F P G A 可编程逻辑两部分集成在一块芯片中,即P S 端和P L 端㊂A R M 和F P G A 部分都拥有丰富的硬件设备和外围接口㊂A R M 处理器拥有内㊁外部存储器,外部包括I 2C 总线接口㊁接口㊁等㊂可编程逻辑部分的外设有:H D M I 接口㊁E E P R OM ㊁实时时钟D S 1302㊁扩展接口等㊂为了实现P S 端和P L 端之间数据高速互联传输,引入了A X I 4接口协议,用来描述主从设备之间的数据传输方式,这些都为Z y n q 7000平台实现嵌入式图像传输系统提供了有力的支撑[9]㊂图2为开发板实物图㊂图2 A X 7010开发板2.2 O V 5642双目摄像头模组摄像头模组采用两片O V 5642型C MO S 感光芯片,两路图像可同时显示或单独显示,摄像头通过D V P 接口与P L 端相连实现图像数据的传输,模组包含电源电路和时钟电路,支持多种图像格式,可采集不同分辨率图像㊂图3是双目摄像头的硬件上电操作时序图㊂图3 O V 5642图像传感器上电时序图t 0ȡ0m s ,从D O V D D 稳定到A V D D 稳定的延迟时间,在D O V D D 上电后快速将A V D D 置高㊂t 1ȡ0m s ,从X V C L K 置低到A V D D 关闭的延迟时间㊂t 2ȡ5m s ,从A V D D 稳定到摄像头上电稳定的延迟时间,在此之后P W D N 可拉低,上电之后X V C L K 可打开㊂t 3ȡ1m s ,从摄像头上电稳定到R E S E T B 拉高的延迟㊂t 4ȡ20m s ,从R E S E T B 拉高到S C C B 初始化的延迟㊂t 5ȡ0m s ,从A V D D 关闭到D O V D D 关闭的延迟㊂t 6ȡ0m s ,从R E S E T B 拉低到A V D D 关闭的延迟㊂3 基于V D M A 构建显示系统是提供的一款核,可将数据流在A X I S t r e a m 格式与M e m o r y M a p 格式之间相互转换来实现与D D R 3之间的通信㊂V D MA 主要应用于视频处理,可缩短开发周期,数据传输高效㊂O V 5642摄像头采集的图像数据通过V D MA 1和V D MA 2写入到A R M (P S 端)的D D R 中,P S 端处理器可对数据进行处理,单路摄像头需要两个V D MA ,一个作为视频的输入,另一个作为输出,因此双目相机需要4个V D MA ,以下介绍硬件系统的搭建㊂3.1 显示系统搭建本系统会用到X i l i n x 提供的I P ,如V D MA ㊁V I D _O U T ㊁V _T C 等实现视频输入输出及控制,也会用到自定义I P 来实现信号驱动和产生像素时钟㊂搭建好的系统如图4所示㊂图4 V D M A 硬件系统架构P r o c e s s i n g _s ys t e m 7中的D D R 已经存储了从P L 端采集到的图像数据,P S 端作为从设备,A x i _v d m a 作为主设备㊂图像数据使用高速S _A X I _H P 0口输出,在Z y n q 内部有4个A X I _H P 的接口,这些接口为P L 端高速访问P S 端的D D R 和O C M 提供了高速通路[10]㊂A x i _v d m a 与P S 端的H P 0接口需要通过A x i _m e m _i n t e r c o n 作为桥梁进行连接㊂通过A x i _v d m a 传输过来的图像数据需要利用A x i_S u b s e t _c o n v e r t e r 来进行数据格式转换,A x i _S u b s e t _c o n -v e r t e r 的作用就是将A X I 4总线接口的32位数据转换成24位数据㊂转换后的图像数据需要通过控制模块对显示格式和图像分辨率等进行设置,通过V _a x i 4s _v i d _o u t 和V _t c 两个I P 的组合实现一系列参数控制,本文通过此I P 将A X I 4S t r e a m 视频流转换成R GB 888格式的信号㊂由于采用(f e r e n t i a l S i gn a l )最小化传输差分信号原理,因此需要自定义I P 核来实现图像格式的转化,r gb 2d v i 为第三方I P 核,用来实现视频信号转TM D S 信号,以驱动显示器显示图像㊂A x i _d yn c l k 用来产生像素时钟㊂3.2 搭建硬件工程在V i v a d o 开发环境中新建工程,首先将两个自定义I P 核r g b 2d v i 和A x i _d yn c l k 添加到I P 库中㊂工程搭建的具体流程如下:①添加设置P r o c e s s i n g S y s t e m :在D i a gr a m 框中添加Z y n q 7000P r o c e s s i n g S ys t e m I P ,设置为S _A X I _H P 0_I n -t e r f a c e 接口有效,将M I O 48㊁M I O 49设置成U a r t 1,F C L K _C L K 0和F C L K _C L K 1使能,分别用作速度较低的A X I 4L i t e 外设时钟和传输速率较高的A X I S t r e a m 时钟,频率分别设置为100MH z 和140MH z ,使能P L 端的I R Q _F 2P [15:0]16个中断㊂②添加设置V D MA :在D i a gr a m 框的空白处添加A X I V i d e o D i r e c t M e m o r y Ac c e s s I P ,设置此I P 只打开读通道,M e m o r y M a p Da t a W i d t h 设置为64位,S t r e a m D a t a W i d t h 设置为32位,G e n L o c k M o d e 设置为M a s t e r ,让系统自动连接,这时会自动生成两个A X I I n t e r c o n n e c t ,一个连接P S 端M _A X I _G P 0总线和A X I _L I T E 接口,另一个用于连接P S 端H P 0接口和V D M A ,并且自动生成两个复位模块,一个用来复位低速A X I _L i t e 总线外设,另一个用来复位高速A X I _G P 0总线外设㊂③添加设置A x i s _S u b s e t _c o n v e r t e r :此I P 用来将32位视频流数据转换为24位,从接口S _A X I S 与V D MA 的主接口M _A X I _MM 2S 相连,时钟接口与处理器的F C L K _C L K 1相连㊂④添加设置V _a x i 4s _v i d _o u t :此I P 作用是产生控制信号及视频信号,将数据流转换成视频流输出,视频输出格式设置为R G B ,数据位宽为8位,时钟接口设为主设备,视频流输入接口与A x i s _S u b s e t _c o n v e r t e r 的M _A X I S 相连,时钟接口与处理器F C L K _C L K 1相连㊂⑤添加设置V _t c 与A x i _d yn c l k :添加后进行自动布线,系统会自动连接㊂⑥添加设置r gb 2d v i :这是之前自行添加的第三方I P ,用来将经过A x i s _S u b s e t _c o n v e r t e r 转换的R G B 格式图像数据转换为TM D S 差分信号,再通过H D M I 接口在显示器上显示㊂R G B 接口为视频信号输入端口,与V _a x i 4s _v i d _o u t 的V i d _i n _o u t 接口相连㊂⑦最后添加一个a x i _g pi o 作为热插拔检测信号,V D -MA 系统将开发板作为信号输出主设备,因此H D M I 的()信号是输入的㊂3.3 图像输出测试将建立好的硬件工程导入到S D K 开发环境,在S D K中对V D MA 和V _t c 两个I P 进行配置,实现任意图像的输出㊂将之前编写好的显示控制代码放入S D K 目录下,其中m a i n 函数初始化V D MA 设备,D i s p l a y I n i t i a l i z e 初始化d i s p C t r l 结构体,通过调用D e m o P r i n t T e s t 函数显示视频图像,D e m o P r i n t T e s t 中的参数p a t t e r n 用来决定显示什么图像,本实验是显示自定义图片,因此参数设置为0㊂pi c _800_600.h 头文件是从网上下载的一幅800ˑ600分辨率图片,程序会把图像数据写到f r a m e 数组中,再将数组中的数据通过相应函数写入D D R 存储器中,这样V D -MA 就可以从D D R 中读取图像数据㊂将程序下载至电路板并运行,显示器就会显示之前下载的图片㊂图5为程序运行结果㊂图5 基于V D M A 显示系统运行结果图6 双目显示系统框架3.4 双目显示系统构建双目显示系统的硬件工程在之前基于V D MA 显示系统的硬件工程基础上还需添加三个V D MA ,为了方便系统的调试,单路摄像头用两个V D MA ,视频的输入和输出用不同的V D MA ,即两路V D MA 输入和两路V D MA 输出,为了实现传输的方便高效,本文将两条V D MA 输出的A X I S t r e a m 合并为一条A X I S t r e a m 流,由于两路视频流对D D R 传输带宽要求高,应使用传输效率高的H P 0和H P 1接口来满足双目摄像头的视频数据传输需求㊂双目系统多了一个重要的O S D (V i d e o O n S c r e e n D i s p l a y)模块,因为双摄像头采集的两个画面在同一显示屏显示需要屏幕划分和相应属性设置,需要O S D 进行控制,此模块可对多个外部输入视频源进行内部图形控制,可对每个图层进行大小调整㊁前后移动㊁不同透明度图层的覆盖等㊂搭建的系统框架图如图6所示㊂4 测试结果及分析在V i v a d o 中搭建好硬件工程,检查无误之后生成比特流,导出硬件,启动S D K ,之前搭建好的硬件信息会自动导入到S D K 环境中㊂将编写好的控制程序导入到工程中,运行双目摄像头工程后运行结果如图7所示㊂通过手动旋转O V 5642摄像头调整焦距使得图像清晰,摄像头采集到的图像由P L 端预处理后存入D D R ,再经过P S 端处理后由H D M I 接口将图像传输至显示器㊂图像分辨率为1920ˑ1080,画面清晰稳定,满足实验需求,在O S D 模块中设置两幅图像呈对角线重叠显示,背景为蓝色㊂图8为单/双目相机硬件资源占用率㊂从统计数据中可以明显看出,双目相机系统的F P G A部分各种硬件资源中除了时钟网络(B U F G )和时钟控制器(MM C M ),其他硬件资源占用率明显高于单目摄像头㊂查找表(L U T )可看作是一个有4位地址线的R A M ,V i v a d o 根据系统原理图和V H D L 硬件语言描述的逻辑电路自动计算所有结果[11],并把真值表写入L U T ,作用是对每一个输入信号的逻辑运算进行地址查找,并将对应内容输出㊂可以看出双目系统比单目系统的查找表数量高出近80%㊂图7双目摄像头实验结果图8 单/双目相机硬件资源占用率P S 和P L 通过B R A M (B l o c k R a n d o m A c c e s s M e m o r y)进行数据交互,在Z y n q 7000中通过P S 端的M a s t e r G P 0端口向B R A M 写数据,在V i v a d o 开发环境下打开单目和双目系统工程图,单击P S 端的M _A X I _G P 0端口会显示出黄色的连接线,单目系统的M _A X I _G P 0端口连接两个A x i_v d m a ,双目相机系统连接4个A x i _v d m a ㊂经过软件模拟计算,双目相机系统的B R AM 功耗大约是单目相机系统的1.5倍㊂单/双目相机系统的P L 端都配置了F C L K _C L K 0㊁F C L K _C L K 1㊁F C L K _C L K 2时钟,因此功耗相同㊂图9为图9 系统硬件资源功耗图双目相机系统在正常运行中硬件的功耗图㊂系统在运行时的功耗为2W 左右,系统在保证高效运行的同时,也实现了低功耗㊂结 语本文针对公安视频侦察工作的需要,设计了一套双目相机硬件系统,此系统通过O V 5642双目摄像头和基于Z y n q 7000架构的A X 7010开发板可实现对图像的采集㊁预处理㊁传输㊁显示功能,显示出来的图像为两个独立摄像头的画面㊂系统基于软硬件协同开发,可基于本文的硬件系统进一步进行软件开发㊂与传统监控相机相比,本文的双目相机可进行后期图像处理,根据图像算法实现深度图像获取,且相机体积更小,功耗更低,具有良好的实时性,符合未来公安视频侦察工作的发展需求㊂参考文献[1]肖政宏,韩秋凤,朱丽群.基于A R M 和D S P 的远程视频监控系统的设计与实现[J ].计算机工程与科学,2006,28(9):5355.[2]何雯,董威,苟辉.基于F P G A 的高速视频采集系统的设计[J ].国外电子测量技术,2016,35(5):8387.[3]孙迎萍,方群.基于D S P 和F P G A 的智能信号源设计[J ].科学技术与工程,2012,12(7):15041507.[4]刘文,冯燕,王巍.基于P C I 的D S P +F P G A 数字信号处理平台[J ].科学技术与工程,2008,8(9):23482351,2355.[5]S i l v a J ,S k l y a r o v V ,S k l i a r o v a I .C o m p a r i s o n o f o n c h i pc o m m u -n i c a t i o n s i n Z y n q 7000a l l p r o g r a m m a b l e s y s t e m s o n c h i p [J ].I E E E E m b ed de d S ys t e m s L e t t e r s ,2015,7(1):3134.[6]李宇成,黄堂猛.基于S 5P V 210的1080P 网络摄像头设计[J ].计算机工程与设计,2014,35(11):38133819.[7]K UM B HA R E P ,K R I S HN A V.D e s i g n i n g h i gh p e r f o r m -a n c e v i d e o s y s t e m s i n 7S e r i e s F P G A s w i t h t h e A X I i n t e r c o n -n e c t [J ].A p pl i c a t i o n N o t e ,2012(7):124.[8]林森,殷新勇,唐延东.双目视觉立体匹配技术研究现状和展望[J ].科学技术与工程,2017,17(30):135147.[9]李昂,刘鹏,王晓曼.基于Z y n q 7000的海雾图像嵌入式系统设计[J ].信息通信,2017(10):5961.[10]S a f a e i A ,W u Q M J .A s y s t e m l e v e l d e s i g n f o r f o r e gr o u n d a n d b a c k gr o u n d i d e n t i f i c a t i o n i n 3d s c e n e s [C ]//C i r c u i t s a n d S y s t e m s (I S C A S ),2016I E E E I n t e r n a t i o n a l S y m po s i u m o n .I E E E ,2016:25712574.[11]宦海,卢松,张雨,等.基于F P G A 的激光自混合干涉信号高速数据处理系统设计[J ].科学技术与工程,2016,16(3):188191,206.周禹辰(硕士研究生),主要研究方向为嵌入式系统与图像处理;卜凡亮(教授),主要研究方向为计算机控制与信息处理㊂(责任编辑:薛士然 收稿日期:2018-09-17)。

基于Zynq-7000平台的宽带卫星终端设计

基于Zynq-7000平台的宽带卫星终端设计蒋振东;陈崇森;贺翔【摘要】介绍基于XILINX Zynq-7000平台的高速卫星终端的硬件设计方案,并根据终端的设计指标要求,结合Zynq-7000平台SoC的特性,设计终端整体软件架构.高速宽带卫星终端的低功耗及小型化设计需求,对硬件平台的选型及设计提出更高的要求.合理的软件架构设计为实现宽带卫星终端的功能及性能指标,向客户提供使用方便、稳定可靠的高性能终端至关重要.该技术方案已应用到某卫星终端研制,满足终端的低功耗及小型化设计需求,实际测试能够实现组网高速通信,对同类型的卫星终端设计具有借鉴意义.【期刊名称】《现代计算机(专业版)》【年(卷),期】2019(000)012【总页数】3页(P98-100)【关键词】Zynq-7000;SoC;卫星终端;小型化【作者】蒋振东;陈崇森;贺翔【作者单位】广州海格通信集团股份有限公司,广州 510663;广州海格通信集团股份有限公司,广州 510663;广州海格通信集团股份有限公司,广州 510663【正文语种】中文0 引言Zynq-7000 是XILINX 公司推出的全可编程SoC片上系统平台,广泛应用到航空航天、汽车、工业自动化、医疗、通信等产品领域。

Zynq-7000 系列芯片内含双核ARM Cotex-A9 硬核以及不同容量的FPGA 资源,外设接口丰富,实现的功耗及性能等级远超分立搭建的CPU+FPGA 平台,Zynq-7000 内部双核ARM 采用AXI 总线与FPGA 部分连接,可实现Gbit 级别以上的高速通信,为宽带卫星终端的研制提供了完美的解决方案。

通过移植Linux 操作系统到Zynq-7000 平台,完成基于纯IP 设计思路的卫星终端软件架构设计。

基于Zynq-7000 平台的硬件方案及软件架构设计成为高性能卫星终端研制的关键环节。

1 Zynq-7000的特性及芯片选型Zynq-7000 的特点[1]如下:(1)处理系统(PS)采用ARM Cortex-A9 双核处理器,实现更佳性能功耗比,支持单精度和双精度浮点,运行速率高达1GHz。

基于ZYNQ7000的低功耗软件无线电平台设计

基于ZYNQ7000的低功耗软件无线电平台设计作者:尹志伟程亮亮来源:《无线互联科技》2018年第03期摘要:文章针对专用无线通信系统中低功耗的应用需求,给出一种新的软件无线电处理平台的硬件设计方案。

该平台满足软件无线电的设计要求,采用Ⅺlinx公司的ZYNQ7000架构处理器,通过外设器件型号优选,实现具有高性能、功耗较低的软件定义无线电硬件平台,且已在工程项目中成功应用。

关键词:无线通信;软件无线电平台;低功耗:ZYNQ7000传统的软件无线电处理平台一般采用GPP+DSP+FPGA的通用架构,3种异构处理器分别实现不同的功能,如图1所示。

其中ARM负责主控功能,实现平台的中心控制、有线接口协议、无线通信协议等;DSP 为波形物理层的核心,实现波形接入控制、基带信号的编解码、交织解交织、调制解调等;FPGA主要负责信号的上下变频、窄带译码等功能[1]。

传统的多芯片架构存在问题:单板功耗高,布板面积大。

而目前无论是军事应用还是民用专业电台应用,均对小型化、低功耗的需求日趋强烈,与此同时,随着应用软件对硬件平台的处理性能的不断提高,高性能与小体积、低功耗已经成为处理平台的基本要求,而传统的数字硬件平台设计方式越来越难以满足这一需求[2]。

本文给出了一种基于ZYNQ7000架构SoC的软件无线电处理平台设计方案,并分析和论证了低功耗设计的思路。

1 硬件架构设计SoC目前是处理器发展的趋势,ZYNQ7000是Xilinx公司发布的双ARM内核+FPGA架构的SoC。

该系列芯片采用28 nm工艺,具有高性能、低功耗等优点,而且该系列芯片具有不同处理性能型号,可满足不同类型的产品需求。

其中,部分型号具有可兼容封装,可以在不更改电路设计的情况下实现产品硬件的升级。

我们选用ZYNQ7000作为新一代数字平台的核心处理器。

基于ZYNQ7000的平台基本架构如图2所示。

图2基于ZYNQ7000的数字平台架构ZYNQ7000的ARM核负责主控、接入等功能,FPGA负责物理层,ARM与FPGA之间的图中配合ZYNQ7000的是高集成度的收发芯片,该类芯片具有ADC,DAC,混频、滤波、增益控制等功能,便于降低平台的功耗和布板尺寸。

基于Zynq7000高清视频采集处理系统Linux移植与应用程序设计

2、系统实现

(1)硬件实现

本系统的硬件平台采用Xilinx Zynq-7000开发板,以ZYNQ-7000为核心,连 接摄像头、SD卡、网口等外部设备进行系统搭建。其中,摄像头通过CAMIF接口 与FPGA相连,实现图像采集;SD卡通过SDIO接口与ARM Cortex-A9处理器相连, 实现数据存储;网口通过EMAC接口与FPGA相连,实现千兆以太网传输。

Zynq7000是Xilinx公司推出的一款基于ARM Cortex-A9内核的FPGA芯片。它 具有高度的可编程性和灵活性,同时集成了丰富的外围设备和高性能的内部资源。 在数字图像处理方面,Zynq7000具有PS和PL可编程性,用户可以通过编程来实现 各种数字图像处理算法,同时其DDR3存储器可以提供快速的数据存储和读取。

移植过程

在Zynq7000高清视频采集处理系统上移植Linux操作系统主要包括以下几个 步骤:

1、获取Linux内核源码并修改配置:根据硬件平台的需求,修改Linux内核 源码的配置文件,以支持Zynq7000硬件平台的特性和需求。

2、编译内核:使用交叉编译器编译修改后的Linux内核源码,生成可在 Zynq7000上运行的Linux内核映像文件。

Zynq7000是Xilinx公司推出的一款基于ARM Cortex-A9架构的FPGA处理器, 它同时集成了高性能的DSP和FPGA可编程逻辑单元,可以满足各种复杂算法的运 行需求。Zynq7000具有高速的DDR内存接口,可以大大提升数据处理速度,此外, 其内置的DMA引擎和高速串行接口也可以满足各种数据传输需求。

2)本系统的架构设计合理,能够满足图像采集处理的实时性要求。

3)本系统的软件实现采用了驱动程序、图像处理算法程序和应用程序三个 层次的结构,具有可维护性和可扩展性强的特点。

基于FPGA ZYNQ7000的高帧频智能目标检测系统的设计方案

基于FPGA ZYNQ7000的高帧频智能目标检测系统的设计方案基于机器视觉的智能目标检测系统应用非常广泛,尤其在航天军工等领域中,经常涉及高速目标的实时检测和控制,对目标检测的智能性和实时性提出了更严格的要求。

在这种应用中,视觉系统相对雷达、声纳具有信息量大、抗干扰能力强、软件处理灵活、体积重量小、成本低等特点,但缺点是传输和处理需要的时间更多,因此很难满足图像信息传输和处理的实时性要求。

高速相机一般通过GigE、CameraLink、USB3.0等接口将图像采集后传输到图像处理器上,这种方式把大量时间消耗到信息传输通道。

为了解决这个问题,最好的方式是直接在近端对传感器芯片采集的图像进行处理。

FPGA凭借其硬件并行运算的优势,越来越多地应用于高速相机以及高速运动检测系统中,极大地提高了图像处理速度,保证了系统的高速、实时性与准确性。

通过FPGA对图像传感器进行近端处理,可以做到采集图像与智能处理同步进行。

其最需要解决的问题是优化智能算法,使得运算更加简单高效,并占用更少的资源。

目前很多学者正致力于高速视觉目标检测系统的研究。

GUQY等人设计了2000f/s的高速智能相机,可以对目标进行智能实时监测。

后又设计了高帧频视频拼接系统,该系统运用了改进的基于特征的视频拼接算法,能够实时合成全景图像,帧率可达500f/s。

麻省理工大学的CHENJG等人通过高速摄像机(5000f/s)对悬臂梁上的目标物体进行位移测量实验,通过PC对数据进行离线分析,得到了与激光测振仪和加速度计测量相一致的振动曲线。

并且通过FFT算法对三组数据进行频域分析,得出了各个共振频率分量。

本文以高帧频与实时性作为研究的切入点,设计了一种基于ZYNQ7000的高速相机平台,充分利用芯片上的FPGA资源及其硬件并行的优势,进行目标提取及质心检测算法的实现。

本文优化了目标检测的FPGA算法,去掉中间缓存环节,以流水线结构对图像数据进行实时流水处理,提高了目标检测算法的处理效率,可以在每帧图像采集后的有限个时钟周期内完成位置检测运算,做到同步检测。

【学习笔记】基于Zynq-7000的宽幅视频处理系统设计与实现

【学习笔记】基于Zynq-7000的宽幅视频处理系统设计与实现2016年电子技术应用第6期作者:韩德强,杨利平,王宗侠摘要:针对安防监控与智慧交通领域无盲区视频摄录的需求,基于Zynq-7000平台优势进行宽幅视频处理软硬件系统的设计。

通过研究基于嵌入式系统的多路视频实时拼接技术,设计并实现了以XC7Z020芯片为核心的视频处理板卡,在双核ARM Cotex-A9硬核处理器端服务程序协同调度下,基于片内FPGA硬件加速能力实现多通道视频实时采集与预处理、投影变换、图像融合,进而形成完整宽幅视频画面,通过远程客户端实现定制化的视频摄录功能。

测试结果表明,该系统是兼具稳定的性能和灵活区域部署能力的便携式解决方案。

0 引言宽幅视频拼接是基于计算机视觉和图形处理技术的整合,其本质就是图像拼接技术,必然与图像传感器技术及图像算法研究密切相关[1],但其对于实时性的较高要求,使得在该领域的技术实践同样需要关注平台的处理性能。

目前市面上普遍采用的主要有通过单目鱼眼镜头捕获全景图像的嵌入式平台方案,以及多通道图像采集拼接形成全景的通用计算机平台方案。

前者对于镜头工艺要求高且存在较大的畸变,而后者凭借性能优势获得好的效果,但设备体积庞大且价格昂贵[2]。

针对以上情况,本文提出了一种基于AP SoC(All Programmable System on Chip,全可编程的片上系统)多通道视频无缝拼接的宽幅视频处理解决方案。

结合用户场景分析,提出具有扩展能力的宽幅视频处理技术,预置多路扩展接口随时增减摄像头以调整视野宽度,满足多种现场宽视角摄录需求。

1 系统总体构架宽幅视频处理系统由本地视频处理系统端和远程摄录客户端两部分组成,系统总体框图如图1所示。

便携式视频处理系统根据监控需求进行配置与部署,远程客户端进行实时定制视野区域摄录。

本地视频处理系统作为设计的主体部分,由视频采集、图像处理、核心调度、用户交互、本地显示、网络通信六个模块组成。

基于Zynq-7000的SRIO高速数据传输设计与实现

基于Zynq-7000的SRIO高速数据传输设计与实现杜金艳;叶旭鸣【期刊名称】《电子设计工程》【年(卷),期】2017(025)024【摘要】为了满足Zynq-7000系列芯片的SRIO数据传输要求,提出了一种基于FPGA控制DMA传输进行SRIO通信的设计方案,并完成了ARM与FPGA核间高吞吐率的数据交互操作.系统的FPGA部分主要用来控制DMA的数据传输和SRIO 事务处理,ARM只进行简单的参数设置,能够完成SRIO各种事务类型的传输.实际应用表明,该系统具有操作简便、高效的特点,同时减轻了CPU的负担,达到了预期效果.%In order to meet the requirements of SRIO data transmission of Zynq-7000 spectrum,a design scheme of SRIO Communication based on the FPGA control of DMA transmidtion is proposed,and the a hign band-width communication between ARM and FPGA core is implemented.The FPGA part of the system is mainly used to control the data transmission of DMA and SRIO transaction processing.ARM only for simple parameter settings,complete the transmission of various types of transaction SRIO.real application shows that the system has the characteristic of simple operation and high efficiency,at the same time release the main CPU,The proposed method achieves the expected effect.【总页数】4页(P30-33)【作者】杜金艳;叶旭鸣【作者单位】天津津航计算技术研究所天津300308;天津津航计算技术研究所天津300308【正文语种】中文【中图分类】TN79+1【相关文献】1.基于高速串行总线SRIO的数据传输 [J], 王磊;王辉球2.多核DSP间基于SRIO数据传输的设计与实现 [J], 魏智伟3.基于国产FPGA的高速SRIO接口设计与实现 [J], 于东英;陈俊;康令州4.基于W5300的高速数据传输系统设计与实现 [J], 杜志美; 文丰; 张凯华5.基于ZYNQ-7000 DMA控制器的UART数据传输的设计与实现 [J], 夏柯;门兰宁因版权原因,仅展示原文概要,查看原文内容请购买。

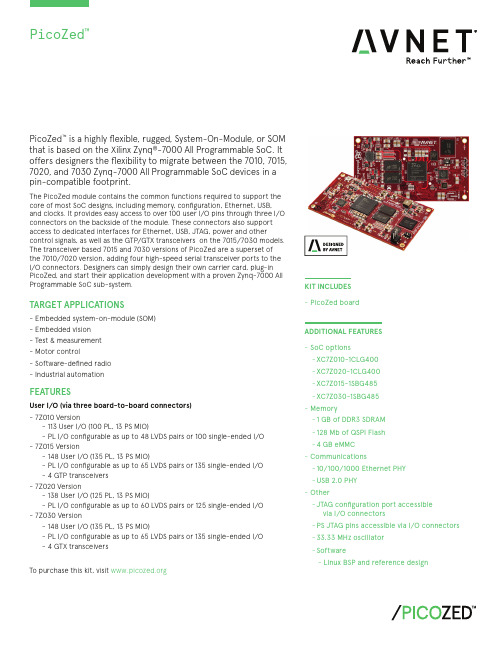

PicoZed 基于Xilinx Zynq-7000 All Programmable SoC的Sy

KIT INCLUDES -PicoZed boardADDITIONAL FEATURES -SoC options -XC7Z010-1CLG400 -XC7Z020-1CLG400 -XC7Z015-1SBG485 -XC7Z030-1SBG485 -Memory-1 GB of DDR3 SDRAM -128 Mb of QSPI Flash -4 GB eMMC -Communications-10/100/1000 Ethernet PHY -USB 2.0 PHY -Other-JTAG confi guration port accessiblevia I/O connectors -PS JTAG pins accessible via I/O connectors -33.33 MHz oscillator -Software-Linux BSP and reference designPicoZed ™ is a highly fl exible, rugged, System-On-Module, or SOM that is based on the Xilinx Zynq ®-7000 All Programmable SoC. It offers designers the fl exibility to migrate between the 7010, 7015, 7020, and 7030 Zynq-7000 All Programmable SoC devices in a pin-compatible footprint.The PicoZed module contains the common functions required to support the core of most SoC designs, including memory, confi guration, Ethernet, USB, and clocks. It provides easy access to over 100 user I/O pins through three I/O connectors on the backside of the module. These connectors also support access to dedicated interfaces for Ethernet, USB, JTAG, power and othercontrol signals, as well as the GTP/GTX transceivers on the 7015/7030 models. The transceiver based 7015 and 7030 versions of PicoZed are a superset of the 7010/7020 version, adding four high-speed serial transceiver ports to the I/O connectors. Designers can simply design their own carrier card, plug-in PicoZed, and start their application development with a proven Zynq-7000 All Programmable SoC sub-system.TARGET APPLICATIONS-Embedded system-on-module (SOM) -Embedded vision -Test & measurement -Motor control-Software-defi ned radio -Industrial automationFEATURESUser I/O (via three board-to-board connectors)-7Z010 Version-113 User I/O (100 PL, 13 PS MIO) -PL I/O confi gurable as up to 48 LVDS pairs or 100 single-ended I/O -7Z015 Version-148 User I/O (135 PL, 13 PS MIO) -PL I/O confi gurable as up to 65 LVDS pairs or 135 single-ended I/O -4 GTP transceivers -7Z020 Version-138 User I/O (125 PL, 13 PS MIO) -PL I/O confi gurable as up to 60 LVDS pairs or 125 single-ended I/O -7Z030 Version-148 User I/O (135 PL, 13 PS MIO) -PL I/O confi gurable as up to 65 LVDS pairs or 135 single-ended I/O -4 GTX transceivers To purchase this kit, visitPicoZed™BLOCK DIAGRAMCopyright © 2017 Avnet, Inc. AVNET, "Reach Further," and the AV logo are registered trademarks of Avnet, Inc. All other brands are the property of their respective owners.LIT# 5048-PB-PDP-AES-Z7PZ-SOM-G-V1FEATURED MANUFACTURERS*Contact your local Avnet sales office for pricing on higher quantitiesCONTACTINFORMATIONNorth America 2211 S 47th StreetPhoenix, Arizona 85034United States of America *******************1-800-585-1602EuropeGruber Str. 60c 85586 Poing Germany********************+49-8121-77702Europe (EBV)Im Technologiepark 2-885586 Poing Germany/contactJapanYebisu Garden Place Tower, 23F 4-20-3 Ebisu, Shibuya-ku Tokyo 150-6023 Japan **********************+81-(0)3-5792-8210Asia151 Lorong Chuan,#06-03 New Tech Park Singapore 556741*********************+65-6580-6000。

基于Zynq-7000的高速实时自适应均衡器设计

基于Zynq-7000的高速实时自适应均衡器设计

何宗苗;姚远程;秦明伟

【期刊名称】《电视技术》

【年(卷),期】2014(38)15

【摘要】设计了一种基于Zynq-7000芯片的高速实时自适应均衡系统,该系统采用GAL-NLMS算法.芯片的PL部分实现了35阶的GAL算法模块和AXI-StreamP设计,PS实现了基于Linux的驱动程序设计,基于Qt的应用程序设计和NLMS算法模块,并详细介绍了系统的开发流程.PL与PS内部通信速率达到了5.32 Gbit/s,外部最高输入速率达到175 Mbit/s,误差百分比小于3%.对当前和今后的高速通信具有很强的实用价值.

【总页数】5页(P88-91,97)

【作者】何宗苗;姚远程;秦明伟

【作者单位】西南科技大学信息工程学院特殊环境机器人技术四川省重点实验室,四川绵阳621010;西南科技大学信息工程学院特殊环境机器人技术四川省重点实验室,四川绵阳621010;西南科技大学信息工程学院特殊环境机器人技术四川省重点实验室,四川绵阳621010

【正文语种】中文

【中图分类】TN911.7

【相关文献】

1.基于Zynq-7000高速图像采集与实时处理系统 [J], 杨晓安;罗杰;苏豪;包文博

2.基于Zynq-7000的SRIO高速数据传输设计与实现 [J], 杜金艳;叶旭鸣

3.基于FPGA+DSP的高速视频实时处理系统设计 [J], 张小永

4.基于Zynq-7000的实时视频图像处理系统框架设计 [J], 张祖昊;王云光

5.基于Zynq-7000的实时视频图像处理系统框架设计 [J], 张祖昊;王云光

因版权原因,仅展示原文概要,查看原文内容请购买。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

犇犲狊犻犵狀狅犳犪犛犅犪狀犱犝犛犅犜狉犪狀狊狆狅狀犱犲狉犅犪狊犲犱狅狀犣犢犖犙7000

ZhangYan,MaJinxin,YeLei,GuJiaquan

(ShanghaiInstituteofSpaceElectronicTechnology,Shanghai 201109,China) 犃犫狊狋狉犪犮狋:ThepurposeofthearticleistodesignasmallS-bandUSBtransponderonthebasisofZYNQtoreducethesizeofthe transponderandruducethepowerconsumptionofthetransponder;ThispaperfirstlyintroducestheadvantageofZYNQ,andputs forwardthedesignschemeofastandardUSBtransponderbasedonZYNQ7000,anddiscussesthekeytechnologyandtheprincipleof modulationanddemodulationofthetransponder.Theworkingprocessofthetransponderisasfollows:whenthesateliteentersthe on-orbitflightstage,thetransponderreceivestheuplinkremotecontrolsubcarriersignaltransmittedfromtheground monitoring station,andafterdemodulation,transmitstheremotecontrolPCMsreamtotherelevantequipmentthroughtheinterfacewithother satellitesubsystems;thetransponderreceivestheuplinkrangingsignaltransmittedfromthegroundmonitoringstation,theranging basebandsignalistransmittedtothegroundafterlocalfrequencyupconversion;thePCMremotedataisreceivedthroughtheUART serialport,andthemodulatedtelemetrydataissenttothegroundstationthroughthetelemetrysubcarrier;theinternaltelemetry informationissenttoothersubsystemsthroughtheserialport.Thatis,thetransponderhasthefunctionsoftransmitdistance、de modulateremotecontrolcommandsandtransmittelemetrysubcarrierinnonspreadspectrum mode;Thetransponder’supconver sionpartanddownconversionpartusetheintegratedchip,tosimplifythecircuit.TheuseoftheZYNQ andtheintegratedchip greatlyreducedthevolumeofthetransponderandruducethepowerconsumptionofthetransponder. 犓犲狔狑狅狉犱狊:ZYNQ;USB;transponder

智能仪器与传感技术

计 算 机 测 量 与 控 制 .2019.27(1) 犆狅犿狆狌狋犲狉 犕犲犪狊狌狉犲犿犲狀狋 牔 犆狅狀狋狉狅犾

· 275 ·

文章编号:1671 4598(2019)01 0275 05 DOI:10.16526/j.cnki.11-4762/tp.2019.01.058 中图分类号:TN927 文献标识码:A

基于犣犢犖犙7000的犛波段 犝犛犅 应答机设计

张 焱,马金鑫,叶 雷,顾家全

(上 海 航 天 电 子 技 术 研 究 所 , 上 海 201109)

摘 要 :文 章 目 的 在 于 在 ZYNQ7000的 基 础 上 设 计 一 款 小 型 的 S 波 段 USB 应 答 机 , 以 缩 小 应 答 机 的 体 积 , 降 低 应 答 机 的 功 耗 ; 文 章 首 先 对 于 ZYNQ 的 优 势 做 了 简 单 的 介 绍 ,并 基 于 ZYNQ7000提 出 了 USB 应 答 机 的 设 计 方 案 ,论 述 了 调 制 、解 调 中 的 关 键技术和工作原理;应答机工作过程如下:卫星进入在轨飞行段时,应答机接收地面测控站发射的上行遥控副载波信号,解调后 将 遥 控 PCM 码 流 通 过 与 卫 星 其 他 分 系 统 接 口 发 送 至 相 关 设 备 ;接 收 地 面 测 控 站 发 射 的 上 行 测 距 信 号 , 将 变 频 后 的 测 距 基 带 信 号 进 行 本 地 上 变 频 后 对 地 发 送 ;通 过 UART 串 口 接 收 PCM 遥 测 数 据 , 将 调 制 后 的 遥 测 数 据 通 过 遥 测 副 载 波 发 送 至 地 面 站 ; 同 时 , 将内部的遥测信息通过串口发送至其它分系统;即该应答机在非扩频模式下具有测距、解调遥控指令和发射遥测副载波的功能; 应答 机 上 下 变 频 部 分 采 用 了 集 成 的 芯 片 ,将 电 路 进 行 了 简 化 ;ZYNQ 及 集 成 芯 片 的 使 用 都 大 大 地 缩 小 了 应 答 机 的 体 积 , 降 低 了 应 答机的功耗。