MIC3289-16YML中文资料

R928中文资料

PHOTOMULTlPLlER TUBESR928, R955Subject to local technical requirements and regulations, availability of products included in this promotional material may vary. Please consult with our sales office. lnformation furnished by HAMAMATSU is believed to be reliabIe. However, no responsibility is assumed for possibIe inaccuracies or ommissions. Specifications are subject to change without notice. No patent right are granted to any of the circuits described herein. © 1997 Hamamatsu Photonics K.K.PHOTOMULTlPLlER TUBES R928, R955 MAXIMUM RATINGS (Absolute Maximum Values)CHARACTERISTlCS (at 25SuppIy Voltage : 1000VdcK : Cathode, Dy : Dynode, P : AnodeJ:K:L:The electron transit time is the interval between the arrival of delta function light pulse at the entrance window of the tube and the time when the anode output reaches the peak amplitude. In measurement, the whole photo-cathode is illuminated.Also called transit time jitter. This is the fluctuation in electron transit time between individual pulses in the signal photoelectron mode, and may be defined as the FWHM of the frequency distribution of electron transit times.Hysteresis is temporary instability in anode current after light and voltage are applied.(1)Current HysteresisThe tube is operated at 750 volts with an anode current of 1 micro-ampere for 5 minutes. The light is then removed from the tube for a minute. The tube is then re-illuminated by the previous light level for a minute to measure the variation.(2)Voltage HysteresisThe tube is operated at 300 volts with an anode current of 0.1 micro-ampere for 5 minutes. The light is then removed from the tube and the supply voltage is quickly increased to 800 volts. After a minute, the supply voltage is then reduced to the previous value and the tube is re-illuminated for a minute to measure the variation.Hysteresis =100(%)l max.l il min.Figure 2: Anode Luminous Sensitivity and Gain CharacteristicsFigure 3: Typical Time ResponseFigure 4: Typical Temperature Coefficient of Anode SensitivityFigure 5: Typical Temperature Characteristic of Dark Current (at 1000V, after 30minute storage)TPMSB0002EATPMSB0003EBTIMEA N O D E 200300500700100010–2A N O D E L U M I N O U S S E N S I T I V I T Y (A /l m )1500G A I N10–1100101102103104102103104105106107108SUPPLY VOLTAGE (V)SUPPLY VOLTAGE (V)T I M E (n s )124681020406080100TPMSB0005EA–40–200+20TEMPERATURE (°C)1608020A N O D E S E N S I T I V I T Y (%)140100+401206040TPMSB0006EA–40–200+20TEMPERATURE (°C)10010.01A N O D E D A R K C U R R E N T (n A )+40100.1PHOTOMULTlPLlER TUBES R928, R955TPMS1001E06MAY. 1997Figure 6: Dimensional Outline and Basing Diagram (Unit : mm)Figure 7: Optional Accessories (Unit : mm)TPMSA0008EADIRECTION OF LIGHTBOTTOM VIEW (BASING DIAGRAM)TACCA0064EASocketD Type Socket Assembly E717-21Warning–Personal Safety HazardsElectrical Shock–Operating voltages applied to thisdevice present a shock hazard.Hamamatsu also provides C4900 series compact high voltage power sup-plies and C6270 series DP type socket assemblies which incorporate a DC to DC converter type high voltage power supply.(E678 – 11A)TACCA0002ED: 330k: 0.01 F SOCKET HAMAMATSU PHOTONICS K.K., Electoron Tube Center314-5, Shimokanzo, Toyooka-village, Iwata-gun, Shizuoka-ken, 438-0193, Japan, Telephone: (81)539/62-5248, Fax: (81)539/62-2205U.S.A.: Hamamatsu Corporation: 360 Foothill Road, Bridgewater. N.J. 08807-0910, U.S.A., Telephone: (1)908-231-0960, Fax: (1)908-231-1218Germany: Hamamatsu Photonics Deutschland GmbH: Arzbergerstr. 10, D-82211 Herrsching am Ammersee, Germany, Telephone: (49)8152-375-0, Fax: (49)8152-2658France: Hamamatsu Photonics France S.A.R.L.: 8, Rue du Saule Trapu, Parc du Moulin de Massy, 91882 Massy Cedex, France, Telephone: (33)1 69 53 71 00, Fax: (33)1 69 53 71 10United Kingdom: Hamamatsu Photonics UK Limted: Lough Point, 2 Gladbeck Way, Windmill Hill, Enfield, Middlesex EN2 7JA, United Kingdom, Telephone: (44)181-367-3560, Fax: (44)181-367-6384North Europe: Hamamatsu Photonics Norden AB: Färögatan 7, S-164-40 Kista Sweden, Telephone: (46)8-703-29-50, Fax: (46)8-750-58-95Italy: Hamamatsu Photonics Italia: S.R.L.: Via Della Moia, 1/E, 20020 Arese, (Milano), Italy, Telephone: (39)2-935 81 733, Fax: (39)2-935 81 741Hybrid Assembly of R928H957-08The H957-08 integrates on R928, a voltage-divider circuit, and a high voltage power supply into a compact magnetic shield case. It can be readily operated by input of 15Vdc.。

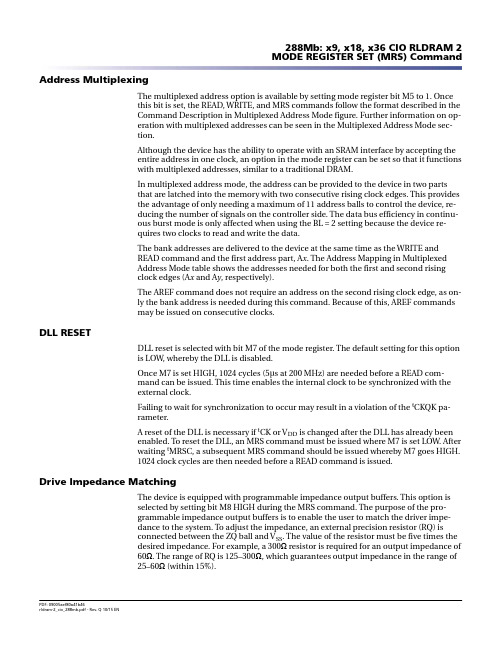

MX28F160C3T资料

MX28F160C3T/B16M-BIT [1M x16] CMOS SINGLE VOLTAGE3V ONLY FLASH MEMORY- Word write suspend to read- Sector erase suspend to word write- Sector erase suspend to read register report•Automatic sector erase, word write and sector lock/unlock configuration •Status Reply- Detection of program and erase operation comple-tion.- Command User Interface (CUI)- Status Register (SR)•Data Protection Performance- Include boot sectors and parameter and main sectors to be locked/unlocked•100,000 minimum erase/program cycles •Common Flash Interface (CFI)•128-bit Protection Register- 64-bit Unique Device Identifier - 64-bit User-Programmable•Latch-up protected to 100mA from -1V to VCC+1V •Package type:- 48-pin TSOP (12mm x 20mm)- 48-ball CSP (8mm x 6mm)FEATURES•Bit Organization: 1,048,576 x 16•Single power supply operation- VCC=VCCQ=2.7~3.6V for read, erase and program operation- VPP=12V for fast production programming - Operating temperature:-40°C~85°C •Fast access time : 70/90/110ns •Low power consumption- 9mA typical active read current, f=5MHz- 18mA typical program current (VPP=1.65~3.6V)- 21mA typical erase current (VPP=1.65~3.6V)- 7uA typical standby current under power saving mode•Sector architecture- Sector structure : 4Kword x 2 (boot sectors), 4Kword x 6 (parameter sectors), 32Kword x 31 (main sectors)- Top/Bottom Boot•Auto Erase and Auto Program- Automatically program and verify data at specified address- Auto sector erase at specified sector •Automatic Suspend EnhanceGENERAL DESCRIPTIONThe MX28F160C3T/B is a 16-mega bit Flash memory organized as 1M words of 16 bits. The 1M word of data is arranged in eight 4Kword boot and parameter sectors,and thirty-one 32K word main sectors which are indi-vidually erasable. MXIC's Flash memories offer the most cost-effective and reliable read/write non-volatile random access memory. The MX28F160C3T/B is packaged in 48-pin TSOP and 48-ball CSP . It is designed to be re-programmed and erased in system or in standard EPROM programmers.fast as 70ns, allowing operation of high-speed micropro-cessors without wait states.MXIC's Flash memories augment EPROM functionality with in-circuit electrical erasure and programming. The MX28F160C3T/B uses a command register to manage this functionality. The command register allows for 100%TTL level control inputs and fixed power supply levels during erase and programming, while maintaining maxi-mum EPROM compatibility.MXIC Flash technology reliably stores memory contents even after 100,000 erase and program cycles. The MXICMX28F160C3T/Bmechanisms. In addition, the combination of advanced tunnel oxide processing and low internal electric fields for erase and program operations produces reliable cy-cling. The MX28F160C3T/B uses a 2.7V~3.6V VCC sup-ply to perform the High Reliability Erase and auto Pro-gram/Erase algorithms.The highest degree of latch-up protection is achieved with MXIC's proprietary non-epi process. Latch-up pro-tection is proved for stresses up to 100 milliamps on address and data pin from -1V to VCC + 1V.The dedicated VPP pin gives complete data protection when VPP< VPPLK.A Command User Interface (CUI) serves as the inter-face between the system processor and internal opera-tion of the device. A valid command sequence written to the CUI initiates device automation. An internal Write State Machine (WSM) automatically executes the algo-rithms and timings necessary for erase, word write and sector lock/unlock configuration operations.A sector erase operation erases one of the device's 32K-word sectors typically within 1.0s, 4K-word sectors typi-cally within 0.5s independent of other sectors. Each sec-tor can be independently erased minimum 100,000 times. Sector erase suspend mode allows system software to suspend sector erase to read or write data from any other sector.Writing memory data is performed in word increments of the device's 32K-word sectors typically within 0.8s and 4K-word sectors typically within 0.1s. Word program sus-pend mode enables the system to read data or execute code from any other memory array location.MX28F160C3T/B features with individual sectors lock-ing by using a combination of bits thirty-nine sector lock-bits and WP, to lock and unlock sectors.The status register indicates when the WSM's sector erase, word program or lock configuration operation is done.The access time is 70/90/110ns (tELQV) over the oper-ating temperature range (-40°C to +85°C) and VCC sup-ply voltage range of 2.7V~3.6V.MX28F160C3T/B's power saving mode feature substan-tially reduces active current when the device is in static mode (addresses not switching). In this mode, the typi-cal ICCS current is 7uA (CMOS) at 3.0V VCC.As CE and RP are at VCC, ICC CMOS standby mode is enabled. When RP is at GND, the reset mode is enabled which minimize power consumption and provide data write protection.A reset time (tPHQV) is required from RP switching high until outputs are valid. Similarly, the device has a wake time (tPHEL) from RP-high until writes to the CUI are recognized. With RP at GND, the WSM is reset and the status register is cleared.MX28F160C3T/BMX28F160C3T/BMX28F160C3T/BTable 1. Pin DescriptionSymbol Type Description and FunctionA0-A19input Address inputs for memory address. Data pin float to high-impedance when the chip isdeselected or outputs are disable. Addresses are internally latched during a write orerase cycle.DQ0-DQ15input/output Data inputs/outputs: Inputs array data on the second CE and WE cycle during a pro-gram command. Data is internally latched. Outputs array and configuration data. Thedata pin float to tri-state when the chip is de-selected.CE input Chip Enable : Activates the device's control logic, input buffers, and sense amplifiers.CE high de-selects the memory device and reduce power consumption to standbylevel. CE is active low.RP input Reset/Deep Power Down: when RP=VIL, the device is in reset/deep power down mode,which drives the outputs to High Z, resets the WSM and minimizes current level.When RP=VIH, the device is normal operation. When RP transitions from VIL to VIH,the device defaults to the read array mode.WE input Write Enable: to control write to CUI and array sector. WE=VIL becomes active. Thedata and addresses are latched on the rising edge of the second WE pulse.VPP input/supply Program/Erase Power Supply:(1.65V~3.6V or 11.4V~12.6V)Lower VPP<VPPLK, to protect any contents against Program and Erase Command.Set VPP=VCC for in-system Read, Program and Erase Operation.Raise VPP to 12V±5% for faster program and erase in a production environment.OE input Output enable: gates the device's outputs during a real cycle.WP input Write Protect: When WP is VIL, the sectors marked Lock Down can't be unlockedthrough software. When WP is VIH, the lock down mechanism is disable and sectorspreviously locked down are now locked and can be unlocked and locked through soft-ware. After WP goes low, any sectors previously marked lock down revert to that state. VCC supply Device power supply: (2.7V~3.6V).VCCQ input I/O Power Supply: supplies for input/output buffers. (VCCQ must be tied to VCC) GND supply Ground voltage: all the GND pin shall not be connected.MX28F160C3T/BSECTOR STRUCTURE (TOP)Sector Sector Size Address Range (h)Boot Sector 04K Word FF000 ~ FFFFFBoot Sector 14K Word FE000 ~ FEFFFParameter Sector 04K Word FD000 ~ FDFFFParameter Sector 14K Word FC000 ~ FCFFFParameter Sector 24K Word FB000 ~ FBFFFParameter Sector 34K Word FA000 ~ FAFFFParameter Sector 44K Word F9000 ~ F9FFFParameter Sector 54K Word F8000 ~ F8FFFMain Sector 032K Word F0000 ~ F7FFFMain Sector 132K Word E8000 ~ EFFFFMain Sector 232K Word E0000 ~ E7FFFMain Sector 332K Word D8000 ~ DFFFFMain Sector 432K Word D0000 ~ D7FFFMain Sector 532K Word C8000 ~ CFFFFMain Sector 632K Word C0000 ~ C7FFFMain Sector 732K Word B8000 ~ BFFFFMain Sector 832K Word B0000 ~ B7FFFMain Sector 932K Word A8000 ~ AFFFFMain Sector 1032K Word A0000 ~ A7FFFMain Sector 1132K Word98000 ~ 9FFFFMain Sector 1232K Word90000 ~ 97FFFMain Sector 1332K Word88000 ~ 8FFFFMain Sector 1432K Word80000 ~ 87FFFMain Sector 1532K Word78000 ~ 7FFFFMain Sector 1632K Word70000 ~ 77FFFMain Sector 1732K Word68000 ~ 6FFFFMain Sector 1832K Word60000 ~ 67FFFMain Sector 1932K Word58000 ~ 5FFFFMain Sector 2032K Word50000 ~ 57FFFMain Sector 2132K Word48000 ~ 4FFFFMain Sector 2232K Word40000 ~ 47FFFMain Sector 2332K Word38000 ~ 3FFFFMain Sector 2432K Word30000 ~ 37FFFMain Sector 2532K Word28000 ~ 2FFFFMain Sector 2632K Word20000 ~ 27FFFMain Sector 2732K Word18000 ~ 1FFFFMain Sector 2832K Word10000 ~ 17FFFMain Sector 2932K Word08000 ~ 0FFFFMX28F160C3T/BSECTOR STRUCTURE (BOTTOM)Sector Sector Size Address Range (h)Boot Sector 04K Word00000 ~ 00FFFBoot Sector 14K Word01000 ~ 01FFFParameter Sector 04K Word02000 ~ 02FFFParameter Sector 14K Word03000 ~ 03FFFParameter Sector 24K Word04000 ~ 04FFFParameter Sector 34K Word05000 ~ 05FFFParameter Sector 44K Word06000 ~ 06FFFParameter Sector 54K Word07000 ~ 07FFFMain Sector 032K Word08000 ~ 0FFFFMain Sector 132K Word10000 ~ 17FFFMain Sector 232K Word18000 ~ 1FFFFMain Sector 332K Word20000 ~ 27FFFMain Sector 432K Word28000 ~ 2FFFFMain Sector 532K Word30000 ~ 37FFFMain Sector 632K Word38000 ~ 3FFFFMain Sector 732K Word40000 ~ 47FFFMain Sector 832K Word48000 ~ 4FFFFMain Sector 932K Word50000 ~ 57FFFMain Sector 1032K Word58000 ~ 5FFFFMain Sector 1132K Word60000 ~ 67FFFMain Sector 1232K Word68000 ~ 6FFFFMain Sector 1332K Word70000 ~ 77FFFMain Sector 1432K Word78000 ~ 7FFFFMain Sector 1532K Word80000 ~ 87FFFMain Sector 1632K Word88000 ~ 8FFFFMain Sector 1732K Word90000 ~ 97FFFMain Sector 1832K Word98000 ~ 9FFFFMain Sector 1932K Word A0000 ~ A7FFFMain Sector 2032K Word A8000 ~ AFFFFMain Sector 2132K Word B0000 ~ B7FFFMain Sector 2232K Word B8000 ~ BFFFFMain Sector 2332K Word C0000 ~ C7FFFMain Sector 2432K Word C8000 ~ CFFFFMain Sector 2532K Word D0000 ~ D7FFFMain Sector 2632K Word D8000 ~ DFFFFMain Sector 2732K Word E0000 ~ E7FFFMain Sector 2832K Word E8000 ~ EFFFFMain Sector 2932K Word F0000 ~ F7FFFMX28F160C3T/B2 PRINCIPLES OF OPERATIONThe product includes an on-chip WSM to manage sec-tor erase, word write and lock-bit configuration functions.After initial device power-up or return from reset mode (see section on Bus Operations), the device defaults to read array mode. Manipulation of external memory con-trol pins allow array read, standby and output disable operations.Status register and identifier codes can be accessed through the CUI independent of the VPP voltage. All functions associated with altering memory contents -sector erase, word write, sector lock/unlock, status and identifier codes - are accessed via the CUI and verified through the status register.Commands are written using standard microprocessor write timings. The CUI contents serve as input to the WSM, which controls the sector erase, word write and sector lock/unlock. The internal algorithms are regulated by the WSM, including pulse repetition, internal verifica-tion and margining of data. Addresses and data are in-ternally latched during write cycles. Address is latched at falling edge of CE and data latched at rising edge of WE. Writing the appropriate command outputs array data, accesses the identifier codes or outputs status register data.Interface software that initiates and polls progress of sector erase, word write and sector lock/unlock can be stored in any sector. This code is copied to and executed from system RAM during flash memory updates. After successful completion, reads are again possible via the Read Array command. Sector erase suspend allows system software to suspend a sector erase to read/write data from/to sectors other than that which is suspend. Word write suspend allows system software to suspend a word write to read data from any other flash memory array location.With the mechanism of sector lock, memory contents cannot be altered due to noise or unwanted operation. When RP=VIH and VCC<VLKO (lockout voltage), any data write alteration can be failure. During read opera-tion, if write VPP voltage is below VPPLK, then hard-ware level data protection is achieved. With CUI's two-step command sequence sector erase, word write or sector lock/unlock, software level data protection is 3 BUS OPERATIONThe local CPU reads and writes flash memory in-sys-tem. All bus cycles to or from the flash memory conform to standard microprocessor bus cycles.3.1 ReadInformation can be read from any sector, configuration codes or status register independent of the VPP volt-age. RP can be at VIH.The first task is to write the appropriate read mode com-mand (Read Array, Read Configuration, Read Query or Read Status Register) to the CUI. Upon initial device power-up or after exit from reset, the device automati-cally resets to read array mode. In order to read data, control pins set for CE, OE, WE, RP and WP must be driven to active. CE and OE must be active to obtain data at the outputs. CE is the device selection control. OE is the data output (DQ0-DQ15) control and active drives the selected memory data onto the I/O bus, WE must be VIH, RP must be VIH, WP must be at VIL or VIH.3.2 Output DisableWith OE at a logic-high level (VIH), the device outputs are disabled. Output pins (DQ0-DQ15) are placed in a high-impedance state.3.3 StandbyCE at a logic-high level (VIH) places the device in standby mode which substantially reduces device power consumption. DQ0~DQ15 outputs are placed in a high-impedance state independent of OE. If deselected dur-ing sector erase, word write or sector lock/unlock, the device continues functioning, and consuming active power until the operation completes.3.4 ResetAs RP=VIL, it initiates the reset mode. The device en-ters reset/deep power down mode. However, the data stored in the memory has to be sustained at least 100nsMX28F160C3T/Band output high impedance state.In read modes, RP-low deselects the memory, places output drivers in a high-impedance state and turns off all internal circuits. RP must be held low for a minimum of 100ns. Time tPHQV is required after return from reset mode until initial memory access outputs are valid. Af-ter this wake-up interval tPHEL or tPHWL, normal op-eration is restored. The CUI is reset to read array mode and status register is set to 80H. Sector lock bit is set at lock status.During sector erase, word write or sector lock/unlock modes, RP-low will abort the operation. Memory con-tents being altered are no longer valid; the data may be partially erased or written.In addition, CUI will go into either array read mode or erase/write interrupted mode. When power is up and the device reset subsequently, it is necessary to read sta-tus register in order to assure the status of the device. Recognizing status register (SR.7~0) will assure if the device goes back to normal reset and enters array read mode.3.5 Read Configuration CodesThe read configuration codes operation outputs the manu-facturer code, device code, sector lock configuration codes, and the protection register. Using the manufac-turer and device codes, the system CPU can automati-cally match the device with its proper algorithms. The sector lock codes identify locked and unlocked sectors.3.6 WriteWriting commands to the CUI enable reading of device data and identifier codes. They also control inspection and clearing of the status register. When VCC=2.7V-3.6V and VPP within VPP1 or VPP2 range, the CUI addition-ally controls sector erase, word write and sector lock/ unlock.The Sector Erase command requires appropriate com-mand data and an address within the sector to be erased. The Full Chip Erase command requires appropriate com-mand data and an address within the device. The Word Write command requires the command and address of mands require the command and address within the de-vice or sector within the device (Sector Lock) to be locked. The Clear Sector Lock-Bits command requires the command and address within the device.The CUI does not occupy an addressable memory loca-tion. It is written when WE and CE are active (whichever goes high first). The address and data needed to ex-ecute a command are latched on the rising edge of WE or CE. Standard microprocessor write timings are used.MX28F160C3T/B4 COMMAND DEFINITIONSThe flash memory has four read modes: read array, readconfiguration, read status, read query, and two writemodes: program, erase. These read modes are acces-sible independent of the VPP voltage. But write modesare disable during VPP<VPPLK. Placing VPP on VPP1/2 enables successful sector erase, word write and sec-tor lock/unlock.Device operations are selected by writing specific com-mands into the CUI. T able 3 defines these commands.Table 2. Bus OperationMode Notes RP CE OE WE DQ0~DQ15Read1,2VIH VIL VIL VIH DOUTOutput Disable2VIH VIL VIH VIH High ZStandby2VIH VIH X X High ZReset2VIL X X X High ZWrite2,3,4,5VIH VIL VIH VIL DINNotes:1.Refer to DC Characteristics for VPPLK, VPP1, VPP2 voltage.2.X can be VIL or VIH for pin and addresses.3.RP at GND±0.2 to ensure the lowest power consumption.4.Refer to Table 3 for valid DIN during a write operation.5.To program or erase the lockable sectors holds WP at VIH.MX28F160C3T/BTable 3. Command Definition (1)Command Bus Notes First Bus Cycle Second Bus CycleCycles Operation Address Data Operation Address DataRequired(1)(2)(3)(1)(2)(3) Read Array1Write X FFHRead Configuration> 22,4Write X90H Read IA ID Read Query22,7Write X98H Read QA QD Read Status Register23Write X70H Read X SRD Clear Status Register13Write X50HSector Erase/Confirm2Write X20H Write SA D0H Word Write22,5Write X40H/10H Write WA WD Program/Erase Suspend1Write X B0HProgram/Erase Resume1Write X D0HSector Lock2Write X60H Write SA01H Sector Unlock26Write X60H Write SA D0H Lock-Down Sector2Write X60H Write SA2FH Protection Program2Write X C0H Write P A PDNotes:1.Bus operation are defined in Table 2 and referred to AC Timing Waveform.2.X=Any address within device.IA=ID-Code Address (refer to Table 4).ID=Data read from identifier code.SA=Sector Address within the sector being erased.WA=Address of memory location to be written.WD=Data to be written at location WA.PA=Program Address, PD=Program DataQA=Query Address, QD=Query Data.3.Data is latched from the rising edge of WE or CE (whichever goes high first)SRD=Data read from status register, see T able 6 for description of the status register bits.4.Following the Read Configuration codes command, read operation access manufacturer, device codes, sectorlock/unlock codes, see chapter 4.2.5.Either 40H or 10H command is recognized by the WSM as word write setup.6.The sector unlock operation simultaneously clear all sector lock.7.Read Query Command is read for CFI query information.MX28F160C3T/B4.1 Read Array CommandUpon initial device power-up and after exit from reset mode, the device defaults to read array mode. This op-eration is also initiated by writing the Read Array com-mand. The device remains enabled for reads until an-other command is written. Once the internal WSM has started a sector erase, word write or sector lock con-figuration the device will not recognize the Read Array command until the WSM completes its operation unless the WSM is suspended via a Sector Erase Suspend or Word Write Suspend command. If RP=VIL device is in read Read Array command mode, this read operation no longer requires VPP . The Read Array command func-tions independently of the VPP voltage and RP can be VIH.4.2 Read Configuration Codes CommandThe configuration code operation is initiated by writing the Read Configuration Codes command (90H). To re-turn to read array mode, write the Read Array Command (FFH). Following the command write, read cycles from addresses shown in T able 4 retrieve the manufacturer,device, sector lock configuration codes and the protec-tion register(see Table 4 for configuration code values).T o terminate the operation, write another valid command.Like the Read Array command, the Read Configuration Codes command functions independently of the VPP voltage and RP can be VIH. Following the Read Configu-ration Codes command, the information is shown:CodeAddress Data (A19-A0)(DQ15-DQ0)Manufacturer Code00000H00C2H Device Code(Top/Bottom)00001H 88C2/88C3H Sector Lock Configuration XX002H LocK - Sector is unlocked DQ0=0- Sector is locked DQ0=1- Sector is locked-down DQ1=1Protection Register Lock 80PR-LK Protection Register81-88PRTable 4: ID Code4.3 Read Status Register CommandCUI writes read status command (70H). The status reg-ister may be read to determine when a sector erase,word write or lock-bit configuration is complete and whether the operation completed successfully. (refer to table 6) It may be read at any time by writing the Read Status Register command. After writing this command,all subsequent read operations output data from the sta-tus register until another valid command is written. The status register contents are latched on the falling edge of CE or OE, whichever occurs last. CE or OE must toggle to VIH before further reads to update the status register latch. The Read Status Register command func-tions independently of the VPP voltage. RP can be VIH.4.4 Clear Status Register CommandStatus register bits SR.5, SR.4, SR.3 or SR.1 are set to "1"s by the WSM and can only be reset by the Clear Status Register command (50H). These bits indicate various failure conditions (see Table 6). By allowing sys-tem software to reset these bits, several operations (such as cumulatively erasing multiple sectors or writing sev-eral words in sequence) may be performed. The status register may be polled to determine if an error occurred during the sequence.T o clear the status register, the Clear Status Register command (50H) is written on CUI. It functions indepen-dently of the applied VPP Voltage. RP can be VIH. This command is not functional during sector erase or word write suspend modes.MX28F160C3T/B4.5 Sector Erase CommandErase is executed one sector at a time and initiated by a two-cycle command. A sector erase setup is first writ-ten (20H), followed by a sector erase confirm (D0H). This command sequence requires appropriate sequencing and an address within the sector to be erased. Sector pre-conditioning, erase, and verify are handled internally by the WSM. After the two-cycle sector erase sequence is written, the device automatically outputs status register data when read (see Figure 8). The CPU can detect sec-tor erase completion by analyzing the output data of the status register bit SR.7.When the sector erase is complete, status register bit SR.5 should be checked. If a sector erase error is de-tected, the status register should be cleared before sys-tem software attempts corrective actions. The CUI re-mains in read status register mode until a new com-mand is issued.This two-step command sequence of set-up followed by execution ensures that sector contents are not acciden-tally erased. An invalid sector Erase command sequence will result in both status register bits SR.4 and SR.5 being set to "1". Also, reliable sector erasure can only occur when 2.7V~3.6V and VPP=VPP1/2. In the absence of this high voltage, sector contents are protected against erasure. If sector erase is attempted while VPP<VPPLK SR.3 and SR.5 will be set to "1". T o successfully erase the boot sector, the corresponding sector lock-bit must be clear first. In parameter and sectors case, it must be cleared the corresponding sector lock-bit. If sector erase is attempted when the excepting above sector being locked conditions, SR.1 and SR.5 will be set to "1". Sec-tor erase is not functional.4.6 Word Write CommandWord write is executed by a two-cycle command se-quence. Word write setup (standard 40H or alternate 10H) is written, followed by a second write that specifies the address and data. The WSM then takes over, controlling the word write and write verify algorithms internally. Af-ter the word write sequence is written, the device auto-matically outputs status register data when read (see Figure 6). The CPU can detect the completion of the word write event by analyzing the status register bit SR.7. When word write is complete, status register bit SR.4should be checked. If word write error is detected, the status register should be cleared. The internal WSM verify only detects errors for "1"s that do not successfully write to "0"s. The CUI remains in read status register mode until it receives another command.Reliable word writes can only occur when VCC=2.7V~3.6V and VPP=VPP1/2. If VPP is not within acceptable limits, the WSM doesn't execut the program command. If word write is attempted while VPP<VPPLK, status register bits SR.3 and SR.4 will be set to "1". Successful word write requires for boot sector that WP is VIH the corresponding sector lock-bit be cleared. In parameter and main sectors case, it must be cleared the corresponding sector lock-bit. If word write is at-tempted when the excepting above sector being clocked conditions, SR.1 and SR.4 will be set to "1". Word write is not functional.4.7 Sector Erase Suspend CommandThe Sector Erase Suspend command (50H) allows sec-tor-erase interruption to read or word write data in an-other sector of memory. Once the sector erase process starts, writing the Sector Erase Suspend command re-quests that the WSM suspend the sector erase sequence at a predetermined point in the algorithm. The device outputs status register data when read after the Sector Erase Suspend command is written. Polling status reg-ister bits SR.7 and SR.6 can determine when the sector erase operation has been suspended (both will be set to "1"). Specification tWHRH2/tEHRH2 defines the sector erase suspend latency.When Sector Erase Suspend command is written to the CUI, if sector erase was finished, the device would be placed read array mode. Therefore, after Sector Erase Suspend command is written to the CUI, Read Status Register command (70H) has to be written to CUI, then status register bit SR.6 should be checked if/when the device is in suspend mode.At this point, a Read Array command can be written to read data from sectors other than that which is sus-pended. A Word Write commands sequence can also be issued during erase suspend to program data in other sectors. Using the Word Write Suspend command (see Section 4.9), a word write operation can also be sus-pended. During a word write operation with sector erase suspended, status register bit SR.7 will return to "0".MX28F160C3T/BHowever, SR.6 will remain "1" to indicate sector erase suspend status.The only other valid commands while sector erase is suspended are Read Status Register, Read Configura-tion, Read Query, Program Setup, Program Resume, Sector Lock, Sector Unlock, Sector Lock-Down and sec-tor erase Resume. After a Sector Erase Resume com-mand is written to the flash memory, the WSM will con-tinue the sector erase process. Status register bits SR.6 and SR.7 will automatically be cleared. After the Erase Resume command is written, the device automatically outputs status register data when read (see Figure 9). VPP must remain at VPP1/2 while sector erase is sus-pended. RP must also remain at VIH (the same RP level used for sector erase). Sector cannot resume until word write operations initiated during sector erase suspend has completed.If the time between writing the Sector Erase Resume command and writing the Sector Erase Suspend com-mand is shorter than 15ms and both commands are writ-ten repeatedly, a longer time is required than standard sector erase until the completion of the operation.4.8 Word Write Suspend CommandThe Word Write Suspend command allows word write interruption to read data in other flash memory locations. Once the word write process starts, writing the Word Write Suspend command requests that the WSM sus-pend the Word write sequence at a predetermined point in the algorithm. The device continues to output status register data when read after the Word Write Suspend command is written. Polling status register bits SR.7 and SR.2 can determine when the word write operation has been suspended (both will be set to "1"). Specification tWHRH1/tEHRH1 defines the word write suspend latency. When Word Write Suspend command write to the CUI, if word write was finished, the device places read array mode. Therefore, after Word Write Suspend command write to the CUI, Read Status Register command (70H) has to be written to CUI, then status register bit SR.2 should be checked for if/when the device is in suspend mode.At this point, a Read Array command can be written to read data from locations other than that which is sus-pended. The only other valid commands while word write is suspended are Read Status Register Read Configura-tion, Read Query and Word Write Resume. After Word Write Resume command is written to the flash memory, the WSM will continue the Word write process. Status register bits SR.2 and SR.7 will automatically be cleared. After the Word Write Resume command is written, the device automatically outputs status register data when read (see Figure 7). VPP must remain at VPP1/2 while in word write suspend mode. RP must also remain at VIH (the same RP level used for word write).If the time between writing the Word Write Resume com-mand and writing the Word Write Suspend command is short and both commands are written repeatedly, a longer time is required than standard word write until the comple-tion of the operation.。

ATMEGA16A中文资料

ATMEGA16A中文资料高性能,低功耗AVR 8-bit微控制器•高级RISC建筑– 131条指令–绝大多数为单时钟周期执行– 32 x 8通用工作寄存器–全静态工作–高达16吞吐量在MIPS 16 MHz–片2—cycle乘数高耐久性非易失性内存段– 16K字节的程序存储器,在系统内可编程Flash– 512字节的EEPROM– 1K字节内部SRAM–写/擦除周期:10,000闪光/ 100,000的EEPROM–数据保存:在20年85°C/100年在25°C(1)–可选引导具有独立锁定Bits代码段•在系统编程的片上引导程序•真Read-While-Write操作–锁编程软件安全JTAG (IEEE std。

1149.1兼容)接口–边界扫描功能根据JTAG标准–广泛的片上调试支持–编程闪存,EEPROM,熔丝位和锁定Bits通过JTAG接口外设特点–两个8—bit定时器/计数器具有独立预分频器和比较模式–一个16-bit定时器/计数器具有独立预分频器,比较功能和捕捉模式–实时计数器具有独立振荡器–四PWM频道– 8-channel, 10-bit ADC• 8单端通道• 7在TQFP 包装差分通道只有• 2在1x, 10x,差分通道具有可编程增益或200x–面向字节的两线串行接口可编程串行USART的––主/从串行接口SPI–可编程看门狗定时器具有独立片内振荡器–片内模拟比较器单片机的特殊功能–上电复位和可编程的掉电检测–内部振荡器校准RC–外部和内部中断源– 6种睡眠模式:空闲,ADC降噪,省电,省电,待机和扩展待机I / O和封装– 32可编程I / O线– 40—pin PDIP, 44—lead TQFP,和44—pad QFN/MLF 工作电压– 2。

7为- 5。

5V ATmega16A速度等级– 0 —为16 MHz ATmega16A功耗@ 1 MHz, 3V,和25°C为ATmega16A–活动:0。

cici-手机外围电路详细介绍

T-FLASH电路

•

•

TF CLK频率为24MHZ,26,25平台均使用的12MHZ的频率。上电后先有CLK信号,通过TFCMD信号发送指令查看时何种类型的T卡,是单线的还是多线的。如果是单线的就用TF-CMD 通讯,如果支持多线就用TF-DAT-0,1,2,3,进行传输。 HSP301-HSP307为主板上的尖端放电点,和TVS管一起使用用来加快放电,消除ESD的干 扰

PDF 文件使用 "pdfFactory Pro" 试用版本创建

MIC电路

PDF 文件使用 "pdfFactory Pro" 试用版本创建

MICBIASP和MICBIASN为MIC电路的正负两路偏置电压,一般为2.4V-2.7V左右 的电压。 C204,C205主要为滤除射频信号的干扰。如果有GSM900MHZ的干扰则使用33PF的电 容,如果有DCS1800MHZ的干扰可以使用12PF的电容,如果有WIFI 2.4GHZ的干扰则 使用8.2PF的电容。 C206主要是抑制共模信号。 C201,C202为100NF电容,主要作用为隔直通交,防止直流电使PA饱和,产生信号偏移, 主要滤除100HZ一下的电流。 B201,B202为磁珠,主要滤除高频部分的干扰。 MIC偏置电流流向为从MICBIASP----MICBIASN,而不用公共的GND,主要是因为GND干 扰太大。 磁珠有很高的电阻率和磁导率,他等效于电阻和电感串联,但电阻值和电感值都随频率变 化。 他比普通的电感有更好的高频滤波特性,在高频时呈现阻性,所以能在相当宽的 频率范围内保持较高的阻抗,从而提高调频滤波效果

PDF 文件使用 "pdfFactory Pro" 试用版本创建

开机关机过程

多家LED驱动IC规格参数资料更新

HV9925 Output Current to 50mA;Universal 85-264VAC Operation;Fixed OFF-Time Buck Converter;Internal 500V Power MOSFET

DM621 4×3装饰照明专用PWM输出驱动恒流IC

DM631 12比特内置PWM+实时检测恒流驱动IC

DM632 16比特内置PWM+实时检测恒流驱动IC

DM163 8×3通道4096级PWM输出恒流驱动IC

DM164 8×3通道4096级PWM输出恒流驱动IC

DD211 二倍升压驱动IC 2-3.3V 最大升压100mA固定式恒流IC

500种 LED驱动IC规格参数资料

台湾地区部分:

明阳半导体股份有限公司

MY9268 适用于动态扫描驱动之16位高精度恒流LED驱动器内建16位多路扫描脉冲密度调变控制

MY9262 16位高精度恒流LED驱动器内建16位自适应脉冲密度调变控制及节能功能

MY9221 12通道(支援 R/G/B *4)恆流LED驱动芯片内建灰阶自适应脉冲密度调制

MY9231 3通道(支援 R/G/B *1)恆流LED驱动芯片内建灰阶自适应脉冲密度调制

MY9291 4通道(支援 R/G/B/W *1)恆流LED驱动芯片内建灰阶自适应脉冲密度调制

MY9163 内建错误侦测及可编程电流增益及节能功能的16位高精度恆流LED驱动器

MY9161 16位高准度恒流LED 驱动芯片

DD231 3信道驱动IC 5-30mA 可设置小体上电即亮型IC

Micrel KSZ8851-16MLL 48-pin单端口以太网控制器与非PCI接口评估板用户指南

KSZ8851-16MLL48-pin Single-Port Ethernet ControllerWith 8-bit or 16-bit Non-PCI InterfaceEvaluation Board User’s GuideRevision 1.1August 2010© Micrel, Inc. 2007All rights reservedMicrel is a registered trademark of Micrel and its subsidiaries in theUnited States and certain other countries. All other trademarks are theproperty of their respective owners.The information furnished by Micrel in this datasheet is believed to be accurate and reliable. However, no responsibility is assumed by Micrel for its use. Micrel reserves the right to change circuitry and specifications at any time without notification to the customer. Micrel Products are not designed or authorized for use as components in life support appliances, devices or systems where malfunction of a product can reasonably be expected to result in personal injury. Life support devices or systems are devices or systems that (a) are intended for surgical implant into the body or (b) support or sustain life, and whose failure to perform can be reasonably expected to result in a significant injury to the user.Micrel, Inc. August 6, 2010A Purchaser's use or sale of Micrel Products for use in life support appliances, devices or systems is at Purchaser's own risk and Purchaser agrees to fully indemnify Micrel for any damages resulting from such use or sale.Revision HistoryRevisionDateSummary of Changes1.0 2/20/2008 Initial Release1.1 8/6/2010Add JP8 for connection between VDD_IO and 1.8V (if VDD_IO is 1.8V). Changed the LED pulled up to 3.3V.Table of Contents1.0Introduction (5)2.0Board Features (5)3.0Evaluation Kit Contents (5)4.0Hardware Description (6)4.1Host Interface (7)4.2Jumper Setting & Definition (8)4.3Power Supply and Test Point Definition (9)4.4RJ-45 Connector and Transformer (9)4.5EEPROM and LED Indicators (9)4.6Board Reset (10)5.0Bill of Materials (11)Micrel, Inc. August 6, 2010List of FiguresFigure 1. KSZ8851-16MLL Evaluation Board (6)Figure 2. KSZ8851-16MLL-Eval Host Interface Connection with Spirent SmartBits (7)List of TablesTable 1. Header JP1 – Host Interface Connection for SD[15:0] (7)Table 2. Header JP1 – Host Interface Connection for Control and Power (8)Table 3. KSZ8851-16MLL-Eval Jumper Definition (8)Table 4. KSZ8851-16MLL-Eval Test Point Definition (9)Table 5. KSZ8851-16MLL EEPROM Format (9)Table 6. KSZ8851-16MLL-Eval Port Status LED Definition (10)Table 7. KSZ8851-16MLL-Eval LED Definition (10)Micrel, Inc. August 6, 20101.0 IntroductionThe KSZ8851-16MLL-Eval Evaluation Board is intended to provide a convenient and fast way to evaluate or demonstrate the functionality and performance of this new Single-Port Ethernet Controller KSZ8851-16MLL device from Micrel.The KSZ8851-16MLL comes with a 48-pin, lead-free LQFP (7mm x 7mm) package and provides an ideal solution for applications requiring high-performance from single-port Ethernet Controller with 8-bit or 16-bit generic processor interface. The KSZ8851-16MLL offers the most cost-effective solution for adding high-throughput Ethernet connectivity to traditional embedded systems.This evaluation board is designed as a stand alone without microcontroller or M16C on board. By default the KSZ8851-16MLL-Eval board comes with an operation of 16-bit bus mode, Little Endian mode and disabled EEPROM for KSZ8851-16MLL device. Customer may wire the board for his desired interface. The purpose is to provide a simple tool that can be used to evaluate the KSZ8851-16MLL device by connecting via headers to customer provided Microcontroller or Non-PCI hardware platform.Micrel provides a basic software driver based on the 8 or 16-bit bus solution and different operating system platforms to evaluate the KSZ8851-16MLL functionality and performance. The software includes a configuration utility to allow quick and easy device setup, initialization and transmit/receive packet. All KSZ8851-16MLL configuration pins and host interface signals are accessible either by jumpers, test points or headers.2.0 Board Features•One KSZ8851-16MLL 48-pin Single-Port Ethernet Controller with shared data bus for host interface•Single +5V/GND power input from headers•RJ-45 Jack for Fast Ethernet cable interface•HP Auto-MDIX for automatic detection and correction for straight-through and crossover cables•Two on board LDO voltage regulators, one for VDD_IO and the other for VDD_A3.3•One AT93C46 for external EEPROM interface•Two LED indicators for port status and activity•One LED indicator for 3.3V output ready•One LED indicator for Power Management Event (PME) output status•Jumpers to configure strapping pins and VDD_IO voltage option•Headers to wire the host interface from external hardware platform•Manual reset button for quick reboot after re-configuration of strapping pins3.0 Evaluation Kit ContentsThe KSZ8851-16MLL Evaluation Kit includes the following hardware:•KSZ8851-16MLL Evaluation BoardThe KSZ8851-16MLL Data Sheet and Hardware Design Package with the following collaterals that can be downloaded from Micrel’s website at •KSZ8851-16MLL Eval Board Schematic (PDF and OrCAD DSN file)•KSZ8851-16MLL Eval Board Gerber File (PDF version included)•KSZ8851-16MLL Eval Board User’s Guide (this document and included BOM)•KSZ8851-16MLL IBIS ModelMicrel, Inc. August 6, 20104.0 Hardware DescriptionThe KSZ8851-16MLL-Eval (shown in Figure 1) comes in a compact form factor and plugs directly into industry standard test equipment such as Spirent SmartBits, the other side of board is wired to external host interface through headers. Configuration of the KSZ8851-16MLL is accomplished through on-board jumper selections and/or by register access via the host shared data/control bus Interface.Figure 1. KSZ8851-16MLL Evaluation Board (Rev 1.1)Other features include a RJ-45 Jack for Fast Ethernet cable connection, transformer (Pulse H1102) to block DC level and provide a true AC coupling, EEPROM (Atmel AT93C46) to load MAC address when it is enabled, jumper to select LDO output for VDD_IO voltage, programmable LED indicators for reporting port link status and activity, and a manual reset button for quick reboot after re-configuration of strapping pins.The KSZ8851-16MLL-Eval receives +5V DC input power supply from its Headers JP1.Micrel, Inc. August 6, 2010Micrel, Inc. August 6, 20104.1 Host InterfaceThe KSZ8851-16MLL-Eval board receives +5V power from the header JP1 (pin 1/3). Figure 2 shows the Host interface connection with Spirent SmartBits for system set-up and performance test.Figure 2. KSZ8851-16MLL-Eval Host Interface Connection with Spirent SmartBitsThe KSZ8851-16MLL-Eval has a 40-pin header (JP1) for Host interface to external any Non-PCI hardware platform. Table 1 lists Shared Data SD[15:0] pin outs for the Host interface on header JP1. Table 2 lists the rest of control signals and power/ground pin outs for the Host interface on header JP1.16-Bit Bus Mode (pin 1 pull-up) 8-Bit Bus Mode (pin 1 pull down) Pin # (JP1) Shared Data Bus Signal CMD = 0 (low) CMD = 1 (high) CMD = 0 (low) CMD = 1 (high) 20 SD0 D0 x (don’t care) D0 A0 19SD1D1 x (don’t care) D1 A1 18 SD2 D2 A2 D2 A2 17 SD3 D3 A3 D3 A3 16 SD4 D4 A4 D4 A4 15 SD5 D5 A5 D5 A5 14 SD6 D6 A6 D6 A6 13 SD7 D7 A7 D7 A7 12 SD8 D8 x (don’t care) GND GND 11 SD9 D9 x (don’t care) GND GND 10 SD10 D10 x (don’t care) GND GND 9SD11D11 x (don’t care) GND GND 8 SD12 D12 BE0 GND GND 7 SD13 D13 BE1 GND GND 6 SD14 D14 BE2 GND GND 5 SD15D15BE3GNDGNDTable 1. Header JP1 – Host Interface Connection for SD[15:0]Pin # (JP1) Power & ControlSignal NamesDescription1, 3 5.0V_IN +5V power supply inputs for this board 2, 4, 21, 22, 25,26, 29, 33, 34, 37, 38, 39, 40 GND Groundinputs/pins23 CPU_CSN Chip Select input from host CPU24 CPU_RSTN Reset input from host CPU27 CPU_PME Power Management Event output to host CPU28 CPU_CMD Command type input from host CPU31 CPU_INTRN Interrupt output to host CPU35 CPU_WRN Write input from host CPU36 CPU_RDN Read input from host CPU30, 32 Spares For customer to useTable 2. Header JP1 – Host Interface Connection for Control and Power4.2 Jumper Setting & DefinitionThe KSZ8851-16MLL-Eval does not require any jumper for normal operation except the VDD_IO option. During power-up, the KSZ8851-16MLL is configured using the chip’s internal pull-up and pull-down resistors with its default strapping pin values which will set this device in operation of 16-bit bus mode, little endian and without EEPROM. Jumpers are provided to override the default settings, allowing for quick configuration and re-configuration of the board. To override the default settings, simply select and close the desired jumper setting(s) and toggle the on-board manual reset button (S1) for the new setting(s) to take effect.The KSZ8851-16MLL-Eval jumper settings are defined in Table 3 below.Jumper Definition Setting DescriptionJP2 EED_IO OFF (Default) OFF: EEPROM is not presentON: EEPROM is presentJP3 3.3V ON (Default) ON: to select 3.3V for VDD_IO (JP5 and JP6 must be OFF)OFF: De-select 3.3VJP4 EESK OFF (Default) OFF: Little EndianON: Big EndianJP5 2.5V OFF (Default) ON: to select 2.5V for VDD_IO (JP3 and JP6 must be OFF)OFF: De-select 2.5VJP6 1.8V OFF (Default) ON: to select 1.8V for VDD_IO (JP3 and JP5 must be OFF)OFF: De-select 1.8VJP7 P1LED1 OFF (Default) OFF: 16-Bit bus modeON: 8-Bit bus modeJP8 VDD_IO OFF (Default) OFF: VDD_IO = 2.5V or 3.3VON: VDD_IO = 1.8VTable 3. KSZ8851-16MLL-Eval Jumper DefinitionMicrel, Inc. August 6, 2010Power Supply and Test Point DefinitionThe KSZ8851-16MLL-Eval is supplied from external +5.0V DC power through a jumper (pin 1 and 3 at JP1), this +5.0V DC input is converted to both +3.3V with a Micrel LDO voltage regulator (U3, MIC5209BM) for VDD_A3.3 analog power and VDD (option for 3.3V, 2.5V or 1.8V) with a Micrel LDO voltage regulator (U5, MIC5209BM) for VDD_IO digital power. The KSZ8851-16MLL contains an internal +1.8V LDO, to provide its core, analog and PLL voltages.The KSZ8851-16MLL-Eval has four test points. They are defined in the following Table 4.Test Point DefinitionTP1 Power supply measurement for VDD_IOTP2 Power supply measurement for VDD_A3.3TP3 1.8V digital core voltage output measurement fromKSZ8851-16MLL internal LDOTP4 External power supply 5.0V_IN measurementTable 4. KSZ8851-16MLL-Eval Test Point Definition4.3 RJ-45 Connector and TransformerThe RJ-45 Jack (J1) connects to standard CAT-5 Ethernet cable to interface with 10Base-T/100Base-TX Ethernet devices. The LAN interface on the KSZ8851-16MLL is connected to a transformer (T1) with 50 ohm termination resistors for both TX+/- and RX+/- differential pairs. The line side of the transformer is connected to the RJ-45 connectors (J1).J1 also supports Auto-MDIX and Auto-Negotiation / Forced Modes.4.4 EEPROM and LED IndicatorsIt is optional in the KSZ8851-16MLL to use an external EEPROM. The EED_IO (JP2) must be pulled high (ON) to use external EEPROM.An external serial EEPROM with a standard microwire bus interface is used for non-volatile storage of information such as the host MAC address. The KSZ8851-16MLL can detect if the EEPROM is either a 1KB (93C46) or 4KB (93C66) EEPROM device. The EEPROM must be organized as 16-bit mode.The KSZ8851-16MLL EEPROM format is given in Table 5.WORD 15 8 7 00H Reserved1H Host MAC Address Byte 2 Host MAC Address Byte 12H Host MAC Address Byte 4 Host MAC Address Byte 33H Host MAC Address Byte 6 Host MAC Address Byte 54H – 6H Reserved7H-3FH Not used for KSZ8851-16MLL (available for user to use)Table 5. KSZ8851-16MLL EEPROM FormatMicrel, Inc. August 6, 2010A dual LED indicator (LED1) is located adjacent to the RJ-45 Connector (J1). The top LED is connected to P1LED1 (pin 1) and bottom LED is connected to P1LED0 (pin 2) of the KSZ8851-16MLL.The two LEDs are programmable to LED mode ‘0’ or ‘1’ via register 0xC6 bits [9], and are defined in the following Table 6.LED Mode0 (Default) 1LED1 (Top) 100BT ACTLED1 (Bottom) LINK/ACT LINKTable 6. KSZ8851-16MLL-Eval Port Status LED DefinitionTable 7 shows the rest of LEDs definition.LED Color DescriptionLED2 Green Power Management Event (PME) StatusLED3 Red 3.3V Power available indicatorTable 7. KSZ8851-16MLL-Eval LED Definition4.5 Board ResetThe KSZ8851-16MLL-Eval generates a reset signal from the reset circuitry during power up. It also provides a push button S1 reset circuit to reset the KSZ8851-16MLL device. During power up, the board is automatically reset. User can also press reset button S1 on the board for a manual reset.Micrel, Inc. August 6, 2010KSZ8851-16MLL-Eval Evaluation Board User’s Guide Rev. 1.1 Micrel, Inc.August 6, 201011/11 5.0 Bill of MaterialsKSZ8851-16MLL Eval Board (Revision 1.1)。

MSM8939核心板项目规格书

I2S NFC 指纹模块接 口 摄像头闪光 灯控制接口 环境光传感 器接口 电池接口 USB MIC EAR Output SPEAKER 耳机

为外挂回声抑制预留 NFC 接口

SPI 总线指纹模块接口

支持

1 1 2 路,开关切换 双路 1 路差分输出 1 路,0.8W max 1路 12+(不用的引脚复用可增加

27 28 30

PRI_MIC_GND PRI_MIC_P MIC_BIAS1

AUDIO AUDIO AUDIO

主 MIC 参考地 主 MIC 输入信号 MIC 偏压 1.8v

主 MIC 地

不要接外围 主地,直接 31 32 33 34 SEC_MIC_GND SEC_MIC_P SPKR_OUT_M SPKR_OUT_P AUDIO AUDIO AUDIO AUDIO 副 MIC 参考地 副 MIC 输入引脚 扬声器输出 M 扬声器输出 P 不要接外围 主地,直接 35 36 37 38 39 40 42 43 44 GND_HEADSET EAR_OUT_M EAR_OUT_P CDC_HPH_L CDC_HPH_R MIC_P_HSET BLSP3_CS1_N PS_HOLD_PMIC_TP LED_R_DRV AUDIO GND AUDIO AUDIO AUDIO AUDIO AUDIO SPI DEBUG PIN LED_DRV 耳机参考地 earpice 输出 M earpice 输出 P 耳机左声道输出 耳机右声道输出 耳机 mic 输入 指纹/SPI 片选信号 1,SPI sdcard 时使用 PS_HOLD 调试引脚 5mA 1.8v logic 接耳机地 副 MIC 地

深圳元麦科技有限公司

WCDMA Band Standard CDMA Band Standard GSM BAND Standard WLAN/BT/ FM 802.11a/b/g/n/ac WLAN WIFI 热点 Bluetooth 4.0 FM 支持 支持 RX 2.4G & 5.8G supported 支持 GSM 850/900/1800/1900; follow 3GPP spec CDMA 1x&EVDO 800; follow 3GPP spec WCDMA 850/900/1900/2100; follow 3GPP spec

MIC4120YME;MIC4129YML TR;MIC4129YME;MIC4120YME TR;MIC4129YME TR;中文规格书,Datasheet资料

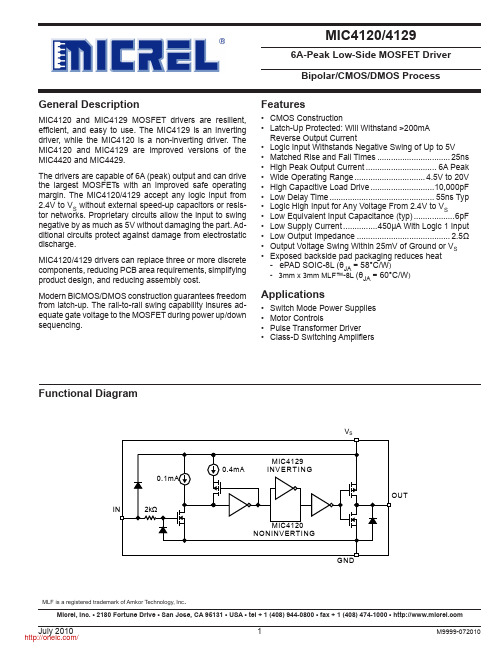

MIC4120/41296A-Peak Low-Side MoSfet Driver Bipolar/CMoS/DMoS ProcessGeneral DescriptionMIC4120 and MIC4129 MOSFET drivers are resilient, efficient, and easy to use. The MIC4129 is an inverting driver, while the MIC4120 is a non-inverting driver. The MIC4120 and MIC4129 are improved versions of the MIC4420 and MIC4429.The drivers are capable of 6A (peak) output and can drive the largest MOSFETs with an improved safe operating margin. The MIC4120/4129 accept any logic input from 2.4V to V S without external speed-up capacitors or resis -tor networks. Proprietary circuits allow the input to swing negative by as much as 5V without damaging the part. Ad -ditional circuits protect against damage from electrostatic discharge.MIC4120/4129 drivers can replace three or more discrete components, reducing PCB area requirements, simplifying product design, and reducing assembly cost.Modern BiCMOS/DMOS construction guarantees freedom from latch-up. The rail-to-rail swing capability insures ad -equate gate voltage to the MOSFET during power up/down sequencing.features• CMOS Construction• Latch-Up Protected: Will Withstand >200mA Reverse Output Current• Logic Input Withstands Negative Swing of Up to 5V • Matched Rise and Fall Times ................................25ns • High Peak Output Current ...............................6A Peak • Wide Operating Range ...............................4.5V to 20V • High Capacitive Load Drive ............................10,000pF • Low Delay Time ..............................................55ns Typ • Logic High Input for Any Voltage From 2.4V to V S• Low Equivalent Input Capacitance (typ) ..................6pF • Low Supply Current ...............450µA With Logic 1 Input • Low Output Impedance .........................................2.5Ω• Output Voltage Swing Within 25mV of Ground or V S • Exposed backside pad packaging reduces heat- ePAD SOIC-8L (θJA = 58°C/W )- 3mm x 3mm MLF™-8L (θJA = 60°C/W )Applications• Switch Mode Power Supplies • Motor Controls• Pulse Transformer Driver •Class-D Switching Amplifiersfunctional DiagramV Micrel, Inc. • 2180 Fortune Drive • San Jose, CA 95131 • USA • tel + 1 (408) 944-0800 • fax + 1 (408) 474-1000 • MLF is a registered trademark of Amkor Technology, Inc.Pin ConfigurationsV S OUT OUT GNDV S IN NC GND EPAD SOIC-8 (ME)MLF-8 (ML)Ordering InformationPart Number Package Configuration Lead Finish MIC4120YME EPAD 8-Pin SOICNon-Inverting Pb-Free MIC4120YML 8-Pin MLF Non-Inverting Pb-Free MIC4129YME EPAD 8-Pin SOICInverting Pb-Free MIC4129YML8-Pin MLFInvertingPb-FreePin DescriptionPin NumberPin NamePin Function 2IN Control Input4, 5GND Ground: Duplicate pins must be externally connected together 1, 8VS Supply Input: Duplicate pins must be externally connected together 6, 7OUT Output: Duplicate pins must be externally connected together 3NC Not connected EPGNDGround: BacksideElectrical Characteristics: (T A = 25°C with 4.5V ≤ V S ≤ 20V unless otherwise specified. Note 3.) Input Voltage slew rate>1V/µs Symbol ParameterConditionsMinTypMaxUnitsINPUT V IH Logic 1 Input Voltage 2.4 1.9 V V IL Logic 0 Input Voltage 1.5 0.8 V V IN Input Voltage Range–5 V S + 0.3 V I IN Input Current0 V ≤ V IN ≤ V S–1010µAOUTPUT V OH High Output Voltage See Figure 1 V S –0.025V V OL Low Output Voltage See Figure 10.025 V R O Output Resistance, I OUT = 10 mA, V S = 20 V 1.4 5 Ω Output Low R O Output Resistance, I OUT = 10 mA, V S = 20 V 1.5 5 Ω Output High I PK Peak Output Current V S = 20 V (See Figure 6) 6 A I R Latch-Up Protection200mAWithstand Reverse CurrentSwItChInG tIMet R Rise Time Test Figure 1, C L = 2200 pF 12 30 ns35 ns t F Fall Time Test Figure 1, C L = 2200 pF 13 30 ns35 ns t D1 Delay Time Test Figure 1 45 75 ns100 ns t D2 Delay Time Test Figure 1 50 75 ns100 ns POWER SUPPLYI S Power Supply Current V IN = 3 V 0.45 3 mAV IN = 0 V 60 400 µA V SOperating Input Voltage4.520V1. Functional operation above the absolute maximum stress ratings is not implied.2. Static-sensitive device. Store only in conductive containers. Handling personnel and equipment should be grounded to prevent damage from static discharge.3. Specification for packaged product only.4. Devices are ESD sensitive. Handling precautions recommended. Human body model: 1.5kΩ in series with 100pF.Absolute Maximum Ratings (Notes 1, 2 and 3)Supply Voltage ...........................................................24V Input Voltage ...............................V S + 0.3V to GND – 5V Input Current (V IN > V S ) ..........................................50mA Storage Temperature .............................–65°C to +150°C Lead Temperature (10 sec.) ...................................300°C ESD Rating, note 4operating RatingsSupply Voltage ..............................................4.5V to 20V Junction Temperature ............................–40°C to +125°C Package Thermal Resistance3x3 MLF™ (q JA ) ...............................................60°C/W EPAD SOIC-8 (q JA ) ..........................................58°C/WFigure 1. Inverting Driver Switching Time90%10%10%0V 5V V S OUTPUTINPUT90%0V90%10%10%0V 5V V S OUTPUTINPUT90%0VFigure 2. Non-inverting Driver Switching Timetest CircuitsTypical CharacteristicsApplications InformationSupply BypassingCharging and discharging large capacitive loads quickly requires large currents. For example, charging a 2500pF load to 18V in 25ns requires a 1.8 A current from the device power supply.The MIC4120/4129 has double bonding on the supply pins, the ground pins and output pins This reduces parasitic lead inductance. Low inductance enables large currents to be switched rapidly. It also reduces internal ringing that can cause voltage breakdown when the driver is operated at or near the maximum rated voltage.Internal ringing can also cause output oscillation due to feedback. This feedback is added to the input signal since it is referenced to the same ground.To guarantee low supply impedance over a wide frequency range, a parallel capacitor combination is recommended for supply bypassing. Low inductance ceramic capacitors should be used. A 1µF low ESR film capacitor in parallel with two 0.1 µF low ESR ceramic capacitors provide adequate bypassing. Connect one ceramic capacitor directly between pins 1 and 4. Connect the second ceramic capacitor directly between pins 8 and 5.GroundingThe high current capability of the MIC4120/4129 demands careful PC board layout for best performance. Since the MIC4129 is an inverting driver, any ground lead impedance will appear as negative feedback which can degrade switch-ing speed. Feedback is especially noticeable with slow-rise time inputs.Figure 3 shows the feedback effect in detail. As the MIC4129 input begins to go positive, the output goes negative and several amperes of current flow in the ground lead. As little as 0.05Ω of PC trace resistance can produce hundreds of millivolts at the MIC4129 ground pins. If the driving logic is referenced to power ground, the effective logic input level is reduced and oscillation may result.To insure optimum performance, separate ground traces should be provided for the logic and power connections. Con-necting the logic ground directly to the MIC4129 GND pins will ensure full logic drive to the input and ensure fast output switching. Both of the MIC4129 GND pins should, however, still be connected to power ground.The E-Pad and MLF packages have an exposed pad under the package. It's important for good thermal performance that this pad is connected to a ground plane.Table 1: MIC4129 Maximum operating frequencyV S Max Frequency20V 1Mhz 15V 1.5MHz 10V 3.5MHzConditions:T A = 25°C, 3. C L = 2500pFInput StageThe input voltage level of the 4129 changes the quiescent supply current. The N channel MOSFET input stage transistor drives a 450µA current source load. With a logic “1” input, the maximum quiescent supply current is 450µA. Logic “0” input level signals reduce quiescent current to 55µA maximum.The MIC4120/4129 input is designed to provide hysteresis. This provides clean transitions, reduces noise sensitivity, and minimizes output stage current spiking when changing states. Input voltage threshold level is approximately 1.5V, making the device TTL compatible over the 4.5V to 20V operating supply voltage range. Input current is less than 10µA over this range.The MIC4129 can be directly driven by the MIC9130, MIC3808, MIC38HC42 and similar switch mode power supply. By offload -ing the power-driving duties to the MIC4120/4129, the power supply controller can operate at lower dissipation. This can improve performance and reliability.The input can be greaterthan the +V S supply, however, current will flow into the input lead. The propagation delay for T D2 will increase to as much as 400ns at room temperature. The input currents can be as high as 30mA p-p (6.4mA RMS ) with the input, 6 V greater than the supply voltage. No damage will occur to MIC4120/4129 however, and it will not latch.The input appears as a 7pF capacitance, and does not change even if the input is driven from an AC source. Care should be taken so that the input does not go more than 5 volts below the negative rail.Power DissipationCMOS circuits usually permit the user to ignore power dis -sipation. Logic families such as 4000 and 74C have outputs which can only supply a few milliamperes of current, and even shorting outputs-to-ground will not force enough current to destroy the device. The MIC4120/4129, on the other hand, can source or sink several amperes and drive large capacitive loads at high frequency. The package power dissipation limitcan easily be exceeded. Therefore, some attention should be given to power dissipation when driving low impedance loads and/or operating at high frequency.The supply current vs frequency and supply current vs capaci -tive load characteristic curves aid in determining power dissi -pation calculations. Table 1 lists the maximum safe operating frequency for several power supply voltages when driving a 2500pF load. More accurate power dissipation figures can be obtained by summing the three dissipation sources.Given the power dissipation in the device, and the thermal resistance of the package, junction operating temperature for any ambient is easy to calculate. For example, the ther -mal resistance of the 8-pin EPAD MSOP package, from the data sheet, is 60°C/W. In a 25°C ambient, then, using a maximum junction temperature of 150°C, this package will dissipate 2W.Accurate power dissipation numbers can be obtained by total -ing the three sources of power dissipation in the device:• Load Power Dissipation (P L )• Quiescent power dissipation (P Q )• Transition power dissipation (P T )Calculation of load power dissipation differs depending upon whether the load is capacitive, resistive or inductive.Resistive Load Power DissipationDissipation caused by a resistive load can be calculated as:P L = I 2 R O D where:I = the current drawn by the loadR O = the output resistance of the driver when the output is high, at the power supply voltage used. (See data sheet)D = fraction of time the load is conducting (duty cycle)Figure 3. Switching Time Degradation Due tonegative feedbacktransition Power DissipationTransition power is dissipated in the driver each time its out -put changes state, because during the transition, for a very brief interval, both the N- and P-channel MOSFETs in the output totem-pole are ON simultaneously, and a current is conducted through them from V +S to ground. The transition power dissipation is approximately:P T = 2 f V S (A•s)where (A•s) is a time-current factor derived from the typical characteristic curves.Total power (P D ) then, as previously described is: P D = P L + P Q +P TDefinitionsC L = Load Capacitance in Farads.D = Duty Cycle expressed as the fraction of time theinput to the driver is high. f = Operating Frequency of the driver in Hertz. I H = Power supply current drawn by a driver when bothinputs are high and neither output is loaded. I L = Power supply current drawn by a driver when bothinputs are low and neither output is loaded. I D = Output current from a driver in Amps. P D = Total power dissipated in a driver in Watts. P L = Power dissipated in the driver due to the driver’sload in Watts. P Q = Power dissipated in a quiescent driver in Watts.P T = Power dissipated in a driver when the outputchanges states (“shoot-through current”) in Watts. NOTE: The “shoot-through” current from a dual transition (once up, once down) for both drivers is shown by the "Typical Characteristic Curve": Crossover Area vs. Supply Voltage and is in am -pere-seconds. This figure must be multiplied by the number of repetitions per second (frequency) to find Watts. R O = Output resistance of a driver in Ohms.V S = Power supply voltage to the IC in Volts.Capacitive Load Power DissipationDissipation caused by a capacitive load is simply the energy placed in, or removed from, the load capacitance by the driver. The energy stored in a capacitor is described by the equation:E = 1/2 C V 2As this energy is lost in the driver each time the load is charged or discharged, for power dissipation calculations the 1/2 is removed. This equation also shows that it is good practice not to place more voltage on the capacitor than is necessary, as dissipation increases as the square of the voltage applied to the capacitor. For a driver with a capacitive load: P L = f C (V S )2where:f = O perating Frequency C = L oad Capacitance V S = D river Supply VoltageInductive Load Power DissipationFor inductive loads the situation is more complicated. For the part of the cycle in which the driver is actively forcing current into the inductor, the situation is the same as it is in the resistive case:P L1 = I 2 R O DHowever, in this instance the R O required may be either the on resistance of the driver when its output is in the high state, or its on resistance when the driver is in the low state, depending on how the inductor is connected, and this is still only half the story. For the part of the cycle when the induc -tor is forcing current through the driver, dissipation is best described asP L2 = I V D (1-D)where V D is the forward drop of the clamp diode in the driver (generally around 0.7V). The two parts of the load dissipation must be summed in to produce P LP L = P L1 + P L2Quiescent Power DissipationQuiescent power dissipation (P Q , as described in the input section) depends on whether the input is high or low. A low input will result in a maximum current drain (per driver) of ≤0.2mA; a logic high will result in a current drain of ≤2.0mA. Quiescent power can therefore be found from: P Q = V S [D I H + (1-D) I L ]where: I H = quiescent current with input high I L = quiescent current with input lowD = fraction of time input is high (duty cycle)V S =power supply voltage5.0V 0V18V0Vfigure 4. Peak output Current test CircuitPackage Information8-Pin 3x3 MLF (ML)8-Pin Exposed Pad SOIC (ME)MICREL INC. 2180 FORTUNE DRIVE SAN JOSE, CA 95131 USAtel + 1 (408) 944-0800 fax + 1 (408) 474-1000 web This information furnished by Micrel in this data sheet is believed to be accurate and reliable. However no responsibility is assumed by Micrel for its use.Micrel reserves the right to change circuitry and specifications at any time without notification to the customer.Micrel Products are not designed or authorized for use as components in life support appliances, devices or systems where malfunction of a product can reasonably be expected to result in personal injury. Life support devices or systems are devices or systems that (a) are intended for surgical implant into the body or (b) support or sustain life, and whose failure to perform can be reasonably expected to result in a significant injury to the user. A Purchaser's use or sale of Micrel Products for use in life support appliances, devices or systems is a Purchaser's own risk and Purchaser agrees to fully indemnifyMicrel for any damages resulting from such use or sale.© 2004 Micrel Incorporated分销商库存信息:MICRELMIC4120YME MIC4129YML TR MIC4129YME MIC4120YME TR MIC4129YME TR MIC4120YML TR。

收音芯片汇总

(立体声)

SOP16

2.2V-3.6V

AM:500KHz-1710KHz

FM:32.0MHz-110.0MHz

32768Hz

1.无需MCU控制(单芯片AM/FM收音机)。

2.通过调整单联电位器来选台(PVR)。

3.通过调整单联电位器来调节音量(立体声)。

4.频率起点和终点可自由设定。

5.新增一路LINEIN功能、立体声指示灯和调谐指示灯。

KT0921

(立体声)

SSOP16

2.2V-3.6V

AM:500KHz-1710KHz

FM:32.0MHz-110.0MHz

32768Hz

1.无需MCU控制(单芯片AM/FM收音机)。

2.通过三种方式选台:按键(CH+、CH-);编码器;单联电位器(PVR)。

3.支持3610频率显示。

4.频率起点和终点可自由设定。

KT0922M

(单声道)

SSOP16

2.2V-3.6V

AM:500KHz-1710KHz

FM:32.0MHz-110.0MHz

32768Hz

1.无需MCU控制(单芯片AM/FM收音机)。

2.通过调整单联电位器来选台(PVR)。

3.通过调整单联电位器来调节音量。

4.频率起点和终点可自由设定。

5.新增一路调谐指示灯。

收音芯片汇总

:/QQ:994843790

4.CH+、CH-、VOL+、VOL-按键。

KT0830EG

(立体声)

SOP16

2.0V-3.6V

FM:64.0MHz-109.0MHz

32768Hz

(可软件设定其他参考频率,最高26.0MHz)

常用开关电源芯片大全之欧阳育创编

常用开关电源芯片大全第1章DC-DC电源转换器/基准电压源1.1 DC-DC电源转换器1.低噪声电荷泵DC-DC电源转换器AAT3113/AAT31142.低功耗开关型DC-DC电源转换器ADP30003.高效3A开关稳压器AP15014.高效率无电感DC-DC电源转换器FAN56605.小功率极性反转电源转换器ICL76606.高效率DC-DC电源转换控制器IRU30377.高性能降压式DC-DC电源转换器ISL64208.单片降压式开关稳压器L49609.大功率开关稳压器L4970A10.1.5A降压式开关稳压器L497111.2A高效率单片开关稳压器L497812.1A高效率升压/降压式DC-DC电源转换器L597013.1.5A降压式DC-DC电源转换器LM157214.高效率1A降压单片开关稳压器LM1575/LM2575/LM2575HV15.3A降压单片开关稳压器LM2576/LM2576HV16.可调升压开关稳压器LM257717.3A降压开关稳压器LM259618.高效率5A开关稳压器LM267819.升压式DC-DC电源转换器LM2703/LM270420.电流模式升压式电源转换器LM273321.低噪声升压式电源转换器LM275022.小型75V降压式稳压器LM500723.低功耗升/降压式DC-DC电源转换器LT107324.升压式DC-DC电源转换器LT161525.隔离式开关稳压器LT172526.低功耗升压电荷泵LT175127.大电流高频降压式DC-DC电源转换器LT176528.大电流升压转换器LT193529.高效升压式电荷泵LT193730.高压输入降压式电源转换器LT195631.1.5A升压式电源转换器LT196132.高压升/降压式电源转换器LT343333.单片3A升压式DC-DC电源转换器LT343634.通用升压式DC-DC电源转换器LT346035.高效率低功耗升压式电源转换器LT346436.1.1A升压式DC-DC电源转换器LT346737.大电流高效率升压式DC-DC电源转换器LT378238.微型低功耗电源转换器LTC175439.1.5A单片同步降压式稳压器LTC187540.低噪声高效率降压式电荷泵LTC191141.低噪声电荷泵LTC3200/LTC3200-542.无电感的降压式DC-DC电源转换器LTC325143.双输出/低噪声/降压式电荷泵LTC325244.同步整流/升压式DC-DC电源转换器LTC340145.低功耗同步整流升压式DC-DC电源转换器LTC340246.同步整流降压式DC-DC电源转换器LTC340547.双路同步降压式DC-DC电源转换器LTC340748.高效率同步降压式DC-DC电源转换器LTC341649.微型2A升压式DC-DC电源转换器LTC342650.2A两相电流升压式DC-DC电源转换器LTC342851.单电感升/降压式DC-DC电源转换器LTC344052.大电流升/降压式DC-DC电源转换器LTC344253.1.4A同步升压式DC-DC电源转换器LTC345854.直流同步降压式DC-DC电源转换器LTC370355.双输出降压式同步DC-DC电源转换控制器LTC373656.降压式同步DC-DC电源转换控制器LTC377057.双2相DC-DC电源同步控制器LTC380258.高性能升压式DC-DC电源转换器MAX1513/MAX151459.精简型升压式DC-DC电源转换器MAX1522/MAX1523/MAX152460.高效率40V升压式DC-DC电源转换器MAX1553/MAX155461.高效率升压式LED电压调节器MAX1561/MAX159962.高效率5路输出DC-DC电源转换器MAX156563.双输出升压式DC-DC电源转换器MAX1582/MAX1582Y64.驱动白光LED的升压式DC-DC电源转换器MAX158365.高效率升压式DC-DC电源转换器MAX1642/MAX164366.2A降压式开关稳压器MAX164467.高效率升压式DC-DC电源转换器MAX1674/MAX1675/MAX167668.高效率双输出DC-DC电源转换器MAX167769.低噪声1A降压式DC-DC电源转换器MAX1684/MAX168570.高效率升压式DC-DC电源转换器MAX169871.高效率双输出降压式DC-DC电源转换器MAX171572.小体积升压式DC-DC电源转换器MAX1722/MAX1723/MAX172473.输出电流为50mA的降压式电荷泵MAX173074.升/降压式电荷泵MAX175975.高效率多路输出DC-DC电源转换器MAX180076.3A同步整流降压式稳压型MAX1830/MAX183177.双输出开关式LCD电源控制器MAX187878.电流模式升压式DC-DC电源转换器MAX189679.具有复位功能的升压式DC-DC电源转换器MAX194780.高效率PWM降压式稳压器MAX1992/MAX199381.大电流输出升压式DC-DC电源转换器MAX61882.低功耗升压或降压式DC-DC电源转换器MAX62983.PWM升压式DC-DC电源转换器MAX668/MAX66984.大电流PWM降压式开关稳压器MAX724/MAX72685.高效率升压式DC-DC电源转换器MAX756/MAX75786.高效率大电流DC-DC电源转换器MAX761/MAX76287.隔离式DC-DC电源转换器MAX8515/MAX8515A88.高性能24V升压式DC-DC电源转换器MAX872789.升/降压式DC-DC电源转换器MC33063A/MC34063A90.5A升压/降压/反向DC-DC电源转换器MC33167/MC3416791.低噪声无电感电荷泵MCP1252/MCP125392.高频脉宽调制降压稳压器MIC220393.大功率DC-DC升压电源转换器MIC229594.单片微型高压开关稳压器NCP1030/NCP103195.低功耗升压式DC-DC电源转换器NCP1400A96.高压DC-DC电源转换器NCP140397.单片微功率高频升压式DC-DC电源转换器NCP141098.同步整流PFM步进式DC-DC电源转换器NCP142199.高效率大电流开关电压调整器NCP1442/NCP1443/NCP1444/NCP1445100.新型双模式开关稳压器NCP1501101.高效率大电流输出DC-DC电源转换器NCP1550102.同步降压式DC-DC电源转换器NCP1570103.高效率升压式DC-DC电源转换器NCP5008/NCP5009 104.大电流高速稳压器RT9173/RT9173A105.高效率升压式DC-DC电源转换器RT9262/RT9262A106.升压式DC-DC电源转换器SP6644/SP6645107.低功耗升压式DC-DC电源转换器SP6691108.新型高效率DC-DC电源转换器TPS54350109.无电感降压式电荷泵TPS6050x110.高效率升压式电源转换器TPS6101x111.28V恒流白色LED驱动器TPS61042112.具有LDO输出的升压式DC-DC电源转换器TPS6112x 113.低噪声同步降压式DC-DC电源转换器TPS6200x114.三路高效率大功率DC-DC电源转换器TPS75003115.高效率DC-DC电源转换器UCC39421/UCC39422116.PWM控制升压式DC-DC电源转换器XC6371117.白光LED驱动专用DC-DC电源转换器XC9116118.500mA同步整流降压式DC-DC电源转换器XC9215/XC9216/XC9217119.稳压输出电荷泵XC9801/XC9802120.高效率升压式电源转换器ZXLB16001.2 线性/低压差稳压器121.具有可关断功能的多端稳压器BAXXX122.高压线性稳压器HIP5600123.多路输出稳压器KA7630/KA7631124.三端低压差稳压器LM2937125.可调输出低压差稳压器LM2991126.三端可调稳压器LM117/LM317127.低压降CMOS500mA线性稳压器LP38691/LP38693128.输入电压从12V到450V的可调线性稳压器LR8129.300mA非常低压降稳压器(VLDO)LTC3025130.大电流低压差线性稳压器LX8610131.200mA负输出低压差线性稳压器MAX1735132.150mA低压差线性稳压器MAX8875133.带开关控制的低压差稳压器MC33375134.带有线性调节器的稳压器MC33998135.1.0A低压差固定及可调正稳压器NCP1117136.低静态电流低压差稳压器NCP562/NCP563137.具有使能控制功能的多端稳压器PQxx138.五端可调稳压器SI-3025B/SI-3157B139.400mA低压差线性稳压器SPX2975140.五端线性稳压器STR20xx141.五端线性稳压器STR90xx142.具有复位信号输出的双路输出稳压器TDA8133143.具有复位信号输出的双路输出稳压器TDA8138/TDA8138A144.带线性稳压器的升压式电源转换器TPS6110x145.低功耗50mA低压降线性稳压器TPS760xx146.高输入电压低压差线性稳压器XC6202147.高速低压差线性稳压器XC6204148.高速低压差线性稳压器XC6209F149.双路高速低压差线性稳压器XC64011.3 基准电压源150.新型XFET基准电压源ADR290/ADR291/ADR292/ADR293151.低功耗低压差大输出电流基准电压源MAX610x152.低功耗1.2V基准电压源MAX6120153.2.5V精密基准电压源MC1403154.2.5V/4.096V基准电压源MCP1525/MCP1541155.低功耗精密低压降基准电压源REF30xx/REF31xx156.精密基准电压源TL431/KA431/TLV431A第2章AC-DC转换器及控制器1.厚膜开关电源控制器DP104C2.厚膜开关电源控制器DP308P3.DPA-Switch系列高电压功率转换控制器DPA423/DPA424/DPA425/DPA4264.电流型开关电源控制器FA13842/FA13843/FA13844/FA138455.开关电源控制器FA5310/FA53116.PWM开关电源控制器FAN75567.绿色环保的PWM开关电源控制器FAN76018.FPS型开关电源控制器FS6M07652R9.开关电源功率转换器FS6Sxx10.降压型单片AC-DC转换器HV-2405E11.新型反激准谐振变换控制器ICE1QS0112.PWM电源功率转换器KA1M088013.开关电源功率转换器KA2S0680/KA2S088014.电流型开关电源控制器KA38xx15.FPS型开关电源功率转换器KA5H0165R16.FPS型开关电源功率转换器KA5Qxx17.FPS型开关电源功率转换器KA5Sxx18.电流型高速PWM控制器L499019.具有待机功能的PWM初级控制器L599120.低功耗离线式开关电源控制器L659021.LINK SWITCH TN系列电源功率转换器LNK304/LNK305/LNK30622.LINK SWITCH系列电源功率转换器LNK500/LNK501/LNK52023.离线式开关电源控制器M51995A24.PWM电源控制器M62281P/M62281FP25.高频率电流模式PWM控制器MAX5021/MAX502226.新型PWM开关电源控制器MC4460427.电流模式开关电源控制器MC4460528.低功耗开关电源控制器MC4460829.具有PFC功能的PWM电源控制器ML482430.液晶显示器背光灯电源控制器ML487631.离线式电流模式控制器NCP120032.电流模式脉宽调制控制器NCP120533.准谐振式PWM控制器NCP120734.低成本离线式开关电源控制电路NCP121535.低待机能耗开关电源PWM控制器NCP123036.STR系列自动电压切换控制开关STR8xxxx37.大功率厚膜开关电源功率转换器STR-F665438.大功率厚膜开关电源功率转换器STR-G865639.开关电源功率转换器STR-M6511/STR-M652940.离线式开关电源功率转换器STR-S5703/STR-S5707/STR-S570841.离线式开关电源功率转换器STR-S6401/STR-S6401F/STR-S6411/STR-S6411F 442.开关电源功率转换器STR-S651343.离线式开关电源功率转换器TC33369~TC3337444.高性能PFC与PWM组合控制集成电路TDA16846/TDA1684745.新型开关电源控制器TDA1685046.“绿色”电源控制器TEA150447.第二代“绿色”电源控制器TEA150748.新型低功耗“绿色”电源控制器TEA153349.开关电源控制器TL494/KA7500/MB375950.Tiny SwitchⅠ系列功率转换器TNY253、TNY254、TNY25551.Tiny SwitchⅡ系列功率转换器TNY264P~TNY268G52.TOP Switch(Ⅱ)系列离线式功率转换器TOP209~TOP22753.TOP Switch-FX系列功率转换器TOP232/TOP233/TOP23454.TOP Switch-GX系列功率转换器TOP242~TOP25055.开关电源控制器UCX84X56.离线式开关电源功率转换器VIPer12AS/VIPer12ADIP57.新一代高度集成离线式开关电源功率转换器VIPer53第3章功率因数校正控制/节能灯电源控制器1.电子镇流器专用驱动电路BL83012.零电压开关功率因数控制器FAN48223.功率因数校正控制器FAN75274.高电压型EL背光驱动器HV8265.EL场致发光背光驱动器IMP525/IMP5606.高电压型EL背光驱动器/反相器IMP8037.电子镇流器自振荡半桥驱动器IR21568.单片荧光灯镇流器IR21579.调光电子镇流器自振荡半桥驱动器IR215910.卤素灯电子变压器智能控制电路IR216111.具有功率因数校正电路的镇流器电路IR216612.单片荧光灯镇流器IR216713.自适应电子镇流器控制器IR252014.电子镇流器专用控制器KA754115.功率因数校正控制器L656116.过渡模式功率因数校正控制器L656217.集成背景光控制器MAX8709/MAX8709A18.功率因数校正控制器MC33262/MC3426219.固定频率电流模式功率因数校正控制器NCP165320.EL场致发光灯高压驱动器SP440321.功率因数校正控制器TDA4862/TDA486322.有源功率因数校正控制器UC385423.高频自振荡节能灯驱动器电路VK05CFL24.大功率高频自振荡节能灯驱动器电路VK06TL第4章充电控制器1.多功能锂电池线性充电控制器AAT36802.可编程快速电池充电控制器BQ20003.可进行充电速率补偿的锂电池充电管理器BQ20574.锂电池充电管理电路BQ2400x5.单片锂电池线性充电控制器BQ2401xB接口单节锂电池充电控制器BQ2402x7.2A同步开关模式锂电池充电控制器BQ241008.集成PWM开关控制器的快速充电管理器BQ29549.具有电池电量计量功能的充电控制器DS277010.锂电池充电控制器FAN7563/FAN756411.2A线性锂/锂聚合物电池充电控制器ISL629212.锂电池充电控制器LA5621M/LA5621V13.1.5A通用充电控制器LT157114.2A恒流/恒压电池充电控制器LT176915.线性锂电池充电控制器LTC173216.带热调节功能的1A线性锂电池充电控制器LTC173317.线性锂电池充电控制器LTC173418.新型开关电源充电控制器LTC198019.开关模式锂电池充电控制器LTC400220.4A锂电池充电器LTC400621.多用途恒压/恒流充电控制器LTC400822.4.2V锂离子/锂聚合物电池充电控制器LTC405223.可由USB端口供电的锂电池充电控制器LTC405324.小型150mA锂电池充电控制器LTC405425.线性锂电池充电控制器LTC405826.单节锂电池线性充电控制器LTC405927.独立线性锂电池充电控制器LTC406128.镍镉/镍氢电池充电控制器M62256FP29.大电流锂/镍镉/镍氢电池充电控制器MAX150130.锂电池线性充电控制器MAX150731.双输入单节锂电池充电控制器MAX1551/MAX155532.单节锂电池充电控制器MAX167933.小体积锂电池充电控制器MAX1736B接口单节锂电池充电控制器MAX181135.多节锂电池充电控制器MAX187336.双路输入锂电池充电控制器MAX187437.单节锂电池线性充电控制器MAX189838.低成本/多种电池充电控制器MAX190839.开关模式单节锂电池充电控制器MAX1925/MAX192640.快速镍镉/镍氢充电控制器MAX2003A/MAX200341.可编程快速充电控制器MAX712/MAX71342.开关式锂电池充电控制器MAX74543.多功能低成本充电控制器MAX846A44.具有温度调节功能的单节锂电池充电控制器MAX8600/MAX860145.锂电池充电控制器MCP73826/MCP73827/MCP7382846.高精度恒压/恒流充电器控制器MCP73841/MCP73842/MCP73843/MCP73844 647.锂电池充电控制器MCP73861/MCP7386248.单节锂电池充电控制器MIC7905049.单节锂电池充电控制器NCP180050.高精度线性锂电池充电控制器VM7205。

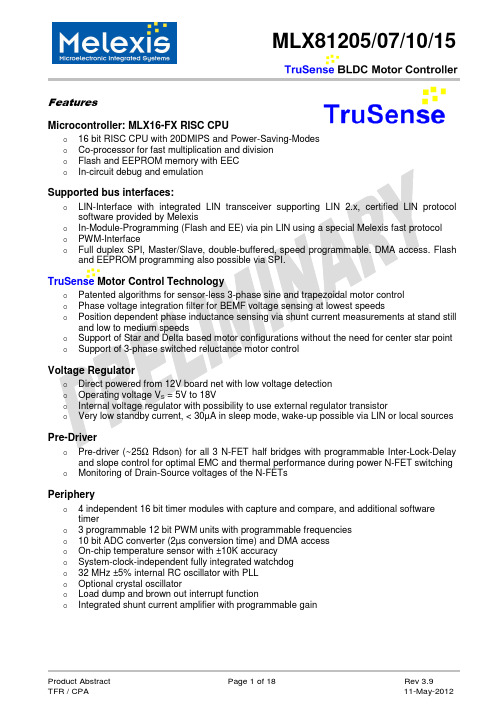

迈来芯芯片datasheet