CMHZ4689中文资料

RFID设备各款电子标签距离及相关参数

PVC白卡(ISO18000-6B、6C):纸质量防拆标签(ISO18000-6B):1、读写器频率915NHZ,功率30dBm。

1、读写器频率915NHZ,功率30dBm。

2、稳定读取距离10米2、隔着玻璃稳定读取距离10米3、芯片类型:NXP 3、芯片类型:NXP4、标签尺寸:8.6cm*5.3cm*1.05mm 4、标签尺寸:8.55cm*5.4cm陶瓷标签(ISO18000-6B):纸质标签(ISO18000-6B):1、读写器频率915NHZ,功率30dBm。

1、读写器频率915NHZ,功率30dBm。

2、隔着玻璃稳定读取距离10米2、稳定读取距离7~8米3、芯片类型:NXP 3、芯片类型:NXP4、标签尺寸:8.8cm*5.3cm*1.05mm 4、标签尺寸:8.55cm*5.4cm纸质标签(ISO18000-6C):纸质标签(ISO18000-6C):1、读写器频率915NHZ,功率30dBm。

1、读写器频率915NHZ,功率30dBm。

2、稳定读取距离7~8米2、稳定读取距离6~7米3、芯片类型:NXP 3、芯片类型:NXP4、标签尺寸:7.6cm*4.8cm 4、标签尺寸:7.5cm*1.4cm*0.4mm不干胶标签(ISO18000-6C):抗高温电子标签(ISO18000-6C):1、读写器频率915NHZ,功率30dBm。

1、读写器频率915NHZ,功率30dBm。

2、稳定读取距离5米2、稳定读取距离10米3、芯片类型:NXP 3、芯片类型:NXP4、标签尺寸:9.2cm*2.4cm*0.2mm 4、标签尺寸:10cm*2.03cm*0.3mm轮胎电子标签(ISO18000-6C):AWID纸质电子标签(ISO18000-6B):1、读写器频率915NHZ,功率30dBm。

1、读写器频率915NHZ,功率30dBm。

2、稳定读取距离5米2、稳定读取距离4~5米3、芯片类型:NXP 3、芯片类型:NXP4、标签尺寸:1.6cm*7.4cm*0.3mm 4、标签尺寸:10.8cm*2.77cmAlien不干胶电子标签(ISO18000-6C)Alien不干胶标签(ISO18000-6C):1、读写器频率915NHZ,功率20dBm 1、读写器频率915NHZ,功率30dBm。

2SD468中文资料

2SD468Silicon NPN EpitaxialApplication• Low frequency power amplifier• Complementary pair with 2SB562Outline2SD4682Absolute Maximum Ratings (Ta = 25°C)ItemSymbol Ratings Unit Collector to base voltage V CBO 25V Collector to emitter voltage V CEO 20V Emitter to base voltage V EBO 5V Collector current I C 1.0A Collector peak current i C(peak) 1.5A Collector power dissipation P C 0.9W Junction temperature Tj 150°C Storage temperatureTstg–55 to +150°CElectrical Characteristics (Ta = 25°C)ItemSymbol Min Typ Max Unit Test conditions Collector to base breakdown voltageV (BR)CBO25——V I C = 10 µA, I E = 0Collector to emitter breakdown voltageV (BR)CEO 20——V I C = 1 mA, R BE = ∞Emitter to base breakdown voltageV (BR)EBO 5——V I E = 10 µA, I C = 0Collector cutoff current I CBO —— 1.0µAV CB = 20 V, I E = 0DC current transfer ratio h FE *185—240V CE = 2 V, I C = 0.5 A*2Collector to emitter saturation voltageV CE(sat)—0.20.5V I C = 0.8 A, I B = 0.08 A*2Base to emitter voltage V BE —0.79 1.0V V CE = 2 V, I C = 0.5 A*2Gain bandwidth product f T —190—MHz V CE = 2 V, I C = 0.5 A*2Collector output capacitanceCob—22—pF V CB = 10 V, I E = 0, f = 1 MHzNotes: 1.The 2SD468 is grouped by h FE as follows.2.Pulse test B C85 to170120 to 2402SD46832SD4684Hitachi CodeJEDECEIAJWeight (reference value)TO-92 Mod—Conforms0.35 gUnit: mm元器件交易网Cautions1.Hitachi neither warrants nor grants licenses of any rights of Hitachi’s or any third party’s patent,copyright, trademark, or other intellectual property rights for information contained in this document.Hitachi bears no responsibility for problems that may arise with third party’s rights, includingintellectual property rights, in connection with use of the information contained in this document.2.Products and product specifications may be subject to change without notice. Confirm that you have received the latest product standards or specifications before final design, purchase or use.3.Hitachi makes every attempt to ensure that its products are of high quality and reliability. However,contact Hitachi’s sales office before using the product in an application that demands especially high quality and reliability or where its failure or malfunction may directly threaten human life or cause risk of bodily injury, such as aerospace, aeronautics, nuclear power, combustion control, transportation,traffic, safety equipment or medical equipment for life support.4.Design your application so that the product is used within the ranges guaranteed by Hitachi particularly for maximum rating, operating supply voltage range, heat radiation characteristics, installationconditions and other characteristics. Hitachi bears no responsibility for failure or damage when used beyond the guaranteed ranges. Even within the guaranteed ranges, consider normally foreseeable failure rates or failure modes in semiconductor devices and employ systemic measures such as fail-safes, so that the equipment incorporating Hitachi product does not cause bodily injury, fire or other consequential damage due to operation of the Hitachi product.5.This product is not designed to be radiation resistant.6.No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without written approval from Hitachi.7.Contact Hitachi’s sales office for any questions regarding this document or Hitachi semiconductor products.Hitachi, Ltd.Semiconductor & Integrated Circuits.Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan Tel: Tokyo (03) 3270-2111 Fax: (03) 3270-5109Copyright ' Hitachi, Ltd., 1999. All rights reserved. Printed in Japan.Hitachi Asia Pte. Ltd.16 Collyer Quay #20-00Hitachi TowerSingapore 049318Tel: 535-2100Fax: 535-1533URLNorthAmerica : http:/Europe : /hel/ecg Asia (Singapore): .sg/grp3/sicd/index.htm Asia (Taiwan): /E/Product/SICD_Frame.htm Asia (HongKong): /eng/bo/grp3/index.htm Japan : http://www.hitachi.co.jp/Sicd/indx.htmHitachi Asia Ltd.Taipei Branch Office3F, Hung Kuo Building. No.167, Tun-Hwa North Road, Taipei (105)Tel: <886> (2) 2718-3666Fax: <886> (2) 2718-8180Hitachi Asia (Hong Kong) Ltd.Group III (Electronic Components)7/F., North Tower, World Finance Centre,Harbour City, Canton Road, Tsim Sha Tsui,Kowloon, Hong Kong Tel: <852> (2) 735 9218Fax: <852> (2) 730 0281 Telex: 40815 HITEC HXHitachi Europe Ltd.Electronic Components Group.Whitebrook ParkLower Cookham Road MaidenheadBerkshire SL6 8YA, United Kingdom Tel: <44> (1628) 585000Fax: <44> (1628) 778322Hitachi Europe GmbHElectronic components Group Dornacher Stra§e 3D-85622 Feldkirchen, Munich GermanyTel: <49> (89) 9 9180-0Fax: <49> (89) 9 29 30 00Hitachi Semiconductor (America) Inc.179 East Tasman Drive,San Jose,CA 95134 Tel: <1> (408) 433-1990Fax: <1>(408) 433-0223For further information write to:。

Samsung-NAND-FLASH命名规则

三星的pure nand flash〔就是不带其他模块只是nand flash存储芯片〕的命名规那么如下:1. Memory (K)2. NAND Flash : 93. Small Classification(SLC : Single Level Cell, MLC : Multi Level Cell,SM : Smart Media, S/B : Small Block)1 : SLC 1 Chip XD Card2 : SLC 2 Chip XD Card4 : SLC 4 Chip XD CardA : SLC + Muxed I/ F ChipB : Muxed I/ F ChipD : SLC Dual SME : SLC DUAL (S/ B)F : SLC NormalG : MLC NormalH : MLC QDPJ : Non-Muxed OneNandK : SLC Die StackL : MLC DDPM : MLC DSPN : SLC DSPQ : 4CHIP SMR : SLC 4DIE STACK (S/ B)S : SLC Single SMT : SLC SINGLE (S/ B)U : 2 STACK MSPV : 4 STACK MSPW : SLC 4 Die Stack4~5. Density〔注:实际单位应该是bit,而不是Byte〕12 : 512M16 : 16M28 : 128M32 : 32M40 : 4M56 : 256M64 : 64M80 : 8M1G : 1G2G : 2G4G : 4G8G : 8GAG : 16GBG : 32GCG : 64GDG : 128G00 : NONE6~7. Organization00: NONE08: x816: x168. VccA : 1.65V~3.6VB : 2.7V (2.5V~2.9V)C : 5.0V (4.5V~5.5V)D : 2.65V (2.4V ~ 2.9V)E : 2.3V~3.6VR : 1.8V (1.65V~1.95V)Q : 1.8V (1.7V ~ 1.95V)T : 2.4V~3.0VU : 2.7V~3.6VV : 3.3V (3.0V~3.6V)W : 2.7V~5.5V, 3.0V~5.5V0 : NONE9. Mode0 : Normal1 : Dual nCE & Dual R/ nB4 : Quad nCE & Single R/ nB5 : Quad nCE & Quad R/ nB9 : 1st block OTPA : Mask Option 1L : Low grade10. GenerationM : 1st GenerationA : 2nd GenerationB : 3rd GenerationC : 4th GenerationD : 5th Generation11. "─"12. PackageA : COBB : TBGAC : CHIP BIZD : 63-TBGAE : TSOP1 (Lead-Free, 1217)F : WSOP (Lead-Free)G : FBGAH : TBGA (Lead-Free)I : ULGA (Lead-Free)J : FBGA (Lead-Free)K : TSOP1 (1217)L : LGAM : TLGAN : TLGA2P : TSOP1 (Lead-Free)Q : TSOP2 (Lead-Free)S : SMART MEDIAT : TSOP2U : COB (MMC)V : WSOPW : WAFERY : TSOP113. TempC : CommercialI : IndustrialS : SmartMediaB : SmartMedia BLUE0 : NONE (Containing Wafer, CHIP, BIZ, Exceptionhandling code)3 : Wafer Level 314. Bad BlockA : Apple Bad BlockB : Include Bad BlockD : Daisychain SampleK : Sandisk BinL : 1~5 Bad BlockN : ini. 0 blk, add. 10 blkS : All Good Block0 : NONE (Containing Wafer, CHIP, BIZ, Exceptionhandling code)15. NAND-Reserved0 : Reserved16. Packing Type- Common to all products, except of Mask ROM- Divided into TAPE & REEL(In Mask ROM, divided into TRAY, AMMO Packing Separately) 【举例说明】K9GAG08U0M 详细信息如下:1. Memory (K)2. NAND Flash : 93. Small Classification(SLC : Single Level Cell, MLC : Multi Level Cell,SM : SmartMedia, S/B : Small Block)G : MLC Normal4~5. DensityAG : 16G (Note: 这里单位是bit而不是byte,因此实际大小是16Gb=2GB)0 : Normal (x8)7. Organization0 : NONE 8 : x88. VccU : 2.7V~3.6V9. Mode0 : Normal10. GenerationM : 1st Generation11. "─"12. PackageP : TSOP1 (Lead-Free)13. TempC : Commercial14. Customer Bad BlockB : Include Bad Block15. Pre-Program Version0 : None整体描述就是:K9GAG08U0M是,三星的MLC Nand Flash,工作电压为2.7V~3.6V,x8〔即I/O是8位〕,大小是2GB〔16Gb〕,TSOP1封装。

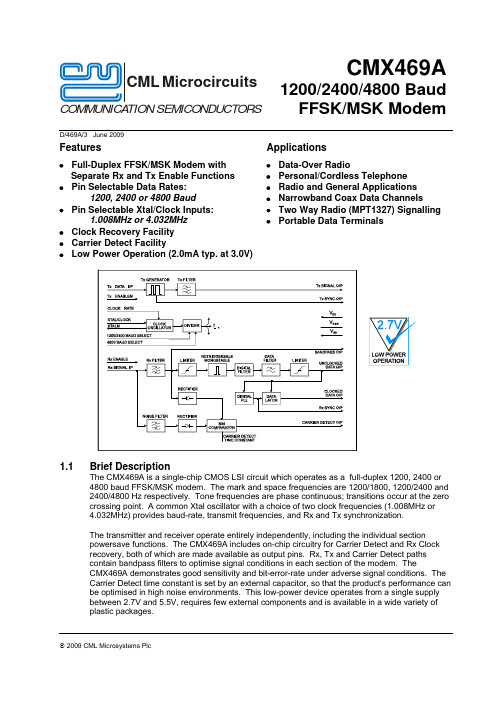

CMX469ADS芯片手册

CML Microcircuits C O M M U N IC A TIO N SEM IC O N D U C T O R SCMX469A 1200/2400/4800 Baud FFSK/MSK ModemJune 2009/469A/3DFeatures Applications• Full-Duplex FFSK/MSK Modem with Separate Rx and Tx Enable Functions • Data-Over Radio• Personal/Cordless Telephone• Pin Selectable Data Rates:1200, 2400 or 4800 Baud • Radio and General Applications • Narrowband Coax Data Channels• Pin Selectable Xtal/Clock Inputs:1.008MHz or 4.032MHz • Two Way Radio (MPT1327) Signalling • Portable Data Terminals• Clock Recovery Facility• Carrier Detect Facility• Low Power Operation (2.0mA typ. at 3.0V)1.1 BriefDescriptionThe CMX469A is a single-chip CMOS LSI circuit which operates as a full-duplex 1200, 2400 or4800 baud FFSK/MSK modem. The mark and space frequencies are 1200/1800, 1200/2400 and 2400/4800 Hz respectively. Tone frequencies are phase continuous; transitions occur at the zero crossing point. A common Xtal oscillator with a choice of two clock frequencies (1.008MHz or4.032MHz) provides baud-rate, transmit frequencies, and Rx and Tx synchronization.The transmitter and receiver operate entirely independently, including the individual sectionpowersave functions. The CMX469A includes on-chip circuitry for Carrier Detect and Rx Clockrecovery, both of which are made available as output pins. Rx, Tx and Carrier Detect pathscontain bandpass filters to optimise signal conditions in each section of the modem. TheCMX469A demonstrates good sensitivity and bit-error-rate under adverse signal conditions. The Carrier Detect time constant is set by an external capacitor, so that the product's performance can be optimised in high noise environments. This low-power device operates from a single supplybetween 2.7V and 5.5V, requires few external components and is available in a wide variety ofplastic packages.CONTENTSSection PageApplications (1)1.0 FeaturesandDescription (1)1.1 BriefDiagram (3)1.2 BlockList (4)1.3 SignalComponents (6)1.4 ExternalDescription (7)1.5 General1.6 Application Notes (8)Enable (8)1.6.1 RxRate Configurations (8)Data1.6.2 OperationalSet Up (8)1.6.3 Test1.6.4 Synchronous Modem Design Considerations (9)Specification (11)1.7 PerformancePerformance (11)1.7.1 Electrical1.7.2 Packaging (17)1.2 BlockDiagramFigure 1 Block Diagram1.3 Signal ListCMX469A D3 E2 Signal DescriptionPin No. Pin No. Name Type 11CLOCK/XTALI/PThe input to the on-chip inverter, for use witheither a 1.008MHz or a 4.032MHz Xtal or an external clock. Clock frequency selection is by means of the CLOCK RATE pin. This affects the operational data rate of the device. Operation of any CML microcircuit without a Xtal or clock input may cause device damage. 2 2 XTALN O/P The output of the on-chip inverter. 33Tx SYNC O/PO/PA squarewave, produced on-chip, to synchronize the input of logic data and transmission of the FFSK/MSK signal.4 5 Tx SIGNAL O/PO/PWhen the transmitter is enabled, this pin outputs the FFSK/MSK signal. With the transmitter disabled, this pin is set to a high-impedance state.5 7 Tx DATA I/P I/P The serial logic data to be transmitted is input to this pin.68Tx ENABLENI/PA logic ‘0’ will enable the transmitter. A logic ‘1’ at this input will put the transmitter into powersave whilst forcing Tx SYNC OUTPUT to a logic ‘1’ and Tx SIGNAL OUTPUT to a high-impedance state. This pin is internally pulled to V DD .7 9 BANDPASS O/P O/PThe output of the Rx Bandpass Filter. This output impedance is typically 10k Ω and may require buffering prior to use. 810Rx ENABLEI/P The control of the Rx function9 11 V BIASBIThe output of the on-chip analogue bias circuitry. Held internally at V DD /2, this pin should be decoupled to V SS by a capacitor (C2). This bias voltage is maintained under all powersave conditions.10 12V SSPWR Negative supply rail (GND).11 13 UNCLOCKED DATA O/P O/PThe recovered asynchronous serial data output from the receiver.12 14 CLOCKED DATA O/PO/PThe recovered synchronous serial data output from the receiver. Data is latched out by the recovered clock, available at the Rx SYNC O/P.CMX469AD3 E2 Signal DescriptionPin No.Pin No.Name Type13 15 CARRIER DETECT O/P O/PWhen an FFSK/MSK signal is being received this output is a logic ‘1’.14 16 Rx SIGNAL I/P I/P The FFSK/MSK signal input for the receiver. This input should be coupled via a capacitor, C3. 1518Rx SYNC O/PO/PA flywheel squarewave output. This clock will synchronize to incoming Rx FFSK/MSK data. 16 19 1200/2400 BAUD SELECTI/PA logic ‘1’ on this pin selects the 1200 baud option. Tone frequencies are: one cycle of 1200Hz represents a logic ‘1,’ one-and-a-half cycles of 1800Hz represents a logic ‘0.’ A logic ‘0’ on this pin selects the 2400 baud option. Tone frequencies are: one-half cycle of 1200Hz represents a logic ‘1,’ one cycle of 2400Hz represents a logic ‘0.’ This function is also used, in part, to select the 4800 baud option. This pin has an internal 1M Ω pullup resistor.17 20 4800 BAUD SELECTI/PA logic ‘1’ on this pin combined with a logic ‘0’ on the 1200/2400 BAUD SELECT pin will select the 4800 baud option (1M Ω pulldown resistor). Tone frequencies are: one-half cycle of 2400Hz represents a logic ‘1,’ one cycle of 4800Hzrepresents a logic ‘0.’ Operation at 4800 baud is only achieved by using a 4.032MHz Xtal or clock.18 21 CLOCK RATE I/PA logic input to select and allow the use of either a 1.008MHz or 4.032MHz Xtal/clock. Logic ‘1’ = 4.032MHz, logic ‘0’ = 1.008MHz. This input has an internal pulldown resistor (1.008MHz). 19 22 CARRIER DETECT TIME CONSTANT BIPart of the carrier detect integration function. The value of C4 connected to this pin will affect the carrier detect response time and hence noise performance.20 24V DDPWR Positive supply rail. A single 2.7 to 5.0 voltsupply is required. This pin should be decoupledto V SS by a capacitor (C5). 4, 6,17, 23No internal connection, do not use.Notes:I/P = Input O/P = Output BI = Bidirectional PWR = PowerComponents1.4 ExternalComponent ValueR1 1.0MΩC1 33.0pFC2 1.0µFC3 0.1µFC4 0.1µFC5 1.0µFC6 1.0µFC7 33.0pFX1 1.008MHzor4.032MHzNotes:1. V BIAS may be decoupled to V SS and V DD using C2 and C6 when input signals are referenced to theV BIAS pin. For input signals referenced to V SS, decouple V BIAS to V SS using C2 only.2. The performance of the Carrier Detect function will be affected by the nature of the noise spectrum inthe received channel. The value of C4 determines the Carrier Detect Time Constant. A long time constant results in improved noise immunity but increased response time. C4 may be varied to trade-off response time for noise immunity.3. A4.032MHz Xtal/clock is required for 4800 Baud operation.Figure 2 Recommended External Components1.5 GeneralDescriptionThe CMX469A has two sections, apart from the Xtal oscillator circuit and clock dividers. These sections may be independently powersaved.TransmitterThe transmitter is enabled by taking Tx EnableN low. Serial data applied to Tx Data Input issampled internally and an FFSK/MSK sequence is generated. After filtering, this is output atTx Signal O/P and the transmit clock derived from this signal is output at Tx Sync O/P.ReceiverThe receiver is enabled by taking Rx Enable high. The signal applied to Rx Signal I/P is filtered and recovered as serial data from the Unclocked Data O/P. A flywheel synchroniser is used to extract a clock from the recovered serial data stream. The clock is available at Rx Sync O/P and the retimed serial data is available at Clocked Data O/P.The integrated peak values of the Rx amplitude are compared with out-of-band noise levels and used to make a signal-to-noise assessment, which is available at Carrier Detect O/P.A Bandpass O/P is also available from the output of the first Rx filter stage, but will requirebuffering before use.Notes1.6 ApplicationEnable1.6.1 RxThe control of the relevant outputs with reference to the Rx Enable input is described below:Rx Enable Rx Function Clock Data O/P Carrier Detect O/P Rx Sync OutEnabledEnabled‘1’ EnabledEnabled‘0’ Powersave ‘0’ ‘1’ or ‘0’ ‘1’ or ‘0’After enabling the Receiver, a time of at least 8 bit periods plus 2ms should be allowed for the CarrierDetect circuit to stabilise and give a valid output.1.6.2 Operational Data Rate ConfigurationsOperational Data Rate Configurations are as described below:Xtal/Clock1.008MHz 4.032MHz FrequencyClock Rate ‘0’ ‘0’ ‘1’ ‘1’ ‘1’ ‘1’ ‘0’ ‘1’ ‘0’ ‘0’1200/2400Select4800 Select ‘0’ ‘0’ ‘0’ ‘0’ ‘1’Rate 1200 2400 1200 2400 4800BaudFigure 3 Suggested CMX469A Test Set-Up1.6.4 Synchronous Modem Design ConsiderationsThe CMX469A is an easily applied data pump which can be used with many protocols. Because it is an MSK (minimum shift keying) modem, it achieves a more noise resistant, higher data rate in a narrower bandwidth than other FSK (frequency shift keying) modems. This characteristic is especially important for wireless applications because it fundamentally determines the bandwidth of RF transmissions, which are strictly limited and controlled by regulatory agencies. Using MSK signalling, the CMX469A data modem can achieve a 2400 bps data rate within the typical 300-3000 Hz voice band of many common radios.In order to achieve this advantage, an MSK modem must precisely control the bit rate and timing of the modulated Tx output signal bits. This control is asserted by the MSK modem with a data clock signal which is output by the modem to pace the Tx data source (e.g. a microcontroller). The data clock signal, in effect, indicates when the Tx data source should provide the next Tx data bit to the modem. See Figure 4. Because this type of interface involves the use of a modem-generated bit clock signal to control the timing of when new Tx data bits must be supplied from the data source, the interface is called synchronous.Another characteristic of a synchronous modem is that, to receive data, it must first learn the data bit timing of the Rx signal stream before it can accurately demodulate Rx data bits. Accordingly, a synchronous modem undergoes a period of training or synchronisation when it first begins to receive a stream of MSK-modulated signal. During this initial receive phase, the received signal is evaluated over several bit times as the modem 'locks-on' and achieves proper receive synchronisation. This training sequence, called a preamble, is a specific data pattern which must be added to the 'front' of a transmit data stream with the start of each new transmission. A specific preamble data pattern (e.g. 16 bits of alternating 0101 .... for the CMX469A) is used to optimise the training accuracy while minimising the number of preamble bits required.Figure 4 Synchronous Transmit OperationNon-synchronous or asynchronous interfaces are commonly found in wired applications which do not have the bandwidth efficiency requirements of wireless systems. A well-known example is the serial port of a personal computer, which can transmit a 1200 bps (or faster) data signal without using an additional data clock signal to control the precise rate and timing of data bits being transmitted to a typical telephone line modem. This is achieved by preceeding the sequence of data bits with a START bit and terminating the sequence of data bits with a STOP bit. The timing of the Rx signal stream can be determined by examining the duration of the START bit to a sufficient accuracy for the reception of a short (usually 8 or 9 bit) sequence of data bits. Popular modem standards, such as ITU V.23 and Bell 202, use FSK signalling to pass such asynchronous serial port data signals over telephone systems.Another aspect of asynchronous interfaces and modems is that they can carry data streams which are not at the exact, nominal data rate. For example, a 1200 bps FSK modem will typically operate properly when supplied with transmit data streams of 1194 to 1206 bps.Because of the differences in synchronous and asynchronous interfaces, they cannot successfully operate if directly connected. In other words, a personal computer's RS232 serial port cannot directly interface to an MSK modem. This is because:• The asynchronous interface may provide data bits too fast or too slow compared to the precise rate required for MSK signalling (a bit rate, or pacing, incompatibility).• The timing of each specific data bit presented by an asynchronous interface will not be aligned with the precise bit timing required for MSK signalling (a bit timing incompatibility).Synchronous and asynchronous interfaces can be successfully interconnected for applications requiring the advantages of both. This typically involves the use of data buffering and retiming circuits to resolve the timing and pacing issues.1.7 Performance Specification1.7.1 Electrical PerformanceAbsolute Maximum RatingsExceeding these maximum ratings can result in damage to the device.Min. Max. Units Supply (V DD - V SS ) -0.3 7.0 V Voltage on any pin to V SS -0.3 V DD + 0.3 VCurrent into or out of V DD and V SS pins -30+30 mA Current into or out of any other pin -20 +20 mAD3 Package Min. Max. Units Total Allowable Power Dissipation at Tamb = 25°C 560 mW ... Derating 5.6 mW/°C Storage Temperature -55 +125 °C Operating Temperature -40 +85 °CE2 Package Min. Max. Units Total Allowable Power Dissipation at Tamb = 25°C 1000 mW ... Derating 10.0 mW/°C Storage Temperature -55 +125 °C Operating Temperature -40 +85 °COperating LimitsCorrect operation of the device outside these limits is not implied.Max.UnitsMin.Notes5.5V2.7Supply (V DD - V SS)Operating Temperature -40 +85 °CXtal Frequency 1 4.028 4.036 MHzNote 1: A Xtal frequency of 1.008MHz (1200/2400 baud only) or 4.032MHz is required for correctoperation. A frequency tolerance of ±0.1% is recommended, but ultimately the tolerance selected willdepend upon system requirements.Operating CharacteristicsFor the following conditions unless otherwise specified:V DD= 2.7V at Tamb = 25°C and V DD= 3.0V to 5.5V at Tamb = −40°C to +85°C,Xtal/Clock Frequency = 4.032MHz, Bit Rate = 1200 baud, Rx Input Level = 300mVrms.UnitsMax.Typ.NotesMin.Static ValuesI DD Rx Enabled, Tx Disabled (V DD = 5.0V) 2 - 3.6 - mAI DD Rx and Tx Enabled (V DD = 5.0V) 2 - 4.5 - mAI DD Rx and Tx Disabled (V DD = 5.0V) 2 - 650 - µAI DD Rx Enabled, Tx Disabled (V DD = 3.0V) 2 - 1.5 - mAI DD Rx and Tx Enabled (V DD = 3.0V) 2 - 2.0 - mAI DD Rx and Tx Disabled (V DD = 3.0V) 2 - 300 - µALogic ‘1’ Level 1 70% - - V DDLogic ‘0’ Level 1 - - 30% V DDDigital Output Impedance - 4.0 - kΩAnalogue and Digital Input Impedance 100 - - kΩTx Output Impedance (V DD = 5.0V) - 0.6 1.0 kΩDynamic ValuesReceiverSignal Input Dynamic Range SNR = 50dB 3, 4 100 230 1000 mVrmsBit Error Rate at SNR = 12dB 4, 5Baud - 2.5 - 10-41200Baud - 1.5 - 10-32400Baud - 1.5 - 10-34800Bit Error Rate at SNR = 20dB 4, 5Baud - <1.0 - 10-81200/2400/4800Receiver Synchronization at SNR = 12dBprobability of bit 16 being correct 7 - 0.995 -Notes Min. Typ. Max. UnitsCarrier Detect3 Sensitivity 1, 7, 8 - - 150 mVrms Probabilty of CD being High after bit 16: with SNR = 12dB 9 0.995 with 230mVrms Noise and No Signal 9 0.05Transmitter OutputTx Output Level 1 - 775 - mVrms Output Level Variation for 1200/1800Hz or 1200/2400Hz or 2400/4800Hz 0 - +/-1.0 dB Output Distortion 10 - 3.0 5.0 % 3rd Harmonic Distortion 10 - 2.0 3.0 % Isochronous Distortion 1200Hz - 1800Hz/1800Hz - 1200Hz - 25.0 40.0 µs 1200Hz - 2400Hz/2400Hz - 1200Hz - 20.0 30.0 µs 2400Hz - 4800Hz/4800Hz - 2400Hz - 10.0 20.0 µs Logic ‘1’ Carrier Frequency 1200 Baud 6 - 1200 - Hz 2400 Baud 6 - 1200 - Hz 4800 Baud 6 - 2400 - Hz Logic ‘0’ Carrier Frequency 1200 Baud 6 - 1800 - Hz 2400 Baud 6 - 2400 - Hz 4800 Baud 6 - 4800 - HzNotes:1. Measured at V DD = 5.0 volts. Signal levels and thresholds are proportional to V DD.2. Excludes any current drawn by external components, but includes current drawn by thecrystal components.3. See Figure 7 (Typical Variation of BER with Input Signal Level).4. SNR = Signal-to-Noise Ratio in the Bit-Rate Bandwidth.5. See Figure 8 (Typical Rx BER vs Signal-to-Noise Ratio).6. Dependent upon Xtal tolerance.7. With an alternating (1010...) pattern.8. Measured with a 150mVrms input signal (no noise).9. A signal level of 230mVrms is used in C.D. probability measurements. Noise bandwidth is5kHz (1200/2400 baud operation) or 8kHz (4800 baud operation). See Section 1.4, Note 2 for details on optimising noise immunity. 10. For an unmodulated carrier.Interface Timing Diagrams1.7.1 Electrical Performance (continued) Interface Timings Notes Min. Typ. Max. Units t ESET Tx Delay, Signal to Disable Time 22.0 - 800 µs t DSET Data Set-Up Time 1 2.0 - - µs t DH Data Hold Time 2.0 - -µs t TXD Tx Delay to O/P Time - 1.2 - µs t TDR Tx Data Rate Period 2 - 833 - µs t RDR Rx Data Rate Period2 800 - 865 µs Undetermined State (see Figure 6) - - 2.0 µs t ID Internal Rx Delay - 1.5 - msNotes: 1. Consider the Xtal/Clock tolerance.2. 1200 Baud example.150200300500700800INPUT SIGNALLEVEL(mVrms)B I T E R R O R R A T E250100501x 10-51x 10-41x 10-31x 10-21x 10-1Figure 7 Typical Variation of Bit Error Rate with Input LevelFigure 8 Typical Rx Bit Error Rate vs Signal-to-Noise Ratio1.7.2 PackagingFigure 9 D3 Mechanical Outline: Order as part no. CMX469AD3Figure 10 E2 Mechanical Outline: Order as part no. CMX469AE2Handling precautions: This product includes input protection, however, precautions should be taken to prevent device damage from electro-static discharge. CML does not assume any responsibility for the use of any circuitry described. No IPR or circuit patent licences are implied. CML reserves the right at any time without notice to change the said circuitry and this product specification. CML has a policy of testing every product shipped using calibrated test equipment to ensure compliance with this product specification. Specific testing of all circuit parameters is not necessarily performed.。

常见频率对应的国际化RFID射频常用协议标准

常见频率对应的国际化RFID射频常用协议标准射频标签的通信标准是标签芯片设计的依据,目前国际上与RFID相关的通信标准主要有:ISO/IEC18000标准(包括7个部分,涉及125KHz、13.56MHz、433MHz、860-96 0MHz、2.45GHz等频段),ISO11785(低频),ISO/IEC14443标准(13.56MHz),ISO/IEC15693标准(13.56MHz)、EPC标准(包括Class0,Class1和GEN2等三种协议,涉及HF和UHF两种频段),DSRC标准(欧洲ETC标准,含5.8GHz)。

现在按频率对一些常用标准做一些简单介绍(并附带介绍一下接触式IC卡的协议标准):1、ISO7816:对接触式IC卡进行了一些规范。

接触式IC卡分逻辑加密卡和存储卡(非加密卡)以及接触式CPU卡:A:逻辑加密卡:可加密存储卡,可以修改芯片相应字节来取得新的密码,如AT88SC102(1 K字节)、AT88SC1608(2KB)、SLE4404(13B)、SLE4406(13B),与FM4406兼容)、SLE55 42(256B)、SLE5528(1KB)、FM4428(1KB)、FM4442(256B)等。

SLE5542的初始密码是6个F,SLE5528的初始密码是4个F.B:非加密卡:也称数据卡,如:AT24C01A、AT24C02、AT24C04、AT24C08、AT24C16、AT24C32、AT24C64、AT24C128、AT24C256、AT45D041等,其中AT45D041为大容量存储卡,存储容量为4M位。

(注:有国产的芯片可以基本代替以上芯片,完全兼容,从外观来区分的话是进口的表面有带ATM的标。

)C:接触式CPU卡:TG56、TG97、TG132等2、125KHz~135KHz:ISO18000-2,对低频识别RFID进行了一些规范。

举例:EM4100和TK4100:是只读低频芯片。

中高频说明书

韩国三荣电子通信公司SAMYUNG ENC注意:请用户使用前务必详阅此说明书。

目 录1 概述-----------------------------2 8 打印机使用---------------------37 1.1 特点-----------------------------2 8.1 DPU-414打印机-----------------37 1.2 基本配置-------------------------2 9 电路---------------------------39 2 特性-----------------------------3 9.1 概述---------------------------39 2.1 技术指标-------------------------3 9.2 电源电路-----------------------39 2.2 中高频发射机---------------------3 9.3 发射电路-----------------------39 2.3 中高频接收机---------------------4 9.4 MF/HF接收电路-----------------39 2.4 DSC控制-------------------------5 9.5 母板(T-550)------------------40 2.5 自动报警-------------------------5 9.6 发射滤波器(T-451)------------40 2.6 中高频控制-----------------------6 9.7 合成器单元(T-553)------------402.7 2.8 数字选择性呼叫(DSC)------------6打印机(DPU-414)----------------69.89.9电源控制(T-555)--------------40功率放大器(T514)-------------413 电源-----------------------------8 9.10 控制(T-557)------------------41 3.1 电源输入-------------------------8 9.11 面板(T-568)------------------41 3.2 交流供电-------------------------8 9.12 值守接收机(T-552)------------41 3.3 直流供电-------------------------8 9.13 接收后板功能示意图-------------42 3.4 电池充电-------------------------84 面板-----------------------------94.1 按钮、旋钮、指示灯说明-----------94.2 液晶显示器----------------------104.3 菜单结构------------------------115 单边带无线电话模式--------------135.1 单边带无线电话模式--------------135.2 单边带菜单显示------------------136 数字选择性呼叫模式--------------176.1 数字选择性呼叫模式选择----------176.2 数字选择性呼叫菜单显示----------177 遇险信号发射--------------------367.1 2182KHz遇险报警信号的发射------367.2 2182KHz遇险报警信号的测试------361、 概述此设备用于自动数字系统通信,包括遇险安全和一般通信,由MF/HF收发机、自动报警系统、数字选择性呼叫组成。

L468中文资料

VF IR IRM trr RthJC

IF = 40 A; TVJ = 25°C TVJ = 125°C VR = VRRM; TVJ = 25°C TVJ = 125°C IF = 75 A; diF /dt = -750 A/µs; TVJ = 125°C VR = 600 V (per diode)

元器件交易网

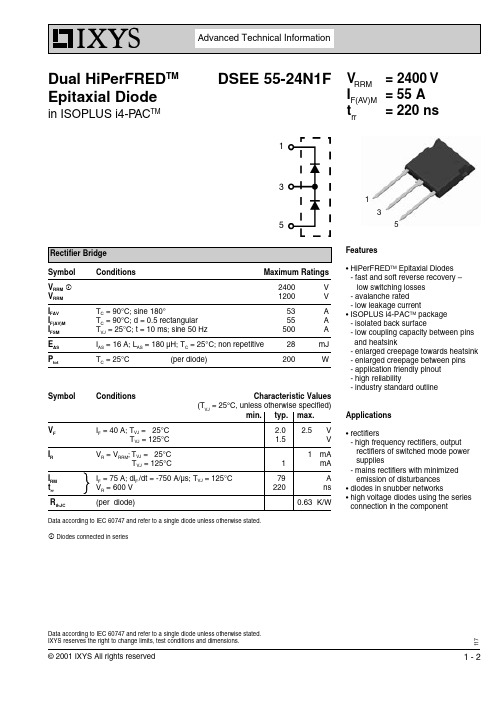

DSEE 55-24N1F

Component Symbol TVJ Tstg VISOL FC Symbol CP d S , dA d S , dA RthCH Weight IISOL ≤ 1 mA; 50/60 Hz mounting force with clip Conditions coupling capacity between shorted pins and mounting tab in the case pin - pin pin - backside metal with heatsink compound 5.5 5.5 0.15 9 Conditions Maximum Ratings -55...+150 -55...+125 2500 20...120 °C °C V~ N Dimensions in mm (1 mm = 0.0394")

元器件交易网

Advanced Technical Information

Dual HiPerFREDTM Epitaxial Diode

in ISOPLUS i4-PACTM

DSEE 55-24N1F

VRRM = 2400 V IF(AV)M = 55 A trr = 220 ns

1

3

1 3

5

Rectifier Bridge Symbol VRRM VRRM IFAV IF(AV)M IFSM EAS Ptot TC = 90°C; sine 180° TC = 90°C; d = 0.5 rectangular TVJ = 25°C; t = 10 ms; sine 50 Hz IAS = 16 A; LAS = 180 µH; TC = 25°C; non repetitive TC = 25°C (per diode) Conditions Maximum Ratings 2400 1200 53 55 500 28 200 V V A A A mJ W Features

cd4069中文资料_数据手册_参数

NS 14 2000 Green (RoHS & no Sb/Br)

CU NIPDAU

Level-1-260C-UNLIM -55 to 125

NS 14 2000 Green (RoHS & no Sb/Br)

CU NIPDAU

Level-1-260C-UNLIM -55 to 125

PW

14

90 Green (RoHS

(5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

ACTIVE TSSOP

ACTIVE

CDIP

D

14

50 Green (RoHS

& no Sb/Br)

CU NIPDAU

Level-1-260C-UNLIM -55 to 125

D

14 2500 Green (RoHS CU NIPDAU | CU SN Level-1-260C-UNLIM -55 to 125

Copyright 2003, Texas Instruments Incorporated

PACKAGE OPTION ADDENDUM

AT24C512B_08中文资料

AT24C512B_08中文资料FeaturesLow-voltage and Standard-voltage Operation–1.8v (V CC = 1.8V to 3.6V)–2.5v (V CC = 2.5V to 5.5V)?Internally Organized 65,536 x 8?Two-wire Serial InterfaceSchmitt Triggers, Filtered Inputs for Noise Suppression ?Bidirectional Data Transfer Protocol1 MHz (2.5V , 5.5V), 400 kHz (1.8V) CompatibilityWrite Protect Pin for Hardware and Software Data Protection ?128-byte Page Write Mode (Partial Page Writes Allowed)?Self-timed Write Cycle (5 ms Max)?High Reliability–Endurance: 1,000,000 Write Cycles –Data Retention: 40 Years ?Lead-free/Halogen-free Devices8-lead PDIP , 8-lead JEDEC SOIC, 8-lead EIAJ SOIC, 8-lead TSSOP , 8-ball dBGA2, and 8-lead Ultra Thin Small Array (SAP) PackagesDie Sales: Wafer Form, Waffle Pack and Bumped DieDescriptionThe AT24C512B provides 524,288 bits of serial electrically erasable and programma-ble read only memory (EEPROM) organized as 65,536 words of 8 bits each. The device’s cascadable feature allows up to eight devices to share a common two-wire bus. The device is optimized for use in many industrial and commercial applications where low-power and low-voltage operation are essential. The devices are available in space-saving 8-pin PDIP, 8-lead JEDEC SOIC, 8-lead EIAJ SOIC, 8-lead TSSOP,8-ball dBGA2 and 8-lead Ultra Thin SAP packages. In addition, the entire family is available in 1.8V (1.8V to 3.6V) and 2.5V (2.5V to 5.5V) versions.T able 0-1.Pin ConfigurationsPin Name Function A0–A2Address Inputs SDA Serial Data SCL Serial Clock Input WPWrite ProtectRev. 5297A–SEEPR–1/08Two-wire Serial EEPROM512K (65,536 x 8)AT24C512Bwith Three Device Address Inputs8-lead PDIP8-lead TSSOPBottom View8-lead SOIC8-ball dBGA2Bottom View25297A–SEEPR–1/08AT24C512BFigure 0-1.Block Diagram Absolute Maximum Ratings*Operating T emperature..................................–55°C to +125°C *NOTICE:Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent dam-age to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.Storage T emperature.....................................–65°C to +150°C Voltage on Any Pinwith Respect to Ground....................................–1.0V to +7.0V Maximum Operating Voltage ..........................................6.25V DC Output Current........................................................5.0 mA35297A–SEEPR–1/08AT24C512B1.Pin DescriptionSERIAL CLOCK (SCL): The SCL input is used to positive edge clock data into each EEPROM device and negative edge clock data out of each device.SERIAL DATA (SDA): The SDA pin is bidirectional for serial data transfer. This pin is open-drain driven and may be wire-ORed with any number of other open-drain or open collector devices.DEVICE/PAGE ADDRESSES (A2, A1, A0): The A2, A1, and A0 pins are device address inputs that are hardwired (directly toGND or to Vcc) for compatibility with other AT24Cxx devices.When the pins are hardwired, as many as eight 512K devices may be addressed on a single bus system. (Device addressing is discussed in detail under “Device Addressing,” page 8.) A device is selected when a corresponding hardware and software match is true. If these pins are left floating, the A2, A1, and A0 pins will be internally pulled down to GND. However, due to capaci-tive coupling that may appear during customer applications, Atmel ? recommends always connecting the address pins to a known state. When using a pull-up resistor, Atmel recommends using 10k Ω or less.WRITE PROTECT (WP): The write protect input, when connected to GND, allows normal write operations. When WP is connected directly to Vcc, all write operations to the memory are inhib-ited. If the pin is left floating, the WP pin will be internally pulled down to GND. However, due to capacitive coupling that may appear during customer applications, Atmel recommends always connecting the WP pins to a known state. When using a pull-up resistor, Atmel rec ommends using 10k Ω or less.45297A–SEEPR–1/08AT24C512B2.Memory OrganizationAT24C512B, 512K SERIAL EEPROM: The 512K is internally organized as 512 pages of 128-bytes each. Random word addressing requires a 16-bit data word address.Note:1.This parameter is characterized and is not 100% tested.Note:1.V IL min and V IH max are reference only and are not tested.Table 2-1.Pin Capacitance (1)Applicable over recommended operating range from: T A = 25°C, f = 1.0 MHz, V CC = +1.8V to +5.5VSymbol Test ConditionMax Units Conditions C I/O Input/Output Capacitance (SDA)8pF V I/O = 0V C IN Input Capacitance (A 0, A 1, SCL) 6pFV IN = 0VTable 2-2.DC CharacteristicsApplicable over recommended operating range from: T AI = –40°C to +85°C, V CC = +1.8V to +5.5V (unless otherwise noted) Symbol Parameter Test ConditionMin TypMax Units V CC1Supply Voltage 1.8 3.6V V CC2Supply Voltage 2.55.5V I CC Supply Current V CC = 5.0V READ at 400 kHz 2.0mAI CC Supply Current V CC = 5.0V WRITE at 400 kHz 3.0mA I SB1Standby CurrentV CC = 1.8V V IN = V CC or V SS1.0μA V CC = 3.6V 3.0μA I SB2Standby Current V CC =2.5V V IN = V CC or V SS2.0μA V CC = 5.5V 6.0μA I LI Input Leakage Current V IN = V CC or V SS 0.10 3.0μA I LO Output Leakage CurrentV OUT = V CC or V SS0.053.0μA V IL Input Low Level (1)–0.6V CC x 0.3V V IH Input High Level (1)V CC x 0.7V CC + 0.5V V OL1Output Low Level V CC = 1.8V I OL = 0.15 mA 0.2V V OL2Output Low LevelV CC = 3.0VI OL = 2.1 mA 0.4V55297A–SEEPR–1/08AT24C512BNotes:1.This parameter is ensured by characterization only.2.AC measurement conditions:R L (connects to V CC ): 1.3 k Ω (2.5V , 5V), 10 k Ω (1.8V)Input pulse voltages: 0.3 V CC to 0.7 V CC Input rise and fall times: ≤ 50 nsInput and output timing reference voltages: 0.5 V CCTable 2-3.AC Characteristics (Industrial Temperature)Applicable over recommended operating range from T AI = ?40°C to +85°C, V CC = +1.8V to +5.5V, CL = 100 pF (unless oth-erwise noted). Test conditions are listed in Note 2.Symbol Parameter1.8-volt2.5, 5.0-volt Units MinMax MinMax f SCL Clock Frequency, SCL 4001000kHz t LOW Clock Pulse Width Low 1.30.4μs t HIGH Clock Pulse Width High 0.60.4μs t i Noise Suppression Time (1)10050ns t AA Clock Low toData Out Valid 0.050.90.050.55μs t BUF Time the bus must be free before a new transmission can start (1) 1.30.5μs t HD.ST A Start Hold Time 0.60.25μs t SU.ST A Start Set-up Time 0.60.25μs t HD.DA T Data In Hold Time 00μs t SU.DAT Data In Set-up Time 100 100ns t R Inputs Rise Time (1)0.30.3μs t F Inputs Fall Time (1)300 100ns t SU.STO Stop Set-up Time 0.60.25μs t DH Data Out Hold Time 5050ns t WRWrite Cycle Time 55ms Endurance (1)25°C, Page Mode, 3.3V1,000,000Write Cycles65297A–SEEPR–1/08AT24C512B3.Device OperationCLOCK and DATA TRANSITIONS: The SDA pin is normally pulled high with an external device.Data on the SDA pin may change only during SCL low time periods (see Figure 3-4 on page 8).Data changes during SCL high periods will indicate a start or stop condition as defined below.START CONDITION: A high-to-low transition of SDA with SCL high is a start condition which must precede any other command (see Figure 3-5 on page 8).STOP CONDITION: A low-to-high transition of SDA with SCLhigh is a stop condition. After a read sequence, the stop command will place the EEPROM in a standby power mode (see Fig-ure 3-5 on page 8).ACKNOWLEDGE: All addresses and data words are serially transmitted to and from the EEPROM in 8-bit words. The EEPROM sends a zero during the ninth clock cycle to acknowl-edge that it has received each word.STANDBY MODE: The AT24C512B features a low power standby mode which is enabled: a)upon power-up and b) after the receipt of the STOP bit and the completion of any internal operations.Software Reset: After an interruption in protocol, power loss or system reset, any 2-wire part can be protocol reset by following these steps: (a) Create a start bit condition, (b)clock 9 cycles, (c) create another start bit followed by stop bit condition as shown below.The device is ready for next communication after above steps have been completed.Figure 3-1.Protocol Reset Condition75297A–SEEPR–1/08AT24C512BFigure 3-3.Write Cycle Timing (SCL: Serial Clock, SDA: Serial Data I/O)Note:1.The write cycle time t WRis the time from a valid stop condition of a write sequence to the end of the internal clear/write cycle.85297A–SEEPR–1/08AT24C512BFigure 3-4.Data ValidityFigure 3-5.Start and Stop DefinitionFigure 3-6.Output Acknowledge95297A–SEEPR–1/08AT24C512B4.Device AddressingThe 512K EEPROM requires an 8-bit device address word following a start condition to enable the chip for a read or write operation (see Figure 6-1 on page 10). The device address word con-sists of a mandatory “1”, “0” sequence for the f irst four most significant bits as shown. This is common to all two-wire EEPROM devices.The 512K uses the three device address bits A2, A1, A0 to allow as many as eight devices on the same bus. These bits must compare to their corresponding hardwired input pins. The A2, A1and A0 pins use an internal proprietary circuit that biases them to a logic low condition if the pins are allowed to float.The eighth bit of the device address is the read/writeoperation select bit. A read operation is ini-tiated if this bit is high and a write operation is initiated if this bit is low.Upon a compare of the device address, the EEPROM will output a “0”. If a compare is not made,the device will return to a standby state.DATA SECURITY: The AT24C512B has a hardware data protection scheme that allows the user to Write Protect the whole memory when the WP pin is at V CC .5.Write OperationsBYTE WRITE: A write operation requires two 8-bit data word addresses following the device address word and acknowledgment. Upon receipt of this address, the EEPROM will again respond with a “0” and then clock in the first 8-bit data word. Following receipt of the 8-bit data word, the EEPROM will output a “0”. The addressing device, such as a microcontroller, then must terminate the write sequence with a stop condition. At this time the EEPROM enters an internally-timed write cycle, t WR , to the nonvolatile memory. All inputs are disabled during this write cycle and the EEPROM will not respond until the write is complete (see Figure 6-2 on page 10).PAGE WRITE: The 512K EEPROM is capable of 128-byte page writes.A page write is initiated the same way as a byte write, but the microcontroller does not send a stop condition after the first data word is clocked in. Instead, after the EEPROM acknowledges receipt of the first data word, the microcontroller can transmit up to 127 more data words. The EEPROM will respond with a “0” after each data word received. The microcontroller must termi-nate the page write sequence with a stop condition (see Figure 6-3 on page 11).The data word address lower 7 bits are internally incremented following the receipt of each data word. The higher data word address bits are not incremented, retaining the memory page row location. When the word address, internally generated, reaches the page boundary, the follow-ing byte is placed at the beginning of the same page. If more than 128 data words are transmitted to the EEPROM, the data word address will “roll over” and previous data will be overwritten. The address roll over during write is from the last byte of the current page to the first byte of the same page.ACKNOWLEDGE POLLING: Once the internally-timed write cycle has started and the EEPROM inputs are disabled, acknowledge polling can be initiated. This involves sending a start condition followed by the device address word. The Read/Write bit is representative of the operation desired. Only if the internal write cycle has completed will the EEPROM respond with a “0”, allowing the read or write sequence to continue.105297A–SEEPR–1/08AT24C512B6.Read OperationsRead operations are initiated the same way as write operations with the exception that the Read/Write select bit in the device address word is set to “1”. There are three read operations:current address read, random address read and sequential read.CURRENT ADDRESS READ: The internal data word address counter maintains the last address accessed during the last read or write operation, incremented by “1”. This address stays validbetween operations as long as the chip power is maintained. The address roll over during read is from the last byte of the last memory page, to the first byte of the first page.Once the device address with the Read/Write select bit set to “1” is clocked in and acknowl-edged by the EEPROM, the current address data word is serially clocked out. The microcontroller does not respond with an input “0” but does generate a following stop condition (see Figure 6-4 on page 11).RANDOM READ: A random read requires a “dummy” byte write sequence to load in the data word address. Once the device address word and data word address are clocked in and acknowledged by the EEPROM, the microcontroller must generate another start condition. The microcontroller now initiates a current address read by sending a device address with the Read/Write select bit high. The EEPROM acknowledges the device address and serially clocks out the data word. The microcontroller does not respond with a “0” but does generate a following stop condition (see Figure 6-5 on page 11).SEQUENTIAL READ: Sequential reads are initiated by either a current address read or a ran-dom address read. After the microcontroller receives a data word, it responds with an acknowledge. As long as the EEPROM receives an acknowledge, it will continue to increment the data word address and serially clock out sequential data words. When the memory address limit is reached, the data word address will roll over and the sequential read will continue. The sequential read operation is terminated when the micr ocontroller does not respond with a “0” but does generate a following stop condition (see Figure 6-6 on page 11).Figure 6-1.Device AddressFigure 6-2.Byte Write115297A–SEEPR–1/08AT24C512BFigure 6-3.Page WriteFigure 6-4.Current Address ReadFigure 6-5.Random ReadFigure 6-6.Sequential Read125297A–SEEPR–1/08AT24C512BNotes: 1.“-B” denotes bulk2.“-T” denotes tape and reel. SOIC = 4K per reel. TSSOP and dBGA2 = 5K per reel. SAP = 3K per reel. EIAJ = 2K per reel.3.Available in tape and reel, and wafer form; order as SL788 for inkless wafer form. Bumped die available upon request.Please contact Serial Interface Marketing.Ordering InformationOrdering CodeVoltage Package Operation RangeA T24C512B-PU (Bulk form only) 1.88P3Lead-free/Halogen-free/Industrial Temperature (–40°C to 85°C)A T24C512B-PU25 (Bulk form only) 2.58P3A T24C512BN-SH-B (1) (NiPdAu Lead Finish) 1.88S1A T24C512BN-SH-T (2) (NiPdAu Lead Finish) 1.88S1A T24C512BN-SH25-B (1) (NiPdAu Lead Finish) 2.58S1A T24C512BN-SH25-T (2) (NiPdAu Lead Finish) 2.58S1A T24C512BW-SH-B (1) (NiPdAu Lead Finish) 1.88S2A T24C512BW-SH-T (2) (NiPdAu Lead Finish) 1.88S2A T24C512BW-SH25-B (1) (NiPdAu Lead Finish) 2.58S2A T24C512BW-SH25-T (2) (NiPdAu Lead Finish) 2.58S2A T24C512B-TH-B (1) (NiPdAu Lead Finish) 1.88A2A T24C512B-TH-T (2) (NiPdAu Lead Finish) 1.88A2A T24C512B-TH25-B (1) (NiPdAu Lead Finish) 2.58A2A T24C512B-TH25-T (2) (NiPdAu Lead Finish) 2.58A2A T24C512BY7-YH-T (2) (NiPdAu Lead Finish) 1.88Y7A T24C512BY7-YH25-T (2) (NiPdAu Lead Finish) 2.58Y7A T24C512BU2-UU-T (2) 1.88U2-1A T24C512B-W-11(3)1.8Die SaleIndustrial Temperature (–40°C to 85°C)Package Type8P38-lead, 0.300" Wide, Plastic Dual In-line Package (PDIP) 8S18-lead, 0.150” Wide, Plastic Gull Wing Small Outline Package (JEDEC SOIC)8S28-lead, 0.200” Wide Plastic Gull Wing Small Outline Package (EIAJ SOIC)8A28-lead, 4.4 mm Body, Plastic Thin Shrink Small Outline Package (TSSOP)8Y78-lead, 6.00 mm x 4.90 mm Body, Ultra Thin, Dual Footprint, Non-leaded, Small Array Package (SAP)8U2-1 8-ball, die Ball Grid Array Package (dBGA2)Options–1.8Low-voltage (1.8V to 3.6V)–2.5Low-voltage (2.5V to 5.5V)135297A–SEEPR–1/08AT24C512B7.Part marking scheme:7.18-PDIP(1.8V)7.28-PDIP(2.5V)TOP MARKSeal YearY = SEAL YEARWW = SEAL WEEK | Seal Week6: 2006 0: 2010 02 = Week 2 | | |7: 2007 1: 2011 04 = Week 4 |---|---|---|---|---|---|---|---| 8: 2008 2: 2012 :: : :::: : A T M L U Y W W 9: 2009 3: 2013 :: : :::: :: |---|---|---|---|---|---|---|---| 50 = Week 50 2 F B 152 = Week 52|---|---|---|---|---|---|---|---| * Lot NumberLot Number to Use ALL Characters in Marking |---|---|---|---|---|---|---|---| |BOTTOM MARKPin 1 Indicator (Dot)No Bottom MarkTOP MARKSeal YearY = SEAL YEARWW = SEAL WEEK | Seal Week6: 2006 0: 2010 02 = Week 2 | | |7: 2007 1: 2011 04 = Week 4 |---|---|---|---|---|---|---|---| 8: 2008 2: 2012 :: : :::: : A T M L U Y W W 9: 2009 3: 2013 :: : :::: :: |---|---|---|---|---|---|---|---| 50 = Week 50 2 F B 252 = Week 52|---|---|---|---|---|---|---|---| * Lot NumberLot Number to Use ALL Characters in Marking |---|---|---|---|---|---|---|---| |BOTTOM MARKPin 1 Indicator (Dot)No Bottom Mark145297A–SEEPR–1/08AT24C512B7.38-SOIC(1.8V)7.48-SOIC(2.5V)TOP MARKSeal YearY = SEAL YEARWW = SEAL WEEK | Seal Week6: 2006 0: 2010 02 = Week 2 | | |7: 2007 1: 2011 04 = Week 4 |---|---|---|---|---|---|---|---| 8: 2008 2: 2012 :: : :::: : A T M L H Y W W 9: 2009 3: 2013 :: : :::: :: |---|---|---|---|---|---|---|---| 50 = Week 50 2 F B 152 = Week 52|---|---|---|---|---|---|---|---| * Lot NumberLot Number to Use ALL Characters in Marking |---|---|---|---|---|---|---|---| |BOTTOM MARKPin 1 Indicator (Dot)No Bottom MarkTOP MARKSeal YearY = SEAL YEARWW = SEAL WEEK | Seal Week6: 2006 0: 2010 02 = Week 2 | | |7: 2007 1: 2011 04 = Week 4 |---|---|---|---|---|---|---|---| 8: 2008 2: 2012 :: : :::: : A T M L H Y W W 9: 2009 3: 2013 :: : :::: :: |---|---|---|---|---|---|---|---| 50 = Week 50 2 F B 252 = Week 52|---|---|---|---|---|---|---|---| * Lot NumberLot Number to Use ALL Characters in Marking |---|---|---|---|---|---|---|---| |BOTTOM MARKPin 1 Indicator (Dot)No Bottom Mark155297A–SEEPR–1/08AT24C512B7.58-TSSOP(1.8V)7.68-TSSOP(2.5V)TOP MARKPin 1 Indicator (Dot)Y = SEAL YEAR WW = SEAL WEEK |6: 2006 0: 2010 02 = Week 2 |---|---|---|---| 7: 2007 1: 2011 04 = Week 4 * H Y W W 8: 2008 2: 2012 :: : :::: : |---|---|---|---|---| 9: 2009 3: 2013:: : :::: :: 2 F B 1 * 50 = Week 50|---|---|---|---|---|52 = Week 52BOTTOM MARK|---|---|---|---|---|---|---|Country of originC 0 0|---|---|---|---|---|---|---| A A A A A A A |---|---|---|---|---|---|---| <- Pin 1 IndicatorTOP MARKPin 1 Indicator (Dot)Y = SEAL YEAR WW = SEAL WEEK |6: 2006 0: 2010 02 = Week 2 |---|---|---|---| 7: 2007 1: 2011 04 = Week 4 * H Y W W 8: 2008 2: 2012 :: : :::: : |---|---|---|---|---| 9: 2009 3: 2013:: : :::: :: 2 F B 2 * 50 = Week 50 |---|---|---|---|---| 52 = Week 52BOTTOM MARK|---|---|---|---|---|---|---|Country of originC 0 0|---|---|---|---|---|---|---| A A A A A A A |---|---|---|---|---|---|---| <- Pin 1 Indicator165297A–SEEPR–1/08AT24C512B7.78-Ultra Thin SAP (1.8V)7.88-Ultra Thin SAP (2.5V)TOP MARKSeal Year| Seal Week Y = SEAL YEARWW = SEAL WEEK | | |6: 2006 0: 2010 02 = Week 2 |---|---|---|---|---|---|---|---| 7: 2007 1: 2011 04 = Week 4 A T M L H Y W W 8: 2008 2: 2012 :: : :::: : |---|---|---|---|---|---|---|---| 9: 2009 3: 2013:: : :::: :: 2 F B 150 = Week 50 |---|---|---|---|---|---|---|---| 52 = Week 52Lot Number|---|---|---|---|---|---|---|---| * |Pin 1 Indicator (Dot)TOP MARKSeal Year| Seal Week Y = SEAL YEARWW = SEAL WEEK | | |6: 2006 0: 2010 02 = Week 2 |---|---|---|---|---|---|---|---| 7: 2007 1: 2011 04 = Week 4 A T M L H Y W W 8: 2008 2: 2012 :: : :::: : |---|---|---|---|---|---|---|---| 9: 2009 3: 2013:: : :::: :: 2 F B 250 = Week 50 |---|---|---|---|---|---|---|---| 52 = Week 52Lot Number|---|---|---|---|---|---|---|---| * |Pin 1 Indicator (Dot)175297A–SEEPR–1/08AT24C512B7.8dBGA2TOP MARKLINE 1-------> 2FBU LINE 2-------> YMTC|<-- Pin 1 This Corner P = Country of OriginY = ONE DIGIT YEAR CODE 4: 2004 7: 20075: 2005 8: 20086: 2006 9: 2009M = SEAL MONTH (USE ALPHA DESIGNATOR A-L) A = JANUARY B = FEBRUARY " " """"""" J = OCTOBER K = NOVEMBERL = DECEMBERTC = TRACE CODE (ATMEL LOT NUMBERS TO CORRESPOND WITH ATK TRACE CODE LOG BOOK)188.Package Information U2-1 - dBGA2195297A–SEEPR–1/08AT24C512B8P3 – PDIP。

常用三极管参数大全

玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理。

C8991资料

GENERALFEATURESSPECIFICATIONS ParameterDescription/ValueUnit Output High Voltage Range Input Voltage RangeControl Voltage / Output Voltage Ratio Control Voltage Range Settling Time AOutput Signal ModeOperating Ambient Temperature B Storage Temperature B WeightI Compact and LightweightI Low Power Consumption (8 mA Max., without signal output)I Wide Output LinearityI No Handling of High Voltage I Easy Handling-200 to -1200+11.5 to +15.51 : 103+0.2 to +1.210Current output 0 to +50-15 to +60Approx. 71V V —V s —°C °C gCHARACTERISTlCS (at +25 °C, -1000 V)DP TYPE SOCKET ASSEMBLYFOR 28 mm(1-1/8 INCH) SIDE-ON PHOTOMULTIPLIER TUBEC8991MAXIMUM RATINGS (Absolute Maximum Values)ParameterValue Output High Voltage Supply Voltage Control Voltage-1200+18+1.2V V VUnit ParameterValue Input Current (Without signal input)Temperature Coefficient (+20 °C to +40 °C)Anode Ripple Interference CLinear DC Output Current of PMT DTyp.Max.Max.Typ.80.0050.011100mA %/°C %/°C mV µAUnit C R L = 1 M Ω, C L = 25 pFD Within ±0.5 % linearityNOTE:A The time required for the output to reach a stable level following a change in the control voltage from +1.0 V to +0.5 V.B No condensation.NOTE:High Voltage Power Supply and Divider Assemblyfor Standard 28 mm (1-1/8 inch) Side-on Photomultiplier TubeThe C8991 is a compact and lightweight socket assembly incorpor-ating a socket, voltage divider circuit and high voltage power supply designed for use with 28 mm(1-1/8") side-on type photomultiplier tube. It features low power consumption and superior output linearity comparing with conventional socket assemblies. In addition, it allows easy handling to operate with +15 V input voltage and connecting to a potentiometer or a +0.2 V to +1.2 V for output voltage adjustments.FEB. 2004Information furnished by HAMAMATSU is believed to be reliable. However, no responsibility is assumed for possible inaccuracies or omissions. Specifications are subject to change without notice. No patent rights are granted to any of the circuits described herein. ©2004 Hamamatsu Photonics K.K.Subject to local technical requirements and regulations, availability of products included in this promotional material may vary. Please consult with our sales office.* HV cont. Input: Impedance of 1 M ΩDP TYPE SOCKET ASSEMBLY C8991TACC1027E02FEB. 2004 IPTACCB0008EATACCC0117EATACCA0053EDFigure 1: Control Voltage/Output Voltage CharacteristicsFigure 2: Sensitivity Adjustment MethodeFigure 3: Dimensional Outline (Unit: mm)CONTROL VOLTAGE (V)+0.2+0.6+1.2O U T P U T V O L T A G E (V )-200-400+0.4+0.8+1.0-600-800-1000-12001)1)VOLTAGE PROGRAMMINGRESISTANCE PROGRAMMINGhigh voltage output.*The case is internally connected to black (GND) wire.Top ViewSide ViewHOUSING DIRECTION OF LIGHTSIGNAL OUTPUT +15 V INPUTHV CONTROL INPUT Vref OUTPUT GROUNDCOAX RG-174/U AWG 22, RED AWG 22, WHITE AWG 22, BLUE AWG 22, BLACKHAMAMATSU PHOTONICS K.K., Electron Tube Division314-5, Shimokanzo, Toyooka-village, Iwata-gun, Shizuoka-ken, 438-0193, Japan, Telephone: (81)539/62-5248, Fax: (81)539/62-2205U.S.A.: Hamamatsu Corporation: 360 Foothill Road, P. O. Box 6910, Bridgewater. N.J. 08807-0910, U.S.A., Telephone: (1)908-231-0960, Fax: (1)908-231-1218 E-mail: usa@Germany: Hamamatsu Photonics Deutschland GmbH: Arzbergerstr. 10, D-82211 Herrsching am Ammersee, Germany, Telephone: (49)8152-375-0, Fax: (49)8152-2658 E-mail: info@hamamatsu.deFrance: Hamamatsu Photonics France S.A.R.L.: 8, Rue du Saule Trapu, Parc du Moulin de Massy, 91882 Massy Cedex, France, Telephone: (33)1 69 53 71 00, Fax: (33)1 69 53 71 10 E-mail: infos@hamamatsu.frUnited Kingdom: Hamamatsu Photonics UK Limited: 2 Howard Court, 10 Tewin Road Welwyn Garden City Hertfordshire AL7 1BW, United Kingdom, Telephone: 44-(0)1707-294888, Fax: 44(0)1707-325777 E-mail: info@ North Europe: Hamamatsu Photonics Norden AB: Smidesv ägen 12, SE-171-41 SOLNA, Sweden, Telephone: (46)8-509-031-00, Fax: (46)8-509-031-01 E-mail: info@hamamatsu.se Italy: Hamamatsu Photonics Italia: S.R.L.: Strada della Moia, 1/E, 20020 Arese, (Milano), Italy, Telephone: (39)02-935 81 733, Fax: (39)02-935 81 741 E-mail: info@hamamatsu.itWEB SITE 。

MP4689_r1.01

1

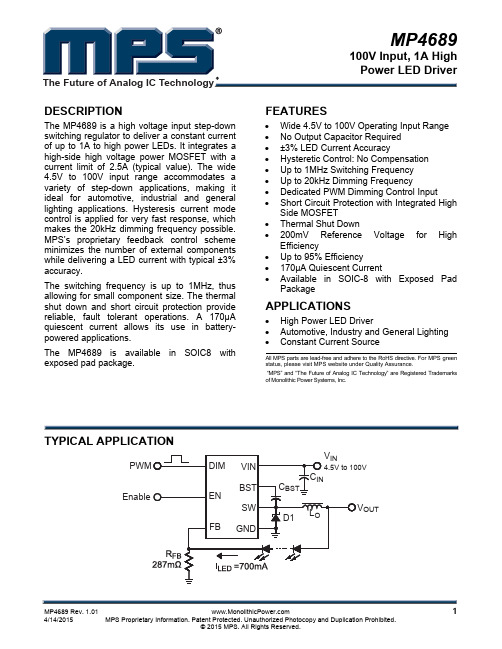

MP4689 – 100V INPUT, 1A HIGH POWER LED DRIVER

ORDERING INFORMATION

Part Number* MP4689DN Package SOIC-8 EP Top Marking MP4689

* For Tape & Reel, add suffix –Z (e.g. MP4689DN–Z); For RoHS compliant packaging, add suffix –LF (e.g. MP4689DN–LF–Z)

2

MP4689 – 100V INPUT, 1A HIGH POWER LED DRIVER

ELECTRICAL CHARACTERISTICS

VIN = 60V, TA= +25C, unless otherwise noted. Specifications over temperature are guaranteed by design and characterization.

MP4689 Rev. 1.01 4/14/2015

MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2015 MPS. All Rights Reserved.

FEATURES

Wide 4.5V to 100V Operating Input Range No Output Capacitor Required ±3% LED Current Accuracy Hysteretic Control: No Compensation Up to 1MHz Switching Frequency Up to 20kHz Dimming Frequency Dedicated PWM Dimming Control Input Short Circuit Protection with Integrated High Side MOSFET Thermal Shut Down 200mV Reference Voltage for High Efficiency Up to 95% Efficiency 170μA Quiescent Current Available in SOIC-8 with Exposed Pad Package High Power LED Driver Automotive, Industry and General Lighting Constant Current Source

CPU卡常用芯片的主要特性参数

CPU卡常用芯片的主要特性参数联合智能卡编辑 CPU卡常用芯片的主要特性参数:芯片名:SLE44C20S;产品描述:保密控制器;时钟/MHz:1~5;工作电压/V:2.7~5.5;编程电:内部;最大供电电流/mA:8;最大电流消耗/μA:100;CPU:8 B;加密协处理器:无;用户ROM区:7 KB;PROM:32 B;EEPROM:1 KB;RAM:256 B;写/擦除时间/ms:3.6/1.8;EEPROM页式编程:1~8 B;基于芯片的保密特性:固件(CMS)+硬件;由软件实现的基于应用程序的保密特性:对称算法(例如DES算法);写/擦除次数/次:≥500 000 ;数据保持/年:≥10。

芯片名:SLE44CR42S;产品描述:加密控制器;时钟/MHz:1~5;工作电压/V:2.7~5.5;编程电:内部;最大供电电流/mA:10;最大电流消耗/μA:100;CPU:8 B;加密协处理器:540 bit算法;用户ROM区:14 KB;PROM:32 B;EEPROM:4KB;RAM:256 B+350 B;写/擦除时间/ms:3.6/1.8;EEPROM页式编程:1~32B;基于芯片的保密特性:固件(CMS)+硬件;由软件实现的基于应用程序的保密特性:对称算法(例如DES算法),硬件支持的非对称算法(例如RSA 算法);写/擦除次数/次:≥500 000;数据保持/年:≥10。

芯片名:SLE66C160S;产品描述:保密控制器;时钟/MHz:1~5;工作电压/V:2.7~5.5;编程电:内部;最大供电电流/mA:5;最大电流消耗/μA:100;CPU:16 B;加密协处理器:无;用户ROM 区:31.5KB;PROM:32 B;EEPROM:16KB;RAM:1280B;写/擦除时间/ms:3.6/1.8;EEPROM页式编程:1~64B;基于芯片的保密特性:固件(CMS)+硬件;由软件实现的基于应用程序的保密特性:对称算法(例如DES算法);写/擦除次数/次:≥500 000;数据保持/年:≥10。

C3589资料

Subject to local technical requirements and regulations, availability of products included in this promotional material may vary. Please consult with our sales office. lnformation furnished by HAMAMATS U is believed to be reliabIe. However, no responsibility is assumed for possibIe inaccuracies or ommissions. Specifications are subject to change without notice. No patent right are granted to any of the circuits described herein. © 1997 Hamamatsu Photonics K.K.

U.S.A.: Hamamatsu Corporation: 360 Foothill Road, Bridgewater. N.J. 08807-0910, U.S.A., Telephone: (1)908-231-0960, Fax: (1)908-231-1218 Germany: Hamamatsu Photonics Deutschland GmbH: Arzbergerstr. 10, D-82211 Herrsching am Ammersee, Germany, Telephone: (49)8152-375-0, Fax: (49)8152-2658 France: Hamamatsu Photonics France S.A.R.L.: 8, Rue du Saule Trapu, Parc du Moulin de Massy, 91882 Massy Cedex, France, Telephone: (33)1 69 53 71 00, Fax: (33)1 69 53 71 10 United Kingdom: Hamamatsu Photonics UK Limted: Lough Point, 2 Gladbeck Way, Windmill Hill, Enfield, Middlesex EN2 7JA, United Kingdom, Telephone: (44)181-367-3560, Fax: (44)181-367-6384 North Europe: Hamamatsu Photonics Norden AB: Färögatan 7, S-164-40 Kista Sweden, Telephone: (46)8-703-29-50, Fax: (46)8-750-58-95 Italy: Hamamatsu Photonics Italia: S.R.L.: Via Della Moia, 1/E, 20020 Arese, (Milano), Italy, Telephone: (39)2-935 81 733, Fax: (39)2-935 81 741

GR-468-CORE中文版

能力有限,翻译的不恰当的地方,请多多见谅(仅供个人学习,请勿商用)

Happy_Fei

3.1.4.2 活化能量……………………………………………………………… 33 3.1.4.3 与多重失效机理相关的附加考虑因素……………………………… 33 3.2 特性测试程序…………………………………………………………………… 34 3.2.1 光谱特性 ……………………………………………………………………… 34 3.2.1.1 MLM激光器的光谱特性………………………………………………35 3.2.1.2 SLM 激光器的光谱特性………………………………………………36 3.2.1.2.1 连续波激光器的考虑因素………………………………… 37 3.2.1.2.2 WDM激光器的考虑因素(略) 3.2.1.2.3 可调激光器的考虑因素(略) 3.2.1.2.4 高比特率应用的考虑因素………………………………… 37 3.2.1.3 LEDs的光谱特性………………………………………………37 3.2.2 输出功率/驱动电流特性…………………………………………………… 38 3.2.2.1 一般输出功率和L-I曲线测量考虑因素(略) 3.2.2.2 激光门槛电流……………………………………………………… 38 3.2.2.3 激光门槛电流的温度灵敏度……………………………………… 38 3.2.2.4 特定电流水平的输出功率水平 3. 2 .2. 4. 1 门槛电流的激光输出功率(略) 3.2.2.4.2 LED输出功率………………………………………39 3.2.2.5 激光L-I曲线的线性度…………………………………………………39 3.2.2.5.1 整体线性度…………………………………………………39 3.2.2.5.2 拐点……………………………………………………… 39 3.2.2.5.3 饱和度(略) 3.2.2.6 激光器的斜效率……………………………………………………… 40 3.2.2.7 相对强度噪声……………………………………………………… 40 3.2.2.8 EELED高效发光………………………………………………………40 3.2.2.9 EELED激光发射的门槛值……………………………………………41 3.2.3 激光器的电压 - 电流曲线………………………………………………… 41 3.2.4 调制输出特性……………………………………………………………… 41 3.2.4.1 调制信号形状……………………………………………………… 41 3.2.4.1.1 眼孔图样…………………………………………………… 41 3.2.4.1.2 上升和下降时间…………………………………………… 42 3.2.4.2 消光比和调制深度…………………………………………………… 44 3.2.4.3 导通延迟……………………………………………………………… 44 3.2.4.4 截止频率……………………………………………………………… 45 3.2.5 可调激光器特性…………………………………………………………… 45 3.2.6 出射光场和元件排列 3.2.6.1 远场图形……………………………………………………………… 45 3.2.6.2 耦合效率……………………………………………………………… 46 3.2.6.3 前后向寻迹比值偏差………………………………………………… 46 3.2.6.4 前后向寻迹误差……………………………………………………… 47 3.2.6.5 偏振消光比…………………………………………………………… 47 3.2.7 调制器的光学和电气特性…………………………………………………… 47 3.2.7.1 EA调制器特性…………………………………………………………47 3

GMW3089中文翻译

GMW30891 介绍1.1范围针对单线CAN,速率为33.333Kbps和83.333Kbps。

1.2义务/主题高速模式只用作当总线接入离线服务节点。

当不执行下载操作时,离线负载会拆除。

2参考2.1外部标准/规范ISO 11898 SAE #970295ISO 16845 SAE J24112.2GM标准/规范2.3其他参考供应商文档下面的芯片已经证明可以使用。

任何与此规范区别的地方备注如下:●Melexis-TH8056-联系方式●Freescale-MC33897*/R2-这个芯片不能用于车辆运行部分网络,因为休眠模式下这个芯片不能满足最大接收电压的要求。

这个芯片休眠时最大接收电压为0.7V。

这个芯片在新的设计中不推荐使用,由MC33897A*/R2替代●Freescale-MC33897A*/R2-这个芯片设计将满足工作与局部网络并且满足休眠指定的最大接收电压下面的芯片在开发中,目前不能证明可以使用。

On Semiconductor-NCV7356下面的供应商的芯片基于GMW3089的V.126版本。

他们当前正考虑根据新的需求设计芯片。

Philips-下面的供应商的芯片基于GMW3089的V.126版本。

他们当前不考虑根据新的需求设计芯片。

Infineon-其他文档-Bosch博世CAN2.0(仅针对显性位同步的接收)3需求物理层有义务提供一种发送数字数据信号到通信介质(1和0)方法,物理层接口是单个线,参考地平面,输出高边电压驱动。

文档中的需求一般应用在特定的工作状况和生命周期,除非另有说明。

3.1物理和数据链路层特性A.对显性高和接收低信号电压进行载波侦听多路访问/冲突解决(CSMA/CR)总线介入和仲裁B.仅在接收到显性位的变化时执行位重新同步C.CAN控制器应能发送和接收两种标准帧格式信息,比如11位CAN 识别符,和扩展帧格式,比如29位CAN 识别符(CAN2.0B 有效)。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

** ∆VZ=VZ @ 100µA MINUS VZ @ 10µA

SOD-123 CASE - MECHANICAL OUTLINE

A D 1 B

E

F

G C

2 H R3

SYMBOL A B C D E F G H

DIMENSIONS INCHES MILLIMETERS MIN MAX MIN MAX 0.037 0.053 0.95 1.35 0.005 0.12 0.008 0.20 0.055 0.071 1.40 1.80 0.098 0.112 2.50 2.84 0.140 0.154 3.55 3.90 0.010 0.25 0.020 0.028 0.50 0.70 SOD-123 (REV:R3)

TEST MAXIMUM CURRENT REVERSE LEAKAGE CURRENT IZT µA 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 µA 1.0 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.05 0.01 0.01 0.01 0.01 0.01 0.01 0.01 0.01 0.01 0.01 0.01 IR @ VR VOLTS 7.6 8.4 9.1 9.8 10.6 11.4 12.1 12.9 13.6 14.4 15.2 16.7 18.2 19.0 20.4 21.2 22.8 25.0 27.3 29.6 32.6 MAXIMUM VOLTAGE CHANGE** ∆VZ VOLTS 0.10 0.11 0.12 0.13 0.14 0.15 0.16 0.17 0.18 0.19 0.20 0.22 0.24 0.25 0.27 0.28 0.30 0.33 0.36 0.39 0.43 MAXIMUM ZENER CURRENT IZM mA 24.8 21.6 20.4 19.0 17.5 16.3 15.4 14.5 13.2 12.5 11.9 10.8 9.9 9.5 8.8 8.5 7.9 7.2 6.6 6.1 5.5 CDE CDF CDH CDJ CDK CDM CDN CDP CDT CDU CDV CDA CDZ CDY CEA CEC CED CEE CEF CEH CEJ MARKING CODE

TM

CMHZ4678 THRU CMHZ4717 LOW LEVEL ZENER DIODE 1.8 VOLTS THRU 43 VOLTS 500mW, 5% TOLERANCE

Semiconductor Corp.

ELECTRICAL CHARACTERISTICS: (TA=25°C), VF=1.5V MAX @ IF=100mA FOR ALL TYPES.

VOLTS VOLTS CMHZ4697 CMHZ4698 CMHZ4699 CMHZ4700 CMHZ4701 CMHZ4702 CMHZ4703 CMHZ4704 CMHZ4705 CMHZ4706 CMHZ4707 CMHZ4708 CMHZ4709 CMHZ4710 CMHZ4711 CMHZ4712 CMHZ4713 CMHZ4714 CMHZ4715 CMHZ4716 CMHZ4717 9.500 10.45 11.40 12.35 13.30 14.25 15.20 16.15 17.10 18.05 19.00 20.90 22.80 23.75 25.65 26.60 28.50 31.35 34.20 37.05 40.85 10 11 12 13 14 15 16 17 18 19 20 22 24 25 27 28 30 33 36 39 43

SOD-123 CASE ABSOLUTE MAXIMUM RATINGS: Power Dissipation (@TA=25°C) Operating and Storage Temperature SYMBOL PD TJ,Tstg UNIT mW °C

500 -65 to +200

ELECTRICAL CHARACTERISTICS: (TA=25°C), VF=1.5V MAX @ IF=100mA FOR ALL TYPES.

** ∆VZ=VZ @ 100µA MINUS VZ @ 10µA

R0 ( gust 2001)

元器件交易网

Central

TYPE MIN ZENER VOLTAGE VZ @ IZT NOM MAX VOLTS 10.50 11.55 12.60 13.65 14.70 15.75 16.80 17.85 18.90 19.95 21.00 23.10 25.20 26.25 28.35 29.40 31.50 34.65 37.80 40.95 45.15

TYPE MIN ZENER VOLTAGE VZ @ IZT NOM MAX VOLTS 1.890 2.100 2.310 2.520 2.835 3.150 3.465 3.780 4.095 4.515 4.935 5.355 5.880 6.510 7.140 7.875 8.610 9.135 9.555 TEST MAXIMUM CURRENT REVERSE LEAKAGE CURRENT IZT µA 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 µA 7.5 5.0 4.0 2.0 1.0 0.8 7.5 7.5 5.0 4.0 10 10 10 10 10 10 1.0 1.0 1.0 IR @ VR VOLTS 1.0 1.0 1.0 1.0 1.0 1.0 1.5 2.0 2.0 2.0 3.0 3.0 4.0 5.0 5.1 5.7 6.2 6.6 6.9 MAXIMUM VOLTAGE CHANGE** ∆VZ VOLTS 0.70 0.70 0.75 0.80 0.85 0.90 0.95 0.95 0.97 0.99 0.99 0.97 0.96 0.95 0.90 0.75 0.50 0.10 0.08 MAXIMUM ZENER CURRENT IZM mA 120.0 110.0 100.0 95.0 90.0 85.0 80.0 75.0 70.0 65.0 60.0 55.0 50.0 45.0 35.0 31.8 29.0 27.4 26.2 CCC CCD CCE CCF CCH CCJ CCK CCM CCN CCP CCT CCU CCV CCA CCX CCY CCZ CDC CDD MARKING CODE

元器件交易网

CMHZ4678 THRU CMHZ4717 LOW LEVEL ZENER DIODE 1.8 VOLTS THRU 43 VOLTS 500mW, 5% TOLERANCE

Central

DESCRIPTION:

TM

Semiconductor Corp.

The CENTRAL SEMICONDUCTOR CMHZ4678 Series Silicon Low Level Zener Diode is a high quality voltage regulator designed for applications requiring an extremely low operating current and low leakage.

VOLTS VOLTS CMHZ4678 CMHZ4679 CMHZ4680 CMHZ4681 CMHZ4682 CMHZ4683 CMHZ4684 CMHZ4685 CMHZ4686 CMHZ4687 CMHZ4688 CMHZ4689 CMHZ4690 CMHZ4691 CMHZ4692 CMHZ4693 CMHZ4694 CMHZ4695 CMHZ4696 1.710 1.900 2.090 2.280 2.565 2.850 3.135 3.420 3.705 4.085 4.465 4.845 5.320 5.890 6.460 7.125 7.790 8.265 8.645 1.8 2.0 2.2 2.4 2.7 3.0 3.3 3.6 3.9 4.3 4.7 5.1 5.6 6.2 6.8 7.5 8.2 8.7 9.1

Lead Code: 1) Cathode 2) Anode

R0 ( 29-August 2001)