FPGA提高同步系统的运行速度

基于FPGA的数字信号处理算法实现与优化

基于FPGA的数字信号处理算法实现与优化数字信号处理(DSP)是一种通过数字计算器对模拟信号进行处理和转换的技术。

在现代通信、音频处理、图像处理、雷达与声呐等领域中,数字信号处理技术得到了广泛的应用。

为了实现高效的数字信号处理,采用FPGA(Field Programmable Gate Array)作为实现平台是一个不错的选择。

本文将探讨基于FPGA的数字信号处理算法的实现与优化。

一、FPGA概述FPGA是一种可编程的逻辑集成电路,由大量可编程逻辑单元(PLU)和大量的内部互联资源构成。

FPGA具有灵活性高、计算密度高、功耗低等优点,因此在数字信号处理领域中得到了广泛应用。

FPGA的可编程性使得它可以灵活地实现各种数字信号处理算法,并可以根据需求对算法进行优化。

二、数字信号处理算法数字信号处理算法包括一系列数学运算和数字滤波器的设计。

常见的数字信号处理算法包括傅里叶变换、滤波、降噪等。

在FPGA上实现数字信号处理算法需要考虑算法的复杂度、延迟和功耗等因素。

将算法转化为硬件描述语言(HDL)可以使得算法在FPGA上运行更高效,且可以通过优化来提高性能。

三、FPGA中数字信号处理算法的实现在FPGA中实现数字信号处理算法需要将算法转化为硬件描述语言,例如VHDL或Verilog。

首先需要对算法进行建模和仿真验证,然后根据算法的复杂度和性能需求进行优化。

通过对算法进行划分和并行化,可以提高算法在FPGA上的运行速度。

此外,还可以采用硬件加速器、数据存储优化等手段来提高算法的效率。

四、优化策略在FPGA中实现数字信号处理算法时,有一些常用的优化策略可以提高算法的性能。

首先是流水线技术,将算法划分为多个阶段并行执行,可以提高系统的运行速度。

其次是定点化运算,使用定点数表示浮点数可以节省资源和功耗。

另外,还可以采用复杂度折中的方法,通过减少部分计算以降低算法复杂度。

五、案例研究以图像处理为例,实现数字信号处理算法的优化。

利用FPGA实现同步FIFO设置方法

一

1 m 一2 m 模 块 的 功 能 是 : 在 系 统 复 0 0

位或上 电之后 ,对 4 M 的 基 准 时 钟 分 频 产 生需 要 0 的 1 M 和 5 时 钟 信 号 ,其 中 A/ 的 采 样 时 钟 和 0 M D

2 F PGA 设 计

F F 的 设 置 是 指 FI 的 两 个 可 编 程 标 志 位 IO Fo ( AF 和 P P AE) 的 偏 置 寄 存 器 的 设 置 ,通 过 设 置 P AF 和 PAE 的 值 ,可 以 灵 活 地 定 义 缓 冲 深 度 的 大 小 ,在 F F 写 到 设 定 深 度 的 时 候 向 DS 产 生 中 IO P

Ab ta t I hsp p r ac n iu ain meh do y c r n u I Oswih F GA n sr c nt i a e , o f rt to fs n h o o sF F t P g o a d VHDL a g a ei raie h ln u g s e l d i t e z n

we n、 ff io

—

iiil wck。 程 序 的顶 层 文 件 如 图 2 nta 和 l

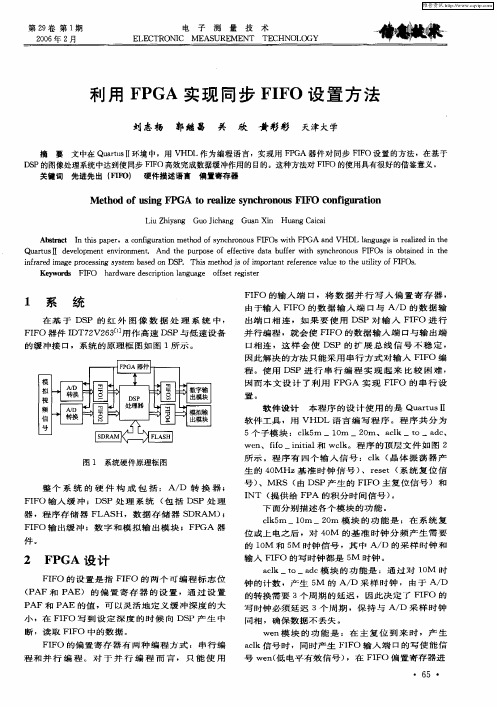

图 1 系统硬件 原理 框图

整 个 系 统 的 硬 件 构 成 包 括 : A/ 转 换 器 ; D FI )输 入 缓 冲 ;DS 处 理 系 统 F( P ( 括 DS 处 理 包 P 器 ・程 序 存 储 器 F LAS , 数 据 存 储 器 S H DRAM ); F FO 输 出 缓 冲 ; 数 字 和 模 拟 输 出 模 块 ;FP I GA 器

程 。使 用 DS 进 行 串 行 编 程 实 现 起 来 比 较 困 难 , P 因而 本 文 设 计 了利 用 F PGA 实 现 FI O 的 串 行 设 F

LabVIEW中的硬件加速和FPGA编程

LabVIEW中的硬件加速和FPGA编程LabVIEW(Laboratory Virtual Instrument Engineering Workbench)是一款强大的图形化编程平台,广泛应用于各个领域的实验室和工程项目中。

随着科技的发展,对系统性能和实时性的需求越来越高,LabVIEW的硬件加速和FPGA编程成为了关键技术。

本文将详细介绍LabVIEW中的硬件加速和FPGA编程的基本原理和实践应用。

一、硬件加速概述硬件加速是指利用硬件设备的计算和运算能力来提高系统的性能和响应速度。

在LabVIEW中,硬件加速通常采用FPGA(Field-Programmable Gate Array)来完成。

FPGA是一种可编程逻辑门阵列,可以即时配置为特定的电子电路,用于实现并行计算和处理。

二、FPGA编程原理FPGA编程是指利用LabVIEW的编程环境对FPGA进行配置和开发。

FPGA编程主要涉及以下几个方面:1. FPGA架构设计LabVIEW提供了丰富的FPGA架构设计工具,使开发人员可以根据具体需求进行配置和设计。

FPGA的架构设计包括逻辑电路、时钟频率、管脚布局等方面的考虑。

2. FPGA逻辑编程LabVIEW使用图形化编程语言G语言进行FPGA逻辑的编程。

开发人员可以通过拖拽和连接节点实现逻辑功能的定义和设计。

G语言中的模块、线程和数据流控制等概念被广泛运用于FPGA编程中。

3. FPGA时序分析FPGA编程中的时序分析是确保逻辑电路在设定的时钟频率下正常工作的重要环节。

LabVIEW提供了时序分析工具,可以帮助开发人员进行时序约束的设定和分析,提高系统的时序稳定性。

三、硬件加速的应用硬件加速在各个领域都有广泛的应用。

以下是几个典型的应用实例:1. 图像处理图像处理需要大量的计算和数据处理能力,利用FPGA实现硬件加速可以大大提高图像处理的速度和效率。

例如,利用FPGA加速的LabVIEW系统可以在实时视频流中进行目标检测和跟踪。

电脑和fpga之间同步通信

电脑和fpga之间同步通信电脑和FPGA之间的同步通信是现代计算机技术中的重要组成部分。

随着计算机性能的不断提升,对于高速、可编程的硬件加速器的需求也越来越大,而FPGA(Field-Programmable Gate Array)正是一种常用的硬件加速器。

本文将介绍电脑和FPGA之间同步通信的基本原理和实现方法。

我们来了解一下什么是FPGA。

FPGA是一种可编程逻辑器件,它由大量的可编程逻辑单元和存储单元组成。

与传统的ASIC (Application-Specific Integrated Circuit)相比,FPGA具有可编程性强、灵活性高的特点。

FPGA可以通过编程将逻辑电路实现在硬件上,从而加速特定的计算任务。

在电脑和FPGA之间进行同步通信时,需要解决两个关键问题:时序同步和数据传输。

时序同步是指电脑和FPGA之间的时钟信号同步。

在计算机系统中,时钟信号被用来同步电路的操作。

在FPGA中,也有时钟信号用于同步逻辑电路的工作。

为了实现电脑和FPGA之间的同步通信,需要保证两者的时钟信号同步。

一种常用的方法是使用专门的时钟模块,将电脑和FPGA的时钟信号进行同步。

这样可以确保数据在电脑和FPGA之间的传输是同步的。

数据传输是电脑和FPGA之间同步通信的另一个重要问题。

为了实现数据的传输,需要设计合适的接口和协议。

一种常用的接口是使用通用并行接口(GPI)或高速串行接口(GSI)。

这些接口可以在电脑和FPGA之间传输数据,并确保数据的同步性和可靠性。

在设计接口和协议时,需要考虑数据的传输速率、数据的格式、错误检测和纠正等因素。

为了提高数据传输的效率,可以使用流水线技术和并行传输技术。

流水线技术将数据分为多个阶段进行传输,从而提高数据的传输速率。

并行传输技术则是同时传输多个数据,进一步提高传输效率。

为了确保数据的正确传输,还需要进行错误检测和纠正。

常用的方法包括奇偶校验、循环冗余检测(CRC)等。

怎样增加程序cpu使用率提高运行速度

怎样增加程序cpu使用率提高运行速度要增加程序的CPU使用率以提高运行速度,有许多方面可以进行优化和改进。

下面是一些建议:1.使用多线程:使用多线程允许程序同时执行多个任务。

将程序拆分成多个线程,使每个线程都能利用CPU的不同核心来执行任务,从而提高程序的并行性和效率。

2.优化算法和数据结构:选择合适的算法和数据结构对于提高程序性能至关重要。

使用高效的算法可以减少CPU的负载,并且优化数据结构可以加快数据的访问和处理速度。

3.减少内存使用:减少程序的内存使用有助于减轻CPU的负担。

可以通过优化代码来减少不必要的内存分配和释放,使用更小内存的数据类型等方式来减少内存占用。

4.使用编译器优化选项:大多数编译器都提供了一些优化选项,可以根据程序的需求进行设置。

这些选项可以在编译时进行各种优化,例如优化代码、内存对齐、预测分支等,从而提高程序的运行速度和CPU利用率。

5. 使用并行编程模型:使用并行编程模型(如OpenMP、CUDA等)可以将计算任务分解为多个并行的子任务,以利用多核处理器的优势。

这样可以提高程序的计算速度和并行性,提高CPU的使用率。

6.使用高性能库或框架:使用经过优化的高性能库或框架可以提高程序的运行效率。

这些库和框架经过专门设计和优化,可以在底层运用高效的算法和数据结构,从而提高程序的性能和CPU使用率。

7.避免频繁的IO操作:频繁的IO操作会降低程序的性能,因为IO操作通常比CPU计算要慢得多。

可以通过使用缓冲区、批量读写等方式来减少IO操作的频率,从而降低对CPU的影响。

8.使用高效的IO操作:如果无法完全避免IO操作,可以选择使用高效的IO操作方法。

例如,使用异步IO、内存映射文件、使用缓存数据等方式可以提高IO操作的速度,减少CPU的等待时间。

9.避免不必要的同步:同步操作会导致线程之间的等待,降低程序的并行性和效率。

在设计和实现程序时,应尽量避免过多的同步操作,从而提高CPU的使用率。

基于FPGA的高速多通道实时同步采集传输系统的设计与实现

S y nc hr o n o u s Ac q ui s i t i o n Tr a ns mi s s i o n S y s t e m Ba s e d o n FPG A

Du Yu - x i a o ,Z h a n g Ha o — t e n g ,C h e n We n - y u,Hu a n g Xu e — b i n,Ca i Z h e n — d i a n,Z h u o J i e ( S c h o o l o f A u t o m a t i o n , G u a n g d o n g U n i v e r s i t y o f T e c h n o l o g y , G u a n g z h o u 5 1 0 0 0 6 , C h i n a )

Abs t r a c t :I n v i e w o f t he la f ws o f r e p e a t e d a n d c u mb e r s o me c o mmun i c a t i o n p r o c e s s, i n e ic f i e n c y a n d s ma l l d a t a t h r o u g h p u t o f t h e t r a di t i o n a l d u a l — c o r e c o nt r o l a c qu i s i t i o n s y s t e m o f mu l t i — l e a d EEG ma c h i n e, i t a d v a n c e s a h i g h s p e e d,mu l t i — c h a n n e l a n d r e a l — t i me s y n c hr o n o us a c q ui s i t i o n s y s t e m ,b a s e d o n FPGA. Th e SDRAM i s ma i n l y c o n t r o l l e d b y FPGA wh i c h F I F O・ - i n t e r na l i z e s t he S DRAM v i a t h e p r o g r a m t o a - ・ c hi e v e t h e a s y n c h r o n o u s c l o c k r e a d i n g — - wh i l e - - wr i t i n g o f t h e S DRAM b y t h e pi n g p o n g o p e r a t i o n o f t wo p a i r s o f F I FO o f SDRAM ,whi c h e ns u r e s t h e o n g o i n g o f i n t e r f a c e ’ S da t a t r a n s mi s s i o n b e t we e n F PGA a n d ARM a n d e ic f i e n t c o mmu ni c a t i o n b y c o n c i s e a n d r i g o r o us pa r a l l e l i n t e r f a c e a g r e e me n t s .Th e F PGA a n d S DRAM c a n b e e q u i v a l e n t t o a S DRAM wh i c h c a n a u t o ma t i c a l l y c o l l e c t da t a .Te s t s s h o w t ha t t h i s s y s t e m a v o i ds t h e r e pe a t e d c o p y o f t r a n s f e r p r o c e s s a n d r e d un d a nt c o mpl e x d a t a t r a n s f e r o p e r a t i o n,a nd i mp r o v e s t he d a t a t h r o u g h pu t a n d t r a ns f e r r a t e,wh i c h me e t s t h e r e q u i r e me n t f o r t h e d e s i g n i n d e x e s o f 2 5 6- l e a d EEG ma c h i n e wi t h t h e s a mpl e re f q u e n c y u p t o 2 0 k Hz o r e v e n hi g h e r . Ke y wo r d s:2 5 6- l e a d EEG;t he h i g h- s p e e d mu l t i - c ha nn e l s a mp l i n g;t he t e c h n i q u e o f r e a l — t i me s y n c h o- r ni z a t i o n:F PCA

FPGA设计的重要规范和经验精华

从大学时代第一次接触FPGA至今已有10多年的时间。

至今记得当初第一次在EDA实验平台上完成数字秒表,抢答器,密码锁等实验时,那个兴奋劲。

当时由于没有接触到HDL硬件描述语言,设计都是在MAX+plus II原理图环境下用74系列逻辑器件搭建起来的。

后来读研究生,工作陆陆续续也用过Quartus II,Foundation,ISE,Libero,并且学习了verilogHDL语言,学习的过程中也慢慢体会到verilog的妙用,原来一小段语言就能完成复杂的原理图设计,而且语言的移植性可操作性比原理图设计强很多。

工作过的朋友肯定知道,公司里是很强调规范的,特别是对于大的设计(无论软件还是硬件),不按照规范走几乎是不可实现的。

逻辑设计也是这样:如果不按规范做的话,过一个月后调试时发现有错,回头再看自己写的代码,估计很多信号功能都忘了,更不要说检错了;如果一个项目做了一半一个人走了,接班的估计得从头开始设计;如果需要在原来的版本基础上增加新功能,很可能也得从头来过,很难做到设计的可重用性。

在逻辑方面,我觉得比较重要的规范有这些:1.设计必须文档化。

要将设计思路,详细实现等写入文档,然后经过严格评审通过后才能进行下一步的工作。

这样做乍看起来很花时间,但是从整个项目过程来看,绝对要比一上来就写代码要节约时间,且这种做法可以使项目处于可控、可实现的状态。

2.代码规范。

如果在另一个设计中的时钟是40ns,复位周期不变,我们只需对CLK_PERIOD进行重新例化就行了,从而使得代码更加易于重用。

b.信号命名要规范化。

1)信号名一律小写,参数用大写。

2)对于低电平有效的信号结尾要用_n标记,如rst_n。

3)端口信号排列要统一,一个信号只占一行,最好按输入输出及从哪个模块来到哪个模块去的关系排列,这样在后期仿真验证找错时后方便很多。

4)一个模块尽量只用一个时钟,这里的一个模块是指一个module或者是一个entity。

基于FPGA的图像处理系统设计与优化

基于FPGA的图像处理系统设计与优化一、简介基于FPGA的图像处理系统是一种先进的处理图像的技术,它利用可编程逻辑器件(FPGA)来完成图像处理任务。

本文将介绍基于FPGA的图像处理系统设计和优化的方法和技术。

二、设计方法1. 需求分析:首先,需要明确图像处理系统的需求,包括输入图像的特性、需要实现的功能和处理速度等要求。

根据需求分析,确定系统的设计目标。

2. 系统架构设计:根据需求和设计目标,设计图像处理系统的整体架构。

该架构应包括输入和输出接口、图像处理模块、以及控制和通信模块等。

3. 图像处理算法设计:根据处理需求,选择适当的图像处理算法,并将其设计成可在FPGA上实现的形式。

在算法设计过程中,应考虑计算复杂度、资源占用以及处理效果等因素。

4. 算法优化:为了提高图像处理系统的性能,可以对算法进行优化。

一种常用的优化方法是并行计算,将图像分成多个块,同时进行处理。

此外,还可以利用数据流架构、流水线和流控等技术来提高系统的效率。

5. 系统实现:根据系统设计和算法优化,利用FPGA开发工具,将系统实现在FPGA上。

在实现过程中,需要编写硬件描述语言(HDL)代码,并进行仿真和调试。

三、优化技术1. 并行计算:将图像分成多个块,同时进行处理,可以大大缩短处理时间,并提高系统的吞吐量。

2. 数据流架构:通过将数据在处理过程中流动,而不是存储在内存中,可以减少存储器的使用,提高系统性能。

3. 流水线:将处理任务划分成多个阶段,并将数据流通过不同阶段的处理单元,可以实现并行处理,提高处理速度。

4. 流控:对处理任务进行流控管理,根据数据产生和消耗的速度进行调整,避免数据冲突,从而提高系统性能。

5. 资源共享:合理利用FPGA上的资源,通过共享存储器、共享逻辑单元等方式,降低资源占用,提高系统的效率。

四、系统性能优化1. 时钟频率优化:通过对FPGA的时钟频率进行调整,可以提高系统的运行速度。

但要注意时钟频率过高可能导致功耗增加和稳定性下降。

基于IEEE802.11a的码元同步和编译码的FPGA实现的开题报告

基于IEEE802.11a的码元同步和编译码的FPGA实现的开题报告1. 研究背景和意义随着无线通信技术的发展和应用需求的增加,Wi-Fi技术已经成为了无线局域网中的主流技术之一。

其中IEEE802.11a标准是一种高速无线局域网技术,其最高传输速率可达到54 Mbps。

在IEEE802.11a中,编码和解码等一系列操作都需要进行码元同步,这对于系统性能的稳定性和可靠性具有重要的影响。

此外,利用FPGA(Field Programmable Gate Array)进行硬件实现,不仅可以提高运行速度,还可以节省功耗和成本,因此FPGA已成为Wi-Fi技术硬件实现的重要手段。

因此,本文主要研究基于IEEE802.11a的码元同步和编译码的FPGA 实现技术,旨在提高Wi-Fi无线通信技术的性能和可靠性。

2. 研究内容和方法本研究的主要内容包括:(1)分析IEEE802.11a标准中的码元同步和编译码过程。

(2)设计并实现码元同步和编译码的FPGA硬件电路。

(3)测试和分析硬件电路的性能和可靠性。

具体研究方法包括:(1)文献综述,对IEEE802.11a标准中的码元同步和编译码进行深入研究和分析。

(2)按照标准规范,设计FPGA硬件电路并进行仿真测试。

(3)在FPGA开发板上实现硬件电路,进行性能测试和比较分析。

3. 预期成果和意义预计本研究将实现基于IEEE802.11a的码元同步和编译码的FPGA 实现技术,评估该技术在Wi-Fi通信中的性能和可靠性。

具体成果包括:(1)实现基于IEEE802.11a标准的码元同步和编译码的FPGA硬件电路。

(2)对比分析硬件实现和软件实现的性能和成本优劣。

(3)验证硬件电路在Wi-Fi通信中的有效性和稳定性。

该研究可为Wi-Fi通信技术的发展和优化提供参考,为相关领域的研究和应用提供新的思路和方法。

基于FPGA的跳频系统快速同步算法设计与实现

( 1 . C o m m a n d A u t o ma t i o n Wo r k s t a t i o n o fX i n j i a n g Mi l i t a r y R e g i o n , U r u m q i 8 3 0 0 4 2 , C h i n a ; 2 . U n i t 6 9 2 4 0 f 咒 A, o U r u m q i 8 3 0 0 4 2 , C h i n a )

试表 明, 该 快 速 同 步 算 法 建 立 时 短 、 同步 稳 定 可 靠 。

关键词 : 跳 频 ;快 速 同步 ; F P G A; 独 立 信 道 法 ;同步 头法

中图 分 类 号 : T N 9 2 5 + . 1 文献标识码 : A 文 章 编 号 :1 6 7 4 — 6 2 3 6 ( 2 0 1 3 ) 0 7 — 0 1 5 2 — 0 3

第2 1 卷 第 7期

Vo 1 . 21

No . 7

— —

电子设 计 工程

El e c t r o n i c De s i g n En g i n e e r i n g

2 0 1 3年 4月

Ap r .2 01 3

基于 F P G A 的跳频 系统快 速 同步算 法设计 与实现

付睿 智 ,杨 玉彬 ,汤华军

( 1 . 新 疆 军 区指 挥 自动化 工作 站 新 疆 鸟 鲁 木 齐 8 3 0 0 4 2 ; 2 . 6 9 2 4 0部 队 新 疆 乌 鲁 木 齐 8 3 0 0 4 2 ) 摘 要 :同 步技 术是 跳 频 系统 的核 心 。本 文针 对 F P G A 的跳 频 系统 , 设计 了 一 种基 于独 立信 道 法 , 同步 字 头 法和 精 准 时 钟 相 结 合 的 快 速 同步 方 法 , 同 时设 计 了基 于双 图案 的 改进 型 独 立 信 道 法 , 同 步算 法协 议 , 协议帧格式等。该设计使 用 V H D L硬 件 语 言 实现 , 采用 A l t e r a公 司的 E P 3 C 1 6 E 1 4 4 C 8作 为 核 心 芯 片 , 并 在 此 硬 件 平 台上 进 行 了功 能验 证 。 实 际 测

FPGA综合优化方法概述

采用流水线设计的优势在于它能提高吞吐量(throughput)。

首次延迟(latency)——(从输入到输出)最长的路径进行初始 化所需要的时间总量; 吞吐延迟——执行一次重复性操作所需要的时间总量。

lld

2. 流水线结构原理及实例

流水线的延时分析

W

1 X 3 2 Z 上图时序分析: 这个组合逻辑包括两级。 第一级的延迟是T1和T3两个延迟中的最 大值; 第二级的延迟等于T2的延迟。 为了通过这个组合逻辑得到稳定的计 算结果输出,需要等待的传播延迟为:

lld

一、概述 面积的优化——逻辑资源的共享。 例如:使用数据选择器实现加法器(运算 器)的共享。

lld

三、时序约束与时序分析 静态时序分析与动态时序仿真的区别

设计中常用的时序概念

同步系统的系统时钟设计思想

3.1 静态时序分析与动态时序仿真的区别

动态时序仿真是针对给定的仿真输入信号波形,模拟设计 在器件实际工作时的功能和延时情况,给出相应的仿真输 出信号波形。它主要用于验证设计在器件实际延时情况下 的逻辑功能。由动态时序仿真报告无法得到设计的各项时 序性能指标,如最高时钟频率等。 静态时序分析则是通过分析每个时序路径的延时,计算出 设计的各项时序性能指标,如最高时钟频率、建立保持时 间等,发现时序违规。它仅仅聚焦于时序性能的分析,并 不涉及设计的逻辑功能,逻辑功能验证仍需通过仿真或其 他手段(如形式验证等)进行。静态时序分析是最常用的 分析、调试时序性能的方法和工具。

一、概述

1.2 设计思想和技巧

1.2.1 逻辑复制

逻辑复制是一种最基本的通过增加面积改善时序条件的优化手段。 这种方法最常用的场合是调整信号的扇出。当一个信号要驱动后 级的许多单元时,也就是有多级扇出时,可能会出现如图1中左图所 示的一些扇出路径的长延时。此时的解决方法就是通过信号逻辑 的复制来减少路径延时,如右图所示。

fpga在通信中的应用(3篇)

第1篇随着信息技术的飞速发展,通信技术已经成为现代社会不可或缺的一部分。

作为通信系统中的一种关键技术,FPGA(现场可编程门阵列)因其高度的灵活性和可定制性,在通信领域得到了广泛的应用。

本文将从FPGA的特点、在通信中的应用场景以及未来发展等方面进行探讨。

一、FPGA的特点1. 高度可定制性:FPGA可以根据用户需求进行编程,实现各种复杂的逻辑功能,满足通信系统对功能的需求。

2. 高性能:FPGA采用高速、低功耗的设计,能够满足通信系统中高速数据处理的实时性要求。

3. 高可靠性:FPGA具有较低的故障率,能够保证通信系统的稳定运行。

4. 高集成度:FPGA将大量的逻辑单元集成在一个芯片上,降低了系统的体积和功耗。

5. 易于升级:FPGA可以通过编程实现功能升级,无需更换硬件设备。

二、FPGA在通信中的应用场景1. 柯尔克霍夫变换(Kerdock Transformation)柯尔克霍夫变换是一种重要的通信技术,能够有效提高通信系统的抗干扰能力和传输速率。

FPGA可以实现高速、低功耗的柯尔克霍夫变换算法,提高通信系统的性能。

2. 滤波器设计在通信系统中,滤波器用于消除噪声和干扰,提高信号质量。

FPGA可以灵活地实现各种滤波器算法,如低通、高通、带通和带阻滤波器等,满足不同场景下的滤波需求。

3. 数字信号处理(DSP)DSP技术在通信系统中扮演着重要角色,如调制、解调、编码、解码等。

FPGA具有强大的并行处理能力,可以实现对大量数据的高速处理,提高通信系统的性能。

4. 调制解调器(Modem)调制解调器是实现数字信号与模拟信号之间转换的关键设备。

FPGA可以灵活地实现各种调制解调算法,如QAM、QPSK、OFDM等,提高通信系统的传输速率和抗干扰能力。

5. 物理层协议处理物理层协议处理是通信系统中不可或缺的一部分,如以太网、Wi-Fi、蓝牙等。

FPGA可以实现对物理层协议的高效处理,提高通信系统的性能。

ARM,单片机,FPGA,嵌入式,DSP

简单的说,嵌入式是嵌入式系统的简称,所谓嵌入式系统是指嵌入到应用对象中的专用计算机系统。

这里的对象就是指产品,比如日常使用的冰箱、空调、洗衣机,或者手机、游戏机等。

这些产品中都有计算机系统,这类计算机系统就是嵌入式计算机系统。

至于单片机、ARM、FPGA、DSP等都是实现嵌入式系统的硬件平台。

根据对象体系的功能复杂性和计算处理复杂性,提供的不同选择。

对于简单的家电控制嵌入式系统,采用简单的8位单片机就足够了,价廉物美,对于手机和游戏机等,就必须采用32位的ARM和DSP等芯片了。

FPGA是一种更偏向硬件的实现方式。

所以要学习嵌入式,要从单片机开始,然后学习ARM和DSP之类我个人认为你说的刚好相反。

不是别的,FPGA就是自己构建硬件电路,而DSP有内嵌的硬件乘法模块。

单片机应该是偏软的,比如说吧, 现在基本上可以完全用高级语言(如C)来编写单片机程序,而DSP 确还是要用到汇编。

你要知道,汇编可以说就是硬件语言。

呵呵,希望对你有用————ARM、FPGA和DSP的特点和区别是什么?发布时间:2009-5-8 14:25 发布者:ARM 阅读次数:833 DSP(digital singnal processor)是一种独特的微处理器,有自己的完整指令系统,是以数字信号来处理大量信息的器件。

一个数字信号处理器在一块不大的芯片内包括有控制单元、运算单元、各种寄存器以及一定数量的存储单元等等,在其外围还可以连接若干存储器,并可以与一定数量的外部设备互相通信,有软、硬件的全面功能,本身就是一个微型计算机。

DSP采用的是哈佛设计,即数据总线和地址总线分开,使程序和数据分别存储在两个分开的空间,允许取指令和执行指令完全重叠。

也就是说在执行上一条指令的同时就可取出下一条指令,并进行译码,这大大的提高了微处理器的速度。

另外还允许在程序空间和数据空间之间进行传输,因为增加了器件的灵活性。

其工作原理是接收模拟信号,转换为0或1的数字信号,再对数字信号进行修改、删除、强化,并在其他系统芯片中把数字数据解译回模拟数据或实际环境格式。

fpga面积优化和速度优化方法

FPGA(Field-Programmable Gate Array)作为一种可编程的逻辑器件,被广泛应用于数字信号处理、通信系统、嵌入式系统等领域。

在设计FPGA电路时,面积和速度是两个核心指标,对于设计人员来说,如何优化FPGA面积和速度是一个非常重要的课题。

本文将从面积优化和速度优化两个方面,探讨FPGA设计中的优化方法。

一、FPGA面积优化方法1. 逻辑优化在FPGA设计中,逻辑优化是一种常见的面积优化方法。

逻辑优化主要包括逻辑综合、布线和布局三个阶段。

在逻辑综合阶段,可以通过逻辑合并、功能分解等技术,减少逻辑门的数量,从而减小FPGA的面积占用。

在布线和布局阶段,可以通过合理的布线规则和布局布线策略,减少开关电路的数量,进而减小FPGA的面积占用。

2. 流水线技术流水线技术是一种常见的面积优化方法,通过将一个大模块分解成多个小模块,并将其连接成流水线,可以减小每个模块的逻辑规模,从而减小FPGA的面积占用。

流水线技术可以有效降低FPGA电路的逻辑深度,提高电路的运行速度。

3. 复用技术在FPGA设计中,复用技术是一种有效的面积优化方法。

通过设计可重用的功能模块,并在不同的部分中多次使用这些功能模块,可以减小FPGA的面积占用。

复用技术可以降低电路的逻辑规模,提高电路的复杂度。

4. 资源共享技术资源共享技术是一种常见的面积优化方法。

通过将同一类型的资源共享给多个功能模块使用,可以减小FPGA的资源占用。

资源共享技术可以降低FPGA的资源消耗,提高电路的资源利用率。

二、FPGA速度优化方法1. 时序优化时序优化是一种常见的速度优化方法。

通过优化时序约束、时钟分配等技术,可以降低电路的时序延迟,提高电路的工作速度。

时序优化可以通过同步技术和异步技术来实现,可以提高电路的工作速度。

2. 缓冲器插入技术缓冲器插入技术是一种有效的速度优化方法。

通过在关键路径上插入缓冲器,可以减小信号传输的延迟,提高电路的工作速度。

FPGA_ASIC-基于FPGA的快速位同步系统设计

基于FPGA的快速位同步系统设计管立新(赣南师范学院电子信息学院 江西赣州, 341000)摘 要:从时分复接系统对位同步系统的性能要求出发,提出了一种基于FPGA的快速位同步系统的设计方案,给出了位同步系统的实验仿真,结果表明该系统有较快的位同步建立时间,节省了FPGA的耗用资源,系统工作稳定、可靠。

关键词:位同步;同步建立时间;现场可编程门阵列;仿真中图分类号:TP311;TN919 文献标识码:AFast Bit Synchronization System Design Based on FPGAGUAN Li-XinElectronic Information Science Department Of Gannan Teacher’s College,GanZhou JiangXi, 341000,china Abstract: According to the performance requirement of bit synchronization in Time Division Multiplexer system, the paper proposed a method to design fast bit synchronization system based on FPGA. The imitation and experiment of bit synchronization system were given, experiment result shows, the system can build synchronization quickly, the circuit work stably and reliable.Keywords: Bit synchronization;Synchronization Build Time;FPGA;Imitation1 引言在时分复接通信系统中,位同步是收、发两端的时钟频率必须同频、同相,这样在接收端才能正确地判决发送端送来的每一个码元。

二维扩频系统帧同步技术研究与FPGA实现

关 系 着 整 个通 信 系 统 的 性 能 。 没 有 准 确 的 同 步 算 法 , 不 能 就

1 T / SC M A 系 统 分 析 FMC D — D

T / —D FMCDSC MA 的 结 构 如 图 1 示 。 显 然 ,FMC D - 所 T / S

进 行 可 靠 的数 据 传 输 , 是 信 息 可 靠 传 输 的 前 提 。 F CDS 它 T/ M —

一

种 新 的通 信 系 统 , 系 统 是 是 一 种 典 型 的 二 维 扩 频 多 统 由 于利 用 多 含 载 波 传 输 数 据 , 邻 载 波 榴

的 间 隔 非 常 小 ,对 系 统 的 频 率 偏 移 和 定 时 偏 移 非 常 敏 感 。 因

a he e . c iv d

Ke rs ji mef qe c-o i sra ; lcre D y wo d:ont —e un yd ma ed mut ar r MA; a n ho i t n F G pe nai ;i n muao ti - r - np i iC r f me y c nz i ; P Ai l s r ao m me t o t g i l in t n mi s t

rsuc r n r u o p tt n S M ah dmo e u mo ue t bl wn o cu l inadC dut l eoref omo s m uai , Ot R oe c o woA ccea v m d lwi mo i id ws cmua o n Pajs be n s h e a t a

Ab t a t A ea lda ay i d n t eT / C DS CDM A y tm r h t cu ea d s n h o i ai nis e . Ac o d n F M C sr c : d t i n l ss s e i ma eo F M — h s se a c i tr n y c r n z t u s e o s c r i gt T / o

高速数据传输中的FPGA调制解调系统设计与时钟同步

高速数据传输中的FPGA调制解调系统设计与时钟同步随着科技的发展,数据传输变得越来越重要。

在高速数据传输领域,FPGA(现场可编程逻辑门阵列)调制解调系统发挥着重要的作用。

本文将介绍FPGA调制解调系统的设计原理,并重点讨论时钟同步的问题。

一、FPGA调制解调系统设计原理FPGA调制解调系统是一种基于FPGA芯片的数字信号处理系统,其设计原理包括以下几个方面:1. 数字信号调制:FPGA调制解调系统通过将模拟信号转化为数字信号进行调制。

调制方式可以是常见的调幅、调频或调相等,根据特定的应用场景进行选择。

FPGA的灵活性使得可以根据需要动态地改变调制方式,实现不同的数据传输要求。

2. 数字信号解调:FPGA调制解调系统通过逆运算将数字信号转化为模拟信号进行解调。

解调的准确性直接影响到数据传输的可靠性和稳定性。

FPGA芯片的高速计算能力和低功耗特性使其成为进行高精度数字信号解调的理想选择。

3. 码型设计:在FPGA调制解调系统中,码型设计是一项关键任务。

合理选择适当的码型设计方案可以提高数据传输的效率和可靠性。

常见的码型设计方法包括幅度键控、频率键控和相位键控等,需要根据实际需求进行选择。

二、时钟同步问题在高速数据传输过程中,时钟同步是一个重要的问题。

时钟同步不仅影响到数据的正确接收和解调,还会对整个系统的性能产生一定的影响。

为了保证时钟同步的稳定性,需要考虑以下几个方面:1. 时钟源选择:选择合适的时钟源对于时钟同步至关重要。

常见的时钟源可以是外部晶振或者其他稳定的时钟信号源。

在选择时钟源的同时,要充分考虑系统的实际需求和环境条件。

2. 时钟同步算法:针对不同的应用场景,可以采用不同的时钟同步算法。

常见的时钟同步算法包括PLL(锁相环)和FLL(锁定环路)等。

选择合适的时钟同步算法可以保证数据传输的稳定性和可靠性。

3. 时钟分频系统:在高速数据传输中,时钟分频系统用于将高速时钟信号转化为适合不同组件使用的低速时钟信号。

fpga优势

1,FPGA运行速度快FPGA内部集成锁项环,可以把外部时钟倍频,核心频率可以到几百M,而单片机运行速度低的多.在高速场合,单片机无法代替FPGA2,FPGA管脚多,容易实现大规模系统单片机IO口有限,而FPGA动辄数百IO,可以方便连接外设.比如一个系统有多路AD,DA,单片机要进行仔细的资源分配,总线隔离,而FPGA由于丰富的IO资源,可以很容易用不同IO连接各外设3,FPGA内部程序并行运行,有处理更复杂功能的能力单片机程序是串行执行的,执行完一条才能执行下一条,在处理突发事件时只能调用有限的中断资源;而FPGA不同逻辑可以并行执行,可以同时处理不同任务,这就导致了FPGA工作更有效率4,FPGA有大量软核,可以方便进行二次开发FPGA甚至包含单片机和DSP软核,并且IO数仅受FPGA自身IO限制,所以,FPGA 又是单片机和DSP的超集,也就是说,单片机和DSP能实现的功能,FPGA一般都能实现FPGA:时序控制能力强。

(时序能力强,没有指令周期,速度快)控制能力较强(由于没有指令集,不如ARM和单片机)。

数字信号处理及算法弱(这里讲的弱是指内部不集成DSP的前提下)DSP:时序控制能力较弱。

(没办法。

有了指令集,就有指令周期。

而且受到时钟约束)控制能力较强(有指令集。

但是不是专业搞控制的)数字信号处理及算法强(专业特长嘛)DSP和FPGA开发的概述:DSP,专用电路(内部结构已经固定)通过对RAM内部的指令和数据工作(这个是CPU和ARM等等的工作方式)所以开发遵循嵌入式软件的设计原则。

调试应更注重于算法的实现。

FPGA,ASIC一种,经典FPGA的内部结构是寄存器+组合逻辑(查找表)。

最后是按照逻辑电路进行设计。

所以是属于硬件设计原则。

调试除了需要关心功能以外,还需要关心电路方面的特性。

比如说延迟,整体功率等等。

开发工具:DSP仿真器,开发板。

仿真器比较多,网上查吧,DSP仿真器,网上大堆的,嫌不够正规,TI网站自己找教程和datasheet。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

FPGA提高同步系统的运行速度

同步电路的速度是指同步时钟的速度。

同步时钟愈快,电路处理数据的时间间隔越短,电路在单位时间处理的数据量就愈大。

我们先来看一看同步电路中数据传递的一个基本模型:如下图

图1

(Tco是触发器时钟到数据输出的延时;Tdelay是组合逻辑的延时;Tsetup是触发器的建立时间)

假设数据已经被时钟的上升沿打入D触发器,那么数据到达第一个触发器的Q端需要Tco,再经过组合逻辑的延时Tdelay到达的第二个触发器的D端,要想时钟能在第二个触发器再次被稳定的锁入触发器,则时钟的延迟不能晚于Tco+Tdelay+Tsetup,(我们可以回顾一下前面讲过建立和保持时间的概念,就可以理解为什么公式最后要加上一个Tdelay)由以上分析可知:最小时钟周期:T=Tco+Tdelay+Tsetup 最快时钟频率 F= 1/T PLD开发软件也正是通过这个公式来计算系统运行速度Fmax

注:在这个逻辑图中有个参数:Tpd ,即时钟的延时参数,我们在刚才做时间分析的时候,没有提这个参数,(如果使用PLD的全局时钟型号,Tpd可以为0,如果是普通时钟,则不为0)。

所以如果考虑到时钟的延时,精确的公式应该是T=Tco+Tdelay+Tsetup-Tpd。

当然以上全部分析的都是器件内部的运行速度,如果考虑芯片I/O管脚延时对系统速度的影响,那么还需要加一些修正。

由于Tco、Tsetup是由具体的器件和工艺决定的,我们设计电路时只可以改变Tdelay。

所以缩短触发器间组合逻辑的延时是提高同步电路速度的关键。

由于一般同步电路都不止一级锁存(如图3),而要使电路稳定工作,时钟周期必须满足最大延时要求,缩短最长延时路径,才可提高电路的工作频率。

如图2所示:我们可以将较大的组合逻辑分解为较小的几块,中间插入触发器,这样可以提高电路的工作频率。

这也是所谓“流水线”(pipelining)技术的基本原理。

图2 分割组合逻辑

对于图3的上半部分,它时钟频率受制于第二个较大的组合逻辑的延时,通过适当的方法平均分配组合逻辑,可以避免在两个触发器之间出现过大的延时,消除速度瓶颈。

图3 转移组合逻辑

PLD开发软件中也有一些设置,通过修改这些设置,可以提高编译后系统速度,但这种速度的提高是很有限的,我们只有理解系统速度的基本原理,认真的优化设计方案,才能从根本上提高系

统的运行速度。