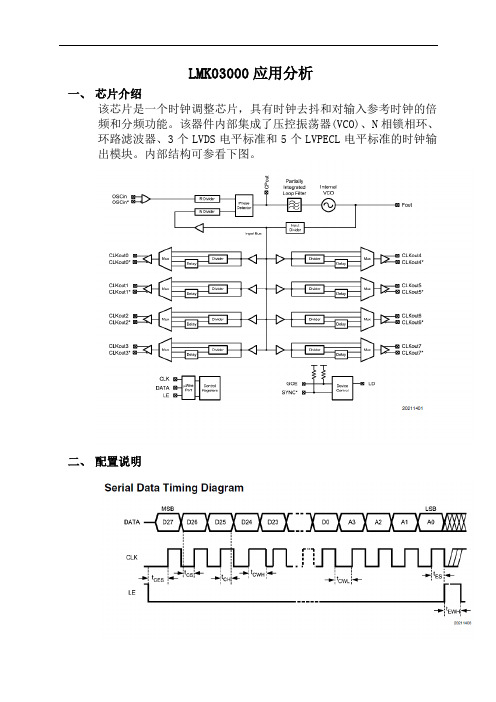

LMK03000DISQENOPB;LMK03000ISQNOPB;LMK03033ISQENOPB;LMK03000CISQNOPB;中文规格书,Datasheet资料

LMK00101SQXNOPB;LMK00101SQNOPB;LMK00101SQENOPB;LMK00101BEVALNOPB;中文规格书,Datasheet资料

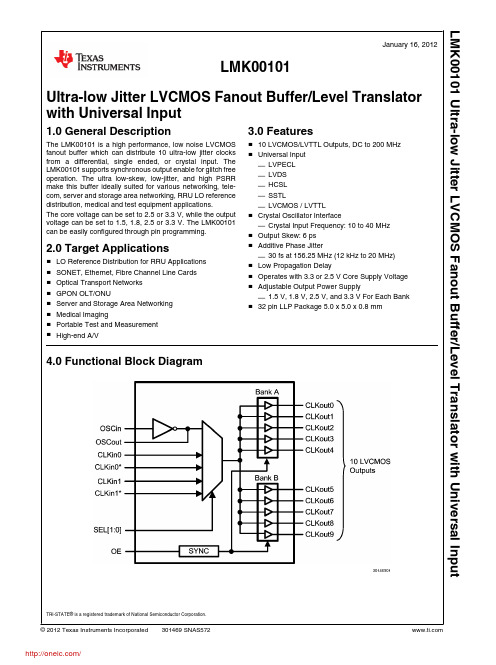

LMK00101January 16, 2012Ultra-low Jitter LVCMOS Fanout Buffer/Level Translator with Universal Input1.0 General DescriptionThe LMK00101 is a high performance, low noise LVCMOS fanout buffer which can distribute 10 ultra-low jitter clocks from a differential, single ended, or crystal input. The LMK00101 supports synchronous output enable for glitch free operation. The ultra low-skew, low-jitter, and high PSRR make this buffer ideally suited for various networking, tele-com, server and storage area networking, RRU LO reference distribution, medical and test equipment applications.The core voltage can be set to 2.5 or 3.3 V, while the output voltage can be set to 1.5, 1.8, 2.5 or 3.3 V. The LMK00101 can be easily configured through pin programming.2.0 Target Applications■LO Reference Distribution for RRU Applications■SONET, Ethernet, Fibre Channel Line Cards■Optical Transport Networks■GPON OLT/ONU■Server and Storage Area Networking■Medical Imaging■Portable Test and Measurement■High-end A/V 3.0 Features■10 LVCMOS/LVTTL Outputs, DC to 200 MHz ■Universal Input—LVPECL—LVDS—HCSL—SSTL—LVCMOS / LVTTL■Crystal Oscillator Interface—Crystal Input Frequency: 10 to 40 MHz■Output Skew: 6 ps■Additive Phase Jitter—30 fs at 156.25 MHz (12 kHz to 20 MHz)■Low Propagation Delay■Operates with 3.3 or 2.5 V Core Supply Voltage ■Adjustable Output Power Supply—1.5 V, 1.8 V, 2.5 V, and 3.3 V For Each Bank ■32 pin LLP Package 5.0 x 5.0 x 0.8 mm4.0 Functional Block Diagram30146901TRI-STATE® is a registered trademark of National Semiconductor Corporation.© 2012 Texas Instruments Incorporated301469 LMK00101 Ultra-low Jitter LVCMOS Fanout Buffer/Level Translator with Universal Input5.0 Connection Diagram32-Pin LLP Package301469026.0 Pin DescriptionsPin #Pin Name Type DescriptionDAP DAP -The DAP should be grounded1CLKout0Output LVCMOS Output2, 6Vddo Power Power Supply for Bank A (CLKout0 to CLKout4) CLKout pins.19,23Vddo Power Power Supply for Bank B (CLKout5 to CLKout9) CLKout pins.3CLKout1Output LVCMOS Output 4,9,15,16,21,25,26,32GND GND Ground5CLKout2Output LVCMOS Output 7CLKout3Output LVCMOS Output 8CLKout4Output LVCMOS Output10Vdd Power Supply for operating core and input buffer 11OSCin Input Input for Crystal 12OSCout Output Output for Crystal 13CLKin0Input Input Pin14CLKin0*Input Optional complimentary input pin 17CLKout5Output LVCMOS Output 18CLKout6Output LVCMOS Output 20CLKout7Output LVCMOS Output 22CLKout8Output LVCMOS Output 24CLKout9Output LVCMOS Output27CLKin1*Input Optional Complimentary Input Pin 28CLKin1Input Input Pin29SEL1Input MSB for Input Clock Selection. This pin has an internal pull-down resistor.30SEL0Input LSB for Input Clock Selection. This pin has an internal pull-down resistor.31OEInputOutput Enable. This pin has an internal pull-down resistor. 2L M K 00101 U l t r a -l o w J i t t e r L V C M O S F a n o u t B u f f e r /L e v e l T r a n s l a t o r w i t h U n i v e r s a l I n p u t7.0 Absolute Maximum Ratings (Note 1, Note 2)If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/ Distributors for availability and specifications.Parameter Symbol Ratings Units Core Supply Voltage Vdd-0.3 to 3.6VOutput Supply Voltage Vddo-0.3 to 3.6V Input Voltage V IN-0.3 to Vdd + 0.3V Storage Temperature Range T STG-65 to 150°CLead Temperature (solder 4 s)T L+260°C Junction Temperature T J+125°C8.0 Recommended Operating ConditionsParameter Symbol Min Typ Max Units Ambient Temperature T A-402585°CCore Supply Voltage Vdd 2.375 3.3 3.45V Output Supply Voltage (Note 3)Vddo 1.425 3.3Vdd VNote 1:"Absolute Maximum Ratings" indicate limits beyond which damage to the device may occur, including inoperability and degradation of device reliability and/or performance. Functional operation of the device and/or non-degradation at the Absolute Maximum Ratings or other conditions beyond those indicated in the Recommended Operating Conditions is not implied. The Recommended Operating Conditions indicate conditions at which the device is functional and the device should not be operated beyond such conditions.Note 2:This device is a high performance integrated circuit with ESD handling precautions. Handling of this device should only be done at ESD protected work stations. The device is rated to a HBM-ESD of > 2.5 kV, a MM-ESD of > 250 V, and a CDM-ESD of > 1 kV.Note 3:Vddo should be less than or equal to Vdd(Vddo≤ Vdd)9.0 Package Thermal Resistance32-Lead LLPPackage Symbols Ratings UnitsThermal resistance from junction to ambienton 4-layer Jedec board (Note 4)θJA50° C/WThermal resistance from junction to case(Note 5)θJC (DAP)20° C/WNote 4:Specification assumes 5 thermal vias connect to die attach pad to the embedded copper plane on the 4-layer Jedec board. These vias play a key role in improving the thermal performance of the LLP. For best thermal dissipation it is recommended that the maximum number of vias be used on the board layout.Note 5:Case is defined as the DAP (die attach pad).LMK00101 Ultra-low Jitter LVCMOS Fanout Buffer/Level Translator with Universal Input10.0 Electrical Characteristics(2.375 V ≤ Vdd ≤ 3.45 V, 1.425 ≤ Vddo ≤ Vdd, -40 °C ≤ T A ≤ 85 °C, Differential inputs. Typical values represent most likely parametric norms at Vdd = Vddo = 3.3 V, T A = 25 °C, at the Recommended Operation Conditions at the time of product charac-terization and are not guaranteed). Test conditions are: F test = 100 MHz, Load = 5 pF in parallel with 50 Ω unless otherwise stated.SymbolParameterTest ConditionsMinTypMaxUnitsTotal Device CharacteristicsVddCore Supply Voltage2.3752.5 or3.33.45VVddo Output Supply Voltage 1.425 1.5,1.8,2.5, or3.3Vdd VI VddCore CurrentNo CLKin1625mAV ddo = 3.3 V, F test = 100 MHz 24 V ddo = 2.5 V, F test = 100 MHz 20 I Vddo[n]Current for Each OutputV ddo = 2.5 V,OE = High, F test = 100 MHz5 mAV ddo = 3.3 V,OE = High, F test = 100 MHz7 OE = Low 0.1 I Vdd + I VddoTotal Device Current with Loads onall outputsOE = High @ 100 MHz95 mAOE = Low16Power Supply Ripple Rejection (PSRR)PSRRRipple Induced Phase Spur Level100 kHz, 100 mVpp Ripple Injected on V dd , V ddo = 2.5 V-44dBcOutputs (Note 6)Skew Output Skew Measured between outputs,referenced to CLKout06 ps f CLKoutOutput Frequency(Note 7)DC 200MHzt Rise Rise/Fall Time V dd = 3.3 V, V ddo = 1.8 V, C L = 10 pF500 psV dd = 2.5 V, V ddo = 2.5 V, C L = 10 pF 300 V dd = 3.3 V, V ddo = 3.3 V, C L = 10 pF200 V CLKout Low Output Low Voltage 0.1V V CLKout High Output High Voltage Vddo-0.1 R CLKoutOutput Resistance50 ohm t jRMS Additive Jitterf CLKout = 156.25 MHz,CMOS input slew rate ≥ 2 V/ns C L = 5 pF, BW = 12 kHz to 20 MHz30fs 4L M K 00101 U l t r a -l o w J i t t e r L V C M O S F a n o u t B u f f e r /L e v e l T r a n s l a t o r w i t h U n i v e r s a l I n p u tSymbol Parameter Test ConditionsMin Typ Max UnitsDigital Inputs (OE, SEL0, SEL1)V Low Input Low Voltage Vdd = 2.5 V 0.4VV High Input High Voltage Vdd = 2.5 V 1.3 Vdd = 3.3 V1.6 I IH High Level Input Current 50uAI IL Low Level Input Current -5 5CLKin0/0* and CLKin1/1* Input Clock Specifications, (Note 9, Note 10)I IH High Level Input Current V CLKin = Vdd 20uA I IL Low Level Input Current(Note 8)V CLKin = 0 V-20 uA V IH Input High Voltage Vdd VV ILInput Low VoltageGND V CMDifferential InputCommon Mode Input Voltage(Note 12)V ID = 150 mV0.5 Vdd-1.2VV ID = 350 mV 0.5 Vdd-1.1V ID = 800 mV0.5 Vdd-0.9V ID Differential Input Voltage Swing CLKin driven differentially 0.15 1.5V OSCin/OSCout Pinsf OSCinInput Frequency (Note 7)Single-Ended Input, OSCout floatingDC200MHzf XTALCrystal Frequency Input Range Fundamental Mode Crystal ESR < 200 Ω ( f Xtal ≤ 30 MHz )ESR < 120 Ω ( f Xtal > 30 MHz )(Note 11, Note 7)10 40MHzC OSCinShunt Capacitance1 pFNote 6:AC Parameters for CMOS are dependent upon output capacitive loading Note 7:Guaranteed by characterization.Note 8:V IL should not go below -0.3 volts.Note 9:See Section 12.1 Differential Voltage Measurement Terminology for definition of V ID and V OD .Note 10:Refer to application note AN-912 Common Data Transmission Parameters and their Definitions for more information.Note 11:The ESR requirements stated are what is necessary in order to ensure that the Oscillator circuitry has no start up issues. However, lower ESR values for the crystal might be necessary in order to stay below the maximum power dissipation requirements for that crystal.Note 12:When using differential signals with V CM outside of the acceptable range for the specified V ID , the clock must be AC coupled.LMK00101 Ultra-low Jitter LVCMOS Fanout Buffer/Level Translator with Universal Input30146942Iddo per Output vs Frequency50100150200250051015C U R R E N T (m A )FREQUENCY (MHz)Cload = 10 pFVddo = 1.5 V Vddo = 1.8 V Vddo = 2.5 V Vddo = 3.3 V 30146976Note 13:Test conditions: LVCMOS Input, slew rate ≥ 2 V/ns, C L = 5 pF in parallel with 50 6L M K 00101 U l t r a -l o w J i t t e r L V C M O S F a n o u t B u f f e r /L e v e l T r a n s l a t o r w i t h U n i v e r s a l I n p u t12.0 Measurement Definitions12.1 Differential Voltage Measurement TerminologyThe differential voltage of a differential signal can be de-scribed by two different definitions causing confusion when reading datasheets or communicating with other engineers. This section will address the measurement and description of a differential signal so that the reader will be able to under-stand and discern between the two different definitions when used.The first definition used to describe a differential signal is the absolute value of the voltage potential between the inverting and non-inverting signal. The symbol for this first measure-ment is typically VID or VODdepending on if an input or outputvoltage is being described.The second definition used to describe a differential signal is to measure the potential of the non-inverting signal with re-spect to the inverting signal. The symbol for this second measurement is VSSand is a calculated parameter. Nowherein the IC does this signal exist with respect to ground, it onlyexists in reference to its differential pair. VSScan be measured directly by oscilloscopes with floating references, otherwisethis value can be calculated as twice the value of VODas de-scribed in the first sectionFigure 1 illustrates the two different definitions side-by-side for inputs and Figure 2 illustrates the two different definitionsside-by-side for outputs. The VIDand VODdefinitions showVAand VBDC levels that the non-inverting and inverting sig-nals toggle between with respect to ground. VSSinput and output definitions show that if the inverting signal is consid-ered the voltage potential reference, the non-inverting signal voltage potential is now increasing and decreasing above and below the non-inverting reference. Thus the peak-to-peak voltage of the differential signal can be measured.VIDand VODare often defined in volts (V) and VSSis oftendefined as volts peak-to-peak (VPP).30146912FIGURE 1. Two Different Definitions for Differential Input Signals30146913FIGURE 2. Two Different Definitions for Differential Output Signals LMK00101 Ultra-low Jitter LVCMOS Fanout Buffer/Level Translator with Universal Input13.0 Functional DescriptionThe LMK00101 is a 10 output LVCMOS clock fanout buffer with low additive jitter that can operate up to 200 MHz. It fea-tures a 3:1 input multiplexer with a crystal oscillator input,single supply or dual supply (lower power) operation, and pin-programmable device configuration. The device is offered in a 32-pin LLP package.13.1 V dd and V ddo Power Supplies (Note 14, Note 15)Separate core and output supplies allow the output buffers to operate at the same supply as the Vdd core supply (3.3 V or 2.5 V) or from a lower supply voltage (3.3 V, 2.5 V, 1.8 V, or 1.5 V). Compared to single-supply operation, dual supply op-eration enables lower power consumption and output-level compatibility.Bank A (CLKout0 to CLKout4) and Bank B (CLKout5 to CLK-out9) may also be operated at different V ddo voltages, provid-ed neither V ddo voltage exceeds V dd .Note 14:Care should be taken to ensure the V ddo voltage does not exceed the Vdd voltage to prevent turning-on the internal ESD protection circuitry.Note 15:DO NOT DISCONNECT OR GROUND ANY OF THE V ddo PINS as the V ddo pins are internally connected within an output bank.13.2 CLOCK INPUTSThe LMK00101 has three different inputs, CLKin0/CLKin0*,CLKin1/CLKin1*, and OSCin that can be driven in different manners that are described in the following sections.13.2.1 SELECTION OF CLOCK INPUTClock input selection is controlled using the SEL0 and SEL1pins as shown in Table 1. Refer to Section 14.1 Driving the Clock Inputs for clock input requirements. When CLKin0 or CLKin1 is selected, the crystal circuit is powered down. When OSCin is selected, the crystal oscillator will start-up and its clock will be distributed to all outputs. Refer to Section 14.2Crystal Interface for more information. Alternatively, OSCin may be driven by a single ended clock, up to 200 MHz, instead of a crystal.TABLE 1. Input SelectionSEL1SEL0Input 00CLKin0, CLKin0*01CLKin1, CLKin1*1XOSCin (Crystal Mode)13.2.1.1 CLKin/CLKin* PinsThe LMK00101 has two differential inputs (CLKin0/CLKin0*and CLKin1/CLKin1*) that can be driven single-ended or dif-ferentially. They can accept AC or DC coupled 3.3V/2.5V LVPECL, LVDS, or other differential and singled ended sig-nals that meet the input requirements under the “CLKin0/0*and CLKin1/1* Input Clock Specifications” portion of the Sec-tion 10.0 El ectrical Characteristics and (Note 12). Refer to Section 14.1 Driving the Clock Inputs for more details on driv-ing the LMK00101 inputs.In the event that a Crystal mode is not selected and the CLKin pins do not have an AC signal applied to them, Table 2 fol-lowing will be the state of the outputs.TABLE 2. CLKinX Input vs. Output States CLKinX CLKinX*Output State Open Open Logic Low Logic Low Logic Low Logic Low Logic High Logic Low Logic High Logic LowLogic HighLogic Low13.3 CLOCK OUTPUTSThe LMK00101 has 10 LVCMOS outputs.13.3.1 Output Enable PinWhen the output enable pin is held High, the outputs are en-abled. When it is held Low, the outputs are held in a Low state as shown in Table 3.TABLE 3. Output Enable Pin StatesOE Outputs Low Disabled (Hi-Z)HighEnabledThe OE pin is synchronized to the input clock to ensure that there are no runt pulses. When OE is changed from Low to High, the outputs will initially have an impedance of about 400 Ω to ground until the second falling edge of the input clock. Starting with the second falling edge of the input clock,the outputs will buffer the input. If the OE pin is taken from Low to High when there is no input clock present, the outputs will either go High or Low and stay a that state; they will not oscillate. When the OE pin is taken from High to Low the out-puts will become Low after the second falling edge of the clock input and then will go to a Disabled (Hi-Z) state starting after the next rising edge.13.3.2 Using Less than Ten OutputsAlthough the LMK00101 has 10 outputs, not all applications will require all of these. In this case, the unused outputs should be left floating with a minimum copper length (Note 16) to minimize capacitance. In this way, this output will con-sume minimal output current because it has no load.Note 16:For best soldering practices, the minimum trace length should extend to include the pin solder mask. This way during reflow, the solder has the same copper area as connected pins. This allows for good, uniform fillet solder joints helping to keep the IC level during reflow. 8L M K 00101 U l t r a -l o w J i t t e r L V C M O S F a n o u t B u f f e r /L e v e l T r a n s l a t o r w i t h U n i v e r s a l I n p u t14.0 Application Information14.1 Driving the Clock InputsThe LMK00101 has two differential inputs (CLKin0/CLKin0*and CLKin1/CLKin1*) that can accept AC or DC coupled 3.3V/2.5V LVPECL, LVDS, and other differential and single ended signals that meet the input requirements specified in Sec-tion 10.0 Electrical Characteristics . The device can accept a wide range of signals due to its wide input common mode voltage range (V CM ) and input voltage swing (V ID )/dynamic range. AC coupling may also be employed to shift the input signal to within the V CM range.To achieve the best possible phase noise and jitter perfor-mance, it is mandatory for the input to have a high slew rate of 2 V/ns (differential) or higher. Driving the input with a lower slew rate will degrade the noise floor and jitter. For this rea-son, a differential input signal is recommended over single-ended because it typically provides higher slew rate and common-mode noise rejection.While it is recommended to drive CLKin0 and CLKin1 with a differential signal input, it is possible to drive them with a sin-gle ended clock. The single-ended input slew rate should be as high as possible to minimize performance degradation.The CLKinX input has an internal bias voltage of about 1.4 V,so the input can be AC coupled as shown in Figure 3, Figure 4, or Figure 5 depending upon the application.30146938FIGURE 3. Single-Ended LVCMOS Input, AC Coupling,Near and Far End Termination30146943FIGURE 4. Single-Ended LVCMOS Input, AC Coupling,Near End Termination30146944FIGURE 5. Single-Ended LVCMOS Input, AC Coupling,Far End Termination A single ended clock may also be DC coupled to CLKinX as shown in Figure 6. If the DC coupled input swing has a com-mon mode level near the devices internal bias of 1.4 V, then only a 0.1 µF bypass cap is required on CLKinX*. Otherwise,if the input swing is not optimally centered near the internal bias voltage, then CLKinX* should be externally biased to the midpoint voltage of the input swing. This can be achieved us-ing external biasing resistors, R B1 and R B2, or another low-noise voltage reference. The external bias voltage should be within the specified input common voltage (VCM) range. This will ensure the input swing crosses the threshold voltage at a point where the input slew rate is the highest.30146939FIGURE 6. Single-Ended LVCMOS Input, DC Couplingwith Common Mode Biasing If the crystal oscillator circuit is not used, it is possible to drive the OSCin input with an single-ended external clock as shown in Figure 7. Configurations similar to Figure 4 or Figure 5 could also be used as long as the OSCout pin is left floating. The input clock should be AC coupled to the OSCin pin, which has an internally generated input bias voltage, and the OSCout pin should be left floating. While OSCin provides an alterna-tive input to multiplex an external clock, it is recommended to use either differential input (CLKinX) since it offers higher op-erating frequency, better common mode, improved power supply noise rejection, and greater performance over supply voltage and temperature variations.LMK00101 Ultra-low Jitter LVCMOS Fanout Buffer/Level Translator with Universal Input30146903FIGURE 7. Driving OSCin with a Single-Ended ExternalClock 14.2 Crystal InterfaceThe LMK00101 has an integrated crystal oscillator circuit that supports a fundamental mode, AT-cut crystal. The crystal in-terface is shown in Figure 8.30146904FIGURE 8. Crystal InterfaceThe load capacitance (C L ) is specific to the crystal, but usually on the order of 18 to 20 pF. While C L is specified for the crys-tal, the OSCin input capacitance (C IN = 1 pF typical) of the device and PCB stray capacitance (C STRAY ~ 1 to 3 pF) can affect the discrete load capacitor values, C 1 and C 2. For the parallel resonant circuit, the discrete capacitor values can be calculated as follows:C L = (C 1 * C 2) / (C 1 + C 2) + C IN + C STRAY(1)Typically, C 1 = C 2 for optimum symmetry, so Equation 1 can be rewritten in terms of C 1only:C L = C 12 / (2 * C 1 ) + C IN + C STRAY(2)Finally, solve for C 1:C 1 = (C L - C IN - C STRAY ) * 2(3)Section 10.0 Electrical Characteristics provides crystal inter-face specifications with conditions that ensure start-up of the crystal, but it does not specify crystal power dissipation. The designer will need to ensure the crystal power dissipation does not exceed the maximum drive level specified by the crystal manufacturer. Overdriving the crystal can cause pre-mature aging, frequency shift, and eventual failure. Drive level should be held at a sufficient level necessary to start-up and maintain steady-state operation.The power dissipated in the crystal, P XTAL , can be computed by:P XTAL = I RMS 2 * R ESR * (1 + C 0 / C L )2(4)Where:•I RMS is the RMS current through the crystal.•R ESR is the maximum equivalent series resistance specified for the crystal.•C L is the load capacitance specified for the crystal.•C 0 is the minimum shunt capacitance specified for the crystal.I RMS can be measured using a current probe (e.g. Tektronix CT-6 or equivalent) placed on the leg of the crystal connected to OSCout with the oscillation circuit active.As shown in Figure 8, an external resistor, R LIM , can be used to limit the crystal drive level if necessary. If the power dissi-pated in the selected crystal is higher than the drive level specified for the crystal with R LIM shorted, then a larger resis-tor value is mandatory to avoid overdriving the crystal. How-ever, if the power dissipated in the crystal is less than the drive level with R LIM shorted, then a zero value for R LIM can be used.As a starting point, a suggested value for R LIM is 1.5 k Ω14.3 Power Supply Ripple RejectionIn practical system applications, power supply noise (ripple)can be generated from switching power supplies, digital ASICs or FPGAs, etc. While power supply bypassing will help filter out some of this noise, it is important to understand the effect of power supply ripple on the device performance.When a single-tone sinusoidal signal is applied to the power supply of a clock distribution device, such as LMK00101, it can produce narrow-band phase modulation as well as am-plitude modulation on the clock output (carrier). In the single-side band phase noise spectrum, the ripple-induced phase modulation appears as a phase spur level relative to the car-rier (measured in dBc).For the LMK00101, power supply ripple rejection (PSRR),was measured as the single-sideband phase spur level (in dBc) modulated onto the clock output when a ripple signal was injected onto the V ddo supply. The PSRR test setup is shown in Figure 9.30146940FIGURE 9. PSRR Test SetupA signal generator was used to inject a sinusoidal signal onto the V ddo supply of the DUT board, and the peak-to-peak ripple amplitude was measured at the V ddo pins of the device. A lim-iting amplifier was used to remove amplitude modulation on the differential output clock and convert it to a single-ended signal for the phase noise analyzer. The phase spur level measurements were taken for clock frequencies of 100 MHz under the following power supply ripple conditions:•Ripple amplitude: 100 mVpp on V ddo = 2.5 V •Ripple frequency: 100 kHzAssuming no amplitude modulation effects and small index modulation, the peak-to-peak deterministic jitter (DJ) can be calculated using the measured single-sideband phase spur level (PSRR) as follows:10L M K 00101 U l t r a -l o w J i t t e r L V C M O S F a n o u t B u f f e r /L e v e l T r a n s l a t o r w i t h U n i v e r s a l I n p u t分销商库存信息:NATIONAL-SEMICONDUCTORLMK00101SQX/NOPB LMK00101SQ/NOPB LMK00101SQE/NOPB LMK00101BEVAL/NOPB。

单片机 学习笔记

压缩BCD码与非压缩BCD码的压缩BCD码的每一位用4位二进制表示,一个字节表示两位十进制数。

例如1001区别——0110B表示十进制数96D;非压缩BCD码用1个字节表示一位十进制数,高四位总是0000,低4位的0000~1001表示0~9.例如00001000B表示十进制数8.中断控制技术的作用:速度匹配故障处理实时处理微处理器的两种结构从内核访问指令和数据的不同空间与总线结构,可以把处理器分为哈佛结构和普林斯顿结构(或冯.诺伊曼结构)。

冯.诺伊曼结构的机器指令、数据和I/O共用一条总线,这样内核在取指时就不能进行数据读写,反之亦然。

这在传统的非流水线处理器(如MCS51)上是没有什么问题的,它们取指、执行分时进行,不会发生冲突。

但在现代流水线处理器上,由于取指、译码和执行是同时进行的(不是同一条指令),一条总线就会发生总线冲突,必须插入延迟等待,从而影响了系统性能。

ARM7TDMI 内核就是这种结构的。

而哈佛结构的处理器采用独立的指令总线和数据总线,可以同时进行取指和数据读写操作,从而提高了处理器的运行性能。

ARM Cortex-M3、ARM966E、ARM926EJ、ARM1136JF等内核都采用了哈佛结构。

简单指令集的CPU在处理一些特定的运算时速度远高于复杂指令集,所以它常被用在工业领域,比如某些软件的专用服务器,流水线操作等方面。

RISC是英文“Reduced Instruction Set Computing ” 的缩写,中文意思是“精简指令集”。

它是在CISC指令系统基础上发展起来的,有人对CISC机进行测试表明,各种指令的使用频度相当悬殊,最常使用的是一些比较简单的指令,它们仅占指令总数的20%,但在程序中出现的频度却占80%。

复杂的指令系统必然增加微处理器的复杂性,使处理器的研制时间长,成本高。

并且复杂指令需要复杂的操作,必然会降低计算机的速度。

基于上述原因,20世纪80年代RISC型CPU诞生了,相对于CISC型CPU ,RISC型CPU不仅精简了指令系统,还采用了一种叫做“超标量和超流水线结构”,大大增加了并行处理能力。

CMX589A_datasheet(v4)

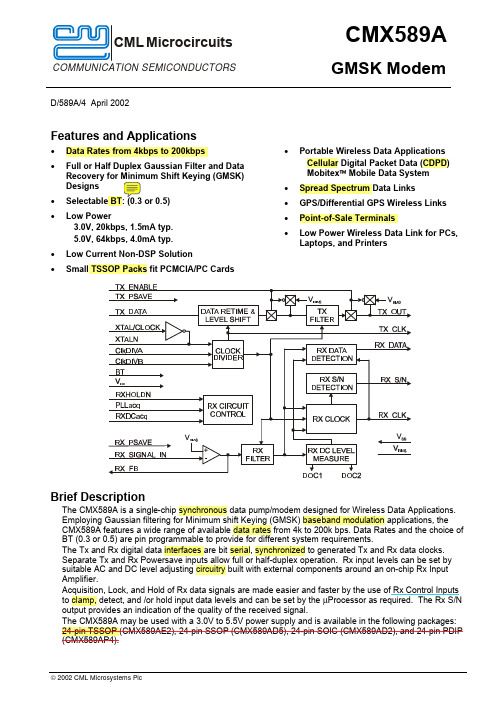

CML MicrocircuitsCOMMUNICATION SEMICONDUCTORSCMX589AGMSK ModemD/589A/4 April 2002Features and Applications• Data Rates from 4kbps to 200kbps•Full or Half Duplex Gaussian Filter and Data Recovery for Minimum Shift Keying (GMSK) Designs• Selectable BT: (0.3 or 0.5) •Low Power3.0V, 20kbps, 1.5mA typ. 5.0V, 64kbps,4.0mA typ. • Low Current Non-DSP Solution•Small TSSOP Packs fit PCMCIA/PC Cards•Portable Wireless Data Applications Cellular Digital Packet Data (CDPD) Mobitex ™ Mobile Data System • Spread Spectrum Data Links • GPS/Differential GPS Wireless Links • Point-of-Sale Terminals•Low Power Wireless Data Link for PCs,Laptops, and PrintersContentsSection Page Features and Applications (1)Brief Description (1)Block Diagram (3)2 Signal List (4)3 External Components (6)4 General Description (8)4.1 Clock Oscillator Divider (8)4.2 Receive (8)4.2.1 Rx Signal Path Description (8)4.2.2 Rx Circuit Control Modes (9)4.2.3 Rx Clock Extraction (10)4.2.4 Rx Data Extraction (10)4.2.6 Rx Signal Quality (12)4.3 Transmit (12)4.3.1 Tx Signal Path Description (12)4.4 Data Formats (14)4.5 Acquisition and Hold Modes (14)5 Application (15)5.1 Radio Channel Requirements (15)5.1.1 Bit Rate, BT, and Bandwidth (15)5.1.2 FM Modulator, Demodulator and IF (15)5.1.3 Two-Point Modulation (16)5.2 AC Coupling of Tx and Rx Signals (17)6 Performance Specifications (18)6.1 Electrical Specifications (18)6.1.1 Absolute Maximum Limits (18)6.1.2 Operating Limits (19)6.1.3 Operating Characteristics (20)6.2 Packages (22)Block DiagramFigure 1: Block Diagram2 Signal ListTable 1: Signal List3 External ComponentsFigure 3: Recommended External ComponentsComponent Notes Value Tolerance Component Notes Value Tolerance R1 1 ±5% C4 0.1µF ±20%R2 1.0MΩ±10% C5 1.0µF ±20%R3 2 ±10% C6 5 ±20%R4 3 ±10% C7 6C1 1 ±10% C8 6C2 4 C9 7C3 4 X1 8Table 2: Recommended External ComponentsRecommended External Component Notes:1. The RC network formed by R1 and C1 is required between the Tx Out pin and the input to the modulator.This network, which can form part of any DC level shifting and gain adjustment circuitry, forms animportant part of the transmit signal filtering. The ground connection to the capacitor C1 should bepositioned to give maximum attenuation of high-frequency noise into the modulator.The component values should be chosen so that the product of the resistance and the capacitance is:For a BT of 0.3 R1.C1 = 0.34/bit rate (bps)For a BT of 0.5 R1.C1 = 0.22/bit rate (bps)Data Rates (kbps)BT = 0.3 BT = 0.5 R1 C1 R1 C1 4 120k Ω 680pF 120k Ω 470pF 4.8 100k Ω 680pF 100k Ω 470pF 8 91k Ω 470pF 120k Ω 220pF 9.6 91k Ω 390pF 47k Ω 470pF 16 47k Ω 470pF 91k Ω 150pF 19.2 100k Ω 180pF 91k Ω 120pF 32 47k Ω 220pF 47k Ω 150pF 38.4 * 47k Ω 180pF 47k Ω 120pF 64 * 56k Ω 100pF 51k Ω 68pF 80 * 39k Ω 68pF 128 * 82k Ω 22pF 144 * 68k Ω 22pF 160 * 62k Ω 22pF 176 * 56k Ω 22pF 192 *51k Ω22pF* V DD ≥ 4.5V, external clockTable 3: Data Rate vs. BT and Selected External Component Values2. R3, R4 and C6 form the gain components for the Rx Input signal. R3 should be chosen as required by thesignal input level. 3. For bit rate ≤ 64kbps, R4 = 100k Ω. For bit rate > 64kbps, R4 = 10k Ω.4. The values chosen for C2 and C3 (including stray capacitance), should be suitable for the applied V DDand the frequency of X1.As a guide: C2 = C3 = 33pF at 1.0MHz falling to 18pF at the maximum frequency.At 3.0V, C2 = C3 = 33pF falling to 18pF at 5.0MHz the equivalent series resistance of X1 should be less than 2.0K Ω falling to 150Ω at the maximum frequency. Stray capacitance on the Xtal/Clock circuit pins must be minimized. 5. For bit rate ≤ 64kbps, C6 = 22pF. For bit rate > 64kbps, C6 =Ω×π××10k 2 rate bit 31e.g. for 128kbps, C6 = 41.1pF.6. C7 and C8 should both be .015µF for a data rate of 8kbps, and inversely proportional to the data rate forother data rates, e.g. 0.030µF at 4kbps, 1800pF at 64kbps, 680pF at 192kbps. 7. The tolerance of C9 is not very critical because it primarily serves as a dc blocking capacitor.8. The CMX589A can operate correctly with the Xtal frequencies between 1.0MHz and 16.0MHz(V DD = 5.0V) and 1.0MHz to 5.0MHz (V DD = 3.0V). External clock frequencies up to 25.6MHz(V DD ≥ 4.5V) are also supported (See Table 4 for examples.) For best results, a crystal oscillator design should drive the clock inverter input with signal levels of at least 40% of V DD , peak to peak. Tuning fork crystals generally cannot meet this requirement. To obtain crystal oscillator design assistance, consult your crystal manufacturer. Operation of this device without a Xtal or Clock input may cause device damage.4 General Description4.1 Clock Oscillator DividerThe Tx and (nominal) Rx data rates are determined by division of the frequency present at the XTALN pin as generated by the on-chip Xtal oscillator, with external components, or supplied from an external source. The division ratio is controlled by the logic level inputs on ClkDivA and ClkDivB pins as shown in Table 4, together with an indication of how various standard data rates may be derived from common µP Xtal frequencies.A/B)(ClkDiv Ratio Division FrequencyXtal/ClkRate Data =* V DD ≥ 4.5V, external clockTable 4: Example Clock/Data RatesNote : The device operation is not guaranteed above 200kbps or below 4kbps at the relevant supply voltage.Figure 4: Minimum µController System Connections4.2 Receive4.2.1Rx Signal Path DescriptionThe function of the Rx circuitry is to: 1. Set the incoming signal to a usable level. 2. Clean the signal by filtering.3. Provide dc level thresholds for clock and data extraction.4. Provide clock timing information for data extraction and external circuits.5. Provide Rx data in a binary form.6. Assess signal quality and provide Signal-to-Noise information.The output of the radio receiver's Frequency Discriminator should be fed to the CMX589A's Rx Filter by a suitable gain and DC level adjusting circuit. This circuit can be built with external components around the on-chip Rx Input Amplifier. The gain should be set so that the signal level at the Rx Feedback pin is nominally 1V peak to peak (for V DD =5.0V) centered around V BIAS when receiving a continuous 1111000011110000.. data pattern.Positive going signal excursions at Rx Feedback pin will produce a logic ‘0’ at the Rx Data Output. Negative going excursions will produce a logic ‘1’.The received signal is fed through the lowpass Rx Filter, which has a -3dB corner frequency of 0.56 times the data bit-rate, before being applied to the Level Measure and Clock and Data extraction blocks.The Level Measuring block consists of two voltage detectors, one of which measures the amplitude of the positive parts of the received signal. The other measures the amplitude of the negative portions. (Positive levels are then used to establish the optimum DC level decision-thresholds for the Clock and Data extraction, depending upon the Rx signal amplitude and any DC offset. 4.2.2Rx Circuit Control ModesThe operating characteristics of the Rx Level Measurement and Clock Extraction circuits are controlled, as shown in Table 6, by logic level inputs applied to the PLLacq, Rx HOLDN and RxDCacq pins to suit a particular application, or to cope with changing reception conditions, reference Figure 5.In general, a data transmission will begin with a preamble, for example, 1100110011001100, to allow the receive modem to establish timing and level-lock as quickly as possible. After the Rx carrier has been detected, and during the time that the preamble is expected, the RxDCacq and PLLacq Inputs should be switched from a logic ‘0’ to a logic ‘1’ so that the Level Measuring and Clock Extraction modes are operated and sequenced as shown.The Rx HOLDN input should normally be held at a logic ‘1’ while data is being received, but may be driven to a logic ‘0’ to freeze the Level Measuring Clock Extraction circuits during a fade. If a fade lasts for less than 200 bit periods, normal operation can be resumed by returning the Rx HOLDN input to a logic ‘1’ at the end of the fade. For longer fades, it may be better to reset the Level Measuring circuits by placing the RxDCacq to a logic ‘1’ for 10 to 20 bit periods.Rx HOLDN has no effect on the Level Measuring circuits while RxDCacq is at a logic ‘1’, and has no effect on the PLL while PLLacq is at a logic ‘1’.A logic ‘0’ on Rx HOLDN does not disable the Rx Clock output, and the Rx Data Extraction and S/N Detector circuits will continue to operate.Figure 5: Rx Mode Control DiagramPLLacq RxHOLDNPLL Action1 1 Acquire Sets the PLL bandwidth wide enough to allow a lock to thereceived signal in less than 8 zero crossings. This mode willoperate as long as PLLacq is a logic “1”.1 to 0 1 MediumBandwidth The correction applied to the extracted clock is limited to a maximum of ±1/16th bit-period for every two received zero-crossings. The PLL operates in this mode for a period of about 30 bits immediately following a 1 to 0 transition of the PLLacq input, provided that the Rx HOLDN input is a logic ‘1’.0 1 NarrowBandwidth The correction applied to the extracted clock is limited to a maximum of ±1/64th bit-period for every two received zero-crossings. The PLL operates in this mode whenever the Rx HOLDN Input is a logic ‘1’ and PLLacq has been a logic ‘0’ for at least 30 bit periods (after Medium Bandwidth operation for instance).0 0 Hold The PLL feedback loop is broken, allowing the Rx Clock tofreewheel during signal fade periods.Table 5: PLL Action Measurement Operational ModesRxDCacq RxHOLDNRx Level Measure Action0 to 1 X Clamp Operates for one bit-time after a 0 to 1 transition of theRXDCacq input. The external capacitors are rapidly chargedtowards a voltage mid-way between the received signal inputlevel and V BIAS, with the charge time-constant being of theorder of 0.5 bit-time.1 X Fast Peak Detect The voltage detectors act as peak-detectors, one capacitor isused to capture the positive-going signal peaks of the RxFilter output signal and the other capturing the negative-going peaks. The detectors operate in this mode wheneverthe RXDCacq input is at a logic ‘1’, except for the initial 1-bitClamp-mode time.0 1 Averaging PeakDetect Provides a slower but more accurate measurement of the signal peak amplitudes.0 0 Hold The capacitor charging circuits are disabled so that theoutputs of the voltage detectors remain substantially at thelast readings (discharging very slowly [time-constant approx.2,000 bits] towards V BIAS).X = Do not careTable 6: Rx Level Measurement Operational Modes4.2.3 Rx Clock ExtractionSynchronized by a PLL circuit to zero-crossings of the incoming data, the Rx Clock Extraction circuitry controls the Rx Clock output. The Rx Clock is also used internally by the Data Extraction circuitry. The PLL parameters can be varied by the Rx Circuit Control inputs PLLacq and Rx HOLDN to operate in one of four PLL modes as described in Table 5 and Table 6.4.2.4 Rx Data ExtractionThe Rx Data Extraction circuit decides whether each received bit is a 1 or 0 by sampling the received signal, after filtering, and comparing the sample values to an adaptive threshold derived from the Level Measuring circuit. This threshold is adapted from bit to bit to compensate for intersymbol interference caused by the and limiting of the overall transmission path and the Gaussian premodulation filter. Extracted data is output from the Rx Data pin, and should be sampled externally on the rising edge of the Rx CLK.4.2.5 Rx S/N DetectionThe Rx S/N Detector system classifies the incoming zero-crossings as GOOD or BAD depending upon the time when each crossing actually occurs with respect to its expected time as determined by the Clock Extraction PLL. This information is then processed to provide a logic level output at the Rx S/N pin. A high level indicates a series of GOOD crossings; a low level indicates a BAD crossing.By averaging this output, it is possible to derive a measure of the Signal-to-Noise-Ratio and hence theBit-Error-Rate of the received signal.Figure 6: Typical Bit-Error-Rate Performance at V DD = 5.0VNote: Figure 6 indicates typical performance, independent of bit rate (although the applied noise bandwidth is considered to match the bit rate used), radio performance (e.g. IF filter distortion), supply voltage (higher bit rates require V DD≥ 4.5V), and other ‘real world’ factors.4.2.6 Rx Signal QualityThe effect of input Rx Signal quality on the Rx S/N output is shown in Figure 7.When power is subsequently restored to the Tx filter, its output will take several bit-times to settle. The Tx Enable input can be used to prevent these abnormal voltages from appearing at the Tx Out pin.Figure 9: Tx Filter ResponseFigure 11: Tx Output Spectrum (Random Data)4.4 Data FormatsThe receive section of the CMX589A works best with data which has a reasonably random structure --the data should contain approximately the same number of ‘ones’ as ‘zeroes’ with no long sequences (>100 bits) of consecutive ones or zeroes. Also, long sequences (>100 bits) of 10101010 ... patterns should be avoided. For this reason, it is recommended that data be made random in some manner before transmission, forexample by exclusive-ORing it with the output of a binary pseudo-random pattern generator.Where data is transmitted in bursts, each burst should be preceded by a preamble designed to allow the receive modem to establish timing and level lock as quickly as possible. This preamble for BT=0.3 should be at least 16 bits long, and should preferably consist of alternating pairs of ones and zeros i.e. 110011001100....; the eye of pattern 10101010 .... has the most gradual slope and will yield poor peak levels for the Rx circuits. For BT=0.5 the eye pattern of 10101010... has reduced intersymbol interference and may be used as the preamble (DC Acq pin should be held high during preamble). See Figure 5.4.5 Acquisition and Hold ModesThe RXDCacq and PLLacq inputs must be pulsed High for about 16 bits at the start of reception to ensure that the DC measurement and timing extraction circuits lock-on to the received signal correctly. Once lock has been achieved, the above inputs should be taken Low again.In most applications, there will be a DC step in the output voltage from the receiver FM discriminator due to carrier frequency offsets as channels are changed or when the remote transmitter is turned on.The CMX589A can tolerate DC offsets in the received signal of at least ±10% of V DD with respect to V BIAS, (measured at the Rx Feedback pin). However, to ensure that the DC offset compensation circuit operates correctly and with minimum delay, the Low to High transition of the RXDCacq and PLLacq inputs should occur after the mean input voltage to the CMX589A has settled to within about 0.1V of its final value.Note: This can place restrictions on the value of any series signal coupling capacitor.As well as using the Rx Hold input to freeze the Level Measuring and Clock Extraction circuits during a signal fade, it may also be used in systems which use a continuously transmitting control channel to freeze the Rx circuitry during transmission of a data packet, allowing reception to resume afterwards without losing bit synchronization. To achieve this, the CMX589A Xtal clock needs to be accurate enough that the derived RxClock output does not drift by more than about 0.1 bit time from the actual received data-rate during the time that the RxHold input is ‘Low’.However; the RXDCacq input may need to be pulsed High for 2 bit durations to re-establish the level measurements if the RxHold input is Low for more that a few hundred bit-times (exact number depends on system crystal tolerances).The voltages on the Doc1 and Doc2 pins reflect the average peak positive and negative excursions of the (filtered) receive signal, and could therefore be used to derive a measure of the data signal amplitude. Note: These pins are driven from very high-impedance circuits, so that the DC load presented by any external circuitry should exceed 10MΩ to V BIAS.5 Application5.1 Radio Channel RequirementsTo achieve legal adjacent channel performance at high bit-rates, a radio with an accurate carrier frequency and an accurate modulation index is required. For optimum channel utilization, (e.g. low BER and high data-rates) attention must be paid to the phase and frequency response of both the IF and baseband circuitry.5.1.1 Bit Rate, BT, and BandwidthThe maximum data rate that can be transmitted over a radio channel depends on the following: Channel spacingAllowable adjacent channel interferenceTx filter bandwidthPeak carrier deviation (Modulation Index)Tx and Rx carrier frequency accuraciesModulator and Demodulator linearityRx IF filter frequency and phase characteristicsUse of error correction techniquesAcceptable error-rateAs a guide to MOBITEX operation, a raw data-rate of 8kbps at 12.5kHz channel spacing may be achievable -depending on local regulatory requirements- using a ±2kHz maximum deviation, a BT of 0.3, and no more than 1.5kHz discrepancy between Tx and Rx carrier frequencies. Forward error correction (FEC) could then be used with interleaving to reduce the effect of burst errors.Reducing the data-rate to 4.8kbps would allow the BT to be increased to 0.5, improving the error-rate performance.5.1.2 FM Modulator, Demodulator and IFFor optimum performance, the eye pattern of the received signal (when receiving random data) applied to the CMX589A should be as close as possible to the Transmit eye pattern examples shown in Figure 10.Of particular importance are general symmetry, cleanliness of the zero-crossings, and for a BT of 0.3, the relative amplitude of the inner eye opening.To achieve this, attention must be paid to:Linearity and frequency/phase response of the Tx frequency modulator. Unless the transmit data is especially encoded to remove low frequency components, the modulator frequency response should extend down to a few hertz. This is because two-point modulation is necessary for synthesizedradios.Bandwidth and phase response of the Rx IF filters.Accuracy of the Tx and Rx carrier frequencies -any difference will shift the received signal towardsone of the skirts of the IF filter response.Ideally, the Rx demodulator should be DC coupled to the CMX589A Rx Signal In pin (with a DC bias added to center the signal at the Rx Feedback pin at V DD/2 [V BIAS]). However, AC coupling can be used provided that:The 3dB cut-off frequency is 20Hz or below (i.e. a 0.1µF capacitor in series with 100kΩ).The data does not contain long sequences of consecutive ones or zeroes.Sufficient time is allowed after a step change at the discriminator output (resulting from channelchanging or the appearance of a RF carrier) for the voltage into the CMX589A to settle before theRXDCacq line is strobed.5.1.3 Two-Point ModulationWhen designing the CMX589A into a radio that uses a frequency synthesizer, a two-point modulation technique is recommended. This is both to prevent the radio's PLL circuitry from counteracting the modulation process, and to provide a clean flat modulation response down to DC.Figure 12 shows a suggested basic configuration to provide a two-point modulation drive from the CMX589A Tx Output using the FX019 or MX019 Digitally Controlled Quad Amplifier Array. The FX019/MX019 elements provide individual set-up, calibration and dynamic control of modulation levels. Level setting control of the amplifiers/attenuators of the FX019/MX019 is via an 8-bit data word. Note that the FX019/MX019 frequency response only supports data rates as high as 8kbps.With reference to Figure 12:The buffer amplifier is required to prevent loading of the CMX589A external RC circuit.Stage B, with R1/R2, provides suitable signal and DC levels for the VCO varactor; C1 is RFdecoupling. The drive level should be adjusted (digitally) to provide the desired deviation.Stage C, with R3/R4, provides the Reference Oscillator drive (application dependent). Thisparameter is set by adjusting for minimum AC signal on the PLL control voltage with a low-frequency modulating signal (inside the PLL bandwidth) applied.Stage D could be used with the components shown if a negative reference drive is required.Stage A provides buffering and overall level control.Figure 12: An Example of Two-Point Modulation Drive with Individual Adjustment Using theFX019/MX0195.2 AC Coupling of Tx and Rx SignalsIn practical applications, it is possible to arrange AC coupling between the CMX589A Tx Output and the frequency modulator to cut-off at a very low frequency, such as 5.0Hz. AC coupling between the receive discriminator and the input of the CMX589A may need a shorter time-constant to avoid problems from voltage steps at the output of the discriminator when changing channels or when the distant transmitter turns on.For these reasons, as well as to maintain reasonable BER, the optimum –3dB cut-off frequencies are around 5.0Hz in the Tx path and 20.0Hz in the Rx path.Figure 13 shows the typical static Bit-Error-Rate performance of the CMX589A operating under nominal conditions for various degrees of AC coupling at the Rx input and the Tx output.Data Rate = 8kbps V DD = 5.0V T AMB = 25°C Tx BT = 0.36 Performance Specifications6.1 Electrical Specifications6.1.1 Absolute Maximum LimitsExceeding these maximum ratings can result in damage to the device.General Notes Min. Typ. Max. Units Supply (V DD-V SS) -0.3 7.0 VVoltage on any pin to V SS-0.3 V DD + 0.3 VCurrentV DD-30 30 mAV SS-30 30 mAAny other pin -20 20 mA D2 / P4 PackagesTotal allowable Power dissipation800 mW at T AMB = 25°CDerating above 25°C 13 mW/°C Operating Temperature -40 85 °C Storage Temperature -55 125 °C D5 Package550 mW Total allowable Power dissipationat T AMB = 25°CDerating above 25°C 9 mW/°C Operating Temperature -40 85 °C Storage Temperature -55 125 °C E2 PackageTotal allowable Power dissipationat T AMB = 25°C 320 mWDerating above 25°C 5.3 mW/°C Operating Temperature -40 85 °C Storage Temperature -55 125 °CTable 7: Absolute Maximum Ratings6.1.2 Operating LimitsCorrect Operation of the device outside these limits is not implied.Notes Min. Typ. Max. Units Supply (V DD-V SS) 3.0 3.3/5.0 5.5 VOperating Temperature -40 85 °CRx and Tx Data RateV DD≥ 3.0V 4 32 kbpsV DD≥ 4.5V 4 200 kbpsXtal FrequencyV DD≥ 3.0V 1.0 5.0 MHzV DD≥ 4.5V 1.0 16.0 MHzExternal Clock FrequencyV DD≥ 3.0V 1 1.0 5.0 MHzV DD≥ 4.5V 1 1.0 25.6 MHzHigh Pulse Width 1 15 nsLow Pulse Width 1 15 nsTable 8: Operating LimitsOperating Limits Notes1. Timing for an external clock input to the Xtal/Clock pin.6.1.3 Operating CharacteristicsFor the following conditions unless otherwise specified.V DD = 5.0V @ T AMB = 25°CXtal/Clock Frequency = 4.096MHz, Data Rate = 8kbps, Noise Bandwidth = Bit RateStatic Values Notes Min. Typ. Max. Units Supply Current Tx PS Rx PS 1I DD (V DD = 3.0V)1 1 - 0.5 - mA0 1 - 1.0 - mA1 0 - 1.0 - mA0 0 - 1.5 - mAI DD (V DD = 5.0V)1 1 - 1.0 - mA0 1 - 2.0 - mA1 0 - 3.0 - mA0 0 - 4.0 - mAInput Logic LevelLogic 1 Input Level 3.5 - - VLogic 0 Input Level - - 1.5 VLogic Input Current 2 -5.0 - 5.0 µA Output Logic LevelLogic 1 Output Level (I OH = 120µA) 4.6 - - VLogic 0 Output Level (I OL = -120µA) - - 0.4 V Transmit Parameters -Tx OUT pin DC bias shift caused by change from-85.0 - 85.0 mV Tx Enable = 0 to Tx Enable = 1 whileTx PSAVE = 0 at 25°CTx OUT, Output Impedance 3 - 1.0 - kΩTx Out, Level 4, 10 0.8 1.0 1.2 V P-P Output DC Offset 12 -0.125 - 0.125 V Tx Data DelayBT = 0.3 5 - 2.0 2.5 bit-periods BT = 0.5 5 - 1.5 2.0 bit-periods Tx PS to Output-Stable time 6 - 4.0 - bit-periods Receive ParametersRx AmplifierInput Impedance 1.0 - - MΩOutput Impedance 7 - 10.0 - KΩVoltage Gain - 50.0 - dB Rx Filter Signal Input Level 8, 10 0.7 1.0 1.3 V P-P Rx Time Delay 9 - - 3.0 bit-periodsStatic Values Notes Min. Typ. Max. Units On-Chip Xtal OscillatorR IN10.0 - - MΩR OUT11 - 50.0 - kΩVoltage Gain 11 - 25.0 - dBTable 9: Operating CharacteristicsOperating Characteristics Notes:1. Not including current drawn from the CMX589A pins by external circuitry. See Absolute MaximumRatings.2. For V IN in the range V SS to V DD.3. For a load of 10KΩ or greater. Tx PS input at logic ‘0’; Tx Enable = ‘1’.4. Data pattern of 1111000011110000…5. Measured between the rising edge of Tx Clock and the centre of the corresponding bit at Tx Out.6. Time between the falling edge of the TXPSAVE and the Tx Out voltage stabilizing to normal outputlevels.7. For a load of 10kΩ or greater. RXPSAVE input at logic ‘0’.8. For optimum performance, Measured at the Rx Feedback pin for an 1111000011110000… pattern.9. Measured between the center of bit at Rx Signal In and corresponding rising edge of the Rx Clock.10. Levels are proportional to applied V DD11. Small signal measurement at 1.0kHz with no load on Xtal output.12. (Tx OUT enabled DC level) – (Tx Out disabled DC level) when transmitting a repeating 11110000 bitpattern.6.2 PackagesFigure 16: 24-pin SSOP Mechanical Outline: Order as part no. CMX589AD5Handling precautions: This product includes input protection, however, precautions should be taken to prevent device damage from electro-static discharge. CML does not assume any responsibility for the use of any circuitry described. No IPR or circuit patent licences are implied. CML reserves the right at any time without notice to change the said circuitry and this product specification. CML has a policy of testing every product shipped using calibrated test equipment to ensure compliance with this product specification. Specific testing of all circuit parameters is not necessarily performed.CML Microcircuits (UK )Ltd4800 Bethania Station Road -Winston-Salem - NC 27105 - USA. Tel: +1 336 744 5050, 800 638 5577 Fax: +1 336 744 5054Sales: us.sales@ Technical Support:us.techsupport@CML Microcircuits (Singapore)P teLtd。

爱迪尔门锁系统接口函数(sdk)说明[整理版]

![爱迪尔门锁系统接口函数(sdk)说明[整理版]](https://img.taocdn.com/s3/m/be6f2b3b2bf90242a8956bec0975f46527d3a729.png)

爱迪尔门锁系统接口函数(SDK)说明(动态联接库函数说明)0000000000000适用门锁接口:Lock3200.DLL,Lock3200K.DLL,Lock4200.DLL,Lock4200D.DL L,Lock5200.DLL,Lock6200.DLL,Lock7200.DLL,Lock7200D.DLL,Lock9200. DLL,Lock9200T.DLL。

0000000000000000适用门锁系统:V5.1及以上版本。

0000000000000000一、门锁函数(必须已经安装并设置好门锁系统)00000000001、Init0000000000初始化。

函数原形:000000000000000000int Init(char *server, int port, int Encoder, int TMEncoder);0000000000 00000参数:00000000000000000server [in]:字符指针,指定门锁系统数据库安装的服务器(SQL Server)名。

00000000000000000Port [in]:串口号,1-COM1,2-COM2,3-COM3,4-COM4依次类推。

0000000000000 00Encoder [in]:发行机类型,0-手动发行机,1-自动发行机。

00000000000000000TMEncoder [in]:TM发行机类型,1-DS9097E,5-DS9097U0000000000000000返回值:见注1。

0000000000000000002、 EndSession0000000000000000结束工作期。

函数原形:000000000000000000int EndSession(void);00000000000000000参数:无00000000000000000返回值:见注1。

0000000000000000003、 IssueCard0000000000000000发行客人卡。

Inovance H2U Series PLC用户手册说明书

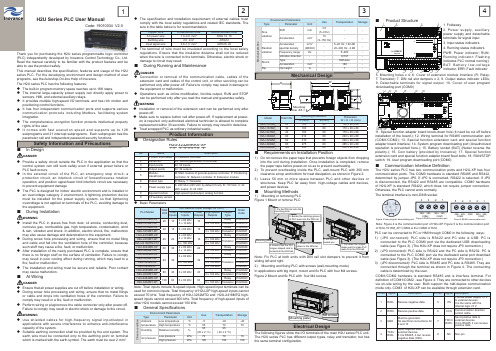

1423H2U Series PLC User ManualCode: 19010034 V2.0Thank you for purchasing the H2U series programmable logic controller (PLC) independently developed by Inovance Control Technology Co., Ltd. Read the manual carefully to be familiar with the product features and be able to use the product safely.This manual describes the specification, features and usage of the H2U series PLC. For the developing environment and design method of user programs, see the Autoshop On-line Help of Inovance.The H2U series PLC has the following features:◆The built-in program memory space reaches up to 16K steps.◆The internal large-capacity power supply can directly apply power tosensors, HMI, and external auxiliary relays.◆It provides multiple high-speed I/O terminals, and has rich motion andpositioning control functions.◆It has four independent communication ports and supports variouscommunication protocols including Modbus, facilitating system integration.◆The comprehensive encryption function protects intellectual propertyrights of the user.◆It comes with fast execution speed and supports up to 128subprograms and 21 interrupt subprograms. Each subprogram has the parameter call and independent password security functions.Safety Information and PrecautionsIn Design◆Provide a safety circuit outside the PLC in the application so that thecontrol system can still work safely even if external power failure or PLC fault occurs.◆In the external circuit of the PLC, an emergency stop circuit, aprotection circuit, an interlock circuit of forward/reverse rotation operation, and position upper/lower limit interlock circuit are necessary to prevent equipment damage ◆The PLC is designed for indoor electric environment and is installed in an overvoltage category 2 environment. A lightning protection device must be installed for the power supply system, so that lighteningovervoltage is not applied on terminals of the PLC, avoiding damage to the equipment.During Installation◆Install the PLC in places free from dust, oil smoke, conducting dust,corrosive gas, combustible gas, high temperature, condensation, wind & rain, vibration and shock. In addition, electric shock, fi re, malfunction may also cause damage and deterioration to the equipment.◆During screw hole processing and wiring, ensure that no metal filingand cable end fall into the ventilation hole of the controller, because such stuff may cause a fi re, fault, or malfunction.◆After installation of the newly purchased PLC is complete, ensure thatthere is no foreign stuff on the surface of ventilation. Failure to comply may result in poor cooling effect during running, which may lead to a fi re, fault or malfunction.◆The installation and wiring must be secure and reliable. Poor contactmay cause malfunction.◆Ensure that all power supplies are cut off before installation or wiring.◆During screw hole processing and wiring, ensure that no metal filings or cable end drops into ventilation holes of the controller. Failure to comply may result in a fi re, fault or malfunction.◆Perform wiring or plug/remove the cable connector only after power-off.◆The specification and installation requirement of external cables mustcomply with the local safety regulations and related IEC standards. The size in the table below is for recommendation.Copper Wire Cross-section Area Recommended CodeAC power wire 1.0–2.0 mm²AWG 12, 18Earthing wire 2.0 mm²AWG12Input signal wire0.8–1.0 mm²AWG18, 20◆The terminal of wire must be insulated according to the local safetyregulations. Ensure that the insulation distance shall not be reduced when the wire is connected to the terminals. Otherwise, electric shock or damage to circuit may result .During Running and Maintenance◆Connection or removal of the communication cable, cables of theextension card and cables of the control unit, or other servicing can be performed only after power-off. Failure to comply may result in damage to the equipment or malfunction.◆Operations such as online modification, forcible output, RUN and STOPProduct Information■Designation RulesH2u-3232MRAX-XP123456789No. NameDescription1Product information H: Inovance controller2Series No.2U: Second generation of controller 3Input points 32: 32 inputs 4Output points 32: 32 outputs5Module classifi cation M: Main module of general-purpose controller, P: Positioning controller, N: Network controller, E: Extension module 6Output type R: Relay, T: Transistor7Power supply type A: 220 VAC (220 VAC by default if null), B: 110 VAC, C: 24 VAC output, D: 24 VDC8Special functionHigh-speed input/output, analog function9XP auxiliary version -◆Basic ParametersPLC Model Total I/Os I/O Features (Input Voltage: 24 VDC)Order Code Total Inputs Hi-Speed Inputs Total Outputs High-Speed Outputs Output TypeH2U-1010MR-XP 2010 2 x 60 kHz6 x 10 kHz 10-Relay 01022078H2U-1010MT-XP 3 x 100 kHz Transistor01022079H2U-1616MR-XP 3216 6 x 60 kHz 16-Relay01022040H2U-1616MT-XP 3 x 100 kHz Transistor01022041H2U-2416MR-XP 4024 2 x 60 kHz4 x 10 kHz 16-Relay 01022048H2U-2416MT-XP 2 x 100 kHzTransistor01022049H2U-2416MTQ-F01 6 x 100 kHz 5 x 100 kHz01028063H2U-3624MR-XP 6036 2 x 60 kHz4 x 10 kHz 24-Relay 01022046H2U-3624MT-XP 2 x 100 kHz Transistor01022047H2U-3232MR-XP 6432 6 x 60 kHz32-Relay01022050H2U-3232MT-XP 3 x 100 kHzTransistor01022045H2U-3232MTQ 6 x 100 kHz 5 x 100 kHz 01022015H2U-3232MTP -8 x 100 kHz01022061H2U-4040MR-XP 8040 6 x 60 kHz 40-Relay01022042H2U-4040MT-XP 3 x 100 kHz Transistor01022062H2U-6464MR-XP 12864 6 x 60 kHz 64-Relay01022043H2U-6464MT-XP3 x 100 kHz Transistor01022044Note: Total inputs include hi-speed inputs. High-speed input terminals can be used for common inputs. Total frequency of H2U-XP high-speed inputs cannot exceed 70 kHz. Total frequency of H2U-3232MTQ and H2U-2416MTQ high-speed inputs cannot exceed 600 kHz. Total frequency of high-speed inputs of other H2U models cannot exceed 100 kHz.At Wiring◆Use shielded cables for high-frequency signal input/output inapplications with severe interference to enhance anti-interference capacity of the system.◆Suitable earthing connection shall be provided by the end system. Theearth wire must be connected only to the earthing point on terminal which is marked with the earth symbol. The earth must be over 2 mm².◆Installation or removal of the extension card can be performed only afterpower-off.◆Make sure to replace button cell after power-off. If replacement at power-on is required, only authorized electrical technician is allowed to complete replacement within 30 seconds. Failure to comply may result in data loss. ◆Treat scrapped PLC as ordinary industrial waste.Environment ParametersUse TransportationStorageTypeParameterUnit M e c h a n i c a l s t r e sSine vibration Shift mm 3.5 (5–9 Hz)--Acceleration m/s 210 (9–150 Hz)--Random vibrationAcceleration spectral density m 2/s 3 (dB/Oct)-5–20 Hz: 1.92 dB 20–200 Hz: -3 dB-Frequency range Hz -5–200-Vibration direction --X/Y/Z -Shock Type--Half-sine -Acceleration m/s 2-180-DipDip heightm-1-Mechanical DesignModel Total I/Os Mounting Dimension Dimension W × H × D (mm)A (mm) B (mm)H2U-1010M_2012080130 x 90 x 88H2U-1616M_32 16080170 x 90 x 88H2U-2416M_4016080170 x 90 x 88H2U-3624M_6021080220 x 90 x 88H2U-3232M_6421080220 x 90 x 88H2U-4040M_8027580285 x 90 x 88H2U-6464M_12834080350 x 90 x 88■Requirements on Installation Position1) Do not remove the paper tape that prevents foreign objects from droppinginto the unit during installation. Once installation is completed, remove the paper tape before power-on so as to prevent overheating.2) To prevent overheating inside the PLC, wall-mount PLC with 300 mmclearance at top and bottom for heat dissipation, as shown in Figure 2.3) Leave 50 mm or more space between PLC and other devices orstructures. Keep PLC far away from high-voltage cables and devices, and power devices.■Mounting Methods1) Mounting or removing PLC Figure 1 Mount or remove PLCDAW BHMounting Hole Ф5 × 4■ Product Structure11. Special function adapter board knock-down hole (It need be cut off before installation of the board.); 12. Wiring terminal for RS485 communication port (COM1/COM2); 13. Special function extension card and special function adapter board interface; 14. System program downloading port (Unauthorized operation is prevented here.); 15. Battery socket (BAT) (Neber reverse the polarity.); 16. Coin battery (provided by Inovance); 17. Special function extension card and special function adapter board fi xed bolts; 18. RUN/STOP switch; 19. User program downloading port (COM0)Note: Fix PLC at both ends with DIN rail slot dampers to prevent it from sliding left and right.2) Mounting and fi xing PLC with screws (wall-mounting mode)In applications with big impct, mount and fi x PLC with four M4 screws.Figure 2 Mount and fi x PLC with four M4 screws2. Buckle the catching groove of PLC base into the DIN rail .3. Press PLC vertically down to the DIN rail .1. Fix the DIN rail onto the mounting plate4. Ensure that the PLC tongue shaped card is locked into the DIN rail .Mounting plate1. Pull down the tongue shape card to make PLC away from the DIN rail .2. Lift the PLC toward you.■Communication Interface Defi nitionThe H2U series PLC has two communication ports and H2U-XP has four communication ports. The COM0 hardware is standard RS485 and RS422, determined by jumper JP0. If JP0 is connected, RS422 is selected. If JP0 is disconnected, the RS422 and RS485 are compatible. COM0 hardware of H2U-XP is standard RS422, which does not require jumper connection. Otherwise, the PLC cannot work normally. The terminal interface is mini-DIN8 socket.⑧①②③④⑤⑥⑦Figure 3 User program downloading port 421485+ 485-COM13485+ 485-COM2Figure 4 RS 485 communication port 421485+ 485-COM13485+ 485-COM25GNDFigure 5 RS 485 communication portNote: Figure 4 is the communication port of H2U-XP . Figure 5 is the communication port of H2U-1010M_XP . COM2 is the COM0 of H2U.PLC can be connected to PC or HMI through COM0 in the following ways:1) (JP0 connected): PLC side is RS422 and PC side is USB. PC isconnected to the PLC COM0 port via the dedicated USB downloading cable (see Figure 3). (The H2U-XP does not require JP0 connection.)2) (JP0 connected): PLC side is RS422 and the PC side is RS232. PC isconnected to the PLC COM0 port via the dedicated serial port download cable (see Figure 3). (The H2U-XP does not require JP0 connection.)3) (JP0 disconnected): PLC side is RS485 and PC side is RS485. They areconnected through the terminal as shown in Figure 4. The connecting cable is determined by the user.■General Specifi cationsEnvironment ParametersUse Transportation Storage Type Parameter Unit C l i m a t e c o n d i t i o nAmbient temperature Low temperature °C -5-40-40High temperature °C 557070Humidity Relative humidity %95 (30 ± 2 °C)95( 40 ± 2 °C)-Air pressureLow pressure kPa 707070High pressurekPa106106106Electrical DesignThe following fi gures show the I/O terminals of the main H2U series PLC unit. The H2U series PLC has different output types, relay and transistor, but has the same terminal confi guration.M4 screwsMounting plate1. Foldaway2. Power supply, auxiliary power supply and detachable terminals for signal input3. Input status indicators4. Running status indicators PWR: Power indicator; RUN: Running indicator: Flashing indicates PLC normal running); B AT: B a t t e r y l o w -v o l t a g e indicator; ERR: Fault indicator5. Mounting holes x 4;6. Cover of extension module interface (R: Relay; T: Transistor)7. DIN rail slot dampers x 2;8. Output status indicator LEDs;9. Detachable terminals for signal output; 10. Cover of user program downloading port (COM0)COM1/COM2 hardware is standard RS485 and is interface terminal. For defi nition of COM1/COM2 , see Figure 4. They are connected to other devices via on-site wiring by the user. Both support the half-duplex communication mode only. COM3 of H2U-XP can be available through extension card.Pin No.Signal DescriptionPin No.Signal Description1RXD-Receive negative data.5+5VProvide power supply +5 V to external devices.It is the same with the internal logic +5 V.2RXD+Receive positive data.6CCSCommunication directioncontrol cable3GNDMust be grounded.No electrical connections for 9 and 107TXD+/RXD+Send positive data toexternal devices.If it is RS485, it can receivepositive data.4TXD-/RXD-Send negative data to external devices.If it is RS485, it can receive negative data (H2U).8NC Non-pinThe following figure shows the internal equivalent circuit of PLC in the relay output mode. The output terminals are divided into several groups, and the groups are electrically isolated. The output contacts of different groups are connected with different power circuits.Figure 8 Internal equivalent circuit of PLC in the relay output mode The following figure shows the internal equivalent circuit of PLC in the transistor output mode.The output terminals are divided into several groups, and the groups are electrically isolated. The transistor output can be used for 24 VDC load circuit only.Figure 9 Internal equivalent circuit of PLC in the transistor output modeProduct Warranty CardCustomerinformationAddress:Company name:Postcode:Contact person:Tel or Email:ProductinformationProduct model:Serial No (Attach here):Name of supplier who supplied you the unit:Failure Description (eg. Fault code)Maintenance personnel:The soft components within [ ] are the battery backup area.• Note 1: Non-battery backup area can be changed into battery backup areavia parameter setting.• Note 2: Battery backup area can be changed into non-battery backup areavia parameter setting.• Note 3: Such permanent battery backup area cannot be changed.■ Programming requirements1) One PC with Microsoft Windows XP or Windows 7 system2) Inovance AutoShop (version 2.0 or above) for the purpose of writing anddownloading user programs3) Inovance USB-mini DIN8 download cable or mouse head download cablefor PC with DB9-type RS232 port■Input SpecificationsThe internal signal circuit composition and external wiring mode of the H2U Series PLC are desribed here. The terminal names in the wiring example vary with the PLC models.The connecting mode is effective to all input points of the PLC.■Output SpecificationsThe H2U series PLC has relay output and transistor output. Their parametersare quite differently. Please select the correct output type so as to avoid misuse. Failure to comply may result in damage to the PLC.The current of transistor output terminals must be less than the allowable maximum current. If the output current of multiple transistor terminals is greater than 100 mA, they should be evenly arranged but not be arranged adjacently, convenient for heat dissipation.It is suggested that the output points, which are set to ON simultaneously, doPLC has a built-in power supply (24 VDC) to detect user switch status, so you only need to connect input signals of dry contact. OC output type is needed if you connect an active transistor or sensor.Output group 0Output group 1Output group 3Output group 0Output group 1Output group 3and for the inductive load in DC circuit, you need add a freewheeling diode, as shown in the following figure.Figure 10 Inductive load absorption circuit,2 WPLC signal input and internal equivalent circuit are shown as Figure 6 below. Circuit of the user and the PLC internal circuit are connected by the terminal. Figure 6 shows the SINK input mode, determined by short connection of the terminal S/S and the terminal 24V.Figure 6 SINK input modeFigure 7 SOURCE input mode24VCOMS /SX0X1X2X2Xn24VDC For self-powered deviceV a r i o u s s i g n a l i n p u t d e v i c e sUser signal wiringI n t e r n a l e q u i v a l e n t c i r c u i t o f P L COutput 3 applies power to sensor. It can also provide external power supply to special function modules. Output 2 provides power supply to the main module and the relay of I/Os of expansion module. Output1 provides power to all modules. During system configuration, make sure that the demand of each power supply does not exceed its maximum capacity.■Terminal Block Definition◆Terminal block definition of H2U-1010MR-XP and H2U-1010MT-XPWhen using H2U-1010MT-XP, Y0, Y1 and Y2 require external powersupply. The user can connect 24VDC(24 V ± 20%) power supply toterminals V+ and V-. Terminal V- hasbeen shorted to COM0 internally. ◆Terminal block definition of H2U-1616MR and H2U-1616MT◆Terminal block definition of H2U-2416MR and H2U-2416MT◆Terminal block definition of H2U-2416MTQ-F01◆Terminal block definition of H2U-3232MTQ (same as that of H2U-3232MTP)■Power S upply Capacitance and Expansion CapacityThe main module and active expansion module of PLC provide power supply toexpansion modules, extension cards and adapters. The I/O points of expansion modules and the number of special function expansion modules must be within the power supply capacitance of the main module or active expansion module.For calculation on power supply capacitance, take the following aspects into considerations:• Each power supply capacitance should be calculated independently.• The expansion capacity is decided by the smaller power supplycapacitance.For example: 24VDD allows connection of six expansion modules, while +5V only allows connection of eight expansion modules. So the system can only be extended up to six expansion modules.■Selection of Extension DeviceWhen designing an H2U series PLC system, we must consider the followingaspects:◆Total I/Os should be within 256 for a main PLC system.◆Power supply capacitance (see Power Supply Specification)◆main modules and active expansion modules can provide 24 VDC and 5VDC power supply to expansion modules and special modules. But total power consumption of all expansion units should be restricted within the power supply capacitance of main module or the active expansion module. ◆The H2U series PLC can be connected to maximum 8 special modules.◆Terminal block definition of H2U-3232MTQ (same as that of H2U-3232MTP)◆Terminal block definition of H2U-6464MR and H2U-6464MT◆。

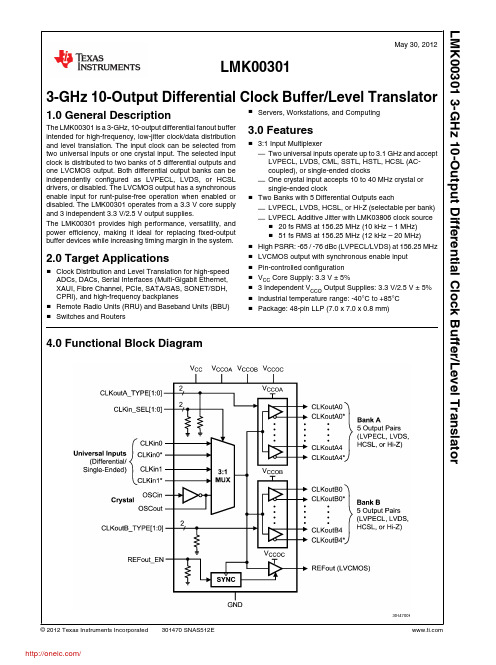

LMK00301SQXNOPB;LMK00301SQNOPB;LMK00301SQENOPB;LMK00301EVALNOPB;中文规格书,Datasheet资料