LTC4253AIGN-ADJ#PBF;LTC4253AIGN-ADJ#TRPBF;中文规格书,Datasheet资料

THS4503ID,THS4503IDGN,THS4503IDGK,THS4502IDGK,THS4502CDGNR,THS4502CDGNRG4, 规格书,Datasheet 资料

V IN-V IN+V OCMV S+V OUT+PDV S-V OUT-THS4502THS4503 SLOS352E–APRIL2002–REVISED OCTOBER2011 Wideband,Low-Distortion Fully Differential AmplifiersCheck for Samples:THS4502,THS4503FEATURES DESCRIPTIONThe THS4502and THS4503are high-performance •Fully Differential Architecturefully differential amplifiers from Texas Instruments.•Bandwidth:370MHz The THS4502,featuring power-down capability,and•Slew Rate:2800V/µs the THS4503,without power-down capability,set newperformance standards for fully differential amplifiers •IMD3:-95dBc at30MHzwith unsurpassed linearity,supporting14-bit •OIP3:51dBm at30MHzoperation through40MHz.Package options include •Output Common-Mode Control the8-pin SOIC and the8-pin MSOP withPowerPAD™for a smaller footprint,enhanced ac •Wide Power Supply Voltage Range:5V,±5V,performance,and improved thermal dissipation 12V,15Vcapability.•Centered Input Common-Mode Range•Power-Down Capability(THS4502)•Evaluation Module AvailableAPPLICATIONS•High Linearity Analog-to-Digital ConverterPreamplifier•Wireless Communication Receiver ChainsRELATED DEVICES•Single-Ended to Differential ConversionDEVICE(1)DESCRIPTION •Differential Line DriverTHS4500/1370MHz,2800V/µs,V ICR Includes V S–•Active Filtering of Differential SignalsTHS4502/3370MHz,2800V/µs,Centered V ICRTHS4120/1 3.3V,100MHz,43V/µs,3.7nV√HzTHS4130/1±15V,150MHz,51V/µs,1.3nV√HzTHS4140/1±15V,160MHz,450V/µs,6.5nV√HzTHS4150/1±15V,150MHz,650V/µs,7.6nV√Hz(1)Even numbered devices feature power-down capability.WARNINGThe THS4502and THS4503may have low-level oscillation when the dietemperature(also known as the junction temperature)exceeds+60°C.Thesedevices are not recommended for new designs where the die temperature isexpected to exceed+60°C.For more information,see Maximum Die Temperatureto Prevent Oscillation section.Please be aware that an important notice concerning availability,standard warranty,and use in critical applications of TexasInstruments semiconductor products and disclaimers thereto appears at the end of this data sheet.PowerPAD is a trademark of Texas Instruments.PRODUCTION DATA information is current as of publication date.Copyright©2002–2011,Texas Instruments Incorporated Products conform to specifications per the terms of the Texasf - Frequency - MHz-80-920204060- T h i r d -O r d e r I n t e r m o d u l a t i o n D i s t o r t i o n - d B c-74THIRD-ORDER INTERMODULATIONDISTORTION-6280100-68-86-9812101416I M D 3B i t sVTHS4502THS4503SLOS352E –APRIL 2002–REVISED OCTOBER 2011This integrated circuit can be damaged by ESD.Texas Instruments recommends that all integrated circuits be handled with appropriate precautions.Failure to observe proper handling and installation procedures can cause damage.ESD damage can range from subtle performance degradation to complete device failure.Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.PACKAGE/ORDERING INFORMATIONORDERABLE PACKAGE AND NUMBERPLASTIC MSOP (1)TEMPERATUREPLASTIC SMALL OUTLINEPLASTIC MSOP PowerPAD (D)(DGN)SYMBOL (DGK)SYMBOL THS4502CD THS4502CDGN BCG THS4502CDGK ATX 0°C to 70°C THS4503CD THS4503CDGN BCK THS4503CDGK ATY THS4502ID THS4502IDGN BCI THS4502IDGK ASX -40°C to 85°C THS4503IDTHS4503IDGNBCLTHS4503IDGKASY(1)All packages are available taped and reeled.The R suffix standard quatity is 2500.The T suffix standard quantity is 250(e.g.,THS4502DT).PIN ASSIGNMENTS2Submit Documentation Feedback Copyright ©2002–2011,Texas Instruments IncorporatedTHS4502THS4503 SLOS352E–APRIL2002–REVISED OCTOBER2011 ABSOLUTE MAXIMUM RATINGSover operating free-air temperature range unless otherwise noted(1)UNITSupply voltage,V S16.5VInput voltage,V I±V SOutput current,I O(2)150mADifferential input voltage,V ID4VContinuous power dissipation See Dissipation Rating Table Maximum junction temperature,T J(3)150°CMaximum junction temperature,continuous operation,long term reliability,T J(4)125°CMaximum junction temperature to prevent oscillation,T J(5)60°CC suffix0°C to70°COperating free-air temperature range,T AI suffix-40°C to85°CStorage temperature range,T stg-65°C to150°C(1)Stresses above these ratings may cause permanent damage.Exposure to absolute maximum conditions for extended periods maydegrade device reliability.These are stress ratings only,and functional operation of the device at these or any other conditions beyond those specified is not implied.(2)The THS450x may incorporate a PowerPAD on the underside of the chip.This acts as a heatsink and must be connected to a thermallydissipative plane for proper power dissipation.Failure to do so may result in exceeding the maximum junction temperature which could permanently damage the device.See TI technical brief SLMA002for more information about utilizing the PowerPAD thermally enhanced package.(3)The absolute maximum temperature under any condition is limited by the constraints of the silicon process.(4)The maximum junction temperature for continuous operation is limited by package constraints.Operation above this temperature mayresult in reduced reliability and/or lifetime of the device.(5)See Maximum Die Temperature to Prevent Oscillation section in the Application Information of this data sheet.PACKAGE DISSIPATION RATINGSθJCθJA(1)PACKAGE(°C/W)(°C/W)D(8pin)38.397.5DGN(8pin) 4.758.4DGK(8pin)54.2260(1)This data was taken using the JEDEC standard High-K test PCB.RECOMMENDED OPERATING CONDITIONSMIN NOM MAX UNITDual supply±5±7.5Supply voltage VSingle supply 4.5515C suffix070 Operating free-air temperature,T A°CI suffix-4085 Copyright©2002–2011,Texas Instruments Incorporated Submit Documentation Feedback3THS4502THS4503SLOS352E–APRIL2002–REVISED ELECTRICAL CHARACTERISTICS V S=±5VR f=R g=499Ω,R L=800Ω,G=+1,Single-ended input unless otherwise noted.THS4502AND THS4503TYP OVER TEMPERATURE(1)MIN/ PARAMETER TEST CONDITIONSTYP/0°C to-40°C to25°C25°C UNITS MAX70°C85°CAC PERFORMANCEG=+1,P IN=-20dBm,R f=392Ω370MHz TypG=+2,P IN=-30dBm,R f=1kΩ175MHz Typ Small-signal bandwidthG=+5,P IN=-30dBm,R f=1.3kΩ70MHz TypG=+10,P IN=-30dBm,R f=1.3kΩ30MHz Typ Gain-bandwidth product G>+10300MHz Typ Bandwidth for0.1dB flatness P IN=-20dBm150MHz Typ Large-signal bandwidth V P=2V220MHz Typ Slew rate4V PP Step2800V/µs Typ Rise time2V PP Step0.8ns Typ Fall time2V PP Step0.6ns Typ Settling time to0.01%V O=4V PP8.3ns Typ Settling time to0.1%V O=4V PP 6.3ns Typ Harmonic distortion G=+1,V O=2V PP Typf=8MHz-83dBc Typ 2nd harmonicf=30MHz-74dBc Typf=8MHz-97dBc Typ 3rd harmonicf=30MHz-78dBc TypThird-order intermodulation V O=2V PP,f c=30MHz,R f=392Ω,-94dBc Typ distortion200kHz tone spacingf c=30MHz,R f=392Ω,Third-order output intercept point52dBm TypReferenced to50ΩInput voltage noise f>1MHz 6.8nV/√Hz Typ Input current noise f>100kHz 1.7pA/√Hz Typ Overdrive recovery time Overdrive=5.5V75ns Typ DC PERFORMANCEOpen-loop voltage gain55525050dB Min Input offset voltage-1-4/+2-5/+3-6/+4mV Max Average offset voltage drift±10±10µV/°C Typ Input bias current4 4.65 5.2µA Max Average bias current drift±10±10nA/°C Typ Input offset current0.5122µA Max Average offset current drift±40±40nA/°C Typ INPUTCommon-mode input range±4.0±3.7±3.4±3.4V Min Common-mode rejection ratio80747070dB Min Input impedance107||1Ω||pF Typ OUTPUTDifferential output voltage swing R L=1kΩ±8±7.6±7.4±7.4V Min Differential output current drive R L=20Ω120110100100mA Min Output balance error P IN=-20dBm,f=100kHz-58dB TypClosed-loop output impedancef=1MHz0.1ΩTyp (single-ended)(1)See Maximum Die Temperature to Prevent Oscillation section in the Application Information of this data sheet.4Submit Documentation Feedback Copyright©2002–2011,Texas Instruments IncorporatedTHS4502THS4503 SLOS352E–APRIL2002–REVISED OCTOBER2011 ELECTRICAL CHARACTERISTICS V S=±5V(continued)R f=R g=499Ω,R L=800Ω,G=+1,Single-ended input unless otherwise noted.THS4502AND THS4503TYP OVER TEMPERATURE(1)MIN/ PARAMETER TEST CONDITIONSTYP/0°C to-40°C to25°C25°C UNITS MAX70°C85°COUTPUT COMMON-MODE VOLTAGE CONTROLSmall-signal bandwidth R L=400Ω180MHz Typ Slew rate2V PP step87V/µs Typ Minimum gain10.980.980.98V/V Min Maximum gain1 1.02 1.02 1.02V/V Max Common-mode offset voltage+2-1.6/+6.8-3.6/+8.8-4.6/+9.8mV Max Input bias current V OCM=2.5V100150170170µA Max Input voltage range±4±3.7±3.4±3.4V Min Input impedance25||1kΩ||pF Typ Maximum default voltage V OCM left floating00.050.100.10V Max Minimum default voltage V OCM left floating0-0.05-0.10-0.10V Min POWER SUPPLYSpecified operating voltage±5±8.25±8.25±8.25V Max Maximum quiescent current23283234mA Max Minimum quiescent current23181412mA Min Power supply rejection(±PSRR)80767370dB Min POWER DOWN(THS4502ONLY)Enable voltage threshold Device enabled ON above-2.9V-2.9V Min Disable voltage threshold Device disabled OFF below-4.3V-4.3V Max Power-down quiescent current800100012001200µA Max Input bias current200240260260µA Max Input impedance50||1kΩ||pF Typ Turnon time delay1000ns Typ Turnoff time delay800ns Typ ELECTRICAL CHARACTERISTICS V S=5VR f=R g=499Ω,R L=800Ω,G=+1,Single-ended input unless otherwise noted.THS4502AND THS4503TYP OVER TEMPERATURE(1)MIN/T PARAMETER TEST CONDITIONSYP/M0°C to-40°C to25°C25°C UNITS AX70°C85°CAC PERFORMANCEG=+1,P IN=-20dBm,R f=392Ω320MHz TypG=+2,P IN=-30dBm,R f=1kΩ160MHz Typ Small-signal bandwidthG=+5,P IN=-30dBm,R f=1.3kΩ60MHz TypG=+10,P IN=-30dBm,R f=1.3kΩ30MHz Typ Gain-bandwidth product G>+10300MHz Typ Bandwidth for0.1dB flatness P IN=-20dBm180MHz Typ Large-signal bandwidth V P=1V200MHz Typ Slew rate2V PP Step1300V/µs Typ Rise time2V PP Step0.6ns Typ Fall time2V PP Step0.8ns Typ Settling time to0.01%V O=2V Step13.1ns Typ (1)See Maximum Die Temperature to Prevent Oscillation section in the Application Information of this data sheet.Copyright©2002–2011,Texas Instruments Incorporated Submit Documentation Feedback5THS4502THS4503SLOS352E–APRIL2002–REVISED ELECTRICAL CHARACTERISTICS V S=5V(continued)R f=R g=499Ω,R L=800Ω,G=+1,Single-ended input unless otherwise noted.THS4502AND THS4503TYP OVER TEMPERATURE(1)MIN/T PARAMETER TEST CONDITIONSYP/M0°C to-40°C to25°C25°C UNITS AX70°C85°CSettling time to0.1%V O=2V Step8.3ns Typ Harmonic distortion V O=2V PP Typf=8MHz,-81dBc Typ 2nd harmonicf=30MHz-60dBc Typf=8MHz-74dBc Typ 3rd harmonicf=30MHz-62dBc Typ Input voltage noise f>1MHz 6.8nV/√Hz Typ Input current noise f>100kHz 1.6pA/√Hz Typ Overdrive recovery time Overdrive=5.5V75ns Typ DC PERFORMANCEOpen-loop voltage gain54514949dB Min Input offset voltage-0.6-3.6/+2.4-4.6/+3.4-5.6/+4.4mV Max Average offset voltage drift±10±10µV/°C Typ Input bias current4 4.65 5.2µA Max Average bias current drift±10±10nA/°C Typ Input offset current0.50.7 1.2 1.2µA Max Average offset current drift±20±20nA/°C Typ INPUTCommon-mode input range1/4 1.3/3.7 1.6/3.4 1.6/3.4V Min Common-mode rejection ratio80747070dB Min Input Impedance107||1Ω||pF Typ OUTPUTDifferential output voltage swing R L=1kΩ,Referenced to2.5V±3.3±2.8±2.6±2.6V Min Output current drive R L=20Ω100908080mA Min Output balance error P IN=-20dBm,f=100kHz-58dB TypClosed-loop output impedancef=1MHz0.1ΩTyp (single-ended)OUTPUT COMMON-MODE VOLTAGE CONTROLSmall-signal bandwidth R L=400Ω180MHz Typ Slew rate2V PP Step80V/µs Typ Minimum gain10.980.980.98V/V Min Maximum gain1 1.02 1.02 1.02V/V Max Common-mode offset voltage2-2.2/6.2-4.2/8.2-5.2/9.2mV Max Input bias current V OCM=2.5V1233µA Max Input voltage range1/4 1.2/3.8 1.3/3.7 1.3/3.7V Min Input impedance25||1kΩ||pF Typ Maximum default voltage V OCM left floating 2.5 2.55 2.6 2.6V Max Minimum default voltage V OCM left floating 2.5 2.45 2.4 2.4V Min POWER SUPPLYSpecified operating voltage516.516.516.5V Max Maximum quiescent current20252931mA Max Minimum quiescent current20161210mA Min Power supply rejection(+PSRR)75726966dB Min6Submit Documentation Feedback Copyright©2002–2011,Texas Instruments IncorporatedTHS4502THS4503 SLOS352E–APRIL2002–REVISED OCTOBER2011 ELECTRICAL CHARACTERISTICS V S=5V(continued)R f=R g=499Ω,R L=800Ω,G=+1,Single-ended input unless otherwise noted.THS4502AND THS4503TYP OVER TEMPERATURE(1)MIN/T PARAMETER TEST CONDITIONSYP/M0°C to-40°C to25°C25°C UNITS AX70°C85°CPOWER DOWN(THS4502ONLY)Enable voltage threshold Device enabled ON above2.1V 2.1V Min Disable voltage threshold Device disabled OFF below0.7V0.7V Max Power-down quiescent current60080012001200µA Max Input bias current100125140140µA Max Input impedance50||1kΩ||pF Typ Turnon time delay1000ns Typ Turnoff time delay800ns TypCopyright©2002–2011,Texas Instruments Incorporated Submit Documentation Feedback7THS4502THS4503SLOS352E–APRIL2002–REVISED TYPICAL CHARACTERISTICSTable of Graphs(±5V)FIGURESmall signal unity gain frequency response1Small signal frequency response20.1dB gain flatness frequency response3Harmonic distortion(single-ended input to differential output)vs Frequency4,6,12,14 Harmonic distortion(differential input to differential output)vs Frequency5,7,13,15 Harmonic distortion(single-ended input to differential output)vs Output voltage swing8,10,16,18 Harmonic distortion(differential input to differential output)vs Output voltage swing9,11,17,19 Harmonic distortion(single-ended input to differential output)vs Load resistance20Harmonic distortion(differential input to differential output)vs Load resistance21Third order intermodulation distortion(single-ended input to differential output)vs Frequency22Third order output intercept point vs Frequency23Slew rate vs Differential output voltage step24Settling time25,26Large-signal transient response27Small-signal transient response28Overdrive recovery29,30Voltage and current noise vs Frequency31Rejection ratios vs Frequency32Rejection ratios vs Case temperature33Output balance error vs Frequency34Open-loop gain and phase vs Frequency35Open-loop gain vs Case temperature36Input bias and offset current vs Case temperature37Quiescent current vs Supply voltage38Input offset voltage vs Case temperature39Common-mode rejection ratio vs Input common-mode range40 Differential output current drive vs Case temperature41Harmonic distortion(single-ended and differential input to differential output)vs Output common-mode voltage42Small signal frequency response at V OCM43Output offset voltage at V OCM vs Output common-mode voltage44Quiescent current vs Power-down voltage45Turnon and turnoff delay times46Single-ended output impedance in power down vs Frequency47Power-down quiescent current vs Case temperature48Power-down quiescent current vs Supply voltage498Submit Documentation Feedback Copyright©2002–2011,Texas Instruments IncorporatedTHS4502THS4503 SLOS352E–APRIL2002–REVISED OCTOBER2011 Table of Graphs(5V)FIGURESmall signal unity gain frequency response50Small signal frequency response510.1dB gain flatness frequency response52Harmonic distortion(single-ended input to differential output)vs Frequency53,54,61,63 Harmonic distortion(differential input to differential output)vs Frequency55,56,62,64 Harmonic distortion(single-ended input to differential output)vs Output voltage swing57,58,65,67 Harmonic distortion(differential input to differential output)vs Output voltage swing59,60,66,68 Harmonic distortion(single-ended input to differential output)vs Load resistance69Harmonic distortion(differential input to differential output)vs Load resistance70Slew rate vs Differential output voltage step71Large-signal transient response72Small-signal transient response73Voltage and current noise vs Frequency74Rejection ratios vs Frequency75Rejection ratios vs Case temperature76Output balance error vs Frequency77Open-loop gain and phase vs Frequency78Open-loop gain vs Case temperature79Input bias and offset current vs Case temperature80Quiescent current vs Supply voltage81Input offset voltage vs Case temperature82Common-mode rejection ratio vs Input common-mode range83Output drive vs Case temperature84Harmonic distortion(single-ended and differential input)vs Output common-mode range85Small signal frequency response at V OCM86Output offset voltage vs Output common-mode voltage87Quiescent current vs Power-down voltage88Turnon and turnoff delay times89Single-ended output impedance in power down vs Frequency90Power-down quiescent current vs Case temperature91Power-down quiescent current vs Supply voltage92Copyright©2002–2011,Texas Instruments Incorporated Submit Documentation Feedback9-2024680.11101001000f - Frequency - MHzS m a l l S i g n a l G a i n - d BSMALL SIGNAL FREQUENCY RESPONSE-4-3.5-3-2.5-2-1.5-1-0.500.510.11101001000f - Frequency - MHzS m a l l S i g n a l U n i t y G a i n - d BSMALL SIGNAL UNITY GAIN FREQUENCY RESPONSE-0.5-0.4-0.3-0.2-0.100.11f - Frequency - MHz0.1 d B G a i n F l a t n e s s - d B0.1 dB GAIN FLATNESS FREQUENCY RESPONSE-100-90-80-70-60-50-40-30-20-1000.1110100H a r m o n i c D i s t o r t i o n - d B cHARMONIC DISTORTIONvsFREQUENCYf - Frequency - MHz-100-90-80-70-60-50-40-30-20-10H a r m o n i c D i s t o r t i o n - d B cHARMONIC DISTORTIONvsFREQUENCYf - Frequency - MHz-100-90-80-70-60-50-40-30-20-10H a r m o n i c D i s t o r t i o n - d B cHARMONIC DISTORTIONvsFREQUENCYf - Frequency - MHz-100-90-80-70-60-50-40-30-20-100.1110100H a r m o n i c D i s t o r t i o n - d B cHARMONIC DISTORTIONvsFREQUENCYf - Frequency - MHz-100-90-80-70-60-50-40-30-20-100H a r m o n i c D i s t o r t i o n - d B cHARMONIC DISTORTIONvsOUTPUT VOLTAGE SWINGV O - Output Voltage Swing - V-100-90-80-70-60-50-40-30-20-100H a r m o n i c D i s t o r t i o n - d B cHARMONIC DISTORTIONvsOUTPUT VOLTAGE SWINGV O - Output Voltage Swing - VTHS4502THS4503SLOS352E –APRIL 2002–REVISED OCTOBER 2011TYPICAL CHARACTERISTICS (±5V Graphs)Figure 1.Figure 2.Figure 3.Figure 4.Figure 5.Figure 6.Figure 7.Figure 8.Figure 9.10Submit Documentation Feedback Copyright ©2002–2011,Texas Instruments Incorporated-100-90-80-70-60-50-40-30-20-1000123456H a r m o n i c D i s t o r t i o n - d B cHARMONIC DISTORTIONvsOUTPUT VOLTAGE SWINGV O - Output Voltage Swing - V-100-90-80-70-60-50-40-30-20-10H a r m o n i c D i s t o r t i o n - d B cHARMONIC DISTORTIONvsFREQUENCYf - Frequency - MHz-100-90-80-70-60-50-40-30-20-1000123456H a r m o n i c D i s t o r t i o n - d B cHARMONIC DISTORTIONvsOUTPUT VOLTAGE SWINGV O - Output Voltage Swing - V-100-90-80-70-60-50-40-30-20-100.1110100H a r m o n i c D i s t o r t i o n - d B cHARMONIC DISTORTIONvsFREQUENCYf - Frequency - MHz-100-90-80-70-60-50-40-30-20-100.1110100H a r m o n i c D i s t o r t i o n - d B cHARMONIC DISTORTIONvsFREQUENCYf - Frequency - MHz-100-90-80-70-60-50-40-30-20-10H a r m o n i c D i s t o r t i o n - d B cHARMONIC DISTORTIONvsFREQUENCYf - Frequency - MHz-100-90-80-70-60-50-40-30-20-100H a r m o n i c D i s t o r t i o n - d B cHARMONIC DISTORTIONvsOUTPUT VOLTAGE SWINGV O - Output Voltage Swing - V-100-90-80-70-60-50-40-30-20-10012345678910H a r m o n i c D i s t o r t i o n - d B cHARMONIC DISTORTIONvsOUTPUT VOLTAGE SWINGV O - Output Voltage Swing - V-100-90-80-70-60-50-40-30-20-10H a r m o n i c D i s t o r t i o n - d B cHARMONIC DISTORTIONvsOUTPUT VOLTAGE SWINGV O - Output Voltage Swing - VFigure 10.Figure 11.Figure 12.Figure 13.Figure 14.Figure 15.Figure 16.Figure 17.Figure 18.-100-90-80-70-60-50-40-30-20-100012345678910H a r m o n i c D i s t o r t i o n - d B cHARMONIC DISTORTIONvsOUTPUT VOLTAGE SWINGV O - Output Voltage Swing - V -100-90-80-70-60-50-40-30-20-1040080012001600H a r m o n i c D i s t o r t i o n - d B cHARMONIC DISTORTIONvsLOAD RESISTANCER L - Load Resistance - Ω-100-90-80-70-60-50-40-30-20-10H a r m o n i c D i s t o r t i o n - d B cHARMONIC DISTORTIONvsLOAD RESISTANCER L - Load Resistance - Ω5001000150020002500300000.51 1.52 2.53 3.54V O - Differential Output Voltage Step - VS R - S l e w R a t e - SLEW RATEvsDIFFERENTIAL OUTPUT VOLTAGE STEPsµV /-100-90-80-70-60-50T h i r d -O r d e r I n t e r m o d u l a t i o n D i s t o r t i o n - d B cTHIRD-ORDER INTERMODULATIONDISTORTIONvsFREQUENCY40302015102030405060T h i r d -O r d e r O u t p u t I n t e r s e p t P o i n t - d B m5055 f - Frequency - MHzTHIRD-ORDER OUTPUT INTERCEPTPOINT vsFREQUENCY607080901004535255101520t - Time - ns- O u t p u t V o l t a g e - VSETTLING TIMEV O-2.5-2-1.5-1-0.500.511.522.55t - Time - ns- O u t p u t V o l t a g e - VSETTLING TIMEV O-3-2-1-1000100200300400500t - Time - ns- O u t p u t V o l t a g e - VLARGE-SIGNAL TRANSIENT RESPONSEV O Figure 19.Figure 20.Figure 21.Figure 22.Figure 23.Figure 24.Figure 25.Figure 26.Figure 27.t - Time - µs0-1-400.10.20.30.40.50.6S i n g l e -E n d e d O u t p u t V o l t a g e - V12OVERDRIVE RECOVERY40.70.80.913-3-5-250-0.5-20.5121.5-1.5-2.5-12.5- I n p u t V o l t a g e - VVI -0.4-0.3-0.2-0.1-1000100200300400500t - Time - ns- O u t p u t V o l t a g e - VSMALL-SIGNAL TRANSIENT RESPONSEV O -6-4-2024600.10.20.30.40.50.60.70.80.91-3-2-10123t - Time - µsS i n g l e -E n d e d O u t p u t V o l t a g e - VOVERDRIVE RECOVERY-I n p u t V o l t a g e - V V IR e j e c t i o n R a t i o s - d BREJECTION RATIOSvsf - Frequency - MHzR e j e c t i o n R a t i o s - d BREJECTION RATIOSvsCASE TEMPERATURECase Temperature - °Cf - Frequency - kHz- V o l t a g e N o i s e -VOLTAGE AND CURRENT NOISEvsFREQUENCYn V /H zV n-70-60-50-40-30-20-10O u t p u t B a l a n c e E r r o r - d BOUTPUT BALANCE ERRORvsFREQUENCYf - Frequency - MHzO p e n -L o o p G a i n - d B OPEN-LOOP GAIN AND PHASEvsFREQUENCYf - Frequency - MHzP h a s e -°O p e n -L o o p G a i n - d BOPEN-LOOP GAINvsCASE TEMPERATURECase Temperature - °CFigure 28.Figure 29.Figure 30.Figure 31.Figure 32.Figure 33.Figure 34.Figure 35.Figure 36.- I n p u t B i a s C u r r e n t -INPUT BIAS AND OFFSET CURRENTvsCASE TEMPERATURECase Temperature - °C- I n p u t O f f s e t C u r r e n t -I I B A µI O S A µV S - Supply Voltage - ±VQ u i e s c e n t C u r r e n t - m AQUIESCENT CURRENTvsSUPPL Y VOLTAGE0.511.522.5-40-30-20-100102030405060708090Case Temperature - °C- I n p u t O f f s e t V o l t a g e - m VINPUT OFFSET VOLTAGEvsCASE TEMPERATUREV O S -150-100-50D i f f e r e n t i a l O u t p u t C u r r e n t D r i v e - m ADIFFERENTIAL OUTPUT CURRENT DRIVEvsCASE TEMPERATURECase Temperature - °C-10Input Common-Mode Voltage Range - V C M R R - C o m m o n -M o d e R e j e c t i o n R a t i o - d BCOMMON-MODE REJECTION RATIOvsINPUT COMMON-MODE RANGEV OC - Output Common-Mode Voltage - VH a r m o n i c D i s t o r t i o n - d B cHARMONIC DISTORTIONvsOUTPUT COMMON-MODE VOLTAGE-3-2-10123SMALL SIGNAL FREQUENCY RESPONSEAT V OCMf - Frequency - MHzS m a l l S i g n a l F r e q u e n c y R e s p o n s e a t V O C M - dB-600-400-2000200400600V OC - Output Common-Mode Voltage - V- O u t p u t O f f s e t V o l t a g e a tOUTPUT OFFSET VOLTAGE AT V OCMvsOUTPUT COMMON-MODE VOLTAGEV O S V O C M - m V-50510********Power-Down Voltage - VQ u i e s c e n t C u r r e n t - m AQUIESCENT CURRENTvsPOWER-DOWN VOLTAGEFigure 37.Figure 38.Figure 39.Figure 40.Figure 41.Figure 42.Figure 43.Figure 44.Figure 45.-1-2-5-3-6-4t - Time - msP o w e r d o w n V o l t a g e S i g n a l - VTURNON AND TURNOFF DELAY TIMESQ u i e s c e n t C u r r e n t - m A-40-30-20-100102030405060708090P o w e r -D o w n Q u i e s c e n t C u r r e n t - m APOWER-DOWN QUIESCENT CURRENTvsCASE TEMPERATURECase Temperature - °C- S i n g l e -E n d e d O u t p u t I m p e d a n c e SINGLE-ENDED OUTPUT IMPEDANCEIN POWER DOWNvsFREQUENCYZ O f - Frequency - MHzi n P o w e r D o w n -Ω0.511.522.533.544.55V S - Supply Voltage - ±VP o w e r -D o w n Q u i e s c e n t C u r r e n t -POWER-DOWN QUIESCENT CURRENTvsSUPPL Y VOLTAGEAµFigure 46.Figure 47.Figure 48.Figure 49.-202468f - Frequency - MHzS m a l l S i g n a l G a i n - d BSMALL SIGNAL FREQUENCY RESPONSE-4-3-2-1010.11101001000f - Frequency - MHzS m a l l S i g n a l U n i t y G a i n - d BSMALL SIGNAL UNITY GAIN FREQUENCY RESPONSE-0.5-0.4-0.3-0.2-0.100.21101001000f - Frequency - MHz0.1 d B G a i n F l a t n e s s - d B0.1 dB GAIN FLATNESSFREQUENCY RESPONSE0.1-100-90-80-70-60-50-40-30-20-100.1110100H a r m o n i c D i s t o r t i o n - dB cHARMONIC DISTORTIONvsFREQUENCYf - Frequency - MHz-100-90-80-70-60-50-40-30-20-100.1110100H a r m o n i c D i s t o r t i o n - d B cHARMONIC DISTORTIONvsFREQUENCYf - Frequency - MHz-100-90-80-70-60-50-40-30-20-100.1110100H a r m o n i c D i s t o r t i o n - d B cHARMONIC DISTORTIONvsFREQUENCYf - Frequency - MHz-100-90-80-70-60-50-40-30-20-100.1110100H a r m o n i c D i s t o r t i o n - d B cHARMONIC DISTORTIONvsFREQUENCYf - Frequency - MHz-100-90-80-70-60-50-40-30-20-1000.511.522.533.544.55H a r m o n i c D i s t o r t i o n - d B cHARMONIC DISTORTIONvsOUTPUT VOLTAGE SWINGV O - Output Voltage Swing - V-100-90-80-70-60-50-40-30-20-1000.511.522.533.544.55H a r m o n i c D i s t o r t i o n - d B cHARMONIC DISTORTIONvsOUTPUT VOLTAGE SWINGV O - Output Voltage Swing - VTYPICAL CHARACTERISTICS (5V GRAPHS)Figure 50.Figure 51.Figure 52.Figure 53.Figure 54.Figure 55.Figure 56.Figure 57.Figure 58.。

电子元件参数大全1

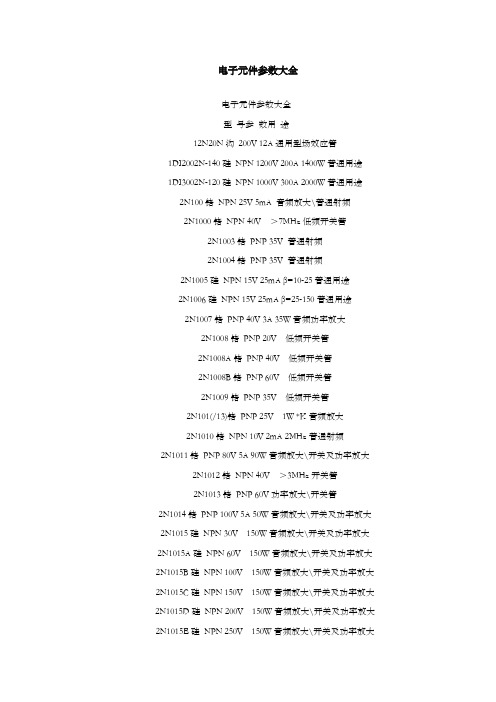

电子元件参数大全电子元件参数大全型号参数用途12N20N沟200V 12A通用型场效应管 1DI2002N-140硅NPN 1200V 200A 1400W普通用途1DI3002N-120硅NPN 1000V 300A 2000W普通用途 2N100锗NPN 25V 5mA 音频放大\普通射频2N1000锗NPN 40V >7MHz低频开关管2N1003锗PNP 35V 普通射频2N1004锗PNP 35V 普通射频2N1005硅NPN 15V 25mA β=10-25普通用途2N1006硅NPN 15V 25mA β=25-150普通用途2N1007锗PNP 40V 3A 35W音频功率放大2N1008锗PNP 20V 低频开关管2N1008A锗PNP 40V 低频开关管2N1008B锗PNP 60V 低频开关管2N1009锗PNP 35V 低频开关管2N101(/13)锗PNP 25V 1W *K音频放大2N1010锗NPN 10V 2mA 2MHz普通射频2N1011锗PNP 80V 5A 90W音频放大\开关及功率放大 2N1012锗NPN 40V >3MHz开关管2N1013锗PNP 60V功率放大\开关管2N1014锗PNP 100V 5A 50W音频放大\开关及功率放大 2N1015硅NPN 30V 150W音频放大\开关及功率放大 2N1015A硅NPN 60V 150W音频放大\开关及功率放大 2N1015B硅NPN 100V 150W音频放大\开关及功率放大 2N1015C硅NPN 150V 150W音频放大\开关及功率放大 2N1015D硅NPN 200V 150W音频放大\开关及功率放大 2N1015E硅NPN 250V 150W音频放大\开关及功率放大2N1015F硅NPN 300V 150W音频放大\开关及功率放大2N1016硅NPN 30V 150W音频放大\开关及功率放大2N1016A硅NPN 60V 150W音频放大\开关及功率放大2N1016B硅NPN 100V 150W音频放大\开关及功率放大2N1016C硅NPN 150V 150W音频放大\开关及功率放大2N1016D硅NPN 200V 150W音频放大\开关及功率放大2N1016E硅NPN 250V 150W音频放大\开关及功率放大2N1016F硅NPN 300V 150W音频放大\开关及功率放大2N1017锗PNP 30V 1A 音频放大2N1018锗PNP 30V 1A 音频放大2N102锗NPN 25V 1.5A 1W *K音频放大2N102/13锗NPN 25V 1.5A 1W *K音频放大2N10202N1021锗PNP 100V 7A 150W功率放大\开关管2N1021A锗PNP 100V 7A 150W功率放大\开关管2N1022锗PNP 120V 7A 150W功率放大\开关管2N1022A锗PNP 120V 7A 150W音频放大\开关及功率放大2N1023锗PNP 40V 10mA 120MHz普通射频2N1024硅PNP 18V 0.1A β>9普通用途2N1025硅PNP 40V 0.1A β>9普通用途2N1026硅PNP 40V 0.1A β=18-44普通用途2N1027硅PNP 18V 0.1A β>18普通用途2N1028硅PNP 12V 0.1A β>9普通用途2N1029锗PNP 50V 25A 90W音频放大\开关及功率放大2N1029A锗PNP 60V 25A 90W音频放大\开关及功率放大2N1029B锗PNP 90V 25A 90W音频放大\开关及功率放大2N1029C锗PNP 100V 25A 90W音频放大\开关及功率放大2N103锗NPN 35V 10mA 音频放大2N1030锗PNP 50V 25A 90W音频放大\开关及功率放大2N1030A锗PNP 60V 25A 90W音频放大\开关及功率放大2N1030B锗PNP 90V 25A 90W音频放大\开关及功率放大 2N1030C锗PNP 100V 25A 90W音频放大\开关及功率放大 2N1031锗PNP 50V 25A 90W音频放大\开关及功率放大 2N1031A锗PNP 60V 25A 90W音频放大\开关及功率放大 2N1031B锗PNP 90V 25A 90W音频放大\开关及功率放大 2N1031C锗PNP 100V 25A 90W音频放大\开关及功率放大 2N1032锗PNP 50V 25A 90W音频放大\开关及功率放大 2N1032A锗PNP 60V 25A 90W音频放大\开关及功率放大 2N1032B锗PNP 90V 25A 90W音频放大\开关及功率放大 2N1032C锗PNP 100V 25A 90W音频放大\开关及功率放大 2N1034硅PNP 50V 0.05A β=15音频放大2N1035硅PNP 50V 0.05A β=30音频放大2N1036硅PNP 50V 0.05A β=60音频放大2N1037硅PNP 50V 0.05A β=30音频放大2N1038锗PNP 40V 3A 20W音频放大\开关及功率放大 2N1038-1锗PNP 40V 3A 20W音频放大\开关及功率放大 2N1038-2锗PNP 40V 3A 20W音频放大\开关及功率放大 2N1039锗PNP 60V 3A 20W音频放大\开关及功率放大 2N1039-1锗PNP 60V 3A 20W音频放大\开关及功率放大 2N1039-2锗PNP 60V 3A 20W音频放大\开关及功率放大 2N104锗PNP 30V 50mA 音频放大2N1040锗PNP 80V 3A 20W音频放大\开关及功率放大 2N1040-1锗PNP 80V 3A 20W音频放大\开关及功率放大 2N1040-2锗PNP 80V 3A 20W音频放大\开关及功率放大 2N1041锗PNP 100V 3A 20W音频放大\开关及功率放大 2N1041-1锗PNP 100V 3A 20W音频放大\开关及功率放大 2N1041-2锗PNP 100V 3A 20W音频放大\开关及功率放大 2N1042锗PNP 40V 3.5A 20W音频放大\开关及功率放大 2N1042-1锗PNP 40V 3.5A 20W音频放大\开关及功率放大 2N1042-2锗PNP 40V 3.5A 20W音频放大\开关及功率放大2N1042-2A锗PNP 40V 3A 20W 普通用途2N1042-2ψ锗PNP 40V 3A 1W 普通用途2N1043锗PNP 60V 3.5A 20W音频放大\开关及功率放大 2N1043-1锗PNP 60V 3.5A 20W音频放大\开关及功率放大 2N1043-2锗PNP 60V 3.5A 20W音频放大\开关及功率放大 2N1043-2ψ锗PNP 60V 3A 1W 普通用途2N1044锗PNP 80V 3.5A 20W音频放大\开关及功率放大 2N1044-1锗PNP 80V 3.5A 20W音频放大\开关及功率放大 2N1044-2锗PNP 80V 3.5A 20W音频放大\开关及功率放大 2N1044-2ψ锗PNP 80V 3A 1W 普通用途2N1045锗PNP 100V 3.5A 20W音频放大\开关及功率放大 2N1045-1锗PNP 100V 3.5A 20W音频放大\开关及功率放大 2N1045-2锗PNP 100V 3.5A 20W音频放大\开关及功率放大 2N1045-2ψ锗PNP 100V 3A 1W 普通用途2N1046锗PNP 100V 10A 50W音频放大\开关及功率放大 2N1046A/B锗PNP 130V 15A 50W音频放大\开关及功率放大2N1047锗NPN 80V 8A 40W音频放大\开关及功率放大 2N1047A硅NPN 80V 8A 40W音频放大\开关及功率放大 2N1047B硅NPN 80V 8A 40W音频放大\开关及功率放大 2N1047C硅NPN 80V 8A 40W音频放大\开关及功率放大 2N1048硅NPN 120V 8A 40W音频放大\开关及功率放大 2N1048A硅NPN 120V 8A 40W音频放大\开关及功率放大 2N1048B硅NPN 120V 8A 40W音频放大\开关及功率放大 2N1048C硅NPN 120V 8A 40W音频放大\开关及功率放大 2N1049硅NPN 80V 8A 40W音频放大\开关及功率放大 2N1049A硅NPN 80V 8A 40W音频放大\开关及功率放大 2N1049B硅NPN 80V 8A 40W音频放大\开关及功率放大 2N1049C硅NPN 80V 8A 40W音频放大\开关及功率放大 2N105锗PNP 35V 15mA 音频放大2N1050A硅NPN 120V 8A 40W音频放大\开关及功率放大 2N1050B硅NPN 120V 8A 40W音频放大\开关及功率放大 2N1050C硅NPN 120V 8A 40W音频放大\开关及功率放大 2N1051硅NPN 40V 0.3A 音频放大2N1052硅NPN 200V 0.2A 开关管2N1053硅NPN 180V 0.2A 开关管2N1054硅NPN 125V 0.2A 开关管2N1055硅NPN 100V 0.2A 开关管2N1056锗PNP 70V 0.3A 低频开关管2N1057锗PNP 45V 0.3A 低频开关管2N1058锗NPN 20V 0.1A 低频开关管2N1059锗NPN 40V 0.1A 低频开关管2N106锗PNP 15V 10mA 音频放大2N1060硅NPN 40V 0.2A <50ns开关管2N1065锗PNP 40V 10MHz普通射频\开关管2N1066锗PNP 40V 10mA 120MHz普通射频2N1067硅NPN 60V 0.5A 5W音频放大\开关及功率放大 2N1068硅NPN 60V 1.5A 10W音频放大\开关及功率放大 2N1069硅NPN 60V 4A 50W音频放大\开关及功率放大 2N107锗PNP 12V 10mA 音频放大2N1070硅NPN 60V 4A 50W音频放大\开关及功率放大 2N1072硅NPN 75V 2A 2W低频开关管2N1073锗PNP 40V 10A 85W音频放大\开关及功率放大 2N1073A锗PNP 80V 10A 85W音频放大\开关及功率放大 2N1073B锗PNP 120V 10A 85W音频放大\开关及功率放大 2N1074硅NPN 50V 0.1A β=14音频放大2N1075硅NPN 50V 0.1A β=25音频放大2N1076硅NPN 50V 0.1A β=50音频放大2N1077硅NPN 50V 0.1A β=18音频放大2N1079硅NPN 60V 3A 60W音频放大\开关及功率放大2N1108锗PNP 16V 5mA 35MHz普通射频2N1109锗PNP 16V 5mA 35MHz普通射频2N111锗PNP 30V 0.2A 3MHz普通射频2N1110锗PNP 16V 5mA 35MHz普通射频2N1111锗PNP 20V 5mA 35MHz普通射频2N1111A锗PNP 20V 5mA 35MHz普通射频2N1111B锗PNP 20V 5mA 35MHz普通射频2N1114锗NPN 25V 0.2A >7MHz低频开关管2N1115锗PNP 20V 0.125A 低频开关管2N1115A锗PNP 20V 0.125A 低频开关管2N1116硅NPN 60V 0.8A 低频开关管2N1117硅NPN 60V 0.8A 低频开关管2N1118硅PNP 25V 0.05A 普通用途2N1118A硅PNP 25V 0.05A 普通用途2N1119硅PNP 10V 0.05A 普通用途2N111A锗PNP 30V 0.2A 3MHz普通射频2N112锗PNP 30V 0.2A 5MHz普通射频2N1120锗PNP 80V 15A 90W音频放大\开关及功率放大 2N1121锗NPN 15V 20mA 8MHz普通射频2N1122锗PNP 12V 0.05A >40MHz普通射频\开关管 2N1122A锗PNP 15V 0.05A >40MHz普通射频\开关管 2N1123锗PNP 46V 0.4A 低频开关管2N1124锗PNP 40V 0.5A β>40低频开关管2N1125锗PNP 40V 0.5A β=50-150低频开关管2N1126锗PNP 40V 0.5A β>40低频开关管2N1127锗PNP 40V 0.5A β=50-150低频开关管2N1128锗PNP 25V 0.5A 音频放大2N1129锗PNP 25V 0.5A 音频放大2N112A锗PNP 30V 0.2A 5MHz普通射频2N113锗PNP 30V 0.2A 10MHz普通射频2N1130锗PNP 30V 0.5A 音频放大2N1131硅PNP 60V 0.6A 低频开关管2N1131A硅PNP 60V 0.6A 低频开关管2N1132硅PNP 50V 0.6A 低频开关管2N1132A硅PNP 60V 0.6A 低频开关管2N1132B硅PNP 70V 0.6A 低频开关管 2N1132B46硅PNP 70V 0.6A 96MHz普通用途2N1135硅PNP 12V 0.05A 普通用途2N1135A硅PNP 12V 0.05A 普通用途2N1136锗PNP 60V 6A 60W音频放大\开关及功率放大 2N1136A锗PNP 90V 6A 60W音频放大\开关及功率放大 2N1136B锗PNP 100V 6A 60W音频放大\开关及功率放大2N1137锗PNP 60V 6A 60W音频放大\开关及功率放大 2N1137A锗PNP 90V 6A 60W音频放大\开关及功率放大 2N1137B锗PNP 100V 6A 60W音频放大\开关及功率放大2N1138锗PNP 60V 6A 60W音频放大\开关及功率放大 2N1138A锗PNP 90V 6A 60W音频放大\开关及功率放大 2N1138B锗PNP 100V 6A 60W音频放大\开关及功率放大2N1139硅NPN 15V 0.1A >100MHz开关管2N114锗PNP 30V 0.2A 20MHz普通射频2N1140硅NPN 40V >60MHz开关管2N1141锗PNP 35V 0.1A >750MHz用于VHF频段及射频2N1141A锗PNP 35V 0.1A >750MHz用于VHF频段及射频2N1142锗PNP 30V 0.1A >600MHz用于VHF频段及射频2N1142A锗PNP 30V 0.1A >600MHz用于VHF频段及射频2N1143锗PNP 25V 0.1A >480MHz用于VHF频段及射频2N1143A锗PNP 25V 0.1A >480MHz用于VHF频段及射频2N1144锗PNP 16V 0.2A β=34-90音频放大2N1145锗PNP 16V 0.2A β=25-90音频放大2N1146锗PNP 40V 15A 69W音频放大\开关及功率放大 2N1146A锗PNP 60V 15A 69W音频放大\开关及功率放大2N1146B锗PNP 80V 15A 69W音频放大\开关及功率放大2N1146C锗PNP 100V 15A 69W音频放大\开关及功率放大2N1147锗PNP 40V 15A 87W音频放大\开关及功率放大 2N1147A锗PNP 60V 15A 87W音频放大\开关及功率放大2N1147B锗PNP 80V 15A 87W音频放大\开关及功率放大2N1147C锗PNP 100V 15A 87W音频放大\开关及功率放大2N1149硅NPN 45V 25mA B=9-20普通用途2N115锗PNP 32V 3A 50W音频放大\开关及功率放大 2N1150硅NPN 45V 25mA β=18-40普通用途2N1151硅NPN 45V 25mA β=18-90普通用途2N1152硅NPN 45V 25mA β=36-90普通用途2N1153硅NPN 45V 25mA β=76-333普通用途2N1154硅NPN 50V 0.06A 普通用途及驱动2N1155硅NPN 80V 0.05A 普通用途及驱动2N1156硅NPN 120V 0.04A 普通用途及驱动2N1157锗PNP 60V 25A 187W功率放大\开关管2N1157A锗PNP 80V 25A 187W功率放大\开关管2N1158锗PNP 20V 0.1A >200MHz普通射频2N1158A锗PNP 20V 0.1A >200MHz普通射频2N1159锗PNP 80V 5A 90W音频放大\开关及功率放大2N116锗PNP2N1160锗PNP 80V 7A 90W音频放大\开关及功率放大 2N1162锗PNP 50V 25A 106W音频放大\开关及功率放大 2N1162A锗PNP 50V 25A 106W音频放大\开关及功率放大2N1163锗PNP 50V 25A 106W音频放大\开关及功率放大 2N1163A锗PNP 50V 25A 106W音频放大\开关及功率放大2N1164锗PNP 80V 25A 106W音频放大\开关及功率放大 2N1164A锗PNP 80V 25A 106W音频放大\开关及功率放大2N1165锗PNP 80V 25A 106W音频放大\开关及功率放大 2N1165A锗PNP 80V 25A 106W音频放大\开关及功率放大2N1166锗PNP 100V 25A 106W音频放大\开关及功率放大2N1166A锗PNP 100V 25A 106W音频放大\开关及功率放大2N1167锗PNP 100V 25A 106W音频放大\开关及功率放大2N1167A锗PNP 100V 25A 106W音频放大\开关及功率放大2N1168锗PNP 50V 5A 45W音频放大\开关及功率放大 2N1169锗NPN 40V 0.4A 低频开关管2N117硅NPN 45V 25mA 4MHz低频开关管2N1170锗PNP 40V 0.4A 低频开关管2N1171锗PNP 30V 1A 低频开关管2N1172锗PNP 40V 1.5A 低频开关管2N1173锗NPN 35V 0.2A 低频开关管2N1174锗PNP 35V 0.2A 低频开关管2N1175锗PNP 35V 0.5A 低频开关管2N1175A锗PNP 35V 0.5A 低频开关管2N1176锗PNP 15V 0.3A 音频放大2N1176A锗PNP 40V 0.3A 音频放大2N1176B锗PNP 60V 0.3A 音频放大2N1177锗PNP 30V 10mA 140MHz普通射频2N1178锗PNP 30V 10mA 140MHz普通射频2N1179锗PNP 30V 10mA 140MHz普通射频2N118硅NPN 45V 25mA 5MHz低频开关管2N1180锗PNP 30V 10mA 100MHz普通射频2N1182锗PNP 60V 5A 106W音频放大\开关及功率放大 2N1183锗PNP 45V 3A 音频放大\开关及功率放大 2N1183A锗PNP 60V 3A 音频放大\开关及功率放大 2N1183B锗PNP 80V 3A 音频放大\开关及功率放大 2N1184锗PNP 45V 3A 音频放大\开关及功率放大 2N1184A锗PNP 60V 3A 音频放大\开关及功率放大 2N1184B锗PNP 80V 3A 音频放大\开关及功率放大2N1185锗PNP 45V 0.5A β=190-400低频开关管2N1186锗PNP 60V 0.5A β=30-70低频开关管2N1187锗PNP 60V 0.5A β=50-120低频开关管2N1188锗PNP 60V 0.5A β=100-225低频开关管2N1189锗PNP 45V 0.5A β=115音频放大及驱动?2N118A硅NPN 45V 25mA 5MHz低频开关管2N119硅NPN 45V 25mA 6MHz低频开关管2N1190锗PNP 45V 0.5A β=170音频放大及驱动?2N1191锗PNP 40V 0.2A β=30-70低频开关管2N1192锗PNP 40V 0.2A β=50-125低频开关管2N1193锗PNP 40V 0.2A β=100-250低频开关管2N1194锗PNP 40V 0.2A β=190-500低频开关管2N1195锗PNP 30V 40mA 1GHz用于UHF频段及射频2N1196硅PNP 70V 0.1A 普通用途2N1197硅PNP 70V 0.1A 普通用途2N1198锗NPN 25V 75mA 9MHz低频开关管2N1199硅NPN 20V 0.1A 125MHz普通射频\开关管2N1199A硅NPN 20V 0.1A 125MHz普通射频\开关管2N1200硅NPN 20V 0.1A 普通射频2N1201硅NPN 20V 0.1A 普通射频2N1202锗PNP 80V 3.5A 34W功率放大\开关管2N1203锗PNP 120V 3.5A 34W功率放大\开关管2N1204锗PNP 20V 0.5A 开关管2N1204A锗PNP 20V 0.5A 开关管2N1205硅NPN 20V 25MHz普通用途2N1206硅NPN 60V 0.15A 3W低频开关管2N1207硅NPN 125V 0.15A 3W低频开关管2N1208硅NPN 60V 5A 45W功率放大\开关管2N1208/1硅NPN 60V 5A 45W功率放大\开关管2N1209硅NPN 45V 5A 45W功率放大\开关管2N1209/1硅NPN 45V 5A 45W功率放大\开关管2N1210硅NPN 60V 5A 30W功率放大\开关管2N1210/1硅NPN 60V 5A 30W功率放大\开关管2N1211硅NPN 80V 5A 30W功率放大\开关管2N1211/1硅NPN 80V 5A 30W功率放大\开关管2N1212硅NPN 60V 5A 45W功率放大\开关管2N1212/1硅NPN 60V 5A 45W功率放大\开关管2N1217锗NPN 20V 25mA 9MHz低频开关管2N1218锗NPN 45V 3A 20W音频放大\开关及功率放大 2N1219硅PNP 30V 0.1A β>18普通用途2N122硅NPN 120V 0.14A 9W低频开关管2N1220硅PNP 30V 0.1A β>9普通用途2N1221硅PNP 30V 0.1A β>18普通用途2N1222硅PNP 30V 0.1A β>9普通用途2N1223硅PNP 30V 0.1A β>6普通用途2N1224锗PNP 40V 10mA 30MHz普通射频2N1225锗PNP 40V 10mA 70MHz普通射频2N1226锗PNP 60V 10mA 30MHz普通射频2N1227锗PNP 35V 3A 50W音频放大\开关及功率放大 2N1228硅PNP 15V 0.1A β=14-32普通用途2N1229硅PNP 15V 0.1A β=28-65普通用途2N123锗PNP 20V 0.5A 开关管2N123/5锗PNP 20V 0.5A 开关管2N1230硅PNP 35V 0.1A β=14-32普通用途2N1231硅PNP 35V 0.1A β=28-65普通用途2N1232硅PNP 60V 0.1A β=14-32普通用途2N1232A硅PNP 60V 0.1A β=14-32普通用途2N1233硅PNP 60V 0.1A β=28-65普通用途2N1234硅PNP 110V 0.1A β=14-32普通用途2N1235硅NPN 120V 5A 85W功率放大\开关管2N1238硅PNP 15V 0.1A β=14-32普通用途2N1239硅PNP 15V 0.1A β=28-65普通用途2N124锗NPN 10V 8mA β=12-24开关管2N1240硅PNP 35V 0.1A β=14-32普通用途2N1241硅PNP 35V 0.1A β=28-65普通用途2N1242硅PNP 60V 0.1A β=14-32普通用途2N1243硅PNP 60V 0.1A β=28-65普通用途2N1244硅PNP 110V 0.1A β=14-32普通用途2N1245锗PNP 30V 4A 20W音频功率放大2N1246锗PNP 30V 4A 20W音频功率放大2N1247硅NPN 6V 5mA β>15普通用途2N1248硅NPN 6V 5mA β>15普通用途2N1249硅NPN 6V 5mA β>15普通用途2N125锗NPN 10V 8mA β=24-48开关管2N1250硅NPN 50V 5A 85W音频放大\开关及功率放大 2N1250/1硅NPN 50V 5A 85W音频放大\开关及功率放大 2N1251锗NPN 20V 0.1A 低频开关管2N1252硅NPN 30V 1A β=15-45低频开关管2N1252A硅NPN 30V 1A β=15-45低频开关管2N1253硅NPN 30V 1A β=30-90低频开关管2N1253A硅NPN 30V 1A β=30-90低频开关管2N1254硅PNP 30V 0.1A β=25-50普通用途2N1255硅PNP 30V 0.1A β=40-80普通用途2N1256硅PNP 40V 0.1A β=25-50普通用途2N1257硅PNP 40V 0.1A β=40-80普通用途2N1258硅PNP 50V 0.1A β=75-150普通用途2N1259硅PNP 50V 0.1A β=25-100普通用途2N126锗NPN 10V 8mA β=48-100开关管 2N1260硅NPN 120V 2A 85W功率放大\开关管2N1261锗PNP 80V 3.5A 34W功率放大\开关管2N1261A锗PNP 80V 3.5A 34W功率放大\开关管2N1262锗PNP 80V 3.5A 34W功率放大\开关管2N1262A锗PNP 80V 3.5A 34W功率放大\开关管2N1263锗PNP 80V 3.5A 34W功率放大\开关管 2N1263A锗PNP 80V 3.5A 34W功率放大\开关管 2N1264锗PNP 20V 10mA 3MHz普通射频2N1264/13锗PNP 20V 10mA 3MHz普通射频 2N1265锗PNP 20V 0.1A 音频放大2N1265/5锗PNP 20V 0.1A 音频放大2N1266锗PNP 10V 音频放大2N1267硅NPN 20V 0.1A β=4-16普通用途2N1268硅NPN 20V 0.1A β=7-30普通用途2N1269硅NPN 20V 0.1A β=20-80普通用途2N127锗NPN 10V 8mA β=100-200开关管2N1270硅NPN 20V 0.1A β=4-16普通用途2N1271硅NPN 20V 0.1A β=7-30普通用途2N1272硅NPN 20V 0.1A β=20-80普通用途 2N1273锗PNP 15V 0.2A 低频开关管2N1274锗PNP 25V 0.2A 低频开关管2N1275硅PNP 100V 0.1A 普通驱动管2N1276硅NP N 40V 25mA β=9-22普通用途 2N1277硅NPN 40V 25mA β=18-44普通用途 2N1278硅NPN 40V 25mA β=37-90普通用途 2N1279硅NPN 40V 25mA β=76-330普通用途2N128锗PNP 10V 5mA 28MHz普通射频2N1280锗PNP 16V 0.4A >5MHz低频开关管 2N1281锗PNP 16V 0.4A >7MHz低频开关管 2N1282锗PNP 16V 0.4A >10MHz低频开关管 2N1283锗PNP 20V 0.4A >5MHz低频开关管 2N1285锗PNP 40V 10mA 100MHz普通射频2N1287锗PNP 20V 50mA2N1287A锗PNP 20V 50mA2N1288锗NPN 15V 0.05A 60MHz开关管2N1289锗NPN 20V 0.05A 60MHz开关管2N129锗PNP 10V 5mA 30MHz普通射频2N1291锗PNP 35V 3A 20W音频放大\开关及功率放大 2N1292锗NPN 35V 3A 25W音频放大\开关及功率放大 2N1293锗PNP 60V 3A 20W音频放大\开关及功率放大 2N1294锗NPN 60V 3A 25W音频放大\开关及功率放大 2N1295锗PNP 80V 3A 20W音频放大\开关及功率放大 2N1296锗NPN 80V 3A 25W音频放大\开关及功率放大 2N1297锗PNP 100V 3A 20W音频放大\开关及功率放大 2N1298锗NPN 100V 3A 25W音频放大\开关及功率放大 2N1299锗NPN 40V 0.2A >4MHz低频开关管2N130锗PNP 25V 10mA 音频放大2N1300锗PNP 13V 0.1A 40MHz普通射频\开关管2N1301锗PNP 13V 0.1A 60MHz普通射频\开关管 2N1302锗NPN 25V 0.3A 5MHz低频开关管2N1303锗PNP 30V 0.3A 5MHz低频开关管2N1304锗NPN 25V 0.3A 10MHz低频开关管2N1305锗PNP 30V 0.3A 10MHz低频开关管2N1306锗NPN 25V 0.3A 15MHz低频开关管2N1307锗PNP 30V 0.3A 15MHz低频开关管2N1308锗NPN 25V 0.3A 25MHz低频开关管2N1309锗PNP 30V 0.3A 20MHz低频开关管2N130A锗PNP 45V 0.1A 音频放大2N131锗PNP 25V 10mA 音频放大2N1310锗NPN 90V 普通驱动管2N1311锗NPN 75V 普通驱动管2N1312锗NPN 50V 普通驱动管2N1313锗PNP 30V 0.4A 12MHz低频开关管2N1314锗PNP 40V 3.5A 125W音频放大\开关及功率放大 2N1315锗PNP 32V 3.5A 125W音频放大\开关及功率放大2N1316锗PNP 30V 0.4A >10MHz低频开关管2N1317锗PNP 20V 0.4A >10MHz低频开关管2N1318锗PNP 10V 0.4A >10MHz低频开关管2N1319锗PNP 20V 0.4A >3MHz低频开关管2N131A锗PNP 45V 0.1A 音频放大2N132锗PNP 25V 10mA 音频放大2N1320锗PNP 35V 3A 20W音频放大\开关及功率放大 2N1321锗NPN 35V 3A 25W音频放大\开关及功率放大 2N1322锗PNP 60V 3A 20W音频放大\开关及功率放大 2N1323锗NPN 60V 3A 25W音频放大\开关及功率放大 2N1324锗PNP 80V 3A 20W音频放大\开关及功率放大 2N1325锗NPN 80V 3A 25W音频放大\开关及功率放大 2N1326锗PNP 100V 3A 20W音频放大\开关及功率放大 2N1327锗NPN 100V 3A 25W音频放大\开关及功率放大 2N1328锗PNP 35V 3A 20W音频放大\开关及功率放大 2N1329锗NPN 35V 3A 25W音频放大\开关及功率放大 2N132A锗PNP 35V 0.1A 音频放大2N133锗PNP 25V 10mA 音频放大2N1330锗NPN 60V 3A 25W音频放大\开关及功率放大 2N1331锗PNP 80V 3A 20W音频放大\开关及功率放大 2N1332锗NPN 80V 3A 25W音频放大\开关及功率放大 2N1333锗PNP 100V 3A 20W音频放大\开关及功率放大 2N1334锗NPN 100V 3A 25W音频放大\开关及功率放大 2N1335硅NPN 120V 0.3A >70MHz普通射频或驱动 2N1336硅NPN 120V 0.3A >70MHz普通射频或驱动 2N1337硅NPN 120V 0.3A >70MHz普通射频或驱动 2N1338硅NPN 80V 0.3A >70MHz普通射频或驱动 2N1339硅NPN 120V 0.3A >70MHz普通射频或驱动 2N133A锗PNP 35V 0.1A 音频放大2N1340硅NPN 150V 0.3A >70MHz普通射频或驱动2N1341硅NPN 120V 0.3A >70MHz普通射频或驱动 2N1342硅NPN 150V 0.3A >70MHz普通射频或驱动 2N1343锗PNP 20V 0.4A >4MHz低频开关管2N1344锗PNP 15V 0.4A >7MHz低频开关管2N1345锗PNP 10V 0.4A >10MHz低频开关管2N1346锗PNP 12V 0.4A >10MHz低频开关管2N1347锗PNP 20V 0.2A >5MHz低频开关管2N1348锗PNP 40V 0.4A >5MHz低频开关管2N1349锗PNP 40V 0.4A >10MHz低频开关管2N135锗PNP 20V 50mA 普通射频2N1350锗PNP 50V 0.4A >8MHz低频开关管2N1351锗PNP 50V 0.4A >8MHz低频开关管2N1352锗PNP 30V 0.2A >低频开关管2N1353锗PNP 15V 0.2A >低频开关管2N1354锗PNP 15V 0.2A >3MHz低频开关管2N1355锗PNP 15V 0.2A >5MHz低频开关管2N1356锗PNP 15V 0.2A >5MHz低频开关管2N1357锗PNP 15V 0.2A >10MHz低频开关管2N1358锗PNP 80V 15A 70W音频放大\开关及功率放大 2N1358A锗PNP 80V 15A 70W音频放大\开关及功率放大 2N1358M锗PNP 80V 15A 70W音频放大\开关及功率放大 2N1359锗PNP 50V 10A 106W音频放大\开关及功率放大 2N136锗PNP 20V 50mA 普通射频2N1360锗PNP 50V 10A 106W音频放大\开关及功率放大 2N1361锗PNP 25V 0.2A 4MHz低频开关管2N1361A锗PNP 25V 0.2A 4MHz低频开关管2N1362锗PNP 100V 10A 106W音频放大\开关及功率放大 2N1363锗PNP 100V 10A 106W音频放大\开关及功率放大 2N1364锗PNP 120V 10A 106W音频放大\开关及功率放大 2N1365锗PNP 120V 10A 106W音频放大\开关及功率放大2N1366锗NPN 18V 25mA >5MHz低频开关管 2N1367锗NPN 18V 25mA >低频开关管2N137锗PNP 10V 50mA 10MHz普通射频2N1370锗PNP 25V 0.2A β=45-165低频开关管2N1371锗PNP 45V 0.2A β=45-165低频开关管2N1372锗PNP 25V 0.2A β=25-105低频开关管2N1373锗PNP 45V 0.2A β=25-105低频开关管2N1374锗PNP 25V 0.2A β=50-165低频开关管2N1375锗PNP 45V 0.2A β=50-165低频开关管2N1376锗PNP 25V 0.2A β=67-165低频开关管2N1377锗PNP 45V 0.2A β=67-165低频开关管2N1378锗PNP 12V 0.2A β=85-330低频开关管2N1379锗PNP 25V 0.2A β=85-330低频开关管 2N138锗PNP 24V 0.15A 低频开关管 2N1380锗PNP 12V 0.2A β=27-330低频开关管2N1381锗PNP 25V 0.2A β=27-330低频开关管2N1382锗PNP 25V 0.2A β=50-150低频开关管2N1383锗PNP 25V 0.2A β=30-150低频开关管2N1384锗PNP 30V 0.5A 35MHz低频开关管2N1385锗PNP 25V 0.1A >250MHz普通射频\开关管 2N1386硅NPN 25V 0.05A 60MHz普通用途2N1387硅NPN 30V 0.05A 50MHz普通用途2N1388硅NPN 45V 0.05A >50MHz普通用途2N1389硅NPN 50V 0.05A >25MHz普通用途 2N138A/B锗PNP 45V 0.1A 低频开关管2N139锗PNP 16V 15mA 普通射频 2N1390硅NPN 20V 0.05A >20MHz普通用途2N1391锗NPN 25V >3MHz低频开关管2N1395锗PNP 40V 10mA 30MHz普通射频2N1396锗PNP 40V 10mA 100MHz普通射频2N1397锗PNP 40V 10mA 120MHz普通射频2N1398锗PNP 30V 10mA >140MHz普通射频2N1399锗PNP 30V 10mA >140MHz普通射频2N140锗PNP 16V 15mA 普通射频2N1400锗PNP 30V 10mA >100MHz普通射频2N1401锗PNP 30V 10mA >120MHz普通射频2N1401A锗PNP 30V 10mA >120MHz普通射频2N1402锗PNP 30V 10mA >100MHz普通射频2N1403锗PNP 15V 0.1A >200MHz普通射频2N1404锗PNP 25V 0.3A 普通射频\开关管2N1404A锗PNP 25V 0.3A 普通射频\开关管2N1405锗PNP 30V 0.05A >250MHz普通射频2N1406锗PNP 30V 0.05A >250MHz普通射频2N1407锗PNP 30V 0.05A >200MHz普通射频2N1408锗PNP 50V 0.2A 低频开关管2N1409硅NPN 30V 0.5A β=15-45低频开关管2N1409A硅NPN 30V 0.5A β=15-45低频开关管2N141锗PNP 60V 0.8A *K音频放大及驱动?2N141/13锗PNP 60V 0.8A 音频放大及驱动?2N1410硅NPN 30V 0.5A β=30-90低频开关管2N1410A硅NPN 30V 0.5A β=30-90低频开关管2N1411锗PNP 5V 0.05A 开关管2N1412锗PNP 100V 15A 150W音频放大\开关及功率放大 2N1412A锗PNP 100V 15A 150W音频放大\开关及功率放大 2N1413锗PNP 35V 0.5A β=25-42低频开关管2N1414锗PNP 35V 0.5A β=34-65低频开关管2N1415锗PNP 35V 0.5A β=53-90低频开关管2N14162N1418硅NPN 30V 0.05A 普通射频\开关管2N1419锗PNP 80V 25A 87W音频放大\开关及功率放大2N142锗NPN 60V 0.8A *K音频放大及驱动?2N142/13锗NPN 60V 0.8A *K音频放大及驱动?2N1420硅NPN 60V 1A 低频开关管2N1420A硅NPN 60V 1A 低频开关管2N1421硅NPN 60V 3A 30W功率放大\开关管2N1422硅NPN 60V 3A 30W功率放大\开关管2N1423硅NPN 60V 3A 60W功率放大\开关管2N1424硅NPN 60V 3A 60W功率放大\开关管2N1425锗PNP 24V 10mA 33MHz普通射频2N1426锗PNP 24V 10mA 33MHz普通射频2N1427锗PNP 6V 0.05A 普通射频\开关管2N1428硅PNP 6V 0.05A 低频开关管2N1429硅PNP 6V 0.05A 低频开关管2N143锗PNP 60V 0.8A 1W *K音频放大及驱动?2N143/13锗PNP 60V 0.8A 1W *K音频放大及驱动?2N1430锗PNP 120V 10A 70W功率放大\开关管2N1431锗NPN 20V 0.1A 低频开关管2N1432锗PNP 45V 10mA 普通射频2N1433锗PNP 80V 3.5A β=20-50音频放大\开关及功率放大 2N1434锗PNP 80V 3.5A β=45-115音频放大\开关及功率放大 2N1435锗PNP 80V 3.5A β=30-75音频放大\开关及功率放大 2N1436锗PNP 15V 0.05A 开关管2N1437锗PNP 100V 3A 23W功率放大\开关管2N1438锗PNP 100V 3A 23W功率放大\开关管2N1439硅PNP 50V 0.1A β=5-12普通用途2N144锗NPN 60V 0.8A 1W *K音频放大及驱动?2N144/13锗NPN 60V 0.8A 1W *K音频放大及驱动?2N1440硅PNP 50V 0.1A β=9-22普通用途2N1441硅PNP 50V 0.1A β=18-36普通用途2N1442硅PNP 50V 0.1A β=30-65普通用途2N1443硅PNP 50V 0.1A β>50普通用途2N1444硅NPN 60V 0.5A 低频开关管2N1445硅NPN 120V 0.75A 低频开关管2N1446锗PNP 45V 0.4A β=16-45低频开关管2N1447锗PNP 45V 0.4A β=36-65低频开关管2N1448锗PNP 45V 0.4A β=50-90低频开关管2N1449锗PNP 45V 0.4A β=70-125低频开关管2N145锗NPN 20V 5mA >普通射频2N1450锗PNP 30V 0.1A 开关管2N1451锗PNP 45V 0.4A β=20-65音频放大2N1452锗PNP 45V 0.4A β=30-90音频放大2N1453锗PNP 30V 5A 43W音频放大\开关及功率放大 2N1454锗PNP 30V 5A 43W音频放大\开关及功率放大 2N1455锗PNP 60V 5A 43W音频放大\开关及功率放大 2N1456锗PNP 60V 5A 43W音频放大\开关及功率放大 2N1457锗PNP 80V 5A 43W音频放大\开关及功率放大 2N1458锗PNP 80V 5A 43W音频放大\开关及功率放大 2N146锗NPN 20V 5mA >普通射频2N1461锗PNP 30V 5A 43W音频放大\开关及功率放大 2N1462锗PNP 30V 5A 43W音频放大\开关及功率放大 2N1463锗PNP 60V 5A 43W音频放大\开关及功率放大 2N1464锗PNP 60V 5A 43W音频放大\开关及功率放大 2N1465锗PNP 120V 3A 20W音频放大\开关及功率放大 2N1466锗PNP 120V 3A 20W音频放大\开关及功率放大2N1468硅NPN2N1469硅PNP 40V 0.1A 普通用途2N147锗NPN 20V 5mA >普通射频2N1470硅NPN 60V 3A 55W音频放大\开关及功率放大 2N1471锗PNP 12V 0.2A 普通用途2N1472硅NPN 25V 0.1A 140MHz开关管2N1473锗NPN 40V 0.4A >4MHz低频开关管2N1474硅PNP 60V 0.1A 普通用途2N1474A硅PNP 60V 0.1A 普通用途2N1475硅PNP 60V 0.1A β=36-88普通用途2N1476硅PNP 100V 0.1A β=12-36普通用途2N1477硅PNP 100V 0.1A β=30-66普通用途2N1478锗PNP 30V 0.5A 低频开关管2N1479硅NPN 60V 1.5A 5W低频开关管2N148锗NPN 16V 5mA >普通射频2N1480硅NPN 100V 1.5A 5W低频开关管2N1481硅NPN 60V 1.5A 5W低频开关管2N1482硅NPN 100V 1.5A 5W低频开关管2N1483硅NPN 60V 3A 25W音频放大\开关及功率放大 2N1484硅NPN 100V 3A 25W音频放大\开关及功率放大 2N1485硅NPN 60V 3A 25W音频放大\开关及功率放大 2N1486硅NPN 100V 3A 25W音频放大\开关及功率放大 2N1487硅NPN 50V 6A 75W音频放大\开关及功率放大 2N1488硅NPN 100V 6A 75W音频放大\开关及功率放大 2N1489硅NPN 60V 6A 75W音频放大\开关及功率放大 2N148A锗NPN 32V 5mA >普通射频2N149锗NPN 16V 5mA >普通射频2N1490硅NPN 100V 6A 75W音频放大\开关及功率放大 2N1491硅NPN 30V 0.1A 250MHzVHF驱动2N1492硅NPN 60V 0.1A 275MHzVHF驱动2N1493硅NPN 100V 0.1A 300MHzVHF驱动2N1494锗PNP 20V 0.5A <35ns开关管2N1494A锗PNP 20V 0.5A <35ns开关管2N1495锗PNP 40V 0.5A <55ns开关管2N1495A锗PNP 40V 0.5A <55ns开关管2N1496锗PNP 40V 0.5A <55ns开关管2N1499锗PNP 20V 0.1A 开关管2N1499A锗PNP 20V 0.1A 开关管2N1499B锗PNP 30V 开关管2N149A锗NPN 32V 5mA >普通射频2N150锗NPN 16V 5mA >普通射频2N1500锗PNP 15V 0.05A 开关管2N1500/18锗PNP 15V 0.05A 开关管 2N1501锗PNP 60V 3.5A 34W功率放大\开关管2N1502锗PNP 40V 3.5A 34W功率放大\开关管2N1504锗PNP 80V 3A 25W功率放大\开关管2N1504/10锗PNP 80V 3A 25W功率放大\开关管 2N1505硅NPN 50V 0.5A 普通射频或驱动2N1506硅NPN 60V 0.5A 普通射频或驱动2N1506A硅NPN 60V 0.5A 普通射频或驱动2N1507硅NPN 60V 1A 低频开关管2N1508硅NPN 100V 1A 1W低频开关管2N1509硅NPN 60V 1A 1W低频开关管2N150A锗NPN 32V 5mA >普通射频2N151锗PNP2N1510锗NPN 75V 0.02A 低频开关管 2N1511硅NPN 60V 6A 75W功率放大\开关管2N1512硅NPN 100V 6A 75W功率放大\开关管2N1513硅NPN 60V 6A 75W功率放大\开关管2N1514硅NPN 100V 6A 75W功率放大\开关管2N1515锗PNP 20V 10mA 70MHz普通射频2N1516锗PNP 20V 10mA 70MHz普通射频2N1517锗PNP 20V 10mA 70MHz普通射频2N1517A锗PNP 40V 10mA 70MHz普通射频2N1518锗PNP 50V 25A 70W音频放大\开关及功率放大 2N1519锗PNP 80V 25A 70W音频放大\开关及功率放大2N152锗PNP2N1520锗PNP 50V 35A 70W音频放大\开关及功率放大2N1521锗PNP 80V 35A 70W音频放大\开关及功率放大2N1522锗PNP 50V 50A 70W音频放大\开关及功率放大2N1523锗PNP 80V 50A 70W音频放大\开关及功率放大2N1524锗PNP 24V 10mA 33MHz普通射频2N1525锗PNP 24V 10mA 33MHz普通射频2N1526锗PNP 24V 10mA 33MHz普通射频2N1527锗PNP 24V 10mA 33MHz普通射频2N1528硅NPN 25V 20mA 20MHz普通射频\开关管2N1529锗PNP 40V 5A 106W音频放大\开关及功率放大2N1529A锗PNP 40V 5A 106W音频放大\开关及功率放大2N153锗PNP2N1418硅NPN 30V 0.05A 普通射频\开关管2N1419锗PNP 80V 25A 87W音频放大\开关及功率放大2N142锗NPN 60V 0.8A *K音频放大及驱动?2N142/13锗NPN 60V 0.8A *K音频放大及驱动?2N1420硅NPN 60V 1A 低频开关管2N1420A硅NPN 60V 1A 低频开关管2N1421硅NPN 60V 3A 30W功率放大\开关管2N1422硅NPN 60V 3A 30W功率放大\开关管2N1423硅NPN 60V 3A 60W功率放大\开关管2N1424硅NPN 60V 3A 60W功率放大\开关管2N1425锗PNP 24V 10mA 33MHz普通射频2N1426锗PNP 24V 10mA 33MHz普通射频2N1427锗PNP 6V 0.05A 普通射频\开关管2N1428硅PNP 6V 0.05A 低频开关管2N1429硅PNP 6V 0.05A 低频开关管2N143锗PNP 60V 0.8A 1W *K音频放大及驱动?2N143/13锗PNP 60V 0.8A 1W *K音频放大及驱动?2N1430锗PNP 120V 10A 70W功率放大\开关管2N1431锗NPN 20V 0.1A 低频开关管2N1432锗PNP 45V 10mA 普通射频2N1433锗PNP 80V 3.5A β=20-50音频放大\开关及功率放大 2N1434锗PNP 80V 3.5A β=45-115音频放大\开关及功率放大 2N1435锗P NP 80V 3.5A β=30-75音频放大\开关及功率放大 2N1436锗PNP 15V 0.05A 开关管2N1437锗PNP 100V 3A 23W功率放大\开关管2N1438锗PNP 100V 3A 23W功率放大\开关管2N1439硅PNP 50V 0.1A β=5-12普通用途2N144锗NPN 60V 0.8A 1W *K音频放大及驱动?2N144/13锗NPN 60V 0.8A 1W *K音频放大及驱动?2N1440硅PNP 50V 0.1A β=9-22普通用途2N1441硅PNP 50V 0.1A β=18-36普通用途2N1442硅PNP 50V 0.1A β=30-65普通用途2N1443硅PNP 50V 0.1A β>50普通用途2N1444硅NPN 60V 0.5A 低频开关管2N1445硅NPN 120V 0.75A 低频开关管2N1446锗PNP 45V 0.4A β=16-45低频开关管2N1447锗PNP 45V 0.4A β=36-65低频开关管2N1448锗PNP 45V 0.4A β=50-90低频开关管2N1449锗PNP 45V 0.4A β=70-125低频开关管2N145锗NPN 20V 5mA >普通射频2N1450锗PNP 30V 0.1A 开关管2N1451锗PNP 45V 0.4A β=20-65音频放大2N1452锗PNP 45V 0.4A β=30-90音频放大2N1453锗PNP 30V 5A 43W音频放大\开关及功率放大2N1454锗PNP 30V 5A 43W音频放大\开关及功率放大2N1455锗PNP 60V 5A 43W音频放大\开关及功率放大2N1456锗PNP 60V 5A 43W音频放大\开关及功率放大2N1458锗PNP 80V 5A 43W音频放大\开关及功率放大 2N146锗NPN 20V 5mA >普通射频2N1461锗PNP 30V 5A 43W音频放大\开关及功率放大 2N1462锗PNP 30V 5A 43W音频放大\开关及功率放大 2N1463锗PNP 60V 5A 43W音频放大\开关及功率放大 2N1464锗PNP 60V 5A 43W音频放大\开关及功率放大 2N1465锗PNP 120V 3A 20W音频放大\开关及功率放大 2N1466锗PNP 120V 3A 20W音频放大\开关及功率放大 2N1468硅NPN2N1469硅PNP 40V 0.1A 普通用途2N147锗NPN 20V 5mA >普通射频2N1470硅NPN 60V 3A 55W音频放大\开关及功率放大 2N1471锗PNP 12V 0.2A 普通用途2N1472硅NPN 25V 0.1A 140MHz开关管2N1473锗NPN 40V 0.4A >4MHz低频开关管2N1474硅PNP 60V 0.1A 普通用途2N1474A硅PNP 60V 0.1A 普通用途2N1475硅PNP 60V 0.1A β=36-88普通用途2N1476硅PNP 100V 0.1A β=12-36普通用途2N1477硅PNP 100V 0.1A β=30-66普通用途2N1478锗PNP 30V 0.5A 低频开关管2N1479硅NPN 60V 1.5A 5W低频开关管2N148锗NPN 16V 5mA >普通射频2N1480硅NPN 100V 1.5A 5W低频开关管2N1481硅NPN 60V 1.5A 5W低频开关管2N1482硅NPN 100V 1.5A 5W低频开关管2N1483硅NPN 60V 3A 25W音频放大\开关及功率放大 2N1484硅NPN 100V 3A 25W音频放大\开关及功率放大 2N1485硅NPN 60V 3A 25W音频放大\开关及功率放大2N1487硅NPN 50V 6A 75W音频放大\开关及功率放大 2N1488硅NPN 100V 6A 75W音频放大\开关及功率放大 2N1489硅NPN 60V 6A 75W音频放大\开关及功率放大 2N148A锗NPN 32V 5mA >普通射频2N149锗NPN 16V 5mA >普通射频2N1490硅NPN 100V 6A 75W音频放大\开关及功率放大 2N1491硅NPN 30V 0.1A 250MHzVHF驱动2N1492硅NPN 60V 0.1A 275MHzVHF驱动2N1493硅NPN 100V 0.1A 300MHzVHF驱动2N1494锗PNP 20V 0.5A <35ns开关管2N1494A锗PNP 20V 0.5A <35ns开关管2N1495锗PNP 40V 0.5A <55ns开关管2N1495A锗PNP 40V 0.5A <55ns开关管2N1496锗PNP 40V 0.5A <55ns开关管2N1499锗PNP 20V 0.1A 开关管2N1499A锗PNP 20V 0.1A 开关管2N1499B锗PNP 30V 开关管2N149A锗NPN 32V 5mA >普通射频2N150锗NPN 16V 5mA >普通射频2N1500锗PNP 15V 0.05A 开关管2N1500/18锗PNP 15V 0.05A 开关管2N1501锗PNP 60V 3.5A 34W功率放大\开关管2N1502锗PNP 40V 3.5A 34W功率放大\开关管2N1504锗PNP 80V 3A 25W功率放大\开关管2N1504/10锗PNP 80V 3A 25W功率放大\开关管2N1505硅NPN 50V 0.5A 普通射频或驱动2N1506硅NPN 60V 0.5A 普通射频或驱动2N1506A硅NPN 60V 0.5A 普通射频或驱动2N1507硅NPN 60V 1A 低频开关管2N1508硅NPN 100V 1A 1W低频开关管2N1509硅NPN 60V 1A 1W低频开关管2N150A锗NPN 32V 5mA >普通射频2N151锗PNP2N1510锗NPN 75V 0.02A 低频开关管2N1511硅NPN 60V 6A 75W功率放大\开关管2N1512硅NPN 100V 6A 75W功率放大\开关管2N1513硅NPN 60V 6A 75W功率放大\开关管2N1514硅NPN 100V 6A 75W功率放大\开关管2N1515锗PNP 20V 10mA 70MHz普通射频2N1516锗PNP 20V 10mA 70MHz普通射频2N1517锗PNP 20V 10mA 70MHz普通射频2N1517A锗PNP 40V 10mA 70MHz普通射频2N1518锗PNP 50V 25A 70W音频放大\开关及功率放大 2N1519锗PNP 80V 25A 70W音频放大\开关及功率放大 2N152锗PNP2N1520锗PNP 50V 35A 70W音频放大\开关及功率放大 2N1521锗PNP 80V 35A 70W音频放大\开关及功率放大 2N1522锗PNP 50V 50A 70W音频放大\开关及功率放大 2N1523锗PNP 80V 50A 70W音频放大\开关及功率放大 2N1524锗PNP 24V 10mA 33MHz普通射频2N1525锗PNP 24V 10mA 33MHz普通射频2N1526锗PNP 24V 10mA 33MHz普通射频2N1527锗PNP 24V 10mA 33MHz普通射频2N1528硅NPN 25V 20mA 20MHz普通射频\开关管2N1529锗PNP 40V 5A 106W音频放大\开关及功率放大 2N1529A锗PNP 40V 5A 106W音频放大\开关及功率放大 2N153锗PNP2N1531A锗PNP 80V 5A 106W音频放大\开关及功率放大 2N1532锗PNP 100V 5A 106W音频放大\开关及功率放大2N1533锗PNP 120V 5A 106W音频放大\开关及功率放大 2N1533A锗PNP 120V 5A 106W音频放大\开关及功率放大 2N1534锗PNP 40V 5A 106W音频放大\开关及功率放大 2N1534A锗PNP 40V 5A 106W音频放大\开关及功率放大 2N1535锗PNP 60V 5A 106W音频放大\开关及功率放大 2N1535A锗PNP 60V 5A 106W音频放大\开关及功率放大 2N1536锗PNP 80V 5A 106W音频放大\开关及功率放大 2N1536A锗PNP 80V 5A 106W音频放大\开关及功率放大 2N1537锗PNP 100V 5A 106W音频放大\开关及功率放大 2N1537A锗PNP 100V 5A 106W音频放大\开关及功率放大 2N1538锗PNP 120V 5A 106W音频放大\开关及功率放大 2N1538A锗PNP 120V 5A 106W音频放大\开关及功率放大 2N1539锗PNP 40V 5A 106W音频放大\开关及功率放大 2N1539A锗PNP 40V 5A 106W音频放大\开关及功率放大 2N154锗PNP2N1540锗PNP 60V 5A 106W音频放大\开关及功率放大 2N1540A锗PNP 60V 5A 106W音频放大\开关及功率放大 2N1541锗PNP 80V 5A 106W音频放大\开关及功率放大 2N1541A锗PNP 80V 5A 106W音频放大\开关及功率放大 2N1542锗PNP 100V 5A 106W音频放大\开关及功率放大 2N1542A锗PNP 100V 5A 106W音频放大\开关及功率放大 2N1543锗PNP 120V 5A 106W音频放大\开关及功率放大 2N1543A锗PNP 120V 5A 106W音频放大\开关及功率放大 2N1544锗PNP 40V 5A 106W音频放大\开关及功率放大 2N1544A锗PNP 40V 5A 106W音频放大\开关及功率放大 2N1545锗PNP 60V 5A 106W音频放大\开关及功率放大 2N1545A锗PNP 60V 5A 106W音频放大\开关及功率放大 2N1546锗PNP 80V 5A 106W音频放大\开关及功率放大 2N1546A锗PNP 80V 5A 106W音频放大\开关及功率放大2N1547A锗PNP 100V 5A 106W音频放大\开关及功率放大 2N1548锗PNP 120V 5A 106W音频放大\开关及功率放大 2N1548A锗PNP 120V 5A 106W音频放大\开关及功率放大 2N1549锗PNP 40V 15A 106W音频放大\开关及功率放大 2N1549A锗PNP 40V 15A 106W音频放大\开关及功率放大 2N155锗PNP 30V 3A 20W音频放大\开关及功率放大2N1550锗PNP 60V 15A 106W音频放大\开关及功率放大 2N1550A锗PNP 60V 15A 106W音频放大\开关及功率放大 2N1551锗PNP 80V 15A 106W音频放大\开关及功率放大 2N1551A锗PNP 80V 15A 106W音频放大\开关及功率放大 2N1552锗PNP 100V 15A 106W音频放大\开关及功率放大 2N1552A锗PNP 100V 15A 106W音频放大\开关及功率放大 2N1553锗PNP 40V 15A 106W音频放大\开关及功率放大 2N1553A锗PNP 40V 15A 106W音频放大\开关及功率放大 2N1554锗PNP 60V 15A 106W音频放大\开关及功率放大 2N1554A锗PNP 60V 15A 106W音频放大\开关及功率放大 2N1555锗PNP 80V 15A 106W音频放大\开关及功率放大 2N1555A锗PNP 80V 15A 106W音频放大\开关及功率放大 2N1556锗PNP 100V 15A 106W音频放大\开关及功率放大 2N1556A锗PNP 100V 15A 106W音频放大\开关及功率放大 2N1557锗PNP 40V 15A 106W音频放大\开关及功率放大 2N1557A锗PNP 40V 15A 106W音频放大\开关及功率放大 2N1558锗PNP 60V 15A 106W音频放大\开关及功率放大 2N1558A锗PNP 60V 15A 106W音频放大\开关及功率放大 2N1559锗PNP 80V 15A 106W音频放大\开关及功率放大 2N1559A锗PNP 80V 15A 106W音频放大\开关及功率放大 2N156锗PNP 30V 3A 20W音频放大\开关及功率放大2N1560锗PNP 100V 15A 106W音频放大\开关及功率放大 2N1560A锗PNP 100V 15A 106W音频放大\开关及功率放大。

NI cDAQ

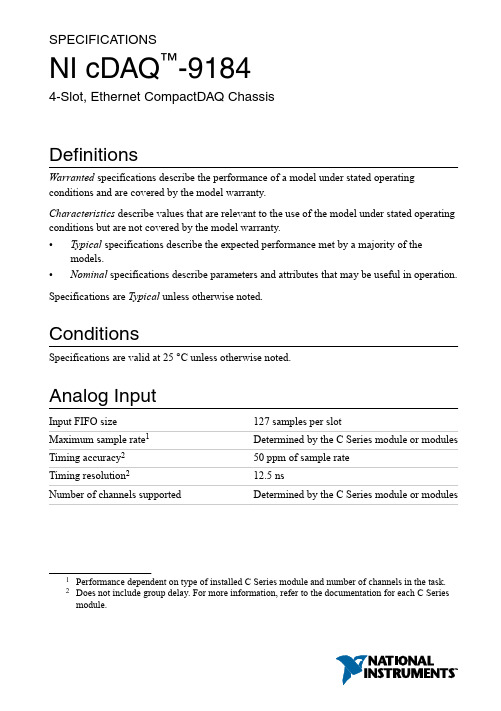

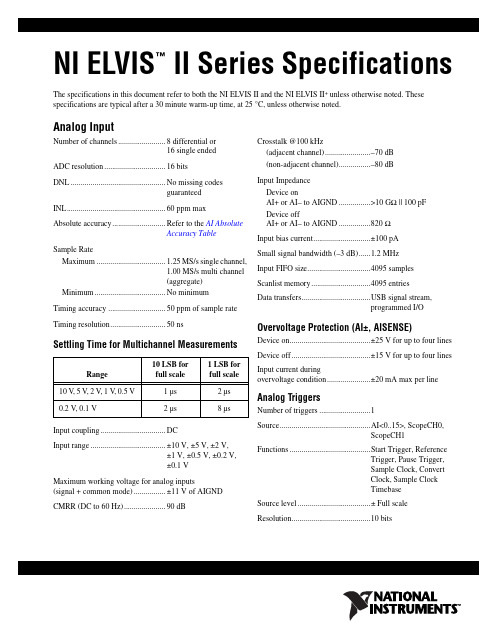

SPECIFICA TIONSNI cDAQ™-91844-Slot, Ethernet CompactDAQ ChassisDefinitionsWarranted specifications describe the performance of a model under stated operating conditions and are covered by the model warranty.Characteristics describe values that are relevant to the use of the model under stated operating conditions but are not covered by the model warranty.•Typical specifications describe the expected performance met by a majority of the models.•Nominal specifications describe parameters and attributes that may be useful in operation. Specifications are Typical unless otherwise noted.ConditionsSpecifications are valid at 25 °C unless otherwise noted.Analog InputInput FIFO size127 samples per slotMaximum sample rate1Determined by the C Series module or modules Timing accuracy250 ppm of sample rateTiming resolution212.5 nsNumber of channels supported Determined by the C Series module or modules 1Performance dependent on type of installed C Series module and number of channels in the task.2Does not include group delay. For more information, refer to the documentation for each C Series module.Analog OutputNumber of channels supportedHardware-timed taskOnboard regeneration16Non-regeneration Determined by the C Series module or modules Non-hardware-timed task Determined by the C Series module or modules Maximum update rateOnboard regeneration 1.6 MS/s (multi-channel, aggregate)Non-regeneration Determined by the C Series module or modules Timing accuracy50 ppm of sample rateTiming resolution12.5 nsOutput FIFO sizeOnboard regeneration8,191 samples shared among channels used Non-regeneration127 samples per slotAO waveform modes Non-periodic waveform,periodic waveform regeneration mode fromonboard memory,periodic waveform regeneration from hostbuffer including dynamic updateDigital Waveform CharacteristicsWaveform acquisition (DI) FIFOParallel modules511 samples per slotSerial modules63 samples per slotWaveform generation (DO) FIFOParallel modules2,047 samples per slotSerial modules63 samples per slotDigital input sample clock frequencyStreaming to application memory System-dependentFinite0 MHz to 10 MHz2| | NI cDAQ-9184 SpecificationsDigital output sample clock frequencyStreaming from application memory System-dependentRegeneration from FIFO0 MHz to 10 MHzFinite0 MHz to 10 MHzTiming accuracy50 ppmGeneral-Purpose Counters/TimersNumber of counters/timers4Resolution32 bitsCounter measurements Edge counting, pulse, semi-period, period,two-edge separation, pulse widthPosition measurements X1, X2, X4 quadrature encoding withChannel Z reloading; two-pulse encoding Output applications Pulse, pulse train with dynamic updates,frequency division, equivalent time sampling Internal base clocks80 MHz, 20 MHz, 100 kHzExternal base clock frequency0 MHz to 20 MHzBase clock accuracy50 ppmOutput frequency0 MHz to 20 MHzInputs Gate, Source, HW_Arm, Aux, A, B, Z,Up_DownRouting options for inputs Any module PFI, analog trigger, many internalsignalsFIFO Dedicated 127-sample FIFOFrequency GeneratorNumber of channels1Base clocks20 MHz, 10 MHz, 100 kHzDivisors 1 to 16 (integers)Base clock accuracy50 ppmOutput Any module PFI terminalNI cDAQ-9184 Specifications| © National Instruments| 3Module PFI CharacteristicsFunctionality Static digital input, static digital output, timinginput, and timing outputTiming output sources3Many analog input, analog output, counter,digital input, and digital output timing signals Timing input frequency0 MHz to 20 MHzTiming output frequency0 MHz to 20 MHzDigital TriggersSource Any module PFI terminalPolarity Software-selectable for most signalsAnalog input function Start Trigger, Reference Trigger,Pause Trigger, Sample Clock,Sample Clock TimebaseAnalog output function Start Trigger, Pause Trigger, Sample Clock,Sample Clock TimebaseCounter/timer function Gate, Source, HW_Arm, Aux, A, B, Z,Up_DownModule I/O StatesAt power-on Module-dependent. Refer to the documentationfor each C Series module.Network InterfaceNetwork protocols TCP/IP, UDPNetwork ports used HTTP:80 (configuration only), TCP:3580;UDP:5353 (configuration only), TCP:5353(configuration only); TCP:31415; UDP:7865(configuration only), UDP:8473 (configurationonly)Network IP configuration DHCP + Link-Local, DHCP, Static,Link-Local3Actual available signals are dependent on type of installed C Series module.4| | NI cDAQ-9184 SpecificationsHigh-performance data streams7Data stream types available Analog input, analog output, digital input,digital output, counter/timer input,counter/timer output, NI-XNET4Default MTU size1500 bytesJumbo frame support Up to 9000 bytesEthernetNetwork interface1000 Base-TX, full-duplex; 1000 Base-TX,half-duplex; 100 Base-TX, full-duplex;100 Base-TX, half-duplex; 10 Base-T,full-duplex; 10 Base-T, half-duplex Communication rates10/100/1000 Mbps, auto-negotiated Maximum cabling distance100 m/segmentPower RequirementsCaution The protection provided by the NI cDAQ-9184 chassis can be impaired ifit is used in a manner not described in the NI cDAQ-9181/9184/9188/9191 UserManual.Note Some C Series modules have additional power requirements. For moreinformation about C Series module power requirements, refer to the documentationfor each C Series module.Note Sleep mode for C Series modules is not supported in the NI cDAQ-9184.V oltage input range9 V to 30 VMaximum power consumption515 W4When a session is active, CAN or LIN (NI-XNET) C Series modules use a total of two data streams regardless of the number of NI-XNET modules in the chassis.5Includes maximum 1 W module load per slot across rated temperature and product variations.NI cDAQ-9184 Specifications| © National Instruments| 5Note The maximum power consumption specification is based on a fully populatedsystem running a high-stress application at elevated ambient temperature and withall C Series modules consuming the maximum allowed power.Power input connector 2 positions 3.5 mm pitch mini-combicon screwterminal with screw flanges, SauroCTMH020F8-0N001Power input mating connector Sauro CTF020V8, Phoenix Contact 1714977,or equivalentPhysical CharacteristicsWeight (unloaded)Approximately 643 g (22.7 oz)Dimensions (unloaded)178.1 mm × 88.1 mm × 64.3 mm(7.01 in. × 3.47 in. × 2.53 in.) Refer to thefollowing figure.Screw-terminal wiringGauge0.5 mm 2 to 2.1 mm2 (20 AWG to 14 AWG)copper conductor wireWire strip length 6 mm (0.24 in.) of insulation stripped from theendTemperature rating85 °CTorque for screw terminals0.20 N · m to 0.25 N · m (1.8 lb · in. to2.2 lb · in.)Wires per screw terminal One wire per screw terminalConnector securementSecurement type Screw flanges providedTorque for screw flanges0.20 N · m to 0.25 N · m (1.8 lb · in. to2.2 lb · in.)If you need to clean the chassis, wipe it with a dry towel.6| | NI cDAQ-9184 SpecificationsFigure 1. NI cDAQ-9184 Dimensions30.6 mm 47.2 mm Safety VoltagesConnect only voltages that are within these limits.V terminal to C terminal30 V maximum, Measurement Category IMeasurement Category I is for measurements performed on circuits not directly connected to the electrical distribution system referred to as MAINS voltage. MAINS is a hazardous liveNI cDAQ-9184 Specifications | © National Instruments | 7electrical supply system that powers equipment. This category is for measurements of voltages from specially protected secondary circuits. Such voltage measurements include signal levels, special equipment, limited-energy parts of equipment, circuits powered by regulatedlow-voltage sources, and electronics.Caution Do not connect the system to signals or use for measurements withinMeasurement Categories II, III, or IV.Note Measurement Categories CAT I and CAT O (Other) are equivalent. These testand measurement circuits are not intended for direct connection to the MAINsbuilding installations of Measurement Categories CAT II, CAT III, or CAT IV.Environmental-20 °C to 55 °C6Operating temperature (IEC 60068-2-1and IEC 60068-2-2)Caution To maintain product performance and accuracy specifications when theambient temperature is between 45 and 55 °C, you must mount the chassishorizontally to a metal panel or surface using the screw holes or the panel mount kit.Measure the ambient temperature at each side of the CompactDAQ system 63.5 mm(2.5 in.) from the side and 25.4 mm (1.0 in.) from the rear cover of the system. Forfurther information about mounting configurations, go to /info and enterthe Info Code cdaqmounting.-40 °C to 85 °CStorage temperature (IEC 60068-2-1 andIEC 60068-2-2)Ingress protection IP 30Operating humidity (IEC 60068-2-56)10% to 90% RH, noncondensingStorage humidity (IEC 60068-2-56)5% to 95% RH, noncondensingPollution Degree (IEC 60664)2Maximum altitude5,000 mIndoor use only.6When operating the NI cDAQ-9184 in temperatures below 0 °C, you must use the PS-15 powersupply or another power supply rated for below 0 °C.8| | NI cDAQ-9184 SpecificationsHazardous LocationsU.S. (UL)Class I, Division 2, Groups A, B, C, D, T4;Class I, Zone 2, AEx nA IIC T4Canada (C-UL)Class I, Division 2, Groups A, B, C, D, T4;Class I, Zone 2, Ex nA IIC T4Europe (ATEX) and International (IECEx)Ex nA IIC T4 GcShock and VibrationTo meet these specifications, you must direct mount the NI cDAQ-9184 system and affix ferrules to the ends of the terminal lines.Operational shock30 g peak, half-sine, 11 ms pulse (Tested inaccordance with IEC 60068-2-27. Test profiledeveloped in accordance withMIL-PRF-28800F.)Random vibrationOperating 5 Hz to 500 Hz, 0.3 g rmsNon-operating 5 Hz to 500 Hz, 2.4 g rms (Tested in accordancewith IEC 60068-2-64. Non-operating testprofile exceeds the requirements ofMIL PRF-28800F, Class 3.)Safety and Hazardous Locations StandardsThis product is designed to meet the requirements of the following electrical equipment safety standards for measurement, control, and laboratory use:•IEC 61010-1, EN 61010-1•UL 61010-1, CSA C22.2 No. 61010-1•EN 60079-0:2012, EN 60079-15:2010•IEC 60079-0: Ed 6, IEC 60079-15; Ed 4•UL 60079-0; Ed 6, UL 60079-15; Ed 4•CSA 60079-0:2011, CSA 60079-15:2012Note For UL and other safety certifications, refer to the product label or the OnlineProduct Certification section.NI cDAQ-9184 Specifications| © National Instruments| 9Electromagnetic CompatibilityThis product meets the requirements of the following EMC standards for electrical equipment for measurement, control, and laboratory use:•EN 61326-1 (IEC 61326-1): Class A emissions; Basic immunity•EN 55011 (CISPR 11): Group 1, Class A emissions•EN 55022 (CISPR 22): Class A emissions•EN 55024 (CISPR 24): Immunity•AS/NZS CISPR 11: Group 1, Class A emissions•AS/NZS CISPR 22: Class A emissions•FCC 47 CFR Part 15B: Class A emissions•ICES-001: Class A emissionsNote In the United States (per FCC 47 CFR), Class A equipment is intended foruse in commercial, light-industrial, and heavy-industrial locations. In Europe,Canada, Australia and New Zealand (per CISPR 11) Class A equipment is intendedfor use only in heavy-industrial locations.Note Group 1 equipment (per CISPR 11) is any industrial, scientific, or medicalequipment that does not intentionally generate radio frequency energy for thetreatment of material or inspection/analysis purposes.Note For EMC declarations and certifications, and additional information, refer tothe Online Product Certification section.CE ComplianceThis product meets the essential requirements of applicable European Directives, as follows:•2014/35/EU; Low-V oltage Directive (safety)•2014/30/EU; Electromagnetic Compatibility Directive (EMC)•2014/34/EU; Potentially Explosive Atmospheres (ATEX)Online Product CertificationRefer to the product Declaration of Conformity (DoC) for additional regulatory compliance information. To obtain product certifications and the DoC for this product, visit / certification, search by model number or product line, and click the appropriate link in the Certification column.10| | NI cDAQ-9184 SpecificationsEnvironmental ManagementNI is committed to designing and manufacturing products in an environmentally responsible manner. NI recognizes that eliminating certain hazardous substances from our products is beneficial to the environment and to NI customers.For additional environmental information, refer to the Minimize Our Environmental Impact web page at /environment. This page contains the environmental regulations and directives with which NI complies, as well as other environmental information not included in this document.Waste Electrical and Electronic Equipment (WEEE) EU Customers At the end of the product life cycle, all NI products must bedisposed of according to local laws and regulations. For more information abouthow to recycle NI products in your region, visit /environment/weee.电子信息产品污染控制管理办法(中国RoHS)中国客户National Instruments符合中国电子信息产品中限制使用某些有害物质指令(RoHS)。

LINEAR TECHNOLOGY LTC4257 说明书

1234257fbSYMBOL PARAMETERCONDITIONSMIN TYPMAX UNITS The ● denotes the specifications which apply over the full operatingtemperature range, otherwise specifications are at T A = 25°C. (Note 3)Note 1: Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.Note 2: All voltages are with respect to GND pin.Note 3: The LTC4257 operates with a negative supply voltage in the range of –1.5V to –57V. To avoid confusion, voltages in this data sheet are always referred to in terms of absolute magnitude. Terms such as “maximum negative voltage” refer to the largest negative voltage and a “rising negative voltage” refers to a voltage that is becoming more negative.Note 4: The LTC4257 is designed to work with two polarity protection diodes between the PSE and PD. Parameter ranges specified in the Electrical Characteristics are with respect to LTC4257 pins and aredesigned to meet IEEE 802.3af specifications when these diode drops are included. See Applications Information.Note 5: Signature resistance is measured via the 2-point ∆V/∆I method as defined by IEEE 802.3af. The LTC4257 signature resistance is offset from 25k to account for diode resistance. With two series diodes, the total PD resistance will be between 23.75k and 26.25k and meet IEEE 802.3af specifications. The minimum probe voltages measured at the LTC4257pins are –1.5V and –2.5V. The maximum probe voltages are –8.5V and –9.5V.Note 6: The LTC4257 includes hysteresis in the UVLO voltages to preclude any start-up oscillation. Per IEEE 802.3af requirements, the LTC4257 willpower up from a voltage source with 20Ω series resistance on the first trial.Note 7: I IN_CLASS does not include classification current programmed at Pin 2. Total supply current in classification mode will be I IN_CLASS + I CLASS (see Note 8).Note 8: I CLASS is the measured current flowing through R CLASS .∆I CLASS accuracy is with respect to the ideal current defined as I CLASS = 1.237/R CLASS . The current accuracy specification does notinclude variations in R CLASS resistance. The total classification current for a PD also includes the IC quiescent current (I IN_CLASS ). See Applications Information.Note 9: For the DD package, this parameter is assured by design and wafer level testing.Note 10: I OUT_LEAK includes current drawn at the V OUT pin by the power good status circuit. This current is compensated for in the 25k Ω signature resistance and does not affect PD operation.Note 11: The LTC4257 includes smart thermal protection. In the event of an overtemperature condition, the LTC4257 will reduce the input current limit by 50% to reduce the power dissipation in the package. If the part continues heating and reaches the shutdown temperature, the current is reduced to zero until the part cools below the overtemperature limit. The LTC4257 is also protected against thermal damage from incorrect classification probing by the PSE. If the LTC4257 exceeds theovertemperature trip point, the classification load current is disabled.ELECTRICAL CHARACTERISTICSR SIGNATURE Signature Resistance–1.5V ≤ V IN ≤ –9.5V, V OUT Tied to GND,●23.2526.00k ΩIEEE 802.3af 2-Point Measurement (Notes 4, 5)V PG_OUT Power Good Output Low Voltage I = 1mA, V IN = –48V, PWRGD Referenced to V IN ●0.5V Power Good Trip PointV IN = –48V, Voltage Between V IN and V OUT (Note 9)V PG_THRES_FALL V OUT Falling ● 1.3 1.5 1.7V V PG_THRES_RISE V OUT Rising● 2.7 3.0 3.3V I PG_LEAK Power Good Leakage V IN = 0V, PWRGD FET Off, V PWRGD = 57V ●1µA R ON On-Resistance I = 300mA, V IN = –48V, Measured from V IN to V OUT 1.01.6Ω(Note 9)● 2.0ΩI OUT_LEAK V OUT Leakage V IN = 0V, Power MOSFET Off, V OUT = 57V (Note 10)●150µA I LIMIT Input Current LimitV IN = –48V, V OUT = –43V (Note 11)●300350400mA I LIMIT_WARM Overtemperature Input Current Limit (Note 11)188mA T OVERTEMP Overtemperature Trip Temperature (Note 11)120°C T SHUTDOWNThermal Shutdown Trip Temperature (Note 11)140°C456789101112134257fbAPPLICATIO S I FOR ATIOW UUU However, if the standard diode bridge is replaced with a Schottky bridge, the transition points between modes will be affected. The application circuit (Figure 11) shows a technique for using Schottky diodes while maintaining proper threshold points to meet IEEE 802.3af compliance.Auxiliary Power SourceIn some applications, it may be desirable to power the PD from an auxiliary power source such as a wall transformer.The auxiliary power can be injected into the PD at several locations and various trade-offs exist. Power can be injected at the 3.3V or 5V output of the isolated power supply with the use of a diode ORing circuit. This method accesses the internal circuits of the PD after the isolation barrier and therefore meets the 802.3af isolation safety requirements for the wall transformer jack on the PD.Power can also be injected into the PD interface portion of the LT4257. In this case, it is necessary to ensure the user cannot access the terminals of the wall transformer jack on the PD since this would compromise the 802.3af isolation safety requirements. Figure 9 demonstrates three methods of diode ORing external power into a PD. Option 1 inserts power before the LTC4257 while options 2 and 3insert power after the LTC4257.If power is inserted before the LTC4257 (option 1), it is necessary for the wall transformer to exceed the LTC4257UVLO turn-on requirement and limit the maximum voltage to 57V. This option provides input current limiting for the transformer, provides valid power good signaling and sim-plifies power priority issues. As long as the wall transformer applies power to the PD before the PSE, it will take priority and the PSE will not power up the PD because the wall power will corrupt the 25k signature. If the PSE is already pow-ering the PD, the wall transformer power will be in parallel with the PSE. In this case, priority will be given to the higher supply voltage. If the wall transformer voltage is higher, the PSE should remove line voltage since no current will bedrawn from the PSE. On the other hand, if the wall trans-former voltage is lower, the PSE will continue to supply power to the PD and the wall transformer power will not be used. Proper operation should occur in either scenario.Auxiliary power can be applied after the LTC4257 as shown in option 2. In this configuration, the wall transformer does not need to exceed the LTC4257 turn-on UVLO requirement;however, it is necessary to include diode D9 to prevent the transformer from applying power to the LTC4257. The transformer voltage requirements will be governed by the needs of the PD switcher and may exceed 57V. However,power priority issues require more intervention. If the wall transformer voltage is below the PSE voltage, then priority will be given to the PSE power. The PD will draw power from the PSE while the transformer will sit unused. This configu-ration is not a problem in a PoE system. On the other hand,if the wall transformer voltage is higher than the PSE volt-age, the PD will draw power from the transformer. In this situation, it is necessary to address the issue of power cycling that may occur if a PSE is present. The PSE will detect the PD and apply power. If the PD is being powered by the wall transformer, then the PD will not meet the minimum load requirement and the PSE will subsequently remove power. The PSE will again detect the PD and power cycling will start. With a transformer voltage above the PSE volt-age, it is necessary to install a minimum load on the output of the LTC4257 to prevent power cycling. Refer to the LTC4257-1 data sheet for an alternative implementation of option 2 which uses the Signature Disable feature.The third option also applies power after the LTC4257, while omitting diode D9. With the diode omitted, the transformer voltage is applied to the LTC4257 in addition to the load.For this reason, it is necessary to ensure that the transformer maintain the voltage between 44V and 57V to keep the LTC4257 in its normal operating range. The third option has the advantage of automatically disabling the 25k signature when the external voltage exceeds the PSE voltage.1415164257fbLoad CapacitorIEEE 802.3af requires that the PD maintain a minimum load capacitance of 5µF. It is permissible to have a much larger load capacitor and the LTC4257 can charge very large load capacitors before thermal issues become a problem. However, the load capacitor must not be too large or the PD design may violate two IEEE 802.3af requirements. The LTC4257 goes into current limit at turn-on and charges the load capacitor with between 300mA and 400mA. The IEEE specification allows this level of inrush current for up to 50ms. Therefore, it is necessary that the PD complete charging of the capacitor within the 50ms time limit. With a maximum input voltage of –57V, these conditions limit the size of the load capacitor to 250µF.Very small output capacitors (≤10µF) will charge very quickly in current limit. The rapidly changing voltage at the output may reduce the current limit temporarily,causing the capacitor to charge at a somewhat reduced rate. Conversely, charging very large capacitors may cause the current limit to increase slightly. In either case,once the output voltage reaches its final value, the input current limit will be restored to its nominal value.If the load capacitor is too large there can be an additional problem with inadvertent power shutdown by the PSE.Consider the following scenario. If the PSE is running atAPPLICATIO S I FOR ATIOW UUU –57V (maximum allowed) and the PD has been detected and powered up, the load capacitor will be charged to nearly –57V. If for some reason the PSE voltage suddenly is reduced to –44V (minimum allowed), the input diodes will reverse bias and PD power will be supplied solely by the load capacitor. D epending on the size of the load capacitor and the DC load of the PD, the PD will not draw any power from the PSE for a period of time. If this period of time exceeds the IEEE 802.3af 300ms disconnect delay, the PSE may remove power from the PD. For this reason, it is necessary to evaluate the load capacitance and load current to ensure that inadvertent shutdown cannot occur.Maintain Power SignatureIn an IEEE 802.3af system, the PSE uses the maintain power signature (MPS) to determine if a PD continues to require power. The MPS requires the PD to periodically draw at least 10mA and also have an AC impedance less than 26.25k Ω in parallel with 0.05µF. The PD application circuits shown in this data sheet meet the requirements necessary to maintain power. If either the DC current is less than 10mA or the AC impedance is above 26.25k Ω,the PSE might disconnect power. The DC current must be less than 5mA and the AC impedance must be above 2M Ωto guarantee power will be removed.174257fbAPPLICATIO S I FOR ATIOW UUU LayoutThe LTC4257 is relativity immune to layout problems.Excessive parasitic capacitance on the R CLASS pin should be avoided. If using the DD package, include an electrically isolated heat sink to which the exposed pad on the bottom of the package can be soldered. For optimal thermal performance, make the heat sink as large as possible.Voltages in a PD can be as large as –57V, so high voltage layout techniques should be employed.The load capacitor connected between Pins 5 and 8 of the LTC4257 can store significant energy when fully charged.The design of a PD must ensure that this energy is not inadvertently dissipated in the LTC4257. The polarity-protection diode(s) prevent an accidental short on thecable from causing damage. However, if the V IN pin is shorted to the GND pin inside the PD while the load capacitor is charged, current will flow through the para-sitic body diode of the internal MOSFET and may cause permanent damage to the LTC4257.Input Surge SuppressionThe LTC4257 is specified to operate with an absolute maximum voltage of –100V and is designed to tolerate brief overvoltage events. However, the pins that interface to the outside world (primarily V IN and GND) can routinely see peak voltages in excess of 10kV. To protect the LTC4257, it is highly recommended that a transient volt-age suppressor be installed between the bridge and the LTC4257 (D3 in Figure 2).1819Information furnished by Linear Technology Corporation is believed to be accurate and reliable.However, no responsibility is assumed for its use. Linear Technology Corporation makes no represen-tation that the interconnection of its circuits as described herein will not infringe on existing patent rights.201630 McCarthy Blvd., Milpitas, CA 95035-7417(408) 432-1900 ● FAX: (408) 434-0507 ● © LINEAR TECHNOLOGY CORPORA TION 2003LT 1205 REV B • PRINTED IN USA。

三极管参数