B8049NL;中文规格书,Datasheet资料

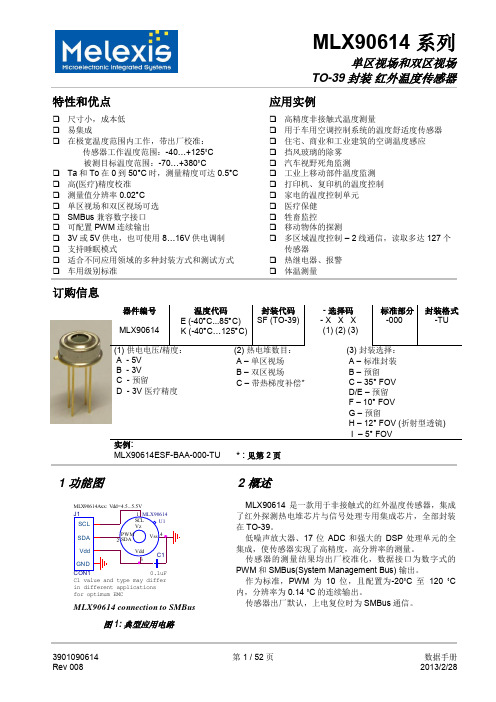

Datasheet MLX90614 中文 数据手册 rev008

3901090614 Rev 008

第 2 / 52 页

数据手册 2013/2/28

应用实例

高精度非接触式温度测量 用于车用空调控制系统的温度舒适度传感器 住宅、商业和工业建筑的空调温度感应 挡风玻璃的除雾 汽车视野死角监测 工业上移动部件温度监测 打印机、复印机的温度控制 家电的温度控制单元 医疗保健 牲畜监控 移动物体的探测 多区域温度控制 – 2 线通信,读取多达 127 个

PWM 引脚也可配置为热继电器(输入是 To),这样可以实现简单且性价比高的恒温控制器或温度报警(冰 点/沸点)应用,其中的温度临界值是用户可编程的。在 SMBus 系统里,这个功能可以作为处理器的中断信号, 以此触发读取主线上从动器的值,并确定精度条件。

传感器有两种供电电压选择:5V 或 3V(电池供电)。其中,5V 也可简便的从更高供电电压(例如 8 至 16V)上通过外接元件调制。(具体请参考“应用信息”)

第 1 / 52 页

数据手册 2013/2/28

LX90614 系列

单区视场和双区视场 TO-39 封装 红外温度传感器

概述(续)

MLX90614 集成了由 Melexis 研发生产的两款芯片: 红外热电堆探测器 MLX81101 专用信号处理芯片 MLX90302,专用于处理红外传感器的输出信号

传感器的测量结果均出厂校准化,数据接口为数字式的 PWM 和 SMBus(System Management Bus) 输出。

作为标准,PWM 为 10 位,且配置为-20˚C 至 120 ˚C 内,分辨率为 0.14 ˚C 的连续输出。

W947D6HBHX5E;W947D2HBJX5E;中文规格书,Datasheet资料

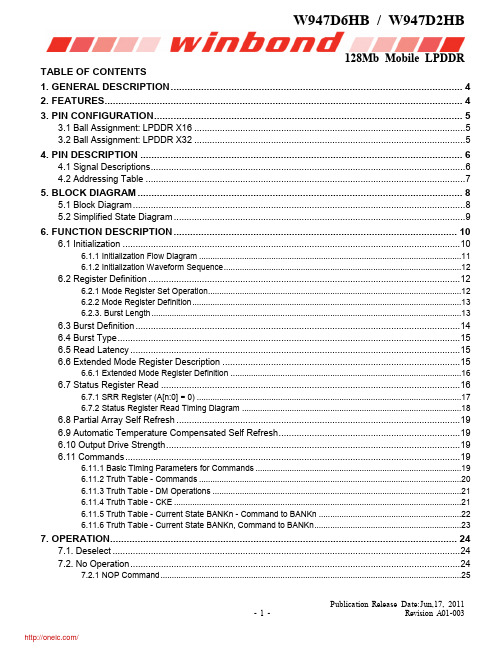

TABLE OF CONTENTS1. GENERAL DESCRIPTION (4)2. FEATURES (4)3. PIN CONFIGURATION (5)3.1 Ball Assignment: LPDDR X16 (5)3.2 Ball Assignment: LPDDR X32 (5)4. PIN DESCRIPTION (6)4.1 Signal Descriptions (6)4.2 Addressing Table (7)5. BLOCK DIAGRAM (8)5.1 Block Diagram (8)5.2 Simplified State Diagram (9)6. FUNCTION DESCRIPTION (10)6.1 Initialization (10)6.1.1 Initialization Flow Diagram (11)6.1.2 Initialization Waveform Sequence (12)6.2 Register Definition (12)6.2.1 Mode Register Set Operation (12)6.2.2 Mode Register Definition (13)6.2.3. Burst Length (13)6.3 Burst Definition (14)6.4 Burst Type (15)6.5 Read Latency (15)6.6 Extended Mode Register Description (15)6.6.1 Extended Mode Register Definition (16)6.7 Status Register Read (16)6.7.1 SRR Register (A[n:0] = 0) (17)6.7.2 Status Register Read Timing Diagram (18)6.8 Partial Array Self Refresh (19)6.9 Automatic Temperature Compensated Self Refresh (19)6.10 Output Drive Strength (19)6.11 Commands (19)6.11.1 Basic Timing Parameters for Commands (19)6.11.2 Truth Table - Commands (20)6.11.3 Truth Table - DM Operations (21)6.11.4 Truth Table - CKE (21)6.11.5 Truth Table - Current State BANKn - Command to BANKn (22)6.11.6 Truth Table - Current State BANKn, Command to BANKn (23)7. OPERATION (24)7.1. Deselect (24)7.2. No Operation (24)7.2.1 NOP Command (25)7.3 Mode Register Set (25)7.3.1 Mode Register Set Command (25)7.3.2 Mode Register Set Command Timing (26)7.4. Active (26)7.4.1 Active Command (26)7.4.2 Bank Activation Command Cycle (27)7.5. Read (27)7.5.1 Read Command (28)7.5.2 Basic Read Timing Parameters (28)7.5.3 Read Burst Showing CAS Latency (29)7.5.4 Read to Read (29)7.5.5 Consecutive Read Bursts (30)7.5.6 Non-Consecutive Read Bursts (30)7.5.7 Random Read Bursts (31)7.5.8 Read Burst Terminate (31)7.5.9 Read to Write (32)7.5.10 Read to Pre-charge (32)7.5.11 Burst Terminate of Read (33)7.6 Write (33)7.6.1 Write Command (34)7.6.2 Basic Write Timing Parameters (34)7.6.3 Write Burst (min. and max. tDQSS) (35)7.6.4 Write to Write (35)7.6.5 Concatenated Write Bursts (36)7.6.6 Non-Consecutive Write Bursts (36)7.6.7 Random Write Cycles (37)7.6.8 Write to Read (37)7.6.9 Non-Interrupting Write to Read (37)7.6.10 Interrupting Write to Read (38)7.6.11 Write to Precharge (38)7.6.12 Non-Interrupting Write to Precharge (38)7.6.13 Interrupting Write to Precharge (39)7.7 Precharge (39)7.7.1 Precharge Command (40)7.8 Auto Precharge (40)7.9 Refresh Requirements (40)7.10 Auto Refresh (40)7.10.1 Auto Refresh Command (41)7.11 Self Referesh (41)7.11.1 Self Refresh Command (42)7.11.2 Auto Refresh Cycles Back-to-Back (42)7.11.3 Self Refresh Entry and Exit (43)7.12 Power Down (43)7.12.1 Power-Down Entry and Exit (43)7.13 Deep Power Down (44)128Mb Mobile LPDDR7.13.1 Deep Power-Down Entry and Exit (44)7.14 Clock Stop (45)7.14.1 Clock Stop Mode Entry and Exit (45)8. ELECTRICAL CHARACTERISTIC (46)8.1 Absolute Maximum Ratings (46)8.2 Input/Output Capacitance (46)8.3 Electrical Characteristics and AC/DC Operating Conditions (47)8.3.1 Electrical Characteristics and AC/DC Operating Conditions (47)8.4 IDD Specification Parameters and Test Conditions (48)8.4.1 IDD Specification Parameters and Test Conditions (48)8.5 AC Timings (51)8.5.1 CAS Latency Definition (With CL=3) (54)8.5.2 Output Slew Rate Characteristics (55)8.5.3 AC Overshoot/Undershoot Specification (55)8.5.4 AC Overshoot and Undershoot Definition (55)9. PACKAGE DIMENSIONS (56)9.1: LPDDR X 16 (56)9.2: LPDDR X 32 (57)10. ORDERING INFORMATION (58)11. REVISION HISTORY (59)1. GENERAL DESCRIPTIONW947D6HB / W947D2HB is a high-speed Low Power double data rate synchronous dynamic random access memory (LPDDR SDRAM), An access to the LPDDR SDRAM is burst oriented. Consecutive memory location in one page can be accessed at a burst length of 2, 4, 8 and 16 when a bank and row is selected by an ACTIVE command. Column addresses are automatically generated by the LPDDR SDRAM internal counter in burst operation. Random column read is also possible by providing its address at each clock cycle. The multiple bank nature enables interleaving among internal banks to hide the pre-charging time. By setting programmable Mode Registers, the system can change burst length, latency cycle, interleave or sequential burst to maximize its performance. The device supports special low power functions such as Partial Array Self Refresh (PASR) and Automatic Temperature Compensated Self Refresh (ATCSR).2. FEATURESVDD = 1.7~1.95VVDDQ = 1.7~1.95V;Data width: x16 / x32Clock rate: 200MHz(-5),166MHz(-6),133MHz(-75)Partial Array Self-Refresh(PASR)Auto Temperature Compensated Self-Refresh(ATCSR) Power Down ModeDeep Power Down Mode (DPD Mode)Programmable output buffer driver strengthFour internal banks for concurrent operationData mask (DM) for write dataClock Stop capability during idle periodsAuto Pre-charge option for each burst accessDouble data rate for data outputDifferential clock inputs (CK and C K)Bidirectional, data strobe (DQS)C AS Latency: 2 and 3Burst Length: 2, 4, 8 and 16Burst Type: Sequential or Interleave 64 ms Refresh periodInterface: LVCMOS compatibleSupport package:Operating Temperature Range :3. PIN CONFIGURATION3.1 Ball Assignment: LPDDR X16(Top View) Pin Configuration 3.2 Ball Assignment: LPDDR X32(Top View) Pin Configuration4. PIN DESCRIPTION 4.1 Signal Descriptions4.2 Addressing Table5. BLOCK DIAGRAM 5.1 Block Diagram5.2 Simplified State Diagram6. FUNCTION DESCRIPTION6.1 InitializationLPDDR SDRAM must be powered up and initialized in a predefined manner. Operations procedures other than those specified may result in undefined operation. If there is any interruption to the device power, the initialization routine should be followed. The steps to be followed for device initialization are listed below.The Mode Register and Extended Mode Register do not have default values. If they are not programmed during the initialization sequence, it may lead to unspecified operation. The clock stop feature is not available until the device has been properly initialized from Step 1 through 11.●Step 1: Provide power, the device core power (VDD) and the device I/O power (VDDQ) must be brought upsimultaneously to prevent device latch-up. Although not required, it is recommended that VDD and VDDQ are from the same power source. Also Assert and hold Clock Enable (CKE) to a LVCMOS logic high level ●Step 2: Once the system has established consistent device power and CKE is driven high, it is safe to applystable clock.●Step 3: There must be at least 200μs of valid clocks before any command may be given to the DRAM. During thistime NOP or DESELECT commands must be issued on the command bus.●Step 4: Issue a PRECHARGE ALL command.●Step 5: Provide NOPs or DESELECT commands for at least tRP time.●Step 6: Issue an AUTO REFRESH command followed by NOPs or DESELECT command for at least tRFC time.Issue the second AUTO REFRESH command followed by NOPs or DESELECT command for at least tRFC time. Note as part of the initialization sequence there must be two Auto Refresh commands issued.The typical flow is to issue them at Step 6, but they may also be issued between steps 10 and 11.●Step 7: Using the MRS command, program the base mode register. Set the desired operation modes.●Step 8: Provide NOPs or DESELECT commands for at least tMRD time.●Step 9: Using the MRS command, program the extended mode register for the desired operating modes. Note theorder of the base and extended mode register programmed is not important.●Step 10: Provide NOP or DESELECT commands for at least tMRD time.●Step 11: The DRAM has been properly initialized and is ready for any valid command.分销商库存信息:WINBONDW947D6HBHX5E W947D2HBJX5E。

B82793S0513N201;B82793C475N265;中文规格书,Datasheet资料

Data and signal line chokesCommon-mode chokes, ring core0.005 … 47 mH, 100 … 1200 mA, 60 °CSeries/Type:B82793C0/S0Date:July 2010¤ EPCOS AG 2010. Reproduction, publication and dissemination of this publication, enclosures hereto and the information contained therein without EPCOS’ prior express consent is prohibited.Rated voltage 42 V AC/80 V DCRated inductance 0.005 mH to 47 mH Rated current 100 mA to 1200 mA Construction■Current-compensated double choke ■Ferrite core■LCP case (UL 94 V-0), silicone potting ■Bifilar winding (B82793C0)■Sector winding (B82793S0)Features■High rated currents, reduced components height ■Qualified to AEC-Q200 (L d 4.7 mH)■Suitable for reflow soldering ■RoHS-compatibleFunction■B82793C0:Suppression of asymmetrical interference coupled in on lines,whereas data signals up to some MHz can pass unaffectedly.■B82793S0:Suppression of asymmetrical and symmetrical interference (by L stray )coupled in on lines. The high-frequency portions of the symmetrical data signal are decreased so far that EMC problems can be significantly reduced.Applications■Automotive applications, e.g. CAN bus ■Industrial applications■Types with L R ! 4.7 mH only for telecom applicationsTerminals■Base material CuSn6■Layer composition Ni, Sn ■Hot-dippedMarking■Marking on component: Manufacturer, process location (coded),winding method (coded), ordering code (short form), date of manufacture (YWWD)■Minimum data on reel: Manufacturer, ordering code,L value and tolerance, quantity, date of packing Delivery mode and packing unit■16-mm blister tape, wound on 330-mm reel ■Packing unit: 1500 pcs./reel Common-mode chokes, ring coreDimensional drawing and pin configurationLayout recommendationTaping and packing Blister tapeReelDimensions in mmDimensions in mmCommon-mode chokes, ring coreCommon-mode chokes, ring coreTechnical data and measuring conditionsRated voltage V R42 V AC (50/60 Hz) / 80 V DCRated temperature T R60 °CRated current I R Referred to 50 Hz and rated temperatureRated inductance L R Measured with Agilent 4284A, 0.1 mA, 20 °CMeasuring frequency:L R d 1 mH = 100 kHzL R! 1 mH = 10 kHzInductance is specified per winding.Inductance tolerance r30% (L R d0.47mH), –30/+50% (L R t1mH) at 20 °C Inductance decrease 'L/L 10% at DC magnetic bias with I R, 20 °CStray inductance L stray,typ Measured with Agilent 4284A, 5 mA, 20 °C, typical valuesMeasuring frequency:L R d 11 P H = 1 MHzL R! 11 P H = 100 kHzDC resistance R typ Measured at 20q C, typical values, specified per winding Solderability SnPb:(215 r3) °C, (3 r0.3) sSn96.5Ag3.0Cu0.5:(245 r5) °C, (3 r0.3) sWetting of soldering area t 95%(to IEC 60068-2-58)Resistance to soldering heat(260 r5) °C, (10 r1) s (to IEC 60068-2-58)Climatic category 40/125/56 (to IEC 60068-1)Storage conditions (packaged)–25 °C … +40 °C, d 75% RHWeight Approx. 0.25 gCharacteristics and ordering codes Sample kit available. Ordering code: B82793X001.For more information refer to chapter “Sample kits”.L R mH L stray,typ nH I R mA R typ m :V test V DC, 2 s Ordering code 0.005 40120060250B82793C0502N2010.011 50 80080250B82793C0113N2010.025 60 800110250B82793C0253N2010.0251400 800110250B82793S0253N2010.051 70 800140250B82793C0513N2010.0512300 800140250B82793S0513N2010.10 100 500180250B82793C0104N2010.47 100 700170750B82793C0474N2151.0 70 700140750B82793C0105N2652.2 120 500400750B82793C0225N2654.7 250 400550750B82793C0475N265For telecommunications203001001800750B82793C0206N2654712001003700750B82793C0476N265Common-mode chokes, ring coreInsertion loss D (typical values at |Z| = 50 :, 20 °C)asymmetrical, all branches in parallel (common mode)symmetrical (differential mode)L R = 0.005 mHL R = 0.025 mH (low L stray)L R = 0.011 mHL R = 0.025 mH (high L stray)Common-mode chokes, ring coreInsertion loss D (typical values at |Z| = 50 :, 20 °C)asymmetrical, all branches in parallel (common mode)symmetrical (differential mode)L R = 0.051 mH (low L stray) L R = 0.10 mH L R = 0.051 mH (high L stray) L R = 0.47 mHCommon-mode chokes, ring coreInsertion loss D (typical values at |Z| = 50 :, 20 °C)asymmetrical, all branches in parallel (common mode)symmetrical (differential mode)L R =1.0 mH L R = 4.7 mH L R = 2.2 mH L R = 20 mHCommon-mode chokes, ring coreInsertion loss D (typical values at |Z| = 50 :, 20 °C)asymmetrical, all branches in parallel (common mode)symmetrical (differential mode)L R = 47 mH Current derating I op/I R versus ambient temperatureCommon-mode chokes, ring coreRecommended reflow soldering curvePb containing solder material (based on CECC 00802 edition 2)Pb-free solder material (based on JEDEC J-STD 020C)Time from 25 °C to T 4: max 300 s Maximal numbers of reflow cycles: 3T 1°C T 2°C T 3°C T 4°C t 1s t 2s t 3s150200217250< 110< 90< 40 @ T 4 –5 °CCommon-mode chokes, ring core分销商库存信息:EPCOSB82793S0513N201B82793C475N265。

IXYB82N120C3H1;中文规格书,Datasheet资料

CES I C110= 82A V CE(sat) ≤ 3.2V t fi(typ)= 93nsHigh-Speed IGBTfor 20-50 kHz SwitchingFeaturesz Optimized for Low Switching Losses zSquare RBSOA zAnti-Parallel Ultra Fast Diode zPositive Thermal Coefficient of Vce(sat)zAvalanche Rated zHigh Current Handling Capability zInternational Standard PackageAdvantagesz High Power DensityzLow Gate Drive RequirementApplicationsz High Frequency Power Inverters z UPSz Motor Drives z SMPSz PFC Circuits z Battery Chargers z Welding Machines zLamp BallastsSymbol Test Conditions Characteristic Values (T J = 25°C, Unless Otherwise Specified) Min. Typ. Max.BV CES I C = 250μA, V GE = 0V 1200 VV GE(th)I C= 250μA, V CE = V GE3.05.0VI CES V CE = V CES , V GE = 0V50μA T J = 125°C 3 mA I GES V CE = 0V, V GE = ±20V±100 nAV CE(sat)I C = 82A, V GE = 15V, Note 12.753.20 V T J = 125°C3.50 VSymbol Test ConditionsMaximum Ratings V CES T J = 25°C to 150°C1200V V CGR T J = 25°C to 150°C, R GE = 1M Ω 1200V V GES Continuous ±20V V GEM Transient ±30V I C25T C = 25°C 160A I C110T C = 110°C 82A I F110T C = 110°C 42A I CM T C= 25°C, 1ms 320AI A T C = 25°C 41 A E AST C = 25°C 800 mJSSOA V GE = 15V, T VJ = 125°C, RG = 2Ω I CM = 164A (RBSOA) Clamped Inductive Load @V CE ≤ V CES P C T C = 25°C1040W T J -55 ... +150°C T JM 150°C T stg -55 ... +150°CT LMaximum Lead Temperature for Soldering 300°CT SOLD 1.6 mm (0.062in.) from Case for 10s 260°CF C Mounting Force 30..120 / 6.7..27N/lb.Weight10g1200V XPT TM IGBT GenX3TM w/ DiodeG = Gate C = Collector E = EmitterTab = CollectorEPLUS264TMG CIXYS Reserves the Right to Change Limits, Test Conditions, and Dimensions.Symbol Test Conditions (T J = 25°C Unless Otherwise Specified)fs I C = 60A, V CE = 10V, Note 1 30 50C ie sC oes V CE = 25V, V GE C resQ g(on)Q ge I C = 82A, V GE = 15V, V Q gc d(on)Pin 1 = Gate Pin 2,4 = Emitter Pin 3 = CollectorNotes:1. Pulse test, t ≤ 300μs, duty cycle, d ≤ 2%.2. Switching times & energy losses may increase for higher V CE (clamp), T J or R G .Reverse Diode (FRED)Symbol Test ConditionsCharacteristic ValuesFig. 1. Output Characteristics @ T 6080100120140160I C - A m p e r e sIXYS Reserves the Right to Change Limits, Test Conditions, and Dimensions.Fig. 7. Transconductance304050607080g f s - S i e m e n sFig. 12. Inductive Switching Energy Loss vs.Gate Resistance345678E o f f - M i l l i J o u l e sE off E on - - - - T J = 125ºC , V GE = 15V V CE = 600VIXYS Reserves the Right to Change Limits, Test Conditions, and Dimensions.Fig. 18. Inductive Turn-on Switching Times vs.Gate Resistance6080100120140160r i - N a n o s e c o n d st r i t d(on) - - - -T J = 125ºC, V GE = 15V V CE = 600VI CFig. 21.Fig. 22.Fig. 23.Fig. 24.Fig. 25.Fig. 26. transient thermal impedance分销商库存信息: IXYSIXYB82N120C3H1。

FDS8949;中文规格书,Datasheet资料

tmOctober 2006FDS8949 Dual N-Channel Logic Level PowerTrench®MOSFET FDS8949Dual N-Channel Logic Level PowerTrench® MOSFET40V, 6A, 29mΩFeaturesMax r DS(on)= 29mΩ at V GS = 10VMax r DS(on)= 36mΩ at V GS = 4.5VLow gate chargeHigh performance trench technology for extremely lowr DS(on)High power and current handling capabilityRoHS compliantGeneral DescriptionThese N-Channel Logic Level MOSFETs are producedusing Fairchild Semiconductor’s advancedPowerTrench® process that has been especially tailoredto minimize the on-state resistance and yet maintainsuperior switching performance.These devices are well suited for low voltage andbattery powered applications where low in-line powerloss and fast switching are required.ApplicationsInverterPower suppliersMOSFET Maximum Ratings TA = 25°C unless otherwise notedThermal CharacteristicsPackage Marking and Ordering InformationSymbol Parameter Ratings UnitsV DS Drain to Source Voltage40VV GS Gate to Source Voltage±20VI DDrain Current -Continuous (Note 1a)6A -Pulsed 20E AS Drain-Source Avalanche Energy (Note 3)26mJP DPower Dissipation for Dual Operation 2W Power Dissipation for Single Operation (Note 1a)(Note 1b)1.60.9T J, T STG Operating and Storage Junction Temperature Range-55 to 150°CRθJA Thermal Resistance-Single operation, Junction to Ambient (Note 1a)81°C/WRθJA Thermal Resistance-Single operation, Junction to Ambient (Note 1b)135RθJC Thermal Resistance, Junction to Case (Note 1)40Device Marking Device Reel Size Tape Width Quantity FDS8949FDS894913’’12mm2500 unitsPin 1SO-8D1D1D2D2S2S1G1G2FDS8949 Dual N-Channel Logic Level PowerTrench ® MOSFETElectrical Characteristics TJ = 25°C unless otherwise notedSymbolParameterTest ConditionsMinTypMaxUnitsOff Characteristics BV DSS Drain to Source Breakdown Voltage I D = 250µA, V GS = 0V 40 V ∆BV DSS ∆T J Breakdown Voltage Temperature CoefficientI D = 250µA, referenced to 25°C33mV/°C I DSS Zero Gate Voltage Drain Current V DS = 32V, V GS = 0V1µA T J = 55°C10µA I GSSGate to Source Leakage CurrentV GS = ±20V,V DS = 0V±100nAOn Characteristics V GS(th)Gate to Source Threshold Voltage V GS = V DS , I D = 250µA 1 1.93V ∆V GS(th) ∆T J Gate to Source Threshold Voltage Temperature Coefficient I D = 250µA, referenced to 25°C -4.6 mV/°Cr DS(on)Drain to Source On Resistance V GS = 10V, I D = 6A2129m ΩV GS = 4.5V, I D = 4.5A 2636V GS = 10V, I D = 6A,T J = 125°C 2943g FSForward TransconductanceV DS = 10V,I D = 6A22S (Note 2)Dynamic CharacteristicsC iss Input Capacitance V DS = 20V, V GS = 0V,f = 1MHz 715955pF C oss Output Capacitance105140pF C rss Reverse Transfer Capacitance6090pF R gGate Resistancef = 1MHz1.1ΩSwitching Characteristicst d(on)Turn-On Delay Time V DD = 20V, I D = 1A V GS = 10V, R GEN = 6Ω918ns t r Rise Time510ns t d(off)Turn-Off Delay Time 2337ns t f Fall Time36ns Q g Total Gate ChargeV DS = 20V, I D = 6A,V GS = 5V 7.711nC Q gs Gate to Source Gate Charge 2.4nC Q gdGate to Drain “Miller”Charge2.8nCDrain-Source Diode Characteristics V SD Source to Drain Diode Forward Voltage V GS = 0V, I S = 6A (note 2) 0.8 1.2V t rr Reverse Recovery Time (note 3)I F = 6A, d iF /d t = 100A/µs1726ns Q rrReverse Recovery Charge711nCand Maximum RatingsNotes:1: R θJA is the sum of the junction-to-case and case-to- ambient thermal resistance where the case thermal reference is defined as the solder mounting surface of the drain pins. R θJC is guaranteed by design while R θJA is determined by the user’s board design.2: Pulse Test: Pulse Width < 300 us, Duty Cycle < 2.0%.3: Starting T J = 25°C, L = 1mH, I AS = 7.3A, V DD = 40V, V GS = 10V.Scale 1:1 on letter size papera) 81°C/W when mounted on a 1in 2 pad of 2 oz copperb) 135°C/W when mounted on a minimum pad .MOSFETMOSFETMOSFETFDS8949 Rev. 6FDS8949 Dual N-Channel Logic Level PowerTrench ® MOSFETTRADEMARKSThe following are registered and unregistered trademarks Fairchild Semiconductor owns or is authorized to use and is not intended to be an exhaustive list of all such trademarks.DISCLAIMERFAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS. THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD’S WORLDWIDE TERMS AND CONDITIONS, SPECIFICALLY THE WARRANTY THEREIN, WHICH COVERS THESE PRODUCTS.LIFE SUPPORT POLICYFAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.As used herein:1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, or (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in significant injury to the user.2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.PRODUCT STATUS DEFINITIONS Definition of TermsACEx™ActiveArray™Bottomless™Build it Now™CoolFET™CROSSVOLT ™DOME™EcoSPARK™E 2CMOS™EnSigna™FACT™FAST ®FASTr™FPS™FRFET™FACT Quiet Series™ GlobalOptoisolator™GTO™HiSeC™I 2C™i-Lo ™ImpliedDisconnect ™IntelliMAX™ISOPLANAR™LittleFET™MICROCOUPLER™MicroFET™MicroPak™MICROWIRE™MSX ™MSXPro ™OCX ™OCXPro ™OPTOLOGIC ®OPTOPLANAR™PACMAN™POP™Power247™PowerEdge™PowerSaver™PowerTrench ®QFET ®QS™QT Optoelectronics™Quiet Series™RapidConfigure ™RapidConnect ™µSerDes ™ScalarPump ™SILENT SWITCHER ®SMART START™SPM™Stealth™SuperFET™SuperSOT™-3SuperSOT™-6SuperSOT™-8SyncFET™TCM™TinyBoost™TinyBuck™TinyPWM™TinyPower™TinyLogic ®TINYOPTO™TruTranslation™UHC™UniFET™UltraFET ®VCX™Wire™Across the board. Around the world.™The Power Franchise ®Programmable Active Droop™Datasheet Identification Product Status DefinitionAdvance InformationFormative or In Design This datasheet contains the design specifications for product development. Specifications may change in any manner without notice.PreliminaryFirst ProductionThis datasheet contains preliminary data, andsupplementary data will be published at a later date.Fairchild Semiconductor reserves the right to make changes at any time without notice in order to improve design.No Identification Needed Full ProductionThis datasheet contains final specifications. Fairchild Semiconductor reserves the right to make changes at any time without notice in order to improve design. Obsolete Not In ProductionThis datasheet contains specifications on a product that has been discontinued by Fairchild semiconductor.The datasheet is printed for reference information only.Rev. I20分销商库存信息: FAIRCHILDFDS8949。

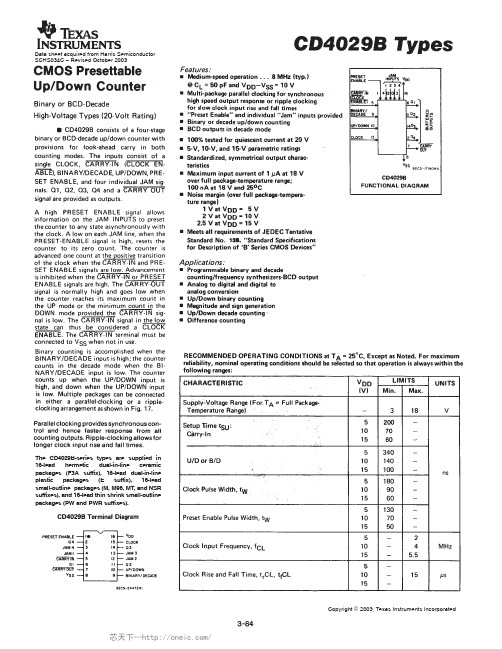

CD4029BM,CD4029BM96,CD4029BM96E4,CD4029BM96G4,CD4029BPWRE4,CD4029BPWRG4, 规格书,Datasheet 资料

The CD4029B-series types are supplied in16-lead hermetic dual-in-line ceramicpackages (F3A suffix), 16-lead dual-in-lineplastic packages (E suffix), 16-leadsmall-outline packages (M, M96, MT, and NSRsuffixes), and 16-lead thin shrink small-outlinepackages (PW and PWR suffixes).Copyright © 2003, Texas Instruments IncorporatedAddendum-Page 1PACKAGING INFORMATIONOrderable Device Status(1)Package Type PackageDrawingPins Package QtyEco Plan(2)Lead/Ball Finish MSL Peak Temp (3)Samples (Requires Login)8101602EA ACTIVE CDIP J 161TBDCall TICall TICD4029BE ACTIVE PDIP N 1625Pb-Free (RoHS)CU NIPDAU N / A for Pkg Type CD4029BEE4ACTIVE PDIP N 1625Pb-Free (RoHS)CU NIPDAU N / A for Pkg TypeCD4029BF ACTIVE CDIP J 161TBD A42N / A for Pkg Type CD4029BF3A ACTIVE CDIP J 161TBD A42N / A for Pkg TypeCD4029BM ACTIVE SOIC D 1640Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM CD4029BM96ACTIVE SOIC D 162500Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM CD4029BM96E4ACTIVE SOIC D 162500Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM CD4029BM96G4ACTIVE SOIC D 162500Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM CD4029BME4ACTIVE SOIC D 1640Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM CD4029BMG4ACTIVE SOIC D 1640Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM CD4029BMT ACTIVE SOIC D 16250Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM CD4029BMTE4ACTIVE SOIC D 16250Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM CD4029BMTG4ACTIVE SOIC D 16250Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM CD4029BNSR ACTIVE SO NS 162000Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM CD4029BNSRE4ACTIVE SO NS 162000Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM CD4029BNSRG4ACTIVE SO NS 162000Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM CD4029BPWR ACTIVE TSSOP PW 162000Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM CD4029BPWRE4ACTIVETSSOPPW162000Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM芯天下--/Addendum-Page 2Orderable Device Status(1)Package Type PackageDrawingPins Package QtyEco Plan(2)Lead/Ball FinishMSL Peak Temp(3)Samples (Requires Login)CD4029BPWRG4ACTIVETSSOPPW162000Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM(1)The marketing status values are defined as follows:ACTIVE: Product device recommended for new designs.LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.PREVIEW: Device has been announced but is not in production. Samples may or may not be available.OBSOLETE: TI has discontinued the production of the device.(2)Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check /productcontent for the latest availability information and additional product content details.TBD: The Pb-Free/Green conversion plan has not been defined.Pb-Free (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.Pb-Free (RoHS Exempt): This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)(3)MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals.TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.OTHER QUALIFIED VERSIONS OF CD4029B, CD4029B-MIL :•Catalog: CD4029B •Military: CD4029B-MILNOTE: Qualified Version Definitions:•Catalog - TI's standard catalog product芯天下--/•Military - QML certified for Military and Defense ApplicationsAddendum-Page 3芯天下--/TAPE AND REELINFORMATION*Alldimensions are nominalDevicePackage Type Package Drawing Pins SPQReel Diameter (mm)Reel Width W1(mm)A0(mm)B0(mm)K0(mm)P1(mm)W (mm)Pin1Quadrant CD4029BM96SOIC D 162500330.016.4 6.510.3 2.18.016.0Q1CD4029BNSR SO NS 162000330.016.48.210.5 2.512.016.0Q1CD4029BPWRTSSOPPW162000330.012.46.95.61.68.012.0Q1PACKAGE MATERIALS INFORMATION14-Jul-2012Pack Materials-Page 1*All dimensionsare nominalDevice Package TypePackage DrawingPins SPQ Length (mm)Width (mm)Height (mm)CD4029BM96SOIC D 162500333.2345.928.6CD4029BNSR SO NS 162000367.0367.038.0CD4029BPWRTSSOPPW162000367.0367.035.0PACKAGE MATERIALS INFORMATION14-Jul-2012Pack Materials-Page 2IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries(TI)reserve the right to make corrections,enhancements,improvements and other changes to its semiconductor products and services per JESD46C and to discontinue any product or service per JESD48B.Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.All semiconductor products(also referred to herein as“components”)are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its components to the specifications applicable at the time of sale,in accordance with the warranty in TI’s terms and conditions of sale of semiconductor products.Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty.Except where mandated by applicable law,testing of all parameters of each component is not necessarily performed.TI assumes no liability for applications assistance or the design of Buyers’products.Buyers are responsible for their products and applications using TI components.To minimize the risks associated with Buyers’products and applications,Buyers should provide adequate design and operating safeguards.TI does not warrant or represent that any license,either express or implied,is granted under any patent right,copyright,mask work right,or other intellectual property right relating to any combination,machine,or process in which TI components or services are rmation published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement e of such information may require a license from a third party under the patents or other intellectual property of the third party,or a license from TI under the patents or other intellectual property of TI.Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties,conditions,limitations,and notices.TI is not responsible or liable for such altered rmation of third parties may be subject to additional restrictions.Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.Buyer acknowledges and agrees that it is solely responsible for compliance with all legal,regulatory and safety-related requirements concerning its products,and any use of TI components in its applications,notwithstanding any applications-related information or support that may be provided by TI.Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures,monitor failures and their consequences,lessen the likelihood of failures that might cause harm and take appropriate remedial actions.Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.In some cases,TI components may be promoted specifically to facilitate safety-related applications.With such components,TI’s goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements.Nonetheless,such components are subject to these terms.No TI components are authorized for use in FDA Class III(or similar life-critical medical equipment)unless authorized officers of the parties have executed a special agreement specifically governing such use.Only those TI components which TI has specifically designated as military grade or“enhanced plastic”are designed and intended for use in military/aerospace applications or environments.Buyer acknowledges and agrees that any military or aerospace use of TI components which have not been so designated is solely at the Buyer's risk,and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.TI has specifically designated certain components which meet ISO/TS16949requirements,mainly for automotive ponents which have not been so designated are neither designed nor intended for automotive use;and TI will not be responsible for any failure of such components to meet such requirements.Products ApplicationsAudio /audio Automotive and Transportation /automotiveAmplifiers Communications and Telecom /communicationsData Converters Computers and Peripherals /computersDLP®Products Consumer Electronics /consumer-appsDSP Energy and Lighting /energyClocks and Timers /clocks Industrial /industrialInterface Medical /medicalLogic Security /securityPower Mgmt Space,Avionics and Defense /space-avionics-defense Microcontrollers Video and Imaging /videoRFID OMAP Mobile Processors /omap TI E2E Community Wireless Connectivity /wirelessconnectivityMailing Address:Texas Instruments,Post Office Box655303,Dallas,Texas75265Copyright©2012,Texas Instruments Incorporated。

BD809G;BD810G;BD810;中文规格书,Datasheet资料

BD809 (NPN), BD810 (PNP)Plastic High Power Silicon TransistorThese devices are designed for use in high power audio amplifiers utilizing complementary or quasi complementary circuits.Features•DC Current Gain − h FE = 30 (Min) @ I C = 2.0 Adc •Pb −Free Packages are Available*MAXIMUM RATINGSRatingSymbol Value Unit Collector −Emitter Voltage V CEO 80Vdc Collector −Base Voltage V CBO 80Vdc Emitter −Base Voltage V EBO 5.0Vdc Collector Current I C 10Adc Base CurrentI B 6.0Adc Total Device Dissipation @ T C = 25°C Derate above 25°CPD 90720W W/°C Operating and Storage Junction Temperature RangeT J , T stg−55 to +150°CTHERMAL CHARACTERISTICSCharacteristicsSymbol Max Unit Thermal Resistance, Junction −to −Caseq JC1.39°C/WStresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.*For additional information on our Pb −Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.10 AMPEREPOWER TRANSISTORS80 VOLTS 90 WATTSTO −220AB CASE 221A −09STYLE 1MARKING DIAGRAMBD8xx =Device Code x = 09 or 10A =Assembly Location Y =YearWW =Work WeekG=Pb −Free PackageSee detailed ordering and shipping information in the package dimensions section on page 4 of this data sheet.ORDERING INFORMATIONELECTRICAL CHARACTERISTICS (T C = 25°C unless otherwise noted)CharacteristicSymbol Min Max Unit Collector −Emitter Sustaining Voltage (Note 1)(I C = 0.1 Adc, I B = 0)BV CEO 80−−VdcCollector Cutoff Current(V CB = 80 Vdc, I E = 0)I CBO − 1.0mAdc Emitter Cutoff Current(V BE = 5.0 Vdc, I C = 0)I EBO −2.0mAdcDC Current Gain(I C = 2.0 A, V CE = 2.0 V)(I C = 4.0 A, V CE = 2.0 V)h FE3015−−Collector −Emitter Saturation Voltage (Note 1)(I C = 3.0 Adc, I B = 0.3 Adc)V CE(sat)− 1.1Vdc Base −Emitter On Voltage (Note 1)(I C = 4.0 Adc, V CE = 2.0 Vdc)V BE(on)−1.6VdcCurrent −Gain Bandwidth Product(I C = 1.0 Adc, V CE = 10 Vdc, f = 1.0 MHz)f T1.5−MHz1.Pulse Test: Pulse Width x 300 m s, Duty Cycle x2.0%.Figure 1. Active Region DC Safe Operating Area(see Note 1)10V CE , COLLECTOR-EMITTER VOLTAGE (VOLTS)310.10.3I C , C O L L E C T O R C U R R E N T (A M P )9080002550100125150175Figure 2. Power −Temperature Derating CurveT C , CASE TEMPERATURE (°C)P D , P O W E R D I S S I P A T I O N (W A T T S )7510706050403020V C E , C O L L E C T O R -E M I T T E R V O L T A G E (V O L T S )V C E , C O L L E C T O R -E M I T T E R V O L T A G E (V O L T S )Figure 3. DC Current GainIC , COLLECTOR CURRENT (AMP)h F E , D C C U R R E N T G A I NNPN BD809PNP BD810I C , COLLECTOR CURRENT (AMP)h F E , D C C U R RE N T G A I N50010050200205.010Figure 4. Collector Saturation Region2.0I B , BASE CURRENT (mA)1.81.61.41.201.00.20.60.80.4 2.01.81.61.41.201.00.20.60.80.4I B , BASE CURRENT (mA)2.81.61.22.400.80.42.0I C , COLLECTOR CURRENT (AMP)V , V O L T A G E (V O L T S )Figure 5. “On” VoltagesI C , COLLECTOR CURRENT (AMP)V , V O L T A G E (V O L T S )2.81.61.22.400.80.42.0Figure 6. Thermal Responset, PULSE WIDTH (ms)1.00.010.70.50.30.20.10.070.050.030.02r (t ), N O R M A L I Z E D E F F E C T I V E T R A N S I E N T T H E R M A L R E S I S T A N C ENote 1:There are two limitations on the power handling ability of a transistor: average junction temperature and second breakdown. Safe operating area curves indicate I C − V CE limits of the transistor that must be observed for reliable operation, i.e., the transistor must not be subjected to greater dissipation than the curves indicate.The data of Figure 1 is based on T J(pk) = 150°C; T C is variable depending on conditions. Second breakdown pulse limits are valid for duty cycles to 10% provided T J(pk)v 150°C. At high case temperatures, thermal limitations will reduce the power that can be handled to values less than the limitations imposed by second breakdown.ORDERING INFORMATIONDevicePackage Shipping †BD809TO −22050 Units / Rail BD809G TO −220(Pb −Free)BD810TO −22050 Units / Rail BD810GTO −220(Pb −Free)†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.PACKAGE DIMENSIONSTO −220CASE 221A −09ISSUE AGNOTES:1.DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.2.CONTROLLING DIMENSION: INCH.3.DIMENSION Z DEFINES A ZONE WHERE ALL BODY AND LEAD IRREGULARITIES ARE ALLOWED.DIM MIN MAX MIN MAX MILLIMETERS INCHES A 0.5700.62014.4815.75B 0.3800.4059.6610.28C 0.1600.190 4.07 4.82D 0.0250.0360.640.91F 0.1420.161 3.61 4.09G 0.0950.105 2.42 2.66H 0.1100.161 2.80 4.10J 0.0140.0250.360.64K 0.5000.56212.7014.27L 0.0450.060 1.15 1.52N 0.1900.210 4.83 5.33Q 0.1000.120 2.54 3.04R 0.0800.110 2.04 2.79S 0.0450.055 1.15 1.39T 0.2350.255 5.97 6.47U 0.0000.0500.00 1.27V 0.045--- 1.15---Z---0.080--- 2.04FSEATING PLANESTYLE 1:PIN 1.BASE2.COLLECTOR3.EMITTER4.COLLECTORON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages.“Typical” parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates,and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.PUBLICATION ORDERING INFORMATION分销商库存信息:ONSEMIBD809G BD810G BD810。

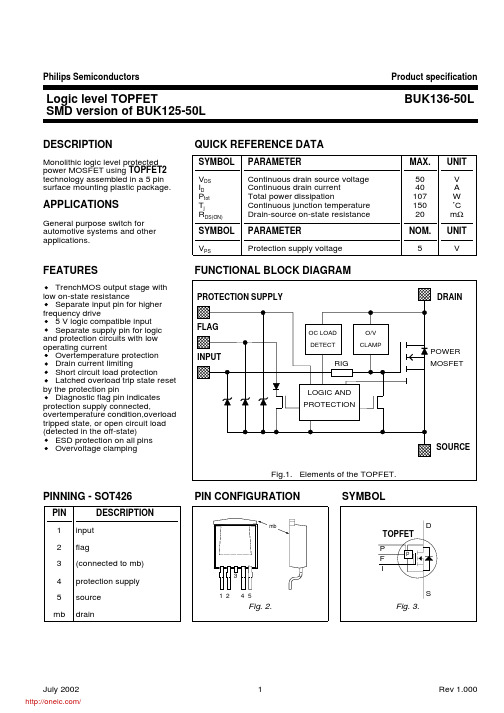

BUK136-50L,118;中文规格书,Datasheet资料

Philips Semiconductors Product specificationLogic level TOPFETBUK136-50LSMD version of BUK125-50LDESCRIPTIONQUICK REFERENCE DATAMonolithic logic level protected SYMBOL PARAMETERMAX.UNIT power MOSFET using TOPFET2technology assembled in a 5 pin V DS Continuous drain source voltage 50V surface mounting plastic package.I D Continuous drain current 40A P tot Total power dissipation107W APPLICATIONST jContinuous junction temperature 150˚C R DS(ON)Drain-source on-state resistance 20m ΩGeneral purpose switch for automotive systems and other SYMBOL PARAMETERNOM.UNIT applications.V PSProtection supply voltage5VFEATURESTrenchMOS output stage with Separate input pin for higher 5 V logic compatible input Separate supply pin for logic Overtemperature protection Drain current limitingShort circuit load protectionLatched overload trip state reset Diagnostic flag pin indicates overtemperature condition,overload tripped state, or open circuit load ESD protection on all pins Overvoltage clampingPINNING - SOT426PIN CONFIGURATIONSYMBOLPhilips Semiconductors Product specification Logic level TOPFET BUK136-50L SMD version of BUK125-50LLIMITING VALUESLimiting values in accordance with the Absolute Maximum Rating System (IEC 134)SYMBOL PARAMETER CONDITIONS MIN.MAX.UNIT Continuous voltageVDS Drain source voltage1VIS= 0 V-50V Continuous currentsI D Drain current VPS= 5 V; Tmb=25˚C-self -AlimitedVPS= 0 V; Tmb=80˚C-40AI I Input current-55mAI F Flag current-55mAIPProtection supply current-55mAThermalPtot Total power dissipation Tmb= 25˚C-107WT stg Storage temperature-55175˚CT j Junction temperature2continuous-150˚CTsoldMounting base temperature during soldering-260˚C ESD LIMITING VALUESYMBOL PARAMETER CONDITIONS MIN.MAX.UNITVCElectrostatic discharge capacitor Human body model;-2kVvoltage C = 250 pF; R = 1.5 kΩOVERLOAD PROTECTION LIMITING VALUEWith an adequate protection supply For overload conditions an n-MOS The drain current is limited to connected, TOPFET can protect transistor turns on between the reduce dissipation in case of short itself from two types of overload -input and source to quickly circuit load. Refer to OVERLOAD overtemperature and short circuit discharge the power MOSFET CHARACTERISTICS.load.gate capacitance.SYMBOL PARAMETER REQUIRED CONDITION MIN.MAX.UNIT Overload protection3protection supplyVDS Drain source voltage VPS≥ 4 V035VOVERVOLTAGE CLAMPING LIMITING VALUESAt a drain source voltage above 50 V the power MOSFET is actively turned on to clamp overvoltage transients. SYMBOL PARAMETER CONDITIONS MIN.MAX.UNITInductive load turn off IDM = 25 A; VDD≤ 20 VEDSM Non-repetitive clamping energy Tmb= 25˚C-550mJEDRM Repetitive clamping energy Tmb≤ 95˚C; f = 250 Hz-60mJ1 Prior to the onset of overvoltage clamping. For voltages above this value, safe operation is limited by the overvoltage clamping energy.2 A higher Tj is allowed as an overload condition but at the threshold Tj(TO)the over temperature trip operates to protect the switch.3 All control logic and protection functions are disabled during conduction of the source drain diode. If the protection circuit was previouslylatched, it would be reset by this condition.Philips Semiconductors Product specification Logic level TOPFET BUK136-50L SMD version of BUK125-50LTHERMAL CHARACTERISTICSYMBOL PARAMETER CONDITIONS MIN.TYP.MAX.UNIT Thermal resistanceRth j-mbJunction to mounting base--0.94 1.17K/W OUTPUT CHARACTERISTICSLimits are for -40˚C ≤ Tmb ≤ 150˚C; typicals are for Tmb= 25˚C unless otherwise specified.SYMBOL PARAMETER CONDITIONS MIN.TYP.MAX.UNIT Off-state VIS= 0 VV(CL)DSS Drain-source clamping voltage ID= 10 mA50-70VIDM= 5 A; tp ≤ 300 µs; δ≤ 0.01506070VI DSS Drain source leakage current1VPS= 0 V; VDS= 40 V--100µATmb= 25˚C-0.110µAOn-state tp≤ 300 µs; δ≤ 0.01; VPS≥ 4 VRDS(ON)Drain-source resistance IDM= 15 A; VIS≥ 4.4 V--40mΩTmb= 25˚C-1520mΩINPUT CHARACTERISTICSLimits are for -40˚C ≤ Tmb ≤ 150˚C; typicals are for Tmb= 25˚C unless otherwise specified.SYMBOL PARAMETER CONDITIONS MIN.TYP.MAX.UNIT Normal operationVIS(TO)Input threshold voltage2ID= 1 mA0.6- 2.6VTmb= 25˚C 1.1 1.6 2.1VI IS Input current VIS= 5 V-16100µAV(CL)IS Input clamping voltage II= 1 mA 5.5 6.48.5VRIGInternal series resistance3to gate of power MOSFET- 1.7-kΩOverload protection latched VPS≥ 4 VI ISL Input current VIS= 5 V1 2.74mA1 The drain current required for open circuit load detection is switched off when there is no protection supply, in order to ensure a low off-statequiescent current. Refer to OPEN CIRCUIT LOAD DETECTION CHARACTERISTICS.2 The measurement method is simplified if VPS = 0 V, in order to distinguish IDfrom IDSP. Refer to OPEN CIRCUIT LOAD DETECTIONCHARACTERISTICS.3 This is not a directly measurable parameter.Philips Semiconductors Product specificationLogic level TOPFETBUK136-50LSMD version of BUK125-50LPROTECTION SUPPLY CHARACTERISTICSLimits are for -40˚C ≤ T mb ≤ 150˚C; typicals are for T mb = 25˚C.SYMBOL PARAMETERCONDITIONSMIN.TYP.MAX.UNIT Protection & detection V PSF Threshold voltage 1I F = 100 µA; V DS = 5 V 2.53.454VNormal operation or protection latched I PS , I PSL Supply current V PS = 4.5 V -210450µA V (CL)PS Clamping voltageI P = 1.5 mA5.56.58.5V Overload protection latched V PSR Reset voltage 1 1.83V t prReset timeV PS ≤ 1 V1045120µsOPEN CIRCUIT LOAD DETECTION CHARACTERISTICSAn open circuit load condition can be detected while the TOPFET is in the off-state. Refer to TRUTH TABLE .V PS = 5 V. Limits are for -40˚C ≤ T mb ≤ 150˚C and typicals are for T mb = 25˚C.SYMBOL PARAMETER CONDITIONSMIN.TYP.MAX.UNIT I DSP Off-state drain current 2V IS = 0 V; 2 V ≤ V DS ≤ 40 V 0.9 1.8 2.7mA V DSF Drain threshold voltage 3V IS = 0 V 0.212V V ISFInput threshold voltage 4I D = 100 µA0.30.81.1VOVERLOAD CHARACTERISTICST mb = 25˚C unless otherwise specified.SYMBOL PARAMETERCONDITIONS MIN.TYP.MAX.UNITShort circuit load protection V PS > 4 VI DDrain current limiting 5V IS = 5 V;-40˚C ≤ T mb ≤ 150˚C 406284A P D(TO)Overload power threshold for protection to operate 90220330W T DSC Characteristic timewhich determines trip time 6250500700µs Overtemperature protection V PS = 5 VT j(TO)Threshold temperaturefrom I D ≥ 4 A or V DS > 0.2 V150170-˚C1 When V PS is less than V PSF the flag pin indicates low protection supply voltage. Refer to TRUTH TABLE.2 The drain source current which flows in a normal load when the protection supply is high and the input is low.3 If V DS < V DSF then the flag indicates open circuit load.4 For open circuit load detection, V IS must be less than V ISF .5 Product specification will include curve showing output characteristics.6 Trip time t d sc varies with overload dissipation P D according to the formula t d sc ~ T DSC / ln[ P D / P D(TO)].Philips Semiconductors Product specificationLogic level TOPFETBUK136-50LSMD version of BUK125-50LTRUTH TABLEFor normal, open-circuit load and overload conditions or inadequate protection supply voltage.Assumes proper external pull-up for flag pin. Refer to FLAG CHARACTERISTICS .CONDITIONPROTECTIONINPUT FLAG OUTPUT Normal on-state 110ON Normal off-state 100OFF Open circuit load 110ON Open circuit load 101OFF Short circuit load 1111OFF Over temperature1X 1OFF Low protection supply voltage 011ON Low protection supply voltage1OFFKEY ‘0’ equals low‘1’ equals high‘X’ equals don’t care.FLAG CHARACTERISTICSThe flag is an open drain transistor which requires an external pull-up circuit.Limits are for -40˚C ≤ T mb ≤ 150˚C; typicals are for T mb = 25˚C.SYMBOL PARAMETER CONDITIONSMIN.TYP.MAX.UNITFlag ‘low’normal operation; V PS = 5 V V FSF Flag voltageI F = 100 µA -0.81V I FSF Flag saturation current V FS = 5 V -10-mAFlag ‘high’overload or fault I FSO Flag leakage current V FS = 5 V -0.110µA V (CL)FS Flag clamping voltage I F = 100 µA5.56.28.5VApplication information R FSuitable external pull-up V FF = 5 V-47-k ΩresistanceSWITCHING CHARACTERISTICST mb = 25˚C; R I = 50 Ω; R IS = 50 Ω; V DD = 15 V; resistive load R L = 10 Ω.SYMBOL PARAMETER CONDITIONS MIN.TYP.MAX.UNIT t d on Turn-on delay time V IS : 0 V ⇒ 5 V- 1.85µs t r Rise time- 3.58µs t d off Turn-off delay time V IS : 5 V ⇒ 0 V -1130µs t fFall time-512µs1 In this condition the protection circuit is latched. To reset the latch the protection pin must be taken low. Refer to PROTECTION SUPPLYCHARACTERISTICS.Philips Semiconductors Product specificationLogic level TOPFETBUK136-50LSMD version of BUK125-50LMECHANICAL DATA1 Epoxy meets UL94 V0 at 1/8". Net mass: 1.5 g.For soldering guidelines and SMD footprint design, please refer to Data Handbook SC18.Philips Semiconductors Product specification Logic level TOPFET BUK136-50L SMD version of BUK125-50LDEFINITIONSDATA SHEET STATUSDATA SHEET PRODUCT DEFINITIONSSTATUS1STATUS2Objective data Development This data sheet contains data from the objective specification forproduct development. Philips Semiconductors reserves the right tochange the specification in any manner without noticePreliminary data Qualification This data sheet contains data from the preliminary specification.Supplementary data will be published at a later date. PhilipsSemiconductors reserves the right to change the specification withoutnotice, in order to improve the design and supply the best possibleproductProduct data Production This data sheet contains data from the product specification. PhilipsSemiconductors reserves the right to make changes at any time inorder to improve the design, manufacturing and supply. Changes willbe communicated according to the Customer Product/ProcessChange Notification (CPCN) procedure SNW-SQ-650ALimiting valuesLimiting values are given in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections ofthis specification is not implied. Exposure to limiting values for extended periods may affect device reliability. Application informationWhere application information is given, it is advisory and does not form part of the specification.Philips Electronics N.V. 2002All rights are reserved. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner.The information presented in this document does not form part of any quotation or contract, it is believed to be accurate and reliable and may be changed without notice. No liability will be accepted by the publisher for any consequence of its use. Publication thereof does not convey nor imply any license under patent or other industrial or intellectual property rights.LIFE SUPPORT APPLICATIONSThese products are not designed for use in life support appliances, devices or systems where malfunction of these products can be reasonably expected to result in personal injury. Philips customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips for any damages resulting from such improper use or sale.1 Please consult the most recently issued datasheet before initiating or completing a design.2 The product status of the device(s) described in this datasheet may have changed since this datasheet was published. The latest information isavailable on the Internet at URL .分销商库存信息: NXPBUK136-50L,118。

SAE AS 8049B 中文版

AEROSPACESTANDARD® AS8049BIssued 1990-07Revised 2005-01Superseding AS8049APerformance Standard for Seatsin Civil Rotorcraft, Transport Aircraft, and General Aviation Aircraft民用旋翼类/运输类和通用航空类飞机座椅的性能标准1.范围1.1 通则本SAE宇航标准(AS)规定了在民用旋翼类、运输类和通用航空类飞机中乘客和机组成员座椅的最低性能标准、鉴定要求及记录文件的最低要求。

制定本文的目的是使座椅在正常工作载荷条件下到达舒适耐用和保护乘员的作用。

本文对座椅/乘员/约束系统在联邦航空条例(14CFR)第23、25、27或29部中公布的静态极限载荷和动态冲击试验条件下保护乘员的验证试验和评估判据进行了规定。

为了促进试验技术的统一和达到合格的数据,同时也提出了试验程序、测试方法、设备和试验结果说明的指南。

本文还叙述了区分座椅供应商和安装座椅的申请者之间对座椅系统性能应负的责任。

座椅供应商的责任包括满足所有座椅系统的性能要求和获得本文叙述的全部数据并提供给安装座椅的申请者。

而安装座椅的申请者则在保证满足座椅安全的全部要求方面对最终系统负责。

1.2 适用性本文论述了用于民用旋翼航空器、运输机和通用航空飞机钟要求的动态试验的座椅系统的性能判据。

1.3 座椅类型本文包括了在飞机型号合格审定钟,用于下列各类飞机的所有乘客和机组成员座椅:表1: 适用座椅类型座椅类型飞机类型 适用FARA 运输类飞机 14 CFR 25部14 CFR 27部B 普通类旋翼航空器14 CFR 29部B 运输类旋翼航空器C 通用航空飞机 14 CFR 23部1.4 单位本文采用了美国习惯的英制单位(磅)和国际系统的公制单位(SI)。

在所有情况,英制优先,公制为近似和保守的换算。

P89LPC935FA,129,P89LPC936FDH系列,P89LPC935FDH,529,P89LPC933FDH系列规格书,Datasheet 资料