MB2861中文资料

PCM3168A中文资料

• EXTERNAL RESET PIN: – ADC/DAC Simultaneous

• AUDIO INTERFACE MODE: – ADC/DAC Independent Master/Slave

• AUDIO DATA FORMAT: – ADC/DAC Independent I2S™, Left-Justified, Right-Justified, DSP, TDM

• POWER SUPPLIES: 5 V for Analog and 3.3 V for Digital

Copyright © 2008, Texas Instruments Incorporated

元器件交PC易M3网 PCM3168A-Q1

SBAS452 – SEPTEMBER 2008 .........................................................................................................................................................................................

• PACKAGE: HTQFP-64 • OPERATING TEMPERATURE RANGE:

– Consumer Grade: –40°C to +85°C – Automotive Audio Grade: –40°C to +105°C

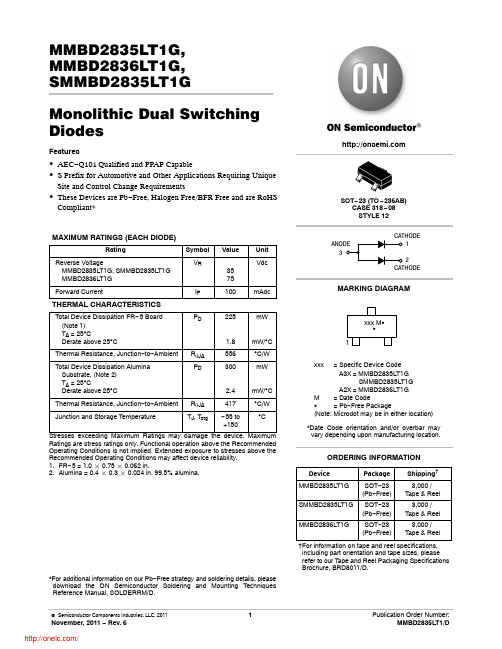

MMBD2835LT1G;MMBD2836LT1G;MMBD2835LT1;MMBD2836LT1;中文规格书,Datasheet资料

Features

AEC−Q101 Qualified and PPAP Capable S Prefix for Automotive and Other Applications Requiring Unique

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D. *For additional information on our Pb−Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

0.1 0.2 0.4 0.6 0.8 1.0 1.2 VF, FORWARD VOLTAGE (VOLTS)

0.001

0

10

20

30

40

50

VR, REVERSE VOLTAGE (VOLTS)

Figure 2. Forward Voltage

FiguFigure 1. Recovery Time Equivalent Test Circuit

2

/

MMBD2835LT1G, MMBD2836LT1G, SMMBD2835LT1G

NJM2881中文资料

∆Vo/∆VIN VIN=Vo+1V ∼ Vo+6V, Io=30mA

-

Load Regulation

∆Vo/∆Io Io=0 ∼ 300mA

-

Dropout Voltage

∆VI-O

Io=100mA

-

Ripple Rejection

RR

ein=200mVrms,f=1kHz,Io=10mA, Vo=3V version

Cp=0.01µF

*5 1.9V ≤ Vo ≤ 2.6V version: Co=2.2µF Vo ≤ 1.8V version: Co=4.7µF

Connect control terminal to VIN terminal The quiescent current can be reduced by using a resistance “R”. Instead, it increases the minimum operating voltage. For further information, please refer to Figure “Output Voltage vs. Control Voltage”.

2 In use of ON/OFF CONTROL:

VIN

VIN

VOUT

VOUT

0.1µF R

NJM2881/82

CONTROL

NOISE BYPASS

GND

1.0µF *5 Cp=0.01µF

*5 1.9V ≤ Vo ≤ 2.6V version: Co=2.2µF Vo ≤ 1.8V version: Co=4.7µF

ELECTRICAL CHARACTERISTICS

MB85RC64中文

铁电存储器MB85RC64(8K×8)1.概述MB85RC64了FRAM(铁电随机存取记忆体)独立芯片配置了8192×8位,形成铁电工艺和硅栅CMOS工艺技术非易失性内存中的细胞。

MB85RC64采用两线串行接口(与世界标准的I2C总线兼容)。

与SRAM不同的MB85RC64是无需使用数据备份电池,能够保留数据。

MB85RC64的读写次数10亿次,与EPROM和FLASH相比,有显著的改善。

而且不在向写完存储器后,不需要查询序列。

2.特性●位操作:8192×8位●工作电压:2.7V—3.3V●工作频率:400KHz●两串行总线:I2C总线2.1标准版,支持标准模式和快速模式,由SCL和SDA控制。

●工作温度范围:-40℃—85℃●数据保持:10年(55℃)●读写寿命:至少每位10亿次●封装:Plastic / SOP, 8-pin (FPT-8P-M02)●低电压消耗:工作电流0.15mA,待机电流5uA3.管脚分配3.管脚功能描述管教编号管脚名功能描述1—3 A0/A1/A2 器件地址一个I2C总线可以连接8个和MB85RC64类似的器件。

通过将A0/A1/A2与VDD和VSS连接,确定每个器件的地址。

如果A0/A1/A2未连接,默认为0。

CPU通过SDA线输出一个地址与器件进行匹配。

4 VSS 数字地5 SDA 数据IO串口这是双向通信的数据IO口,用来读写铁电存储器的阵列数据,这是开漏极输出,可能是与其它漏极开路(或者集电极开路信号总线)进行线或运算,因此需要一个上拉电阻连接到外部电路。

6 SCL 时钟串口这是时钟输入口,时钟上升沿进行数据采样,下降沿进行数据输出。

7 WP 写保护WP是H电平,禁止写入。

WP是L电平,可进行写数据,如果WP没有置位,默认为L电平。

而读数据操作,不受WP 管脚的限制。

8 VDD 电源电压4.模块框图5.I2C电路MB85RC64有两线串行接口,支持I2C总线,并作为从器件工作。

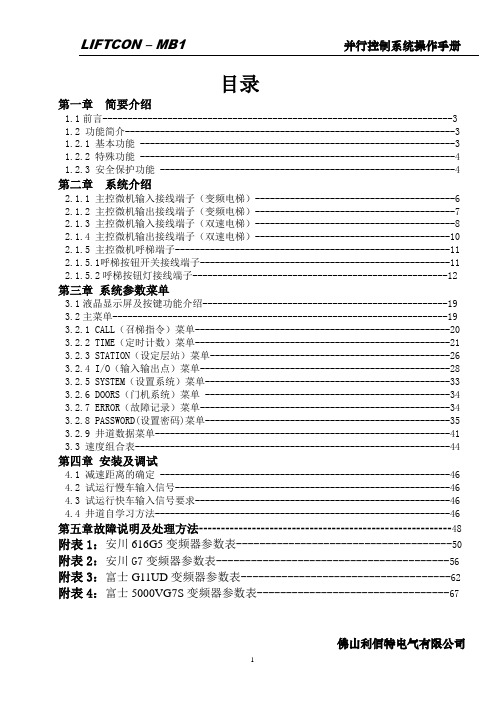

MB1说明书带变频参数表资料

目录第一章简要介绍1.1前言----------------------------------------------------------------------3 1.2 功能简介------------------------------------------------------------------3 1.2.1 基本功能 ---------------------------------------------------------------3 1.2.2 特殊功能 ---------------------------------------------------------------4 1.2.3 安全保护功能 -----------------------------------------------------------4 第二章系统介绍2.1.1 主控微机输入接线端子(变频电梯)----------------------------------------6 2.1.2 主控微机输出接线端子(变频电梯)----------------------------------------7 2.1.3 主控微机输入接线端子(双速电梯)----------------------------------------8 2.1.4 主控微机输出接线端子(双速电梯)---------------------------------------10 2.1.5 主控微机呼梯端子-------------------------------------------------------11 2.1.5.1呼梯按钮开关接线端子--------------------------------------------------11 2.1.5.2呼梯按钮灯接线端子---------------------------------------------------12 第三章系统参数菜单3.1液晶显示屏及按键功能介绍-------------------------------------------------19 3.2主菜单-------------------------------------------------------------------19 3.2.1 CALL(召梯指令)菜单---------------------------------------------------20 3.2.2 TIME(定时计数)菜单---------------------------------------------------21 3.2.3 STATION(设定层站)菜单------------------------------------------------26 3.2.4 I/O(输入输出点)菜单--------------------------------------------------28 3.2.5 SYSTEM(设置系统)菜单-------------------------------------------------33 3.2.6 DOORS(门机系统)菜单 -------------------------------------------------34 3.2.7 ERROR(故障记录)菜单--------------------------------------------------34 3.2.8 PASSWORD(设置密码)菜单-------------------------------------------------35 3.2.9 井道数据菜单-----------------------------------------------------------41 3.3 速度组合表---------------------------------------------------------------44第四章安装及调试4.1 减速距离的确定 ----------------------------------------------------------46 4.2 试运行慢车输入信号-------------------------------------------------------46 4.3 试运行快车输入信号要求---------------------------------------------------46 4.4 井道自学习方法-----------------------------------------------------------46 第五章故障说明及处理方法---------------------------------------------------------48 附表1:安川616G5变频器参数表-------------------------------------50附表2:安川G7变频器参数表----------------------------------------56 附表3:富士G11UD变频器参数表------------------------------------62 附表4:富士5000VG7S变频器参数表---------------------------------67第一章简要介绍1.1 前言LIFTCON-MB1并行电梯控制微机是一款高性能低价格电梯控制系统,是以可靠、低价功能全、易维护、易使用、美观为设计思想。

BGA2866,115;中文规格书,Datasheet资料

1. Product profile1.1General descriptionSilicon Monolithic Microwave Integrated Circuit (MMIC) wideband amplifier with internalmatching circuit in a 6-pin SOT363 plastic SMD package.1.2Features and benefitsInput internally matched to 50 ΩA gain of 23.2 dB at 250 MHz increasing to 24.3 dB at 2150 MHz Output power at 1 dB gain compression = 4 dBm Supply current = 17.4 mA at a supply voltage of 5 V Reverse isolation > 32 dB up to 2150 MHzGood linearity with low second order and third order products Noise figure = 3.8 dB at 950 MHz Unconditionally stable (K > 1)No output inductor required1.3ApplicationsLNB IF amplifiersGeneral purpose low noise wideband amplifier for frequencies betweenDC and 2.2GHz2. Pinning informationBGA2866MMIC wideband amplifierRev. 2 — 1 November 2010Product data sheetTable 1.PinningPin Description Simplified outline Graphic symbol1V CC 2, 5GND23RF_OUT 4GND16RF_IN132456sym052132, 5643. Ordering information4. Marking5. Limiting values6. Thermal characteristics7. CharacteristicsTable 2.Ordering informationType number Package NameDescriptionVersion BGA2866-plastic surface-mounted package; 6 leadsSOT363Table 3.MarkingType numberMarking code DescriptionBGA2866*ED* = - : made in Hong Kong * = p : made in Hong Kong * = W : made in China * = t : made in MalaysiaTable 4.Limiting valuesIn accordance with the Absolute Maximum Rating System (IEC 60134).Symbol Parameter Conditions Min Max Unit V CC supply voltage RF input AC coupled−0.5 5.5V I CC supply current -36mA P tot total power dissipation T sp = 90 °C -200mW T stg storage temperature −40+125°C T j junction temperature -125°C P drivedrive power-−15dBmTable 5.Thermal characteristics Symbol ParameterConditionsTyp Unit R th(j-sp)thermal resistance from junction to solder pointP tot =200mW; T sp =90°C300K/WTable 6.CharacteristicsV CC = 5.0 V; Z S = Z L = 50 Ω; P i = −40 dBm; T amb = 25 °C; measured on demo board; unless otherwise specified.Symbol Parameter ConditionsMin Typ Max Unit V CC supply voltage 4.5 5.0 5.5V I CCsupply current14.717.420.1mATable 6.Characteristics …continuedV CC = 5.0 V; Z S = Z L = 50 Ω; P i = −40 dBm; T amb = 25 °C; measured on demo board; unless otherwise specified.Symbol Parameter Conditions Min Typ Max Unit G p power gain f = 250 MHz22.623.223.8dBf = 950 MHz23.223.924.6dBf = 2150 MHz22.824.325.8dB RL in input return loss f = 250 MHz182022dBf=950MHz242628dBf = 2150 MHz111824dB RL out output return loss f = 250 MHz212630dBf=950MHz121314dBf = 2150 MHz101114dB ISL isolation f = 250 MHz406081dBf=950MHz414344dBf = 2150 MHz323537dB NF noise figure f = 250 MHz 3.4 3.9 4.4dBf = 950 MHz 3.4 3.8 4.2dBf = 2150 MHz 3.5 3.9 4.3dB B−3dB−3 dB bandwidth 3 dB below gain at 1GHz 3.1 3.3 3.4GHz K Rollett stability factor f = 250 MHz333537f = 950 MHz 3.8 4.1 4.4f = 2150 MHz 1.3 1.6 1.9P L(sat)saturated output power f = 250 MHz567dBmf = 950 MHz578dBmf = 2150 MHz245dBm P L(1dB)output power at 1 dB gain compression f = 250 MHz345dBmf = 950 MHz345dBmf = 2150 MHz134dBm IP3I input third-order intercept point P drive=−36dBm (for each tone)f1=250MHz; f2=251MHz−6−4−2dBmf1=950MHz; f2=951MHz−9−7−4dBmf1=2150MHz; f2=2151MHz−16−12−9dBm IP3O output third-order intercept point P drive=−36dBm (for each tone)f1=250MHz; f2=251MHz171921dBmf1=950MHz; f2=951MHz151720dBmf1=2150MHz; f2=2151MHz91215dBm P L(2H)second harmonic output power P drive=−33dBmf1H=250MHz; f2H=500MHz−53−51−49dBmf1H=950MHz; f2H=1900MHz−43−41−40dBm ΔIM2second-order intermodulation distance P drive=−36dBm (for each tone)f1=250MHz; f2=251MHz364758dBcf1=950MHz; f2=951MHz324355dBc8. Application informationFigure1 shows a typical application circuit for the BGA2866 MMIC. The device isinternally matched to 50 Ω and therefore does not need any external matching. The valueof the input and output DC blocking capacitors C2 and C3 should not be more than 100 pFfor applications above 100 MHz. However, when the device is operated below 100 MHz,the capacitor value should be increased.The 22 nF supply decoupling capacitor C1 should be located as close as possible to theMMIC.The PCB top ground plane, connected to pins 2, 4 and 5 must be as close as possible tothe MMIC, preferably also below the MMIC. When using via holes, use multiple via holesas close as possible to the MMIC.8.1Application examples8.2Graphs8.3TablesTable 7.Supply current over temperature and supply voltagesTypical values.Symbol Parameter Conditions T amb (°C)Unit−402585I CC supply current V CC=4.5V16.4115.2714.36mAV CC=5.0V17.7316.6315.85mAV CC=5.5V19.2917.7317.27mA Table 8.Second harmonic output power over temperature and supply voltagesTypical values.Symbol Parameter Conditions T amb (°C)Unit−402585 P L(2H)second harmonic output power f = 250 MHz; P drive=−33dBmV CC=4.5V−48−49−51dBmV CC= 5.0V−49−51−53dBmV CC=5.5V−50−52−54dBmf = 950 MHz; P drive=−33dBmV CC=4.5V−40−41−42dBmV CC= 5.0V−40−41−42dBmV CC=5.5V−40−41−42dBmTable 9.Input power at 1 dB gain compression over temperature and supply voltages Typical values.Symbol Parameter Conditions T amb (°C)Unit−402585P i(1dB)input power at 1dB gain compression f = 250 MHzV CC=4.5V−18−18−19dBmV CC= 5.0V−18−18−18dBmV CC=5.5V−17−18−18dBmf = 950 MHzV CC=4.5V−19−19−19dBmV CC= 5.0V−18−18−19dBmV CC=5.5V−18−18−18dBmf = 2150 MHzV CC=4.5V−20−21−22dBmV CC= 5.0V−20−21−22dBmV CC=5.5V−20−21−22dBm Table 10.Output power at 1 dB gain compression over temperature and supply voltages Typical values.Symbol Parameter Conditions T amb (°C)Unit−402585P L(1dB)output power at 1dB gain compression f = 250 MHzV CC=4.5V433dBmV CC= 5.0V544dBmV CC=5.5V554dBmf = 950 MHzV CC=4.5V433dBmV CC= 5.0V544dBmV CC=5.5V654dBmf = 2150 MHzV CC=4.5V320dBmV CC= 5.0V421dBmV CC=5.5V431dBm分销商库存信息: NXPBGA2866,115。

MU2861键盘控制器C080620(中性)

键盘控制器(KEYBOARD CONTROLLER)使用说明书Operation Instruction键盘控制器使用说明书温馨提示:感谢您使用本公司产品。

为了让您能够尽快熟练的操作本机,请您仔细阅读我们为您配备内容详细的使用说明书,从中您可以获取有关产品安全注意事项、产品介绍以及产品使用方法等方面的知识。

当您阅读完说明书后,请将它妥善保存好,以备日后参考。

如果您在产品的使用过程中发现什么问题,请联系产品技术服务人员。

谢谢您的合作!申明:在编写此说明书时我们非常小心谨慎,并认为此说明书中所提供的信息是正确可靠的,然而难免会有错误和疏漏之处,请您多加包涵并热切欢迎您的指正。

但是我们将不对本手册可能出现的问题和疏漏负责。

同时,由于我们无法控制用户对本手册可能造成的误解,因此,将不负责在使用本手册的过程中出现的事故或由此引起的损坏。

对于因使用本产品所造成的任何损坏第三方的索赔不负责任。

对于因软件的误操作、产品维修、或其它意外情况等引起资料的删改或丢失不负任何责任,也不对由此造成的其它间接损失负责。

本产品的发行和销售由原始购买者在许可协议条款下使用。

未经允许,任何单位和个人不得将本说明书全部或部分复制、再生或翻译成其它机器可读形式的电子媒介。

本说明书若有任何修改恕不另行通知。

因软件版本升级而造成的与本说明书不符,以软件为准。

注:本设备在出厂前已经过严格的质量测试,符合国家电磁辐射标准。

目 录设备概述 (4)第一部分 控制摄像机 (6)1.1 选择摄像机 (6)1.2 控制摄像机方向 (6)1.3 控制摄像机镜头 (7)1.4 预置位操作 (7)1.4.1 设置预置位 (7)1.4.2 调用预置位 (7)1.4.3 清除预置位 (7)1.5 图像返回 (8)1.6 自动巡视 (8)1.6.1 设置巡视队列 (8)1.6.2 调用巡视队列 (8)1.7 轨迹扫描 (8)1.7.1 设置轨迹扫描 (8)1.7.2 调用轨迹扫描 (8)1.8 区域扫描 (9)1.8.1 设置区域扫描 (9)1.8.2 调用区域扫描 (9)1.9 云台自动扫描 (9)1.10 操作辅助功能 (9)1.11 智能摄像机菜单设置 (10)第二部分 控制数字录像机 (10)2.1 选择数字录像机 (10)2.2 登录数字录像机 (11)2.3 图像监控 (11)2.4 图像抓拍 (11)2.5 多画面监控 (11)2.6 图像浏览 (11)2.7 图像播放、暂停 (11)2.8 图像快退、快进 (11)2.9 图像段首、段末 (12)2.10 图像帧退、帧进............................................................12 2.11 图像录制 (12)2.12 图像停止 (12)2.13 信息显示 (12)2.14 录像机菜单设置 (12)第三部分 键盘设置 (13)3.1 通讯速率设置 (13)3.2 控制协议设置 (13)3.3 操作员设置 (14)3.3.1 设置键盘号 (14)3.3.2 设置操作员密码 (15)3.4 常规设置 (15)3.4.1 按键声音 (15)3.4.2 背光控制 (15)3.4.3 恢复出厂设置 (16)3.5 语言选择 (16)3.6 软件版本 (16)3.7 退出 (16)第四部分 键盘连接 (17)4.1 键盘与智能摄像机、解码器连接示意图 (17)4.2 键盘与数字录像机连接示意图 (18)4.3 键盘与海康威视数字录像机连接示意图 (19)4.4 键盘与汉邦数字录像机连接示意图 (20)安全事项 (21)键盘控制器KEYBOARD CONTROLLER设备概述:键盘控制器是以操作控制智能摄像机、数字录像机为特色的操作设备。

EPM7128STI100-10中文资料(Altera)中文数据手册「EasyDatasheet - 矽搜」

v v v v v v v v v v v

All MAX 7000S

设备

v v (1) v v v v v v v v v v v v

注意事项: (1) 仅在只有EPM7128S,EPM7160S,EPM7192S和EPM7256S设备. (2) 在多电压I / O接口是不是在44引脚封装.

4

芯片中文手册,看全文,戳

1,800

2,500

3,200

3,750

5,000

96

128

160

192

256

6

8

10

12

16

76

100

104

124

164

7.5

7.5

10

12

12

6

6

7

7

733来自333

4.5

4.5

5

6

6

125.0

125.0

100.0

90.9

90.9

1

芯片中文手册,看全文,戳

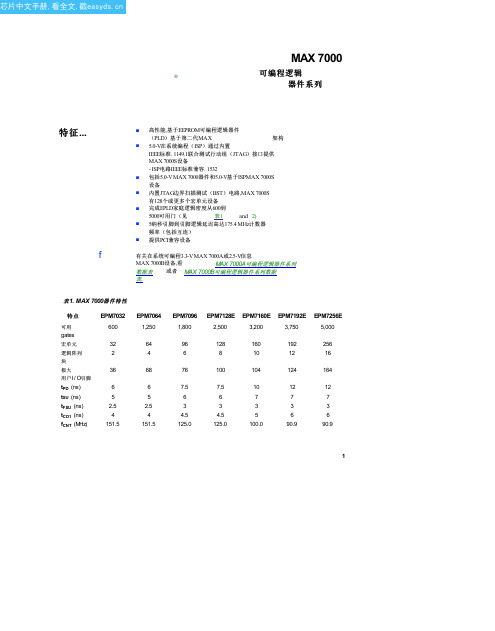

MAX 7000可编程逻辑器件系列数据手册

芯片中文手册,看全文,戳

®

2005年 9月版 . 6.7

MAX 7000

可编程逻辑 器件系列

数据表

特征... f

■ 高性能,基于EEPROM可编程逻辑器件

(PLD)基于第二代MAX

架构

■ 5.0-V在系统编程(ISP)通过内置

IEEE标准. 1149.1联合测试行动组(JTAG)接口提供

See 表3

表 3. MAX 7000速度等级

器

-5

-6

EPM7032

v

EPM7032S v

HSMS-286P中文资料

Surface Mount RF Schottky Detector Diodes in SOT-363 (SC-70, 6 Lead)Technical DataFeatures•Unique configurations in surface mount SOT-363package–increase flexibility–save board space–reduce cost•Excellent sensitivity for better detection–HSMS-286a for higherfrequencies–HSMS-285a zero bias for less power consumption•HSMS-286K groundedcenter leads provide up to10dB higher isolation •Matched diodes forconsistent performance •Better thermal conductivity for higher power dissipationApplicationsBoth are ideal for RF/ID and RF Tag; cellular and other consumer applications requiring small and large signal detection; modulation; RF to DC conversion; or voltage doubling.HSMS-285L/PHSMS-286K/L/P/RPackage Lead CodeIdentification(Top View)DescriptionHewlett-Packard’s HSMS-285L/Pand HSMS-286K/L/P/R families havebeen optimized for use as detectorsin the 915 MHz to 5.8 GHz range.The HSMS-285a, with a bandwidthof 0.01 - 7 GHz, requires no batteryor power supply, and is well suitedas a very simple and inexpensivedetector. The HSMS-286a operatesin the 0.3 - 8 GHz range and is a highperformance detector for upperfrequencies.Available in various packageconfigurations, these two familiesof detector diodes provide low costsolutions to a wide variety of designproblems. Hewlett-Packard’smanufacturing techniques assurethat when multiple diodes aremounted into a single SOT-363package, they are taken fromadjacent sites on the wafer, assuringthe highest possible degree ofmatch.PUNCONNECTEDTRIORHIGH ISOLATIONUNCONNECTED PAIR123654Pin Connections andPackage MarkingNotes:1.Package marking providesorientation and identification.2.See “Electrical Specifications” forappropriate package marking.RF Electrical Parameters, T C = +25o C, Single DiodePart Typical Tangential Sensitivity Typical Voltage Sensitivity γTypical Video Number TSS (dBm) @ f =(mV/µW) @ f =Resistance R v (K Ω)HSMS-915 MHz 2.45 GHz 5.8 GHz 915 MHz 2.45 GHz 5.8 GHz 285L -57-56-554030228.0285P Test Video Bandwidth = 2 MHzPower in = -40 dBmZero BiasConditions Zero BiasR L = 100 K Ω, Zero Bias 286K -57-56-555035255.0286L 286P 286R Test Video Bandwidth = 2 MHzPower in = –40 dBm I b = 5 µAConditionsI b = 5 µA R L = 100 K Ω, I b = 5 µASymbol ParameterUnit Absolute Maximum [1]P IV Peak Inverse Voltage V 2.0T J Junction Temperature °C 150T STG Storage Temperature °C -65 to 150T OP Operating Temperature °C -65 to 150θjcThermal Resistance [2]°C/W140Absolute Maximum Ratings, T C = 25ºC, Single DiodeNotes:1.Operation in excess of any one of these conditions may result in permanent damage to the device.2.T C = +25°C, where T C isdefined to be the temperature at the package pins where contact is made to the circuit board.ESD WARNING:Handling Precautions Should Be Taken To Avoid Static Discharge.DC Electrical Specifications, T C = +25°C, Single DiodePart Package Maximum ForwardTypical Number Marking Lead Voltage V FCapacitance C THSMS-Code [1]Code Configuration (mV)(pF)285L PL L Unconnected Trio 1502500.30285P PP P Bridge Quad 286KTKL High Isolation 2503500.25Unconnected Pair 286L TL L Unconnected Trio 286P TP P Bridge Quad 286R ZZ RRing QuadTest ConditionsI F = 0.1 mA [2]I F = 1.0 mA [2]V R = 0.5V to -1.0V f = 1 MHz [3]Notes:1.Package marking code is laser marked.2.∆V F for diodes in trios and quads is 15.0 mV maximum at 1.0 mA.3.∆C T for diodes in trios and quads is 0.05 pF maximum at -0.5 V.Equivalent Circuit ModelHSMS-285a Series, HSMS-286a Series Single DiodeSPICE ParametersParameterUnits HSMS-285aHSMS-286aB V V 3.87.0C JO pF 0.120.10E G eV 0.690.69I BV A 3 E -4 1 E -5I S A 3 E -6 5 E -8N 1.06 1.08R S Ω30 6.0P B (V J )V0.350.65P T (XTI)22M0.50.5C jR j =8.33 X 10-5 nT I b + I swhereI b = externally applied bias current in ampsI s = saturation current (see table of SPICE parameters)T = temperature, °Kn = identity factor (see table of SPICE parameters)R S = series resistance (see Table of SPICE parameters)Typical Parameters, Single Diode110100110F O R W A R D C U R R E N T (µA )F O R W A R D V O L T AG E D I F F E R E N C E (m V )V O L T A G E O U T (m V )POWER IN (dBm)0.050.150.200.100.25FORWARD VOLTAGE (V)Figure 3. Forward Voltage Match, HSMS-286a Series..01.11101000.10.20.30.40.70.60.80.90.5 1.0F O R W A R D C U R R E N T (m A )FORWARD VOLTAGE (V)Figure 2. Forward Current vs. Forward Voltage at Temperature, HSMS-286a Series.Figure 1. +25°C Forward Current vs. Forward Voltage, HSMS-285a Series.110100100010,000–40–30–100–2010Figure 6. Dynamic TransferCharacteristic as a Function of DC Bias, HSMS-286a .Figure 4. +25°C Output Voltage vs.Input Power, HSMS-285a Series at Zero Bias, HSMS-286a Series at 3 µA Bias.Figure 5. +25°C Expanded Output Voltage vs. Input Power. See Figure 4.535304010152025.1110100O U T P U T V O L T A G E (m V )BIAS CURRENT (µA)Figure 7. Voltage Sensitivity as a Function of DC Bias Current, HSMS-286a .Figure 8. Output Voltage vs.Temperature, HSMS-285a Series.I F – F O R W A R D C U R R E N T (m A )00.01V F – FORWARD VOLTAGE (V)0.8 1.010010.10.2 1.810 1.40.40.6 1.2 1.6V O L T A G E O U T (m V )POWER IN (dBm)V O L TA G E O U T (m V )0.3POWER IN (dBm)10130O U T P U T V O L T A G E (m V)TEMPERATURE (°C)Applications Information IntroductionHewlett-Packard’s HSMS-285L and HSMS-285P zero bias Schottky diodes have been developed specifically for low cost, high volume detector applications where bias current is not available. The HSMS-286L, HSMS-286P and HSMS-286R DC biased Schottky diodes have been developed for low cost, high volume detector applications where stability over temperature is an important design consideration.Schottky Barrier Diode CharacteristicsStripped of its package, a Schottky barrier diode chip consists of a metal-semiconductor barrier formed by deposition of a metal layer on a semiconductor. The most common of several different types, the passivated diode, is shown in Figure 9, along with its equivalent circuit.Figure 9. Schottky Diode Chip.R S is the parasitic series resistance of the diode, the sum of the bondwire and leadframe resistance, the resistance of the bulk layer of silicon, etc. RF energy coupled into R S is lost as heat—it does not contribute to the rectified output of the diode.C J is parasitic junction capacitance of the diode, controlled by the thickness of the epitaxial layer and the diameter of the Schottky contact. R j is the junction resistance of the diode, a function of the total current flowing through it.8.33 x 10-5n TR j == R V – R sI S + I b0.026whereI SI bI SBarriercharacteristics of a Schottkydiode. Barrier height will bealtered, and at the same time C Jand R S will be changed. In general,very low barrier height diodes(with high values of I S, suitable forzero bias applications) are realizedon p-type silicon. Such diodesfjCROSS-SECTION OF SCHOTTKYBARRIER DIODE CHIP CIRCUITR V and C J are very difficult tomeasure. Consider the impedance of C J = 0.12 pF when measured at 1 MHz — it is approximately 1 M Ω.For a well designed zero biasSchottky, R V is in the range of 5 to 25 K Ω, and it shorts out thejunction capacitance. Moving up to a higher frequency enables the measurement of the capacitance,but it then shorts out the video resistance. The best measurement technique is to mount the diode in series in a 50 Ω microstrip test circuit and measure its insertion loss at low power levels (around -20 dBm) using an HP8753C network analyzer. The resulting display will appear as shown in Figure 11.I N S E R T I O N L O S S (d B )FREQUENCY (MHz)Figure 11. Measuring C J and R V .At frequencies below 10 MHz, the video resistance dominates the loss and can easily be calculated from it. At frequencies above 300MHz, the junction capacitance sets the loss, which plots out as a straight line when frequency is plotted on a log scale. Again,calculation is straightforward.L P and C P are best measured on the HP8753C, with the diode terminating a 50 Ω line on theinput port. The resulting tabulation of S 11 can be put into a microwave linear analysis program having the five element equivalent circuit with R V , C J and R S fixed. The optimizer can then adjust the values of L P and C P until the calculated S 11 matches the measured values. Note thatextreme care must be taken to de-embed the parasitics of the 50 Ωtest fixture.Detector CircuitsWhen DC bias is available,Schottky diode detector circuits can be used to create low cost RF and microwave receivers with a sensitivity of -55 dBm to -57dBm.[1] Moreover, since external DC bias sets the video impedance of such circuits, they display classic square law response over a wide range of input power levels [2,3]. These circuits can take a variety offorms, but in the most simple case they appear as shown in Figure 12.This is the basic detector circuit used with the HSMS-286X family of diodes.Where DC bias is not available, a zero bias Schottky diode is used to replace the conventional Schottky in these circuits, and bias choke L 1is eliminated. The circuit then is reduced to a diode, an RFimpedance matching network and (if required) a DC return choke and a capacitor. This is the basic detector circuit used with the HSMS-285a family of diodes.Output voltage can be virtually doubled and input impedance(normally very high) can be halved through the use of the voltage doubler circuit [4].In the design of such detector circuits, the starting point is the equivalent circuit of the diode, as shown in Figure 10. Of interest in the design of the video portion ofthe circuit is the diode’s video impedance —the other fourelements of the equivalent circuit disappear at all reasonable video frequencies. In general, the lowerthe diode’s video impedance, the better the design.RF INFigure 12. Basic Detector Circuits.The situation is somewhat more complicated in the design of the RF impedance matching network,which includes the package inductance and capacitance (which can be tuned out), the series resistance, the junction[1] Hewlett-Packard Application Note 923, Schottky Barrier Diode Video Detectors.[2] Hewlett-Packard Application Note 986, Square Law and Linear Detection.[3] Hewlett-Packard Application Note 956-5, Dynamic Range Extension of Schottky Detectors.[4] Hewlett-Packard Application Note 956-4, Schottky Diode Voltage Doubler.capacitance and the videoresistance. Of these five elements of the diode’s equivalent circuit,the four parasitics are constants and the video resistance is a function of the current flowing through the diode. 26,000R V ≈ I S + I bwhereI S = diode saturation currentin µAI b = bias current in µA Saturation current is a function of the diode’s design,[5] and it is a constant at a given temperature.For the HSMS-285X series, it is typically 3 to 5 µA at 25°C. For the medium barrier HSMS-2860 family,saturation current at room temperature is on the order of 50nA.Together, saturation and (if used)bias current set the detection sensitivity, video resistance and input RF impedance of theSchottky detector diode. Since no external bias is used with theHSMS-285a series, a single transfer curve at any given frequency is obtained, as shown in Figure 4.Where bias current is used, some tradeoff in sensitivity and square law dynamic range is seen, asshown in Figure 6 and described in reference [3].The most difficult part of the design of a detector circuit is the input impedance matching network. A discussion of such circuits can be found in the data sheet for the HSMS-285a /HSMS-286a single SOT-323 detector diodes (Hewlett-Packard publication 5965-4704E).Six Lead CircuitsThe differential detector is often used to provide temperature compensation for a Schottky detector, as shown in Figure 13.Figure 13. Differential Detector.These circuits depend upon the use of two diodes having matched V f characteristics over alloperating temperatures. This is best achieved by using two diodes in a single package, such as the SOT-143 HSMS-2865 as shown in Figure 14.amplifierFigure 14. Conventional Differen-tial Detector.In high power differential detec-tors, RF coupling from the detec-tor diode to the reference diode produces a rectified voltage in the latter, resulting in errors.Isolation between the two diodes can be obtained by using theHSMS-286K diode with leads 2 and 5 grounded. The difference between this product and the conventional HSMS-2865 can be seen in Figure 15.HSMS-2865SOT-143HSMS-286K SOT-3633465411223Figure 15. Comparing Two Diodes.The HSMS-286K, with leads 2 and 5 grounded, offers some isolation from RF coupling between the diodes. This product is used in a differential detector as shown in Figure 16.amplifierFigure 16. High Isolation Differential Detector.In order to achieve the maximum isolation, the designer must take care to minimize the distance from leads 2 and 5 and their respective ground via holes. In addition, the ground structure should isolate the input RF and reference lines, as shown in Figure 17.RF InputFigure 17. Diode Mounting,HSMS-286K.[5] Hewlett-Packard Application Note 969, An Optimum Zero Bias Schottky Detector Diode.Note that the ground strip which runs from the two via holes at the top to the one at the bottom not only provides ground potential for leads 2 and 5, but it isolates the two input/output lines.Tests were run on the HSMS-282K and the conventional HSMS-2825pair, which compare with each other in the same way as theHSMS-2865 and HSMS-286K, with the results shown in Figure 18.O U T P U T V O L T A G E (m V )INPUT POWER (dBm)Figure 18. Comparing HSMS-282K with HSMS-2825.The line marked “RF diode, V out ”is the transfer curve for the detector diode —both theHSMS-2825 and the HSMS-282K exhibited the same output voltage.The data were taken over the 50dB dynamic range shown. To the right is the output voltage (transfer) curve for the reference diode of the HSMS-2825, showing 37dB of isolation. To the right of that is the output voltage due to RF leakage for the reference diode of the HSMS-282K, demonstrating 10dB higher isolation than the conventional part.Such differential detector circuits generally use single diodedetectors, either series or shunt mounted diodes. The voltage doubler (HP Application Note 956-4) offers the advantage of twice the output voltage for a given input power. The two concepts can be combined into the differential voltage doubler, as shown in Figure 19.Figure 19. Differential Voltage Doubler, HSMS-286P.Here, all four diodes of theHSMS-286P are matched in their V f characteristics, because they came from adjacent sites on the wafer. A similar circuit can be realized using the HSMS-286R ring quad.Other configurations of six lead Schottky products can be used to solve circuit design problems while saving space and cost.Thermal Considerations The obvious advantage of the SOT-363 over the SOT-143 is combination of smaller size and two extra leads. However, the copper leadframe in the SOT-363has a thermal conductivity four times higher than the Alloy 42leadframe of the SOT-143, which enables it to dissipate more power.The maximum junction tempera-ture for these three families of Schottky diodes is 150°C under all operating conditions. The follow-ing equation, equation 1, applies to the thermal analysis of diodes:T j = (V f I f + P RF )θjc + T aEquation (1).whereT j = junction temperature T a = diode case temperature θjc = thermal resistance V f I f = DC power dissipated P RF = RF power dissipated Note that θjc , the thermal resis-tance from diode junction to the foot of the leads, is the sum of two component resistances,θjc = θpkg + θchipEquation (2).Package thermal resistance for the SOT-363 package is approxi-mately 100°C/W, and the chip thermal resistance for these three families of diodes is approxi-mately 40°C/W. The designer will have to add in the thermal resistance from diode case toambient —a poor choice of circuit board material or heat sink design can make this number very high.Equation (1) would be straightfor-ward to solve but for the fact that diode forward voltage is a func-tion of temperature as well asforward current. The equation,equation 3, for V f is: 11600 (V f – I f R s ) nTI f= I Se – 1Equation (3).wheren = ideality factor T = temperature in °KR s = diode series resistance and I S (diode saturation current)is given by2 1 1 n – 4060 ( T – 298)I s = I 0 ( T )e 298Equation (4).Equations (1) and (3) are solved simultaneously to obtain the value of junction temperature for given values of diode case temperature,DC power dissipation and RF power dissipation.Temperature Compensation The compression of the detector’s transfer curve is beyond the scope of this data sheet, but somegeneral comments can be made.As was given earlier, the diode’s video resistance is given by 8.33 x 10-5 nTR V =I S + I bwhere T is the diode’s tempera-ture in °K.As can be seen, temperature has a strong effect upon R V , and this will in turn affect video bandwidth and input RF impedance. A glance at Figure 7 suggests that the proper choice of bias current in the HSMS-286a series can mini-mize variation over temperature.The detector circuits described earlier were tested over tempera-ture. The 915MHz voltage doubler using the HSMS-286a series produced the output voltages as shown in Figure 20. The use of 3µA of bias resulted in the highest voltage sensitivity, but at the cost of a wide variation over tempera-ture. Dropping the bias to 1µA produced a detector with much less temperature variation.A similar experiment was con-ducted with the HSMS-286a series in the 5.8GHz detector. Once again, reducing the bias to some level under 3µA stabilized the output of the detector over a wide temperature range.It should be noted that curves such as those given in Figures 20and 21 are highly dependent upon the exact design of the input impedance matching network.The designer will have to experi-ment with bias current using his specific design.Figure 20. Output Voltage vs.Temperature and Bias Current in the 915 MHz Voltage Doubler using the HSMS-286a Series.O U T P U T V O L T A G E (m V )TEMPERATURE (°C)Figure 21. Output Voltage vs.Temperature and Bias Current in the 5.80 GHz Voltage Detector using the HSMS-286a Series.O U T P U T V O L T A G E (m V )TEMPERATURE (°C)TIME (seconds)T E M P E R A T U R E (°C )05010015020025060120180240300Figure 23. Surface Mount Assembly Profile.Diode BurnoutAny Schottky junction, be it an RF diode or the gate of a MESFET, is relatively delicate and can be burned out with excessive RF power. Many crystal video receivers used in RFID (tag)applications find themselves in poorly controlled environments where high power sources may be present. Examples are the areas around airport and FAA radars,nearby ham radio operators, the vicinity of a broadcast band transmitter, etc. In suchenvironments, the Schottky diodes of the receiver can be protected by a device known as a limiterdiode.[6] Formerly available only in radar warning receivers and other high cost electronic warfare applications, these diodes have been adapted to commercial and consumer circuits.Hewlett-Packard offers a complete line of surface mountable PIN limiter diodes. Most notably, our HSMP-4820 (SOT-23) or HSMP-482B (SOT-323) can act as a very fast (nanosecond) power-sensitive switch when placed between the antenna and the Schottky diode,shorting out the RF circuit temporarily and reflecting the excessive RF energy back out the antenna.Assembly InstructionsSOT-363 PCB FootprintA recommended PCB pad layout for the miniature SOT-363 (SC-706 lead) package is shown in Figure 22 (dimensions are in inches). This layout provides ample allowance for packageplacement by automated assembly equipment without addingparasitics that could impair the performance.Figure 22. PCB Pad Layout (dimensions in inches).SMT AssemblyReliable assembly of surface mount components is a complex process that involves manymaterial, process, and equipment factors, including: method of heating (e.g., IR or vapor phase reflow, wave soldering, etc.)circuit board material, conductor thickness and pattern, type of solder alloy, and the thermalconductivity and thermal mass of components. Components with a low mass, such as the SOT-363package, will reach solder reflow temperatures faster than those with a greater mass.HP’s SOT-363 diodes have been qualified to the time-temperature profile shown in Figure 23. Thisprofile is representative of an IR reflow type of surface mount assembly process.After ramping up from room temperature, the circuit board with components attached to it (held in place with solder paste)passes through one or morepreheat zones. The preheat zones increase the temperature of the board and components to prevent thermal shock and begin evaporat-ing solvents from the solder paste.The reflow zone briefly elevates the temperature sufficiently to produce a reflow of the solder.The rates of change of tempera-ture for the ramp-up and cool-down zones are chosen to be low enough to not cause deformation of the board or damage to compo-nents due to thermal shock. The maximum temperature in the reflow zone (T MAX ) should not exceed 235 °C.These parameters are typical for a surface mount assembly process for HP SOT-363 diodes. As ageneral guideline, the circuit board and components should be exposed only to the minimum temperatures and times necessary to achieve a uniform reflow of solder.[6] Hewlett-Packard Application Note 956-4, Schottky Diode Voltage Doubler.11Package DimensionsOutline SOT-363 (SC-70, 6 Lead)0.425 (0.017)0.25 (0.010)0.15 (0.006)0.10 (0.004)DIMENSIONS ARE IN MILLIMETERS (INCHES)Part Number Ordering InformationPart Number No. of Devices ContainerHSMS-28xa-TR2*1000013" ReelHSMS-28xa-TR1*30007" ReelHSMS-28xa-BLK*100antistatic bag* where x = 5 or 6a = L or P for HSMS-285aK, L, P, or R for HSMS-286aDevice OrientationUSER FEEDEND VIEWTOP VIEWNote: “##” represents Package Marking Code. Package marking is right side up with carrier tape perforations at top. Conforms to Electronic Industries RS-481, “Taping of Surface Mounted Components for Automated Placement.” Standard Quantity is3,000Devices per Reel.Tape Dimensions and Product OrientationFor Outline SOT-363 (SC-70, 6 Lead)(COVER TAPE THICKNESS)DESCRIPTION SYMBOL SIZE (mm)SIZE (INCHES)LENGTHWIDTHDEPTHPITCHBOTTOM HOLE DIAMETERA0B0K0PD12.24 ± 0.102.34 ± 0.101.22 ± 0.104.00 ± 0.101.00 + 0.250.088 ± 0.0040.092 ± 0.0040.048 ± 0.0040.157 ± 0.0040.039 + 0.010CAVITYDIAMETERPITCHPOSITIONDP0E1.55 ± 0.054.00 ± 0.101.75 ± 0.100.061 ± 0.0020.157 ± 0.0040.069 ± 0.004PERFORATIONWIDTHTHICKNESSWt18.00 ± 0.300.255 ± 0.0130.315 ± 0.0120.010 ± 0.0005CARRIER TAPECAVITY TO PERFORATION(WIDTH DIRECTION)CAVITY TO PERFORATION(LENGTH DIRECTION)FP23.50 ± 0.052.00 ± 0.050.138 ± 0.0020.079 ± 0.002DISTANCEWIDTHTAPE THICKNESSCT t5.4 ± 0.100.062 ± 0.0010.205 ± 0.0040.0025 ± 0.00004COVER TAPE/go/rfFor technical assistance or the location ofyour nearest Hewlett-Packard sales office,distributor or representative call:Americas/Canada: 1-800-235-0312 or408-654-8675Far East/Australasia: Call your local HPsales office.Japan: (81 3) 3335-8152Europe: Call your local HP sales office.Data subject to change.Copyright © 1998 Hewlett-Packard Co.Obsoletes 5966-2032E5968-2355E (12/98)。

mh88612b中文资料_数据手册_IC数据表

Line interface for:

• PABX • Intercoms • Key Telephone Systems • Control Systems

DS5752

Issue 1

May 2002

Ordering Information

MH88612BV-2 20 Pin SIL Package

A 1.0µF capacitor connected from pin 19 (CAP) to ground will provide adequate attenuation when ringing is applied. Once an off-hook condition has been detected a logic low should be applied to pin 13 (RC) which will deactivate the relay (K1) to disconnect the ringing voltage from pin 11 and reconnect to pin 15. At that time the SLIC will revert to constant current feed operation.

11

RF Ring Feed (Input) is normally connected to Ring relay for negative battery feed voltage

and ringing voltage input.

12

VCC Positive Power Supply Voltage (+5V).

The SLIC can detect an off-hook condition during ringing but there is a large AC component which must be filtered out to give a true off-hook condition at SHK.

MB98D81223资料

2M/4M-BYTE 3 V-ONL Y FLASH MINIATURE CARDThe Fujitsu Flash Miniature cards conform to “Miniature Card Specification” pubulished by MCIF; Miniature Card Implementers Forum.The Fujitsu Flash Miniature cards are small form factor Flash memory cards targeted various markets; digital pho-tography, audio recording, hand held PCs and other small portable equipments. Miniature cards’ high performance, small size (38 mm × 33 mm × 3.5 mm), low cost and simple interface are ideal for portable applications that require high speed flash disk drives or eXecute In Place (XIP).The Flash Miniature cards are 5 V-only operational and allow the users to use as ×8 or ×16 organization on low power at high speed.•Small size: 33.0 mm (length) × 38.0 mm (width) × 3.5 mm (thickness)•+3.3 V power supply program and erase•Command control for Automated Program/Automated Erase operation•Erase Suspend Read/Program Capability•128 KB Sector Erase (at ×16 mode)•Any Combination of Sectors Erase and Full Chip Erase•Detection of completion of program/erase operation with Data# Polling or Toggle bit.•Ready/Busy Output with BUSY#•Reset Function with RESET# pin•Write protect function with WP switch•Low VCC Write Inhibit•AIS (Attribute Information Structure) is available from the address “0000H” of Lower Byte.2MB98D81123/81223-15s PACKAGEs DESCRIPTIONDIFFERENCESMB98D81123MB98D81223 Density 2 MB 4 MB Memory Device8 M bit8 M bit Quantity24 Read 1 B unit←Program 1 B unit←Chip Erase 1 MB unit 1 MB unit Sector Erase64 KB unit←Number of Sectors3264 Erase Suspend Read Yes Yes Erase Suspend Program Yes Yes Address A0 to A19A0 to A20 RESET#Yes Yes BUSY#Yes Yes(CRD-60P-M02)MB98D81123/81223-15s PAD ASSIGNMENTSPad No Symbol Pad No Symbol Pad No Symbol Pad No Symbol 1A1816N.C.31A1946CD#2A1617N.C.32A1747N.C.3A1418OE#33A1548BUSY#4N.C.19D1534A1349WE#5CEH#20D1335A1250D146A1121D1236RESET#51RFU7A922D1037A1052D118A823D938VS1#53VS2#9A624D039A754D810A525D240N.C.55D111A326D441A456D312A227N.C.42CEL#57D513A028D743A158D614N.C.29N.C.44N.C.59N.C.15N.C.30N.C.45N.C.60A20 *EX 1V CC EX 2GND EX 3CINS#* :A20 is “N.C.” for MB98D81123.34MB98D81123/81223-15s PAD DESCRIPTIONS* :T ake notice that those pads are connected internally.s PAD LOCATIONSSymbol I/O Pad Name Symbol I/O Pad Name A0 to A20I Address Input BUSY#O Ready/BusyD0 to D15I/O Data Input/Output CD#O Card Detect *CEL#I Card Enable for Lower Byte VS1#, VS2#O Voltage Sense CEH#I Card Enable for Upper Byte N.C.—Non Connection OE#I Output Enable V CC—Power SupplyWE#I Write Enable GND—GroundRESET#I Hardware Reset CINS#OCard InsertionMB98D81123/81223-15s BLOCK DIAGRAMMB98D8112356MB98D81123/81223-15 MB98D812237MB98D81123/81223-15s CHIP AND SECTOR DECODINGERASE SECTOR DECODING TABLESector Address (SA)A 19A 18A 17A 16Sector 151111Sector 141110Sector 13111Total 16 sectors per 1 chip••••••••••••••••Sector 20010Sector 10001Sector 08MB98D81123/81223-15s CHIP CONFIGURATIONThe miniature cards use 2 or 4 pcs of Flash Memory.•2 pcs of Flash Memory are operated simultaneously at 16 bit mode and even number of chip is applied to lower byte and odd number of chip is applied to upper byte.At ×8 bit mode, even address and odd address are selected with CEL# and CEH#.× 16 bit mode1CEL# = “L”, CEH# = “L”::Odd Number of Chip + Even Number of ChipOdd Number of Chip + Even Number of ChipOdd Number of Chip + Even Number of ChipOdd Number of Chip + Even Number of ChipD15 • • • • • • • • • • • • • • D0003h002h001h000h2× 8 bit modeCEL# = “H”, CEH# = “L”::odd Number of Chipodd Number of Chipodd Number of Chipodd Number of ChipD15 • • • •D8003h002h001h000hCEL# = “L”, CEH# = “H”::even Number of Chipeven Number of Chipeven Number of Chipeven Number of ChipD7 • • • • •D0003h002h001h000hMB98D81123/81223-15s FUNCTION DESCRIPTIONS1.Read ModeThe data in the common can be read with “OE#=VIL” and “WE#=VIH”. The address is selected with A0-A20.And CEL# and CEH# select output mode.2.Standby Mode–CEL# and CEH# at “VIH” place the card in Standby mode. D0-D15 are placed in a high-Z state independent of the status “OE#” and “WE#”.3.Output Disable Mode–The outputs are disabled with OE# and WE# at “VIH”. D0-D15 are placed in high-Z state.4.Write Mode1) Common Memory Write–The card is in Write mode with “OE#=VIH” and “WE# and CE#=VIL”.–Commands can be written at the Write mode.–Two types of the Write mode, “WE# control” and “CE# control” are available.mand Definitions–User can select the card operation by writing the specific address and data sequences into the command register. If incollect address and data are written or improper sequence is done, the card is reseted to read mode. See “COMMAND DEFINISION T ABLE”.6.Automated Program Capability–Programming operation can switch the data from “1” to “0”.–The data is programmed on a byte-by-byte or word-by-word basis.–The card will automatically provide adequate internally generated programming pulses and verify the pro-grammed cell margin by writing four bus cycle operation. The card returns to Common Memory Read mode automatically after the programming is completed.–Addresses are latched at falling edge of WE# or CE# and data is latched at rising edge of WE# or CE#. The fourth rising edge of WE# or CE# on the command write cycle begins programming operation.–We can check whether a byte (word) programming operation is completed successfully by sequence flug with BUSY#, Data# Polling or Toggle Bit function. See “WRITE OPERATION STATUS”.–Any commands written to the chip during programming operation will be ignored.7.Automated Chip Erase Capability–We can execute chip erase operation by 6 bus cycle operation. Chip erase does not require the user to program the chip prior to erase. Upon executing the Erase command sequence the chip automatically will program and verify the entire memory for an all zero data pattern prior to electrical erase. The system is not required to provide any controls or timing during these operations.–The card returns to Common Memory Read mode automatically after the chip erasing is completed.–Whether or not chip erase operation is completed successfully can be checked by sequence flug with BUSY#, Data# Polling or Toggle Bit function. See “WRITE OPERATION STATUS”.–Any commands written to the chip during programming operation will be ignored.910MB98D81123/81223-158.Automated Sector Erase Capability–We can execute the erase operation on any sectors by 6 bus cycle operation.–A time-out of 50 µs (typ.) from the rising edge of the last Sector Erase command will initiate the Sector Erase command(s).–Multiple sectors in a chip can be erased concurrently. This sequence is followed with writes of 30H to addresses in other sectors desired to be concurrently erased. The time between writes 30H must be less than 50 µs, otherwise that command will not be accepted. Any command other than Sector Erase or Erase Suspend during this time-out period will reset the chip to Read mode. The automated sector erase begins after the 50µs (typ.) time out from the rising edge of WE# pulse for the last Sector Erase command pulse. Whether the sector erase window is still open can be monitored with D3 and D11.–Sector Erase does not require the user to program the chip prior to erase. The chip automatically programs “0” to all memory locations in the sector(s) prior to electrical erase. The system is not required to provide any controls or timing during these operations.–The card returns to Common Memory Read mode automatically after the chip erasing is completed.–Whether or not sector erase operation is completed successfully can be checked by sequence flug with BUSY#, Data# Polling or T oggle Bit function. The sequence flug must be read from the address of the sector involved in erase operation. See “WRITE OPERATION STA TUS”.9.Erase Suspend–Erase Suspend command allows the user to interrupt the sector erase operation and then do data reads or program from or to a non-busy sector in the chip which has the sector(s) suspended erase. This command is applicable only during the sector erase operation (including the sector erase time-out period after the sector erase commands 30H) and will be ignored if written during the chip erase or programming operation. Writing this command during the time-out will result in immediate termination of the time-out period. The addresses are “don’t cares” in wrinting the Erase Suspend or Resume commands in the chip.–When the Erase Suspend command is written during a Sector Erase operation, the chip will enter the Erase Suspend Read mode. User can read the data from other sectors than those in suspention. The read operation from sectors in suspention results D2/D10 toggling. User can program to non-busy sectors by writing program commands.–A read from a sector being erase suspended may result in invalid data.10. Intelligent Identifier (ID) Read Mode–Each common memory can execute an Intelligent Identifier operation, initiated by writing Intelligent ID com-mand (90H). Following the command write, a read cycle from address 00H retrieves the manufacture code, and a read cycle from address 01H returns the device code as follows. To terminate the operation, it is necessary to write Read/Reset command.11. Hardware Reset–The Card may be reset by driving the RESET# pin to VIL. The RESET# pin must be kept High (VIL) for at least 500 ns. Any operation in progress will be terminated and the card will be reset to the read mode 20 µs after the RESET# pin is driven Low. If a hardware reset occurs during a program operation, the data at that particular location will be indeterminate.–When the RESET# pin is Low and the internal reset is complete, the Card goes to standby mode and cannot be accessed. Also, note that all the data output pins are High-Z for the duration of the RESET# pulse. Once the RESET# pin is taken high, the Card requires 500 ns of wake up time until outputs are valid for read access.–If hardware reset occurs during a erase operation, there is a possibility that the erasing sector(s) cannot be used.12. Data Protection–The card has WP (Write Protect) switch for write lockout.–To avoid initiation of a write cycle during V CC power-up and power-down, a write cycle is locked out for V CC less than 3.2 V. If V CC < V LKO, the command register is disabled and all internal program/erase circuits are disabled.Under this condition the device will reset to the read mode. Subsequent writes will be ignored until the V CC level is greater than V LKO.It is the users responsibility to ensure that the control pins are logically correct to prevent unintentional writes when V CC is above 3.2 V.–If V CC would be less than V LKO during program/erase operation, the operation will stop. And after that, the operation will not resume even if V CC returns recommended voltage level. Therefore, program command must be written again because the data on the address interrupted program operation is invalid. And regarding interrupting erase operation, there is possibility that the erasing sector(s) cannot be used.–Noise pulses of less than 5 ns (typical) on OE#, CE# or WE# will not initiate a write cycle.s FUNCTION TRUTH TABLEH : “H” level, L : “L ” level , X : “H” or “L ”Note:*1.WPSW = Write Protect Switch, NP = NON-PROTECT, P = PROTECTMode RESET#CEH#CEL#OE#WE#WPSW *1Data Input/Output D8 to D15D0 to D7Hardware ResetLX X X X P or NP High-Z High-Z Standby H H H XXP or NPHigh-Z High-Z Read (×8 bit)H L LHP or NPHigh-Z DOUT L H DOUT High-Z Read (×16 bit)L L DOUT DOUT Write (×8 bit)H L HLNPHigh-Z DIN L H DIN High-Z Write (×16 bit)L L DIN DIN Output DisableHL P High-Z High-Z L H High-Z High-Z LLHigh-ZHigh-Zs COMMAND DEFINITION TABLECommand Table for 8-bit ModeNote:CA:Chip Address.(address in chip selected by A20 for MB98D81223)SA:Sector Address (address in 64 KB selected by A16, A17, A18, A19 and A20)P A:Program Address (address to be programmed)RA:Read Address (address to be read)IA:Intelligent ID read address (Manufacture Code 0000H, Device Code 0001H)PD:Programming data RD:Read dataID:Intelligent Identifier (ID) CodeCommandBusCycle 1st Bus Write Cycle 2nd BusWrite/Read Cycle 3rd BusWrite Cycle 4th BusWrite/Read Cycle5th BusWrite Cycle 6th Bus Write CycleRead/Reset 12Write Read CAF0HRARDRead/Reset 24Write Write Write Read CAAAHCA55HCAF0HRARDRead Intelligent ID Codes 4Write Write Write Read CAAAHCA55HCA90HIAIDByte Program4Write Write Write Write CAAAHCA55HCAA0HPAPDSector Erase 6Write Write Write Write Write Write CAAAHCA55HCA80HCAAAHCA55HSA30HChip Erase 6Write Write Write Write Write Write CAAAHCA55HCA80HCAAAHCA55HCA10HSector Erase Suspend 1Write CAB0HSector Erase Resume 1Write CA30HCommand Table for 16-bit ModeNote:CA:Chip Address.(address in chip selected by A20 for MB98D81223)SA:Sector Address (address in 128 KB selected by A16, A17, A18, A19 and A20)P A:Program Address (address to be programmed)RA:Read Address (address to be read)IA:Intelligent ID read address (Manufacture Code 0000H, Device Code 0001H)PD:Programming data RD:Read dataID:Intelligent Identifier (ID) CodeCommandBusCycle 1st Bus Write Cycle 2nd BusWrite/Read Cycle 3rd BusWrite Cycle 4th BusWrite/Read Cycle5th BusWrite Cycle 6th Bus Write CycleRead/Reset 12Write Read CAF0F0HRARDRead/Reset 24Write Write Write Read CAAAAAHCA5555HCAF0F0HRARDRead Intelligent ID Codes 4Write Write Write Read CAAAAAHCA5555HCA9090HIAIDByte Program4Write Write Write Write CAAAAAHCA5555HCAA0A0HPAPDSector Erase 6Write Write Write Write Write Write CAAAAAHCA5555HCA8080HCAAAAAHCA5555HSA3030HChip Erase 6Write Write Write Write Write Write CAAAAAHCA5555HCA8080HCAAAAAHCA5555HCA1010HSector Erase Suspend 1Write CAB0B0HSector Erase Resume 1Write CA3030Hs WRITE OPERATION STATUSHardware Sequence Flag Table(1): Erase Suspended Sector (2): Non-Erase Suspended SectorNotes:*1.Performing successive read operations from the erase-suspended sector will cause D 2, D 10 to toggle.*2.Performing successive read operations from any address will cause D 6, D 14 to toggle.*3.Reading the byte address being programmed while in the erase-suspend program mode will indicatelogic ‘1’ at the D 2, D 10 bit. However, successive reads from the erase-suspended sector will cause D 2,D 10 to toggle.D7, D15 (Data# Polling)The card features Data# Polling as a method to indicate to the host that the Program/Erase Operation are in progress or completed. During the program operation an attempt to read the program address will produce the compliment of the data last written to D 7/D 15. Upon completion of the program operation, an attempt to read the program address will produce the true data last written to D 7/D 15. During the erase operation, an attempt to read the program address will produce a “0” at the D 7/D 15 output. Upon completion of the erase operation an attempt to read the device will produce a “1” at the D 7/D 15 output.For Chip Erase, the Data# Polling is valid after the rising edge of the sixth WE# pulse in the six write pulse sequence. For sector erase, the Data# Polling is valid after the last rising edge of the sector erase WE# pulse.Even if the device has completed the operation and D 7/D 15 has a valid data, the data outputs on D 0 to D 6/D 8 to D 14 may be still invalid. The valid data on D 0 to D 7/D 8 to D 15 will be read on the successive read attempts.The Data# Polling feature is only active during the programming operation, erase operation, sector erase time-out, Erase Suspend Read mode and Erase Supend Program mode.D6, D14 (Toggle Bit I)The card also features the “Toggle Bit” as a method to indicate to the host system that the Program/Erase Operation are in progress or completed.During an Program or Erase cycle, successive attempts to read (OE# or CE# toggling) data from the card will result in D 6/D 14 toggling between one and zero. Once the Program or Erase cycle is completed, D 6/D 14 will stop toggling and valid data will be read on the next successive attempts. During programming, the Toggle Bit is valid after the rising edge of the fourth WE# pulse in the four write pulse sequence. For chip erase, the Toggle Bit is valid after the rising edge of the sixth WE# pulse in the six write pulse sequence. For sector erase, the Toggle Bit is valid after the last rising edge of the sector erase WE# pulse. The Toggle Bit is also active during the sector time out.Either CE# or OE# toggling will cause the D 6/D 14 to toggle.Status D 7, D 15D 6, D 14D 5, D 13D 3, D 11D 2, D 10BUSY#InProgressProgramming D 7#, D 15#Toggle 0010Erasing0Toggle 01Toggle 0Erase Suspend Read(1)1100Toggle *11(2)Data Data Data Data Data 1Erase Suspend Program D 7#, D 15#T oggle *200*1, *30Exceeded Time LimitsProgrammingD 7#, D 15#Toggle 1010Erasing 0Toggle 11N/A 0Erase Suspend ProgramD 7#, D 15#Toggle1N/AD5, D13 (Exceeded Timing Limits)D5/D13 will indicate if the program or erase time has exceeded the specified limits (internal pulse count). Under these conditions D5/D13 will produce a “1”. This is a failure condition which indicates that the program or erase cycle was not successfully completed. Data# Polling is the only operating function of the card under this condition.If this failure condition occurs during sector erase operation, it specifies that a particular sector is bad and it may not be reused, however, other sectors are still functional and may be used for the program or erase operation.The chip must be reset to use other sectors. Write the Reset command sequence to the chip, and then execute Program or Erase command sequence. This allows the system to continue to use the other active sectors in the chip.If this failure condition occurs during the chip erase operation, it specifies that the entire chip is bad or combination of sectors are bad.If this failure condition occurs during the byte programming operation, it specifies that the entire sector containing that byte is bad and this sector may not be reused, (other sectors are still functional and can be reused).The D5/D13 failure condition may also appear if a user tries to program a non blank location without erasing. In this case the card locks out and never completes the card operation. Hence, the system never reads a valid data on D7/D15 bit and D6/D14 never stops toggling. Once the card has exceeded timing limits, the D5/D13 bit will indicate a “1”. Please note that this is not a device failure condition since the device was incorrectly used.D3, D11 (Sector Erase Timer)After the completion of the initial sector erase command sequence the sector erase time-out will begin. D3/D11 will remain low until the time-out is complete. Data# Polling and Toggle Bit are valid after the initial sector erase command sequence.If Data# Polling or the T oggle Bit indicates the card has been written with a valid erase command, D3/D11 may be used to determine if the sector erase timer window is still open. If D3/D11 is high (“1”) the internally controlled erase cycle has begun; attempts to write subsequent commands to the card will be ignored until the erase operation is completed as indicated by Data# Polling or Toggle Bit. If D3/D11 is low (“0”), the card will accept additional sector erase commands. T o insure the command has been accepted, the system software should check the status of D3/D11 prior to and following each subsequent sector erase command. If D3/D11 were high on the second status check, the command may not have been accepted.Refer to T able: Hardware Sequence Flags.D2, D10This T oggle bit, along with D6, can be used to determine whether the card is in the Erase operation or in Erase Suspend.Successive reads from the erasing sector will cause D2 to toggle during the Erase operation. If the card is in the erase-suspended-read mode, successive reads from the erase-suspended sector will cause D2 to toggle. When the card is in the erase-suspended-program mode, successive reads from the byte address of the non-erase suspended sector will indicate a logic ‘1’ at the D2 bit.D6 is different from D2 in that D6 toggles only when the standard Program or Erase, or Erase Suspend Program operation is in progress.BUSY#The card provides a BUSY# open-drain output pin as a way to indicate to the system that the program or erase operation are either in progress or has been completed. If the output is low, the card is busy with either a program or erase operation. If the card is placed in an Erase Suspend mode, the BUSY# output will be high.During programming, the BUSY# pin is driven low after the rising edge of the fourth WE# pulse. During an erase operation, the BUSY# pin is driven low after the rising edge of the sixth WE# pulse. The BUSY# pin will indicatea busy condition during the RESET# pulse.s PROGRAM/ERASE FLOWCHARTs ABSOLUTE MAXIMUM RATINGS *1*1.Permanent device damage may occur if the above Absolute Maximum Ratings are exceeded. Functionaloperation should be restricted to the conditions as detailed in the operational sections of this data sheet.Exposure to absolute maximum rating conditions for extended periods may affect device reliability.s RECOMMENDED OPERATING CONDITIONSs DC CHARACTERISTICSNotes:*1.This value does not apply to CEL#, CEH# and WE#.*2.This value does not apply to CD# and CINS#.ParameterSymbol Value Unit Supply Voltage V CC –0.5 to +5.5V Input Voltage V IN –0.5 to V CC +0.5V Output VoltageV OUT –0.5 to V CC +0.5V Temperature under Bias T A 0 to +60°C Storage T emperatureT STG–30 to +70°CParameterSymbol Min Typ Max Unit V CC Supply Voltage V CC 3.1353.30 3.465V GroundGND 0V Ambient T emperatureT A055°CParameterTest ConditionsSymbol ValueUnit MinTypMax Input Leakage Current *1V CC = V CC max., V IN = GND or V CCI LI ±10µA Output Leakage Current *2V CC = V CC max., V IN = GND or V CC I LO ±10µA Standby CurrentCEL#, CEH#,RESET# = V CC ±0.3 V I SB1—1070µA CEL#, CEH#, RESET# = V IHI SB2 5.0mA Active Read Current V CC = V CC max., CEL#, CEH# = V IL Cycle = 150 ns, I OUT = 0 mA I CC15080mA Program Current Program in progress (×16 mode)I CC260100mA Erase Current Erase in progress (×16 mode)I CC360100mA Input Low Voltage —V IL –0.5—0.6V Input High Voltage —V IH 0.7 V CC—V CC +0.5V Output Low Voltage I OL = 4.0 mA, V CC = V CC min.V OL 0.45V Output High Voltage I OH = –2.0 mA, V CC = V CC min.V OH 2.4V Low V CC Lock-out Voltage—V LKO2.3—2.5Vs CAPACITANCE (T A = 25°C, f = 1 MHz, V IN = V I/O = GND)Parameter Symbol Min Max Unit Input Capacitance *1C IN40pF I/O Capacitance *2C I/O40pF Notes:*1.This value does not apply to CEL#, CEH# and WE#.*2.This value does not apply to VS1#, CD# and CINS#.s AC TEST CONDITIONS•Input Pulse Levels: V IH = 3.0 V, V IL = 0.0 V•Input Pulse Rise and Fall Times: 5 ns•Timing Reference LevelsInput: V IL = 1.5 V, V IH = 1.5 VOutput: V OL = 1.5 V, V OH = 1.5 VOutput Load: 1TTL +100 pFs PROGRAM AND ERASE PERFORMANCESParameter Min Typ Max Unit Byte Program Time *183600µs Chip Programming Time *18.4T.B.D.Sec. Sector Erase Time *2115Sec. Program/Erase Cycles100,000Cycles Notes:*1.Excludes system-level overhead.*2.Excludes 00H programming prior to erasure.s AC CHARACTERISTICS(Recommended operating conditions unless otherwise noted.)READ CYCLE *1Parameter Symbol Min Max Unit Read Cycle Time t RC150ns Card Enable Access Time t CE150ns Address Access Time t ACC150ns Output Enable Access Time t OE75ns Card Enable to Output in Low-Z *2t CLZ5ns Card Disable to Output in High-Z *2t CHZ75ns Output Enable to Output in Low-Z *2t OLZ5ns Output Disable to Output in High-Z *2t OHZ60ns Output Hold from Address Change t OH0ns Ready Time from RESET#t RDY20µs Notes:*1.Rise/Fall time < 5 ns.*2.T ransition is measured at the point of ±500 mV from steady state voltage.PROGRAM/ERASE CYCLENotes:*1.These do not include the preprogramming time.*2.Not 100% tested.ParameterSymbol Min TypMaxUnit Write Cycle Time t WC 150ns Address Setup Time t AS 20ns Address Hold Time t AH 20ns Data Setup Time t DS 50ns Data Hold Timet DH 20ns Read Recovery Time (WE# control)t GHWL 10ns Read Recovery Time (CE# control)t GHEL 10ns Output Enable Hold Time t OEH 10ns Card Enable Setup Time t CS 0ns Card Enable Hold Time t CH 10ns Write Enable Pulse Width t WP 80ns Write Enable Setup Time t WS 0ns Write Enable Hold Time t WH 10ns Card Enable Pulse Widtht CP 100ns Duration of Byte Program Operation (/WE Control)t WHWH18µs Duration of Erase Operation *1 (/WE Control)t WHWH2115s Duration of Byte Program Operation (/CE Control)t EHEH18µs Duration of Erase Operation *1(/CE Control)t EHEH2115s V CC Setup Time *2t VCS 50µs Reset Pulse Width t RP 500ns Busy Delay Timet BSY90nss TIMING DIAGRAMREAD CYCLE TIMING DIAGRAM (WE# = V IH, RESET# = V IH)READ CYCLE TIMING DIAGRAM (continued) (WE# = V IH, RESET# = V IH)READ CYCLE TIMING DIAGRAM (continued) (WE# = V IH, RESET# = V IH)3132PROGRAM CYCLE TIMING DIAGRAM (WE# = CONTROLLED, RESET# = V IH)Notes:*1.See “FUNCTION TRUTH TABLE”.*2.PCMA1/PCMA2 = Command Address for Program, PA = Program Address, PD = Program Data. See “COMMAND DEFINITION TABLE”.PROGRAM CYCLE TIMING DIAGRAM (CE# = CONTROLLED, RESET# = V IH)Notes:*1.See “FUNCTION TRUTH TABLE”.*2.PCMA1/PCMA2 = Command Address for Program, PA = Program Address, PD = Program Data. See “COMMAND DEFINITION TABLE”.3334ERASE CYCLE TIMING DIAGRAM (WE# = CONTROLLED, RESET# = V IH)Notes:*1.See “FUNCTION TRUTH TABLE”.*MA1/CCMA2 = Command Address for Chip Erase, SCMA1/SCMA2 = Command Address for Sector Erase, SA = Sector Address. See “COMMAND DEFINITION TABLE”.ERASE CYCLE TIMING DIAGRAM (CE# = CONTROLLED, RESET# = V IH)Notes:*1.See “FUNCTION TRUTH TABLE”.*MA1/CCMA2 = Command Address for Chip Erase, SCMA1/SCMA2 = Command Address for Sector Erase, SA = Sector Address. See “COMMAND DEFINITION TABLE”.3536DATA# POLLING CYCLE TIMING DIAGRAM (RESET# = V IH)Notes:*1.VA = PA for Programming Cycle, VA = SA for Sector Erase, VA = CA for Chip Erase.*2.See “FUNCTION TRUTH TABLE”.*3.t EHEH1,2 for CE# Control.*4.Program/Erase operation is finished.。

PS2861H-1-F3-A,PS2861H-1-A, 规格书,Datasheet 资料

FEATURES• LONG INSULATION DISTANCE: 0.4 mm MIN.• HIGH CURRENT TRANSFER RATIO: CTR = 200% TYP• SMALL AND THIN PACKAGE Half-pitch 4-pin SOP , 1.27 mm • HIGH ISOLATION VOLTAGE: 3,000 V r.m.s.• TAPING PRODUCT NUMBERPS2861H-1-F3/F4 :3 500 pcs/reelDESCRIPTIONNEC's PS2861H-1 is an optically coupled isolator containing a GaAs light emitting diode and an NPN silicon phototran-sistor. This is a half-pitch SOP (Small Out-line Package) for high density mounting surface mountable applications. This is ideal for implementing highly isolated interface, 3kVrms in accordance with international safety standards.• SWITCHING MODE POWER SUPPLY • MODEM, FAX AND TELEPHONE• DATA INTERFACE OF DIFFERENT POTENTIALSPART NUMBER PS2861H-1SYMBOLSPARAMETERSUNITS MINTYP MAX DiodeV F Forward Voltage, I F = 5 mA V 1.15 1.4I R Reverse Current, V R = 5 VμA 5C tJunction Capacitance, V= 0, f = 1 MHzpF 15Transistor I CEO Collector to Emitter Dark Current, I F = 0 mA, V CE = 40 V nA 100CoupledV ECO(Sat)Collector Saturation Voltage, I F = 5 mA, I C = 2 mA V 0.3CTR Current Transfer Ratio, I F = 5 mA, V CE = 5 V %50200400CTR Current Transfer Ratio, I F = 1 mA, V CE = 5 V %25135270R I-O Isolation Resistance, V I-O = 1 k V DC Ω1011C I-O Isolation Capacitance, V = 0 V, f = 1 MHz pF 0.4t r Rise Time, V CC = 5 V, I C = 2 mA, R L = 100 Ωμs 4t fFall Time, V CC = 5 V, I C = 2 mA, R L = 100 Ωμs6ELECTRICAL CHARACTERISTICS (T A = 25°C, Unless otherwise specified)APPLICATIONDate Published: July 17, 2006The information in this document is subject to change without notice. Before using this document, please confirmthat this is the latest version.ABSOLUTE MAXIMUM RATINGS 1 (T A = 25°C)Notes:1. Operation in excess of any one of these parameters may result in permanent damage.2. PW = 100 µs, duty cycle = 1%.3. AC voltage for 1 minute at T A = 25 °C, RH = 60 % between input and ouput.PART NUMBERSYMBOLSPARAMETERS RATING UNIT DiodeV F Forward Voltage 50mA I R Reverse Current 6V P DPower Dissipation 60mW Transistor ΔP D /ºC Power Dissipation Derating0.6mW/ºC CoupledI FP Peak Forward Current 20.5A V CEO Collector to Emitter Voltage40V V ECO Emitter to Collector Voltage5VI C Collector Current 40mA P C Power Dissipation 120mW ΔP C /ºC Power Dissipation Derating 1.2mW/ºC BV Isolation Voltage 33,000V r.m.s.P T Total Power Dissipation 170mW T A Operating Temperature -55 to 100ºC T stgStorage Temperature-55 to 150ºCLife Support ApplicationsThese NEC products are not intended for use in life support devices, appliances, or systems where the malfunction of these products can reasonably be expected to result in personal injury. The customers of CEL using or selling these products for use in such applications do so at their own risk andagree to fully indemnify CEL for all damages resulting from such improper use or sale.A Business Partner of NEC Compound Semiconductor Devices, Ltd.Pin Connection (Top View)1. Anode 2. Cathode 3. Emitter 4. Collector1.271PS2861H-1OUTLINE DIMENSIONS (Units in mm)PART NUMBER PACKAGE PACKING STYLE APPLICATION PART NUMBER PS2861H-14-pin SOPMagazine case 100 pcs PS2861H-1PS2861H-1-F3Embossed Tape 3500 pcs/reelPS2861H-1-F4ORDERING INFORMATION (Solder Contains Lead)PART NUMBER PACKAGE PACKING STYLE APPLICATION PART NUMBER PS2861H-1-A 4-pin SOPMagazine case 100 pcs PS2861H-1PS2861H-1-F3-A Embossed Tape 3500 pcs/reelPS2861H-1-F4-AORDERING INFORMATION (Pb-Free)4590 Patrick Henry DriveSanta Clara, CA95054-1817Telephone: (408)919-2500Facsimile:(408) 988-0279Subject:Compliance with EU DirectivesCEL certifies, to its knowledge, that semiconductor and laser products detailed below are compliant with the requirements of European Union (EU) Directive 2002/95/EC Restriction on Use of Hazardous Substances in electrical and electronic equipment (RoHS) and the requirements of EU Directive 2003/11/EC Restriction on Penta and Octa BDE.CEL Pb-free products have the same base part number with a suffix added. The suffix –A indicates that the device is Pb-free. The –AZ suffix is used to designate devices containing Pb which are exempted from the requirement of RoHS directive (*). In all cases the devices have Pb-free terminals. All devices with these suffixes meet the requirements of the RoHS directive.This status is based on CEL’s understanding of the EU Directives and knowledge of the materials that go into its products as of the date of disclosure of this information.Restricted Substanceper RoHS Concentration Limit per RoHS(values are not yet fixed)Concentration containedin CEL devices-A-AZLead (Pb)< 1000 PPM Not Detected(*) Mercury< 1000 PPM Not Detected Cadmium< 100 PPM Not Detected Hexavalent Chromium< 1000 PPM Not DetectedPBB< 1000 PPM Not DetectedPBDE< 1000 PPM Not DetectedIf you should have any additional questions regarding our devices and compliance to environmental standards, please do not hesitate to contact your local representative.Important Information and Disclaimer: Information provided by CEL on its website or in other communications concerting the substance content of its products represents knowledge and belief as of the date that it is provided. CEL bases its knowledge and belief on information provided by third parties and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. CEL has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. CEL and CEL suppliers consider certain information to be proprietary,and thus CAS numbers and other limited information may not be available for release.In no event shall CEL’s liability arising out of such information exceed the total purchase price of the CEL part(s) at issue sold by CEL to customer on an annual basis.See CEL Terms and Conditions for additional clarification of warranties and liability.。

华邦(winbond)产品手册

PRODUCT GUIDE ==Winbond、ISSI 授权香港及中国代理== 8 位单片宽工作电压系列

型号 ROM 型式 ROM RAM I/O 脚 外扩存储 器空间 64K 工作电压 定时器/ 计数器 3 封装 Int 特殊功能 PDIP 6 CMOS 通用功能 特殊 I/O 口 /INT2, /INT3,WDT 特殊 I/O 口 /INT2, /INT3,WDT 16 KB 掩膜 ROM W78L54 掩膜 16K 256 32/36 64K 5.5V - 1.8V 3 8 特殊 I/O 口 /INT2,/INT3,WDT W78L801 掩膜 4K 256 36 64K 5.5V - 1.8V 2 12 特殊 I/O 口,P1 口 退出省电方式 WDT 可多次编程,特殊 I/O 口 / INT2, /INT3, WDT 可多次编程特殊 I/O 口 / INT2, /INT3, WDT 可多次编程特殊 I/O 口 / INT2, /INT3, WDT 可多次编程,可在线编程 特殊 I/O 口/ INT2, /INT3 可多次编程,可在线编程 W78LE516 Flash EPROM 64K 512 32/36 64K 5.5V - 2.4V 3 8 特殊 I/O 口,/ INT2, /INT3, 可多次编程,可在线编程 W78LE365 Flash EPROM 64K 1280 32/36 64 K 5.5V - 2.4V 3 8 特殊 I/O 口/ INT2, /INT3,WTD,PWM 特殊 I/O 口 W78LE812 Flash EPROM 8K 256 36 64K 5.5V - 2.4V 3 14 P1 口退出省电方式 WDT,UART 40 44 44 40 44 44 40 44 44 40 44 44 40 44 44 40 PLCC 44 PQFP 44

EMS22P30-M25-LS6中文资料(bourns)中文数据手册「EasyDatasheet - 矽搜」

电气特性

解析度................................................................................................................................................................................................................ 1024国 绝缘电阻(500 VDC) ......................................................................................................................................................................1,000兆欧 电气行程........................................................................................................................................................................................................续 电源电压........................................................................................................................................................................5.0 VDC±10%,3.3 VDC±10% 电源电流.................................................................................................................................................................................................20 mA(最大值)

MB3771中文资料

s RECOMMENDED OPERATING CONDITIONS

Parameter Power supply voltage Output current Operating ambient temperature Symbol VCC IRESET IOUTC Top Value Min. 3.5 0 0 −40 Max. 18 20 6 +85 Unit V mA mA °C

−

Comp. C

VSC

+

VSB / RESIN 6

−

Comp. B

S 4 1 CT 8 3 GND

RESET OUTC

2

元器件交易网

MB3771

s FUNCTIONAL DESCRIPTIONS

Comparators Comp.A and Comp.B apply a hysteresis to the detected voltage, so that when the voltage at either the VSA or VSB pin falls below 1.23 V the RESET output signal goes to “low” level. Comp. B may be used to detect any given voltage(Sample Application 3), and can also be used as a forced reset pin (with reset hold time) with TTL input (Sample Application 6). Note that if Comp.B is not used, the VSB pin should be connected to the VCC pin (Sample Application 1). Instantaneous breaks or drops in the power supply can be detected as abnormal conditions by the MB3771 within a 2 µs interval. However because momentary breaks or drops of this duration do not cause problems in actual systems in some cases, a delayed trigger function can be created by connecting capacitors to the VSA or VSB pin (Sample Application 8). Because the RESET output has built-in pull-up resistance, there is no need to connect to external pull-up resistance when connected to a high impedance load such as a CMOS logic IC. Comparator Comp. C is an open-collector output comparator without hysteresis, in which the polarity of input/ output characteristics is reversed. Thus Comp. C is useful for over-voltage detection (Sample Application 11) and positive logic RESET signal output (Sample Application 7), as well as for creating a reference voltage (Sample Application 10). Note that if Comp. C is not used, the VSC pin should be connected to the GND pin (Sample Application 1).

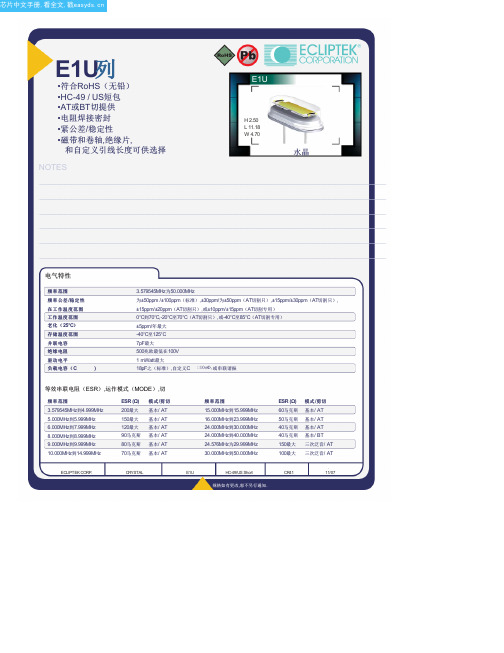

E1UAA20-16.257M中文资料(ECLIPTEK)中文数据手册「EasyDatasheet - 矽搜」

E1U列•符合RoHS(无铅)•HC-49 / US短包•AT或BT切提供•电阻焊接密封•紧公差/稳定性•磁带和卷轴,绝缘片,和自定义引线长度可供选择NOTES H 2.50L 11.18W 4.70水晶_____________________________________________________________________________________________________________________________________________________________________________________________ _____________________________________________________________________________________________________________________________________________________________________________________________ _____________________________________________________________________________________________________________________________________________________________________________________________ _____________________________________________________________________________________________________________________________________________________________________________________________ _____________________________________________________________________________________________________________________________________________________________________________________________ _____________________________________________________________________________________________________________________________________________________________________________________________ _____________________________________________________________________________________________________________________________________________________________________________________________ _____________________________________________________________________________________________________________________________________________________________________________________________ _____________________________________________________________________________________________________________________________________________________________________________________________ _____________________________________________________________________________________________________________________________________________________________________________________________ _____________________________________________________________________________________________________________________________________________________________________________________________ _____________________________________________________________________________________________________________________________________________________________________________________________电气特性频率范围频率公差/稳定性在工作温度范围温度范围工作温度范围老化(25°C)存储温度范围并联电容绝缘电阻驱动电平负载电容(C)3.579545MHz为50.000MHz为±50ppm /±100ppm(标准),±30ppm/为±50ppm(AT切割只),±15ppm/±30ppm(AT切割只),±15ppm/±20ppm(AT切割只),或±10ppm/±15ppm(AT切割专用)0°C到70°C,-20°C至70°C(AT切割只),或-40°C至85°C(AT切割专用)±5ppm/年最大-40°C至125°C7pF最大500兆欧最低在100V1 mWatt最大18pF之(标准),自定义C 10pF,或串联谐振等效串联电阻(ESR),运作模式(MODE),切频率范围3.579545MHz到4.999MHz5.000MHz到5.999MHz6.000MHz到7.999MHz8.000MHz到8.999MHz9.000MHz到9.999MHz10.000MHz到14.999MHz ESR (Ω)200最大150最大120最大90马克斯80马克斯70马克斯模式/剪切基本/ AT基本/ AT基本/ AT基本/ AT基本/ AT基本/ AT频率范围15.000MHz到15.999MHz16.000MHz到23.999MHz24.000MHz到30.000MHz24.000MHz到40.000MHz24.576MHz为29.999MHz30.000MHz到50.000MHzESR (Ω)60马克斯50马克斯40马克斯40马克斯150最大100最大模式/剪切基本/ AT基本/ AT基本/ AT基本/ BT三次泛音/ AT三次泛音/ AT.ECLIPTEK CORP.CRYSTAL E1U HC-49/US Short CR4111/07零件编码指南E1U A A 18 - 20.000M - I2 TR频率公差/稳定性A =±50PPM 25°C时,±0℃至100ppm70℃B =±50PPM,在25°C,±100ppm-20℃至70℃C =±50PPM,在25°C,±100ppm温度范围为-40°C至85°CD =±30ppm25°C时,±0℃50PPM至70℃E =±30ppm25°C时,为±50ppm -20℃至70℃F =±30ppm25°C时,为±50ppm -40°C至85°CG =±15ppm25°C时,±0℃为30ppm至70℃H =±15ppm25°C时,±30ppm-20℃至70℃J =±15ppm25°C时,±30ppm温度范围为-40°C至85°C K =±15ppm25°C时,±0℃为20ppm至70℃L =±15ppm25°C时,±20ppm-20℃至70℃M =±15ppm25°C时,±20ppm温度范围为-40°C至85°C N =±10ppm25°C时,±0℃为15ppm至70℃P =±10ppm25°C时,±15ppm-20℃至70℃包装选择空白=散装,A =盘,TR =卷带式可选项空白=无(标准)CX =自定义引线长度I2 =绝缘子标签频率负载电容S =系列X X = X X pF(自定义)动作模式/水晶切割A =基本/ A TB =三次泛音/ A TD =基本/ BT外形尺寸ALL DIM ENSIONS IN M ILLIM ET ERS 卷带尺寸ALL DIM ENSIONS IN M ILLIM ET ERS环境/机械特性PARAMET ER SPECIFICAT ION 标记规格1000 Pieces per ReelCompliant to EIA-468B精细泄漏测试总泄漏测试铅完整铅端接机械冲击耐焊接热抗溶剂可焊性温度循环振荡M IL-STD-883,方法1014,条件AM IL-STD-883,方法1014,条件CM IL-STD-883 2004方法锡2微米 - 6微米M IL-STD-202,方法213,条件CM IL-STD-202,方法210M IL-STD-202,方法215M IL-STD-883,2002年法M IL-STD-883,法1010M IL-STD-883,方法2007,条件A1号线:电子X X.X X X中号Frequency in MHz(5 Digits Maximum + Decimal).ECLIPTEK CORP.CRYSTAL E1U HC-49/US Short CR4111/07。

bp2861规格书

bp2861规格书样本

BP2861是一款降压型LED恒流驱动芯片,采用SOP7封装,芯片工作在电感电流临界连续模式,适用于5Vac~265Vac 全范围输入电压的非隔离降压型LED恒流电源,芯片内部集成500V功率开关,采用栅极退磁检测技术和高压JFET供电技术,无需VCC 电容和启动电阻,使其外围器件更简单,节约了外围的成本和体积。

BP2861芯片采用内置高精度的电流采样电路和恒流控

制技术,实现高精度的 LED 恒流输出和优异的线电压调整率。

芯片工作在电感电流临界模式,输出电流不随电感量和LED 工作电压的变化而变化,实现优异的负载调整率。

降压led驱动芯片BP2861具有多重保护功能,包括LED 短路保护,芯片供电欠压保护,芯片温度过热调节等。

非隔离降压型LED恒流驱动芯片BP2861特点;

与BP2866X引脚兼容

集成600V 超快恢复二极管

无VCC 电容、无启动电阻

集成高压供电功能

低母线电压下不闪灯

多灯并联无闪烁

±5%LED 输出电流精度

LED 短路保护

过热调节功能(ic温度达到140°)

主要应用;

LED蜡烛灯、LED 球泡灯、其它 LED 照明BP2861芯片管脚(引脚封装及描述)。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

10 nAx

10 nBx

High voltage level Low voltage level Don’t care High impedance “off” state

nOEBA

August 27, 1993

2

元器件交易网

Philips Semiconductors Advanced BiCMOS Products Product specification

LOGIC SYMBOL (IEEE/IEC)

46 47 EN1(BA) EN2(AB)

21 20 EN1(BA) EN2(AB)

45

1 2

48

33

1 2

8

44 42 41 39 38 37 36 35 34

49 50 51 1 2 3 5 6 7

32 31 29 28 27 25 24 23 22

• ESD protection exceeds 2000 V per MIL

STD 883 Method 3015 and 200 V per Machine Model

• Provides high performance bus interface

QUICK REFERENCE DATA