A63L73361中文资料

L7386A中文资料

18

Telephone: 781-935-4442 Fax: 781-938-5867

sales@ Engineering Catalog 169

索诺泰克超声刀可切割的材料示例说明书

FB-0131-6LFB -3186-4L FB -0231-6L ---FB -3236-6L FB -3234FB -3136-6L4FB -3136-5H FB -3126-3L FB -3134FB -4136-1WSH-3510SF-3441SF-3400ⅡSF-30SF-0102SF-653 TechnologyWe own a patent for the blade holding system.Notations used in this leaflet :The ultrasonic cutter is a safe and clean processing machine that does not discharge cutting chips, polluted water, noise or smoke. The cutting blade performs expansion and contraction movements at an ultrafast speed of 20,000 times or over per second with the amplitude of up to 70 microns.As a result, it can cut the materials that are usually hard to cut easily and beautifully.The SONOFILE ultrasonic cutter, utilizing ultrasonic vibrations of a specialized processing machine manufacturer SONOTEC features excellent durability and smooth operability as well by employing our own blade holding system.We will test-cut free of charge if a work sample is provided.We will choose thecombination of the oscillator and the transducer, which are optimum for the intended material and the cuttingconditions.With our knowledge and experience accumulated for a long period, we will propose the ultrasonic cutters that bestfit the customer.Check the sharpness of our cutter through the test cutting.For use with automated equipment M echanism that the cord and the air tube rotate Detachable cord( For details, see Page 5. )For use with manual equipment Product conforming to CEFeaturesFeaturesHigh-power Ultrasonic Cutter featuring Maximum Output of 500 W◎ Cutter with a maximum power output of 500 W capable of handling materials requiring high-power cutting.◎ Tools including carbide blades and long blades can be used.◎ Mountable on automated machinery, industrial robots and plotters.◎ Various types of prepregs (boron, Kevlar, polyethylene fibers, etc.)◎ Rubber (vulcanized latex, non-vulcanized latex, sheetingmaterials, sealing materials and tubes) and leather (natural and artificial)◎ Thermoplastics (boards, sheeting materials, films, laminated materials, flooring materials)◎ Fabric materials, nonwoven fabrics and paper (specially-treated paper and coated paper)The oscillator with a maximum power output of 500 W enabled powerful cutting of difficult-to-cut and extra-tough work pieces. Abrasion resistant carbide blade with 1 mm thickness can be used. Exchanging signals for on/off, emergency stop, change of output level, and other features with automated machinery or industrial robots is, of course, possible.◎ Cutter with a maximum power output of 500 Wcapable of handling materials requiring high-power cutting.◎ Tools including carbide blades and long blades can beused.◎ Mountable on automated machinery, industrial robotsand plotters.Features◎ Powerful ultrasonic cutter with a maximum poweroutput of 300 W.◎ Mountable on automated machinery, industrial robotsand plotters.FeaturesSH -3510SF -3441Standard Model for Use with Automated MachineryThis ultrasonic oscillator is capable of exchanging signals with the main units of automated machinery, industrial robots, plotters, etc., for operations, such as turning on/off, emergency stop and switching the output level.Frequency adjustment Automatic tracking type Maximum output 500 WOutput adjustment Step-less continuously-variable type Power requirement Single phase 200 VAC, 50/60 Hz Power consumption 1000VAOuter dimensions300 (W) x 400 (D) x 200 (H) (mm)Weight 10.2kgFunctionDetection of error causeExternal deviceconnection functionOscillation ON/OFF, Adjustment of ultrasonic output, Warning of error stop, Recovery from errorFrequency adjustmentAutomatic tracking type Maximum output 300 WOutput adjustment Step-less continuously-variable type Power requirement Single phase 200 VAC, 50/60 Hz Power consumption 500 VAOuter dimensions 232 (W) x 340 (D) x 170 (H) (mm)Weight6.5 kgExternal deviceconnection functionOscillation ON/OFF, Adjustment of ultrasonic output, Warning of error stopSpecificationsSpecificationsfor 3510for SH -3510SF -3441-8701SF -3110-8500RRThis is a large amplitude type where theblade vibration amplitude is made larger than conventional models. With a 42 mm diameter cylindrical shape, the model is easy to be mounted on automated machinery, industrial robots and plotters. It is best suited forcutting and punching processing of 3D parts by mounting on industrial robots, in addition to processing of sheets and punching.The transducer generates powerful and stable vibrations even for cutting that requires high power, and the profile is designed to endure long-term use.The main body of the transducer is a cylindrical duralumin case that is easy for mounting on automated machinery. The blade width can be selected according to applications, which enables to design the blade that fits the profile of the article to be machined. Particularly, the transducer is best fit to up-and-down push cutting (guillotine system) and punching.The transducer features compact size, but powerful performance thanks to the high frequency drive, thereby ensuring sharp cutting. The user-friendly design of shape enables to fully utilize the robot’s operation area. A forced air-cooling system andextended continuous use have been realized by featuring the air inlet.-81108541RRThe transducer is suitable for gate cutting of molded articles containing glass or carbon fibers, which are hard to cut or machine in the past.*The total length varies depending on the tool on which the transducer is mounted.*We can make varioustypes of custom-order punching tools.Punching SampleFrequency24 kHz Cord length Up to 10 mHousing material SUS303 / Resin (Duracon)Outer dimensions φ12 / φ23 / φ55 x 221L (mm)Weight 1,160 g Blade thickness1.0 mmFrequency20 kHz Cord length Up to 10 m Housing material SUS303Outer dimensions φ42 / φ55 x 269L (mm)Weight 1,600 g (excluding the cord)Blade thicknessThe thickness depends on the specifications.Frequency20 kHz Cord length Up to 10 m Housing material Aluminum alloyOuter dimensions φ16 / φ46 x 168.5 L (mm)Weight 600 g (excluding the cord)Blade thicknessThe thickness depends on the specifications.FB -4221-9FB -0231-6L FB -0131-6LStandard ToolsOptional ToolStandard ToolsFB -3136-6L4FB -3296-1SpecificationsSpecificationsSpecificationsFrequency22 kHz Cord length Up to 10 m Housing material SUS 303Outer dimensions Hexagonal 11 / φ42 x 175L (mm)Weight650 gBlade thicknessThe thickness depends on the specifications of holder (0.4 to 1.0 mm)SpecificationsStandard ToolsFB -3136-5HFrequency40 kHz Cord length Up to 10 m Housing material SUS 303Outer dimensionsφ10 / φ26 / φ42 x 175 L (mm)Weight 650 g Blade thickness0.6 mmSpecifications220.81106743.8φ55φ23( Unit : mm )( Unit : mm )1751162237φ42( Unit : mm )( Unit : mm )( Unit : mm )φ12Angle type49271758822382710φ26φ4211094269φ55φ42137.5168.531306FB-3234FB-3294-2◎ Stable vibrations with a maximum amplitude of 30microns ensure remarkable cutting performance.◎ Our unique technologies suppress the heat generationof transducers, thus enabling extended continuoususe.◎ Adoption of the exclusive square-head screws and thescrewdriver ensures easy and robust mounting of tools.Features◎ An ultrasonic cutter featuring the size convenient forcarrying around.◎ The transducer is provided with a hand switch and theactivation of operation is notified with illuminationand sound◎ The cutter can also be used as a versatile machine forcutting various materials.FeaturesThis is a manual type ultrasonic cutter, which daringly pursued niceuser-friendliness. It is provided with a portable handle and storagerack for use at various jobsites. It is best fitted for a wide range ofapplications including carbon prepregs, resins, rubber, and fabrics. Forsafety measures, the activation of ultrasonic vibration is reported withillumination and sound. The product complies with the CE Standard.This is a high-frequency cutter featuring the 40 kHz (40,000 vibrationsper second) vibration frequency of tool with the amplitude of 30 microns.It maximizes the effect of ultrasonic high-speed micro vibrations. A widerange of materials, including newly developed composite materials,rubber and leather, can be cut at will with low processing pressure, sharpcutting surface and little cutting chips. The power control circuit speciallydeveloped by us and the cooling air inlet suppress the heat generation oftransducer even for large amplitude, thus enabling extended continuoususe. (For a long-time operation without air cooling, contact us.)◎ Rubber (vulcanized latex, non-vulcanized latex, sheetingmaterials, sealing materials and tubes) and leather(natural and artificial)◎ Thermoplastics (boards, sheeting materials, films,laminated materials, flooring materials)◎ Fabric materials, nonwoven fabrics, and paper (specially-treated paper and coated paper)Specifications: Oscillator653TransducerFrequency40KHzCord length Up to 10 mHousing material SUS 303Outer dimensionsφ10/φ30×139.5L(mm)Weight300 g (excluding the cord)Blade thicknessThe thickness depends on the specifications ofthe holder. ( 0.4 mm / 0.5 mm / 0.6 mm )Frequency22 kHzCord length 3 mHousing material Resin (Duracon)Outer dimensions Hexagonal 11 / φ40 x 155L (mm)Weight350 gBlade thickness0.4 mmFrequency adjustment Automatic tracking typeMaximum output /Output adjustment100 W / Step-less continuously-variable typePower requirement Single phase 200 VAC, 50/60 HzPower consumption300 VAOuter dimensions230 (W) x 232 (D) x 144 (H) (mm)Weight 4.6 kgExternal deviceconnection functionOscillation ON/OFF, Detectionof high load, Warning of errorstop, Recovery from errorSpecifications: OscillatorFrequency adjustment Automatic tracking typeMaximum output /Output adjustment100 W / Step-less continuously-variable typePower requirement Single phase 200 VAC, 50/60 HzPower consumption300 VAOuter dimensions230 (W) x 232 (D) x 144 (H) (mm)(194 (H) including the handle)Weight 4.8 kg ( 5.7 kg including the storage rack)External deviceconnection functionOscillation from transducer ON/OFFWhile oscillation is activated, the lampon the transducer illuminates andsound is generated from the oscillator.Specifications: Oscillator◎ Carbon prepregs with thickness up to t10◎ Thermoplastics◎ Rubber◎FabricsApplicableMaterialsApplicableMaterials*Manufacturing of the 200 V type is also possible.-TransducerSF-653Oscillator SF-0102OscillatorFB-3136-5HStandard ToolsStandard Tool139.511524.513615537φ40φ30φ10Hand Switch( Unit : mm )This is a highly versatile hand tool compatible with small and large blades depending on the applications.This is a manual-operation type transducer that allows the use of large tools, such as of the chisel typeand knife type to assist high power manual operations, including stripping exterior building walls and rustremoval.This is a high-frequency cutter featuring the 40 kHz (40,000 vibrationsper second) vibration frequency of tools with an amplitude of 30 microns.It maximizes the effect of ultrasonic high-speed micro vibrations. A widerange of materials, including newly developed composite materials,rubber, and leather, can be cut at will with low processing pressure,sharp cutting surfaces, and little cutting chips.This is a high-power ultrasonic cutter featuring the ultrasonic poweroutput of 220 W. The tool’s ultrasonic vibrations at a frequency of 22 kHz(22,000 vibrations per second) drastically reduce the cutting resistance.Varieties of materials can be cut even more rapidly and cleanly with alower processing pressure. A function to enable constant monitoring ofloads during cutting was added anew, thereby ensuring added safety anduser friendliness.FB-3136-6L4FB-3134FB-3294-2◎ The output adjustment can be done in step-lessand continuous manner from the minimum to themaximum levels.◎ The constant amplitude circuit always keeps vibrationsat stable amplitude.◎ The overload protection circuit is featured.◎ Force air cooling is possible by installing the air inlet(SF-3140).Features◎ Stable vibrations with a maximum amplitude of 30microns ensure remarkable cutting performance.◎ Light in weight and easy-to-hold transducer (150 g)where much greater importance is attached to itsoperating performance.◎ Adoption of the exclusive square-head screws andthe screwdriver ensures easy and robust mounting oftools.FeaturesHigh-output cutter for manual operation: Assisting manual operations with clear cutting The effect of ultrasonic high-speed micro vibrations realized cutting of materials at will.Frequency adjustment Automatic tracking typeMaximum output220 WOutput adjustment Step-less continuously-variable typePower requirement Single phase 100 VAC, 50/60 HzPower consumption500 VAOuter dimensions142 (W) x 294 (D) x 210 (H) (mm)(260 (H) including the handle)Weight 4.5kgSpecifications: OscillatorSpecifications: TransducerFrequency40 kHzCord length 4 mHousing material Resin (Duracon)Outer dimensionsφ10 / φ18.5 / φ28 x 150.6 L (mm)Weight150 g (excluding the cord)Blade thickness Dedicated for use with a 0.4 mm bladeHP-660TransducerSF-7400TransducerSF-3140SF-3400ⅡOscillatorSF-30OscillatorFrequency adjustment Automatic tracking typeMaximum output / Outputadjustment45 W / Two-step continuously-variable typePower requirement Single phase 100 VAC, 50/60 HzPower consumption100 VAOuter dimensions Approx. 170 (W) x 180 (D) x 78 (H) (mm)Weight Approx. 1.5 kgSpecifications: Oscillator Welding Tool ScraperSpecifications: Transducer SF-3140Specifications: Transducer SF-7400Frequency22 kHzCord length(Up to 10 m)Housing material Resin (Duracon)Outer dimensionsφ16 / φ40 x 154L (mm)Weight340 g (excluding the cord)Hand switch Pushbutton typeFrequency22 kHzCord length Up to 10 mHousing material Aluminum alloyOuter dimensions Hexagonal 12 / φ27/ φ40 x 260L (mm)Weight600 g (excluding the cord)Blade thickness0.6 mmStandard ToolsOptional ToolStandard Tools◎ Plastics (boards, sheets, films, laminated materials)◎ Various types of prepregs (single sheet cutting,overlapped cutting)◎ Leather (natural and artificial)◎ Rubber (vulcanized latex, non-vulcanized latex)◎ Fabric materials, nonwoven fabrics◎ Paper and cardboards◎ Rubber (vulcanized latex, non-vulcanized latex,sheeting materials, sealing materials and tubes)and leather (natural and artificial)◎ Thermoplastics (boards, sheeting materials, films,laminated materials, flooring materials)◎ Fabric materials, nonwoven fabrics and paper(specially treated paper and coated paper)ApplicableMaterials対象材料ApplicableMaterials1051053515φ27φ40φ1226086.352.811.5φ18.5φ28150.6Hand Switchwith Lamp14212154φ40φ16( Unit : mm )( Unit : mm )( Unit : mm )。

L6997资料

PIN CONNECTION (Top View)

NOSKIP GNDSENSE INT VSENSE VCC GND VREF VFB OSC SS

1 2 3 4 5 6 7 8 9 10

TSSOP20

20 19 18 17 16 15 14 13 12 11

BOOT HGATE PHASE VDR LGATE PGND PGOOD OVP SHDN ILIM

SHUTDOWN SECTION SHDN Device On Device Off ISHVDR ISHVCC Drivers shutdown current Devices shutdown current 1.2

SOFT START SECTION ISS Soft Start current Active Soft start and voltage CURRENT LIMIT AND ZERO CURRENT COMPARATOR ILIM input bias current Zero Crossing Comparator offset Phase-gnd DKILIM Current limit factor RILIM = 2KΩ to 200KΩ 4.6 -2 1.6 1.8 5 5.4 2 2 VSS = 0.4V 4 300 400 6 500

ELECTRICAL CHARACTERISTICS (VCC = VDR = 3.3V; Tamb = 0°C to 85°C unless otherwise specified)

Symbol SUPPLY SECTION Vin VCC, VDR VCC Turn-onvoltage Turn-off voltage Hysteresis IqVDR IqVcc Quiescent Current Drivers Device Quiescent current VFB > VREF VFB > VREF Input voltage range Vout=Vref Fsw=110Khz Iout=1A 1 3 2.86 2.75 90 7 400 20 600 28 5.5 2.97 2.9 V V V V mV µA µA V 0.6 SHDN to GND SHDN to GND 1 5 15 V µA µA µA mV µA mV µA Parameter Test Condition Min. Typ. Max. Unit

FLZ3V6A中文资料

FLZ2V2 - FLZ39V Zener DiodesMarch 2006FLZ2V2 - FLZ39VZener DiodesAbsolute Maximum Ratings T a= 25°C unless otherwise noted* These ratings are limiting values above which the serviceability of the diode may be impaired.Thermal Characteristics* Device mounted on FR-4 PCB with 3’’ × 4.5” X 0.06 with only signal traceElectrical Characteritics Tamb = 25°C unless otherwise specifiedPackage Marking and Ordering InformationSymbolParameterValueUnitsP D Power Dissipation500mW T STG Storage Temperature Range -65 to +175°C T J Maximum Junction Temperature 175°C I ZMMaximum Regulator CurrentP D /V ZmASymbolParameterValueUnitR θJAThermal Resistance, Junction to Ambient300°C/WSymbolParameter/ Test conditionMin.Typ.Max.UnitV FForward Voltage / I F =200mA----1.2VDevice MarkingDevicePackageReel SizeTape WidthQuantityColor Band Marking Per ToleranceRefer to Product table listSOD-807”8mm2,500SOD-80 Glass caseColor Band Denotes CathodeColor Band MarkingTolerance 1st Band 2nd Band A Blue Red B Blue Green C Blue Black D Blue GrayFLZ3V0B 3.02 3.12 3.2135204501351 FLZ3V3FLZ3V3A 3.17 3.27 3.3635204501141 FLZ3V3B 3.33 3.43 3.5235204501141 FLZ3V6FLZ3V6A 3.48 3.57 3.6648208501 2.81 FLZ3V6B 3.64 3.73 3.8148208501 2.81 FLZ3V9FLZ3V9A 3.78 3.88 3.9740208501 1.41 FLZ3V9B 3.93 4.03 4.1240208501 1.41 FLZ4V3FLZ4V3A 4.07 4.15 4.23322085010.471 FLZ4V3B 4.22 4.30 4.38322085010.471FLZ4V3C 4.35 4.44 4.52322085010.471 FLZ4V7FLZ4V7A 4.48 4.56 4.64212077010.191 FLZ4V7B 4.60 4.68 4.75212077010.191FLZ4V7C 4.73 4.81 4.89212077010.191 FLZ5V1FLZ5V1A 4.86 4.94 5.021********.19 1.5 FLZ5V1B 4.99 5.08 5.16172068510.19 1.5FLZ5V1C 5.13 5.23 5.33172068510.19 1.5 FLZ5V6FLZ5V6A 5.31 5.41 5.5010.52042510.75 2.5 FLZ5V6B 5.48 5.58 5.6810.52042510.75 2.5FLZ5V6C 5.66 5.76 5.8610.52042510.75 2.5 FLZ6V2FLZ6V2A 5.83 5.94 6.048.5202551 3.33 FLZ6V2B 6.01 6.12 6.228.5202551 3.33FLZ6V2C 6.18 6.28 6.388.5202551 3.33 FLZ6V8FLZ6V8A 6.33 6.45 6.57 6.6201230.5 1.1 3.5 FLZ6V8B 6.54 6.66 6.77 6.6201230.5 1.1 3.5FLZ6V8C 6.72 6.83 6.93 6.6201230.5 1.1 3.5 FLZ7V5FLZ7V5A 6.907.047.17 6.620950.50.3 4.0 FLZ7V5B7.137.267.39 6.620950.50.3 4.0FLZ7V5C7.357.497.62 6.620950.50.3 4.0 FLZ8V2FLZ8V2A7.587.737.88 6.620950.50.35 FLZ8V2B7.847.998.13 6.620950.50.35FLZ8V2C8.098.248.39 6.620950.50.35 FLZ9V1FLZ9V1A8.348.518.68 6.620950.50.36 FLZ9V1B8.638.808.97 6.620950.50.36FLZ9V1C8.919.099.27 6.620950.50.36FLZ12VB11.5311.7111.899.510950.50.1339FLZ12VC11.8312.0512.279.510950.50.1339 FLZ13V FLZ13VA12.2112.4512.6811.410950.50.13310 FLZ13VB12.6212.8713.1211.410950.50.13310FLZ13VC13.0713.3315.3811.410950.50.13310 FLZ15V FLZ15VA13.5213.7914.0513.310950.50.13311 FLZ15VB13.9914.2614.5213.310950.50.13311FLZ15VC14.4514.7214.9913.310950.50.13311 FLZ16V FLZ16VA14.9015.1915.4715.2101320.50.13312 FLZ16VB15.3615.6515.9315.2101320.50.13312FLZ16VC15.8316.1416.4515.2101320.50.13312 FLZ18V FLZ18VA16.3816.7017.0219.4101230.50.13313 FLZ18VB16.9617.2917.6119.4101230.50.13313FLZ18VC17.5617.9018.2419.4101230.50.13313 FLZ20V FLZ20VA18.1718.5218.8623.5101700.50.13315 FLZ20VB18.7819.1319.4823.5101700.50.13315FLZ20VC19.4219.8020.1823.5101700.50.13315FLZ20VD19.9320.3020.6723.5101700.50.13315 FLZ22V FLZ22VA20.2820.6621.0325.651700.50.13317 FLZ22VB20.8221.2121.5925.651700.50.13317FLZ22VC21.2921.6622.0225.651700.50.13317FLZ22VD21.7522.1522.5425.651700.50.13317 FLZ24V FLZ24VA22.3222.6923.0629.051700.50.13319 FLZ24VB22.8123.2423.6729.051700.50.13319FLZ24VC23.3523.7824.2129.051700.50.13319FLZ24VD23.8724.3124.7529.051700.50.13319 FLZ27V FLZ27VA24.3324.8925.453852100.50.133 21 FLZ27VB25.0425.6226.193852100.50.133 21FLZ27VC25.6926.2926.883852100.50.133 21FLZ27VD26.3626.9727.573852100.50.133 21 FLZ30V FLZ30VA27.0727.6928.314652100.50.133 23 FLZ30VB27.7728.4129.054652100.50.133 23FLZ30VC28.4429.0929.744652100.50.133 23FLZ30VD29.1029.7730.434652100.50.133 23FLZ36VD34.1934.8935.596352100.50.13327 FLZ39V FLZ39VA34.8635.5736.287252100.50.13330 FLZ39VB35.5336.2636.997252100.50.13330FLZ39VC36.1836.9237.667252100.50.13330FLZ39VD36.8237.5838.337252100.50.13330Note :1. Zener Voltage(V z)The zener voltage is measured with the device junction in the thermal equilibrium at the lead temperature (TL) at at 30°C ± 1°C and 3/8” lead length.Dimensions in MillimetersFAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY FAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR As used herein:2. A critical component is any component of a life support device Formative or In This datasheet contains the design specifications for This datasheet contains preliminary data, andThis datasheet contains final specifications. Fairchild This datasheet contains specifications on a product Across the board. Around the world.™DISCLAIMERPRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.LIFE SUPPORT POLICYSYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, or (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in significant injury to the user.or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.PRODUCT STATUS DEFINITIONS Definition of TermsDatasheet Identification Product Status DefinitionAdvance InformationDesign product development. Specifications may change in any manner without notice.PreliminaryFirst Productionsupplementary data will be published at a later date.Fairchild Semiconductor reserves the right to make changes at any time without notice in order to improve design.No Identification Needed Full ProductionSemiconductor reserves the right to make changes at any time without notice in order to improve design. Obsolete Not In Productionthat has been discontinued by Fairchild semiconductor.The datasheet is printed for reference information only.PACMAN™POP™Power247™PowerEdge™SPM™Stealth™SuperFET™SuperSOT™-3The Power Franchise ®Programmable Active Droop™Rev. I18。

LS7366中文资料

GENERAL FEATURES:• Operating voltage: 3.0V to 5.5V (V DD - V SS )• 5V count frequency: 40MHz • 3V count frequency: 20MHz • 32-bit counter (CNTR).• 32-bit data register (DTR) and comparator.• 32-bit output register (OTR).• Two 8-bit mode registers (MDR0, MDR1) for programmable functional modes.• 8-bit instruction register (IR).• 8-bit status register (STR).• Latched Interrupt output on Carry or Borrow or Compare or Index.• Index driven counter load, output register load or counter reset.• Internal quadrature clock decoder and filter.• x1, x2 or x4 mode of quadrature counting.• Non-quadrature up/down counting.• Modulo-N, Non-recycle, Range-limit or Free-running modes of counting• 8-bit, 16-bit, 24-bit and 32-bit programmable configuration synchronous (SPI) serial interface• LS7366 (DIP); LS7366-S (SOIC); LS7366-TS (TSSOP) - See Figure 1-SPI/MICROWIRE (Serial Peripheral Interface):• Standard 4-wire connection: MOSI, MISO, SS/ and SCK. • Slave mode only.GENERAL DESCRIPTION:LS7366 is a 32-bit CMOS counter, with direct interface for quadra-ture clocks from incremental encoders. It also interfaces with the index signals from incremental encoders to perform variety of marker functions.For communications with microprocessors or microcontrollers, it provides a 4-wire SPI/MICROWIRE bus.The four standard bus I/Os are SS/, SCK, MISO and MOSI. The data transfer between a micro-controller and a slave LS7366 is synchronous. The synchronization is done by the SCK clocks supplied by the microcontroller.Each transmission is organized in blocks of 1 to 5 bytes of data. A transmission cycle is intitiated by a high to low transition of the SS/ input. The first byte received in a transmission cycle is always an instruction byte, whereas the second through the fifth bytes are always interpreted as data bytes. A transmission cycle is terminated with the low to high transition of the SS/ input. Received bytes are shifted in at the MOSI input, MSB first, with the leading edges (high transition) of the SCK clocks. Output data are shifted out on the MISO output, MSB first, with the trailing edges (low transition) of the SCK clocks.32-BIT QUADRATURE COUNTER WITH SERIAL INTERFACE1234567891011121314Vss V DD B A INDEX LFLAG/SS/SCK LS7366MISO MOSIf CKi f CKO PIN ASSIGNMENT TOP VIEWCNT_EN DFLAG/FIGURE 1LSI/CSILSI Computer Systems, Inc. 1235 Walt Whitman Road, Melville, NY 11747 (631) 271-0400 FAX (631) 271-0405LS7366U L®A3800January 2005Read and write commands cannot be combined.For example, when the device is shifting out read data on MISO output, it ignores the MOSI input,even though the SS/ input is active. SS/ must be terminated and reasserted before the device will accept a new command.The counter can be configured to operate as a 1, 2, 3 or 4-byte counter. When configured as a n-byte counter, the CNTR, DTR and OTR are all configured as n-byte registers, where n = 1, 2, 3 or 4. The content of the instruction/data identity is automatically adjusted to match the n-byte configu-ration. For example, if the counter is configured as a 2-byte counter, the instruction “write to DTR”expects 2 data bytes following the instruction byte.If the counter is configured as a 3-byte counter, the same instruction will expect 3 bytes of data follow-ing the instruction byte.Following the transfer of the appropriate number of bytes any further attempt of data transfer is ignored until a new instruction cycle is started by switching the SS/ input to high and then low.The counter can be programmed to operate in a number of different modes, with the operating characteristics being written into the two mode registers MDR0 and MDR1. Hardware I/Os are provided for event driven operations, such as processor interrupt and index related functions.I/O Pins:Following is a description of all the input/output pins.A (Pin 12)B (Pin 11)Inputs. A and B quadrature clock outputs from incremental encoders are directly applied to the A and B inputs of the LS7366. These clocks are ideally 90 degrees out-of-phase signals. A and B inputs are validated by on-chip digital filters and then decoded for up/down direction and count clocks.In non-quadrature mode, A serves as the count input andB serves as the direction input (B = high enables up count, B = low enables down count). In non-quadrature mode,the A and B inputs are not filtered internally, and are instantaneous in nature.INDEX (Pin 10)Input. The INDEX is a programmable input that canbe driven directly by the Index output of an incremental encoder. It can be programmed via the MDR to functionas one of the following:LCNTR (load CNTR with data from DTR), RCNTR(reset CNTR), or LOTR (load OTR with data from CNTR). Alternatively, the INDEX input can be masked out for"no functionality".In quadrature mode, the INDEX input is validated with the filter clock in order to synchronize with the quadrature inputs A and B. To be valid, the INDEX signal in quadrature mode must overlap the condition in which both A and B are low or both A and B are high. In non-quadrature mode, however, the INDEX input is instantaneous in nature and totally independent of A and B.f CK i (Pin 2), f CK0 (Pin 1)Input, Output. A crystal connected between these 2 pins generates the basic clock for filtering the A, B and INDEX inputs in the quadrature count mode. Instead of a crystal the f CKi input may also be driven by an external clock.The frequency at the f CKi input is either divided by 2(if MDR0 <B7> = 1) or divided by 1 (if MDR0 <B7> = 0)for the filter circuit. For proper filtering of the A, B andthe Index inputs the following condition must be satisfied:f f≥ 4f QAWhere f f is the internal filter clock frequency derived from the fCKi in accordance with the status of MDR0 <B7> and f QA is the maximum frequency of Clock A in quadrature mode.In non-quadrature count mode, f CKi is not used and should be tied off to any stable logic state.SS/ (Pin 4)A high to low transition at the SS/ (Slave Select) input selects the LS7366 for serial bi-directional data transfer;a low to high transition disables serial data transferand brings the MISO output to high impedance state.This allows for the accommodation of multiple slave units on the serial I/O.CNT_EN (Pin 12)Input. Counting is enabled when CNT_EN input is high; counting is disabled when this input is low.There is an internal pull-up resistor on this input.LFLAG/ (Pin 8), DFLAG/ (Pin 9)Outputs. LFLAG/ and DFLAG/ are programmable outputs to flag the occurences of Carry (counter overflow), Borrow (counter underflow), Compare (CNTR = DTR) and INDEX. The LFLAG/ is an open drain latched output. In contrast, the DFLAG/ is a push-pull instantaneous output. The LFLAG/ can be wired in multi-slave configuration, forming a single processor interrupt line. When active LFLAG/ switches to logic 0 and can be restored to the high impedence state only by clearing the status register, STR. In contrast, the DFLAG/ dynamically switches low with occurences of Carry, Borrow, Compare and INDEX conditions. The configuration of LFLAG/ and DFLAG/ are made through the control register MDR1. In free-running count mode LFLAG/ and DFLAG/ output the same status information in latched and dynamic form, respectively. In single-cycle mode the DFLAG/ outputs CY and BW signals independent of the MDR1 configura-tion. In range-limit and modulo-n modes, DFLAG/ outputs CMP signal in count-up direction (at CNTR = DTR) and BW signal when CNTR underflows independent of the MDR1 configuration. In effect, DFLAG/ generates mode-relevant marker signals in all modes, excepting the free-running count mode wherein MDR1 configures the output signal selection.MOSI (RXD) (Pin 7)Input. Serial output data from the host processor is shifted into the LS7366 at this input.MISO (TXD) (Pin 6)Output. Serial output data from the LS7366 is shifted out on the MISO (Master In Slave Out) pin. The MISO output goes into high impedance state when SS/ input is at logic high, providing multiple slave-unit serial outputs to be wire-ORed.SCK (Pin 5)Input. The SCK input serves as the shift clock input for transmit-ting data in and out of LS7366 on the MOSI and the MISO pins, respectively. Since the LS7366 can operate only in the slave mode, the SCK signal is provided by the host processor as a means for synchronizing the serial transmission between itself and the slave LS7366.REGISTERS:The following is a list of LS7366 internal registers:Upon power-up the registers DTR, CNTR, STR, MDR0 and MDR1 are reset to zero.DTR. The DTR is a software configurable 8, 16, 24 or 32-bit input data register which can be written into directly from MOSI, the serial input. The DTR data can be transferred into the 32-bit counter (CNTR) under program control or by hardware index signal. The DTR can be cleared to zero by software control.In certain count modes, such as modulo-n and range-limit,DTR holds the data for "n" and the count range, respectively.In compare operations, whereby compare flag is set, the DTR is compared with the CNTR.STR. The STR is an 8-bit status register which stores count related status information.CY BW CMP IDX CEN PLS U/D S 7 6 5 4 3 2 1 0CY: Carry (CNTR overflow) latchBW: Borrow (CNTR underflow) latch CMP: Compare (CNTR = DTR) latch IDX: Index latchCEN: Count enable status: 0: counting disabled, 1: counting enabled7366-012405-3IR . The IR is an 8-bit register that fetches instruction bytes from the received data stream and executes them to perform such functions as setting up the operating mode for the chip (load the MDR) and data transfer among the various registers.B7 B6 B5 B4 B3 B2 B1 B0B2 B1 B0 = XXX (Don’t care)B5 B4 B3 = 000: Select none= 001: Select MDR0 = 010: Select MDR1= 011: Select DTR = 100: Select CNTR = 101: Select OTR = 110: Select STR = 111: Select noneB7 B6 = 00: CLR register= 01: RD register = 10: WR register = 11: LOAD register The actions of the four functions, CLR, RD, WR and LOAD are elaborated in Table 1.TABLE 1Number of Bytes OP Code Register OperationMDR0Clear MDR0 to zero MRD1Clear MDR1 to zero1 CLR DTR NoneCNTR Clear CNTR to zero OTR None STR Clear STR to zero MDR0Output MDR0 serially on TXD (MISO)MDR1Output MDR1 serially on TXD (MISO)2 to 5 RD DTR NoneCNTR Transfer CNTR to OTR, then output OTR seriallyon TXD (MISO)OTR Output OTR serially on TXD (MISO)STR Output STR serially on TXD (MISO)MDR0Write serial data at RXD (MOSI) into MDR0MDR1Write serial data at RXD (MOSI) into MDR12 to 5 WR DTR Write serial data at RXD (MOSI) into DTRCNTR None OTR None STR None MDR0None MDR1None1 LOAD DTR NoneCNTR Transfer DTR to CNTR in “parallel”OTR Transfer CNTR to OTR in “parallel”CNTR. The CNTR is a software configurable 8, 16, 24 or 32-bit up/down counter which counts the up/down pulses resulting from the quadrature clocks applied at the A and B inputs, or alternatively, in non-quadrature mode, pulses applied at the A input. By means of IR intructions the CNTR can be cleared, loaded from the DTR or in turn, can be transferred into the OTR. The “clear CNTR”and the “load CNTR” commands in the ”range-limit” mode, however have limitations. In this mode when the CNTR is frozen in up count direction at CNTR = DTR, a “clear CNTR” command will only function if the count direction is reversed from up to down. Similarly, in the down direction at CNTR = 0, a “load CNTR” command will only function if the direction is reversed from down to up.OTR. The OTR is a software configuration 8, 16, 24 or 32-bit register which can be read back on the MISO output. Since instantaneous CNTR value is often needed to be read while the CNTR continues to count, the OTR serves as a convenient dump site for instantaneous CNTR data which can then be read without interfering with the counting process.PLS: Power loss indicator latch; set upon power upU/D: Count direction indicator: 0: count down, 1: count up S: Sign bit. 1: negative, 2: positiveA “CLR STR” command to IR resets all status bits except CEN and U/D. In quadrature mode, if the quadrature clocks have been halted, the status bits CY, BW and CMP are not affected by a “CLR STR” command under the following conditions: CY: If CNTR = FFFFFFFF with status bit U/D = 1 BW: If CNTR = 0 with status bit U/D = 0 CMP: If CNTR = DTRIn non-quadrature mode the same rules apply if input A is held at logic low.7366-112204-4ABSOLUTE MAXIMUM RATINGS: (All voltages referenced to Vss)Parameter Symbol Values Unit DC Supply Voltage V DD +7.0V Voltage V IN Vss - 0.3 to V DD + 0.3 VOperating Temperature T A -25 to +85o C Storage Temperature T STG -65 to +150o C MDR1. The MDR1 (Mode Register 1) is an 8-bit read/write register which is appended to MDR0 for additional modes. Upon power-up MDR1 is cleared to zero.B7 B6 B5 B4 B3 B2 B1 B0B1 B0 = 00: 4-byte counter mode = 01: 3-byte counter mode = 10: 2-byte counter mode. = 11: 1-byte counter mode B2 = 0: Enable counting = 1: Disable counting B3 = : not used B4 = 0: NOP= 1: FLAG on IDX (B4 of STR) B5 = 0: NOP= 1: FLAG on CMP (B5 of STR) B6 = 0: NOP= 1: FLAG on BW (B6 of STR) B7 = 0: NOP= 1: FLAG on CY (B7 of STR)MDR0. The MDR0 (Mode Register 0) is an 8-bit read/write register that sets up the operating mode for the LS7366. The MDR0 is written into by executing the "write-to-MDR0" instruction via the instruction register. Upon power up MDR0 is cleared to zero. The following is a breakdown of the MDR bits:B7 B6 B5 B4 B3 B2 B1 B0B1 B0 = 00: non-quadrature count mode. (A = clock, B = direction). = 01: x1 quadrature count mode (one count per quadrature cycle). = 10: x2 quadrature count mode (two counts per quadrature cycle). = 11: x4 quadrature count mode (four counts per quadrature cycle).B3 B2 = 00: free-running count mode.= 01: single-cycle count mode (counter disabled with carry or borrow, re-enabled with reset or load). = 10: range-limit count mode (up and down count-ranges are limited between DTR and zero, respectively; counting freezes at these limits but resumes when direction reverses). = 11: modulo-n count mode (input count clock frequency is divided by a factor of (n+1), where n = DTR, in both up and down directions).B5 B4 = 00: disable index.= 01: configure index as the "load CNTR" input (transfers DTR to CNTR). = 10: configure index as the "reset CNTR" input (clears CNTR to 0). = 11: configure index as the "load OTR" input (transfers CNTR to OTR). B6 = 0: Negative index input = 1: Positive index inputB7 = 0: Filter clock division factor = 1 = 1: Filter clock division factor = 2NOTE: Applicable to both LFLAG/ and DFLAG/DC Electrical Characteristics. (T A = -25˚C to +85°C)Parameter Symbol Min. TYP Max. Unit RemarksSupply Voltage V DD 3.0- 5.5V-Supply Current I DD300400450µA V DD = 3.0VI DD700800950µA V DD = 5.0VInput Voltagesf CK i, Logic high V CH- 2.1 2.3V V DD = 3.0VV CH- 3.5 3.7V V DD = 5.0Vf CKi, Logic Low V CL0.70.9-V V DD = 3.0VV CL 1.3 1.5-V V DD = 5.0VAll other inputs, Logic High V AH- 1.9 2.1V V DD = 3.0VV AH- 3.2 3.5V V DD = 5.0VAll other inputs, Logic Low V AL0.50.7-V V DD = 3.0VV AL 1.0 1.2-V V DD = 5.0VInput Currents:CNT_EN Low I IEL- 3.0 5.0µA V AL = 0.7V, V DD = 3.0VI IEL-10.015.0µA V AL = 1.2V, V DD = 5.0V CNT_EN High I IEH- 1.0 3.0µA V AH = 1.9V, V DD = 3.0VI IEH- 4.0 6.0µA V AH = 3.2V, V DD = 5.0V All other inputs, High or Low--00µA-Output Currents:FLAG Sink I OFL-1.3-2.0-mA V OUT = 0.5V, V DD = 3.0VI OFL-3.2-4.0-mA V OUT = 0.5V, V DD = 5.0V FLAG Source- 0 0-mA Open Drain Outputf CKO Sink I OCL-1.3-2.0-mA V OUT = 0.5V, V DD = 3.0VI OCL-3.2-4.0-mA V OUT = 0.5V, V DD = 5.0V f CKO Source I OCH 1.3 2.0-mA V OUT = 2.5V, V DD = 3.0VI OCH 3.2 4.0-mA V OUT = 4.5V, V DD = 5.0V TXD/MISO:Sink I OML-1.5-2.4-mA V OUT = 0.5V, V DD = 3.0VI OML-3.8-4.8-mA V OUT = 0.5V, V DD = 5.0V Source I OMH 1.5 2.4-mA V OUT = 0.5V, V DD = 3.0VI OMH 3.8 4.8-mA V OUT = 0.5V, V DD = 5.0V Transient Characteristics. (T A = -25˚C to +85˚C, V DD = 5V ± 10%)Parameter Symbol Min. Value Max.Value Unit Remarks(See Fig. 2 & 3)SCK High Pulse Width t CH100-ns-SCK Low Pulse Width t CL100-ns-SS/ Set Up Time t CSL100-ns-SS/ Hold Time t CSH100-ns-Quadrature Mode(See Fig. 4, 6 & 7)f CKI High Pulse Width t112-ns-f CKI Pulse Width t212-ns-f CKI Frequency f FCK-40MHz-Effective Filter Clock fF Period t325-ns t3 = t1+t2, MDR0 <7> = 0t350-ns t3 = 2(t1+t2), MDR0 <7> = 1 Effective Filter Clock f F frequency f F-40MHz f F = 1/ t3Quadrature Separation t426-ns t4 > t3Quadrature Clock Pulse Width t552-ns t5≥ 2t3Quadrature Clock frequency f QA, f QB-9.6MHz f QA = f QB < 1/4t3 Quadrature Clock to Count Delay t Q14t35t3--x1 / x2 / x4 Count Clock Pulse Width t Q212-ns t Q2 = (t3)/2Index Input Pulse Width ti d32-ns t id > t4Index Set Up Time ti s-5ns-Index Hold Time ti h-5ns-Quadrature clock to t fl 4.5t3 5.5t3ns-DFLAG/ or LFLAG/ delayDFLAG/ output width t fw26-ns t fw = t4Parameter Symbol Min. Value Max.Value Unit RemarksNon-Quadrature Mode(See Fig. 5 & 8)Clock A - High Pulse Width t612-ns-Clock A - Low Pulse Width t712-ns-Direction Input B Set-up Time t8S12-ns-Direction Input B Hold Time t8H10-ns-Clock Frequency (non-Mod-N)f A-40MHz f A = (1/(t6 + t7))Clock to DFLAG/ or t920-ns-LFLAG/ delayDFLAG/ output width t1012-ns t10 = t7Transient Characteristics. (T A = -25˚C to +85˚C, V DD = 3.3V ± 10%)Parameter Symbol Min. Value Max.Value Unit Remarks(See Fig. 2 & 3)SCK High Pulse Width t CH120-ns-SCK Low Pulse Width t CL120-ns-SS/ Set Up Time t CSL120-ns-SS/ Hold Time t CSH120-ns-Quadrature Mode(See Fig. 4, 6 & 7)f CKI High Pulse Width t124-ns-f CKI Pulse Width t224-ns-f CKI Frequency f FCK-20MHz-Effective Filter Clock fF Period t350-ns t3 = t1+t2, MDR0 <7> = 0t3100-ns t3 = 2(t1+t2), MDR0 <7> = 1 Effective Filter Clock f F frequency f F-20MHz f F = 1/t3Quadrature Separation t452-ns t4 > t3Quadrature Clock Pulse Width t5105-ns t5≥ 2t3Quadrature Clock frequency f QA, f QB- 4.5MHz f QA = f QB < 1/4t3 Quadrature Clock to Count Delay t Q14t35t3--x1/x2/x4 Count Clock Pulse Width t Q225-ns t Q2 = (t3)/2Index Input Pulse Width t id60-ns t id > t4Index Set Up Time t is-10ns-Index Hold Time t ih-10ns-Quadrature clock to t fl 4.5t3 5.5t3ns-DFLAG/ or LFLAG/ delayDFLAG/ output width t fw52-ns t fw = t4Non-Quadrature Mode(See Fig. 5 & 8)Clock A - High Pulse Width t624-ns-Clock A - Low Pulse Width t724-ns-Direction Input B Set-up Time t8S24-ns-Direction Input B Hold Time t8H24-ns-Clock Frequency (non-Mod-N)f A-40MHz f A = (1/(t6 + t7))Clock to DFLAG/or t940-ns-LFLAG/ delayDFLAG/ output width t1024-ns t10 = t7。

LOA676中文资料

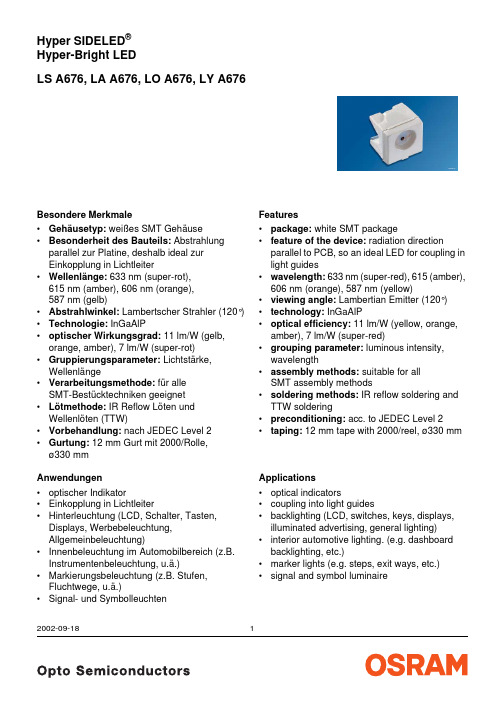

LS A676, LA A676, LO A676, LY A676Hyper SIDELED ®Hyper-Bright LED2002-09-181Besondere Merkmale•Geh äusetyp: wei ßes SMT Geh äuse•Besonderheit des Bauteils: Abstrahlung parallel zur Platine, deshalb ideal zur Einkopplung in Lichtleiter•Wellenl änge: 633 nm (super-rot), 615nm (amber), 606 nm (orange), 587nm (gelb)•Abstrahlwinkel: Lambertscher Strahler (120°)•Technologie: InGaAlP•optischer Wirkungsgrad: 11 lm/W (gelb, orange, amber), 7 lm/W (super-rot)•Gruppierungsparameter: Lichtst ärke, Wellenl änge•Verarbeitungsmethode: f ür alle SMT-Best ücktechniken geeignet •L ötmethode: IR Reflow L öten und Wellenl öten (TTW)•Vorbehandlung: nach JEDEC Level 2•Gurtung: 12 mm Gurt mit 2000/Rolle, ø330mm Anwendungen•optischer Indikator•Einkopplung in Lichtleiter•Hinterleuchtung (LCD, Schalter, Tasten, Displays, Werbebeleuchtung, Allgemeinbeleuchtung)•Innenbeleuchtung im Automobilbereich (z.B. Instrumentenbeleuchtung, u.ä.)•Markierungsbeleuchtung (z.B. Stufen, Fluchtwege, u.ä.)•Signal- und SymbolleuchtenFeatures•package: white SMT package•feature of the device: radiation directionparallel to PCB, so an ideal LED for coupling in light guides•wavelength: 633 nm (super-red), 615 (amber), 606 nm (orange), 587 nm (yellow)•viewing angle: Lambertian Emitter (120°)•technology: InGaAlP•optical efficiency: 11 lm/W (yellow, orange, amber), 7 lm/W (super-red)•grouping parameter: luminous intensity, wavelength•assembly methods: suitable for all SMT assembly methods•soldering methods: IR reflow soldering and TTW soldering•preconditioning: acc. to JEDEC Level 2•taping: 12 mm tape with 2000/reel, ø330mmApplications•optical indicators•coupling into light guides•backlighting (LCD, switches, keys, displays, illuminated advertising, general lighting)•interior automotive lighting. (e.g. dashboard backlighting, etc.)•marker lights (e.g. steps, exit ways, etc.)•signal and symbol luminaire2002-09-182Anm.:-1 gesamter Farbbereich (siehe Seite 4)-24 gesamter Farbbereich, Lieferung in Einzelgruppen (siehe Seite 5)-26 gesamter Farbbereich, Lieferung in Einzelgruppen (siehe Seite 5)Die Standardlieferform von Serientypen beinhaltet eine untere bzw. eine obere Familiengruppe,die aus nur 3bzw.4 Halbgruppen besteht. Einzelne Halbgruppen sind nicht erhältlich.In einer Verpackungseinheit /Gurt ist immer nur eine Halbgruppe enthalten.Note:-1 Total color tolerance range (please see page 4)-24 Total color tolerance range, delivery in single groups (please see page 5)-26 Total color tolerance range, delivery in single groups (please see page 5)The standard shipping format for serial types includes a lower or upper family group of 3or 4individual groups. Individual half groups are not available.No packing unit /tape ever contains more than one luminous intensity half group.TypTypeEmissions-farbe Color of EmissionFarbe derLichtaustritts-fl ächeColor of the Light Emitting AreaLichtst ärkeLuminous Intensity I F = 20mA I V (mcd)LichtstromLuminous FluxI F = 20mA ΦV (mlm)BestellnummerOrdering CodeLS A676-N2P2-1LS A676-P2R1-1super-red colorless clear 35.5 ...71.056.0 ...140.0150 (typ.)280 (typ.)Q62703Q5074Q62703Q5075LA A676-Q1R1-1LA A676-R1S2-1amber colorless clear 71.0 ...140.0112.0 ...280.0310 (typ.)560 (typ.)Q62703Q4972Q62703Q4973LO A676-Q1R1-24LO A676-R1S2-24orange colorless clear 71.0 ...140.0112.0 ...280.0310 (typ.)560 (typ.)Q62702Q5032Q62702Q5033LY A676-P2Q2-26LY A676-Q2S1-26yellowcolorless clear56.0 ...112.090.0 ...224.0240 (typ.)440 (typ.)Q62703Q5111Q62703Q5112Grenzwerte Maximum RatingsBezeichnung Parameter SymbolSymbolWerteValuesEinheitUnitLS, LO, LA LYBetriebstemperatur Operating temperature range Top– 55 … + 100°CLagertemperaturStorage temperature range Tstg– 55 … + 100°CSperrschichttemperatur Junction temperature Tj+ 100°CDurchlassstrom Forward current IF30mAStoßstromSurge currentt≤ 10 µs, D = 0.005IFM10.2ASperrspannung1) Reverse voltage VR12VLeistungsaufnahme Power consumption Ptot80mWWärmewiderstand Thermal resistanceSperrschicht/UmgebungJunction/ambientSperrschicht/LötpadJunction/solder pointMontage auf PC-Board FR 4 (Padgröße ≥ 16mm2) mounted on PC board FR 4 (pad size ≥ 16 mm 2)Rth JARth JS530300K/WK/W1)für kurzzeitigen Betrieb geeignet / suitable for short term application2002-09-1832002-09-184Kennwerte (T A = 25 °C)Characteristics Bezeichnung ParameterSymbol SymbolWerte Values Einheit UnitLSLA LO LY Wellenl änge des emittierten Lichtes (typ.)Wavelength at peak emission I F = 20mAλpeak645622610591nmDominantwellenl änge 1)(typ.)Dominant wavelength 1)I F = 20mAλdom633± 6615± 6606–6/+3587–7/+8nmSpektrale Bandbreite bei 50 % I rel max (typ.)Spectral bandwidth at 50 % I rel max I F = 20mA∆λ16161615nmAbstrahlwinkel bei 50 % I V (Vollwinkel)(typ.)Viewing angle at 50 % I V 2ϕ120120120120Grad deg.Durchlassspannung 2)(typ.)Forward voltage 2)(max.)I F = 20mA V F V F 2.02.4 2.02.4 2.02.4 2.02.4V VSperrstrom(typ.)Reverse current (max.)V R = 12 VI R I R 0.01100.01100.01100.0110µA µATemperaturkoeffizient von λpeak (typ.)Temperature coefficient of λpeak I F = 20mA; –10°C ≤ T ≤ 100°C TC λpeak0.140.130.130.13nm/KTemperaturkoeffizient von λdom (typ.)Temperature coefficient of λdom I F = 20mA; –10°C ≤ T ≤ 100°C TC λdom0.050.060.070.10nm/KTemperaturkoeffizient von V F (typ.)Temperature coefficient of V F I F = 20mA; –10°C ≤ T ≤ 100°C TC V– 2.0– 1.8– 1.7– 2.5mV/KOptischer Wirkungsgrad (typ.)Optical efficiency I F = 20mAηopt7111111lm/W1)Wellenl ängen werden mit einer Stromeinpr ägedauer von 25ms und einer Genauigkeit von ±1nm ermittelt.Wavelengths are tested at a current pulse duration of 25ms and a tolerance of ±1nm.2)Spannungswerte werden mit einer Stromeinpr ägedauer von 1ms und einer Genauigkeit von ±0,1V ermittelt.Voltages are tested at a current pulse duration of 1ms and a tolerance of ±0.1V.2002-09-185Helligkeitswerte werden mit einer Stromeinpr ägedauer von 25ms und einer Genauigkeit von ±11% ermittelt.Luminous intensity is tested at a current pulse duration of 25ms and a tolerance of ±11%.1)Wellenl ängengruppen / Wavelength groupsGruppe Group yellow orange Einheit Unit min.max.min.max.2580583600603nm 3583586603606nm 4586589606609nm 5589592nm 6592595nmHelligkeits-GruppierungsschemaLuminous Intensity Groups LichtgruppeLuminous Intensity Group Lichtst ärkeLuminous Intensity I V (mcd)Lichtstrom Luminous Flux ΦV (mlm)N2P1P2Q1Q2R1R2S1S235.5 ...45.045.0 ...56.056.0 ...71.071.0 ...90.090.0 ...112.0112.0 ...140.0140.0 ...180.0180.0 ...224.0224.0 ...280.0120 (typ.)150 (typ.)190 (typ.)240 (typ.)300 (typ.)380 (typ.)480 (typ.)600 (typ.)760 (typ.)Gruppenbezeichnung auf Etikett Group Name on Label Beispiel: P2-3Example: P2-3LichtgruppeLuminous Intensity Group Halbgruppe Half Group Wellenl änge Wavelength P23Relative spektrale Emission I rel = f (λ), T A = 25 °C, I F = 20mA Relative Spectral EmissionV(λ) = spektrale AugenempfindlichkeitStandard eye response curveAbstrahlcharakteristik I rel = f (ϕ)2002-09-186Durchlassstrom I F = f (V F)Forward CurrentMaximal zulässiger Durchlassstrom I F = f (T) Max. Permissible Forward Current Relative Lichtstärke I V/I V(20mA) = f (I F) Relative Luminous IntensityV V(25 °C)ARelative Luminous Intensity2002-09-187Zulässige Impulsbelastbarkeit I F = f (t p) Permissible Pulse Handling Capability Duty cycle D = parameter, T A = 25 °CF p Permissible Pulse Handling Capability Duty cycle D = parameter, T A = 85 °CZulässige Impulsbelastbarkeit I F = f (t p) Permissible Pulse Handling Capability Duty cycle D = parameter, T A = 25 °CF p Permissible Pulse Handling Capability Duty cycle D = parameter, T A = 85 °C2002-09-188MaßzeichnungPackage OutlinesMaße werden wie folgt angegeben: mm (inch) / Dimensions are specified as follows: mm (inch). Kathodenkennung:abgeschrägte EckeCathode mark:bevelled edgeGewicht / Approx. weight:40 mg2002-09-189Lötbedingungen Vorbehandlung nach JEDEC Level 2 Soldering Conditions Preconditioning acc. to JEDEC Level 2 IR-Reflow Lötprofil(nach IPC 9501)IR Reflow Soldering Profile(acc. to IPC 9501)2002-09-1810Wellenlöten (TTW)(nach CECC 00802)TTW Soldering(acc. to CECC 00802)2002-09-1811Empfohlenes Lötpaddesign Wellenlöten (TTW)Recommended Solder Pad TTW SolderingMaße werden wie folgt angegeben: mm (inch) / Dimensions are specified as follows: mm (inch) 2002-09-1812Empfohlenes Lötpaddesign IR Reflow LötenRecommended Solder Pad IR Reflow SolderingMaße werden wie folgt angegeben: mm (inch) / Dimensions are specified as follows: mm (inch). Gurtung / Polarität und Lage Verpackungseinheit2000/Rolle, ø330 mm Method of Taping / Polarity and Orientation Packing unit2000/reel, ø330 mmMaße werden wie folgt angegeben: mm (inch) / Dimensions are specified as follows: mm (inch)2002-09-18132002-09-1814Published by OSRAM Opto Semiconductors GmbH Wernerwerkstrasse 2, D-93049 Regensburg © All Rights Reserved.Attention please!The information describes the type of component and shall not be considered as assured characteristics.All typical data and graphs are basing on representative samples, but don ’t represent the production range. If requested, e.g. because of technical improvements, these typ. data will be changed without any further notice.Terms of delivery and rights to change design reserved. Due to technical requirements components may contain dangerous substances. For information on the types in question please contact our Sales Organization.If printed or downloaded, please find the latest version in the Internet.PackingPlease use the recycling operators known to you. We can also help you – get in touch with your nearest sales office.By agreement we will take packing material back, if it is sorted. You must bear the costs of transport. For packing material that is returned to us unsorted or which we are not obliged to accept, we shall have to invoice you for any costs incurred.Components used in life-support devices or systems must be expressly authorized for such purpose! Critical components 1 may only be used in life-support devices or systems 2 with the express written approval of OSRAM OS.1A critical component is a component used in a life-support device or system whose failure can reasonably be expected to cause the failure of that life-support device or system, or to affect its safety or the effectiveness of that device or system.2Life support devices or systems are intended (a) to be implanted in the human body, or (b) to support and/or maintain and sustain human life. If they fail, it is reasonable to assume that the health of the user may be endangered.Revision History:2002-09-18Date of changePrevious Version:2002-08-19Page Subjects (major changes since last revision)12recommended solder pad (TTW soldering)4value (wavelength amber/yellow 5wavelength groups2wavelength grouping for yellow and orange 14annotations2002-07-254value (TC λdom from 0.04 to 0.05nm/K)2002-07-2513recommended solder pad (IR reflow soldering)2002-08-013, 4value (reverse voltage from 3V to 12V)2002-09-18。

AU6366中文资料

AU6366USB2.0 Single LUNMultiple Flash Card Reader Controller Technical Reference ManualAU6366USB2.0 Single LUN Multiple Flash Card Reader ControllerC o p y r i g h tCopyright © 1997 - 2007. Alcor Micro, Corp. All Rights Reserved. No part of this data sheet may be reproduced, transmitted, transcribed, stored in a retrieval system or translated into any language or computer language, in any form or by any means, electronic, mechanical, magnetic, optical, chemical, manual or otherwise, without prior written permission from Alcor Micro, Corp.T r a d e m a r k A c k n o w l e d g e m e n t sThe company and product names mentioned in this document may be the trademarks or registered trademarks of their manufacturers.D i s c l a i m e rAlcor Micro, Corp. reserves the right to change this product without prior notice. Alcor Micro, Corp. makes no warranty for the use of its products and bears no responsibility for any error that appear in this document. Specifications are subject to change without prior notice.R e v i s i o n H i s t o r yDate Revision DescriptionJan 2006 1.00W Official ReleaseAug 2006 1.01W Update new address of Los Angeles OfficeNov 2006 1.02W Modify “1.2 Features”July 2007 1.03W Modify “5.6 Power Switch Feature”C o n t a c t I n f o r m a t i o n:Web site: /Taiwan China ShenZhen OfficeAlcor Micro, Corp. Rm.2407-08, Industrial Bank Building 4F, No 200 Kang Chien Rd., Nei Hu, No.4013, Shennan Road,Taipei, Taiwan, R.O.C. ShenZhen,China. 518026Phone: 886-2-8751-1984 Phone: (0755) 8366-9039Fax: 886-2-2659-7723 Fax: (0755) 8366-9101Santa Clara Office Los Angeles Office2901 Tasman Drive, Suite 206 9070 Rancho Park CourtSanta Clara, CA 95054 Rancho Cucamonga, CA 91730USA USA Phone: (408) 845-9300 Phone: (909) 483-9900Fax: (408) 845-9086 Fax: (909) 944-0464<Memo>Table of Contents1. Introduction (1)1.1 Description (1)1.2 Features (1)2. Application Block Diagram (2)3. Pin Assignment (3)4. System Architecture and Reference Design (6)4.1 AU6366 Block Diagram (6)5. Electrical Characteristics (7)5.1 Absolute Maximum Ratings (7)5.2 Recommended Operating Conditions (7)5.3 General DC Characteristics (7)5.4 DC Electrical Characteristics of 3.3V I/O Cells (8)5.5 USB Transceiver Characteristics (8)5.6 Power Switch Feature (12)6. Mechanical Information (13)7. Abbreviations (14)iList of FiguresFigure 2.1 Block Diagram (2)Figure 3.1 Pin Assignment Diagram (3)Figure 4.1 AU6366 Block Diagram (6)Figure 5.1 Built-in card power switch I-V curve (12)Figure 5.2 Card Detect Power-on Timing (12)Figure 6.1 Mechanical Information Diagram (13)List of TablesTable 3.1 Pin Descriptions (4)Table 5.1 Absolute Maximum Ratings (7)Table 5.2 Recommended Operating Conditions (7)Table 5.3 General DC Characteristics (7)Table 5.4 DC Electrical Characteristics of 3.3V I/O Cells (8)Table 5.5 Electrical characteristics (8)Table 5.6 Static characteristic:Digital pin (9)Table 5.7 Static characteristic:Analog I/O pins(DP/DM) (9)Table 5.8 Dynamic characteristic:Analog I/O pins(DP/DM) (10)ii1. Introduction1.1D e s c r i p t i o nThe AU6366 is a single chip integrated USB 2.0 multimedia card reader controller that enables PC/DVD/Printer to read/write various type of flash media cards. Flash media cards such as CF, SMC, XD, SD, MMC, Memory Stick are widely used in digital camera, cell phone, PDA and MP3 player to store digital photos and compressed music.Performance of AU6366 is maximized by implementing the latest and fastest card specification available form the industry.The AU6366 is designed in shared pin architecture to meet cost and space regulate for Notebook end reunite.1.2F e a t u r e sSupport USB V2.0 specification and USB Device Class Definition for Mass Storage, Bulk-Transport V1.0Support CF/MD/SD/MMC/MS/MS_Pro/MS_Duo/xD/SMC compatible flash cardSupport the latest flash card specification: CF 3.0 (16-bit IDE mode), SD1.1 (HS-SD), MMC4.0 (8-bit), MSPro parallel mode (4-bit), xD 1.2 Hardware DMA engine integrated for performance enhancementWork with default driver from Windows ME/2000/XP and Mac OS X; Windows 98/2000(SP1/SP2) and Mac OS 9 are supported by vendor driver fromAlcor.Ping-pong FIFO implementation for concurrent bus operationSupport multiple sectors transfer optimize performanceSupport slot-to-slot read/write operationSupport Dynamic Icon UtilitySupport LED for bus operating indicationPower switch integrated to reduce production BOM cost30MHz 8051 CPUBuilt in 3.3V to 2.5V regulatorRun at 12MHz crystalAvailable in 48-pin LQFP packageAU6366 USB 2.0 Single LUN Multiple Flash Card Reader Controller V1.03W 12. Application Block DiagramThe following application drawing demonstrates a typical card reader block diagram using AU6366. By connecting one card reader to a desktop or notebook PC through USB bus, the AU6366 becomes a bus-powered, high speed USB card reader, which can be used as a bridge for data transfer between Desktop PC and Notebook PC.Figure 2.1 Block DiagramSMC/SD/MMCAU6366AU6366 USB 2.0 Single LUN Multiple Flash Card Reader Controller V1.03W 2AU6366 USB 2.0 Single LUN Multiple Flash Card Reader Controller V1.03W33. Pin AssignmentThe AU6366 is delivered in 48pin LQFP form factor. Documented below is a figure shows signal names of each pin and a table in the following page describes each pin in more details.Figure 3.1 Pin Assignment DiagramCARDDATA15CFWTN CLEDCHIPRESETN GNDAVDDARPUAVDD DPDMAVSS RREFXDCDNCONTROLOUT5CONTROLOUT4CONTROLOUT3CONTROLOUT2CONTROLOUT1CONTROLOUT0VDDCARDDATA1CARDDATA2GNDCARDDATA0SDCDNVSSHCPWR_V33SMCDNCFCDNMSINSVDD25VPVSSPVDDXOVDDHXICARDDATA3CARDDATA4CARDDATA5CARDDATA6CARDDATA7CARDDATA8CARDDATA9CARDDATA10CARDDATA11CARDDATA12CARDDATA14CARDDATA13AU6366 USB 2.0 Single LUN Multiple Flash Card Reader Controller V1.03W4Table 3.1 Pin DescriptionsPin #Pin NameI/ODescription1 CARDDATA15 I/O CF Data15/xD Data72 CFWTN I CF WAITN3 CLED O Card Operating LED4 CHIPRESETNI Chip Reset, Pull up with RC 5 GNDA PLL Ground 6 VDDA I PLL VDD 2.5V7 RPU I Connected with an 1.5k pull up resistor to 3.3 VDD 8 AVDD I Analog Power 3.3V 9 DP I/O DP 10 DM I/O DM11 AVSS Analog Ground12 RREF I Connected an 1k resistor to GND for impedance match13 PVDD I OSC Power 3.3V 14 XI I 12 MHz crystal input. 15 XO O 12 MHz crystal output. 16 PVSS OSC Ground 17 VDD25V O Core Power 2.5V 18 VDDH I 3.3V for IO pad 19 CPWR_V33 O Card Power 3.3V 20 VSSH Power Ground 21 MSINS I MS INS22 SMCDN I SMC Card Detect 23 CFCDN I CF Card Detect 24 SDCDN I SD Card Detect 25 XDCDN I xD Card Detect26 CONTROLOUT5 O CFRESETN and SMWRN/XDWRN 27 CONTROLOUT4 O CFWRN and SMRDN/XDRDN 28 CONTROLOUT3 O CFRDN and XDCEN/SMCEN 29CONTROLOUT2OCFAD2 and SMALE/XDALEAU6366 USB 2.0 Single LUN Multiple Flash Card Reader Controller V1.03W5Pin #Pin NameI/ODescription30 CONTROLOUT1 O CFAD1, MSCLK and SMCLE/XDCLE 31 CONTROLOUT0O CFAD0, SDCLK and MSBS 32 VDD I Core power 2.5V 33 GND Core Ground34 CARDDATA0 I/O CFDATA0, MSDATA0,and SDCMD 35 CARDDATA1 I/O CFDATA1,MSDATA1,XDWPN,and SMWPN 36 CARDDATA2 I/O CFDATA2,MSDATA2,and SDWP37 CARDDATA3 I/O CFDATA3,MSDATA3,SMRBN,and XDRBN 38 CARDDATA4 I/O CFDATA4 and SDDATA0 39 CARDDATA5 I/O CFDATA5 and SDDATA1 40 CARDDATA6 I/O CFDATA6 and SDDATA2 41 CARDDATA7 I/O CFDATA7 and SDDATA342 CARDDATA8 I/O CFDATA8,XDDATA0, and SDDATA4 43 CARDDATA9 I/O CFDATA9,XDDATA1, and SDDATA5 44 CARDDATA10 I/O CFDATA10,XDDATA2, and SDDATA6 45 CARDDATA11 I/O CFDATA11,XDDATA3, and SDDATA7 46 CARDDATA12 I/O CFDATA12 and XDDATA4 47 CARDDATA13 I/O CFDADA13 and XDDATA5 48CARDDATA14I/OCFDATA14 and XDDATA64. System Architecture and Reference Design4.1 A U 6366 B l o c k D i a g r a mFigure 4.1 AU6366 Block DiagramCF MD SMC SD MMC MS xDUSB Upstream PortAU6366 USB 2.0 Single LUN Multiple Flash Card Reader Controller V1.03W65. Electrical Characteristics5.1A b s o l u t e M a x i m u m R a t i n g sTable 5.1 Absolute Maximum RatingsSYMBOL PARAMETER RATING UNITS V DDH Power Supply -0.3 to V DDH +0.3 VV IN Input Signal Voltage -0.3 to 3.6 VV OUT Output Signal Voltage-0.3 to V DDH +0.3 VT STG Storage Temperature-40 to 150 O C5.2 Recommended Operating ConditionsTable 5.2 Recommended Operating ConditionsSYMBOL PARAMETER MIN TYP MAX UNITS V DDH Power Supply 3.0 3.3 3.6 V V DD Digital Supply 2.25 2.5 2.75 V V IN Input Signal Voltage 0 3.3 3.6 V T OPR Operating Temperature 0 70 O C 5.3G e n e r a l D C C h a r a c t e r i s t i c sTable 5.3 General DC CharacteristicsSYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITSI IN Input current No pull-up orpull-down-10 ±1 10 µAI OZ Tri-state leakage current-10 ±1 10 µA C IN Input capacitance Pad Limit 2.8 ρF C OUT Output capacitance Pad Limit 2.8 ρFC BID Bi-directional buffercapacitancePad Limit 2.8 ρFAU6366 USB 2.0 Single LUN Multiple Flash Card Reader Controller V1.03W 75.4D C E l e c t r i c a l C h a r a c t e r i s t i c s o f3.3V I/O C e l l sTable 5.4 DC Electrical Characteristics of 3.3V I/O CellsLimitsSYMBOL PARAMETER CONDITIONSMIN TYP MAXUNIT V DDH Power supply 3.3V I/O 3.0 3.3 3.6 V V il Input low voltage 0.8 VV ih Input high voltage LVTTL2.0 VV ol Output low voltage ∣I ol∣=2~16mA 0.4 V V oh Output high voltage ∣I oh∣=2~16mA 2.4 V R pu Input pull-up resistance PU=high, PD=low55 75 190 KΩR pd Input pull-down resistance PU=low, PD=high40 75 190 KΩI in Input leakage current V in= V DDH or 0 -10 ±1 10 μAI oz Tri-state output leakagecurrent-10 ±1 10 μA5.5U S B T r a n s c e i v e r C h a r a c t e r i s t i c sTable 5.5 Electrical characteristicsSymbol Parameter Conditions Min.Typ. Max.Unit VD33 Analog supply Voltage 3.0 3.3 3.6 V VDDUVDDADigital supply Voltage 2.25 2.5 2.75 VI CC Operating supply current High speed operatingat 480 MHz73mAI CC (susp)Suspend supply currentIn suspend mode,current with 1.5kΩpull-up resistor on pinRPU disconnected120µAAU6366 USB 2.0 Single LUN Multiple Flash Card Reader Controller V1.03W 8Table 5.6 Static characteristic:Digital pinSymbol Parameter Conditions Min. Typ. Max. UnitInput levelsV IL Low-level input voltage 0.8 V V IH High-level input voltage 2.0 VOutput levelsV OL Low-level output voltage 0.2 V V OH High-level output voltage VDDH-0.2V Table 5.7 Static characteristic:Analog I/O pins(DP/DM)Symbol Parameter Conditions Min.Typ. Max. UnitUSB2.0 Transceiver(HS)Input Levels(differential receiver)V HSDIFF High speed differentialinput sensitivity∣V I(DP)-V I(DM)∣measured at theconnection asapplication circuit300 mVV HSCM High speed data signalingcommon mode voltagerange-50 500mVSquelch detected 100 mVV HSSQ High speed squelchdetection threshold No squelch detected150 mVDisconnectiondetected625 mVV HSDSC High speed disconnectiondetection threshold Disconnection notdetected525mVOutput LevelsV HSOIHigh speed idle leveloutput voltage(differential)-10 10mVV HSOLHigh speed low leveloutput voltage(differential)-10 10mVV HSOHHigh speed high leveloutput voltage(differential)-360 400mVV CHIRPJ Chirp-J output voltage(differential)700 1100mVV CHIRPK Chirp-K output voltage(differential)-900 -500mVResistanceR DRV Driver output impedance Equivalent resistanceused as internal chiponly3 6 9 ΩAU6366 USB 2.0 Single LUN Multiple Flash Card Reader Controller V1.03W 9Overallresistanceincluding externalresistor40.5 45 49.5 TerminationV TERM Termination voltage forpull-up resistor on pinRPU3.0 3.6V USB1.1 Transceiver(FS/LS)Input Levels(differential receiver)V DI Differential inputsensitivity∣V I(DP)-V I(DM)∣0.2 VV CM Differential commonmode voltage0.8 2.5V Input Levels(single-ended receivers)V SE Single ended receiverthreshold0.8 2.0VOutput levelsV OL Low-level output voltage0 0.3 V V OH High-level output voltage 2.8 3.6 VTable 5.8 Dynamic characteristic:Analog I/O pins(DP/DM)Symbol Parameter Conditions Min.Typ. Max. UnitDriver CharacteristicsHigh-Speed Modet HSR High-speed differentialrise time500 pst HSF High-speed differential falltime500 psFull-Speed Modet FR Rise time CL=50pF;10 to 90﹪of∣V OH-V OL∣;4 20nst FF Fall time CL=50pF;90 to 10﹪of∣V OH-V OL∣;4 20nst FRMA Differential rise/fall timematching(t FR / t FF)Excluding the firsttransition from idlemode90 110 %V CRS Output signal crossovervoltageExcluding the firsttransition from idlemode1.32.0 VLow-Speed Modet LR Rise time CL=200pF-600pF;10 to 90﹪of∣V OH-V OL∣;75 300nsAU6366 USB 2.0 Single LUN Multiple Flash Card Reader Controller V1.03W 10t LFFall timeCL=200pF-600pF ;90 to 10﹪of ∣V OH -V OL ∣; 75 300 nst LRMA Differential rise/fall timematching (t LR / t LF )Excluding the firsttransition from idlemode80 125 % V CRS Output signal crossovervoltageExcluding the firsttransition from idlemode 1.3 2.0 V V OHHigh-level output voltage2.83.6VAU6366 USB 2.0 Single LUN Multiple Flash Card Reader Controller V1.03W115.6 P o w e r S w i t c h F e a t u r eFigure 5.1 Built-in card power switch I-V curve3.3V+/- 0.3V1ms to 10ms ( Depend Load Capacitor )CARD_POWERCARD_DETECT100ms + System Polling timingFigure 5.2 Card Detect Power-on TimingAU6366 USB 2.0 Single LUN Multiple Flash Card Reader Controller V1.03W126. Mechanical InformationFigure 6.1 Mechanical Information DiagramGAUGE PLANE SEATING PLANE1.60.15 1.45 0.16 BSC BSC BSC BSC BSC 0.270.75 REF1.JEDEC OUTLINE: MS-026 BBC2. DIMENSIONS D1 AND E1 DO NOT INCLUDE MOLD PROTRUSION.ALLOWABLE PROTRUSION IS 0.25mm PER SIDE. D1 AND E1 ARE MAXIMUM PLASTIC BODY SIZE DIMENSIONS IMCLUDING MOLD MISMATCH.3. DIMENSION b DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL NOT CAUSE THE LEAD WIDTH TO EXCEED THE MAXIMUM b DIMENSION BY MORE THAN 0.08mmAU6366 USB 2.0 Single LUN Multiple Flash Card Reader Controller V1.03W137. AbbreviationsIn this chapter some of the terms and abbreviations used throughout the technical reference manual are listed as follows.SIE Serial Interface EngineCF Compact FlashMD Micro DriveSMC SmartMedia CardMS Memory StickSD Secure DigitalMMC Multimedia CardUTMI USB Transceiver Macrocell InterfaceAbout Alcor Micro, Corp.Alcor Micro, Corp. designs, develops and markets highly integrated and advanced peripheral semiconductor, and software driver solutions for the personal computer and consumer electronics markets worldwide. We specialize in USB solutions and focus on emerging technology such as USB and IEEE 1394. The company offers a range of semiconductors including controllers for USB hub, integrated keyboard/USB hub and USB Flash memory card reader…etc. Alcor Micro, Corp. is based in Taipei, Taiwan, with sales offices in Taipei, Japan, Korea and California. Alcor Micro is distinguished by its ability to provide innovative solutions for spec-driven products. Innovations like single chip solutions for traditional multiple chip products and on-board voltage regulators enable the company to provide cost-efficiency solutions for the computer peripheral device OEM customers worldwide.AU6366 USB 2.0 Single LUN Multiple Flash Card Reader Controller V1.03W 14。

ISL6336资料

ISL6336, ISL6336A

Ordering Information

PART NUMBER

PART MARKING

TEMP. RANGE (°C)

PACKAGE (Pb-Free)

PKG. DWG. #

ISL6336CRZ*

ISL6336 CRZ0 来自o +7048 Ld 7x7 QFN

L48.7x7

Microprocessor loads can generate load transients with extremely fast edge rates and require high efficiency over the full load range. The ISL6336, ISL6336A utilizes Intersil’s proprietary Active Pulse Positioning (APP) and Adaptive Phase Alignment (APA) modulation scheme and a proprietary active phase dropping/adding and diode emulation scheme to achieve extremely fast transient response with fewer output capacitors and high efficiency from light load to full load.

• Precision Multiphase Core Voltage Regulation - Differential Remote Voltage Sensing - ±0.5% System Accuracy Over Life, Load, Line and Temperature - Bi-directional Adjustable Reference-Voltage Offset

OB6663L Datasheet

FEATURES

■

■ ■ ■ ■ ■ ■ ■ ■ ■ ■ ■ ■ ■ ■

on

ht C

O

nBr

©On-Bright Electronics

ig

fid en tia

Integrated Transition Mode (TM) PFC Controller and Quasi-Resonant (QR) PWM Controller Built-in Dual Output PFC Control Multi-Mode Operation for QR Stage Separated AGND and PGND Provide Better Noise Immunity Analog Multiplier with Built-in THD Optimizer for PFC Stage Line Feed-forward Compensation for PFC Stage Enhanced Dynamic Response for PFC Stage Less than 200mW Standby Power Consumption Minimum QR Short Circuit Power Consumption Audio Noise Free Operation External Latch Triggering for Both Converters Minimum OFF time for Ringing Suppression Maximum ON Time Limit for QR Converter Built-in 4ms Soft Start for QR Converter Internal Leading Edge Blanking for Both Converters

BATT-3V6;EL-USB-3;中文规格书,Datasheet资料

Martel Electronics Corporation T el: 800-821-0023PO Box 770Email: sales@ Londonderry, NH 03053 USAWeb: © Copyright 2005 Martel Eectronics CorporationAll trademarks are the property of their respective owners.P/N 000000000 Rev. xFEATURESORDERING INFORMATIONStock Number Standard Data LoggerEL-USB-3(Data Logger,Measurement Leads,Software on CD and Battery)Replacement BatteryBAT 3V6•0-30V d.c.Measurement Range •Logging Rates between 1s and 12hr •Stores 32,510readings•Connection via two screw terminals•USB Interface for Set-up and Data Download •User-Programmable Alarm Thresholds •Red and Green LED Status Indication •Replaceable Internal Lithium BatteryEL-USB-3Voltage USB Data LoggerThis data logger measures and stores up to 32,510voltage readings over a 0-30V d.c.measurement range.The user can easily set up the logging rate and start time,and download the stored data by plugging the module straight into a PC's USB port and running the purpose designed software under Windows 98,2000or XP .The data can then be graphed,printed and exported to other applications.The data logger is supplied complete with a long-life lithium battery.Correct functioning of the unit is indicated by flashing red and green LED.The data logger features a pair of screw terminals and is is supplied complete with a set of measurement leads terminating in crocodile clips.WINDOWS CONTROL SOFTWAREEasy to install and use,the control software runs under Windows 98,2000and XP (Home and ProfessionalEditions).It allows the user to set up and download any EL-USB-3.The latest version of the control software may be downloaded from . DATA LOGGER SET-UPS•Logger Name•Logging Rate (1s,10s,1m,5m,30m,1hr,6hr,12hr)•High and Low Alarms •Start Date and Start Time*depending on ambient temperature,logging rate and use of alarm LED./2Martel Electronics Corporation DT -EL -USB3EL-USB-3Voltage USB Data LoggerLED FLASHING MODESEL-USB-3features a red and a green LED.The LEDs on an EL-USB-3will flash in one of the following ways,assuming alarm latching is turned off (exact timings to be confirmed).By default latching is disabled,so the red LED will continue to flash,even after the logged voltage has returned to normal.The red LED will effectively have latched into its alarm condition.This feature ensures that the user is notified that an alarm level has been exceeded,without the need to download the data from the logger.Latching can be turned on via the control software.The red LED will then no longer continue to flash after the logged voltage has returned to normal.Instead,the green LED will then flash.-Green single flash,Logger primed and ready to start.every 30seconds-Green single flash,Logging in progress,last stored value OKevery 10seconds -Red single flash,Logging in progress,the last stored reading is equal to or the low alarm level every 10seconds (If latching is turned on,then a stored value is equal to or exceeds the low alarm level)-Red double flash Logging in progress,the last stored reading is equal to or exceeds the high alarm level every 10seconds(If latching is turned on,then a stored value is equal to or exceeds the high alarm level)-Green single flash,Low battery,logging in progress,the last stored value OKevery 20seconds -Red single flash,Low battery,logging in progress,the last stored value is equal to or exceeds the low alarm levelevery 20seconds -Red double flash,Low battery,logging in progress,the last stored value is equal to or exceeds the high alarm levelevery 20seconds-Green double flash,Logger is full,last stored value OKevery 20seconds -Red/Green single flash,Logger is full,last stored value is equal to or exceeds the low or high alarm levelevery 20seconds,alarm latching turned on -No LEDs flashLEDs disabled during configuration to save battery power and increase logging duration.orBattery dead.exceeds /DT -EL -USB3Martel Electronics Corporation 3EL-USB-3Voltage USB Data Loggerbattery voltage /分销商库存信息:MARTEL-ELECTRONICSBATT-3V6EL-USB-3。

61113中文资料

61113 GENERAL PURPOSE (NPN) TRANSISTOR SURFACE MOUNT PACKAGE(2N2369AUB)Mii OPTOELECTRONIC PRODUCTSDIVISIONFeatures:• Hermeticallysealed •Hermetically sealed 3 pin LCC •MIL-PRF-19500 screening available A pplications:• AnalogSwitches• SignalConditioning •Small Signal Amplifiers • HighDensityPackagingDESCRIPTIONThe 61113 is a N-P-N, general-purpose switching and amplifier transistor in a 3 pin leadless chip carrier package. All packages are hermetically sealed for high reliability and harsh environments. This device is available custom binned to customer specifications in commercial or screened to MIL-PRF-19500 up to JANS level.ABSOLUTE MAXIMUM RATINGSCollector-Base Voltage - V CBO.................................................................................................................................................40Vdc Collector-Emitter Voltage - V CEO..............................................................................................................................................15Vdc Collector-Emitter Voltage - V CES..............................................................................................................................................40Vdc Emitter-Base Voltage - V EBO...................................................................................................................................................4.5Vdc Collector Current – I C(Peak).......................................................................................................................................................500mA Continuous Collector Current ................................................................................................................................................200mA Maximum Junction Temperature...........................................................................................................................................+200°C Operating Temperature (See part selection guide for actual operating temperature)............................................-65°C to +125°C61113 SURFACE MOUNT NPN GENERAL PURPOSE TRANSISTOR (TYPE 2N2369AUB) ELECTRICAL CHARACTERISTICST A = 25°C unless otherwise specified.PARAMETER SYMBOL MIN MAX UNITS TEST CONDITIONS NOTE Collector-Base Breakdown Voltage BV CBO40V dc I C = 10µA, I E= 0Collector-Emitter Breakdown Voltage BV CEO40V dc I C= 10µA , I B= 0µACollector-Emitter Sustaining Voltage BV CES15V dc I C= 10m A , I B= 0µAEmitter-Base Breakdown Voltage BV EBO 4.5V dc I C= 0, I E= 10µACollector-Base Cutoff Current I CBO0.4µA V CB = 20V, I E = 030µA V CB = 20V, I E= 0, T A = 150°CCollector-Emitter Cutoff Current I CES0.4µA V CE = 20VForward-Current Transfer Ratio h fe-120-V CE = 1V, I C = 10mAh fe20-V CE = 1V, I C = 100mAh fe20-V CE = 2V, I C = 100mAh fe420-V CE = 1V, I C = 10mA @ -55ºC1h fe630-V CE= 0.35V, I C = 10mA @ -55ºCCollector-Emitter Saturation Voltage V CE (SAT)0.20V I C = 10mA, I B= 1mA1V CE (SAT)0.30V I C = 10mA, I B= 1mA @ +125ºCV CE (SAT)0.25V I C = 30mA, I B= 3mAV CE (SAT)0.50V I C = 100mA, I B= 10mA1 Base-Emitter Saturation Voltage V BE (SAT)0.70.85V I C = 10mA, I B= 1mA1V BE (SAT)0.59-V I C = 10mA, I B= 1mA @ +125ºCV BE (SAT) 1.02V I C = 10mA, I B= 1mA @ -55ºC1.15V I C = 30mA, I B= 3mAV BE (SAT) 1.60V I C = 100mA, I E= 10mA1SMALL-SIGNAL CHARACTERISTICSCurrent-Gain – Bandwidth Product f r500MHz V CB = 10V, 100kHz, < f < 1 MHzC IBO25pF V EB = 0.5 V, 100kHz, < f < 1 MHzInput Capacitance(Output Open Capacitance)Turn-On Time t on35nS V CC= 30V, I C = 150mA,I B1 = 15mATurn-Off Time t off300nS V CC = 30V, I C = 150mA,I B1 = I B2 = 15mANOTES:1. Pulse width < 300µs, duty cycle <2.0%.SELECTION GUIDEPART NUMBER PART DESCRIPTION61113-0012N2369AUB PNP transistor, commercial version61113-0022N2369AUB PNP transistor, JAN level screening61113-0032N2369AUB PNP transistor, JANTX level screening61113-0042N2369AUB PNP transistor, JANTXV level screening61113-0052N2369AUB PNP transistor, JANS level screeningNOTE: Also available in dual and quad configurations upon request. Can also be supplied in gull wing surface mount versions.。

A67L7336E-4.5中文资料

NC NC NC VCCQ VSSQ NC NC I/Ob0 I/Ob1 VSSQ VCCQ I/Ob2 I/Ob3 VCC VCC VCC VSS I/Ob4 I/Ob5 VCCQ VSSQ I/Ob6 I/Ob7 I/Ob8/NC NC VSSQ VCCQ NC NC NC

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50

PRELIMINARY

(December, 1999, Version 0.1)

1

AMIC Technology, Inc.

DBA and Direct Bus Alternation are trademarks of AMIC Technology, Inc

元器件交易网

Block Diagram (128K X 32/36)

ZZ MODE

MODE LOGIC

ADV/LD

CEN CLK

CLK LOGIC

BURST LOGIC ADDRESS COUNTER CLR

A0-A16

ADDRESS REGISTERS

WRITE ADDRESS REGISTER

WRITE ADDRESS REGISTER

8/9

BYTEa WRITE DRIVER BYTEb WRITE DRIVER BYTEc WRITE DRIVER BYTEd WRITE DRIVER

8/9

8/9 ADV/LD R/W BWE BW1 BW2 BW3 BW4 WRITE REGISTRY & CONTROL LOGIC

UPA672T-T1-A;中文规格书,Datasheet资料