TLC320AC02IFN中文资料

tlc5620中文资料

tlc5620中文资料2010-01-13 11:00TLC5620C, TLC5620IQUADRUPLE 8-BIT DIGITAL-TO-ANALOG CONVERTERS Four 8-Bit Voltage Output DACs4通道8位电压输出D/A转换器。

5-V Single-Supply Operation5V单电源Serial Interface串行接口High-Impedance Reference Inputs高阻抗的基准输入Programmable 1 or 2 Times Output Range可编程实现1至2倍的输出范围Simultaneous Update Facility设备可同时进行更新Internal Power-On Reset内置上电复位Low-Power Consumption低功耗Half-Buffered Output半缓冲输出Applications应用Programmable Voltage Sources可编程电源Digitally Controlled Amplifiers/Attenuators可数字控制的放大器和衰减器Mobile Communications移动通信Automatic Test Equipment自动测试设备Process Monitoring and Control过程监控Signal Synthesis信号合成Description描述The TLC5620C and TLC5620I are quadruple 8-bit voltage outputdigital-to-analog converters (DACs) with buffered reference inputs (high impedance). The DACs produce an output voltage that ranges between either one or two times the reference voltages and GND, and the DACs are monotonic. The device is simple to use, running from a single supply of 5 V. A power-on reset function is incorporated to ensure repeatable start-up conditions.TLC5620C和TLC5620I是带有高阻抗缓冲输入的4通道8位电源输出数模转换器集合。

CCL300DC3-ACF2中文资料

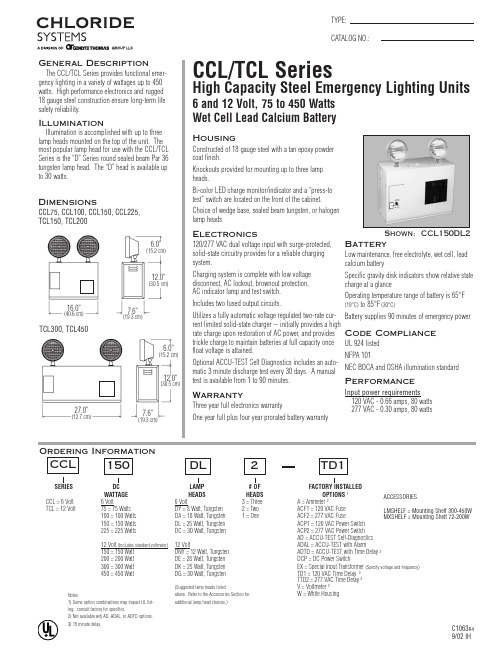

ACCESSORIESLMSHELF = Mounting Shelf 300-450W MXSHELF = Mounting Shelf 72-200WOrdering InformationSERIES DC WATTAGE HEADS HEADS OPTIONS 1CCL = 6 Volt 6 Volt6 Volt3 = Three A = Ammeter 2TCL = 12 Volt75 = 75 Watts DY = 8 Watt, Tungsten 2 = Two ACF1 = 120 VAC Fuse 100 = 100 Watts DA = 18 Watt, Tungsten 1 = OneACF2 = 277 VAC Fuse 150 = 150 Watts DL = 25 Watt, Tungsten ACP1 = 120 VAC Power Switch 225 = 225 WattsDC = 30 Watt, Tungsten ACP2 = 277 VAC Power Switch AD = ACCU-TEST Self-Diagnostics 12 Volt (Includes standard voltmeter)12 VoltADAL = ACCU-TEST with Alarm150 = 150 Watt DNY = 12 Watt, Tungsten ADTD = ACCU-TEST with Time Delay 3200 = 200 Watt DE = 28 Watt, Tungsten DCP = DC Power Switch300 = 300 Watt DK = 25 Watt, Tungsten EX = Special Input Transformer (Specify voltage and frequency)450 = 450 WattDG = 30 Watt, TungstenTD1 = 120 VAC Time Delay 3TTD2 = 277 VAC Time Delay 3(Suggested lamp heads listedV = Voltmeter 2above. Refer to the Accessories Section for W = White Housingadditional lamp head choices.)CCL15016.0”(40.6 cm)TCL300, TCL4506.0”(15.2 cm)7.6”(19.3 cm)12.0”(30.5 cm)27.0”(12.7 cm)6.0”(15.2 cm)7.6”(19.3 cm)12.0”(30.5 cm)Notes:1) Some option combinations may impact UL list-ing. consult factory for specifics.2) Not available witj AD, ADAL, or ADTD options.3) 15 minute delay.元器件交易网Housing18 gauge steel housing with a tan epoxy powder coat finish.Knockouts provided for mounting up to three lamp heads.The suggested lamp head is the “D” Series round sealed beam Par 36 tungsten. To order lamp heads other than the suggested “D” head, refer to Chloride Accessories Section..Suggested SpecificationFurnish and install Chloride Systems emergency lighting unit model ________. The unit shall be constructed to meet Underwriter’s Laboratories, Inc. Standard #924and the National Electrical Code (NEC).INSTALLATION AND OPERATION -Unit shall be easily field connected to a 120 or 277 VAC, 60 hertz, unswitched power source. Installation must comply with the NEC as well as other applicable codes. Upon utility power failure or brownout, the unit shall automatically transfer to battery power and maintain the required illumina-tion level for a minimum period of 90 minutes. Upon restoration of utility power, the charger shall restore the battery to full charge within UL 924 requirements follow-ing a rated discharge of not more than 90 minutes.CHARGER -Product shall utilize a fully automatic, voltage regulated, two-rate current limited solid-state charger. The charging system shall maintain the battery at full capacity without the need for periodic exercising or equalization. The following features shall be standard: Low voltage disconnect (LVD), brownout protection and AC lockout.BATTERY -The battery shall be a low maintenance, free electrolyte, wet cell, lead calcium battery. The lead calcium battery shall provide trouble-free operation in temperatures up to 85°F (30°C).HOUSING -The unit housing shall be constructed of 18 gauge steel with a tan epoxy powder coat finish.Chloride SystemsISO8C1063R49/02 IH272 West Stag Park Service Road •Burgaw NC 28425Telephone: (910) 259 1000 •Facsimile: (800) 258 Lamp Head Photometrics(For DL, suggested head for CCL)(For DK, suggested head for TCL)Vertical203050100Up 2010feet 010Down 20.2.1406070.31.5Horizontal203050100Left 2010feet 010Right 20.2.1406070.31.5203050100Up 2010feet 010Down 20Photometric No. 3406070801.3.2.1.5Horizontal203050100Left 3010feet 01020Right 301.3.2.120.540607080。

Protek 3201_3290N 中文说明书_东方嘉仪

误动作时

U

U

虽然此仪器的电源可以开机,如有误动作(不正常工作或死机现象)时,请按照下述步骤安 全使用。

1) Protek 3201N/3290N接上电源(电源适配器AC Adapter)。 2) 按Reset 键。 (Reset 键在 Battery 装入口的底面) 3) 不正常工作时, 另外有一种方法是 通过系统菜单(Menu)的测试(TEST)组上选择

PC电脑连接(Connection for PC)……………………………………………………………64

自动电源Auto Power……………………………………………………………………………65

偏置Offset……………………………………………………………………………………66

菜单(Menu)…………………………………………………………………………………67

电 话 :(青 岛 )0532-86069117 (南京)025-52405707 (天津)022-60501825

9

3201N/3290N 用户手册

仪器仪表销售 注册品牌

存储 /读出Save/Load ………………………………………………………………………54

频率计数器(Frequency Counter)………………………………………………………58

RESET 键即可。

电池 (Battery)

U

此仪器使用Ni-MH Rechargeable Battery(镍-氢充电电池;以下称Ni-MH充电电池) 6个,可 以充电后使用。

1) Ni-MH充电电池为消耗品,随着使用时间的增加,Ni-MH充电电池的寿命会缩短。 2) Ni-MH 充电电池的实际使用时间,缩短为刚刚购买时的实际使用时间一半时请更换

Powertec i250C i320C电气方案备用零件说明说明书

Spare Parts - Electrical Schematic Spare Parts - Electrical Schematic1 IM3070 09/2018 REV03POWERTEC i250C STANDARD POWERTEC i250C ADVANCED POWERTEC i320C STANDARDPOWERTEC i320C ADVANCEDSpare Parts (2)Figure A: Powertec i250C/i320C STD/ADV Machine Assembly .................................................................................. 2 Figure B: Powertec i250C/i320C STD/ADV Inside Machine Assembly ....................................................................... 4 Figure C: Powertec i250C/i320C STD/ADV Wire Drive Assembly ............................................................................... 5 Figure D: Powertec i250C/i320C STD Front Assembly ................................................................................................ 6 Figure E: Powertec i250C/i320C ADV Front Assembly (6)Electrical Schematic (8)Lincoln Electric Bester Sp. z o.o.ul. Jana III Sobieskiego 19A, 58-263 Bielawa, Polandwww.lincolnelectric.euSpare Parts - Electrical Schematic Spare Parts - Electrical Schematic2 Spare PartsSP50430, SP50431, SP50432, SP50433 REV03ASSEMBLY PAGE NAMEP o w e r t e c M a c h i n e A s s e m b l yM a c h i n e F r o n t A s s e m b l y W i r e D r i v e A s s e m b l y & E u r o S o c k e t A s s e m b l yP o w e r t e c i 250C /i 320C S T D F r o n t A s s e m b l y P o w e r t e c i 250C /i 320C A D V F r o n t A s s e m b l y M i s c e l l a n e o u s I t e m s CODE NO.: K NO.: FIGURE NO.:A B C D E - 50430POWERTEC i250C STANDARD 1 1 1 1 - 1 50431 K14157-2 POWERTEC i250C ADVANCED 2 2 2 - 2 2 50432 K14158-1 POWERTEC i320C STANDARD 3 3 3 3 - 3 50433 K14158-2 POWERTEC i320C ADVANCED 444-44Figure A: Powertec i250C/i320C STD/ADV Machine AssemblyItem Description Part Number QTY 1 2 3 4 5 6 CABLE GRD-300A-50-5M 1 x x x x1 WELDING2 SIDE PANEL KIT R-1019-486-1R 1 x x x x3 COVERKIT R-3019-455-1/02R 1 x x x x4 HANDLE R-0010-292-1R 1 x x x x5 BASE, PARTITION, SHELF KIT R-3019-426-1R 1 x x x x6 SIDE COVER KIT R-0010-623-1R 1 x x x x7 FRONT AND REAR PANEL KIT R-8040-387-1R 1 x x x x8 LOCK 0654-610-004R 2 x x x xHINGE 0654-610-007R 2 x x x x9 LEAF10 MAIN INPUT CORD R-5041-497-1R 1 x x x x11 WHEELS 1029-660-127R 2 x x x x12 WHEELS 1029-660-250R 2 x x x xSpare Parts - Electrical Schematic Spare Parts - Electrical Schematic3Spare Parts - Electrical SchematicSpare Parts - Electrical Schematic4Figure B: Powertec i250C/i320C STD/ADV Inside Machine AssemblyItem DescriptionPart NumberQTY 1 2 3 4 5 6 13 TRANSFORMER AND CHOKE R-8040-382-2R 1 x x x x 14 INVERTER BOARD R-6042-079-1R 1 x x x x 15 HALL SENSOR W4900004R 1 x x x x 16 FAN W66X1369R 2 x x x x 17 INPUT FILTER Y051-1R1 x x x x 18 SOLENOID 0972-423-040R 1 x x x x 19 CABLE RELIEF1361-599-674R 1 x x x x 20FUSE SOCKET 1158-632-032R 1 x x x x FUSE 1A 400V 1158-660-003R 1 x x x x 21 PC BOARD R-6042-081-1R 1 x x x x 22 WIRE SPOOL HUB 0744-000-335R 1 x x x x 23 PLASTIC NUT 0744-000-336R 1 x x x x 24 USB SOCKET 1158-641-061R 1 - x - x 25 SWITCH1115-280-004R 1 x x x x 26 THREE PHASE BRIDGE1156-112-206R 1 x x x x 27CONTROL BOARD R-6042-082-2R 1 x - - - CONTROL BOARD R-6042-082-1R 1 - x - - CONTROL BOARD R-6042-080-2R 1 - - x - CONTROL BOARD R-6042-080-1R 1 - - - x 28 OUTPUT BRIDGE R-8040-388-1R 1 x x x x 29 LED MODULE R-5041-508-1R 2x x x xFigure C: Powertec i250C/i320C STD/ADV Wire Drive AssemblyItem Description Part Number QTY 1 2 3 4 5 6 30 WIRE DRIVE MOTOR 1111-722-048R 1 x x x x31 COMPLETE FEED PLATE ASSEMBLY(INCLUDES 1.0/1.2 MM DRIVE ROLLS ANDWIRE GUIDE KIT)0744-000-009R 1 x x x xSpare Parts - Electrical Schematic Spare Parts - Electrical Schematic5Spare Parts - Electrical SchematicSpare Parts - Electrical Schematic6Figure D: Powertec i250C/i320C STD Front AssemblyFigure E: Powertec i250C/i320C ADV Front AssemblyItem Description Part Number QTY 1 2 3 4 5 632 DISPLAY FRONT PANEL KIT R-0010-619-2R 1 x - x -33 USER INTERFACE PCB R-6042-078-1R 1 x - x -34 KNOB 9SM22778-2 2 x - x -35 BUTTON 9SS23055 2 x - x - 1 - x - x36 MAIN SWITCH 1115-270-022R 1 x x x x37 EURO SLEEVE C-1891-006-1R 1 x x x x38 SOCKET W7690350 R 2 x x x x39 PCB R-6042-077-1R 1 - x - x40 DISPLAY FRONT PANEL KIT R-0010-618-2R 1 - x - x41 LCD 0942-177-002R 1 - x - x42 KNOB 9SM22778-3 2 - x - xMiscelaneous Items (not shown in figure A, B, C, D, E)Item Description Part Number QTY 1 2 3 4 5 643 HARNESSES KIT R-5041-494-1R 1 x x x xSpare Parts - Electrical Schematic Spare Parts - Electrical Schematic7Electrical SchematicSpare Parts - Electrical Schematic Spare Parts - Electrical Schematic8234Spare Parts - Electrical Schematic Spare Parts - Electrical Schematic9。

TLC272_02中文资料

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

1

元器件交易网 TLC272, TLC272A, TLC272B, TLC272Y, TLC277 LinCMOS PRECISION DUAL OPERATIONAL AMPLIFIERS

SLOS091E – OCTOBER 1987 – REVISED FEBRUARY 2002

D Trimmed Offset Voltage: D D

D D D D D D

NC 1IN – NC 1IN + NC

4 5 6 7 8

3 2 1 20 19 18 17 16 15 14 9 10 11 12 13

NC 1OUT NC VDD NC NC 2OUT NC 2IN – NC

NC – No internal connection

SLOS091E – OCTOBER 1987 – REVISED FEBRUARY 2002

equivalent schematic (each amplifier)

VDD P3 P4 R6

R1 IN – P1 IN +

R2

N5 P5 P6

实验3 信号发生器实验

a=2πf0/fS=2π/N=2π/16=0.3927 首先在程序中计算出cos(a)及初始值y[0]和y[1]。 cos(a)= 0.9238795; y[0]=sin(0)=0; y[1]=sin(a )=0.382683; n≥2以后的y[n]的值,通过递归计算得出。

2020/5/13

/* write to handset codec */ *(volatile u16*)DXR1_ADDR(HANDSET_CODEC)=data;

2020/5/13

3.产生连续的波形的方法

利用DSP和D/A转换器可以产生连续的正弦波信 号,以及矩形波、锯齿波、三角波等其它各种信号 波形。 产生连续的波形的方法一般有两种:

i&=0x00ff; //mod 255

out_buffer[j]=amp*SINE_TABLE[i];//数据存放在数组中

j++;

//amp为放大倍数

j&=0x00ff;

2020/5/13

三、实验内容

1.分别利用计算法和查表法产生1000Hz的余弦波 信号,比较两者的特点,并使用示波器观测产生 信号的频率和幅度。 2. 分别利用泰勒级数及递归差分方程计算法产生 1000Hz的正弦波信号,比较其输出。 3.利用计算法产生其他非正弦类周期信号波形, 如周期矩形波、三角波、锯齿波等。利用示波器 可以能通过SPEAKER(J6)端口观察到这些波形吗?

查表法部分参考程序

s16 SINE_TABLE[]={

0x00324

,0x00647 …};//存放原始数据表,256字

// 输出信号频率的计算:f=fs/(256/N),一个周期取点数为N

i=i+1; //62.5HZ

Infineon单片机详解

开发板电路图

CPU部分 电源部分 JTAG接口与启动配置 串行接口电路 CAN接口电路 LIN接口电路 LED 电路 EEPROM电路

非屏蔽中断 辅助晶振

CPU部分

主晶振

带上划线符号为低电平有效 复位引脚 片选信号 异步/同步 串行接口

地址/数 据总线

比较/捕 获模块

定时器引脚 输入

数据存储区地址映射

程序存储区

XC167中有两个片上程序存储区,用于代码/数据存储 256KB程序FLASH/ROM,C0‘0000H…C3‘FFFFH存储 代码和常量数据。FLASH可以通过软件(反复)编 程,ROM只能在工厂掩模编程 6KB程序SRAM(PSRAM)E0‘0000H…E0‘17FFH存储 临时代码和其它数据,比如高级引导加载程序可写 在PRAM中,继而执行该程序对片上存储器进行编程

XC167CI实验板功能模块介绍

XC167-CI实验板

XC167CI简装开发板的特点

英飞凌系列的XC167CI采用的是TQFP144 的封装形式 板上的双重电源可以为XC167CI提供5V伏 / 2点6伏的电压。 高速的CAN收发器,LIN 收发器,EPROM, URAT(RS232串口) 8位低功耗的LED

第三章:体系结构

存储器组织 中央处理器

XC167CI芯片模块框图 双端口RAM

可编程FLASH 片上调试支持 实时控制 看门狗定时器 晶振/锁相环 中断和外围 事件控制器 程序RAM 程序管理单元 数据管理单元

数据 RAM

异步/同步 AD转换器 串行接口

高速同步串 行接口

外围总线控制 比较/捕获 单元 TwinCAN 模块

TLC0820A中文资料

2008年北京市大学生电子设计竞赛芯片资料TLC372 双路通用LinCMOSTM 差动比较器∙单电源或双电源供电∙宽电源范围供电2V~18V∙5V电源时低漏电流150μA∙TTL输入电平时快速响应时间200ns∙内置ESD保护∙高输入阻抗典型值1012Ω∙外部低输入偏置电流典型值5PA∙超稳定的低输入偏置电压∙输入失调电压在最恶劣的输入条件下变化0.23μV/月,包括第一个30天∙共模输入电压包括地∙输出兼容TTL MOS CMOS∙引脚兼容LM393引脚功能∙1IN - 1路比较器反相输入∙1IN+ 1路比较器通向输入∙1OUT 1路比较器输出∙2IN - 2路比较器反相输入∙2IN+ 2路比较器同相输入∙2OUT 2路比较器输出∙GND 电源地∙VCC 电源正∙NC 空脚,不连接这个器件由两个独立电压比较器,使用LinCMOSTM工艺制造的,支持单电源。

输出是N 沟道漏极开路,实现正逻辑连接。

完全最大的测定值运行环境范围(除非另行注释)支持电压VDD(注释1)...............................................................+18V差分输入电压VID(注释2)...........................................................±18V输入电压范围.....................................................................-0.3~18V输出电压VO (18V)输入电流II ......................................................................±5mA输出电流IO.......................................................................20mA输出短路到地持续电流.............................................................无限制注释:1、差分电压除外,全部电压相对于地。

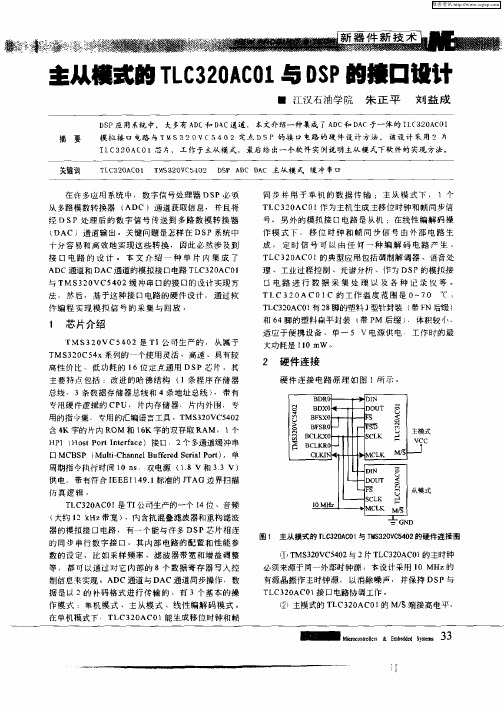

主从模式的TLC320AC01与DSP的接口设计

口 MC P ( l . h n e fee e il ot . 单 BS Mut C a n l i Bu rdS ra P r)

接 口 电路 的 设 计 。 本 文 介绍 一 种 单 片 内集 成 了 A DC通道 和 D AC通 道 的模 拟 接 口电 路 T C 2 A 0 L 30 C 1 与 T S 2 VC5 0 M 0 3 4 2缓 冲 串 口的接 口的 设计 实瑚 方

TL 3 0 C 2 AC0 1的典型应用包括调制解调 器 、语音处 理 、工业 过 程控 制 、光谱 丹析 、作 为 DS P的模 拟 接

维普资讯

圭从模式的 T C 2A O 与 D P L 3 0 C I S 的接口设计

一 江 汉石 油 学 院 朱 正 平 刘 益 成

关 键词

T C E A O T S 2 V 5 0 I P A C D C 主 从模 式 缓冲 串口 L B O C I  ̄ 3 0 C 4 2 ) D A S 同 步 并 用 于 单 机 的 数 据 传 输 j主 从 模 式 下 . 1个

据 是以 2的补码格式 进行传输 的 。有 3个基本的操 作模式 :单机模 式 、主 从模 式 、线性编解 码模式 。 在单机模 式下 .T C3 0 C0 L 2 A 1能生成移位时钟和 帧

维普资讯

新 器 件 新 技 术

从模 式 的 T 3 0 LC 2 AC0 的 M/ 1 g接地 S M # 1hI T 00, MR

RS X I M B NT S B XM S XS

爱台顿:智能地址可编号火警传感器CAP320、CAPT340、CAH330数据手册说明书

Intelligent addressable sensorsCAP320, CAPT340, CAH330This range of intelligent addressable sensors have been specifically designed to operate with Eaton’s intelligent addressable fire systems.All sensors are third party approved to the relevant section of EN54 (part 7 for smoke detectors, part 5 for heat detectors and part 17 for short circuit isolators).The optical sensor (CAP320) is suitable for mostapplications giving the fastest response to slow burning or smouldering fires which give rise to large visible smoke particles.The photo-thermal sensor (CAPT340) will respond quickly to fast clean burning fires yet maintain the advantage of optical sensors when detecting smouldering fires The thermal enhancement of this sensor allows a higher alarm threshold which provides a greater rejection of false alarms. The sensor will also raise an alarm at temperatures exceeding 60ºC.The CAPT340 has day/night modes available,programmeable from the site installer software. The day mode uses the heat aspect of the sensor for areas which may have smoky environments during, for example working hours. The night mode uses a combination of A2S and smoke detection. If not programmed, the sensor defaults to dual mode.The heat sensor (CAH330) can be set to one of 3 modes 77ºC / 92ºC and rate of rise. These sensors are designed to be used in environments where the ambient conditions might cause false alarms if smoke detection were to be used, for example where there is a high level of dust, fumes, steam or smoke under normal conditions.Features• Soft addressed• Integral short circuit isolator • Single address• Wide range of sensor types• 360° visibility LED using lightpipe technology • Drift compensation •Aesthetically pleasingBenefits• Quick and simple to install • Single “multi-mode” heat sensor• Wide viewing angle for increased LED visibility • Common mounting base • Positive “lock” indication• Discreet design for incorporation into any decor •Easy to maintain/serviceT echnical specificationCode CAP320CAPT340CAH330Description Optical smoke sensorPhoto-Thermal sensorMulti-Mode heat sensorStandards EN54 Pt7 2000 + A1:2002, EN54 Pt17EN54 Pt5 2000 + A1:2002, EN54 Pt7 2000 + A1:2002, EN54 Pt 17EN54 Pt5 2000 + A1:2002, EN54 Pt17Operating volatage 18V dc to 30V dc 18V dc to 30V dc 18V dc to 30V dc Standby current 220μA (max)220μA (max)220μA (max)Alarm current 5mA (max)5mA (max)5mA (max)Addressing mode Auto addressAuto addressAuto addressSpecification Mounting position Ceiling in open areasCeiling in open areasCeiling in open areasMounting options Surface mount with CAB300 base Surface mount with CAB300 base Surface mount with CAB300 base Area coverage 100m² (subject to local standard)100m² (subject to local standard)100m² (subject to local standard)System wiringMin. 1.5mm, 2 core loop or spur Min. 1.5mm, 2 core loop or spur Min. 1.5mm, 2 core loop or spurHeat class Rate of Rise N/A A1S A1R Fixed Heat 77ºC N/A N/A BS Fixed Heat 90ºCN/AN/ACSAlarm Temperature (static)AIR N/A 60ºC 60ºC BS N/A N/A 77ºC CSN/AN/A90ºCIndication360° visibility light pipe360° visibility light pipe360° visibility light pipeEnvironmentalOperating temperature -10°C to +60°C -10°C to +50°C -10°C to +60°C Humidity (non condensing)0 to 95% RH 0 to 95% RH 0 to 95% RHPhysical Construction PC/ABS PC/ABS PC/ABS Colour - Ral No.White - 9003White - 9003White - 9003Dimensions excel base (Dia x D)101mm x 33mm 101mm x 43mm 101mm x 43mm Dimensions incl base (Dia x D)104mm x 45mm 104mm x 55m 104mm x 55mm Weight (without base)76g 76g 76g IP RatingIP30IP30IP30CompatibilitySuitable for use withEaton: Cooper addressable fire systems Eaton: Cooper addressable fire systems Eaton: Cooper addressable fire systemsLED state LED state behaviour System eventOff LED is not illuminated.Global flash is disabled**.Slow flash Momentary flash approximately once every 30 seconds*.Global flash enabled. Detector is in quiescent state.Fast flashMomentary flashapproximately 25 times per minute*.>24 detectors are in fire state.OnLED is constantly illuminated.Detector is in fire state.*Timing can vary depending on loop address quantities.** D etector flash in quiescent state can be disabled via control panel menu (CF3000, CF1100, CF2000).LEDsDescriptionCodeCAP320 Optical smoke sensor 400002FIRE-0002X CAPT340 Photo/Thermal sensor 400004FIRE-0004X CAH330 Multi-Mode heat sensor 400003FIRE-0003X Standard baseCAB300Conventional remote indicatorCIR301Duct probe (requires detector & base)MDP201Loop connected remote indicatorMRIADCatalogue numbersEatonEMEA Headquarters Route de la Longeraie 71110 Morges, Switzerland Eaton.eu© 2019 EatonAll Rights ReservedPublication No. TD-EN-1219December 2019Eaton is a registered trademark.All other trademarks are property of their respective owners.。

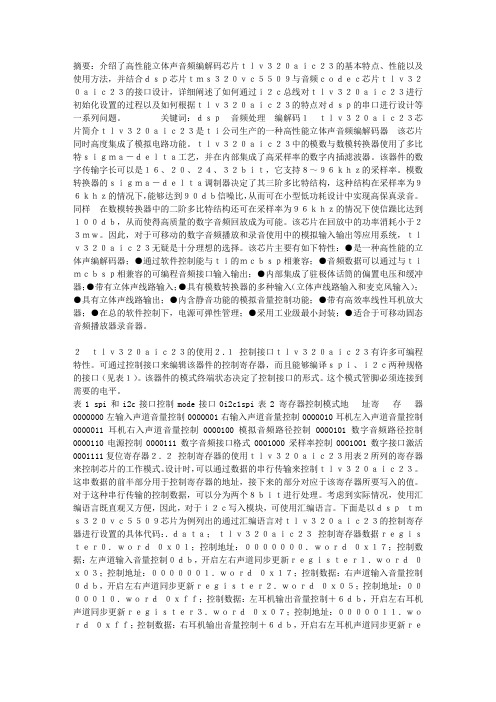

TLC320AIC23在音频处理中的应用

摘要:介绍了高性能立体声音频编解码芯片tlv320aic23的基本特点、性能以及使用方法,并结合dsp芯片tms320vc5509与音频codec芯片tlv320aic23的接口设计,详细阐述了如何通过i2c总线对tlv320aic23进行初始化设置的过程以及如何根据tlv320aic23的特点对dsp的串口进行设计等一系列问题。

关键词:dsp 音频处理 编解码1tlv320aic23芯片简介tlv320aic23是ti公司生产的一种高性能立体声音频编解码器 该芯片同时高度集成了模拟电路功能。

tlv320aic23中的模数与数模转换器使用了多比特sigma-delta工艺,并在内部集成了高采样率的数字内插滤波器。

该器件的数字传输字长可以是16、20、24、32bit,它支持8~96khz的采样率。

模数转换器的sigma-delta调制器决定了其三阶多比特结构,这种结构在采样率为96khz的情况下,能够达到90db信噪比,从而可在小型低功耗设计中实现高保真录音。

同样 在数模转换器中的二阶多比特结构还可在采样率为96khz的情况下使信躁比达到100db,从而使得高质量的数字音频回放成为可能。

该芯片在回放中的功率消耗小于23mw。

因此,对于可移动的数字音频播放和录音使用中的模拟输入输出等应用系统,tlv320aic23无疑是十分理想的选择。

该芯片主要有如下特性:●是一种高性能的立体声编解码器;●通过软件控制能与ti的mcbsp相兼容;●音频数据可以通过与timcbsp相兼容的可编程音频接口输入输出;●内部集成了驻极体话筒的偏置电压和缓冲器;●带有立体声线路输入;●具有模数转换器的多种输入(立体声线路输入和麦克风输入);●具有立体声线路输出;●内含静音功能的模拟音量控制功能;●带有高效率线性耳机放大器;●在总的软件控制下,电源可弹性管理;●采用工业级最小封装;●适合于可移动固态音频播放器录音器。

2tlv320aic23的使用2.1控制接口tlv320aic23有许多可编程特性。

TLC32040资料

TLC32040M ANALOG INTERFACE CIRCUIT

SGLS031 – MAY 1990

• • • • • • •

Advanced LinCMOS™ Silicon-Gate Process Technology 14-Bit Dynamic Range ADC and DAC Variable ADC and DAC Sampling Rate up to 19 200 Samples Per Second Switched-Capacitor Antialiasing Input Filter and Output-Reconstruction Filter Serial Port for Direct Interface to SMJ320E14, SMJ32020, SMJ320C25, and SMJ320C30 Digital Processors Synchronous or Asynchronous ADC and DAC Conversion Rates With Programmable Incremental ADC and DAC Conversion Timing Adjustments Serial Port Interface to SN54299 Serial-to-Parallel Shift Register for Parallel Interface to SMJ320C10, SMJ320C15, SMJ320E15, or Other Digital Processors

DR MSTR CLK VDD REF DGTL GND SHIFT CLK EODX

5 6 7 8 9

FSR EODR RESET NU NU NU IN+

Canon MX320 series 基本指南

(-)或 (+)按钮

(11) 黑白按钮 开始进行黑白打印、复印、扫描、传真等。

(12) 停止按钮 取消正在进行的打印、传送或扫描作业。

(13) 彩色按钮 开始进行彩色打印、复印、扫描、传真等。

(14) 传真质量按钮 选择要发送的传真的扫描分辨率和对比度。

(15) 音频按钮 在传真模式中,暂时切换到音频拨号或用于数字键拨号,并且在输入字符时更改输入模式。

页首

本机概述

目录 > 本机概述

本机概述

本节描述在使用本机之前需要了解的本机部件名称和基本操作。

主要部件

前视图 后视图 内部视图 操作面板

如何在液晶显示屏上浏览菜单

各种模式中的基本操作 选择模式 从指定模式中选择菜单项目 设置选项的基本操作

高级指南 故障排除

5 页/113 页

页首

主要部件

目录 > 本机概述 > 主要部件

在清洁本机之前,请务必先从电源插座拔出本机插头。 如果在清洁本机时不小心开启本机,可能造成人身伤害或损坏本机。

请勿尝试拆卸或改装本机。 本机内部没有可供用户自行修理的部件。 本机内有高压部件。 切勿尝试任何本指南中未描述的维护操作。

请勿将推荐设备以外的设备连接到本机的直接打印端口或电缆线连接器。 这会造成火灾或电击。

内部视图

8 页/113 页

(19) 墨盒锁定盖 将墨盒(FINE Cartridge)锁定到位。

(20) 扫描单元(机盖) 扫描原稿。 更换墨盒(FINE Cartridge)或取出本机中的卡纸时将其打开。 要打开扫描单元(机盖),请在 文档盖板关闭的状态下将其抬起。

(21) 扫描单元支架 承托打开的扫描单元(机盖)。

可达科技 CA30CAN CAF 第四代三重电磁盾感应靠近传感器数据手册说明书

Proximity Sensors Capacitive Thermoplastic Polyester Housing Types CA30CAN/CAF.....• 4TH Generation TRIPLESHIELD TM• Adjustable sensing distance: 2 - 20 mm flush or 4-30 mm non-flush• Protection: short-circuit, transients and reverse polarity • Dust and humidity compensation • Dust or temperature alarm output • Rated operational voltage: 10-40 VDC • Output: DC 200 mA, NPN or PNP • Standard Output: NO and NC• LED indications for power-supply, output and stability • IP67, IP68, IP69K, Nema 1, 2, 4, 4X, 5, 6, 6P, 12• Cable and M12 connector versions availableProduct DescriptionThe CA30CA.. capacitive proximity switches feature an improved 4TH generation TRI-PLESHIELD TM technology. F urthermore, these sensors feature increased immunity to electromagnetic interfer-ence (EMI), especially to fre-quency drives. Not only does 4TH generation TRIPLESH-IELD TM feature an increased EMI, but it also increases the immunity to humidity and dust. The implementation of stability indication eases the setup procedure, as both Stable ON and Stable OF F positions are indicated bythe green and yellow LEDs.increased by 20 – 25 % allowing room for additional stable detection.gives an early warning that have to be cleaned.The temperature alarm func-tion raises an alarm if the sensing surface goes beyond 60 degree Celsius.The sensor housing is featur-ing IP69K as well as approval by ECOLAB for cleaning and disinfection agents. Rated operating distance (S n ) Non-flush mounted sensor 0 - 25 mm (factory setting 25 mm), (ref. target 75x75 mm ST37, 1 mm thick, grounded) Flush mounted sensor 0 - 16 mm (factory setting 16 mm - non-flush mounted) (ref. target 48x48 mm ST37, 1 mm thick, grounded)Specifications EN 60947-5-2Housing Sensor Output OutputConnectionRated operating Ordering no. Ordering no. Ordering no.diameter type type function distance (S n ) StandardDust alarmTemperature alarmM 30 Flush NPN NO+NC Cable 0 - 16 mm CA30CAF16NA M 30 Flush NPN NO+NC M12 Plug 0 - 16 mm CA30CAF16NAM1M 30 Flush PNP NO+NC Cable 0 - 16 mm CA30CAF16PA M 30 Flush PNP NO+NC M12 Plug 0 - 16 mm CA30CAF16PAM1M 30 Flush PNP NO Cable 0 - 16 mm CA30CAF16PODU CA30CAF16POTAM 30 Flush PNP NC Cable 0 - 16 mmCA30CAF16PCDU CA30CAF16PCTA M 30 Flush PNP NC M12 Plug 0 - 16 mm CA30CAF16PCM1DUM 30 Non-Flush NPN NO+NC Cable 0 - 25 mm CA30CAN25NA M 30 Non-Flush NPN NO+NC M12 Plug 0 - 25 mm CA30CAN25NAM1M 30 Non-Flush PNP NO+NC Cable 0 - 25 mm CA30CAN25PA M 30 Non-Flush PNP NO+NC M12 Plug 0 - 25 mm CA30CAN25PAM1M 30 Non-Flush PNP NO Cable 0 - 25 mm CA30CAN25PODU CA30CAN25POTA M 30Non-FlushPNPNCCable0 - 25 mmCA30CAN25PCDU CA30CAN25PCTAType SelectionCA30CAN/CAF.....Specifications (cont.) EN 60947-5-2* The IP69K test according to DIN 40050-9 for high-pressure, high-temperature wash-down applications. The sensor must not only be dust tight (IP6X), but also able to withstand high-pressure and steam cleaning. The sensor is exposed to high-pressure water from a spray nozzle that is fed with 80°C water at 8’000– 10’000 KPa (80–100bar) and a flow rate of 14–6L/min. The nozzle is held 100 –150 mm from the sensor at angles of 0°, 30°, 60° and 90° for 30s each. The test device sits on a turntable that rotates with a speed of 5 times per minute. The sensor must not suffer any damaging effects from the high pressure water in appear-ance and function.90°60°30°0°The environments in which capacitive sensors are installed can often be unsta-ble as regards temperature, humidity, object distance and industrial (noise) inter-ference. This is why Carlo Gavazzi offers, as a stand-ard feature in all TRIPLESH-IELD™ capacitive sensors, a user-friendly sensitivity adjustment instead of a fixed sensing range. Likewise, these sensors provide an extended sensing range to accommodate mechanicallydemanding areas and tem-perature stability to ensure high immunity to electromag-netic interference (EMI) and a minimum need for adjusting sensitivity if the temperature varies.Note:The sensors are factory set (default) to nominal sensing range S n .Adjustment GuideCA30CAN/CAF.....Wiring DiagramDetection DiagramCA30CAN/CAF.....Detection Stability IndicationDimensionsInstallation HintsCapacitive sensors have a unique ability to detect al-most any material in li q uid or solid form. Capa c i t ive sen-sors are able to detect me-tallic as well as non-metallic ob j ects. How e ver, their tradi-tional use is for non-metallic materials such as:• Plastics Industry Resins, regrinds or mould-ed products.• Chemical IndustryCleansers, fertilizers, liq-uid soaps, corrosives andpe t r o c hemicals.• Wood IndustrySaw dust, paper products,door and window frames.• Ceramics & GlassI ndustryRaw materials, clay orfinish e d products, bottles.• Packaging IndustryPackage inspection for lev-el or contents, dry goods,fruits and vegetables, dairyproducts.Materials are detected due totheir dielectric constant. Thebigger the size of an object,the higher the density of ma-terial, the better or easier it isto detect the object.The nominal sensing di s tan-ce for a capacitive sensoris refe r r ed to a groundedme t al plate (ST37). For addi-tional information regardingdi e lec t ric ratings of materi-als please re f er to TechnicalInformation.Relief of cable strain Protection of the sensing face Switch mounted on mobile carrier To avoid interference from inductive voltage/current peaks, separate the prox. switch pow-er cables from any other power cables, e.g.motor, contactor or solenoid cablesNot correctCorrectThe cable should not be pulled A proximity switch should not serve asmechanical stopAny repetitive flexing of thecable should be avoided Delivery Contents•Capacitive switch: CA30CAN/CAF.......• User manual• 2 x M30 fingernuts• Screwdriver• Packaging: Cardboard boxAccessories• Connector type CONB14NF-... -series.• Mounting Brackets AMB30-S.. (straight),AMB30-A.. (angled)CA30CAN/CAF.....。

TMP320C6211GJL120资料

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. VelociTI, TMS320C62x, and MicroStar BGA are trademarks of Texas Instruments. Motorola is a trademark of Motorola, Inc. † IEEE Standard 1149.1-1990 Standard-Test-Access Port and Boundary Scan Architecture.

Copyright 2004, Texas Instruments Incorporated

POST OFFICE BOX 1443

• HOUSTON, TEXAS 77251−1443

1

元器件交易网

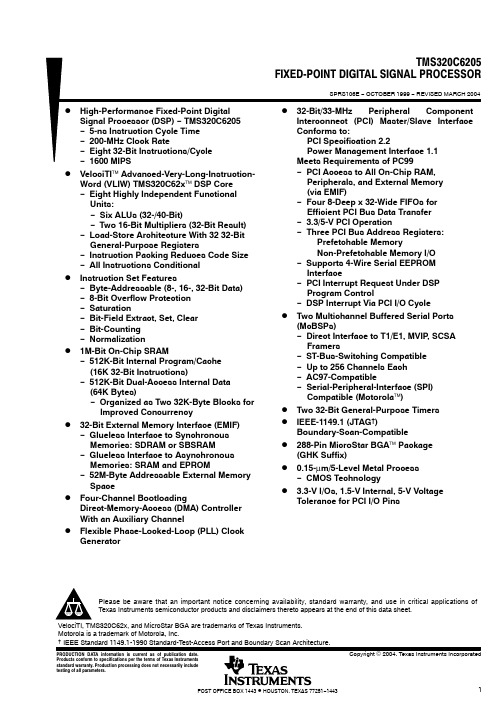

TMS320C6205 FIXED-POINT DIGITAL SIGNAL PROCESSOR

元器件交易网

TMS320C6205 FIXED-POINT DIGITAL SIGNAL PROCESSOR

SPRS106E − OCTOBER 1999 − REVISED MARCH 2004

D High-Performance Fixed-Point Digital

D 32-Bit/33-MHz

DLeabharlann D D D D DPeripheral Component Interconnect (PCI) Master/Slave Interface Conforms to: PCI Specification 2.2 Power Management Interface 1.1 Meets Requirements of PC99 − PCI Access to All On-Chip RAM, Peripherals, and External Memory (via EMIF) − Four 8-Deep x 32-Wide FIFOs for Efficient PCI Bus Data Transfer − 3.3/5-V PCI Operation − Three PCI Bus Address Registers: Prefetchable Memory Non-Prefetchable Memory I/O − Supports 4-Wire Serial EEPROM Interface − PCI Interrupt Request Under DSP Program Control − DSP Interrupt Via PCI I/O Cycle Two Multichannel Buffered Serial Ports (McBSPs) − Direct Interface to T1/E1, MVIP, SCSA Framers − ST-Bus-Switching Compatible − Up to 256 Channels Each − AC97-Compatible − Serial-Peripheral-Interface (SPI) Compatible (Motorola) Two 32-Bit General-Purpose Timers IEEE-1149.1 (JTAG†) Boundary-Scan-Compatible 288-Pin MicroStar BGA Package (GHK Suffix) 0.15-µm/5-Level Metal Process − CMOS Technology 3.3-V I/Os, 1.5-V Internal, 5-V Voltage Tolerance for PCI I/O Pins

最新-TLC320AC01与DSP的接口设计 精品

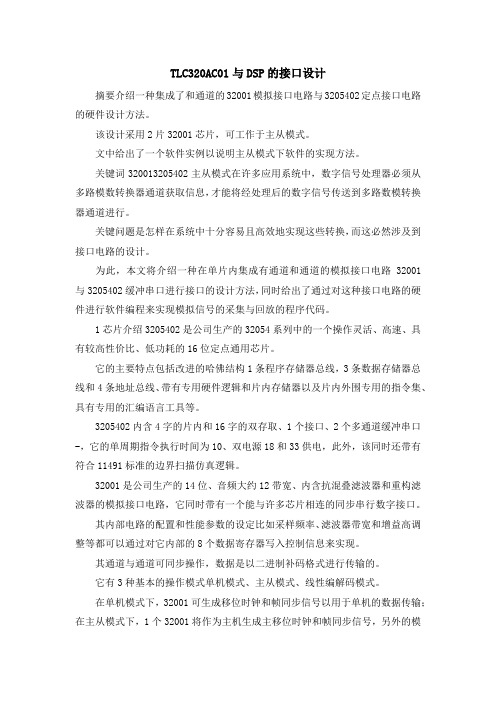

TLC320AC01与DSP的接口设计摘要介绍一种集成了和通道的32001模拟接口电路与3205402定点接口电路的硬件设计方法。

该设计采用2片32001芯片,可工作于主从模式。

文中给出了一个软件实例以说明主从模式下软件的实现方法。

关键词320013205402主从模式在许多应用系统中,数字信号处理器必须从多路模数转换器通道获取信息,才能将经处理后的数字信号传送到多路数模转换器通道进行。

关键问题是怎样在系统中十分容易且高效地实现这些转换,而这必然涉及到接口电路的设计。

为此,本文将介绍一种在单片内集成有通道和通道的模拟接口电路32001与3205402缓冲串口进行接口的设计方法,同时给出了通过对这种接口电路的硬件进行软件编程来实现模拟信号的采集与回放的程序代码。

1芯片介绍3205402是公司生产的32054系列中的一个操作灵活、高速、具有较高性价比、低功耗的16位定点通用芯片。

它的主要特点包括改进的哈佛结构1条程序存储器总线,3条数据存储器总线和4条地址总线、带有专用硬件逻辑和片内存储器以及片内外围专用的指令集、具有专用的汇编语言工具等。

3205402内含4字的片内和16字的双存取、1个接口、2个多通道缓冲串口-,它的单周期指令执行时间为10、双电源18和33供电,此外,该同时还带有符合11491标准的边界扫描仿真逻辑。

32001是公司生产的14位、音频大约12带宽、内含抗混叠滤波器和重构滤波器的模拟接口电路,它同时带有一个能与许多芯片相连的同步串行数字接口。

其内部电路的配置和性能参数的设定比如采样频率、滤波器带宽和增益高调整等都可以通过对它内部的8个数据寄存器写入控制信息来实现。

其通道与通道可同步操作,数据是以二进制补码格式进行传输的。

它有3种基本的操作模式单机模式、主从模式、线性编解码模式。

在单机模式下,32001可生成移位时钟和帧同步信号以用于单机的数据传输;在主从模式下,1个32001将作为主机生成主移位时钟和帧同步信号,另外的模。

32寸IPB电源的培训资料

Load regulation 负载调整率

±5%

±5%

家电维修资料网

具体的技术指标

FHD 屏规格书 家电维修资料网

Adobe Acrobat 7.0

Inverter部份的特性(型号:CAS_LC320WUE-SAA1;lamp:16; EEFL) Document

90Vac---270Vac

47---63HZ

2.205A

20A/100Vac 40A/220Vac ≥ 82% ≥ 87% ≥ 86%

GB17625.0-1998 IEC61000-3-2 calls D ≤0.35mv/220Vac

T3.15AH/250Vac & T1AL/250Vac ≥96% (90VAC) ≥93% (220VAC) ≥90% (264VAC) ≤0.15W

Efficiency (full load when 90V) 效率(100V输入时最大负载) Efficiency (full load when 220V) 效率(220V输入时最大负载) Efficiency (full load when 264V) 效率(264V输入时最大负载)

Harmonic current

谐波电流

Leakage current

漏电流

Input FUSC spec

输入保险丝规格

Power Factor(full load)

功率因数范围

Standby Power Consumption 待机功耗(3.3V负载≤10mA, 230Vac)

家电维修资料网

100Vac---240Vac

开机: 当收到MCU发出开机的高电平信号后、经DB15、RB22后送到QB21的B极,此时QB21导通、光耦IC6的1、2脚导通、将信 号耦合到光耦IC6的3、4脚。这时QB1导通,VCC供电通过QB1输出10~12V电压,给继电器提供工作电压,继电器闭合,主电源接 通交流。

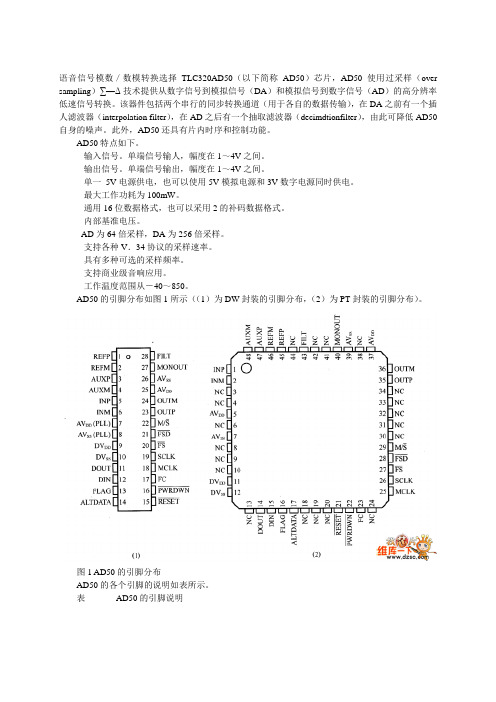

TLC320AD50

语音信号模数/数模转换选择TLC320AD50(以下简称AD50)芯片,AD50使用过采样(over sampling)∑—Δ技术提供从数字信号到模拟信号(DA)和模拟信号到数字信号(AD)的高分辨率低速信号转换。

该器件包括两个串行的同步转换通道(用于各自的数据传输),在DA之前有一个插人滤波器(interpolation filter),在AD之后有一个抽取滤波器(decimdtionfilter),由此可降低AD50自身的噪声。

此外,AD50还具有片内时序和控制功能。

AD50特点如下。

·输入信号。

单端信号输人,幅度在1~4V之间。

·输出信号。

单端信号输出,幅度在1~4V之间。

·单一5V电源供电,也可以使用5V模拟电源和3V数字电源同时供电。

·最大工作功耗为100mW。

·通用16位数据格式,也可以采用2的补码数据格式。

·内部基准电压。

· AD为64倍采样,DA为256倍采样。

·支持各种V.34协议的采样速率。

·具有多种可选的采样频率。

·支持商业级音响应用。

·工作温度范围从-40~850。

AD50的引脚分布如图1所示((1)为DW封装的引脚分布,(2)为PT封装的引脚分布)。

图1 AD50的引脚分布AD50的各个引脚的说明如表所示。

表AD50的引脚说明续表在AD50正常工作前,必须对它进行正确的初始化。

初始化操作的主要工作是配置AD50的4个控制寄存器CR1、CR2、CR3和CR4。

控制寄存器的读写是通过二次通信来实现。

在二次通信中,D0~D7为写人控制寄存器的数据或者从控制寄存器读出的数据,D8~D12的内容决定选择哪个控制寄存器,D13位决定是读操作还是写操作。

由D8~D13位确定的所有情况如表2所示。

表2 AD50的D8~D13位确定的所有操作情况表3 控制寄存器1的各个控制位的功能说明表4 控制寄存器2的各个控制位的功能说明表5 控制寄存器3的各个控制位的功能说明表6 控制寄存器4的各个控制位的功能说明表7 控制寄存器4的第4~第6位对应的N值AD50控制寄存器的设置必须在二次通信中完成。

TLC1543CN;TLC1543CDW;TLC1543CFN;TLC1543QDB;TLC1542CFN;中文规格书,Datasheet资料

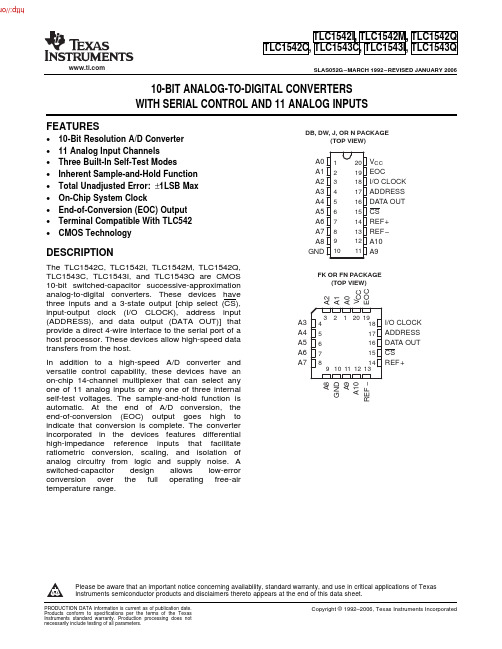

FEATURESDESCRIPTIONDB, DW, J, OR N PACKAGE(TOP VIEW)FK OR FN PACKAGE(TOP VIEW)210A1REFOCAGN ACCTLC1542I,,TLC1542M,,TLC1542QTLC1542C,TLC1543C,TLC1543I,TLC1543QSLAS052G–MARCH1992–REVISED JANUARY200610-BIT ANALOG-TO-DIGITAL CONVERTERSWITH SERIAL CONTROL AND11ANALOG INPUTS•10-Bit Resolution A/D Converter•11Analog Input Channels•Three Built-In Self-Test Modes•Inherent Sample-and-Hold Function•Total Unadjusted Error:±1LSB Max•On-Chip System Clock•End-of-Conversion(EOC)Output•Terminal Compatible With TLC542•CMOS TechnologyThe TLC1542C,TLC1542I,TLC1542M,TLC1542Q,TLC1543C,TLC1543I,and TLC1543Q are CMOS10-bit switched-capacitor successive-approximationanalog-to-digital converters.These devices havethree inputs and a3-state output[chip select(CS),input-output clock(I/O CLOCK),address input(ADDRESS),and data output(DATA OUT)]thatprovide a direct4-wire interface to the serial port of ahost processor.These devices allow high-speed datatransfers from the host.In addition to a high-speed A/D converter andversatile control capability,these devices have anon-chip14-channel multiplexer that can select anyone of11analog inputs or any one of three internalself-test voltages.The sample-and-hold function isautomatic.At the end of A/D conversion,theend-of-conversion(EOC)output goes high toindicate that conversion is complete.The converterincorporated in the devices features differentialhigh-impedance reference inputs that facilitateratiometric conversion,scaling,and isolation ofanalog circuitry from logic and supply noise.Aswitched-capacitor design allows low-errorconversion over the full operating free-airtemperature range.Please be aware that an important notice concerning availability,standard warranty,and use in critical applications of TexasInstruments semiconductor products and disclaimers thereto appears at the end of this data sheet.PRODUCTION DATA information is current as of publication date.Copyright©1992–2006,Texas Instruments Incorporated Products conform to specifications per the terms of the TexasInstruments standard warranty.Production processing does notnecessarily include testing of all parameters.DATAOUTTYPICAL EQUIVALENT INPUTSINPUT CIRCUIT IMPEDANCE DURING SAMPLING MODEINPUT CIRCUIT IMPEDANCE DURING HOLD MODE1 k Ω TYPC i = 60 pF TYP (equivalent input capacitance)5 M Ω TYPA0−A10A0−A10TLC1542I,,TLC1542M,,TLC1542QTLC1542C,TLC1543C,TLC1543I,TLC1543QSLAS052G–MARCH 1992–REVISED JANUARY 2006These devices have limited built-in ESD protection.The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.AVAILABLE OPTIONSPACKAGESMALL T ASMALL OUTLINECHIP CARRIERPLASTIC DIPCHIP CARRIERCERAMIC DIPOUTLINE (DW)(FN)(N)(FK)(J)(DB)TLC1542CDW TLC1542CFN TLC1542CN 0°C to 70°C TLC1543CDB TLC1543CDW TLC1543CFN TLC1543CN TLC1542IDW TLC1542IFN TLC1542IN -40°C to 85°C TLC1543IDB TLC1543IDW TLC1543IFN TLC1543INTLC1542QFN -40°C to 125°C TLC1543QDBTLC1543QDWTLC1543QFN-55°C to 125°CTLC1542MFKTLC1542MJFUNCTIONAL BLOCK DIAGRAM2Submit Documentation FeedbackDETAILED DESCRIPTIONTLC1542I,,TLC1542M,,TLC1542Q TLC1542C,TLC1543C,TLC1543I,TLC1543QSLAS052G–MARCH1992–REVISED JANUARY2006 TERMINAL FUNCTIONSTERMINALI/O DESCRIPTIONNAME NO.ADDRESS17I Serial address input.A4-bit serial address selects the desired analog input or test voltage that is to beconverted next.The address data is presented with the MSB first and shifts in on the first four risingedges of I/O CLOCK.After the four address bits have been read into the address register,this input isignored for the remainder of the current conversion period.A0-A101-9,11,12I Analog signal inputs.The11analog inputs are applied to these terminals and are internallymultiplexed.The driving source impedance should be less than or equal to1kΩ.CS15I Chip select.A high-to-low transition on this input resets the internal counters and controls and enablesDATA OUT,ADDRESS,and I/O CLOCK within a maximum of a setup time plus two falling edges ofthe internal system clock.A low-to-high transition disables ADDRESS and I/O CLOCK within a setuptime plus two falling edges of the internal system clock.DATA OUT16O The3-state serial output for the A/D conversion result.This output is in the high-impedance statewhen CS is high and active when CS is low.With a valid chip select,DATA OUT is removed from thehigh-impedance state and is driven to the logic level corresponding to the MSB value of the previousconversion result.The next falling edge of I/O CLOCK drives this output to the logic levelcorresponding to the next most significant bit,and the remaining bits shift out in order with the LSBappearing on the ninth falling edge of I/O CLOCK.On the tenth falling edge of I/O CLOCK,DATAOUT is driven to a low logic level so that serial interface data transfers of more than ten clocksproduce zeroes as the unused LSBs.EOC19O End of conversion.This output goes from a high to a low logic level on the trailing edge of the tenthI/O CLOCK and remains low until the conversion is complete and data are ready for transfer.GND10I The ground return terminal for the internal circuitry.Unless otherwise noted,all voltage measurementsare with respect to this terminal.I/O CLOCK18I Input/output clock.This terminal receives the serial I/O CLOCK input and performs the following fourfunctions:1)It clocks the four input address bits into the address register on the first four rising edgesof the I/O CLOCK with the multiplex address available after the fourth rising edge.2)On the fourthfalling edge of I/O CLOCK,the analog input voltage on the selected multiplex input begins chargingthe capacitor array and continues to do so until the tenth falling edge of I/O CLOCK.3)It shifts thenine remaining bits of the previous conversion data out on DATA OUT.4)It transfers control of theconversion to the internal state controller on the falling edge of the tenth clock.REF+14I The upper reference voltage value(nominally V CC)is applied to this terminal.The maximum inputvoltage range is determined by the difference between the voltage applied to this terminal and thevoltage applied to the REF-terminal.REF-13I The lower reference voltage value(nominally ground)is applied to this terminal.V CC20I Positive supply voltageWith chip select(CS)inactive(high),the ADDRESS and I/O CLOCK inputs are initially disabled and DATA OUT is in the high-impedance state.When the serial interface takes CS active(low),the conversion sequence begins with the enabling of I/O CLOCK and ADDRESS and the removal of DATA OUT from the high-impedance state. The serial interface then provides the4-bit channel address to ADDRESS and the I/O CLOCK sequence to I/O CLOCK.During this transfer,the serial interface also receives the previous conversion result from DATA OUT. I/O CLOCK receives an input sequence that is between10and16clocks long from the host serial interface.The first four I/O clocks load the address register with the4-bit address on ADDRESS,selecting the desired analog channel,and the next six clocks providing the control timing for sampling the analog input.There are six basic serial-interface timing modes that can be used with the device.These modes are determined by the speed of I/O CLOCK and the operation of CS as shown in Table1.These modes are(1)a fast mode with a10-clock transfer and CS inactive(high)between conversion cycles,(2)a fast mode with a10-clock transfer and CS active(low)continuously,(3)a fast mode with an11-to16-clock transfer and CS inactive(high) between conversion cycles,(4)a fast mode with a16-clock transfer and CS active(low)continuously,(5)a slow mode with an11-to16-clock transfer and CS inactive(high)between conversion cycles,and(6)a slow mode with a16-clock transfer and CS active(low)continuously.3Submit Documentation FeedbackFAST MODESMODE 1:FAST MODE,CS INACTIVE (HIGH)BETWEEN CONVERSION CYCLES,10-CLOCK TRANSFER MODE 2:FAST MODE,CS ACTIVE (LOW)CONTINUOUSLY,10-CLOCK TRANSFERMODE 3:FAST MODE,CS INACTIVE (HIGH)BETWEEN CONVERSION CYCLES,11-to 16-CLOCK TLC1542I,,TLC1542M,,TLC1542QTLC1542C,TLC1543C,TLC1543I,TLC1543QSLAS052G–MARCH 1992–REVISED JANUARY 2006The MSB of the previous conversion appears at DATA OUT on the falling edge of CS in mode 1,mode 3,and mode 5,on the rising edge of EOC in mode 2and mode 4,and following the sixteenth clock falling edge in mode 6.The remaining nine bits are shifted out on the next nine falling edges of I/O CLOCK.Ten bits of data are transmitted to the host-serial interface through DATA OUT.The number of serial clock pulses used also depends on the mode of operation,but a minimum of ten clock pulses is required for conversion to begin.On the tenth clock falling edge,the EOC output goes low and returns to the high logic level when conversion is complete and the result can be read by the host.Also,on the tenth clock falling edge,the internal logic takes DATA OUT low to ensure that the remaining bit values are zero when the I/O CLOCK transfer is more than ten clocks long.Table 1lists the operational modes with respect to the state of CS,the number of I/O serial transfer clocks that can be used,and the timing edge on which the MSB of the previous conversion appears at the output.Table 1.MODE OPERATIONTIMING MODESCSNO.OF 1/O CLOCKMSB AT DATA OUT (1)DIAGRAM Mode 1High between conversion cycles 10CS falling edge Figure 9Mode 2Low continuously10EOC rising edge Figure 10Fast ModesMode 3High between conversion cycles 11TO 16(2)CS falling edge Figure 11Mode 4Low continuously16(2)EOC rising edge Figure 12Mode 5High between conversion cycles 11to 16(3)CS falling edge Figure 13Slow Modes Mode 6Low continuously16(3)16th clock falling edgeFigure 14(1)These edges also initiate serial-interface communication.(2)No more than 16clocks should be used.(3)No more than 16clocks should be used.The device is in a fast mode when the serial I/O CLOCK data transfer is completed before the conversion is completed.With a 10-clock serial transfer,the device can only run in a fast mode since a conversion does not begin until the falling edge of the tenth I/O CLOCK.In this mode,CS is inactive (high)between serial I/O CLOCK transfers and each transfer is ten clocks long.The falling edge of CS begins the sequence by removing DATA OUT from the high-impedance state.The rising edge of CS ends the sequence by returning DATA OUT to the high-impedance state within the specified delay time.Also,the rising edge of CS disables the I/O CLOCK and ADDRESS terminals within a setup time plus two falling edges of the internal system clock.In this mode,CS is active (low)between serial I/O CLOCK transfers and each transfer is ten clocks long.After the initial conversion cycle,CS is held active (low)for subsequent conversions;the rising edge of EOC then begins each sequence by removing DATA OUT from the low logic level,allowing the MSB of the previous conversion to appear immediately on this output.TRANSFERIn this mode,CS is inactive (high)between serial I/O CLOCK transfers,and each transfer can be 11to 16clocks long.The falling edge of CS begins the sequence by removing DATA OUT from the high-impedance state.The rising edge of CS ends the sequence by returning DATA OUT to the high-impedance state within the specified delay time.Also,the rising edge of CS disables the I/O CLOCK and ADDRESS terminals within a setup time plus two falling edges of the internal system clock.4Submit Documentation FeedbackMODE 4:FAST MODE,CS ACTIVE (LOW)CONTINUOUSLY,16-CLOCK TRANSFERSLOW MODESMODE 5:SLOW MODE,CS INACTIVE (HIGH)BETWEEN CONVERSION CYCLES,11-to 16-CLOCK MODE 6:SLOW MODE,CS ACTIVE (LOW)CONTINUOUSLY,16-CLOCK TRANSFERADDRESS BITSANALOG INPUTS AND TEST MODESTLC1542I,,TLC1542M,,TLC1542QTLC1542C,TLC1543C,TLC1543I,TLC1543QSLAS052G–MARCH 1992–REVISED JANUARY 2006In this mode,CS is active (low)between serial I/O CLOCK transfers and each transfer must be exactly 16clocks long.After the initial conversion cycle,CS is held active (low)for subsequent conversions;the rising edge of EOC then begins each sequence by removing DATA OUT from the low logic level,allowing the MSB of the previous conversion to appear immediately on this output.In a slow mode,the conversion is completed before the serial I/O CLOCK data transfer is completed.A slow mode requires a minimum 11-clock transfer into I/O CLOCK,and the rising edge of the eleventh clock must occur before the conversion period is complete;otherwise,the device loses synchronization with the host-serial interface and CS has to be toggled to initialize the system.The eleventh rising edge of the I/O CLOCK must occur within 9.5µs after the tenth I/O clock falling edge.TRANSFERIn this mode,CS is inactive (high)between serial I/O CLOCK transfers and each transfer can be 11to 16clocks long.The falling edge of CS begins the sequence by removing DATA OUT from the high-impedance state.The rising edge of CS ends the sequence by returning DATA OUT to the high-impedance state within the specified delay time.Also,the rising edge of CS disables the I/O CLOCK and ADDRESS terminals within a setup time plus two falling edges of the internal system clock.In this mode,CS is active (low)between serial I/O CLOCK transfers and each transfer must be exactly 16clocks long.After the initial conversion cycle,CS is held active (low)for subsequent conversions.The falling edge of the sixteenth I/O CLOCK then begins each sequence by removing DATA OUT from the low state,allowing the MSB of the previous conversion to appear immediately at DATA OUT.The device is then ready for the next 16-clock transfer initiated by the serial interface.The 4-bit analog channel-select address for the next conversion cycle is presented to the ADDRESS terminal (MSB first)and is clocked into the address register on the first four leading edges of I/O CLOCK.This address selects one of 14inputs (11analog inputs or three internal test inputs).The 11analog inputs and the three internal test inputs are selected by the 14-channel multiplexer according to the input address as shown in Tables 2and 3.The input multiplexer is a break-before-make type to reduce input-to-input noise injection resulting from channel switching.Sampling of the analog input starts on the falling edge of the fourth I/O CLOCK,and sampling continues for six I/O CLOCK periods.The sample is held on the falling edge of the tenth I/O CLOCK.The three test inputs are applied to the multiplexer,sampled,and converted in the same manner as the external analog inputs.5Submit Documentation Feedbackht t p ://oCONVERTER AND ANALOG INPUTTLC1542I,,TLC1542M,,TLC1542QTLC1542C,TLC1543C,TLC1543I,TLC1543QSLAS052G–MARCH 1992–REVISED JANUARY 2006Table 2.ANALOG-CHANNEL-SELECT ADDRESSVALUE SHIFTED INTO ADDRESSINPUTANALOG INPUT SELECTEDBINARY HEX A000000A100011A200102A300113A401004A501015A601106A701117A810008A910019A101010ATable 3.TEST-MODE-SELECT ADDRESS(1)V ref+is the voltage applied to the REF+input,and V ref-is the voltage applied to the REF-input.(2)The output results shown are the ideal values and vary with the reference stability and with internal offsets.The CMOS threshold detector in the successive-approximation conversion system determines each bit by examining the charge on a series of binary-weighted capacitors (see Figure 1).In the first phase of the conversion process,the analog input is sampled by closing the S C switch and all S T switches simultaneously.This action charges all the capacitors to the input voltage.In the next phase of the conversion process,all S T and S C switches are opened and the threshold detector begins identifying bits by identifying the charge (voltage)on each capacitor relative to the reference (REF-)voltage.In the switching sequence,ten capacitors are examined separately until all ten bits are identified and then the charge-convert sequence is repeated.In the first step of the conversion phase,the threshold detector looks at the first capacitor (weight =512).Node 512of this capacitor is switched to the REF+voltage,and the equivalent nodes of all the other capacitors on the ladder are switched to REF-.If the voltage at the summing node is greater than the trip point of the threshold detector (approximately one-half V CC ),a 0bit is placed in the output register and the 512-weight capacitor is switched to REF-.If the voltage at the summing node is less than the trip point of the threshold detector,a 1bit is placed in the register and the 512-weight capacitor remains connected to REF+through the remainder of the successive-approximation process.The process is repeated for the 256-weight capacitor,the 128-weight capacitor,and so forth down the line until all bits are counted.With each step of the successive-approximation process,the initial charge is redistributed among the capacitors.The conversion process relies on charge redistribution to count and weigh the bits from MSB to LSB.6Submit Documentation FeedbackCHIP-SELECT OPERATIONREFERENCE VOLTAGE INPUTSTLC1542I,,TLC1542M,,TLC1542QTLC1542C,TLC1543C,TLC1543I,TLC1543QSLAS052G–MARCH 1992–REVISED JANUARY 2006Figure 1.Simplified Model of the Successive-Approximation SystemThe trailing edge of CS starts all modes of operation,and CS can abort a conversion sequence in any mode.A high-to-low transition on CS within the specified time during an ongoing cycle aborts the cycle,and the device returns to the initial state (the contents of the output data register remain at the previous conversion result).Exercise care to prevent CS from being taken low close to completion of conversion because the output data can be corrupted.There are two reference inputs used with the device:REF+and REF-.These voltage values establish the upper and lower limits of the analog input to produce a full-scale and zero reading respectively.The values of REF+,REF-,and the analog input should not exceed the positive supply or be lower than GND consistent with the specified absolute maximum ratings.The digital output is at full scale when the input signal is equal to or higher than REF+and at zero when the input signal is equal to or lower than REF-.7Submit Documentation FeedbackABSOLUTE MAXIMUM RATINGSRECOMMENDED OPERATING CONDITIONSTLC1542I,,TLC1542M,,TLC1542QTLC1542C,TLC1543C,TLC1543I,TLC1543QSLAS052G–MARCH 1992–REVISED JANUARY 2006over operating free-air temperature range (unless otherwise noted)(1)UNITV CC ,see (2)Supply voltage range -0.5V to 6.5V V I Input voltage range -0.3V to V CC +0.3V V O Output voltage range -0.3V to V CC +0.3VV ref+Positive reference voltage V CC +0.1V V ref-Negative reference voltage -0.1V Peak input current (any input)±20mA Peak total input current (all inputs)±30mA TLC1542C,TLC1543C 0°C to 70°C TLC1542I,TLC1543I -40°C to 85°C T AOperating free-air temperature rangeTLC1542Q,TLC1543Q -40°C to 125°C TLC1542M-55°C to 125°C T stg Storage temperature range,-65°C to 150°CLead temperature 1,6mm (1/16inch)from the case for 10seconds260°C(1)Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device.These are stress ratings only,and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied.Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.(2)All voltage values are with respect to digital ground with REF-and GND wired together (unless otherwise noted).(1)Analog input voltages greater than that applied to REF+convert as all ones (1111111111),while input voltages less than that applied to REF-convert as all zeros (0000000000).The device is functional with reference voltages down to 1V (V ref+-V ref-);however,the electrical specifications are no longer applicable.(2)To minimize errors caused by noise at CS,the internal circuitry waits for a setup time plus two falling edges of the internal system clock after CS ↓before responding to control input signals.Therefore,no attempt should be made to clock in an address until the minimum CS setup time has elapsed.(3)For 11-to 16-bit transfers,after the tenth I/O CLOCK falling edge (≤2V)at least 1I/O CLOCK rising edge (≥2V)must occur within 9.5µs.(4)This is the time required for the clock input signal to fall from V IH min to V IL max or to rise from V IL max to V IH min.In the vicinity of normal room temperature,the devices function with input clock transition time as slow as 1µs for remote data-acquisition applications where the sensor and the A/D converter are placed several feet away from the controlling microprocessor.8Submit Documentation FeedbackELECTRICAL CHARACTERISTICS OPERATING CHARACTERISTICSTLC1542I,,TLC1542M,,TLC1542Q TLC1542C,TLC1543C,TLC1543I,TLC1543QSLAS052G–MARCH1992–REVISED JANUARY2006RECOMMENDED OPERATING CONDITIONS(continued)MIN NOM MAX UNITTLC1542C,TLC1543C070TLC1542I,TLC1543I-4085T A Operating free-air temperature,°CTLC1542Q,TLC1543Q-40125TLC1542M-55125over recommended operating free-air temperature range,VCC =Vref+=4.5V to5.5V,I/O CLOCK frequency=2.1MHz(unless otherwise noted)PARAMETER TEST CONDITIONS MIN TYP(1)MAX UNITV CC=4.5V,I OH=-1.6mA 2.4V OH High-level output voltage VV CC=4.5V to5.5V,I OH=-20µA V CC-0.1V CC=4.5V,I OL=1.6mA0.4V OL Low-level output voltage VV CC=4.5V to5.5V,I OL=20µA0.1Off-state V O=V CC,CS at V CC10I OZ(high-impedance-state)µAV O=0,CS at V CC-10 output currentI IH High-level input current V I=V CC0.005 2.5µAI IL Low-level input current V I=00.005-2.5µAI CC Operating supply current CS at0V0.8 2.5mASelected channel leakage Selected channel at V CC,Unselected channel at0V1current TLC1542/TLC1543µASelected channel at0V,Unselected channel at V CC-1 C,I,or QSelected channel at V CC,Unselected channel at0V,1T A=25°CSelected channel at0V,Selected channel leakage Unselected channel at VCC ,-1µAT A=25°Ccurrent TLC1542MSelected channel at V CC,Unselected channel at0V 2.5Selected channel at0V,Unselected channel at V CC-2.5Maximum static analogV ref+=V CC,V ref-=GND10µA reference current into REF+Analog7inputsInputC i pFcapacitance Control5inputs(1)All typical values are at V CC=5V,T A=25°C.over recommended operating free-air temperature range,VCC =Vref+=4.5V to5.5V,I/O CLOCK frequency=2.1MHz(unless otherwise noted)TESTMIN TYP(1)MAX UNITCONDITIONSTLC1542C,I,or Q±0.5LSBE L Linearity error,see(2))TLC1543C,I,or Q±1LSBTLC1542M±1LSB(1)All typical values are at T A=25°C.(2)Linearity error is the maximum deviation from the best straight line through the A/D transfer characteristics.9Submit Documentation FeedbackTLC1542I,,TLC1542M,,TLC1542QTLC1542C,TLC1543C,TLC1543I,TLC1543QSLAS052G–MARCH 1992–REVISED JANUARY2006OPERATING CHARACTERISTICS (continued)over recommended operating free-air temperature range,V CC =V ref+=4.5V to 5.5V,I/O CLOCK frequency =2.1MHz (unless otherwise noted)(3)Zero-scale error is the difference between 0000000000and the converted output for zero input voltage;full-scale error is the difference between 1111111111and the converted output for full-scale input voltage.(4)Analog input voltages greater than that applied to REF+convert as all ones (1111111111),while input voltages less than that applied to REF-convert as all zeros (0000000000).The device is functional with reference voltages down to 1V (V ref+-V ref-);however,the electrical specifications are no longer applicable.(5)Total unadjusted error comprises linearity,zero-scale,and full-scale errors.(6)Both the input address and the output codes are expressed in positive logic.(7)I/O CLOCK period =1/(I/O CLOCK frequency)(see Figure 6)(8)Any transitions of CS are recognized as valid only if the level is maintained for a setup time plus two falling edges of the internal clock (1.425µs)after the transition.10Submit Documentation Feedback分销商库存信息:TITLC1543CN TLC1543CDW TLC1543CFN TLC1543QDB TLC1542CFN TLC1542CNTLC1542IN TLC1542IDW TLC1543IFN TLC1543IN TLC1543CDB TLC1543QFN TLC1542CDW TLC1543CDWR TLC1543CDBR TLC1543CDBRG4TLC1543CDWRG4TLC1543IDBR TLC1543IDBRG4TLC1543IDWR TLC1543IDWRG4 TLC1543CNE4TLC1543CDWG4TLC1543QDBR TLC1542CDWR TLC1542CDWRG4TLC1543IFNG3 TLC1542IDWR TLC1542IDWRG4TLC1543INE4 TLC1543CDBG4TLC1543CFNG3TLC1543IDB TLC1543IDBG4TLC1543IDW TLC1542CFNG3 TLC1542CNE4TLC1542INE4TLC1542CDWG4 TLC1542IDWG4TLC1542QFN。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。