74FCT16244中文资料

74系列芯片功能表汇总

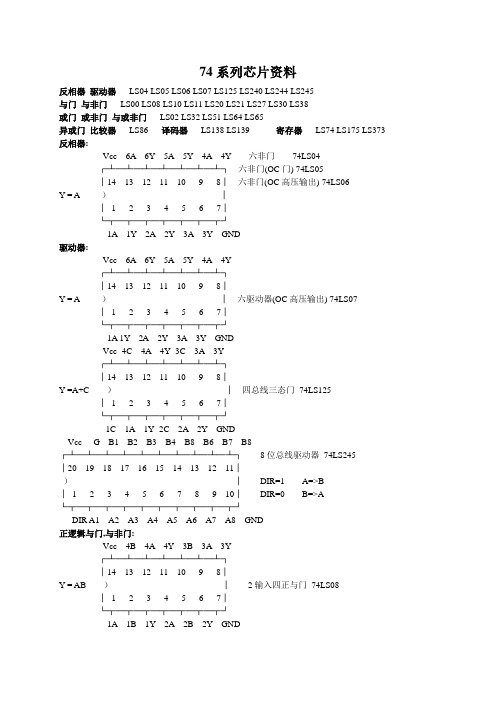

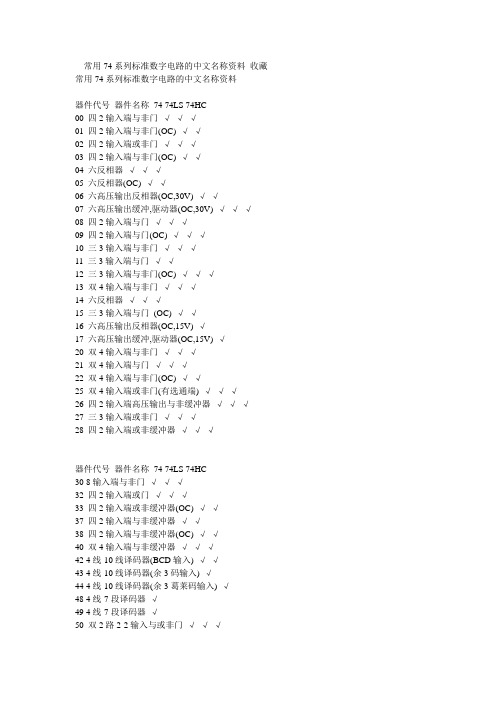

74系列芯片功能表汇总74系列标准数字电路功能表——中文资料名称类别功能7400 TTL 2输入端四与非门7401 TTL 集电极开路2输入端四与非门7402 TTL 2输入端四或非门7403 TTL 集电极开路2输入端四与非门7404 TTL 六反相器7405 TTL 集电极开路六反相器7406 TTL 集电极开路六反相高压驱动器7407 TTL 集电极开路六正相高压驱动器7408 TTL 2输入端四与门7409 TTL 集电极开路2输入端四与门7410 TTL 3输入端3与非门74107 TTL 带清除主从双J-K触发器74109 TTL 带预置清除正触发双J-K触发器7411 TTL 3输入端3与门74112 TTL 带预置清除负触发双J-K触发器7412 TTL 开路输出3输入端三与非门74121 TTL 单稳态多谐振荡器74122 TTL 可再触发单稳态多谐振荡器74123 TTL 双可再触发单稳态多谐振荡器74125 TTL 三态输出高有效四总线缓冲门74126 TTL 三态输出低有效四总线缓冲门7413 TTL 4输入端双与非施密特触发器74132 TTL 2输入端四与非施密特触发器74133 TTL 13输入端与非门74136 TTL 四异或门74138 TTL 3-8线译码器/复工器74139 TTL 双2-4线译码器/复工器7414 TTL 六反相施密特触发器74145 TTL BCD—十进制译码/驱动器7415 TTL 开路输出3输入端三与门74150 TTL 16选1数据选择/多路开关74151 TTL 8选1数据选择器74153 TTL 双4选1数据选择器74154 TTL 4线—16线译码器74155 TTL 图腾柱输出译码器/分配器74156 TTL 开路输出译码器/分配器74157 TTL 同相输出四2选1数据选择器74158 TTL 反相输出四2选1数据选择器7416 TTL 开路输出六反相缓冲/驱动器74160 TTL 可预置BCD异步清除计数器74161 TTL 可予制四位二进制异步清除计数器74162 TTL 可预置BCD同步清除计数器74163 TTL 可予制四位二进制同步清除计数器74164 TTL 八位串行入/并行输出移位寄存器74165 TTL 八位并行入/串行输出移位寄存器74166 TTL 八位并入/串出移位寄存器74169 TTL 二进制四位加/减同步计数器7417 TTL 开路输出六同相缓冲/驱动器74170 TTL 开路输出4×4寄存器堆74173 TTL 三态输出四位D型寄存器74174 TTL 带公共时钟和复位六D触发器74175 TTL 带公共时钟和复位四D触发器74180 TTL 9位奇数/偶数发生器/校验器74181 TTL 算术逻辑单元/函数发生器74185 TTL 二进制—BCD代码转换器74190 TTL BCD同步加/减计数器74191 TTL 二进制同步可逆计数器74192 TTL 可预置BCD双时钟可逆计数器74193 TTL 可预置四位二进制双时钟可逆计数器74194 TTL 四位双向通用移位寄存器74195 TTL 四位并行通道移位寄存器74196 TTL 十进制/二-十进制可预置计数锁存器74197 TTL 二进制可预置锁存器/计数器7420 TTL 4输入端双与非门7421 TTL 4输入端双与门7422 TTL 开路输出4输入端双与非门74221 TTL 双/单稳态多谐振荡器74240 TTL 八反相三态缓冲器/线驱动器74241 TTL 八同相三态缓冲器/线驱动器74243 TTL 四同相三态总线收发器74244 TTL 八同相三态缓冲器/线驱动器74245 TTL 八同相三态总线收发器74247 TTL BCD—7段15V输出译码/驱动器74248 TTL BCD—7段译码/升压输出驱动器74249 TTL BCD—7段译码/开路输出驱动器74251 TTL 三态输出8选1数据选择器/复工器74253 TTL 三态输出双4选1数据选择器/复工器74256 TTL 双四位可寻址锁存器74257 TTL 三态原码四2选1数据选择器/复工器74258 TTL 三态反码四2选1数据选择器/复工器74259 TTL 八位可寻址锁存器/3-8线译码器7426 TTL 2输入端高压接口四与非门74260 TTL 5输入端双或非门74266 TTL 2输入端四异或非门7427 TTL 3输入端三或非门74273 TTL 带公共时钟复位八D触发器74279 TTL 四图腾柱输出S-R锁存器7428 TTL 2输入端四或非门缓冲器74283 TTL 4位二进制全加器74290 TTL 二/五分频十进制计数器74293 TTL 二/八分频四位二进制计数器74295 TTL 四位双向通用移位寄存器74298 TTL 四2输入多路带存贮开关74299 TTL 三态输出八位通用移位寄存器7430 TTL 8输入端与非门7432 TTL 2输入端四或门74322 TTL 带符号扩展端八位移位寄存器74323 TTL 三态输出八位双向移位/存贮寄存器7433 TTL 开路输出2输入端四或非缓冲器74347 TTL BCD—7段译码器/驱动器74352 TTL 双4选1数据选择器/复工器74353 TTL 三态输出双4选1数据选择器/复工器74365 TTL 门使能输入三态输出六同相线驱动器74365 TTL 门使能输入三态输出六同相线驱动器74366 TTL 门使能输入三态输出六反相线驱动器74367 TTL 4/2线使能输入三态六同相线驱动器74368 TTL 4/2线使能输入三态六反相线驱动器7437 TTL 开路输出2输入端四与非缓冲器74373 TTL 三态同相八D锁存器74374 TTL 三态反相八D锁存器74375 TTL 4位双稳态锁存器74377 TTL 单边输出公共使能八D锁存器74378 TTL 单边输出公共使能六D锁存器74379 TTL 双边输出公共使能四D锁存器7438 TTL 开路输出2输入端四与非缓冲器74380 TTL 多功能八进制寄存器7439 TTL 开路输出2输入端四与非缓冲器74390 TTL 双十进制计数器74393 TTL 双四位二进制计数器7440 TTL 4输入端双与非缓冲器7442 TTL BCD—十进制代码转换器74352 TTL 双4选1数据选择器/复工器74353 TTL 三态输出双4选1数据选择器/复工器74365 TTL 门使能输入三态输出六同相线驱动器74366 TTL 门使能输入三态输出六反相线驱动器74367 TTL 4/2线使能输入三态六同相线驱动器74368 TTL 4/2线使能输入三态六反相线驱动器7437 TTL 开路输出2输入端四与非缓冲器74373 TTL 三态同相八D锁存器74374 TTL 三态反相八D锁存器74375 TTL 4位双稳态锁存器74377 TTL 单边输出公共使能八D锁存器74378 TTL 单边输出公共使能六D锁存器74379 TTL 双边输出公共使能四D锁存器7438 TTL 开路输出2输入端四与非缓冲器74380 TTL 多功能八进制寄存器7439 TTL 开路输出2输入端四与非缓冲器74390 TTL 双十进制计数器74393 TTL 双四位二进制计数器7440 TTL 4输入端双与非缓冲器7442 TTL BCD—十进制代码转换器74447 TTL BCD—7段译码器/驱动器7445 TTL BCD—十进制代码转换/驱动器74450 TTL 16:1多路转接复用器多工器74451 TTL 双8:1多路转接复用器多工器74453 TTL 四4:1多路转接复用器多工器7446 TTL BCD—7段低有效译码/驱动器74460 TTL 十位比较器74461 TTL 八进制计数器74465 TTL 三态同相2与使能端八总线缓冲器74466 TTL 三态反相2与使能八总线缓冲器74467 TTL 三态同相2使能端八总线缓冲器74468 TTL 三态反相2使能端八总线缓冲器74469 TTL 八位双向计数器7447 TTL BCD—7段高有效译码/驱动器7448 TTL BCD—7段译码器/内部上拉输出驱动74490 TTL 双十进制计数器7449174498 TTL 八进制移位寄存器7450 TTL 2-3/2-2输入端双与或非门74502 TTL 八位逐次逼近寄存器74503 TTL 八位逐次逼近寄存器7451 TTL 2-3/2-2输入端双与或非门74533 TTL 三态反相八D锁存器74534 TTL 三态反相八D锁存器7454 TTL 四路输入与或非门74540 TTL 八位三态反相输出总线缓冲器7455 TTL 4输入端二路输入与或非门74563 TTL 八位三态反相输出触发器74564 TTL 八位三态反相输出D触发器74573 TTL 八位三态输出触发器74574 TTL 八位三态输出D触发器74645 TTL 三态输出八同相总线传送接收器74670 TTL 三态输出4×4寄存器堆7473 TTL 带清除负触发双J-K触发器7474 TTL 带置位复位正触发双D触发器7476 TTL 带预置清除双J-K触发器7483 TTL 四位二进制快速进位全加器7485 TTL 四位数字比较器7486 TTL 2输入端四异或门7490 TTL 可二/五分频十进制计数器7493 TTL 可二/八分频二进制计数器7495 TTL 四位并行输入\输出移位寄存器7497 TTL 6位同步二进制乘法器常用74系列标准数字电路的中文名称资料器件代号器件名称74 74LS 74HC00 四2输入端与非门√√√01 四2输入端与非门(OC) √√02 四2输入端或非门√√√03 四2输入端与非门(OC) √√04 六反相器√√√05 六反相器(OC) √√06 六高压输出反相器(OC,30V) √√07 六高压输出缓冲,驱动器(OC,30V) √√√08 四2输入端与门√√√09 四2输入端与门(OC) √√√10 三3输入端与非门√√√11 三3输入端与门√√12 三3输入端与非门(OC) √√√13 双4输入端与非门√√√14 六反相器√√√15 三3输入端与门√√16 六高压输出反相器(OC,15V) √17 六高压输出缓冲,驱动器(OC,15V) √20 双4输入端与非门√√√21 双4输入端与门√√√22 双4输入端与非门(OC) √√25 双4输入端或非门(有选通端) √√√26 四2输入端高压输出与非缓冲器√√√27 三3输入端或非门√√√28 四2输入端或非缓冲器√√√30 8输入端与非门√√√32 四2输入端或门√√√33 四2输入端或非缓冲器(OC) √√37 四2输入端与非缓冲器√√38 四2输入端与非缓冲器(OC) √√40 双4输入端与非缓冲器√√√42 4线-10线译码器(BCD输入) √√43 4线-10线译码器(余3码输入) √44 4线-10线译码器(余3葛莱码输入) √48 4线-7段译码器√49 4线-7段译码器√50 双2路2-2输入与或非门√√√√√√51 2路3-3输入,2路2-2输入与或非门52 4路2-3-2-2输入与或门√53 4路2-2-2-2输入与或非门√54 4路2-3-3-2输入与或非门√√55 2路4-4输入与或非门√60 双4输入与扩展器√√61 三3输入与扩展器√62 4路2-3-3-2输入与或扩展器√64 4路4-2-3-2输入与或非门√65 4路4-2-3-2输入与或非门(OC) √70 与门输入J-K触发器√71 与或门输入J-K触发器√72 与门输入J-K触发器√74 双上升沿D型触发器√√78 双D型触发器√√85 四位数值比较器√86 四2输入端异或门√√√87 4位二进制原码/反码√95 4位移位寄存器√101 与或门输入J-K触发器√102 与门输入J-K触发器√107 双主-从J-K触发器√108 双主-从J-K触发器√109 双主-从J-K触发器√110 与门输入J-K触发器√111 双主-从J-K触发器√√112 双下降沿J-K触发器√。

电子元器件芯片74FCT162244ATPACT中文规格书

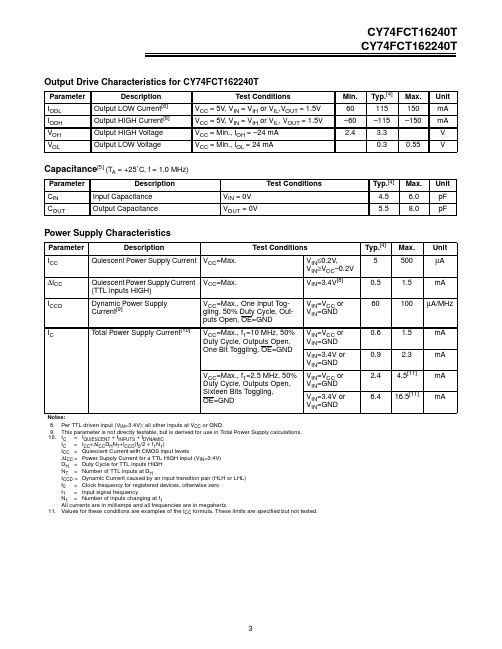

CY74FCT16240T CY74FCT162240T3Output Drive Characteristics for CY74FCT162240T ParameterDescription Test Conditions Min.Typ.[4]Max.Unit I ODLOutput LOW Current [6]V CC = 5V , V IN = V IH or V IL ,V OUT = 1.5V 60115150mA I ODHOutput HIGH Current [6]V CC = 5V , V IN = V IH or V IL , V OUT = 1.5V –60–115–150mA V OHOutput HIGH Voltage V CC = Min., I OH = –24 mA 2.4 3.3V V OL Output LOW Voltage V CC = Min., I OL = 24 mA 0.30.55V Capacitance [5](T A = +25˚C, f = 1.0 MHz)ParameterDescription Test Conditions Typ.[4]Max.Unit C INInput Capacitance V IN = 0V 4.5 6.0pF C OUT Output Capacitance V OUT = 0V 5.58.0pF Power Supply Characteristics ParameterDescription Test Conditions Typ.[4]Max.Unit I CCQuiescent Power Supply Current V CC =Max.V IN ≤0.2V ,V IN ≥V CC –0.2V 5500µA ∆I CCQuiescent Power Supply Current (TTL inputs HIGH)V CC =Max.V IN =3.4V [8]0.5 1.5mA I CCD Dynamic Power SupplyCurrent [9]V CC =Max., One Input Tog-gling, 50% Duty Cycle, Out-puts Open,OE=GND V IN =V CC or V IN =GND 60100µA/MHz I C Total Power Supply Current [10]V CC =Max., f 1=10 MHz, 50%Duty Cycle, Outputs Open,One Bit Toggling,OE=GNDV IN =V CC or V IN =GND 0.6 1.5mA V IN =3.4V or V IN =GND 0.9 2.3mA V CC =Max., f 1=2.5 MHz, 50%Duty Cycle, Outputs Open,Sixteen Bits Toggling,OE=GND V IN =V CC or V IN =GND 2.4 4.5[11]mA V IN =3.4V orV IN =GND 6.416.5[11]mANotes:8.Per TTL driven input (V IN =3.4V); all other inputs at V CC or GND.9.This parameter is not directly testable, but is derived for use in Total Power Supply calculations.10.I C =I QUIESCENT + I INPUTS + I DYNAMIC I C =I CC +∆I CC D H N T +I CCD (f 0/2 + f 1N 1)I CC =Quiescent Current with CMOS input levels∆I CC =Power Supply Current for a TTL HIGH input (V IN =3.4V)D H =Duty Cycle for TTL inputs HIGHN T =Number of TTL inputs at D H I CCD =Dynamic Current caused by an input transition pair (HLH or LHL)f 0=Clock frequency for registered devices, otherwise zerof 1=Input signal frequencyN 1=Number of inputs changing at f 1All currents are in milliamps and all frequencies are in megahertz.11.Values for these conditions are examples of the I CC formula. These limits are specified but not tested.。

74LVTH16244TTR, 规格书,Datasheet 资料

1/13February 2004sHIGH SPEED:t PD =3.2ns (MAX.)at T A =85°C V CC =3.0V sLOW POWER DISSIPATION HIGH LEVEL OUTPUT:I CC =190µA (MAX.)at T A =85°C sOUTPUT IMPEDANCE:|I OH |=32mA,I OL =64mA (MIN at V CC =3.0V)|I OH |=8mA,I OL =24mA (MIN at V CC =2.7V)sBALANCED PROPAGATION DELAYS:t PLH ≅t PHLsPOWER DOWN PROTECTION ON INPUTS AND OUTPUTSsCOMPATIBLE WITH TTL OUTPUTS:V IH =2V (MIN),V IL =0.8V(MAX)at V CC =2.7to 3.6VsPOWER-UP/DOWN 3-STATE:I OZPU =100µA MAX at V CC =0V to 1.5V,V CC =1.5V to 0V,T A =85°Cs BUS HOLD PROVIDED ON DATA INPUTS sOPERATING VOLTAGE RANGE:V CC (OPR)=2.7V to 3.6VsPIN AND FUNCTION COMPATIBLE WITH 74SERIES H16244sLATCH-UP PERFORMANCE EXCEEDS 500mA (JESD 17)DESCRIPTIONThe 74LVTH16244is a low voltage BiCMOS 16BIT BUS BUFFER (NON-INVERTED)fabricated with sub-micron silicon gate and five-layer metal wiring BiCMOS technology.It is ideal and full specified for hot-insertion and high speed 3.3V ap-plications;the power-up/down 3-state circuitry places the outputs in the high impedance state during power-up/down,which prevents driver con-flict.This function is guaranteed when V CC is be-tween 0and 1.5V.It can be interfaced to 3.3V sig-nal environment for both inputs and outputs.Any nG output control governs four BUS BUFFERS.Output Enable input (nG)tied together gives full 16-bit operation.When nG is LOW,the outputs are on.When nG is HIGH,the output are in high impedance state effectively isolated.Bus hold on data inputs is provided in order to eliminate the need for external pull-up or pull-down resistors.All inputs and outputs are equipped with protec-tion circuits against static discharge,giving them ESD immunity and transient excess voltage.74LVTH16244LOW VOLTAGE BICMOS 16BIT BUS BUFFER WITH BUS HOLD AND POWER UP 3-STATEORDER CODESPACKAGE T &RTSSOP4874LVTH16244TTR TFBGA5474LVTH16244LBRLOGIC DIAGRAMOb s o l e t e P r o d uc t (s ) - od u c t (s ) O b s o le t e P r o d u c t (s ) - o l e t e P r o dOb s o l e t e P r o d uc t (s ) - O b s o l e t e P r od 74LVTH162442/13INPUT AND OUTPUT EQUIVALENT CIRCUITPIN DESCRIPTIONTFBGA PIN N oTSSOP PIN N oSYMBOLNAME AND FUNCTIONA3,J31,241G,4G Output Enable Inputs A6,B5,B6,C5,C6,D5,D6,E5,E6,F5,F6,G5,G6,H5,H6,J647,46,44,43,41,40,38,37,36,35,33,32,30,29,27,261A1-4,2A1-43A1-4,4A1-4Data Inputs A1,B2,B1,C2,C1,D2,D1,E2,E1,F2,F1,G2,G1,H2,H1,J12,3,5,6,8,9,11,12,13,14,16,17,19,20,22,231Y1-4,2Y1-43Y1-4,4Y1-4Data OutputsJ4,A425,483G,2G Output Enable Inputs D3,D4,E3,E4,F3,F44,10,15,21,28,34,39,45GND Ground (0V)A2,A5,B3,B4,H3,H4,J2,J5-NC No ConnectedC4,G4,C3,G342,31,7,18V CCPositive Supply VoltageO b s o l e t e P r o d u c t (s ) - O b s o lOb s o l e74LVTH162443/13PIN CONNECTION (top view for TSSOP,top through view for BGA)TRUTH TABLEZ =High Impedance;X =Don’t care,n =1..4,x =1..4INPUTSOUTPUT nG xAn xYn L L LL H H HXZOb s o l e t e P r o d uc t (s ) - O b s o l e t e P r od u c t (s ) 74LVTH162444/13ABSOLUTE MAXIMUM RATINGSAbsolute Maximum Ratings are those values beyond which damage to the device may occur.Functional operation under these conditions isnot implied(*)500mW:≅ 65°C derated to 300mW by 10mW/°C:65°C to 85°CRECOMMENDED OPERATING CONDITIONS1)V I from 0.8V to 2.0V at V CC =2.7V to 3.6VSymbol ParameterValue Unit V CC Supply Voltage -0.5to +4.6V V I DC Input Voltage-0.5to +4.6V V O DC Output Voltage (Output disabled)-0.5to +4.6V V O DC Output Voltage -0.5to V CC +0.5V I IK DC Input Diode Current −50mA I OK DC Output Diode Current −50mA I O DC Output Current low state 128mA I O DC Output Current high state 64mA I CC DC V CC or Ground Current ±100mA P d Power Dissipation (*)400mWT stgStorage Temperature-65to +150°CT LLead Temperature (10sec)300°CSymbol ParameterValue Unit V CC Supply Voltage 2.7to 3.6V V I Input Voltage (An,nG)0to 3.6VV O Output VoltageV CC VV OOutput Voltage (Output Disabled) 3.6VT op Operating Temperature -40to 85°Cdt/dV CC Minimum Power-up ramp rate200µs/V dt/dvInput Rise and Fall Time (note 1)0to 20ns/VO b s o l e t e P r o d u c t (s ) - O b s o l e t e P r o d u c t (s )Ob s o l e t e P r o d uc t (s ) - O b s o l e t e P r od u c t (s ) 74LVTH162445/13DC SPECIFICATIONS(*)Power Supply Range V CC =3.3±0.3VSymbolParameterTest ConditionValueUnitV CC (V)T A =25°C -40to 85°C Min.Typ.Max.Min.Max.V IK Input Voltage Clamp (An,nG)2.7I IK =-18mA-0.85-1.2V V IH High Level Input Voltage (An,nG)2.7 2.0 2.0V3.3(*) 2.02.0V IL Low Level Input Voltage (An,nG)2.70.80.8V3.3(*)0.80.8I IControl Input Leakage Current3.6V I =GND or V CC ±1µA Data Input Leakage Current3.6V I =GND or V CCnG =GND ±1µA I I(HOLD)Data Input Hold Current3.0V I =0.8V13575µA3.0V I =2.0V -135-753.6V I =0to 3.6V ±500µAV OHHigh Level Output Voltage2.7I O =-100µA 2.5V2.7I O =-8mA 2.43.0I O =-32mA 2.0V OLLow Level Output Voltage2.7I O =100µA0.2V2.7I O =24mA 0.53.0I O =16mA 0.43.0I O =32mA 0.53.0I O =64mA0.55I OZHigh Impedance Output Leakage Current3.6V O =0.5V or 3.0V V I =V IL or V IH nG =V CC±5µAI OZPUHigh Impedance Output Leakage Current0to 1.5V O =0.5V or 3.0V V I =GND or V CC nG =GND or V CC±100µAI OZPDHigh Impedance Output Leakage Current 1.5to 0V O =0.5V or 3.0V V I =GND or V CC nG =GND or V CC±100µAI OFFPower Off Leakage CurrentV I =GND to 3.6V V O =GND to 3.6V ±100µAI CCAQuiescent Supply Current3.6V O =High ,I O =00.19mAV O =Low,I O =05.0nG =V CC,I O =0V O =GND or V CC0.19∆I CCMaximum Quiescent Supply Current /Input (An or nG)3.3(*)V I =V CC -0.6V An,nG =V CC or GND0.2mAO b s o l e t e P r o d u c t (s ) - O b s o l e t e P r o d u c t (s )Ob s o l e t e P r o d uc t (s ) 74LVTH162446/13AC ELECTRICAL CHARACTERISTICS1)Skew is defined as the absolute value of the difference between the actual propagation delay for any two outputs of the same device switching in the same direction,either HIGH or LOW (t OSLH =|t PLHm -t PLHn |,t OSHL =|t PHLm -t PHLn |2)Parameter guaranteed by designCAPACITANCE CHARACTERISTICSTEST CIRCUITC L =50pF or equivalent (includes jig and probe capacitance)R L =R 1=500Ωor equivalentR T =Z OUT of pulse generator (typically 50Ω)SymbolParameterTest ConditionValueUnitV CC =2.7V V CC =3.3± 0.3V Min.Max.Min.Typ.Max.t PLH Propagation Delay Time An to Yn T A =-40to 85°C3.7 1.2 2.5 3.2ns t PHL Propagation Delay Time An to Yn 3.7 1.2 2.5 3.2ns t PZL Output Enable Time nG to Yn 5.0 1.2 2.74.0ns t PZH Output Enable Time nG to Yn5.0 1.2 2.7 4.0ns t PLZ Output Disable Time nG to Yn 4.4 2.0 3.7 4.2ns t PHZOutput Disable Time nG to Yn 5.02.24.45.1ns t OSLHt OSHLOutput To Output Skew Time (note1,2)0.5nsSymbol ParameterTest Condition ValueUnitV CC (V)T A =25°C -40to 85°C Min.Typ.Max.Min.Max.C IControl Input Capacitance open 6pFC OOutput Capacitance3.315pFTEST SWITCH t PLH ,t PHLOpen t PZL ,t PLZ (V CC =3.0to 3.6V)6V t PZL ,t PLZ (V CC =2.7V)6V t PZH ,t PHZGNDt (s ) - O b s o l e t e P r o d u c t (s )Ob s o l e t e P r o d uc t (s74LVTH162447/13WAVEFORM SYMBOL VALUEWAVEFORM 1:PROPAGATION DELAY (f=1MHz;50%duty cycle)SymbolV CC3.0to 3.6V2.7V V IH 2.7V V CC V M 1.5V 1.5V V X V OL +0.3V V OL +0.15V V YV OH -0.3VV OH -0.15VO b s o l e t e POb s o l e t e P r o d uc t (s ) - O b s o l e74LVTH162448/13WAVEFORM 2:OUTPUT ENABLE AND DISABLE TIME (f=1MHz;50%duty cycle)O b s o l e t e P r o d u c t (s )Ob s o l e t e P r o d uc t (s ) - O b s o l e t e P r od u c t (s ) 74LVTH1624413/13Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for theconsequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.The ST logo is a registered trademark of STMicroelectronics All other names are the property of their respective owners © 2004 STMicroelectronics - All Rights Reserved STMicroelectronics GROUP OF COMPANIESAustralia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States.O b s o l e t e P r o d u c t (s ) - O b s o l e t e P r o d u c t (s )。

74HC164中文资料(功能,真值表,引脚图及电气参数介绍)

74HC164中文资料(功能,真值表,引脚图及电气参数介绍)

移位寄存器74HC164中文资料(功能,真值表,引脚图及电气参数介绍)

SN54HC164,/SN74HC164是8位移位寄存器,当其中一个(或二个)选通串行输入端的低电平禁止进入新数据,并把第一个触发器在下一个时钟脉冲来后复位到低电平时,门控串行输入端(A 和B)可完全控制输入数据。

一个高电平输入后就使另一个输入端赋能,这个输入就决定了第一个触发器的状态。

虽然不管时钟处于高电平或低电平时,串行输入端的数据都可以被改变,但只有满足建立条件的信息才能被输入。

时钟控制发生在时钟输入由低电平到高电平的跃变上。

为了减小传输线效应,所有输入端均采用二极管钳位。

74HC164功能表:

H=高电平(稳定态) L=低电平(稳定态)×=不定↑=从低电平转换到高电平

QA0…QH0=在稳定态输入条件建立前QA…QH 的相应电平

QAn…QHn=在最近的时钟输入条件(↑)建立前QA…QH 的相应电平,表示移位一位

74HC164引脚图及逻辑图:

图1 逻辑图(正逻辑)

图2 引脚图

74HC164电气参数:

Absolute Maximum Ratings绝对最大额定值

DC SPECIFICATIONS直流电气规格表:

DC SPECIFICATIONS直流电气规格(续)

图3 参数测量信息

74HC164典型工作时序图

图4 typical clear, shift, and clear sequence典型清除、移位和清除时序

74HC164应用电路

TAG标签:74真值引脚表图。

74系列中文资料(超级全)

┌┴─┴─┴─┴─┴─┴─┴┐ 双 D 触发器 74LS74

│14 13 12 11 10 9 8 │

)

│

│ 1 2 3 4 5 6 7│

└┬─┬─┬─┬─┬─┬─┬┘

1Cr 1D 1Ck 1St 1Q -1Q GND

Vcc 8Q 8D 7D 7Q 6Q 6D 5D 5Q ALE

┌┴─┴─┴─┴─┴─┴─┴─┴─┴─┴┐ 8 位锁存器 74LS373

Vcc -G B1 B2 B3 B4 B8 B6 B7 B8

┌┴─┴─┴─┴─┴─┴─┴─┴─┴─┴┐ 8 位总线驱动器 74LS245

│20 19 18 17 16 15 14 13 12 11│

)

│ DIR=1 A=>B

│ 1 2 3 4 5 6 7 8 9 10│ DIR=0 B=>A

└┬─┬─┬─┬─┬─┬─┬─┬─┬─┬┘

___

)

│ Y = A+B

│ 1 2 3 4 5 6 7│

└┬─┬─┬─┬─┬─┬─┬┘

1Y 1A 1B 2Y 2A 2B GND

Vcc 2Y 2B 2A 2D 2E 1F

┌┴─┴─┴─┴─┴─┴─┴┐ 双与或非门 74S51

│14 13 12 11 10 9 8│

_____

)

│ 2Y = AB+DE

DIR A1 A2 A3 A4 A5 A6 A7 A8 GND

正逻辑与门,与非门:

Vcc 4B 4A 4Y 3B 3A 3Y

┌┴─┴─┴─┴─┴─┴─┴┐

│14 13 12 11 10 9 8│

Y = AB )

│ 2 输入四正与门 74LS08

│ 1 2 3 4 5 6 7│

74ch164中文资料

查看文章74HC164引脚图与中文资料2010-01-25 15:048 位串入、并出移位寄存器1. 概述74HC164、74HCT164 是高速硅门 CMOS 器件,与低功耗肖特基型 TTL (LSTTL) 器件的引脚兼容。

74HC164、74HCT164 是 8 位边沿触发式移位寄存器,串行输入数据,然后并行输出。

数据通过两个输入端(DSA 或 DSB)之一串行输入;任一输入端可以用作高电平使能端,控制另一输入端的数据输入。

两个输入端或者连接在一起,或者把不用的输入端接高电平,一定不要悬空。

时钟 (CP) 每次由低变高时,数据右移一位,输入到 Q0, Q0 是两个数据输入端(DSA 和 DSB)的逻辑与,它将上升时钟沿之前保持一个建立时间的长度。

主复位 (MR) 输入端上的一个低电平将使其它所有输入端都无效,同时非同步地清除寄存器,强制所有的输出为低电平。

2. 特性门控串行数据输入异步中央复位符合 JEDEC 标准 no. 7A静电放电 (ESD) 保护:·HBM EIA/JESD22-A114-B 超过 2000 V·MM EIA/JESD22-A115-A 超过 200 V 。

多种封装形式额定从 -40 °C 至+85 °C 和 -40 °C 至+125 °C 。

3. 功能图图 1. 逻辑符号图 2. IEC 逻辑符号图 3. 逻辑图图 4. 功能图4. 引脚信息图 5. DIP14、SO14、SSOP14 和 TSSOP14 封装的引脚配置引脚说明符号引脚说明DSA 1 数据输入DSB 1 数据输入Q0~Q3 3~6 输出GND 7 地 (0 V)CP 8 时钟输入(低电平到高电平边沿触发)/M/R 9 中央复位输入(低电平有效)Q4~Q7 10~13 输出VCC 14 正电源罗亩的笔记74HC164英文资料temp_08121617411733.rar74HC164中文资料temp_08121617428539.rar阅读:次参考链接:/news/2008-12/8713.htm。

74FCT244中文资料

1Data sheet acquired from Harris SemiconductorSCHS270AFeatures•CD54/74FCT240, CD54/74FCT240AT - Inverting •CD54/74FCT241,CD54/74FCT244,CD54/74FCT244AT -Non-Inverting •Buffered Inputs•Typical Propagation Delay:4.1ns at VCC = 5V , TA = 25o C (FCT240AT, FCT244AT)•SCR-Latchup-Resistant BiCMOS Process and Circuit Design •FCTXXX Types - Speed of Bipolar FAST ®/AS/S;FCTXXXAT Types - 30% Faster Than FAST/AS/S with Significantly Reduced Power Consumption •48mA to 64mA Output Sink Current (Commer-cial/Extended Industrial)•Output Voltage Swing Limited to 3.7V at VCC = 5V •Controlled Output-Edge Rates •Input/Output Isolation to VCC•BiCMOS Technology with Low Quiescent PowerDescriptionThe CD54/74FCT240,240AT ,241,244and 244AT three-state octal buffers/line drivers use a small-geometry BiCMOS technology.The output stage is a combination of bipolar and CMOS transistors that limits the output-HIGH level to two diode drops below VCC.This resultant lowering of output swing (0V to 3.7V)reduces power bus ringing (a source of EMI)and minimizes VCC bounce and ground bounce and their effects during simultaneous output switching.The output configuration also enhances switching speed and is capable of sinking 48mA to 64mA.The CD54/74FCT240,240A T ,244and 244AT have active-LOW output enables (1OE,2OE).The CD54/74FCT241and CD54/74FCT241AT have one active-LOW (1OE)and one active-HIGH (2OE) output enable.Functional DiagramNOTE:H = High Voltage Level, L = LOW Voltage Level X = Immaterial, Z = HIGH ImpedanceOrdering InformationPART NUMBER TEMP. RANGE (o C)PACKAGE CD54/74FCT240E -55 to 125, 0 to 7020 Ld PDIP CD54/74FCT240ATE -55 to 125, 0 to 7020 Ld PDIP CD54/74FCT241E -55 to 125, 0 to 7020 Ld PDIP CD54/74FCT244E -55 to 125, 0 to 7020 Ld PDIP CD54/74FCT244ATE -55 to 125, 0 to 7020 Ld PDIP CD54/74FCT240M -55 to 125, 0 to 7020 Ld SOIC CD54/74FCT240ATM -55 to 125, 0 to 7020 Ld SOIC CD54/74FCT241M -55 to 125, 0 to 7020 Ld SOIC CD54/74FCT244M -55 to 125, 0 to 7020 Ld SOIC CD54/74FCT244ATM -55 to 125, 0 to 7020 Ld SOIC CD54/74FCT240SM -55 to 125, 0 to 7020 Ld SSOP CD54/74FCT241SM -55 to 125, 0 to 7020 Ld SSOP CD54/74FCT244SM -55 to 125, 0 to 7020 Ld SSOPCD54FCT240H -55 to 125CD54FCT241H -55 to 125CD54FCT244H-55 to 125CD54/74FCT240, CD54/74FCT240AT TRUTH TABLE INPUT INPUT OUTPUT1OE,20EA Y L L H L H L HXZCD54/74FCT244, CD54/74FCT244AT TRUTH TABLE INPUT INPUT OUTPUT1OE,2OEA Y L L H L H L HXZCD54/74FCT241 TRUTH TABLEINPUT OUTPUT INPUT OUTPUT 1OE 1A 1Y 2OE2A 2Y L L L L X Z L H H H L L H XZH HH1816141297532468111315171191A01A11A21A32A02A12A22A31OE 2OE1Y01Y11Y21Y32Y02Y12Y22Y31Y01Y11Y21Y32Y02Y12Y22Y3241, 2442401OE 2OE240, 244241VCC = 20GND = 10February 1996CAUTION: These devices are sensitive to electrostatic discharge. Users should follow proper IC Handling Procedures.Copyright © Harris Corporation 1996File Number2227.3CD54/74FCT240, CD54/74FCT240AT,CD54/74FCT241, CD54/74FCT244,CD54/74FCT244ATFCT Interface LogicOctal Buffers/Line Drivers, Three-StateFAST® is a registered trademark of Fairchild Semiconductor Corporation.CD74FCT240AT and CD74FCT244AT were not acquired from Harris Semiconductor.元器件交易网Switching Specifications FCT Series tr, tf = 2.5ns, C L = 50pF, R L - See Figure 2PARAMETER SYMBOL V CC(V)+25oC0o C to+70o C-55o C to+125o C+25oC0o C to+70o C-55o C to+125o CUNITS TYP MIN MAX MIN MAX TYP MIN MAX MIN MAXPropagation DelaysData to Outputs FCT240/AT t PLH,t PHL5†5 1.58 1.59 4.4 1.5 5.6 1.5 6.7nsFCT241t PLH,t PHL54 1.5 6.5 1.57-----nsFCT244/AT t PLH,t PHL5 4.5 1.5 6.5 1.57 3.8 1.5 5.3 1.5 6.2µsOutput Enable Times FCT240/AT t PZL,t PZH57 1.510 1.510.5 4.7 1.5 6.2 1.57.7µsFCT241t PZL,t PZH5 5.5 1.58 1.58.5-----nsFCT244/AT t PZL,t PZH56 1.58 1.58.5 4.8 1.5 6.5 1.57.8nsOutput Disable Times FCT240/AT t PLZ,t PHZ56 1.59.5 1.5104 1.5 5.6 1.5 6.5µsFCT241t PLZ,t PHZ5 4.5 1.57 1.57.5-----nsFCT244/AT t PLZ,t PHZ55 1.57 1.57.5 4.5 1.5 5.8 1.5 6.8µsPower DissipationCapacitanceFCT240/AT C PD§-38 Typical38 Typical pFFCT241 C PD§-33 Typical-pFFCT244/AT C PD§35 Typical35 Typical pFMin. (Valley) V OHV During Switch-ing of Other Outputs(Output Under Test Not Switching)V OHVSeeFigure 150.5 Typical at +25o C VMax. (Peak) V OLP During Switch-ing of Other Outputs(Output Under Test Not Switching)V OLPSeeFigure 15 1 Typical at +25o C VInput Capacitance C I---10-10--10-10pF 3-State Output Capacitance C O---15-15--15-15pF†5V:min. is at 5.5V, max. is at 4.5V.5V:min. is at 5.25V for 0o C to +70o C, max. is at 4.75V for 0o C to +70o C, typ. is at 5V§C PD,measured per function,is used to determine the dynamic power consumption.P D(per package)=V CC I CC+∑(V CC2fiC PD+V O2 fo C L + V CC∆I CC D) where:V CC = supply voltage∆I CC = flow through current x unit loadC L = output load capacitanceD = duty cycle of input highfo = output frequencyfi = input frequencyCD54/74FCT540, CD54/74FCT540AT, CD54/74FCT241, CD54/74FCT244, CD54/74FCT244AT2IMPORTANT NOTICETexas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI’s standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE (“CRITICAL APPLICATIONS”). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER’S RISK.In order to minimize risks associated with the customer’s applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI’s publication of information regarding any third party’s products or services does not constitute TI’s approval, warranty or endorsement thereof.Copyright © 1999, Texas Instruments Incorporated。

IDT74FCT162245ET中文资料

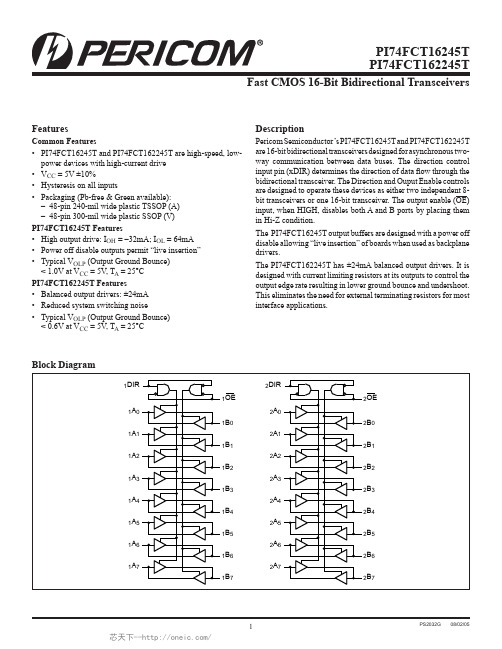

MILITARY AND COMMERCIAL TEMPERATURE RANGESAUGUST 1996The 16-bit transceivers are built using advanced dual metal CMOS technology. These high-speed, low-power transceiv-ers are ideal for synchronous communication between two busses (A and B). The Direction and Output Enable controls operate these devices as either two independent 8-bit trans-ceivers or one 16-bit transceiver. The direction control pin (xDIR) controls the direction of data flow. The output enable pin (x OE ) overrides the direction control and disables both ports. All inputs are designed with hysteresis for improved noise margin.The FCT16245T are ideally suited for driving high-capaci-tance loads and low-impedance backplanes. The output buff-ers are designed with power off disable capability to allow "live insertion" of boards when used as backplane drivers.The FCT162245T have balanced output drive with current limiting resistors. This offers low ground bounce, minimal undershoot, and controlled output fall times– reducing the need for external series terminating resistors. The FCT162245T are plug-in replacements for the FCT16245T and ABT16245 for on-board interface applications.The FCT166245T are suited for very low noise, point-to-point driving where there is a single receiver, or a light lumpedThe IDT logo is a registered trademark of Integrated Device Technology, Inc.FUNCTIONAL BLOCK DIAGRAM1 DIR1OE1A 11A 21A 31A 41A 51A 61A 71A 81B 11B 21B 31B 41B 51B 61B 71B 82545 drw 022 DIR22A 12A 22A 32A 42A 52A 62A 72A 82B 12B 22B 32B 42B 52B 62B 72B 82545 drw 01•Common features:–0.5 MICRON CMOS Technology–High-speed, low-power CMOS replacement for ABT functions–Typical t SK (o) (Output Skew) < 250ps–Low input and output leakage ≤ 1µA (max.)–ESD > 2000V per MIL-STD-883, Method 3015;> 200V using machine model (C = 200pF, R = 0)–Packages include 25 mil pitch SSOP, 19.6 mil pitchTSSOP, 15.7 mil pitch TVSOP and 25 mil pitch Cerpack –Extended commercial range of -40°C to +85°C •Features for FCT16245T/AT/CT/ET:–High drive outputs (-32mA I OH , 64mA I OL )–Power off disable outputs permit “live insertion”–Typical V OLP (Output Ground Bounce) < 1.0V at V CC = 5V, T A = 25°C•Features for FCT162245T/AT/CT/ET:–Balanced Output Drivers:±24mA (commercial),±16mA (military)–Reduced system switching noise–Typical V OLP (Output Ground Bounce) < 0.6V at V CC = 5V,T A = 25°C1DIR 1B 1GND1B 3V CCGND2B 2GNDV CCGND1B 21B 41B 51B 61B 71B 82B 12B 32B 42B 52B 72B 82B 62DIR1A 11A 2GND1A 31A 4V CC1A 51A 61A 71A 82A 12A 22A 32A 4V CC2A 52A 72A 82A 6GNDGNDGND21OE 2545 drw 04CERPACK TOP VIEWFEATURES: (Cont'd.)DESCRIPTION: (Cont'd.)•Features for FCT166245T/AT/CT:–Light Drive A Port:±8mA (commercial),±6mA (military)–High Drive B Port:+64mA, –32mA (commercial),+48mA, –24mA (military)–Minimal system switching noise–Typical V OLP (Output Ground Bounce) < 0.25V at V CC = 5V,T A = 25°C (A Port Switching)•Features for FCT162H245T/AT/CT/ET:–Bus Hold retains last active bus state during 3-state –Eliminates the need for external pull up resistorsload (<100pF). The buffers are designed to limit the output current to levels which will avoid noise and ringing on the signal lines without using external series terminating resis-tors. These parts have a ±8mA driver on the "A" Port and a +64/–32mA driver on the "B" Port, making them ideal for interfacing noisy system busses to noise sensitive interfaces.The FCT162H245T have "Bus Hold" which retains the input's last state whenever the input goes to high impedance.This prevents "floating" inputs and eliminates the need for pull-up/down resistors.PIN CONFIGURATIONS1DIR 1B 1GND1B 3V CCGND2B 2GNDV CCGND1B 21B 41B 51B 61B 71B 82B 12B 32B 42B 52B 72B 82B 62DIR1A 11A 2GND1A 31A 4V CC1A 51A 61A 71A 82A 12A 22A 32A 4V CC2A 52A 72A 82A 6GNDGNDGND212545 drw 03SSOP/TSSOP/TVSOP TOP VIEW1. This parameter is measured at characterization but not tested.(1)2545 tbl 02CAPACITANCE (T A = +25°C, f = 1.0MHz)(1)1.H = HIGH Voltage LevelL = LOW Voltage Level X = Don't CareZ = High Impedance2545 tbl 01NOTES:1.On FCT162H245T these pins have “Bus Hold”. All other pins are standard inputs, outputs or I/Os.2.On FCT166245T this is the ±8mA Port.3.On FCT166245T this is the +64/–32mA Port.1.Stresses greater than those listed under ABSOLUTE MAXIMUM RAT-INGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.2.All device terminals except FCT162XXXT and FCT166XXXT (A-Port)Output and I/O terminals.3.Output and I/O terminals for FCT162XXXT and FCT166XXXT (A-Port).ADC ELECTRICAL CHARACTERISTICS OVER OPERATING RANGE (STANDARD PARTS)Following Conditions Apply Unless Otherwise Specified:NOTES:1.For conditions shown as Max. or Min., use appropriate value specified under Electrical Characteristics for the applicable device type.2.Typical values are at Vcc = 5.0V, +25°C ambient.3.Not more than one output should be tested at one time. Duration of the test should not exceed one second.4.Duration of the condition can not exceed one second.5.The test limit for this parameter is ± 5µA at T A = –55°C.DC ELECTRICAL CHARACTERISTICS OVER OPERATING RANGE (BUS HOLD) Following Conditions Apply Unless Otherwise Specified:A CC A CCNOTES:1.For conditions shown as Max. or Min., use appropriate value specified under Electrical Characteristics for the applicable device type.2.Typical values are at Vcc = 5.0V, +25°C ambient.3.Not more than one output should be tested at one time. Duration of the test should not exceed one second.4.Pins with Bus Hold are identified in the pin description.5.The test limit for this parameter is ± 5µA at T A = –55°C.6.Does not include Bus Hold I/O pins.1.For conditions shown as Max. or Min., use appropriate value specified under Electrical Characteristics for the applicable device type.2.Typical values are at V CC = 5.0V, +25°C ambient.3.Per TTL driven input (V IN = 3.4V). All other inputs at V CC or GND.4.This parameter is not directly testable, but is derived for use in Total Power Supply Calculations.5.Values for these conditions are examples of the I CC formula. These limits are guaranteed but not tested.6.I C = I QUIESCENT + I INPUTS + I DYNAMICI C = I CC + ∆I CC D H N T + I CCD (f CP N CP/2 + f i N i)I CC = Quiescent Current (I CCL, I CCH and I CCZ)∆I CC = Power Supply Current for a TTL High Input (V IN = 3.4V)D H = Duty Cycle for TTL Inputs HighN T = Number of TTL Inputs at D HI CCD = Dynamic Current Caused by an Input Transition Pair (HLH or LHL)f CP = Clock Frequency for Register Devices (Zero for Non-Register Devices)N CP = Number of Clock Inputs at f CPf i = Input FrequencyN i = Number of Inputs at f iNOTES:1.See test circuit and waveforms.2.Minimum limits are guaranteed but not tested on Propagation Delays.3.Skew between any two outputs of the same package switching in the same direction. This parameter is guaranteed by design.4.This parameter is guaranteed but not tested.5.Including parts with Bus Hold.ANOTES:1.See test circuit and waveforms.2.Minimum limits are guaranteed but not tested on Propagation Delays.3.Skew between any two outputs of the same package switching in the same direction. This parameter is guaranteed by design.4.This parameter is guaranteed but not tested.C L =Load capacitance: includes jig and probe capacitance.R T =Termination resistance: should be equal to Z OUT of the PulseGenerator.7.0V3V 1.5V 0V3V 1.5V 0V 3V 1.5V 0V 3V 1.5V 0V DATA INPUTPRESET CLEAR ETC.1.5V1.5V3V 1.5V 0V 1.5V V OH OUTPUT3V 1.5V 0VV OL 3V 1.5V0V 3.5V 0VV OLENABLEDISABLEV OHPRESET CLEARCLOCK ENABLEETC.PROPAGATION DELAYSET-UP, HOLD AND RELEASE TIMES PULSE WIDTHSWITCH POSITIONTEST CIRCUITS AND WAVEFORMS TEST CIRCUITS FOR ALL OUTPUTSNOTES:1.Diagram shown for input Control Enable-LOW and input Control Disable-HIGH2.Pulse Generator for All Pulses: Rate ≤ 1.0MHz; t F ≤ 2.5ns; t R ≤ 2.5ns2545 drw 092545 drw 052545 drw 062545 drw 082545 drw 07ENABLE AND DISABLE TIMESORDERING INFORMATION2545 drw 10IDT XXXXXX X X BlankB PV PA PF E 245T 245AT 245CT 245ET CommercialMIL-STD-883, Class BShrink Small Outline Package (SO48-1)Thin Shrink Small Outline Package (SO48-2)Thin Very Small Outline Package (SO48-3)CERPACK (E48-1)Non-Inverting 16-Bit Bidirectional Transceiver5474–55°C to +125°C –40°C to +85°CFCTBlank H Standard Bus Hold1616216616-Bit High Drive16-Bit Balanced Drive 16-Bit Light Drive X X。

74ACT16244中文资料

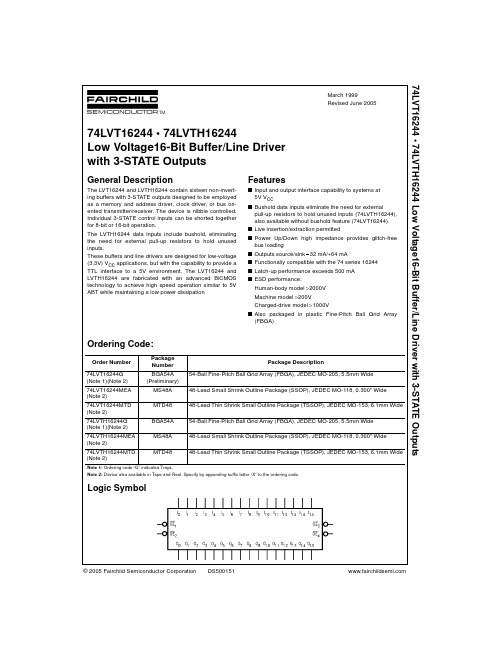

74ACT1624416-BIT BUS BUFFERWITH 3STATE OUTPUTS (NON INVERTED)®February 2000s HIGH SPEED:t PD =4.8ns (TYP.)at V CC =5V sLOW POWER DISSIPATION:I CC =8µA (MAX.)at T A =25o CsCOMPATIBLEWITH TTL OUTPUTS V IH =2V (MIN),V IL =0.8V(MAX)s50ΩTRANSMISSION LINE DRIVING CAPABILITYsSYMMETRICAL OUTPUT IMPEDANCE:|I OH |=I OL =24mA (MIN)sBALANCED PROPAGATION DELAYS:t PLH ≅t PHLsOPERATING VOLTAGERANGE:V CC (OPR)=4.5V to 5.5VsIMPROVED LATCH-UP IMMUNITYDESCRIPTIONThe ACT16244is an advanced CMOS 16-BIT BUS BUFFER (3-STATE)fabricated with sub-micron silicon gate and double-layer metal wiring C 2MOS technology.G output control governs four BUS BUFFERs.The device is designed to be used with 3-state memory address drivers,clock drivers,and bus-oriented receivers and transmitters.The device can be used as four 4-bit buffers,two 8-bit buffers,or one 16-bit buffer.The device is designed to interface directly High Speed CMOS systems with TTL,NMOS and CMOS output voltage levels.All inputs and outputs are equipped with protection circuits against static discharge,giving them 2KV ESD immunity and transient excess voltage.TSSOPPIN CONNECTIONORDER CODESPACKAGE TUBET &R TSSOP74ACT16244TTR1/8TRUTH TABLEINPUT OUTPUTG An Yn L L L L H H HXZX:”H”or ”L”Z:High impe danceINPUT AND OUTPUT EQUIVALENT CIRCUITIEC LOGIC SYMBOLSPIN DESCRIPTIONPIN NoSYMBOLNAME AND FUNCTION 11G Output Enable Input 2,3,5,61Y1to 1Y4Data Outputs 8,9,11,122Y1to 2Y4Data Outputs 13,14,16,173Y1to 3Y4Data Outputs 19,20,22,234Y1to 4Y4Data Outputs 244G Output Enable Input 253G Output Enable Input 30,29,27,264A1to 4A4Data Inputs 36,35,33,323A1to 3A4Data Inputs 41,40,38,372A1to 2A4Data Inputs 47,46,44,431A1to 1A4Data Inputs 482G Output Enable Input 4,10,15,21,28,34,39,45GND Ground (0V)7,18,31,42V CCPositive Supply Voltage74ACT162442/874ACT16244ABSOLUTE MAXIMUM RATINGSSymbol Parameter Value Unit V CC Supply Voltage-0.5to+7V V I DC Input Voltage-0.5to V CC+0.5V V O DC Output Voltage-0.5to V CC+0.5VI IK DC Input Diode Current±20mAI OK DC Output Diode Current±20mAI O DC Output Current±50mAI CC orI GN D DC V CC or Ground Current±400mAT stg Storage Temperature-65to+150o C T L Lead Temperature(10sec)300o C Absolute Maximum Ratingsarethose values beyond which dam age to the device may occur.Functional operation un der these condition is not implied.RECOMMENDED OPERATING CONDITIONSSymbol Parameter Value Unit V CC Supply Voltage 4.5to5.5V V I Input Voltage0to V CC V V O Output Voltage0to V CC V T op Operating Temperature:-40to+85o C dt/dv Input Rise and Fall Time V CC=4.5to5.5V(note1)8ns/V 1)V IN from0.8V to2.0V3/8DC SPECIFICATIONSSymbol Parameter Test Conditions Value UnitV CC (V)T A=25o C-40to85o C Min.Typ.Max.Min.Max.V IH High Level Input Voltage 4.5V O=0.1V orV CC-0.1V 2.0 2.0V5.5 2.0 2.0V IL Low Level Input Voltage 4.5V O=0.1V orV CC-0.1V 0.80.8V5.50.80.8V OH High Level OutputVoltage 4.5I O=-50µA 4.4 4.49 4.4V 5.5I O=-50µA 5.4 5.49 5.44.5I O=-24mA 3.94 3.85.5I O=-24mA 4.94 4.8V OL Low Level OutputVoltage 4.5I O=50µA0.0010.10.1V 5.5I O=50mA0.0010.10.14.5I O=24mA0.360.445.5I O=24mA0.360.44I I Input Leakage Current 5.5V I=V CC orGND±0.1±1µAI OZ High Impedance OutputLeakage Current 5.5V I=V IH orV ILV O=V CC orGND±0.5±5µAI CC T Max I CC/Input 5.5V I=V CC-2.1V0.91mA I CC Quiescent SupplyCurrent5.5V I=V CC orGND880µAI OLD Dynamic Output Current(note1,2)5.5V OLD=1.65V max75mAI OH D V OHD=3.85V min-75mA1)Maximum test duration2ms,one output loaded attime2)Inciden t wave switch ing is guaranteed on transmission lines with impeda nces aslow as50Ω.74ACT162444/8TEST CIRCUITTESTSWITCH t PLH ,t PHL Open t PZL ,t PLZ 2V CC t PZH ,t PHZGNDC L =50pF or equivalent (includes jigand probe capacitance)R L =R 1=500ΩorequivalentR T =Z OU T of pulse generator (typ ically 50Ω)CAPACITIVE CHARACTERISTICSSymbolParameterTest ConditionsValueUnitV CC (V)T A =25oC-40to 85oC Min.Typ.Max.Min.Max.C IN Input Capacitance 5.0 3.6pF C OUT Output Capacitance 5.011pF C PDPower Dissipation Capacitance (note 1)5.042pF1)C PD isdefined as the value of the IC’sinternal equiva lent capacitance which is calculated fromthe operating current consumption without load.(Referto Test Circuit).Average operating current can be obtained bythe following equation.I CC (opr)=C PD •V CC •f IN +I CC /16(per circuit)AC ELECTRICAL CHARACTERISTICS (C L =50pF,R L =500Ω,Input t r =t f =3ns)SymbolParameterTest ConditionValueUnitV CC (V)T A =25oC -40to 85o CMin.Typ.Max.Min.Max.t PLH t PHL Propagation Delay Time 5.0(*) 2.0 3.3 5.0 2.0 6.0ns 3.0 4.8 6.5 3.08.0t PZL t PZH Output Enable Time 5.0(*)4.0 6.58.7 4.09.7ns 3.05.57.7 3.08.8t PL Z t PH ZOutput Disable Time5.0(*)4.0 6.08.0 4.09.2ns3.04.66.43.07.3(*)Voltage range is 5V ±0.5V74ACT162445/874ACT16244WAVEFORM1:PROPAGATION DELAYS(f=1MHz;50%duty cicle) WAVEFORM2:OUTPUT ENABLE AND DISABLE TIME(f=1MHz;50%duty cicle) 6/8DIM.mminch MIN.TYP.MAX.MIN.TYP.MAX.A 1.10.433A10.050.100.150.0020.0040.006A20.850.90.950.3350.3540.374b 0.170.270.00670.011c 0.090.200.00350.0079D 12.412.512.60.4080.4920.496E 7.958.18.250.3130.3190.325E1 6.06.1 6.20.2360.2400.244e 0.5BSC 0.0197BSCK 0o 4o 8o 0o 4o 8o L0.500.600.700.0200.0240.028cEbA2AE1D1PIN 1IDENTIFICATIONA1LK eTSSOP48MECHANICAL DATA74ACT162447/874ACT16244Information furnished is believed to be accurate and reliable.However,STMicroelectroni c s assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use.No license is granted by implication or otherwise under any patent or patent rights of STMicroelectroni c s.Specification mentioned in this publication are subject to change without notice.This publication supersedes and replaces all informati o n previously supplied.STMicroelectronics products are not authorized for use as critical components in life support devices or systems withoutexpress written approval of STMicroelectronics.The ST logo is a registered trademark of STMicroelectronics©2000STMicroelectronics–Printed in Italy–All Rights ReservedSTMicroelectronics GROUP OF COMPANIESAustralia-Brazil-China-Finland-France-Germany-Hong Kong-India-Italy-Japan-Malaysia-Malta-MoroccoSingapore-Spain-Sweden-Switzerland-United Kingdom-U.S.A..8/8。

PI74FCT244ATS中文资料

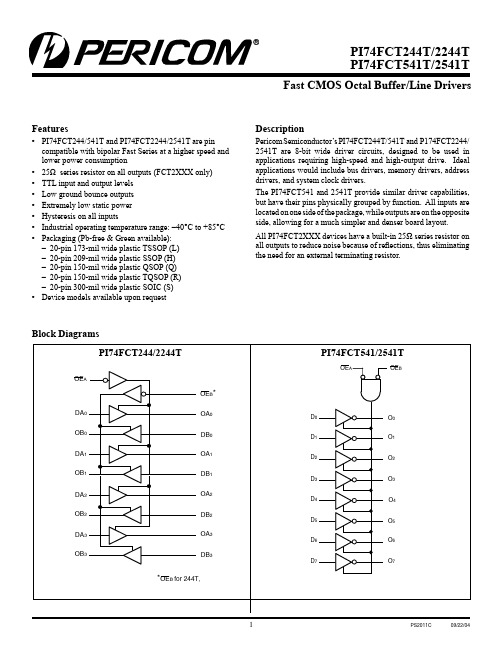

Block DiagramsDescriptionPericom Semiconductor’s PI74FCT244T/541T and P174FCT2244/2541T are 8-bit wide driver circuits, designed to be used in applications requiring high-speed and high-output drive. Ideal applications would include bus drivers, memory drivers, address drivers, and system clock drivers.The PI74FCT541 and 2541T provide similar driver capabilities, but have their pins physically grouped by function. All inputs are located on one side of the package, while outputs are on the opposite side, allowing for a much simpler and denser board layout.All PI74FCT2XXX devices have a built-in 25Ω series resistor on all outputs to reduce noise because of reflections, thus eliminating the need for an external terminating resistor.Features• PI74FCT244/541T and PI74FCT2244/2541T are pin compatible with bipolar Fast Series at a higher speed and lower power consumption• 25Ω series resistor on all outputs (FCT2XXX only)• TTL input and output levels • Low ground bounce outputs • Extremely low static power • Hysteresis on all inputs• Industrial operating temperature range: –40°C to +85°C • Packaging (Pb-free & Green available): – 20-pin 173-mil wide plastic TSSOP (L) – 20-pin 209-mil wide plastic SSOP (H) – 20-pin 150-mil wide plastic QSOP (Q) – 20-pin 150-mil wide plastic TQSOP (R) – 20-pin 300-mil wide plastic SOIC (S)• Device models available upon requestFast CMOS Octal Buffer/Line DriversPI74FCT244T/2244T PI74FCT541T/2541TProduct Pin DescriptionPin Name DescriptionOEA, OEB3-State Output Enable Inputs (Active LOW) OEB(1)3-State Output Enable Input (Active HIGH) Dxx InputsOxx OutputsGND GroundV CC Power Truth TableInputs(1)Outputs(1) OE A OE B OE B(2)D244541 L L H L L L L L H H H H H H L X Z Z Note:1. H = High V oltage Level, X = Don't Care, L = LowV oltage Level, Z = High Impedance2. OE B for 241 only.PI74FCT540/541/2541T Pin ConfigurationPI74FCT241/2241/244/2244T Pin Configuration1 2 3 4 5 6 7 8 9 1020 19 18 17 16 15 14 13 12 11OE A DA0 OB0 DA1 OB1 DA2 OB2 DA3 OB3 GNDVccOE BOA0DB0OA1DB1OA2DB2OA3DB320-PinH20L20P20Q20R20S201234567891020191817161514131211OE AD0D1D2D3D4D5D6D7GNDVccOE BO0*O1*O2*O3*O4*O5*O6*O7*20-PinH20L20P20Q20R20S20Maximum Ratings(Above which the useful life may be impaired. For user guidelines, not tested.)Note:Stresses greater than those listed under MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other con-ditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.DC Electrical Characteristics (Over the Operating Range, TA = –40°C to +85°C, VCC = 5.0V ± 5%)Parameters Description Test Conditions (1)Min.Typ (2)Max.UnitsV OH Output HIGH V oltage V CC = Min., V IN = V IH or V IL I OH = –15.0mA 2.43.0VV OL Output LOW Current V CC = Min., V IN = V IH or V IL I OL = 64mA 0.30.55V OL Output LOW Current V CC = Min., V IN = V IH or V IL I OL = 12mA (25ΩSeries)0.30.50V IH Input HIGH V oltage Guaranteed Logic HIGH Level 2.0V IL Input LOW V oltage Guaranteed Logic LOW Level 0.8I IH Input HIGH Current V CC = Max.V IN = V CC 1µAI IL Input LOW Current V CC = Max.V IN = GND –1I OZH High Impedance V CC = M AX .V OUT = 2.7V 1I OZL Output Current V OUT = 0.5V–1V IK Clamp Diode V oltage V CC = Min., I IN = –18mA –0.7–1.2V I OFF Power Down Disable V CC = GND , V OUT = 4.5V ——100µA I OS Short Circuit Current V CC = Max.(3), V OUT = GND–60–120mA V HInput Hysteresis200Capacitance (T A = 25°C, f = 1 MHz)Parameters (4)DescriptionTest ConditionsTyp.Max.Units C IN Input Capacitance V IN = 0V 610pFC OUTOutput CapacitanceV OUT = 0V812Notes:1. For Max. or Min. conditions, use appropriate value specified under Electrical Characteristics for the applicable device type.2. Typical values are at Vcc = 5.0V , +25°C ambient and maximum loading.3. Not more than one output should be shorted at one time. Duration of the test should not exceed one second.4. This parameter is determined by device characterization but is not production tested.Storage Temperature.............................................................–65°C to +150°C Ambient Temperature with Power Applied.............................-40°C to +85°C Supply V oltage to Ground Potential (Inputs & Vcc Only)......–0.5V to +7.0V Supply V oltage to Ground Potential (Outputs & D/O Only)...–0.5V to +7.0V DC Input V oltage.....................................................................–0.5V to +7.0V DC Output Current................................................................................120mA Power Dissipation....................................................................................0.5WPower Supply CharacteristicsParameters Description Test Conditions(1)Min.Typ(2)Max.UnitsI CC Quiescent PowerSupply Current V CC = Max.V IN = GND or V CC0.1500µAΔI CC Supply Current perInput @ TTL HIGH V CC= Max.V IN= 3.4V(3)0.5 2.5mAI CCD Supply Current perInput per MHz(4)V CC= Max.,Outputs OpenOE A = OE B = GND orOE A = GND, OE B = V CCOne Bit Toggling50% Duty CycleV IN = V CCV IN= GND0.150.25mA/MHzI C Total Power SupplyCurrent(6)V CC= Max.,Outputs Openf I = 10 MH Z50% Duty CycleOE A = OE B = GND orOE A = GND, OE B = V CCOne Bit TogglingV IN = V CCV IN= GND 1.5 3.5(5)mAV IN = 3.4VV IN = GND 1.8 4.5(5)V CC= Max.,Outputs Openf I = 2.5 MH Z50% Duty CycleOE A = OE B = GND orOE A = GND, OE B = V CCEight Bits TogglingV IN = V CCV IN= GND 3.0 6.0(5)V IN = 3.4VV IN = GND 5.014.0(5)Notes:1. For Max. or Min. conditions, use appropriate value specified under Electrical Characteristics for the applicable device.2. Typical values are at Vcc = 5.0V, +25°C ambient.3. Per TTL driven input (V IN= 3.4V); all other inputs at Vcc or GND.4. This parameter is not directly testable, but is derived for use in Total Power Supply Calculations.5. Values for these conditions are examples of the Icc formula. These limits are guaranteed but not tested.6. I C = I QUIESCENT + I INPUTS + I DYNAMICI C = I CC + ΔI CC D H N T + I CCD (f CP/2 + f I N I)I CC = Quiescent CurrentΔI CC = Power Supply Current for a TTL High Input (V IN= 3.4V)D H= Duty Cycle for TTL Inputs HighN T= Number of TTL Inputs at D HI CCD= Dynamic Current Caused by an Input Transition Pair (HLH or LHL)f CP = Clock Frequency for Register Devices (Zero for Non-Register Devices)f I = Input FrequencyN I= Number of Inputs at f IAll currents are in milliamps and all frequencies are in megahertz.PI74FCT244/2244T Switching Characteristics over Operating RangeParam-eters Description Condi-tions(1)244T/2244T244AT/2244AT244CT/2244CT244DTUnits .Min Max Min Max Min Max Min Maxt PLHt PHL Propagation DelayC L = 50p F 1.5 6.5 1.5 4.8 1.5 4.1 1.5 3.6nst PZH t PZL Output Enable TimeOE X to O N 1.58.0 1.5 6.2 1.5 5.8 1.5 4.8nst PHZ t PLZ Output DisableTime(3)OE X to O N1.57.0 1.5 5.6 1.5 5.2 1.5 4.0nsNotes:1. See test circuit and wave forms.2. Minimum limits are guaranteed but not tested on Propagation Delays.3. This parameter is guaranteed but not production tested.PI74FCT541/2541T Switching Characteristics over Operating RangeParameters Description Conditions(1)541T/2541T541AT/2541AT541CT/2541CT541DTUnits .Min Max Min Max Min Max Min Maxt PLH t PHL Propagation DelayD N to O NC L = 50p FR L = 500Ω1.5 6.0 1.5 4.8 1.5 4.1 1.5 3.8nst PZH t PZL Output Enable TimeOE X to O N 1.59.5 1.5 6.2 1.5 5.8 1.5 5.2nst PHZ t PLZ Output DisableTime(3)OE X to O N1.5 6.5 1.5 5.6 1.5 5.2 1.5 5.2nsNotes:1. See test circuit and wave forms.2. Minimum limits are guaranteed but not tested on Propagation Delays.3. This parameter is guaranteed but not production tested.Ordering Information: PI74FCT244TOrdering Code Package Code Speed Grade Package DescriptionPI74FCT244TH H Blank20-pin 209-mil wide plastic SSOPPI74FCT244TL L Blank20-pin 173-mil wide plastic TSSOPPI74FCT244TLE L Blank Pb-free & Green, 20-pin 173-mil wide plastic TSSOP PI74FCT244TQ Q Blank20-pin 150-mil wide plastic QSOPPI74FCT244TS S Blank20-pin 300-mil wide plastic SOICPI74FCT244ATH H A20-pin 209-mil wide plastic SSOPPI74FCT244ATL L A20-pin 173-mil wide plastic TSSOPPI74FCT244ATQ Q A20-pin 150-mil wide plastic QSOPPI74FCT244ATS S A20-pin 300-mil wide plastic SOICPI74FCT244ATSE S A Pb-free & Green, 20-pin 300-mil wide plastic SOIC PI74FCT244CTH H C20-pin 209-mil wide plastic SSOPPI74FCT244CTL L C20-pin 173-mil wide plastic TSSOPPI74FCT244CTQ Q C20-pin 150-mil wide plastic QSOPPI74FCT244CTS S C20-pin 300-mil wide plastic SOICPI74FCT244DTQ Q D20-pin 150-mil wide plastic QSOPPI74FCT244DTS S D20-pin 300-mil wide plastic SOICPI74FCT244DTSE S D Pb-free & Green, 20-pin 300-mil wide plastic SOIC Ordering Information: PI74FCT2244TOrdering Code Package Code Speed Grade Package DescriptionPI74FCT2244TQ Q Blank20-pin 150 mil wide plastic QSOPPI74FCT2244TS S Blank20-pin 300 mil wide plastic SOICPI74FCT2244ATH H A20-pin 209 mil wide plastic SSOPPI74FCT2244ATL L A20-pin 173 mil wide plastic TSSOPPI74FCT2244ATQ Q A20-pin 150 mil wide plastic QSOPPI74FCT2244ATS S A20-pin 300 mil wide plastic SOICPI74FCT2244CTL L C20-pin 173 mil wide plastic TSSOPPI74FCT2244CTQ Q C20-pin 150 mil wide plastic QSOPPI74FCT2244CTS S C20-pin 300 mil wide plastic SOICPericom Semiconductor Corporation • 1-800-435-2336 • Ordering Information: PI74FCT2541TOrdering Code Package CodeSpeed GradePackage DescriptionPI74FCT2541TL L Blank 20-pin 173 mil wide plastic TSSOP PI74FCT2541TQ Q Blank 20-pin 150 mil wide plastic QSOP PI74FCT2541TS S Blank 20-pin 300 mil wide plastic SOIC PI74FCT2541ATH H A 20-pin 209 mil wide plastic SSOP PI74FCT2541ATL L A 20-pin 173 mil wide plastic TSSOP PI74FCT2541ATQ Q A 20-pin 150 mil wide plastic QSOP PI74FCT2541ATS S A 20-pin 300 mil wide plastic SOIC PI74FCT2541CTH H C 20-pin 209 mil wide plastic SSOP PI74FCT2541CTLLV20-pin 173 mil wide plastic TSSOPNotes:1. Thermal characteristics can be found on the company web site at /packaging/Ordering Information: PI74FCT541TOrdering Code Package CodeSpeed GradePackage DescriptionPI74FCT541TQ Q Blank 20-pin 150-mil wide plastic QSOPPI74FCT541TQE Q Blank Pb-free & Green, 20-pin 150-mil wide plastic QSOP PI74FCT541TS S Blank 20-pin 300-mil wide plastic SOIC PI74FCT541ATL L A 20-pin 173-mil wide plastic TSSOP PI74FCT541ATQ Q A 20-pin 150-mil wide plastic QSOP PI74FCT541ATS S A 20-pin 300-mil wide plastic SOICPI74FCT541ATSE S A Pb-free & Green, 20-pin 300-mil wide plastic SOIC PI74FCT541ATH H A 20-pin 209-mil wide plastic SSOP PI74FCT541CTL L C 20-pin 173-mil wide plastic TSSOP PI74FCT541CTQ Q C 20-pin 150-mil wide plastic QSOP PI74FCT541CTS S C 20-pin 300-mil wide plastic SOIC PI74FCT541CTHHC20-pin 209-mil wide plastic SSOP。

常用74系列标准数字电路的中文名称资料

常用74系列标准数字电路的中文名称资料收藏常用74系列标准数字电路的中文名称资料器件代号器件名称74 74LS 74HC00 四2输入端与非门√√√01 四2输入端与非门(OC) √√02 四2输入端或非门√√√03 四2输入端与非门(OC) √√04 六反相器√√√05 六反相器(OC) √√06 六高压输出反相器(OC,30V) √√07 六高压输出缓冲,驱动器(OC,30V) √√√08 四2输入端与门√√√09 四2输入端与门(OC) √√√10 三3输入端与非门√√√11 三3输入端与门√√12 三3输入端与非门(OC) √√√13 双4输入端与非门√√√14 六反相器√√√15 三3输入端与门(OC) √√16 六高压输出反相器(OC,15V) √17 六高压输出缓冲,驱动器(OC,15V) √20 双4输入端与非门√√√21 双4输入端与门√√√22 双4输入端与非门(OC) √√25 双4输入端或非门(有选通端) √√√26 四2输入端高压输出与非缓冲器√√√27 三3输入端或非门√√√28 四2输入端或非缓冲器√√√器件代号器件名称74 74LS 74HC30 8输入端与非门√√√32 四2输入端或门√√√33 四2输入端或非缓冲器(OC) √√37 四2输入端与非缓冲器√√38 四2输入端与非缓冲器(OC) √√40 双4输入端与非缓冲器√√√42 4线-10线译码器(BCD输入) √√43 4线-10线译码器(余3码输入) √44 4线-10线译码器(余3葛莱码输入) √48 4线-7段译码器√49 4线-7段译码器√50 双2路2-2输入与或非门√√√51 2路3-3输入,2路2-2输入与或非门√√√52 4路2-3-2-2输入与或门√53 4路2-2-2-2输入与或非门√54 4路2-3-3-2输入与或非门√√55 2路4-4输入与或非门√60 双4输入与扩展器√√61 三3输入与扩展器√62 4路2-3-3-2输入与或扩展器√64 4路4-2-3-2输入与或非门√65 4路4-2-3-2输入与或非门(OC) √70 与门输入J-K触发器√71 与或门输入J-K触发器√72 与门输入J-K触发器√器件代号器件名称74 74LS 74HC74 双上升沿D型触发器√√78 双D型触发器√√85 四位数值比较器√86 四2输入端异或门√√√87 4位二进制原码/反码√95 4位移位寄存器√101 与或门输入J-K触发器√102 与门输入J-K触发器√107 双主-从J-K触发器√108 双主-从J-K触发器√74F74是高速的TTL芯片和74HC一样就是速度高109 双主-从J-K触发器√110 与门输入J-K触发器√111 双主-从J-K触发器√√112 双下降沿J-K触发器√113 双下降沿J-K触发器√114 双下降沿J-K触发器√116 双4位锁存器√120 双脉冲同步驱动器√121 单稳态触发器√√√122 可重触发单稳态触发器√√√123 可重触发双稳态触发器√√√125 四总线缓冲器√√√126 四总线缓冲器√√√128 四2输入端或非线驱动器√√√132 四2输入端与非门√√√d触发器芯片有:74HC74 74LS90 双D触发器74LS7474LS364八D触发器(三态)7474、74 H74、74F74、74ALS74、74L74、74LS74A、74S74、74HC73、74C74双D型正沿触发器(带预置和清除端)74174、74LS174、74F174、74ALS174、74S174、74HC174、74C174六D型触发器(带清除端)74175、74LS175、74F175、74ALS175、74S175、74HC175、74C175 四D型触发器(带清除端)74273、74LS273、74S273、74F273、74ALS273、74HC273 八D型触发器(带清除端)74LS364八D触发器(三态)74LS377、74F377、74S3777八D 触发器74LS378、74F378、74S378、74HC378六D 触发器74LS379、74F379、74S379、74HC379八D 触发器。

74FCT163H244CPVCT资料

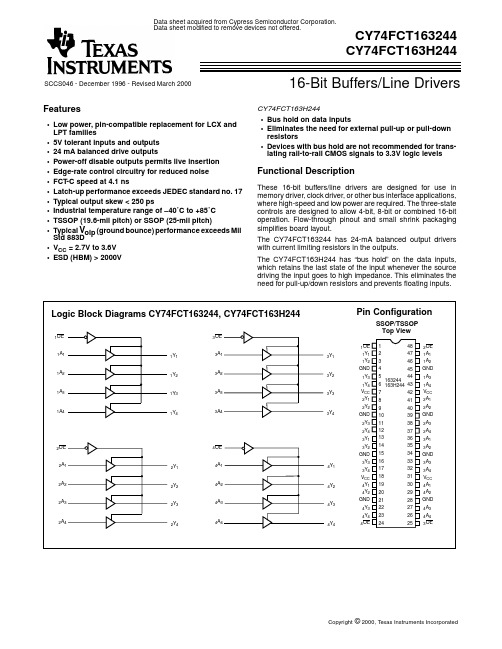

16-Bit Buffers/Line DriversCY74FCT163244CY74FCT163H244SCCS046 - December 1996 - Revised March 2000Data sheet acquired from Cypress Semiconductor Corporation.Data sheet modified to remove devices not offered.Features•Low power, pin-compatible replacement for LCX and LPT families•5V tolerant inputs and outputs •24 mA balanced drive outputs•Power-off disable outputs permits live insertion •Edge-rate control circuitry for reduced noise •FCT-C speed at 4.1 ns•Latch-up performance exceeds JEDEC standard no.17•Typical output skew < 250 ps•Industrial temperature range of –40˚C to +85˚C •TSSOP (19.6-mil pitch) or SSOP (25-mil pitch)•Typical V olp (ground bounce)performance exceeds Mil Std 883D•V CC = 2.7V to 3.6V •ESD (HBM) > 2000VCY74FCT163H244•Bus hold on data inputs•Eliminates the need for external pull-up or pull-down resistors•Devices with bus hold are not recommended for trans-lating rail-to-rail CMOS signals to 3.3V logic levelsFunctional DescriptionThese 16-bit buffers/line drivers are designed for use in memory driver,clock driver,or other bus interface applications,where high-speed and low power are required.The three-state controls are designed to allow 4-bit,8-bit or combined 16-bit operation.Flow-through pinout and small shrink packaging simplifies board layout.The CY74FCT163244has 24-mA balanced output drivers with current limiting resistors in the outputs.The CY74FCT163H244has “bus hold”on the data inputs,which retains the last state of the input whenever the source driving the input goes to high impedance.This eliminates the need for pull-up/down resistors and prevents floating inputs.GNDLogic Block Diagrams CY74FCT163244, CY74FCT163H244Pin Configuration12345678910111233323130292526272836351OE34SSOP/TSSOP Top View1Y 11Y 21Y 31Y 41314151617181920212223244544434241373839404847461A 11A 21A 31A 41OE2Y 12Y 22Y 32Y 42A 12A 22A 32A 42OE 1Y 11Y 21Y 31Y 41A 11A 21A 31A 42OE GNDGNDV CC 2Y 32Y 42Y 12Y 22A 12A 22A 32A 4V CC GNDGND3Y 33Y 43Y 13Y 23A 13A 23A 33A 4GNDGNDV CC 4Y 34Y 44Y 14Y 24A 14A 24A 34A 4V CC GND4OE3OE3Y 13Y 23Y 33Y 43A 13A 23A 33A 43OE4Y 14Y 24Y 34Y 44A 14A 24A 34A 44OE163244163H244Maximum Ratings [3,4](Above which the useful life may be impaired.For user guide-lines, not tested.)Storage T emperature................................. –55°C to +125°C Ambient T emperature withPower Applied............................................ –55°C to +125°C Supply Voltage Range.....................................0.5V to +4.6VDC Input Voltage ...........................................–0.5V to +7.0V DC Output Voltage.........................................–0.5V to +7.0V DC Output Current(Maximum Sink Current/Pin)........................–60 to +120 mA Power Dissipation..........................................................1.0WPin DescriptionName DescriptionOE Three-State Output Enable Inputs (Active LOW)A Data Inputs [1]YThree-State OutputsFunction Table [2]InputsOutputsOE A Y L L L L H H HXZOperating RangeRange Ambient Temperature V CC Industrial–40°C to +85°C2.7V to3.6VElectrical Characteristics for Non Bus Hold Devices Over the Operating Range V CC =2.7V to 3.6VParameter DescriptionTest ConditionsMin.Typ.[5]Max.Unit V IH Input HIGH Voltage All Inputs2.05.5V V IL Input LOW Voltage 0.8V V H Input Hysteresis [6]100mV V IK Input Clamp Diode Voltage V CC =Min., I IN =–18 mA –0.7– 1.2V I IH Input HIGH Current V CC =Max., V I =5.5±1µA I IL Input LOW CurrentV CC =Max., V I =GND ±1µA I OZH High Impedance Output Current (Three-State Output pins)V CC =Max., V OUT =5.5V ±1µA I OZL High Impedance Output Current (Three-State Output pins)V CC =Max., V OUT =GND ±1µA I OS Short Circuit Current [7]V CC =Max., V OUT =GND –60–135–240mA I OFF Power-Off DisableV CC =0V , V OUT ≤4.5V ±100µA I CC Quiescent Power Supply Current V IN ≤0.2V ,V IN >V CC –0.2V V CC =Max.0.110µA ∆I CCQuiescent Power Supply Current (TTL inputs HIGH)V IN =V CC –0.6V [8]V CC =Max.2.030µANotes:1.On the CY74FCT163H244, these pins have “bus hold.”2.H = HIGH Voltage Level. L = LOW Voltage Level. X = Don’t Care. Z = High Impedance.3.Operation beyond the limits set forth may impair the useful life of the device. Unless otherwise noted, these limits are over the operating free-air temperaturerange.4.With the exception of inputs with bus hold, unused inputs must always be connected to an appropriate logic voltage level, preferably either V CC or ground.5.Typical values are at V CC =3.3V , T A = +25˚C ambient.6.This parameter is specified but not tested.7.Not more than one output should be shorted at a time.Duration of short should not exceed one second.The use of high-speed test apparatus and/or sampleand hold techniques are preferable in order to minimize internal chip heating and more accurately reflect operational values.Otherwise prolonged shorting of a high output may raise the chip temperature well above normal and thereby cause invalid readings in other parametric tests. In any sequence of parameter tests, I OS tests should be performed last.8.Per TTL driven input; all other inputs at V CC or GND.Electrical Characteristics For Bus Hold Devices Over the Operating Range V CC=2.7V to 3.6VParameter Description Test Conditions Min.Typ.[5]Max.Unit V IH Input HIGH Voltage All Inputs 2.0V CC V V IL Input LOW Voltage0.8V V H Input Hysteresis[6]100mV V IK Input Clamp Diode Voltage V CC=Min., I IN=–18 mA–0.7–1.2V I IH Input HIGH Current V CC=Max., V I=V CC±100µA I IL Input LOW Current±100µAI BBH I BBL Bus Hold Sustain Current on Bus Hold Input[9]V CC=Min.V I=2.0V–50µAV I=0.8V+50µAI BHHO I BHLO Bus Hold Overdrive Current on Bus Hold In-put[9]V CC=Max., V I=1.5V±500µAI OZH High Impedance Output Current(Three-State Output pins)V CC=Max., V OUT=V CC±1µAI OZL High Impedance Output Current(Three-State Output pins)V CC=Max., V OUT=GND±1µA I OS Short Circuit Current[7]V CC=Max., V OUT=GND–60–135–240mA I OFF Power-Off Disable V CC=0V, V OUT≤4.5V±100µA I CC Quiescent Power Supply Current V IN≤0.2V,V IN>V CC–0.2VV CC=Max.+40µA∆ICC Quiescent Power supply Current(TTL inputs HIGH)V IN=V CC–0.6V[8]VCC=Max.+350µAElectrical Characteristics For Balanced Drive Devices Over the Operating Range V CC=2.7V to 3.6V Parameter Description Test Conditions Min.Typ.[5]Max.Unit I ODL Output LOW Dynamic Current[7]V CC=3.3V, V IN=V IHor V IL, V OUT=1.5V45180mAI ODH Output HIGH Dynamic Current[7]V CC=3.3V, V IN=V IHor V IL, V OUT=1.5V–45–180mA V OH Output HIGH Voltage V CC=Min., I OH= –0.1 mA V CC–0.2VV CC=3.0V, I OH= –8 mA 2.4[10] 3.0VV CC=3.0V, I OH= –24 mA 2.0 3.0V V OL Output LOW Voltage V CC=Min., I OL= 0.1mA0.2VV CC=Min., I OL= 24 mA0.30.55Notes:9.Pins with bus hold are described in Pin Description.10.V OH = V CC – 0.6V at rated current.Capacitance[6](T A = +25˚C, f = 1.0 MHz)Parameter Description Test Conditions Typ.[5]Max.Unit C IN Input Capacitance V IN = 0V 4.5 6.0pF C OUT Output Capacitance V OUT = 0V 5.58.0pFPower Supply CharacteristicsParameter Description Test Conditions Typ.[5]Max.UnitI CCD Dynamic Power SupplyCurrent[10]V CC=Max.,One Input Toggling,50% Duty Cycle,Outputs Open,OE=GNDV IN=V CC orV IN=GND5075µA/MHzI C Total Power SupplyCurrent[11]V CC=Max., f1=10 MHz, 50%Duty Cycle,Outputs Open,OneBit T oggling,OE=GNDV IN=V CC orV IN=GND0.50.8mAV IN=V CC–0.6V orV IN=GND0.50.8mAV CC=Max., f1=2.5 MHz, 50%Duty Cycle, Outputs Open, Six-teen Bits Toggling,OE=GNDV IN=V CC orV IN=GND2.03.0[12]mAV IN=V CC–0.6V orV IN=GND2.03.3[12]mANotes:11.This parameter is not directly testable, but is derived for use in Total Power Supply calculations.12.I C=I QUIESCENT + I INPUTS+ I DYNAMICI C=I CC+∆I CC D H N T+I CCD(f0/2 + f1N1)I CC=Quiescent Current with CMOS input levels∆I CC=Power Supply Current for a TTL HIGH input (V IN=3.4V)D H=Duty Cycle for TTL inputs HIGHN T=Number of TTL inputs at D HI CCD=Dynamic Current caused by an input transition pair(HLH or LHL)f0=Clock frequency for registered devices, otherwise zerof1=Input signal frequencyN1=Number of inputs changing at f1All currents are in milliamps and all frequencies are in megahertz.13.Values for these conditions are examples of the I CC formula. These limits are specified but not tested.Switching Characteristics Over the Operating Range V CC =3.0V to 3.6V [14,15]Parameter DescriptionCY74FCT163244A CY74FCT163H244ACY74FCT163244C CY74FCT163H244C Min.Max.Min.Max.Unit Fig. No.[16]t PLH t PHL Propagation Delay Data to Output1.5 4.8 1.5 4.1ns 1, 3t PZH t PZL Output Enable Time 1.5 6.2 1.5 5.8ns 1, 7, 8t PHZ t PLZ Output Disable Time 1.55.6 1.55.2ns 1, 7, 8t SK(O)Output Skew [17]0.50.5ns—Notes:14.Minimum limits are specified but not tested on Propagation Delays.15.For V CC =2.7, propagation delay, output enable and output disable times should be degraded by 20%.16.See “Parameter Measurement Information” in the General Information section.17.Skew between any two outputs of the same package switching in the same direction. This parameter is ensured by design.Ordering Information CY74FCT163244Speed (ns)Ordering CodePackage Name Package TypeOperating Range 4.1CY74FCT163244CPACT Z4848-Lead (240-Mil) TSSOP IndustrialCY74FCT163244CPVC/PVCT O4848-Lead (300-Mil) SSOP 4.8CY74FCT163244AP ACT Z4848-Lead (240-Mil) TSSOP IndustrialCY74FCT163244APVC/PVCTO4848-Lead (300-Mil) SSOPOrdering Information CY74FCT163H244Speed (ns)Ordering CodePackage Name Package TypeOperating Range 4.174FCT163H244CPACT Z4848-Lead (240-Mil) TSSOP IndustrialCY74FCT163H244CPVC O4848-Lead (300-Mil) SSOP 74FCT163H244CPVCTO4848-Lead (300-Mil) SSOPPackage Diagrams48-Lead Shrunk Small Outline Package O4848-Lead Thin Shrunk Small Outline Package Z48IMPORTANT NOTICETexas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI’s standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE (“CRITICAL APPLICATIONS”). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER’S RISK.In order to minimize risks associated with the customer’s applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI’s publication of information regarding any third party’s products or services does not constitute TI’s approval, warranty or endorsement thereof.Copyright © 2000, Texas Instruments Incorporated。

电子行业74系列芯片中文资料超级全

电子行业74系列芯片中文资料超级全CD4506双二组2输入可扩展或非门CD4508双4位锁存D型触发器CD4510可预置BCD码加/减计数器CD4511BCD锁存,7段译码,驱动器CD4512八路数据选择器CD4513BCD锁存,7段译码,驱动器(消隐)CD45144位锁存,4线-16线译码器CD45154位锁存,4线-16线译码器CD4516可预置4位二进制加/减计数器CD4517双64位静态移位寄存器CD4518双BCD同步加计数器CD4519四位与或选择器CD4520双4位二进制同步加计数器CD452124级分频器CD4522可预置BCD同步1/N计数器CD4526可预置4位二进制同步1/N计数器CD4527BCD比例乘法器CD4528双单稳态触发器CD4529双四路/单八路模拟开关CD4530双5输入端优势逻辑门CD453112位奇偶校验器CD45328位优先编码器CD4536可编程定时器CD4538精密双单稳CD4539双四路数据选择器CD4541可编程序振荡/计时器CD4543BCD七段锁存译码,驱动器CD4544BCD七段锁存译码,驱动器CD4547BCD七段译码/大电流驱动器CD4549函数近似寄存器CD4551四2通道模拟开关CD4553三位BCD计数器CD4555双二进制四选一译码器/分离器CD4556双二进制四选一译码器/分离器CD4558BCD八段译码器CD4560"N"BCD加法器CD4561"9"求补器CD4573四可编程运算放大器CD4574四可编程电压比较器CD4575双可编程运放/比较器CD4583双施密特触发器CD4584六施密特触发器CD45854位数值比较器CD45998位可寻址锁存器。

74VHCT244AMX中文资料

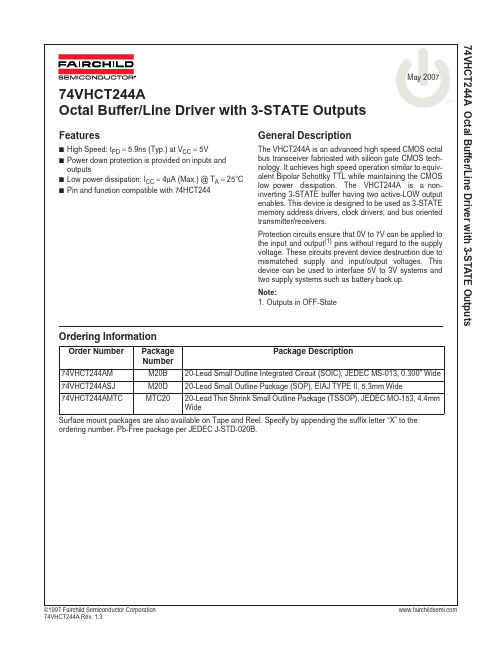

元器件交易网74VHCT244A Octal Buffer/Line Driver with 3-STATE Outputs74VHCT244A Octal Buffer/Line Driver with 3-STATE OutputsConnection DiagramPin DescriptionLogic SymbolTruth TablesH = HIGH Voltage Level L = LOW Voltage Level Z = High ImpedancePin NamesDescriptionOE 1 , OE 2 3-STATE Output Enable InputsI 0 –I 7 InputsO 0 –O 73-STATE OutputsInputs Outputs(Pins 12, 14, 16, 18)OE 1I nL L L L H H HXZInputs Outputs (Pins 3, 5, 7, 9)OE 2I nL L L L H H HXZ元器件交易网74VHCT244A Octal Buffer/Line Driver with 3-STATE OutputsAbsolute Maximum RatingsStresses exceeding the absolute maximum ratings may damage the device. The device may not function or beoperable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.Recommended Operating Conditions (5)The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not recommend exceeding them or designing to absolute maximum ratings.Notes:2.HIGH or LOW state. I OUT absolute maximum rating must be observed.3.When outputs are in OFF-STATE or when V CC = 0V.4.V OUT < GND, V OUT > V CC (Outputs Active).5.Unused inputs must be held HIGH or LOW. They may not float.Symbol ParameterRatingV CC Supply Voltage –0.5V to +7.0V V IN DC Input Voltage –0.5V to +7.0V V OUTDC Output Voltage Note 2 Note 3–0.5V to V CC + 0.5V–0.5V to +7.0VI IK Input Diode Current –20mA I OK Output Diode Current (4) ±20mA I OUT DC Output Current ±25mA I CC DC V CC /GND Current ±75mAT STG Storage Temperature–65°C to +150°CT LLead Temperature (Soldering, 10 seconds)260°CSymbol ParameterRatingV CC Supply Voltage 4.5V to +5.5V V IN Input Voltage 0V to +5.5V V OUTOutput Voltage Note 2 Note 30V to V CC 0V to +5.5V T OPR Operating Temperature–40°C to +85°C t r , t fInput Rise and Fall Time, V CC =5.0V ± 0.5V0ns/V ~ 20ns/V元器件交易网74VHCT244A Octal Buffer/Line Driver with 3-STATE OutputsDC Electrical CharacteristicsNoise CharacteristicsNote:6.Parameter guaranteed by design.SymbolParameterV CC (V)Conditions T A = 25°CT A = –40°C to +85°C UnitsMin.Typ.Max.Min.Max. V IH HIGH Level Input Voltage4.5 2.0 2.0V5.5 2.02.0V IL LOW Level Input Voltage4.50.80.8V5.50.80.8V OH HIGH Level Output Voltage4.5V IN = V IH or V ILI OH = –50µA 4.40 4.50 4.40V I OH = –8mA 3.943.80V OL LOW Level Output Voltage4.5V IN = V IH or V ILI OL = 50µA 0.00.10.1V I OL = 8mA 0.360.44I OZ 3-STATE Output OFF-STATE Current 5.5V IN = V IH or V IL , V OUT = V CC or GND ±0.25±2.5µA I IN Input Leakage Current0–5.5V IN = 5.5V or GND ±0.1±1.0µA I CC Quiescent Supply Current5.5V IN = V CC or GND 4.040.0µA I CCT Maximum I CC /Input 5.5V IN = 3.4V , Other Input = V CC or GND 1.35 1.50mA I OFFOutput Leakage Current (Power Down State)0.0V OUT = 5.5V0.55.0µA SymbolParameterV CC (V)ConditionsT A = 25°CUnitsTyp.LimitsV OLP (6)Quiet Output Maximum Dynamic V OL5.0C L = 50pF 0.9 1.1V V OLV (6)Quiet Output Minimum Dynamic V OL5.0C L = 50pF –0.9–1.1V V IHD (6)Minimum HIGH Level Dynamic Input Voltage5.0C L = 50pF 2.0V V ILD (6)Maximum HIGH Level Dynamic Input Voltage5.0C L = 50pF0.8V元器件交易网74VHCT244A Octal Buffer/Line Driver with 3-STATE OutputsAC Electrical CharacteristicsNotes:7.Parameter guaranteed by design. t OSLH = |t PLH max – t PLH min |; t OSHL = |t PHL max – t PHL min |8.C PD is defined as the value of the internal equivalent capacitance which is calculated from the operating current consumption without load. Average operating current can be obtained by the equation:I CC (Opr.) = C PD • V CC • f IN + I CC / 8 (per F/F). The total C PD when n pcs. of the Octal D Flip-Flop operates can be calculated by the equation: C PD (total) = 20 + 12nSymbolParameterV CC (V)ConditionsT A = 25°CT A = –40°C to +85°CUnitsMin.Typ.Max.Min.Max.t PLH , t PHL Propagation Delay Time5.0 ± 0.5C L = 15pF 5.47.4 1.08.5nsC L = 50pF 5.98.41.09.5t PZL , t PZH 3-STATE Output Enable Time 5.0 ± 0.5R L = 1k ΩC L = 15pF 7.710.4 1.012.5ns C L = 50pF 8.211.4 1.013.5t PLZ , t PHZ3-STATE Output Disable Time5.0 ± 0.5R L = 1k ΩC L = 50pF8.811.4 1.013.0ns t OSLH , t OSHL Output to OutputSkew5.0 ± 0.5(7)1.01.0ns C IN Input Capacitance V CC = Open 41010pF C OUT Output Capacitance V CC = 5.0V9pF C PDPower Dissipation Capacitance(8)18pFFigure 1. 20-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300" WidePackage Number M20B74VHCT244A Octal Buffer/Line Driver with 3-STATE Outputs The™TinyBoost。

PI74FCT162245ATAE,PI74FCT162245CTVE,PI74FCT162245TVE,PI74FCT16245ATAE, 规格书,Datasheet 资料

45

GND

44

1A2

43

1A3

42

VCC

41

1A4

40

1A5

39 GND

38

1A6

37

1A7

36

2A0

35

2A1

34 GND

33

2A2

32

2A3

31

VCC

30

2A4

29

2A5

28 GND

27

2A6

26

2A7

25

2OE

Truth Table

Inputs(1)

XOE

XDIR

L

L

L

H

H

X

Outputs(1)

Units V

µA

V mA mV

PI74FCT16245T Output Drive Characteristics (Over the Operating Range)

Parameters

Description

Test Conditions(1)

IOH = –3.0mA

VOH

Output HIGH Voltage VCC = Min., VIN = VIH or VIL IOH = –15.0mA

Block Diagram

1DIR

1A0 1A1 1A2 1A3 1A4 1A5 1A6 1A7

1OE 1B0 1B1 1B2 1B3 1B4 1B5 1B6 1B7

2DIR

2A0 2A1 2A2 2A3 2A4 2A5 2A6 2A7

2OE 2B0 2B1 2B2 2B3 2B4 2B5 2B6 2B7

Parameters

74act244scx手册解读

74act244scx手册解读74ACT244SCX是一款集成逻辑芯片,属于TTL(晶体管-晶体管逻辑)系列。

本手册将对其进行详细解读,包括芯片的功能特性、引脚功能、电气特性及应用示例等方面。

首先,让我们来了解一下74ACT244SCX芯片的功能特性。

该芯片是一个具有8个双向缓冲器的三态缓冲器,用于将一个8位数据线的逻辑电平转换为另一个8位数据线的逻辑电平。

这意味着它可以完成数据信号的转发,适用于数码信号的放大、隔离和解耦等应用。

此外,芯片还具有高噪声抵抗能力和可逆的数据传输功能。

接下来,我们来了解一下74ACT244SCX芯片的引脚功能。

该芯片共有20个引脚,包括8个输出端口(Y1-Y8)、8个输入端口(A1-A8)和一个使能端口(G)。

输入端口用于接收输入信号,输出端口用于输出经过处理后的信号,而使能端口用于控制芯片的工作状态。

在三态缓冲器(Tri-State Buffer)的应用中,使能端口(G)非常重要,它可以使输出端口(Y1-Y8)高阻抗(高阻抗状态)。

我们再来了解一下74ACT244SCX芯片的电气特性。

该芯片具有广泛的工作电压范围,可以在2V至6V的电压下正常工作。

其输入电压范围为0V至Vcc,输出电压范围为0V至Vcc,高电平输入电压范围为0.7Vcc至Vcc,低电平输入电压范围为0V至0.3Vcc。

另外,该芯片具有高速操作能力,最大时钟频率可达100MHz,非常适合高速数据传输的应用。

最后,我们来看一些74ACT244SCX芯片的应用示例。

这款芯片广泛应用于各种数据信号传输和处理电路中。

常见的应用场景包括数据总线驱动、数据信号放大、数据隔离、数据解耦等。

此外,由于其高速操作能力和可靠性,还可应用于工业领域的自动化控制系统和通信设备等。

综上所述,74ACT244SCX是一款集成逻辑芯片,具有8个双向缓冲器的三态缓冲器功能。

其引脚功能包括8个输入端口、8个输出端口和1个使能端口。

该芯片具有高噪声抵抗能力、可逆的数据传输功能和广泛的工作电压范围。

74系列功能大全(中文)

74系列功能大全(中文)74、74HC、74LS系列芯片资料,从网上下的,集合了一下系列电平典型传输延迟ns 最大驱动电流(-Ioh/Lol)mAAHC CMOS 8.5 -8/8AHCT COMS/TTL 8.5 -8/8HC COMS 25 -8/8HCT COMS/TTL 25 -8/8ACT COMS/TTL 10 -24/24F TTL 6.5 -15/64ALS TTL 10 -15/64LS TTL 18 -15/24注:同型号的74系列、74HC系列、74LS系列芯片,逻辑功能上是一样的。

74LSxx的使用说明如果找不到的话,可参阅74xx或74HCxx的使用说明。

有些资料里包含了几种芯片,如74HC161资料里包含了74HC160、74HC161、74HC162、74HC163四种芯片的资料。

找不到某种芯片的资料时,可试着查看一下临近型号的芯片资料。