74LVT245MTCX中文资料

MC74LCX245DWR2中文资料

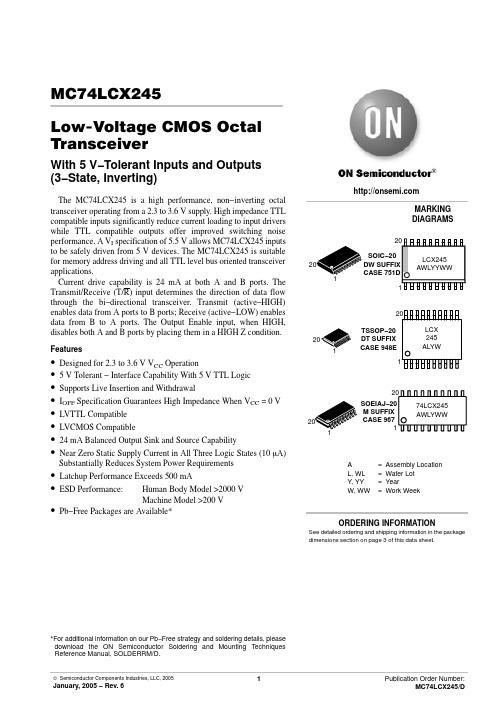

MC74LCX245Low−Voltage CMOS Octal TransceiverWith 5 V−Tolerant Inputs and Outputs (3−State, Inverting)The MC74LCX245 is a high performance, non−inverting octal transceiver operating from a 2.3 to 3.6 V supply. High impedance TTL compatible inputs significantly reduce current loading to input drivers while TTL compatible outputs offer improved switching noise performance. A V I specification of 5.5 V allows MC74LCX245 inputs to be safely driven from 5 V devices. The MC74LCX245 is suitable for memory address driving and all TTL level bus oriented transceiver applications.Current drive capability is 24 mA at both A and B ports. The Transmit/Receive (T/R) input determines the direction of data flow through the bi−directional transceiver. Transmit (active−HIGH) enables data from A ports to B ports; Receive (active−LOW) enables data from B to A ports. The Output Enable input, when HIGH, disables both A and B ports by placing them in a HIGH Z condition. Features•Designed for 2.3 to 3.6 V V CC Operation•5 V Tolerant − Interface Capability With 5 V TTL Logic •Supports Live Insertion and Withdrawal•I OFF Specification Guarantees High Impedance When V CC = 0 V •LVTTL Compatible•LVCMOS Compatible•24 mA Balanced Output Sink and Source Capability•Near Zero Static Supply Current in All Three Logic States (10 m A) Substantially Reduces System Power Requirements •Latchup Performance Exceeds 500 mA•ESD Performance:Human Body Model >2000 VMachine Model >200 V•Pb−Free Packages are Available**For additional information on our Pb−Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.See detailed ordering and shipping information in the package dimensions section on page 3 of this data sheet.ORDERING INFORMATIONB0OE 19T/R 1A0B1A1B2A2B3A3B4A4B5A5B6A6B7A7Figure 1. Pinout (Top View)192018171615142134567V CC 1381291110OE B0B1B2B3B4B5B6B7T/RA0A1A2A3A4A5A6A7GNDH = High Voltage Level L = Low Voltage Level Z = High Impedance StateX = High or Low Voltage Level and Transitions are Acceptable For I CC reasons, Do Not Float InputsFigure 2. Logic DiagramMAXIMUM RATINGSvalues (not normal operating conditions) and are not valid simultaneously. If these limits are exceeded, device functional operation is not implied, damage may occur and reliability may be affected.1.I O absolute maximum rating must be observed.RECOMMENDED OPERATING CONDITIONSORDERING INFORMATIONSpecifications Brochure, BRD8011/D.*This package is inherently Pb−Free.DC ELECTRICAL CHARACTERISTICSIAC CHARACTERISTICS t R = t F = 2.5 ns; R L = 500 WThe specification applies to any outputs switching in the same direction, either HIGH−to−LOW (t OSHL) or LOW−to−HIGH (t OSLH); parameter guaranteed by design.DYNAMIC SWITCHING CHARACTERISTICSmeasured in the LOW state.CAPACITIVE CHARACTERISTICSWAVEFORM 1 − PROPAGATION DELAYS t R = t F = 2.5 ns, 10% to 90%; f = 1 MHz; t W = 500 ns V CC0 VV OHV OLAn, BnWAVEFORM 2 − OUTPUT ENABLE AND DISABLE TIMESt R = t F = 2.5 ns, 10% to 90%; f = 1 MHz; t W = 500 ns0 V Figure 3. AC WaveformsV OH V HZV OLV CCV LZ Symbol V CC3.3 V ±0.3 V2.7 V 2.5 V ±0.2 VVmi 1.5 V 1.5 V V CC /2Vmo 1.5 V 1.5 V V CC /2V HZ V OL + 0.3 V V OL + 0.3 V V OL + 0.15 V V LZV OH − 0.3 VV OH − 0.3 VV OH − 015 VBn, AnOPENV6 V GNDC L = 50 pF at V CC = 3.3 0.3 V or equivalent (includes jig and probe capacitance)C L = 30 pF at V CC = 2.5 0.2 V or equivalent (includes jig and probe capacitance)R L = R 1 = 500 W or equivalentR T = Z OUT of pulse generator (typically 50 W )Figure 4. Test CircuitPACKAGE DIMENSIONSSOIC−20DW SUFFIX CASE 751D−05ISSUE GTSSOP−20DT SUFFIX CASE 948E−02ISSUE BDIM A MIN MAX MIN MAX INCHES 6.600.260MILLIMETERS B 4.30 4.500.1690.177C 1.200.047D 0.050.150.0020.006F 0.500.750.0200.030G 0.65 BSC 0.026 BSC H 0.270.370.0110.015J 0.090.200.0040.008J10.090.160.0040.006K 0.190.300.0070.012K10.190.250.0070.010L 6.40 BSC 0.252 BSCM0 8 0 8 ____1.DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.2.CONTROLLING DIMENSION:MILLIMETER.3.DIMENSION A DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS. MOLD FLASH OR GATE BURRS SHALL NOT EXCEED 0.15 (0.006) PER SIDE.4.DIMENSION B DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION.INTERLEAD FLASH OR PROTRUSION SHALL NOT EXCEED 0.25 (0.010) PER SIDE.5.DIMENSION K DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.08(0.003) TOTAL IN EXCESS OF THE K DIMENSION AT MAXIMUM MATERIAL CONDITION.6.TERMINAL NUMBERS ARE SHOWN FOR REFERENCE ONLY .7.DIMENSION A AND B ARE TO BE DETERMINED AT DATUM PLANE −W−.6.400.252−−−−−−PACKAGE DIMENSIONSSOEIAJ−20M SUFFIX CASE 967−01ISSUE ODIM MIN MAX MIN MAX INCHES−−− 2.05−−−0.081MILLIMETERS 0.050.200.0020.0080.350.500.0140.0200.180.270.0070.01112.3512.800.4860.5045.10 5.450.2010.2151.27 BSC 0.050 BSC 7.408.200.2910.3230.500.850.0200.0331.10 1.500.0430.0590 0.700.900.0280.035−−−0.81−−−0.032A 1H E Q 1L E _10 _0 _10 _NOTES:1.DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.2.CONTROLLING DIMENSION: MILLIMETER.3.DIMENSIONS D AND E DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS AND ARE MEASURED AT THE PARTING LINE. MOLD FLASH ORPROTRUSIONS SHALL NOT EXCEED 0.15 (0.006)PER SIDE.4.TERMINAL NUMBERS ARE SHOWN FOR REFERENCE ONLY.5.THE LEAD WIDTH DIMENSION (b) DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.08 (0.003)TOTAL IN EXCESS OF THE LEAD WIDTHDIMENSION AT MAXIMUM MATERIAL CONDITION.DAMBAR CANNOT BE LOCATED ON THE LOWER RADIUS OR THE FOOT. MINIMUM SPACEBETWEEN PROTRUSIONS AND ADJACENT LEAD TO BE 0.46 ( 0.018).A b c D E e L M ZON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further noticeto any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages.“Typical” parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates,and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.PUBLICATION ORDERING INFORMATION。

74LVC245A; 74LVCH245A 八路总线收发器; 3 状态 数据手册说明书

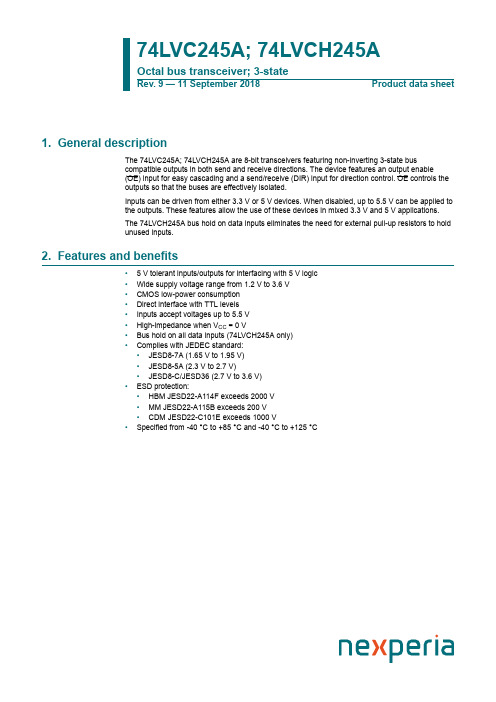

74LVC245A; 74LVCH245AOctal bus transceiver; 3-stateRev. 9 — 11 September 2018Product data sheet1. General descriptionThe 74LVC245A; 74LVCH245A are 8-bit transceivers featuring non-inverting 3-state buscompatible outputs in both send and receive directions. The device features an output enable(OE) input for easy cascading and a send/receive (DIR) input for direction control. OE controls theoutputs so that the buses are effectively isolated.Inputs can be driven from either 3.3 V or 5 V devices. When disabled, up to 5.5 V can be applied tothe outputs. These features allow the use of these devices in mixed 3.3 V and 5 V applications.The 74LVCH245A bus hold on data inputs eliminates the need for external pull-up resistors to holdunused inputs.2. Features and benefits• 5 V tolerant inputs/outputs for interfacing with 5 V logic•Wide supply voltage range from 1.2 V to 3.6 V•CMOS low-power consumption•Direct interface with TTL levels•Inputs accept voltages up to 5.5 V•High-impedance when V CC = 0 V•Bus hold on all data inputs (74LVCH245A only)•Complies with JEDEC standard:•JESD8-7A (1.65 V to 1.95 V)•JESD8-5A (2.3 V to 2.7 V)•JESD8-C/JESD36 (2.7 V to 3.6 V)•ESD protection:•HBM JESD22-A114F exceeds 2000 V•MM JESD22-A115B exceeds 200 V•CDM JESD22-C101E exceeds 1000 V•Specified from -40 °C to +85 °C and -40 °C to +125 °C3. Ordering information4. Functional diagram5. Pinning information5.1. Pinning74LVC245A 74LVCH245ADIR V CC A0OE A1B0A2B1A3B2A4B3A5B4A6B5A7B6GND B7001aak2921234567891012111413161518172019Fig. 3.Pin configuration SOT163-1 (SO20),SOT339-1 (SSOP20) and SOT360-1 (TSSOP20)001aak29374LVC245A 74LVCH245AT ransparent top viewB6A6A7B5A5B4A4B3A3B2A2B1A1B0A0OE G N D B 7D I R V C C9128137146155164173182191011120terminal 1 index areaGND (1)(1) This is not a supply pin. The substrate is attached to this pad using conductive die attach material. There is no electrical or mechanical requirement to solder this pad. However, if it is soldered, the solder land should remain floating or be connected to GND.Fig. 4.Pin configuration SOT764-1 (DHVQFN20)5.2. Pin description6. Functional descriptionTable 3. Function selectionH = HIGH voltage level; L = LOW voltage level; X = don’t care; Z = high impedance OFF-state.7. Limiting valuesTable 4. Limiting valuesIn accordance with the Absolute Maximum Rating System (IEC 60134). Voltages are referenced to GND (ground = 0 V).[1]The minimum input voltage ratings may be exceeded if the input current ratings are observed.[2]The output voltage ratings may be exceeded if the output current ratings are observed.[3]For SO20 packages: above 70 °C derate linearly with 8 mW/K.For (T)SSOP20 packages: above 60 °C derate linearly with 5.5 mW/K.For DHVQFN20 packages: above 60 °C derate linearly with 4.5 mW/K.8. Recommended operating conditions9. Static characteristicsTable 6. Static characteristicsAt recommended operating conditions. Voltages are referenced to GND (ground = 0 V).[1]All typical values are measured at V CC = 3.3 V (unless stated otherwise) and T amb = 25 °C.[2]The bus hold circuit is switched off when V I ˃ V CC allowing 5.5 V on the input terminal.[3]For I/O ports the parameter I OZ includes the input leakage current.[4]Valid for data inputs of bus hold parts only (74LVCH245A). Note that control inputs do not have a bus hold circuit.[5]The specified sustaining current at the data input holds the input below the specified V I level.[6]The specified overdrive current at the data input forces the data input to the opposite input state.10. Dynamic characteristicsTable 7. Dynamic characteristicsVoltages are referenced to GND (ground = 0 V). For test circuit see Fig. 7.[1]Typical values are measured at T amb = 25 °C and V CC = 1.2 V, 1.8 V, 2.5 V, 2.7 V and 3.3 V respectively.[2]t pd is the same as t PLH and t PHL.t en is the same as t PZL and t PZH.t dis is the same as t PLZ and t PHZ.[3]Skew between any two outputs of the same package switching in the same direction. This parameter is guaranteed by design.[4]C PD is used to determine the dynamic power dissipation (P D in μW).P D = C PD × V CC2 × f i × N + Σ(C L × V CC2 × f o) where:f i = input frequency in MHz; f o = output frequency in MHzC L = output load capacitance in pFV CC = supply voltage in VoltsN = number of inputs switchingΣ(C L × V CC2 × f o) = sum of the outputs.10.1. Waveforms and test circuit11. Package outlineSO20: plastic small outline package; 20 leads; body width 7.5 mm SOT163-1Fig. 8.Package outline SOT163-1 (SO20)SSOP20: plastic shrink small outline package; 20 leads; body width 5.3 mm SOT339-1Fig. 9.Package outline SOT339-1 (SSOP20)TSSOP20: plastic thin shrink small outline package; 20 leads; body width 4.4 mm SOT360-1Fig. 10.Package outline SOT360-1 (TSSOP20)DHVQFN20: plastic dual in-line compatible thermal enhanced very thin quad flat package; no leads;Fig. 11.Package outline SOT764-1 (DHVQFN20)12. Abbreviations13. Revision history14. Legal informationData sheet status[1]Please consult the most recently issued document before initiating orcompleting a design.[2]The term 'short data sheet' is explained in section "Definitions".[3]The product status of device(s) described in this document may havechanged since this document was published and may differ in case ofmultiple devices. The latest product status information is available onthe internet at https://.DefinitionsDraft — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. Nexperia does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information. Short data sheet — A short data sheet is an extract from a full data sheet with the same product type number(s) and title. A short data sheet is intended for quick reference only and should not be relied upon to contain detailed and full information. For detailed and full information see the relevant full data sheet, which is available on request via the local Nexperia sales office. In case of any inconsistency or conflict with the short data sheet, the full data sheet shall prevail.Product specification — The information and data provided in a Product data sheet shall define the specification of the product as agreed between Nexperia and its customer, unless Nexperia and customer have explicitly agreed otherwise in writing. In no event however, shall an agreement be valid in which the Nexperia product is deemed to offer functions and qualities beyond those described in the Product data sheet.DisclaimersLimited warranty and liability — Information in this document is believedto be accurate and reliable. However, Nexperia does not give any representations or warranties, expressed or implied, as to the accuracyor completeness of such information and shall have no liability for the consequences of use of such information. Nexperia takes no responsibility for the content in this document if provided by an information source outside of Nexperia.In no event shall Nexperia be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removalor replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.Notwithstanding any damages that customer might incur for any reason whatsoever, Nexperia’s aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of Nexperia.Right to make changes — Nexperia reserves the right to make changesto information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.Suitability for use — Nexperia products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunctionof an Nexperia product can reasonably be expected to result in personal injury, death or severe property or environmental damage. Nexperia and its suppliers accept no liability for inclusion and/or use of Nexperia products in such equipment or applications and therefore such inclusion and/or use is at the customer’s own risk.Quick reference data — The Quick reference data is an extract of the product data given in the Limiting values and Characteristics sections of this document, and as such is not complete, exhaustive or legally binding. Applications — Applications that are described herein for any of these products are for illustrative purposes only. Nexperia makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.Customers are responsible for the design and operation of their applications and products using Nexperia products, and Nexperia accepts no liability for any assistance with applications or customer product design. It is customer’s sole responsibility to determine whether the Nexperia product is suitableand fit for the customer’s applications and products planned, as well asfor the planned application and use of customer’s third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products. Nexperia does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer’s applications or products, or the application or use by customer’s third party customer(s). Customer is responsible for doing all necessary testing for the customer’s applications and products using Nexperia products in order to avoid a default of the applications and the products or of the application or use by customer’s third party customer(s). Nexperia does not accept any liability in this respect.Limiting values — Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC 60134) will cause permanent damage to the device. Limiting values are stress ratings only and (proper) operation of the device at these or any other conditions above thosegiven in the Recommended operating conditions section (if present) or the Characteristics sections of this document is not warranted. Constant or repeated exposure to limiting values will permanently and irreversibly affect the quality and reliability of the device.Terms and conditions of commercial sale — Nexperia products aresold subject to the general terms and conditions of commercial sale, as published at /profile/terms, unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. Nexperia hereby expressly objects to applying the customer’s general terms and conditions with regard to the purchase of Nexperia products by customer.No offer to sell or license — Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.Export control — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.Non-automotive qualified products — Unless this data sheet expressly states that this specific Nexperia product is automotive qualified, the product is not suitable for automotive use. It is neither qualified nor tested in accordance with automotive testing or application requirements. Nexperia accepts no liability for inclusion and/or use of non-automotive qualified products in automotive equipment or applications.In the event that customer uses the product for design-in and use in automotive applications to automotive specifications and standards, customer (a) shall use the product without Nexperia’s warranty of the product for such automotive applications, use and specifications, and (b) whenever customer uses the product for automotive applications beyond Nexperia’s specifications such use shall be solely at customer’s own risk, and (c) customer fully indemnifies Nexperia for any liability, damages or failed product claims resulting from customer design and use of the product for automotive applications beyond Nexperia’s standard warranty and Nexperia’s product specifications.Translations — A non-English (translated) version of a document is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.TrademarksNotice: All referenced brands, product names, service names and trademarks are the property of their respective owners.Contents1. General description (1)2. Features and benefits (1)3. Ordering information (2)4. Functional diagram (2)5. Pinning information (3)5.1. Pinning (3)5.2. Pin description (3)6. Functional description (3)7. Limiting values (4)8. Recommended operating conditions (4)9. Static characteristics (5)10. Dynamic characteristics (7)10.1. Waveforms and test circuit (8)11. Package outline (10)12. Abbreviations (14)13. Revision history (14)14. Legal information (15)© Nexperia B.V. 2018. All rights reservedFor more information, please visit: Forsalesofficeaddresses,pleasesendanemailto:*************************** Date of release: 11 September 2018。

74lvc245中文说明

74LV245是低压硅栅CMOS器件,与74HC245和74HCT245针脚和功能兼容。

74LV245是八位元收发器,在发送和接收方向上都具有非反相3态总线兼容输出。

发送/接收(DIR)输入控制方向,而输出使能(OE)输入则可实现轻松级联。

针脚OE控制输出,因此总线可以得到有效隔离。

特性和优势

•宽工作电压范围:1.0 V至5.5 V

•最适合低压应用:1.0 V至3.6 V

•接受介于VCC = 2.7 V和VCC = 3.6 V之间的TTL输入电平

•VCC = 3.3 V且T amb = 25 °C时的典型输出地弹:< 0.8 V

•VCC = 3.3 V且T amb = 25 °C时的典型高电平输出电压(VOH)欠冲:> 2 V •ESD保护:

o HBM JESD22-A114E超过2000 V

o MM JESD22-A115-A超过200 V

•多种封装选择

•额定温度范围为-40 °C至+85 °C和-40 °C至+125 °C

外形图

显示功能框图

真值表

INPUTS INPUTS/OUTPUT OE DIR An Bn

H=高电压L=低电压X=无输入、Z=高阻态。

SN74LVC8T245中文资料

VI

Input voltage range(2)

VO

Voltage range applied to any output in the high-impedance or power-off state(2)

VO

Voltage range applied to any output in the high or low state(2)(3)

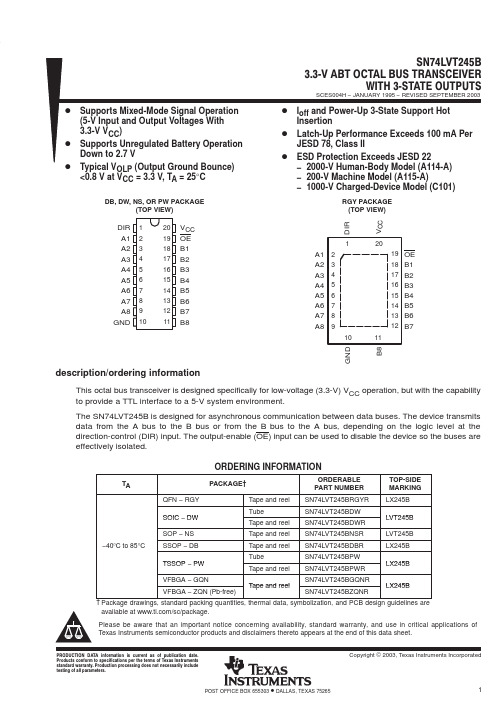

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

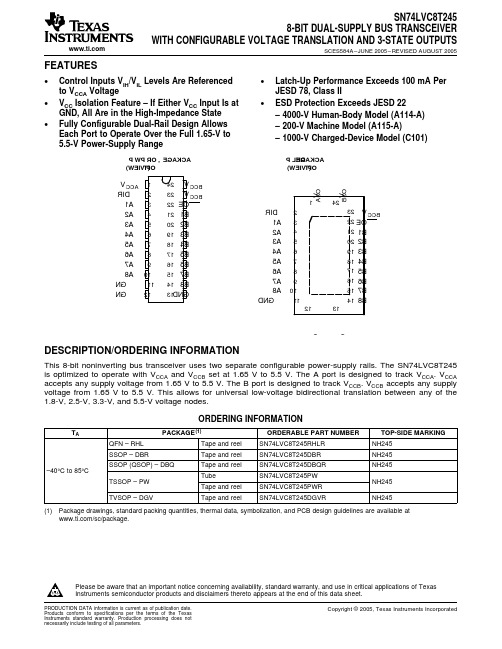

• ESD Protection Exceeds JESD 22 – 4000-V Human-Body Model (A114-A) – 200-V Machine Model (A115-A) – 1000-V Charged-Device Model (C101)

O (PTVIEW) ACKARGEHL P

O (PTVIEW) ACKAGE , OR PW P DB, DBQ, DGV

13 B8 14 B7 15 B6 16 B5 17 B4 18 B3 19 B2 20 B1 21 OE 22 BCC V 23

24

12 11 10 9 8 7 6 5 4 3 2

1

GND A8 A7 A6 A5 A4 A3 A2 A1 DIR

Copyright © 2005, Texas Instruments Incorporated

MC74LVX245八线总线传输器说明书

MC74LVX245Octal Bus TransceiverWith 5 V−Tolerant InputsThe MC74LVX245 is an advanced high speed CMOS octal bus transceiver.It is intended for two−way asynchronous communication between data buses. The direction of data transmission is determined by the level of the T/R input. The output enable pin (OE) can be used to disable the device, so that the buses are effectively isolated.All inputs are equipped with protection circuits against static discharge.Features•High Speed: t PD = 4.7 ns (Typ) at V CC = 3.3 V•Low Power Dissipation: I CC = 4 m A (Max) at T A = 25°C •Power Down Protection Provided on Inputs •Balanced Propagation Delays •Low Noise: V OLP = 0.8 V (Max)•Pin and Function Compatible with Other Standard Logic Families •Latchup Performance Exceeds 300 mA•ESD Performance:Human Body Model > 2000 V;Machine Model > 200 V•These Devices are Pb−Free and are RoHS CompliantApplication Notes•Do Not Force a Signal on an I/O Pin when it is an Active Output,Damage May Occur•All Floating (High Impedance) Input or I/O Pins must be Fixed by Means of Pullup or Pulldown Resistors or Bus Terminator ICs •A Parasitic Diode is Formed between the Bus and V CC Terminals Therefore, the LVX245 cannot be Used to Interface 5.0 V to 3.0 VSystems DirectlySee detailed ordering and shipping information in the package dimensions section on page 5 of this data sheet.ORDERING INFORMATION120MARKING DIAGRAMSSOIC−20DW SUFFIX CASE 751DTSSOP−20DT SUFFIX CASE 948ELVX245= Specific Device Code A = Assembly Location WL, L = Wafer Lot Y= YearWW, W = Work WeekG or G= Pb−Free Package(Note: Microdot may be in either location)LVX 245ALYW G GSOIC−20TSSOP−20PIN ASSIGNMENT20−Lead (Top View)192018171615142134567V CC 1381291110OE B0B1B2B3B4B5B6B7T/R A0A1A2A3A4A5A6A7GNDB0OE 19T/R 1A0B1A1B2A2B3A3B4A4B5A5B6A6B7A7Figure 1. Logic DiagramTable 1. PIN NAMESPins FunctionOE T/R A0−A7Bo−B7Output Enable Input Transmit/Receive InputSide A 3−State Inputs or 3−State Outputs Side B 3−State Inputs or 3−State OutputsINPUTS OPERATING MODE Non−Inverting OE T/R L L B Data to A Bus L H A Data to B Bus HXZH = High Voltage Level; L = Low Voltage Level; Z = High Impedance State;X = High or Low Voltage Level and Transitions are Acceptable; For I CC reasons, Do Not Float InputsMAXIMUM RATINGSSymbol Parameter Value Unit V CC DC Supply Voltage–0.5 to +7.0V V in DC Input Voltage (T/R, OE)–0.5 to +7.0V V I/O DC Output Voltage–0.5 to V CC +0.5VI IK Input Diode Current−20mAI OK Output Diode Current±20mAI out DC Output Current, per Pin±25mAI CC DC Supply Current, V CC and GND Pins±75mAP D Power Dissipation180mW T stg Storage Temperature–65 to +150°C Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.RECOMMENDED OPERATING CONDITIONSSymbol Parameter Min Max Unit V CC DC Supply Voltage 2.0 3.6V V in DC Input Voltage (T/R, OE)0 5.5V V I/O DC Output Voltage0V CC V T A Operating Temperature, All Package Types−40+85°CD t/D V Input Rise and Fall Time0100ns/V Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.DC ELECTRICAL CHARACTERISTICSSymbol Parameter Test Conditions V CCVT A = 25°C T A = −40 to 85°CUnit Min Typ Max Min MaxV IH High−Level Input Voltage 2.03.03.61.52.02.41.52.02.4VV IL Low−Level Input Voltage 2.03.03.60.50.80.80.50.80.8VV OH High−Level Output Voltage(V in = V IH or V IL)I OH = −50 m AI OH = −50 m AI OH = −4 mA2.03.03.01.92.92.582.03.01.92.92.48VV OL Low−Level Output Voltage(V in = V IH or V IL)I OL = 50 m AI OL = 50 m AI OL = 4 mA2.03.03.00.00.00.10.10.360.10.10.44VI in Input Leakage Current V in = 5.5 V or GND(T/R, OE)3.6±0.1±1.0m AI OZ Maximum 3−State Leakage Current V in = V IL or V IHV out = V CC or GND 3.6±0.25±2.5m AI CC Quiescent Supply Current V in = V CC or GND 3.6 4.040.0m A Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.AC ELECTRICAL CHARACTERISTICS (Input t r = t f= 3.0 ns)Symbol Parameter Test ConditionsT A = 25°C T A = −40 to 85°CUnit Min Typ Max Min Maxt PLH, t PHL Propagation DelayInput to OutputV CC = 2.7 V C L = 15 pFC L = 50 pF6.18.610.714.21.01.013.517.0nsV CC = 3.3 ± 0.3 V C L = 15 pFC L = 50 pF4.77.26.610.11.01.08.011.5t PZL, t PZH Output Enable Time toHigh and Low LevelV CC = 2.7 V C L = 15 pFR L = 1 k W C L = 50 pF9.011.516.920.41.01.020.524.0nsV CC = 3.3 ± 0.3 V C L = 15 pFR L = 1 k W C L = 50 pF7.19.611.014.51.01.013.016.5t PLZ, t PHZ Output Disable Time FromHigh and Low LevelV CC = 2.7 V C L = 50 pFR L = 1 k W11.518.0 1.021.0nsV CC = 3.3 ± 0.3 V C L = 50 pFR L = 1 k W9.612.8 1.014.5t OSHL t OSLH Output−to−Output Skew(Note 1)V CC = 2.7 V C L = 50 pFV CC = 3.3 ±0.3 V C L = 50 pF1.51.51.51.5ns1.Skew is defined as the absolute value of the difference between the actual propagation delay for any two separate outputs of the same device.The specification applies to any outputs switching in the same direction, either HIGH−to−LOW (t OSHL) or LOW−to−HIGH (t OSLH); parameter guaranteed by design.CAPACITIVE CHARACTERISTICSSymbol ParameterT A = 25°C T A = −40 to 85°CUnit Min Typ Max Min MaxC in Input Capacitance (T/R, OE)41010pFC I/O Maximum 3−State I/O Capacitance8pFC PD Power Dissipation Capacitance (Note 2)21pF2.C PD is defined as the value of the internal equivalent capacitance which is calculated from the operating current consumption without load.Average operating current can be obtained by the equation: I CC(OPR) = C PD V CC f in + I CC/8 (per bit). C PD is used to determine the no−load dynamic power consumption; P D = C PD V CC2 f in + I CC V CC.NOISE CHARACTERISTICS (Input t r = t f = 3.0ns, C L = 50pF, V CC = 3.3V, Measured in SOIC Package)Symbol CharacteristicT A = 25°CUnit Typ MaxV OLP Quiet Output Maximum Dynamic V OL0.50.8V V OLV Quiet Output Minimum Dynamic V OL−0.5−0.8V V IHD Minimum High Level Dynamic Input Voltage 2.0V V ILD Maximum Low Level Dynamic Input Voltage0.8VFigure 2. Figure 3.V CCGNDSWITCHING WAVEFORMSOEA or BA or BV CCGND HIGHIMPEDANCE V OL +0.3V V OH -0.3V HIGHIMPEDANCEV CC GNDT/R*Includes all probe and jig capacitance C L *TEST POINT *Includes all probe and jig capacitanceTEST POINT CONNECT TO V CC WHEN TESTING t PLZ AND t PZL .CONNECT TO GND WHEN TESTING t PHZ AND t PZH .TEST CIRCUITSFigure 4. Propagation Delay Test Circuit Figure 5. 3−State Test CircuitORDERING INFORMATIONDevicePackage Shipping †MC74LVX245DWR2G SOIC−20(Pb−Free)1000 / Tape & Reel MC74LVX245DTR2GTSSOP−20(Pb−Free)2500 / Tape & Reel†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.CASE 948E−02ISSUE CDIM A MIN MAX MIN MAX INCHES 6.600.260MILLIMETERS B 4.30 4.500.1690.177C 1.200.047D 0.050.150.0020.006F 0.500.750.0200.030G 0.65 BSC 0.026 BSC H 0.270.370.0110.015J 0.090.200.0040.008J10.090.160.0040.006K 0.190.300.0070.012K10.190.250.0070.010L 6.40 BSC 0.252 BSCM0 8 0 8 ____NOTES:1.DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.2.CONTROLLING DIMENSION:MILLIMETER.3.DIMENSION A DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS. MOLD FLASH OR GATE BURRS SHALL NOT EXCEED 0.15 (0.006) PER SIDE.4.DIMENSION B DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION.INTERLEAD FLASH OR PROTRUSIONSHALL NOT EXCEED 0.25 (0.010) PER SIDE.5.DIMENSION K DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.08(0.003) TOTAL IN EXCESS OF THE K DIMENSION AT MAXIMUM MATERIAL CONDITION.6.TERMINAL NUMBERS ARE SHOWN FOR REFERENCE ONLY .7.DIMENSION A AND B ARE TO BE DETERMINED AT DATUM PLANE −W−.DETAIL E6.400.252------16X0.360.65PITCHSOLDERING FOOTPRINT**For additional information on our Pb−Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.CASE 751D−05ISSUE GM0.25SA SBTDIM MIN MAXMILLIMETERSA 2.35 2.65A10.100.25B0.350.49C0.230.32D12.6512.95E7.407.60e 1.27 BSCH10.0510.55h0.250.75L0.500.90q0 7NOTES:1.DIMENSIONS ARE IN MILLIMETERS.2.INTERPRET DIMENSIONS AND TOLERANCESPER ASME Y14.5M, 1994.3.DIMENSIONS D AND E DO NOT INCLUDE MOLDPROTRUSION.4.MAXIMUM MOLD PROTRUSION 0.15 PER SIDE.5.DIMENSION B DOES NOT INCLUDE DAMBARPROTRUSION. ALLOWABLE PROTRUSIONSHALL BE 0.13 TOTAL IN EXCESS OF BDIMENSION AT MAXIMUM MATERIALCONDITION.__ON Semiconductor and the are registered trademarks of Semiconductor Components Industries, LLC (SCILLC) or its subsidiaries in the United States and/or other countries.SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC’s product/patent coverage may be accessed at /site/pdf/Patent−Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. “Typical” parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.PUBLICATION ORDERING INFORMATIONMouser ElectronicsAuthorized DistributorClick to View Pricing, Inventory, Delivery & Lifecycle Information:O N Semiconductor:MC74LVX245MELG MC74LVX245MG MC74LVX245DTR2MC74LVX245DTR2G MC74LVX245DWR2 MC74LVX245DWR2G。

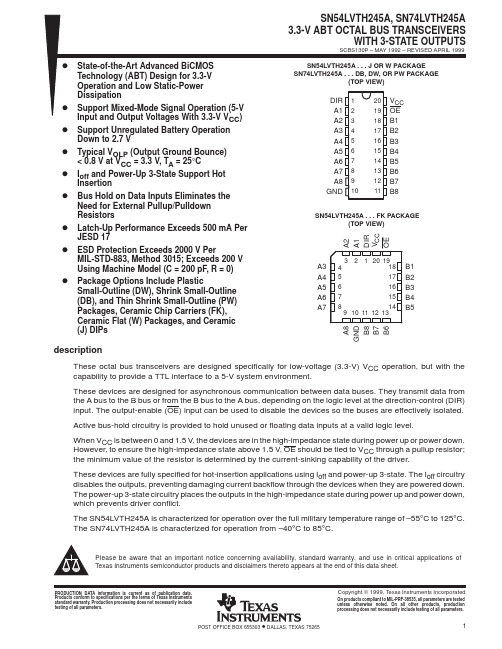

SN74LVTH245中文资料

元器件交易网IMPORTANT NOTICETexas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinueany product or service without notice, and advise customers to obtain the latest version of relevant informationto verify, before placing orders, that information being relied on is current and complete. All products are soldsubject to the terms and conditions of sale supplied at the time of order acknowledgement, including thosepertaining to warranty, patent infringement, and limitation of liability.TI warrants performance of its semiconductor products to the specifications applicable at the time of sale inaccordance with TI’s standard warranty. Testing and other quality control techniques are utilized to the extentTI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarilyperformed, except those mandated by government requirements.CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OFDEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE (“CRITICALAPPLICATIONS”). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, ORWARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHERCRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TOBE FULLY AT THE CUSTOMER’S RISK.In order to minimize risks associated with the customer’s applications, adequate design and operatingsafeguards must be provided by the customer to minimize inherent or procedural hazards.TI assumes no liability for applications assistance or customer product design. TI does not warrant or representthat any license, either express or implied, is granted under any patent right, copyright, mask work right, or otherintellectual property right of TI covering or relating to any combination, machine, or process in which suchsemiconductor products or services might be or are used. TI’s publication of information regarding any thirdparty’s products or services does not constitute TI’s approval, warranty or endorsement thereof.Copyright © 1999, Texas Instruments Incorporated。

74VCX245BQX中文资料

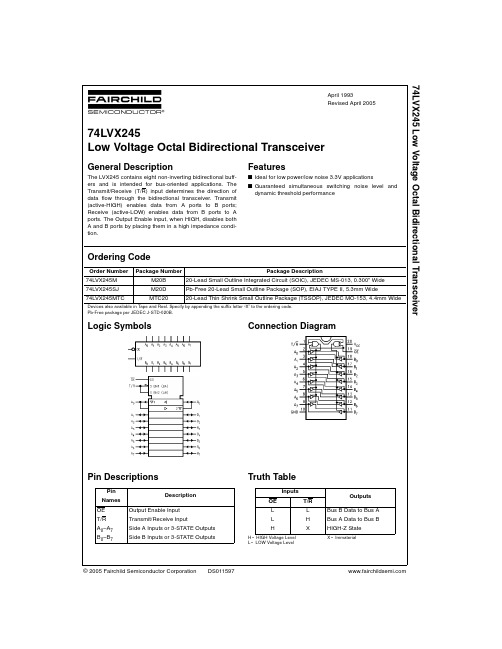

© 2005 Fairchild Semiconductor Corporation DS500167June 1999Revised April 200574VCX245 Low Voltage Bidirectional Transceiver with 3.6V Tolerant Inputs and Outputs74VCX245Low Voltage Bidirectional Transceiver with 3.6V Tolerant Inputs and OutputsGeneral DescriptionThe VCX245 contains eight non-inverting bidirectional buff-ers with 3-STATE outputs and is intended for bus oriented applications. The T/R input determines the direction of data flow. The OE input disables both the A and B ports by plac-ing them in a high impedance state.The 74VCX245 is designed for low voltage (1.4V to 3.6V)V CC applications with I/O compatibility up to 3.6V.The 74VCX245 is fabricated with an advanced CMOS technology to achieve high-speed operation while main-taining low CMOS power dissipation.Featuress 1.4V to 3.6V V CC supply operation s 3.6V tolerant inputs and outputss Power-off high impedance inputs and outputs s Supports Live Insertion and Withdrawal (Note 1)s t PD3.5 ns max for 3.0V to 3.6V V CC s Static Drive (I OH /I OL )r 24 mA @ 3.0V V CCs Uses patented noise/EMI reduction circuitry s Latchup performance exceeds 300 mA s ESD performance:Human body model ! 2000V Machine model ! 200Vs Leadless DQFN Pb-Free packageNote 1: To ensure the high impedance state during power up and power down, OE n should be tied to V CC through a pull up resistor. The minimum value of the resistor is determined by the current sourcing capability of the driver.Ordering Code:Pb-Free package per JEDEC J-STD-020B.Note 2: Devices also available in Tape and Reel. Specify by appending the suffix letter “X” to the ordering code.Note 3: DQFN package available in Tape and Reel only,Logic Symbol Pin DescriptionsOrder Number Package Number Package Description74VCX245WM (Note 2)M20B 20-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300" Wide74VCX245BQX (Note 3)MLP020B Pb-Free 20-Terminal Depopulated Quad Very-Thin Flat Pack No Leads (DQFN), JEDEC MO-241, 2.5 x 4.5mm74VCX245MTC (Note 2)MTC2020-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm WidePin Names DescriptionOE Output Enable Input (Active LOW)T/R Transmit/Receive InputA 0–A 7Side A Inputs or 3-STATE OutputsB 0–B 7Side B Inputs or 3-STATE Outputs 274V C X 245Connection DiagramsPin Assignments for SOIC and TSSOPPin Assignment for DQFN(Top Through View)Truth TableH HIGH Voltage Level L LOW Voltage Level X ImmaterialZ High ImpedanceNote 4: Unused bus terminals during HIGH Z State must be held HIGH or LOW.Logic DiagramInputs OutputsOE T/R L L BusB 0–B 7 Data to Bus A 0–A 7L H Bus A 0–A 7 Data to Bus B 0–B 7HXHIGH Z State on A 0–A 7, B 0–B 7 (Note 4)74VCX245Absolute Maximum Ratings (Note 5)Recommended Operating Conditions (Note 7)Note 5: The Absolute Maximum Ratings are those values beyond which the safety of the device cannot be guaranteed. The device should not be operated at these limits. The parametric values defined in the Electrical Characteristics tables are not guaranteed at the Absolute Maximum Rat-ings. The “Recommended Operating Conditions ” table will define the condi-tions for actual device operation.Note 6: I O Absolute Maximum Rating must be observed.Note 7: Floating or unused inputs must be held HIGH or LOW.DC Electrical CharacteristicsSupply Voltage (V CC ) 0.5V to 4.6V DC Input Voltage (V I ) 0.5V to 4.6V DC Output Voltage (V O )Outputs 3-STATE 0.5V to 4.6V Outputs Active (Note 6)0.5V to V CC 0.5VDC Input Diode Current (I IK ) V I 0V 50 mADC Output Diode Current (I OK ) V O 0V 50 mA V O ! V CC50 mADC Output Source/Sink Current (I OH /I OL )r 50 mA DC V CC or Ground Current r 100 mAStorage Temperature (T STG )65q C to 150q CPower Supply Operating 1.4V to 3.6VInput Voltage 0.3V to 3.6VOutput Voltage (V O )Output in Active States 0V to V CC Output in 3-STATE 0V to 3.6VOutput Current in I OH /I OL V CC 3.0V to 3.6V r 24 mA V CC 2.3V to 2.7V r 18 mA V CC 1.65V to 2.3V r 6 mA V CC 1.4V to 1.6Vr 2 mAFree Air Operating Temperature (T A ) 40q C to 85q CMinimum Input Edge Rate ('t/'V)V IN 0.8V to 2.0V, V CC 3.0V10 ns/VSymbol ParameterConditionsV CC Min MaxUnits(V)V IHHIGH Level Input Voltage2.7 to3.6 2.0V2.3 to 2.7 1.61.65 to 2.30.65 u V CC 1.4 to 1.60.65 u V CCV ILLOW Level Input Voltage2.7 to3.60.8V 2.3 to 2.70.71.65 to 2.30.35 u V CC 1.4 to 1.60.35 u V CCV OHHIGH Level Output VoltageI OH 100 P A 2.7 to 3.6V CC 0.2VI OH 12 mA 2.7 2.2I OH 18 mA 3.0 2.4I OH 24 mA 3.0 2.2I OH 100 P A 2.3 to 2.7V CC 0.2I OH 6 mA 2.3 2.0I OH 12 mA 2.3 1.8I OH 18 mA 2.3 1.7I OH 100 P A 1.65 to 2.3V CC 0.2I OH 6 mA 1.65 1.25I OH 100 P A 1.4 to 1.6V CC 0.2I OH 2 mA1.41.05 474V C X 245DC Electrical Characteristics (Continued)Note 8: Outputs disabled or 3-STATE only.AC Electrical Characteristics (Note 9)Note 9: For C L 50P F, add approximately 300 ps to the AC maximum specification.Note 10: Skew is defined as the absolute value of the difference between the actual propagation delay for any two separate outputs of the same device. The specification applies to any outputs switching in the same direction, either HIGH-to-LOW (t OSHL ) or LOW-to-HIGH (t OSLH ).Symbol ParameterConditionsV CC Min Max Units(V)V OLLOW Level Output VoltageI OL 100 P A 2.7 to 3.60.2VI OL 12 mA 2.70.4I OL 18 mA 3.00.4I OL 24 mA 3.00.55I OL 100 P A 2.3 to 2.70.2I OL 12 mA 2.30.4I OL 18 mA 2.30.6I OL 100 P A 1.65 to 2.30.2I OL 6 mA 1.650.3I OL 100 P A 1.4 to 1.60.2I OL 2 mA1.40.35I I Input Leakage Current 0 d V I d 3.6V 1.4 to 3.6r 5.0P A I OZ 3-STATE Output Leakage 0 d V O d 3.6V 1.4 to 3.6r 10P A V I V IH or V IL I OFF I Power-OFF Leakage Current 0 d (V I , V O ) d 3.6V 010P A I CC Quiescent Supply Current V I V CC or GND1.4 to 3.620P A V CC d (V I , V O ) d 3.6V (Note 8) 1.4 to 3.6r 20'I CCIncrease in I CC per InputV IH V CC 0.6V2.7 to3.6750P ASymbol ParameterConditionsV CC T A 40q C to 85q C UnitsFigure (V)Min Max Number t PHL , t PLHPropagation Delay C L 30 pF, R L 500:3.3 r 0.30.6 3.5nsFigures 1, 2A n to B n or B n to A n2.5 r 0.20.8 4.21.8 r 0.15 1.58.4C L 15 pF, R L 2k :1.5 r 0.1 1.016.8Figures 5, 6t PZL , t PZHOutput Enable TimeC L 30 pF, R L 500:3.3 r 0.30.64.5nsFigures 1, 3, 42.5 r 0.20.8 5.61.8 r 0.151.59.8C L 15 pF, R L 2k :1.5 r 0.1 1.019.6Figures 5, 7, 8t PLZ , t PHZOutput Disable TimeC L 30 pF, R L 500:3.3 r 0.30.6 3.6nsFigures 1, 3, 42.5 r 0.20.8 4.01.8 r 0.151.57.2C L 15 pF, R L 2k :1.5 r 0.1 1.014.4Figures 5, 7, 8t OSHL Output to Output Skew C L 30 pF, R L 500:3.3 r 0.30.5nst OSLH(Note 10)2.5 r 0.20.51.8 r 0.150.75C L 15 pF, R L 2k :1.5 r 0.11.574VCX245Dynamic Switching CharacteristicsCapacitanceSymbol ParameterConditionsV CC (V)T A 25q C UnitsTypical V OLPQuiet Output Dynamic Peak V OLC L 30 pF, V IH V CC , V IL 0V1.80.3V2.50.73.31.0V OLVQuiet Output Dynamic Valley V OLC L 30 pF, V IH V CC , V IL 0V1.8 0.3V2.5 0.73.31.0V OHVQuiet Output Dynamic Valley V OHC L 30 pF, V IH V CC , V IL 0V1.8 1.3V2.5 1.73.32.0Symbol ParameterConditionsT A 25q C Units Typical C IN Input Capacitance V I 0V or V CC , V CC 1.8V, 2.5V or 3.3V 6.0pF C I/O Input/Output Capacitance V I 0V or V CC , V CC 1.8V, 2.5V or 3.3V7.0pF C PDPower Dissipation CapacitanceV I 0V or V CC , f 10 MHz, V CC 1.8V, 2.5V or 3.3V20.0pF 674V C X 245AC Loading and Waveforms (VCC 3.3V r 0.3V to 1.8V r 0.15V)FIGURE 1. AC Test CircuitFIGURE 2. Waveform for Inverting and Non-Inverting FunctionsFIGURE 3. 3-STATE Output High Enable and Disable Times for Low Voltage LogicFIGURE 4. 3-STATE Output Low Enable and Disable Times for Low Voltage LogicTEST SWITCH t PLH , t PHL Opent PZL , t PLZ 6V at V CC 3.3V r 0.3V;V CC x 2 at V CC 2.5V r 0.2V; 1.8V r 0.15Vt PZH , t PHZGNDSymbol V CC3.3V r 0.3V2.5V r 0.2V 1.8V r 0.15VV mi 1.5V V CC /2V CC /2V mo 1.5V V CC /2V CC /2V X V OL 0.3V V OL 0.15V V OL 0.15V V YV OH 0.3VV OH 0.15VV OH 0.15V74VCX245AC Loading and Waveforms (VCC 1.5 r 0.1V)FIGURE 5. AC Test CircuitFIGURE 6. Waveform for Inverting and Non-Inverting FunctionsFIGURE 7. 3-STATE Output High Enable and Disable Times for Low Voltage LogicFIGURE 8. 3-STATE Output Low Enable and Disable Times for Low Voltage LogicTEST SWITCH t PLH , t PHL Opent PZL , t PLZ V CC x 2 at V CC 1.5V r 0.1Vt PZH , t PHZGNDSymbol V CC 1.5V r 0.1V V mi V CC /2V mo V CC /2V X V OL 0.1V V YV OH 0.1V 874V C X 245Tape and Reel SpecificationTape Format for DQFNTAPE DIMENSIONS inches (millimeters)REEL DIMENSIONS inches (millimeters)PackageTape Number Cavity Cover Tape DesignatorSection Cavities Status Status Leader (Start End)125 (typ)Empty Sealed BQXCarrier 3000Filled Sealed Trailer (Hub End)75 (typ)EmptySealedTapeSize A B C D N W1W212 mm13.00.0590.5120.795 2.1650.4880.724(330.0)(1.50)(13.00)(20.20)(55.00)(12.4)(18.4) 74VCX245Physical Dimensions inches (millimeters) unless otherwise noted20-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300" WidePackage Number M20B 1074V C X 245Physical Dimensionsinches (millimeters) unless otherwise noted (Continued)Pb-Free 20-Terminal Depopulated Quad Very-Thin Flat Pack No Leads (DQFN), JEDEC MO-241, 2.5 x 4.5mmPackage Number MLP020BPhysical Dimensions inches (millimeters) unless otherwise noted (Continued)20-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm WidePackage Number MTC20Fairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications.LIFE SUPPORT POLICYFAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:1.Life support devices or systems are devices or systemswhich, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be rea-sonably expected to result in a significant injury to the user.2. A critical component in any component of a life supportdevice or system whose failure to perform can be rea-sonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.元器件交易网 74VCX245 Low Voltage Bidirectional Transceiver with 3.6V Tolerant Inputs and Outputs。

74HC245中文资料,74HC245N规格书,74HC245D技术文档,DATASHEET,NXP代理商

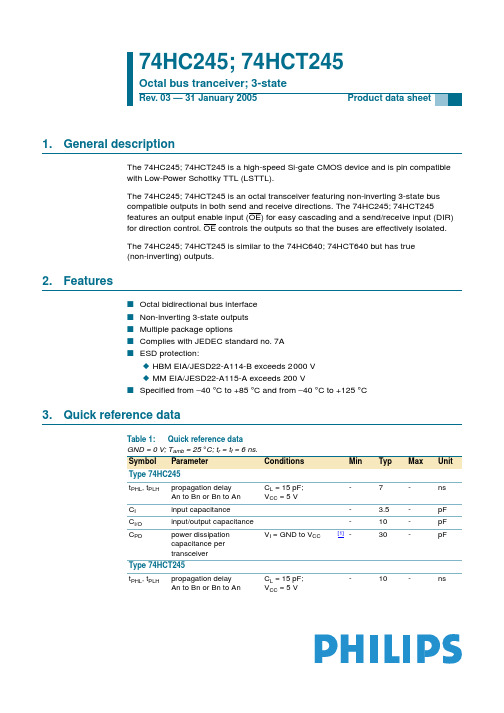

74HC245; 74HCT245

Octal bus tranceiver; 3-state

Rev. 03 — 31 January 2005

Product data sheet

1. General description

The 74HC245; 74HCT245 is a high-speed Si-gate CMOS device and is pin compatible with Low-Power Schottky TTL (LSTTL).

plastic shrink small outline package; 20 leads; body width 5.3 mm

SOT339-1

74HCT245BQ

−40 °C to +125 °C

DHVQFN20 plastic dual-in-line compatible thermal enhanced SOT764-1 very thin quad flat package no leads; 20 terminals; body 2.5 × 4.5 × 0.85 mm

x HBM EIA/JESD22-A114-B exceeds 2000 V x MM EIA/JESD22-A115-A exceeds 200 V s Specified from −40 °C to +85 °C and from −40 °C to +125 °C

3. Quick reference data

SOT163-1

74HCT245PW

−40 °C to +125 °C TSSOP20 plastic thin shrink small outline package; 20 leads; SOT360-1 body width 4.4 mm

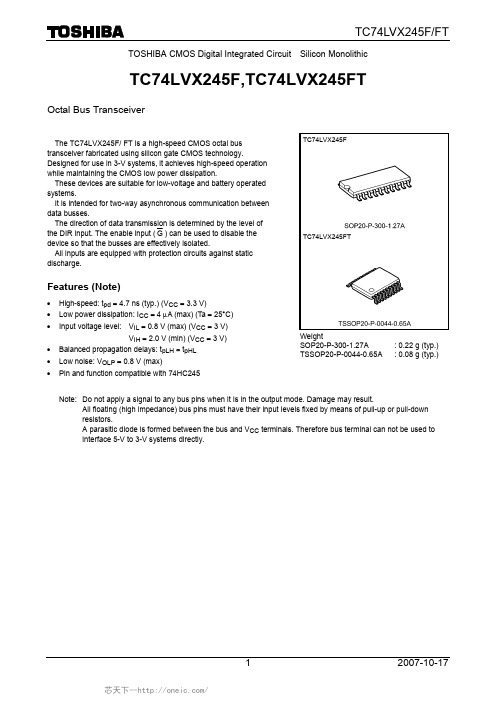

TC74LVX245FT(EL,M),TC74LVX245FW,TC74LVX245FT(EL),TC74LVX245FW(ELP), 规格书,Datasheet 资料

TOSHIBA CMOS Digital Integrated Circuit Silicon MonolithicTC74LVX245F,TC74LVX245FTOctal Bus TransceiverThe TC74LVX245F/ FT is a high-speed CMOS octal bus transceiver fabricated using silicon gate CMOS technology.Designed for use in 3-V systems, it achieves high-speed operation while maintaining the CMOS low power dissipation.These devices are suitable for low-voltage and battery operated systems.It is intended for two-way asynchronous communication between data busses.The direction of data transmission is determined by the level of the DIR input. The enable input (G ) can be used to disable the device so that the busses are effectively isolated.All inputs are equipped with protection circuits against static discharge.Features (Note)• High-speed: t pd = 4.7 ns (typ.) (V CC = 3.3 V) • Low power dissipation: I CC = 4 μA (max) (Ta = 25°C) • Input voltage level: V IL = 0.8 V (max) (V CC = 3 V)V IH = 2.0 V (min) (V CC = 3 V)• Balanced propagation delays: t pLH ∼ − tpHL •Low noise: V OLP = 0.8 V (max)• Pin and function compatible with 74HC245Note: Do not apply a signal to any bus pins when it is in the output mode. Damage may result.All floating (high impedance) bus pins must have their input levels fixed by means of pull-up or pull-down resistors.A parasitic diode is formed between the bus and V CC terminals. Therefore bus terminal can not be used to interface 5-V to 3-V systems directly.TC74LVX245FTC74LVX245FTWeightSOP20-P-300-1.27A : 0.22 g (typ.) TSSOP20-P-0044-0.65A: 0.08 g (typ.)Pin Assignment (top view)IEC Logic SymbolTruth TableX: Don’t care Z: High impedanceAbsolute Maximum Ratings (Note)Note: Exceeding any of the absolute maximum ratings, even briefly, lead to deterioration in IC performance or evendestruction.Using continuously under heavy loads (e.g. the application of high temperature/current/voltage and thesignificant change in temperature, etc.) may cause this product to decrease in the reliability significantly even if the operating conditions (i.e. operating temperature/current/voltage, etc.) are within the absolute maximum ratings and the operating ranges.Please design the appropriate reliability upon reviewing the Toshiba Semiconductor Reliability Handbook (“Handling Precautions”/“Derating Concept and Methods”) and individual reliability data (i.e. reliability testreport and estimated failure rate, etc).V CC 20 G B1 B2 B3 B4 19 18 17 16 15 14 DIR 1234567A1 A2 A3 A4 A5 A6 B5 8910A7 A8GND 13 12 11B6 B7B8GOperating Ranges (Note)Note: The operating ranges must be maintained to ensure the normal operation of the device. Unused inputs and bus inputs must be tied to either VCC or GND. Please connect both bus inputs and the bus outputs with VCC or GND when the I/O of the bus terminal changes by the function. In this case, please note that the output is not short-circuited.Electrical CharacteristicsDC CharacteristicsTa = 25°CTa = −40 to85°CCharacteristics Symbol Test ConditionV CC (V)MinTyp.Max Min MaxUnit2.0 1.5 ⎯⎯ 1.5 ⎯ 3.0 2.0 ⎯ ⎯ 2.0 ⎯ H-level V IH⎯3.6 2.4 ⎯ ⎯ 2.4 ⎯2.0 ⎯ ⎯ 0.5 ⎯ 0.53.0 ⎯ ⎯ 0.8 ⎯ 0.8 Input voltageL-level V IL⎯ 3.6⎯⎯ 0.8 ⎯ 0.8VI OH = −50 μA2.0 1.9 2.0 ⎯ 1.9 ⎯ I OH = −50 μA3.0 2.9 3.0 ⎯ 2.9 ⎯ H-level V OHV IN = V IHor V ILI OH = −4 mA3.02.58⎯⎯ 2.48 ⎯I OL = 50 μA 2.0 ⎯ 0 0.1 ⎯ 0.1I OL = 50 μA 3.0 ⎯ 0 0.1 ⎯ 0.1Output voltageL-level V OLV IN = V IHor V ILI OL = 4 mA 3.0 ⎯ ⎯ 0.36 ⎯ 0.44V3-State output Off-state current I OZ V IN = V IH or V IL V OUT = V CC or GND 3.6 ⎯ ⎯ ±0.25 ⎯ ±2.5μA Input leakage current I IN V IN = 5.5 V or GND 3.6 ⎯ ⎯±0.1⎯±1.0μA Quiescent supply currentI CCV IN = V CC or GND3.6⎯⎯ 4.0 ⎯ 40.0μAAC Characteristics (input: t r= t f= 3 ns)Note 1: Parameter guaranteed by design.(t osLH= |t pLHm− t pLHn|, t osHL= |t pHLm− t pHLn|)Note 2: Parameter guaranteed by design.Note 3: C PD is defined as the value of the internal equivalent capacitance which is calculated from the operating current consumption.Average operating current can be obtained by the equation:I CC (opr)= C PD・V CC・f IN+ I CC/8 (per bit)Noise Characteristics (Ta = 25°C, input: t r= t f= 3 ns, C L= 50 pF)Characteristics Symbol TestConditionV CC (V)Typ. Limit Unit Quiet output maximum dynamic V OL V OLP⎯ 3.30.50.8V Quiet output minimum dynamic V OL V OLV⎯ 3.3−0.5 −0.8V Minimum high level dynamic inputvoltage V IHV IHD⎯ 3.3⎯ 2.0 VMaximum low level dynamic inputvoltage V ILV ILD⎯ 3.3⎯ 0.8 VInput Equivalent Circuit Bus Terminal Equivalent Circuit (An, Bn)Weight: 0.22 g (typ.)Weight: 0.08 g (typ.)RESTRICTIONS ON PRODUCT USE•Toshiba Corporation, and its subsidiaries and affiliates (collectively “TOSHIBA”), reserve the right to make changes to the information in this document, and related hardware, software and systems (collectively “Product”) without notice.•This document and any information herein may not be reproduced without prior written permission from TOSHIBA. Even with TOSHIBA’s written permission, reproduction is permissible only if reproduction is without alteration/omission.•Though TOSHIBA works continually to improve Product’s quality and reliability, Product can malfunction or fail. Customers are responsible for complying with safety standards and for providing adequate designs and safeguards for their hardware, software and systems which minimize risk and avoid situations in which a malfunction or failure of Product could cause loss of human life, bodily injury or damage to property, including data loss or corruption. Before creating and producing designs and using, customers must also refer to and comply with (a) the latest versions of all relevant TOSHIBA information, including without limitation, this document, the specifications, the data sheets and application notes for Product and the precautions and conditions set forth in the “TOSHIBA Semiconductor Reliability Handbook” and (b) the instructions for the application that Product will be used with or for. Customers are solely responsible for all aspects of their own product design or applications, including but not limited to (a) determining the appropriateness of the use of this Product in such design or applications; (b) evaluating and determining the applicability of any information contained in this document, or in charts, diagrams, programs, algorithms, sample application circuits, or any other referenced documents; and (c) validating all operating parameters for such designs and applications. TOSHIBA ASSUMES NO LIABILITY FOR CUSTOMERS’ PRODUCT DESIGN OR APPLICATIONS.•Product is intended for use in general electronics applications (e.g., computers, personal equipment, office equipment, measuring equipment, industrial robots and home electronics appliances) or for specific applications as expressly stated in this document.Product is neither intended nor warranted for use in equipment or systems that require extraordinarily high levels of quality and/or reliability and/or a malfunction or failure of which may cause loss of human life, bodily injury, serious property damage or serious public impact (“Unintended Use”). Unintended Use includes, without limitation, equipment used in nuclear facilities, equipment used in the aerospace industry, medical equipment, equipment used for automobiles, trains, ships and other transportation, traffic signaling equipment, equipment used to control combustions or explosions, safety devices, elevators and escalators, devices related to electric power, and equipment used in finance-related fields. Do not use Product for Unintended Use unless specifically permitted in this document.•Do not disassemble, analyze, reverse-engineer, alter, modify, translate or copy Product, whether in whole or in part.•Product shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable laws or regulations.•The information contained herein is presented only as guidance for Product use. No responsibility is assumed by TOSHIBA for any infringement of patents or any other intellectual property rights of third parties that may result from the use of Product. No license to any intellectual property right is granted by this document, whether express or implied, by estoppel or otherwise.•ABSENT A WRITTEN SIGNED AGREEMENT, EXCEPT AS PROVIDED IN THE RELEVANT TERMS AND CONDITIONS OF SALE FOR PRODUCT, AND TO THE MAXIMUM EXTENT ALLOWABLE BY LAW, TOSHIBA (1) ASSUMES NO LIABILITYWHATSOEVER, INCLUDING WITHOUT LIMITATION, INDIRECT, CONSEQUENTIAL, SPECIAL, OR INCIDENTAL DAMAGES OR LOSS, INCLUDING WITHOUT LIMITATION, LOSS OF PROFITS, LOSS OF OPPORTUNITIES, BUSINESS INTERRUPTION AND LOSS OF DATA, AND (2) DISCLAIMS ANY AND ALL EXPRESS OR IMPLIED WARRANTIES AND CONDITIONS RELATED TO SALE, USE OF PRODUCT, OR INFORMATION, INCLUDING WARRANTIES OR CONDITIONS OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, ACCURACY OF INFORMATION, OR NONINFRINGEMENT.•Do not use or otherwise make available Product or related software or technology for any military purposes, including without limitation, for the design, development, use, stockpiling or manufacturing of nuclear, chemical, or biological weapons or missile technology products (mass destruction weapons). Product and related software and technology may be controlled under the Japanese Foreign Exchange and Foreign Trade Law and the U.S. Export Administration Regulations. Export and re-export of Product or related software or technology are strictly prohibited except in compliance with all applicable export laws and regulations. •Please contact your TOSHIBA sales representative for details as to environmental matters such as the RoHS compatibility of Product.Please use Product in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. TOSHIBA assumes no liability for damages or losses occurring as a result of noncompliance with applicable laws and regulations.。

74LVC245DB中文资料

VI/O

DC input voltagC output voltage range

0

5.5

0

VCC

0

VCC

Tamb

operating ambient temperature range in free air

−40

+85

tr, tf

input rise and fall times

or any other conditions beyond

2. The input and output voltage ratings may be exceeded if the input and output current ratings are observed.

April 1994

3

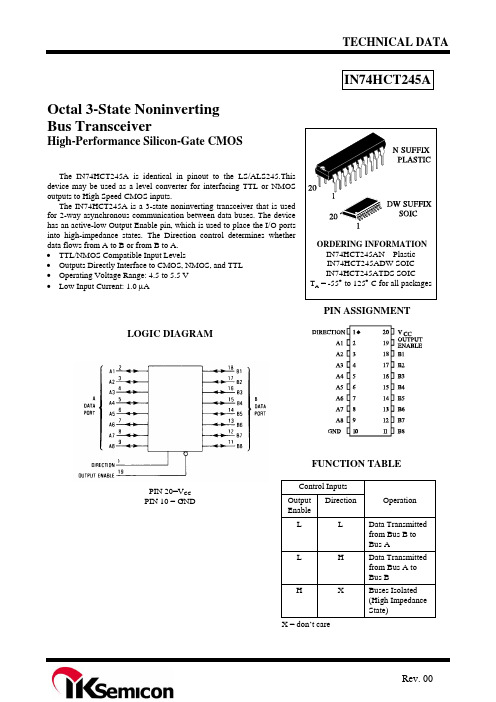

FUNCTION TABLE

INPUTS INPUTS/OUTPUT

OE DIR

An

L

L A=B

Bn inputs

L H inputs B = A

HX

Z

Z

H = HIGH voltage level L = LOW voltage level X = don’t care Z = high impedance OFF-state

The 74LVC245 is an octal transceiver featuring non-inverting 3-state bus compatible outputs in both send and receive directions. The ’245’ features an output enable (OE) input for easy cascading and a send/receive (DIR) input for direction control. OE controls the outputs so that the buses are effectively isolated. The ’245’ is identical to the ’640’ but has true (non-inverting) outputs.

74xx245中文资料

74

Vcc=最大

VI=5.5V VI=7V

Vcc=最大,VIH=2.7V

IIL输入低电平电流

Vcc=最大,VIL=0.4V

IOS输出短路电流 IOZH输出高阻态时高

电平电流 IOZL输出高阻态时低

电平电流

Icc 电源电流

Vcc=最大

Vcc=最大,VIH=2V VIL=最大,VO=2.7V Vcc=最大,VIH=2V,VIL=最大

5

5.5

4.75

5

5.25

2

0.7 0.8 -12 -15

12 24

单位 V V V mA mA

参

数

tPLH输出由低到高传输延迟时间 tPHL输出由高到低传输延迟时间 tPZH输出由高阻态到高允许时间 tPZL输出由高阻态到低允许时间 tPHZ输出由高到高阻态禁止时间 tPLZ输出由低到高阻态禁止时间

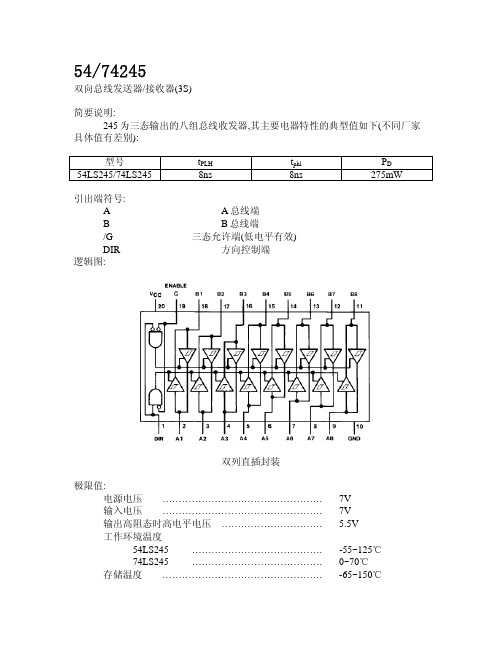

54/74245

双向总线发送器/接收器(3S)

简要说明: 245 为三态输出的八组总线收发器,其主要电器特性的典型值如下(不同厂家

具体值有差别):

型号

tPLH

54LS245/74LS245

8ns

tphl

PD

8ns

275mW

引出端符号: A B /G DIR

逻辑图:

A 总线端 B 总线端 三态允许端(低电平有效) 方向控制端

测试条件

Vcc =5V CL=45pF RL=667 Ω

Vcc=5V CL=5pF RL=90 Ω

静态特性(TA 为工作环境温度范围)

LS245 最大

12 12 40 40 25 25

单位

ns ns ns ns ns nsቤተ መጻሕፍቲ ባይዱ

74LVC245AQ资料

A1 2

3

A2 A3 4

A4 5

6

A5

7

A6A7 8A8 9The IDT logo is a registered trademark of Integrated Device Technology, Inc.

INDUSTRIAL TEMPERATURE RANGE

1

© 2006 Integrated Device Technology, Inc.

元器件交易网

IDT74LVC245A 3.3V CMOS OCTAL BUS TRANSCEIVER WITH 3-STATE OUTPUTS

3.3V CMOS OCTAL BUS TRANSCEIVER WITH 3-STATE OUTPUTS AND 5 VOLT TOLERANT I/O

2

元器件交易网

IDT74LVC245A 3.3V CMOS OCTAL BUS TRANSCEIVER WITH 3-STATE OUTPUTS

INDUSTRIAL TEMPERATURE RANGE

DC ELECTRICAL CHARACTERISTICS OVER OPERATING RANGE

PIN CONFIGURATION

DIR 1

A1

2

A2

3

A3

4

A4

5

A5

6

20

VCC

19 OE

18

B1

17

B2

16

B3

15

B4

ABSOLUTE MAXIMUM RATINGS(1)

Symbol

Description

Max

Unit

HD74LVC245AT中文资料

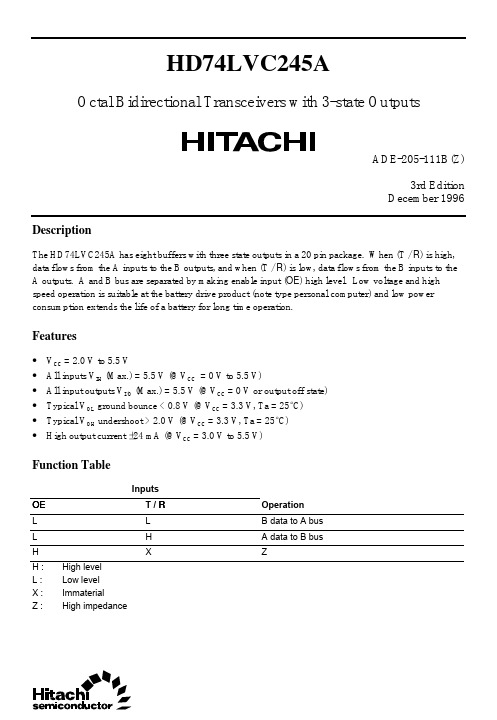

HD74LVC245AOctal Bidirectional Transceivers with 3-state OutputsADE-205-111B(Z)3rd EditionDecember 1996 DescriptionThe HD74LVC245A has eight buffers with three state outputs in a 20 pin package. When (T / R) is high, data flows from the A inputs to the B outputs, and when (T / R) is low, data flows from the B inputs to the A outputs. A and B bus are separated by making enable input (OE) high level. Low voltage and high speed operation is suitable at the battery drive product (note type personal computer) and low power consumption extends the life of a battery for long time operation.Features•V CC = 2.0 V to 5.5 V•All inputs V IH (Max.) = 5.5 V (@V CC = 0 V to 5.5 V)•All input outputs V I/O (Max.) = 5.5 V (@V CC = 0 V or output off state)•Typical V OL ground bounce < 0.8 V (@V CC = 3.3 V, Ta = 25°C)•Typical V OH undershoot > 2.0 V (@V CC = 3.3 V, Ta = 25°C)•High output current ±24 mA (@V CC = 3.0 V to 5.5 V)Function TableInputsOE T / R OperationL L B data to A busL H A data to B busH X ZH :High levelL :Low levelX :ImmaterialZ :High impedanceHD74LVC245ARev.3, Dec. 1996, page 2 of 10Pin ArrangementAbsolute Maximum RatingsItemSymbol Ratings Unit ConditionsSupply voltage V CC –0.5 to 6.0V Input diode current I IK –50mA V I = –0.5 V Input voltage V I –0.5 to 6.0V T / R , OE Output diode current I OK –50mA V O = –0.5 V 50mA V O = V CC +0.5 V Input / output voltage V I/O –0.5 to V CC +0.5V Output "H" or "L"–0.5 to 6.0V Output "Z" or V CC :OFF Output current I O±50mA V CC , GND current / pin I CC or I GND 100mA Storage temperatureTstg–65 to 150°CNote:The absolute maximum ratings are values which must not individually be exceeded, and furthermore,no two of which may be realized at the same time.HD74LVC245ARev.3, Dec. 1996, page 3 of 10Recommended Operating ConditionsItemSymbol Ratings Unit Conditions Supply voltage V CC 1.5 to 5.5V Data retention 2.0 to 5.5V At operation Input / output voltageV I 0 to 5.5V T / R , OE V I/O0 to V CC V Output "H" or "L"0 to 5.5V Output "Z" or V CC :OFFOperating temperature Ta –40 to 85°C Output currentI OH –12mA V CC = 2.7 V –24*2mA V CC = 3.0 V to 5.5 V I OL12mA V CC = 2.7 V 24*2mA V CC = 3.0 V to 5.5 V Input rise / fall time *1t r , t f10ns/VNotes: 1.This item guarantees maximum limit when one input switches.Waveform : Refer to test circuit of switching characteristics.2.duty cycle ≤ 50%HD74LVC245ARev.3, Dec. 1996, page 4 of 10Electrical CharacteristicsTa = –40 to 85°CItem Symbol V CC (V)MinMax Unit Test ConditionsInput voltageV IH 2.7 to 3.6 2.0—V 4.5 to 5.5V CC ×0.7—V V IL2.7 to3.6—0.8V 4.5 to 5.5—V CC ×0.3V Output voltageV OH2.7 to 5.5V CC –0.2—V I OH = –100 µA 2.7 2.2—V I OH = –12 mA 3.0 2.4—V 3.0 2.2—V I OH = –24 mA 4.53.8—V V OL2.7 to 5.5—0.2V I OL = 100 µA 2.7—0.4V I OL = 12 mA 3.0—0.55V I OL = 24 mA 4.5—0.55V Input currentI IN 0 to 5.5—±5.0µA V IN = 5.5 V or GND Off state output currentI OZ2.7 to 5.5—±5.0µA V IN = V CC , GND V OUT = 5.5 V or GNDOutput leak currentI OFF—20µA V IN / V OUT = 5.5 V Quiescent supply current I CC2.7 to3.6—±10µA V IN / V OUT = 3.6 to 5.5 V 2.7 to 5.5—10µA V IN = V OUT or GND∆I CC3.0 to 3.6—500µAV IN = one input at (V CC –0.6)V,other inputs at V CC or GNDHD74LVC245ARev.3, Dec. 1996, page 5 of 10Switching CharacteristicsTa = –40 to 85°CItemSymbol V CC (V)Min Typ Max Unit From (Input)To (Output)Propagation delay timet PLH 2.7——8.0ns A or BB or At PHL3.3±0.3 1.5—7.0ns 5.0±0.5—— 5.5ns Output enable timet ZH 2.7——9.5ns OEA or Bt ZL3.3±0.3 1.5—8.5ns 5.0±0.5——7.0ns Output disable timet ZH 2.7——8.5ns OEA or Bt LZ3.3±0.3 1.5—7.5ns 5.0±0.5—— 6.5ns Between outut pins skew *1t OSLH2.7———ns t OSHL3.3±0.3—— 1.0ns 5.0±0.5—— 1.0ns Input capacitance C IN 2.7— 3.0—pF Output capacitance C O2.7—15.0—pFNote:1.This parameter is characterized but not tested.tos LH = | t PLHm - t PLHn |, tos HL = | t PHLm - t PHLn |HD74LVC245ATest CircuitWaveforms – 1Rev.3, Dec. 1996, page 6 of 10HD74LVC245A Waveforms – 2Rev.3, Dec. 1996, page 7 of 10HD74LVC245A Package DimensionsRev.3, Dec. 1996, page 8 of 10HD74LVC245ARev.3, Dec. 1996, page 9 of 10HD74LVC245ARev.3, Dec. 1996, page 10 of 10Disclaimer1.Hitachi neither warrants nor grants licenses of any rights of Hitachi’s or any third party’s patent,copyright, trademark, or other intellectual property rights for information contained in this document.Hitachi bears no responsibility for problems that may arise with third party’s rights, including intellectual property rights, in connection with use of the information contained in this document.2.Products and product specifications may be subject to change without notice. Confirm that you have received the latest product standards or specifications before final design, purchase or use.3.Hitachi makes every attempt to ensure that its products are of high quality and reliability. However,contact Hitachi’s sales office before using the product in an application that demands especially high quality and reliability or where its failure or malfunction may directly threaten human life or cause risk of bodily injury, such as aerospace, aeronautics, nuclear power, combustion control, transportation,traffic, safety equipment or medical equipment for life support.4.Design your application so that the product is used within the ranges guaranteed by Hitachi particularly for maximum rating, operating supply voltage range, heat radiation characteristics, installationconditions and other characteristics. Hitachi bears no responsibility for failure or damage when used beyond the guaranteed ranges. Even within the guaranteed ranges, consider normally foreseeable failure rates or failure modes in semiconductor devices and employ systemic measures such as fail-safes, so that the equipment incorporating Hitachi product does not cause bodily injury, fire or other consequential damage due to operation of the Hitachi product.5.This product is not designed to be radiation resistant.6.No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without written approval from Hitachi.7.Contact Hitachi’s sales office for any questions regarding this document or Hitachi semiconductor products.Sales OfficesHitachi, Ltd.Semiconductor & Integrated Circuits.Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan Tel: Tokyo (03) 3270-2111 Fax: (03) 3270-5109Copyright Hitachi, Ltd., 2000. All rights reserved. Printed in Japan.Hitachi Asia Ltd. Hitachi Tower16 Collyer Quay #20-00, Singapore 049318Tel : <65>-538-6533/538-8577 Fax : <65>-538-6933/538-3877URL : .sg URLNorthAmerica : /Europe : /hel/ecg Asia : Japan : http://www.hitachi.co.jp/Sicd/indx.htmHitachi Asia Ltd.(Taipei Branch Office)4/F, No. 167, Tun Hwa North Road, Hung-Kuo Building, Taipei (105), Taiwan Tel : <886>-(2)-2718-3666 Fax : <886>-(2)-2718-8180 Telex : 23222 HAS-TPURL : Hitachi Asia (Hong Kong) Ltd.Group III (Electronic Components) 7/F., North Tower, World Finance Centre,Harbour City, Canton Road Tsim Sha Tsui, Kowloon, Hong KongTel : <852>-(2)-735-9218 Fax : <852>-(2)-730-0281URL : Hitachi Europe Ltd.Electronic Components Group.Whitebrook ParkLower Cookham Road MaidenheadBerkshire SL6 8YA, United Kingdom Tel: <44> (1628) 585000Fax: <44> (1628) 585160Hitachi Europe GmbHElectronic Components Group Dornacher Stra ße 3D-85622 Feldkirchen, Munich GermanyTel: <49> (89) 9 9180-0Fax: <49> (89) 9 29 30 00Hitachi Semiconductor (America) Inc.179 East Tasman Drive,San Jose,CA 95134 Tel: <1> (408) 433-1990Fax: <1>(408) 433-0223For further information write to:Colophon 2.0。

74LVC245AD原版数据手册.pdf-EasyDatasheet

Parameter supply voltage input clamping current input voltage output clamping current output voltage output current supply current ground current storage temperature total power dissipation

3 of 18

NXP Semiconductors

74LVC245A; 74LVCH245A

Octal bus transceiver; 3-state

6. Functional description

Table 3. Inputs OE L L H

[1]

Function selection[1] Inputs/outputs DIR L H X An An = Bn inputs Z Bn inputs Bn = An Z

terminal 1 index area 20 VCC 19 OE 18 B0 17 B1 16 B2 15 B3 14 B4 GND(1) GND 10 B7 11 13 B5 12 B6 DIR 2 3 4 5 6 7 8 9 1 A0 A1 DIR A0 A1 A2 A3 A4 A5 A6 A7 1 2 3 4 5 6 7 8 9 20 VCC 19 OE 18 B0 17 B1 16 B2 15 B3 14 B4 13 B5 12 B6 11 B7

0.5 0.5 100 65

Tamb = 40 C to +125 C

[3]

-

The minimum input voltage ratings may be exceeded if the input current ratings are observed. The output voltage ratings may be exceeded if the output current ratings are observed. For SO20 packages: above 70 C derate linearly with 8 mW/K. For (T)SSOP20 packages: above 60 C derate linearly with 5.5 mW/K. For DHVQFN20 and DHXQFN20 packages: above 60 C derate linearly with 4.5 mW/K.

SN74LVT245BPWR中文资料

PACKAGING INFORMATIONOrderable Device Status (1)Package Type Package Drawing Pins Package Qty Eco Plan (2)Lead/Ball FinishMSL Peak Temp (3)SN74LVT245BDBLE OBSOLETE SSOP DB 20TBDCall TI Call TISN74LVT245BDBR ACTIVE SSOP DB 202000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LVT245BDBRE4ACTIVE SSOPDB 202000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LVT245BDW ACTIVE SOIC DW 2025Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LVT245BDWE4ACTIVE SOIC DW 2025Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LVT245BDWG4ACTIVE SOIC DW 2025Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LVT245BDWR ACTIVE SOIC DW 202000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LVT245BDWRE4ACTIVE SOIC DW 202000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LVT245BDWRG4ACTIVE SOIC DW 202000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LVT245BGQNRACTIVEBGA MI CROSTA R JUNI ORGQN201000TBDSNPBLevel-1-240C-UNLIMSN74LVT245BNSR ACTIVE SO NS 202000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LVT245BNSRE4ACTIVE SO NS 202000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LVT245BPW ACTIVE TSSOP PW 2070Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LVT245BPWE4ACTIVE TSSOP PW 2070Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LVT245BPWLE OBSOLETE TSSOP PW 20TBDCall TI Call TISN74LVT245BPWR ACTIVE TSSOP PW 202000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LVT245BPWRE4ACTIVE TSSOP PW 202000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LVT245BPWRG4ACTIVE TSSOP PW 202000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LVT245BRGYR ACTIVE QFN RGY 201000Green (RoHS &no Sb/Br)CU NIPDAU Level-2-260C-1YEAR SN74LVT245BRGYRG4ACTIVE QFN RGY 201000Green (RoHS &no Sb/Br)CU NIPDAU Level-2-260C-1YEAR SN74LVT245BZQNRACTIVEBGA MI CROSTA R JUNI ORZQN201000Green (RoHS &no Sb/Br)SNAGCULevel-1-260C-UNLIM(1)The marketing status values are defined as follows:ACTIVE:Product device recommended for new designs.LIFEBUY:TI has announced that the device will be discontinued,and a lifetime-buy period is in effect.NRND:Not recommended for new designs.Device is in production to support existing customers,but TI does not recommend using this part in a new design.PREVIEW:Device has been announced but is not in production.Samples may or may not be available.6-Dec-2006OBSOLETE:TI has discontinued the production of the device.(2)Eco Plan -The planned eco-friendly classification:Pb-Free (RoHS),Pb-Free (RoHS Exempt),or Green (RoHS &no Sb/Br)-please check /productcontent for the latest availability information and additional product content details.TBD:The Pb-Free/Green conversion plan has not been defined.Pb-Free (RoHS):TI's terms "Lead-Free"or "Pb-Free"mean semiconductor products that are compatible with the current RoHS requirements for all 6substances,including the requirement that lead not exceed 0.1%by weight in homogeneous materials.Where designed to be soldered at high temperatures,TI Pb-Free products are suitable for use in specified lead-free processes.Pb-Free (RoHS Exempt):This component has a RoHS exemption for either 1)lead-based flip-chip solder bumps used between the die and package,or 2)lead-based die adhesive used between the die and leadframe.The component is otherwise considered Pb-Free (RoHS compatible)as defined above.Green (RoHS &no Sb/Br):TI defines "Green"to mean Pb-Free (RoHS compatible),and free of Bromine (Br)and Antimony (Sb)based flame retardants (Br or Sb do not exceed 0.1%by weight in homogeneous material)(3)MSL,Peak Temp.--The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications,and peak solder temperature.Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is provided.TI bases its knowledge and belief on information provided by third parties,and makes no representation or warranty as to the accuracy of such information.Efforts are underway to better integrate information from third parties.TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals.TI and TI suppliers consider certain information to be proprietary,and thus CAS numbers and other limited information may not be available for release.In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s)at issue in this document sold by TI to Customer on an annualbasis.6-Dec-2006IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard warranty. T esting and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. T o minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements. Following are URLs where you can obtain information on other Texas Instruments products and application solutions:Products ApplicationsAmplifiers Audio /audioData Converters Automotive /automotiveDSP Broadband /broadbandInterface Digital Control /digitalcontrolLogic Military /militaryPower Mgmt Optical Networking /opticalnetwork Microcontrollers Security /securityLow Power Wireless /lpw Telephony /telephonyVideo & Imaging /videoWireless /wirelessMailing Address:Texas InstrumentsPost Office Box 655303 Dallas, Texas 75265Copyright 2006, Texas Instruments Incorporated。

SN74LVCH245APWRG4资料