基于DSP+FPGA的高速信号采集与处理系统的信号完整性分析

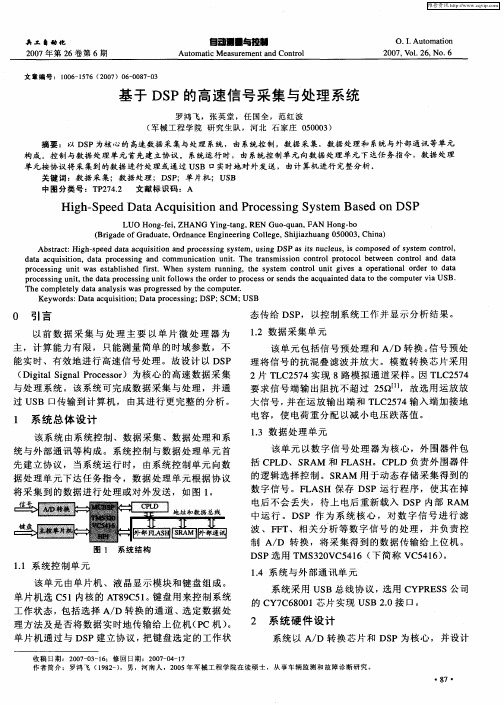

基于DSP的高速信号采集与处理系统

( i t inl rc s r D g a Sg a Poes )为核心 的高速 数据采集 il o 与 处 理系 统 。该 系 统 可 完 成 数 据 采 集 与处 理 ,并 通

中图分 类号 :T 2 42 文献 标 识码 :A P 7 .

H i h— pe d D aaAc u sto nd Pr c s i g S e t q i ii n a o e sng Syse s d o SP t m Ba e n D

LUO n — e , Ho g f i ZHANG n —a g, Yi g t n REN o q a , AN n — o Gu — u n F Ho g b

( ia eo rd ae Orn n eE gn eigCol e S ia h a g0 0 0 , ia Br d f a u t, d a c n ie r l g , hj z u n 5 0 3 Chn ) g G n e i

Ab ta t Hi h s e d d t c u s t n a d p o e s n y tm ,u i g DSP a t u l u , sc m p s d o y t m o to , s r c : g — p e a a a q i i o n r c s i g s se i sn sis n c e s i o o e fs se c nr l d t c u sto .d t r c s i g a o mu i a i n un t h r n mi so o to r t c l b t e o to n a a a a a q iii n a a p o e sn nd c m n c to i.T e ta s s i n c n r l p o o o e we n c n r l a d d t p o e sn n t wa s a ls e is .W h n s s e r n i g h y t m on r l u i g v s a o e a i a r e o d t r c si g u i s e t b ih d fr t e y t m u n n ,t e s se c to n t i e p r t on l o d r t a a p o e sn n t t e d t r c s i g u i f l wst e o d rt r c s rs n st e a q a n e a at h o p t rv a US r c s i g u i, h a ap o e sn n t o l o h r e o p o e so e d h c u i t d d t o t e c m u e i B. Th o e c mp e e y d t n l i sp o r s e y t e c m p t r l t l a a a aysswa r g e s d b h o ue. Ke wo d : t c u sto ; t r c s i g; y r s Da a a q iii n Da a p o e s n DS S P; CM ; US B

基于DSP_FPGA的高速数字信号处理平台

术,该平台还具有一定的开放性和可

示意图与图2相似,只是核电压不同。

程序与数据存储器 F L A S H 采用 扩展性,可以很好地满足设计的完善、

由超大规模FPGA芯片和高速的DSP芯 Intel公司的E28F320,其存储容量为 功能的扩充及程序的更改。

片组成系统的核心,是为了发挥两者 32Mbit。由 DSP 的供电芯片TPS70348

图2 DSP芯片的供电示意图

表 1 FPGA 芯片与 DSP 芯片的比较

F P G A 芯片

编程方式

V H D L 、A H D L 语言及图形编程等,

实现容易

资源重复利用性

通过外部处理器动态配置

硬件资源结构

可实现并行的乘法器/加法器操作

处理速度

并行运算速度快,只受硬件结构限制

适合的信号处理运算 高速并行处理

的优势。FPGA 芯片与 DSP 芯片相比, 为其一起供电,TPS70348芯片的复位

系统的软件设计流程

由于其结构上的优势,FPGA芯片更适 信号 /RESET为 FLASH 和 DSP的共同复

本文设计的平台通过动态配置可

w w w . e e p w . c o m . c n 电子产品世界 2004.10 /下半月 91

式中:SNR为输出信号的信噪比; B 为比特分辨数,即A/D 的转换位数; 为采样速率;输入模拟信号的最高频

理技术已在通信、信息、电子、自动控

总体硬件框架

制、航天及军事等领域中得到广泛应

图1为本文要介绍

用。

的高速数字信号处理平

以现代通信理论为基础,以数字 台的硬件框图,主要包

信号处理为核心的软件无线电技术是 括五个功能块:高速A/

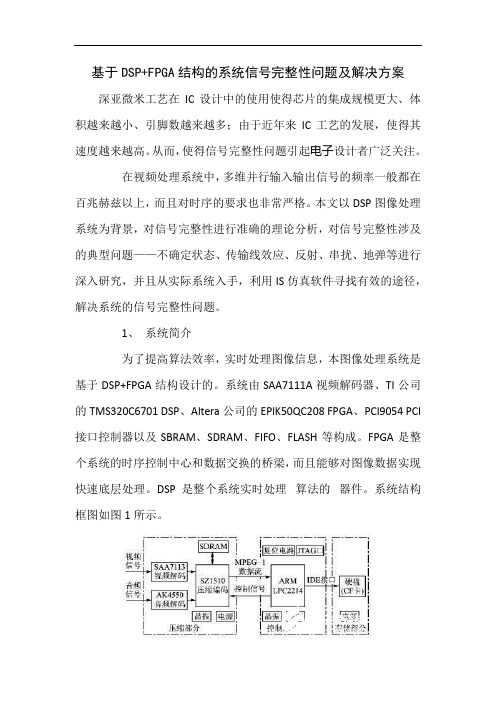

基于DSP+FPGA结构的系统信号完整性问题及解决方案

基于DSP+FPGA结构的系统信号完整性问题及解决方案深亚微米工艺在IC设计中的使用使得芯片的集成规模更大、体积越来越小、引脚数越来越多;由于近年来IC工艺的发展,使得其速度越来越高。

从而,使得信号完整性问题引起电子设计者广泛关注。

在视频处理系统中,多维并行输入输出信号的频率一般都在百兆赫兹以上,而且对时序的要求也非常严格。

本文以DSP图像处理系统为背景,对信号完整性进行准确的理论分析,对信号完整性涉及的典型问题——不确定状态、传输线效应、反射、串扰、地弹等进行深入研究,并且从实际系统入手,利用IS仿真软件寻找有效的途径,解决系统的信号完整性问题。

1、系统简介为了提高算法效率,实时处理图像信息,本图像处理系统是基于DSP+FPGA结构设计的。

系统由SAA7111A视频解码器、TI公司的TMS320C6701 DSP、Altera公司的EPlK50QC208 FPGA、PCI9054 PCI 接口控制器以及SBRAM、SDRAM、FIFO、FLASH等构成。

FPGA是整个系统的时序控制中心和数据交换的桥梁,而且能够对图像数据实现快速底层处理。

DSP是整个系统实时处理算法的器件。

系统结构框图如图1所示。

在整个系统中,PCB电路板的面积仅为15cm×l5cm,系统时钟频率高达167MHz,时钟沿时间为0.6ns。

由于系统具有快斜率瞬变和极高的工作频率以及很大的电路密度,使得如何处理高速信号问题成为一个制约设计成功的关键因素。

2、系统中信号完整性问题及解决方案2.1 信号完整性问题产生机理原理框图信号的完整性是指信号通过物理电路传输后,信号接收端看到的波形与信号发送端发送的波形在容许的误差范围内保持一致,并且空间邻近的传输信号间的相互影响也在容许的范围之内。

因此,信号完整性分析的主要目标是保证高速数字信号可靠的传输。

实际信号总是存在电压的波动,如图2所示。

在A、B两点由于过冲和振铃的存在使信号振幅落入阴影部分的不确定区,可能会导致错误的逻辑电平发生。

基于FPGA和DSP的高速数据采集实时处理系统的设计

基于FPGA和DSP的高速数据采集实时处理系统的设计马秀娟;考丽;赵国良

【期刊名称】《电子器件》

【年(卷),期】2007(030)003

【摘要】为实现激光目标回波的快速捕获、检测及实时处理,提出一种

ADC+FPGA+DSP的数据采集与实时处理的设计.激光回波通过高速模数转换器(ADC)转换成数字信号,经FIFO乒乓高速缓存,然后再送到DSP进行实时处理.电路简单、可靠、实时性强,最高采样率达200 MHz,具有8 bit垂直分辨率,4 M×8位数据存储空间.该系统能准确实时地计算出目标距离、速度,适时预警,符合汽车防撞激光雷达中信号处理的要求.详细介绍了系统的设计方案及各主要组成模块.

【总页数】5页(P1009-1013)

【作者】马秀娟;考丽;赵国良

【作者单位】哈尔滨工程大学,哈尔滨,150001;哈尔滨工业大学,山东,威海,264209;哈尔滨工业大学,山东,威海,264209;哈尔滨工程大学,哈尔滨,150001

【正文语种】中文

【中图分类】TP274;TN919

【相关文献】

1.基于DSP和FPGA的高速数据采集处理系统 [J], 高迎慧;刘宾;王佳;尹菲

2.一种基于DSP+FPGA系统架构的雷达实时信号处理系统的设计与实现 [J], 韩涛;孙娟;刘汝猛;裘磊

3.基于FPGA+DSP实时图像采集处理系统设计 [J], 靖固;杨华宇

4.基于FPGA+DSP的高速视频实时处理系统设计 [J], 张小永

5.基于FPGA+DSP的高速视频实时处理系统设计 [J], 张小永

因版权原因,仅展示原文概要,查看原文内容请购买。

基于DSP+FPGA的实时信号采集系统设计与实现

基于DSP+FPGA的实时信号采集系统设计与实现周新淳【期刊名称】《计算机测量与控制》【年(卷),期】2017(025)008【摘要】为了提高对实时信号采集的准确性和无偏性,提出一种基于DSP+FPGA 的实时信号采集系统设计方案.系统采用4个换能器基阵并联组成信号采集阵列单元,对采集的原始信号通过模拟信号预处理机进行放大滤波处理,采用TMS32010DSP芯片作为信号处理器核心芯片实现实时信号采集和处理,包括信号频谱分析和目标信息模拟,由DSP控制D/A转换器进行数/模转换,通过FPGA实现数据存储,在PC机上实时显示采样数据和DSP处理结果;通过仿真实验进行性能测试,结果表明,该信号采集系统能有效实现实时信号采集和处理,抗干扰能力较强.%In order to improve the accuracy and bias of real-time signal acquisition,a real-time signal acquisition system based on DSP +-FPGA is proposed.The system adopts 4 transducer array to build parallel array signal acquisition unit,the original signal acquisition amplification filtering through analog signal pretreatment,using TMS32010DSP chip as the core of signal processor chip to realize real-time signal acquisition andprocessing,including the signal spectrum analysis and target information simulation,controlled by DSP D/A converter DAC,through the realization of FPGA data storage,real-time display on the PC and DSP sampling data processing results.The performance of the system is tested by simulation.The results show that the signal acquisition system caneffectively realize the real-time signal acquisition and processing,the anti-interference ability is strong.【总页数】4页(P210-213)【作者】周新淳【作者单位】宝鸡文理学院物理与光电技术学院,陕西宝鸡721016【正文语种】中文【中图分类】TN911【相关文献】1.基于DSP+FPGA的高速信号采集与处理系统的信号完整性分析 [J], 邱燕军;申功勋2.基于VPX的多DSP+FPGA红外图像处理系统设计与实现 [J], 祝树生;李晶;吕殿君;陈冉;仇公望3.基于DSP+FPGA多通道单端/差分信号采集系统 [J], 邓轲;范俊锋;吝莹4.基于DSP+FPGA的IRFPA实时图像数字处理系统设计与实现 [J], 何健;胡旭;李勃;洪建堂5.实时视频信号采集与处理系统设计与实现 [J], 李一鹏;张晓峰;张晔因版权原因,仅展示原文概要,查看原文内容请购买。

基于DSP的高速数据采集与处理系统

基于DSP的高速数据采集与处理系统摘要:提出了一种基于DSP的高速数据采集系统的设计方案,对其中高速A/D、高速缓存、DSP控制以及数据通讯接口等内容进行了讨论,提出了更为有效的同步控制方式。

该设计方案电路简单、可进行多通道扩展、具有一定的通用性。

关键词:DSP 高速A/D FIFO 异步串行通讯在电子测量中,常常需要对高速信号进行采集与处理。

例如,在光传感技术中,对光脉冲散射信号的测量;在雷达工程中,对电磁脉冲信号的测量等,就需要对高速信号进行采集与算是,而且对此类高速信号的测量,往往对数据采集与处理系统提出严格的要求。

本文设计并实现了一种基于DSP的高速数据采集与处理。

该设计方案电路简单、可靠性好、具有一定的通用性、可以进行多通道扩展。

系统主要包括高速A/D、高速缓存、DSP处理器、通讯接口四个部分,其结构示意图如图1所示。

For personal use only in study and research; not for commercial use1 同步与过程控制在通常的数据采集系统中,测量过程是通过对A/D变换器的控制来实现的。

但对于一个伉速采集系统而言,这种方法有局限性。

因为高速A/D建立稳定的工作状态需要相当长时间,频繁的改变A/D的工作状态会影响测量的精度,严重时会造成信号的失真。

在本设计方案中,同步命令并不直接作用于高速A/D。

自通电时起,A/D和时钟电路始终处于工作状态,同步命令通过对高速FIFO的写入端的控制,即允许或禁止对FIFO写入,实现对采样数据的取舍。

与A/D相比,高速FIFO的写有效时间为 3ns,对同步和过程控制更为有利。

For personal use only in study and research; not for commercial use一次完整的测量过程是从DSP发出同步命令开始的。

同步命令一方面触发发射机工作,另一方面允许对FIFO写入,对采样的数据进行存储。

高速DSP数据采集的信号完整性问题(精)

高速DSP数据采集的信号完整性问题摘要:深入研究高速数字电路设计中的信号完整性问题;分析电路中破坏信号完整性的原因;结合一个实际的DSP数据采集系统、阐述实现信号完整性的具体方案。

关键词:信号完整性ADSP21161 数据采集噪声控制引言当前,日渐精细的半导体工艺使得晶体管尺寸越来越小,因而器件的信号跳变也就越来越快,高速数字系统的快斜率瞬变和极高的工作频率,以及很大的电路密集度,导致高速数字电路系统设计领域的信号完整性问题以及电磁兼容性问题日趋严重。

破坏了信号完整性将直接导致信号失真、定时错误,以及产生不正确数据、地址和控制信号,从而千万系统误工作甚至导致系统崩溃。

因此,信号完整性问题已经越来越引起高速数字电路设计人员的关注。

1信号完整性问题产生的机理信号完整性的问题主要包括传输线效应,如反射、时延、振铃、信号的过程与下冲以及信号之间的串扰等,涉及传输线上的信号质量及信号定时的准确性。

良好的信号质量是确保稳定时序的关键。

由于反射和串扰造成的信号质量问题都很可能带来时序的偏移和紊乱。

例如,串扰会影响信号的传播延迟,导致在时钟的上升沿或下降沿处采不到准确的逻辑;反射会造成数据信号在逻辑门限附近波动,从而影响信号上升沿或下降沿变化;时钟走线的干扰会造成一定的时钟偏移。

信号完整性分析与设计是最重要的高速PCB板级和系统级分析与设计手段,在硬件电路设计中扮演着越来越重要的作用。

一个数字系统能否正确工作,其关键在于信号定时是否准确。

信号定时和信号在传输线上的传输延迟与信号波形的损坏程度密切相关。

信号传输延迟和波形破损的原因复杂多样,但主要是以下三种原因破坏了信号的完整性。

①电源、地址噪声。

它主要是源自于电源路径以及IC封装所造成的分布电感的存在。

当系统的速度愈快,同时转换逻辑状态的I/O引脚个数愈多时,会产生较大的瞬态电流,导致电源线上和地线睥电压波动和变化,这就是平进所说的接地反弹。

接地反弹是数字系统的几个主要噪声来源之一。

基于DSP和FPGA的高速数据采集处理系统

125105,China)

on

Abstract:In order to acquire the data accurately and rapidly,a multi—channel real-time acquisition system based programmable gates

DSP,field controlled

words:data

a

prospect of application.

acquisition;DSP;FPGA;ADS8364

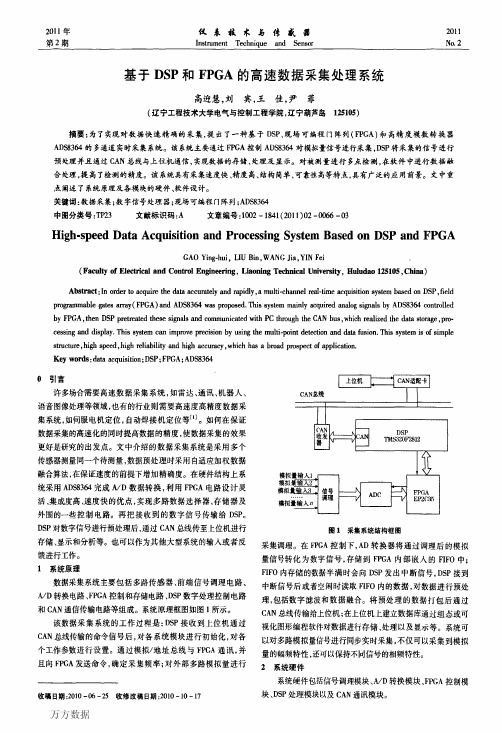

0引言

许多场合需要高速数据采集系统,如雷达、通讯、机器人、

语音图像处理等领域,也有的行业则需要高速度高精度数据采 集系统,如伺服电机定位,自动焊接机定位等…。如何在保证 数据采集的高速化的同时提高数据的精度,使数据采集的效果 更好是研究的出发点。文中介绍的数据采集系统是采用多个 传感器测量同一个待测量,数据预处理时采用自适应加权数据 融合算法,在保证速度的前提下增加精确度。在硬件结构上系 统采用ADS8364完成A/D数据转换,利用FPGA电路设计灵 活、集成度高、速度快的优点,实现多路数据选择器、存储器及 外围的一些控制电路。再把接收到的数字信号传输给DSP。 DSP对数字信号进行预处理后,通过CAN总线传至上位机进行 存储、显示和分析等。也可以作为其他大型系统的输入或者反 馈进行工作。 1系统原理 数据采集系统主要包括多路传感器、前端信号调理电路、

V

CAN通信模块设计 系统可利用TMS320F2812 DSP内部自带的CAN控制器,

无需另外添加。只需另加一个CAN收发器就能组成CAN总线 网络,选用PCA82C250,该器件对总线提供差动发送能力并对 CAN控制器提供差动接收能力,是使用最广泛的CAN收发器。 CAN总线通讯模块主要作用是将上位机的命令传输给DSP,并 且将采集到的数据传输给上位机,用于数据存储和处理。 3系统软件设计 系统软件采用模块化、结构化的编程方法。包括数据采集 模块、DSP处理模块、CAN总线接口的通讯模块。 3.1数据采集模块软件设计 数据采集模块主要是FPGA控制,FPGA内部编程有时钟 脉冲产生器、控制器、FIFO存储器等设计。在软件设计中可设 置FIFO的参数、各种标志和控制位,如深度、宽度,空满、半满 全满、可编程满等标志位,写使能、读使能等控制位,以便实现 与DSP的逻辑接口H1。当接到DSP信号后,初始化各个子程 序模块和ADS8364,包括AD采样的速率、参考电压的设定、时 钟的初值和分频比以及控制器的初值。 初始化完成后,FPGA输出时钟信号给AD8364并且提供 HOLD保持信号,启动转换。等待AD8364转换完成后产生中断

基于FPGA的高速数据采集及分析

基于FPGA的高速数据采集及分析FPGA(现场可编程门阵列)是一种基于硬件逻辑配置的可编程电路芯片,具有高度的灵活性和性能优势,被广泛应用于高速数据采集及分析领域。

在本文中,我们将介绍FPGA在高速数据采集及分析中的优势和应用。

首先,FPGA具备高速采集能力。

由于FPGA的硬件并行性和高度可定制的特性,它可以同时处理多个数据流和通道,实现高速的数据采集。

FPGA内置的时钟管理模块和高速IO接口可以实现对高速数据的快速采样和传输,使得FPGA成为高速数据采集系统中不可或缺的核心组件。

其次,FPGA具备实时的数据处理能力。

FPGA内部的硬件逻辑可以根据实际需求进行定制,实现针对特定应用场景的数据处理算法。

与传统的软件算法相比,FPGA可以并行处理大量的数据,实现实时的数据处理和分析。

这对于需要快速响应的实时应用非常重要,例如雷达信号处理、医学图像处理等。

此外,FPGA还具有低延迟的特性。

FPGA采用硬件描述语言进行编程,可以直接在硬件层面上实现数据处理算法,避免了软件层面的中间环节和延迟。

由于硬件级别的并行处理能力,FPGA可以实时响应来自外部传感器的数据,减少数据传输和处理的延迟时间,提高系统的实时性。

在高速数据采集及分析应用中,FPGA可以用于数据预处理、数据压缩和数据加速等方面。

在数据预处理方面,FPGA可以进行数据的滤波、采样率变换和数据校正等操作,提高数据质量和可靠性。

在数据压缩方面,FPGA可以采用各种算法(如哈夫曼编码、小波变换等)进行数据压缩,减少数据存储和传输的成本。

在数据加速方面,FPGA可以进行并行计算和加速算法的硬件实现,提高数据处理的速度和效率。

除了上述应用,FPGA在高速数据采集及分析领域还可以用于实时图像处理、机器学习加速和高性能计算等方面。

例如,FPGA可以用于实时视频图像的处理和分析,实现目标检测、跟踪和识别等功能。

同时,FPGA可以配置深度学习算法进行机器学习任务的加速,提高算法的执行效率。

基于FPGA的高速数据采集与处理系统研究

基于FPGA的高速数据采集与处理系统研究近年来,随着科技的不断发展和进步,以及信息化时代的到来,传统的数据采集与处理方式已经无法满足日益增长的数据处理需求,而基于FPGA的高速数据采集与处理系统成为了一种重要的选择。

本文将从以下几个方面探讨基于FPGA的高速数据采集与处理系统的研究。

一、FPGA的基本概念与特点FPGA全称为Field Programmable Gate Array,即现场可编程门阵列。

它是一种可编程逻辑器件,具有灵活性高、可重复编程、性能优异等特点。

FPGA的基本结构由可编程逻辑单元、可编程连线资源和I/O单元组成。

其中,可编程逻辑单元用于实现逻辑运算,可编程连线资源用于连接不同逻辑单元,I/O单元则用于与外部设备进行数据交互。

FPGA的工作原理是通过将Verilog或VHDL等高级语言代码编译成二进制文件,然后通过下载到FPGA芯片中实现功能。

FPGA具有灵活性高、可重复编程、性能优异等特点,如在数据采集和处理中,由于采集数据来源的差异性和复杂性,需要对采集和处理过程进行实时控制,使用FPGA可实现强大的实时控制能力,能够将数据采集与处理相结合,达到高效、稳定和可靠的数据处理效果。

二、基于FPGA的高速数据采集采集数据是数据处理的第一步,准确且高效的数据采集对于后续的数据处理具有至关重要的意义。

在基于FPGA的高速数据采集系统中,通常采用DMA(Direct Memory Access)方式实现高速数据传输,以便实现高效的数据采集。

DMA是一种数据传输方式,其不需要CPU的介入,直接将数据从外部设备读写到内存中,从而有效提高数据采集速度和效率。

在基于FPGA的数据采集系统中,通常在FPGA外加一块高速缓存,通过DMA方式,在缓存区内进行前端数据的处理和分包,然后再通过FPGA与下一段处理单元进行数据交互。

三、基于FPGA的高速数据处理基于FPGA的高速数据处理是本文的重点。

数据处理是对采集到的数据进行计算、分类、过滤、压缩等处理操作,直接决定了数据处理的质量和效率。

基于DSP和FPGA的高速数据采集处理系统_高迎慧

作为控制模块,FPGA 接收到 DSP 的转换命令后,控制 A / D 转

换模块进行数据采集。ADC 控制模块利用 Verilog HDL 语言进

行描述,再利用 C 语言编写用于描述控制寄存器的头文件。将

控制模块 Verilog HDL 文件和寄存器头文件利用 SOPC Builder

对其封装成一个 IP 核。作为存储模块,利用 FPGA 内部丰富的

路复用应用。根据其放大倍数公式

G

=

1

+

49. 4 RG

K,可

确

定

选

取

一个 250 Ω 的电阻即可使得放大输出电压在 0 ~ 5 V 之间。为

了 保 证 输 入 信 号 的 变 换 精 度,这 里 应 选 择 温 漂 较 小 的 精 密 电

阻。经 AD620 放大后需加入低通滤波来消除高频干扰成分。

2. 2 A / D 转换模块设计

接收上位机的命令。以模拟地址 / 数据总线的方式与 FPGA 通 信,控制数据采集和对采集到的数据进行预处理( 包括数字滤 波和数据融合) 。这里选用 32 位定点 DSPTMS320F2812 芯片, 它采用 1. 8 V 的内核电压,具有 3. 3 V 的外围接口电压,最高 频率 150 MHz,片内有 18 KB 的 RAM,128 KB 的高速 Flash。

以 16 位的方式输出。地址 / 模式信号( A0,A1,A2) 为数据读取

方式的控制信号,共有 3 种方式,分别为单通道、周期、F道信息,这里必须将 ADD

引脚值为高电平。 2. 3 FPGA 模块[3]

在该设计系统中 FPGA 是 重 要 的 控 制 模 块 和 存 储 模 块。

0 引言 许多场合需要高 速 数 据 采 集 系 统,如 雷 达、通 讯、机 器 人、

基于DSP+FPGA的高速采样系统设计

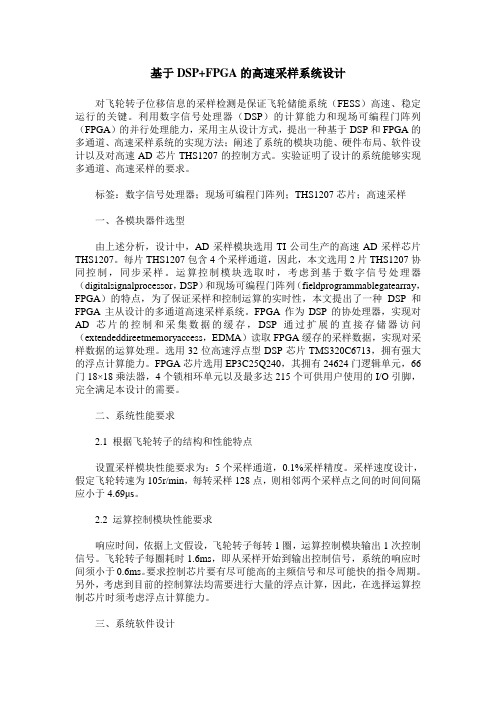

基于DSP+FPGA的高速采样系统设计对飞轮转子位移信息的采样检测是保证飞轮储能系统(FESS)高速、稳定运行的关键。

利用数字信号处理器(DSP)的计算能力和现场可编程门阵列(FPGA)的并行处理能力,采用主从设计方式,提出一种基于DSP和FPGA的多通道、高速采样系统的实现方法;阐述了系统的模块功能、硬件布局、软件设计以及对高速AD芯片THS1207的控制方式。

实验证明了设计的系统能够实现多通道、高速采样的要求。

标签:数字信号处理器;现场可编程门阵列;THS1207芯片;高速采样一、各模块器件选型由上述分析,设计中,AD采样模块选用TI公司生产的高速AD采样芯片THS1207。

每片THS1207包含4个采样通道,因此,本文选用2片THS1207协同控制,同步采样。

运算控制模块选取时,考虑到基于数字信号处理器(digitalsignalprocessor,DSP)和现场可编程门阵列(fieldprogrammablegatearray,FPGA)的特点,为了保证采样和控制运算的实时性,本文提出了一种DSP和FPGA主从设计的多通道高速采样系统。

FPGA作为DSP的协处理器,实现对AD芯片的控制和采集数据的缓存,DSP通过扩展的直接存储器访问(extendeddireetmemoryaccess,EDMA)读取FPGA缓存的采样数据,实现对采样数据的运算处理。

选用32位高速浮点型DSP芯片TMS320C6713,拥有强大的浮点计算能力。

FPGA芯片选用EP3C25Q240,其拥有24624门逻辑单元,66门18×18乘法器,4个锁相环单元以及最多达215个可供用户使用的I/O引脚,完全满足本设计的需要。

二、系统性能要求2.1 根据飞轮转子的结构和性能特点设置采样模块性能要求为:5个采样通道,0.1%采样精度。

采样速度设计,假定飞轮转速为105r/min,每转采样128点,则相邻两个采样点之间的时间间隔应小于4.69μs。

基于DSP和FPGA的数字化信号处理系统研究

基于DSP和FPGA的数字化信号处理系统研究数字化信号处理技术在现代通信和控制系统中得到了广泛应用,从手机信号到高速列车系统,都需要数字化信号处理系统进行相关转化和处理。

在数字化信号处理技术中,DSP和FPGA作为重要的核心模块,能够快速、高效地实现信号处理。

本文将详细介绍基于DSP和FPGA的数字化信号处理系统的研究及其应用。

一、数字化信号处理系统的基本概念数字化信号处理是指将模拟信号进行采样、量化、编码等处理,最终转化成数字信号,然后通过数字信号处理器进行数字处理、分析、传输、存储等过程的技术。

数字化信号处理系统由三个基本部分组成:信号采集设备、数字信号处理单元和数字信号输出设备。

信号采集设备包括模拟滤波器、模拟前端电路、ADC(模拟-数字转换器)等部分。

ADC是数字化信号处理系统的核心之一,它将模拟信号转换成数字信号,然后将其传给数字信号处理器。

数字信号处理器又可以分为DSP和FPGA两个部分。

DSP是数字信号处理器中较常见的一种芯片,它采用高速运算功能单元和专门的算法解释器来实现快速、高效的数字信号处理。

FPGA则更多用在数字信号的逻辑实现和调度方面。

它采用硬件描述语言编写程序,并将运算资源进行逻辑连接,以实现功能的高度定制性和并行性。

数字信号输出设备包括DAC(数字-模拟转换器)、模拟滤波器、调制器等。

它的主要作用是将处理后的数字信号转换成模拟信号输出给外界。

二、数字化信号处理系统的应用领域数字化信号处理技术已经得到广泛应用,包括但不限于以下领域:1. 通信系统:数字化信号处理技术广泛用于手机、网络通信、卫星通信、无线电通信等领域,以提高语音、图像等信息的传输效率和质量。

2. 控制系统:数字化信号处理技术在飞行控制、电力控制、轨道交通等自动化控制系统中应用广泛,以实现对复杂系统的高效监控和控制。

3. 图像处理:数字化图像处理技术应用于图像处理、视频处理等领域,是计算机视觉、虚拟现实等技术的基础。

基于DSP与FPGA的高速数据采集系统的设计

拟开关 D 0 G4 8来 实 现 两 组 8路 采样 信 号 的切 换 , 以 实现 对 两 可 组信号进行同时变换 , 如单 相 的 电压 和 电流 。D 0 G4 8最 大 导 通

电阻 为 1 0 最 大 击 穿 电压 为 4 V, 长 开 关 时 间为 2 0 s 该 O Q, 4 最 5 n。

.

程 琼 原腾 飞 付 波 ( 湖北工业大学电气与电子工程学院, 湖北 武汉 4 0 6 ) 3 0 8

摘 要

针 对传 统 数 据 采 集 系统 的 不 足 , 据 电 力 系统 数 据 采 集要 求 , 建 了 以 D P和 F G 为核 心 的数 据 采 集 系统 。 系统 以 根 构 S P A F G 为 主 控 CP P A U, 实现 对 AD 转换 器 的 控 制 ,并 实现 数 据 的存 储 功 能 。 该数 据 采 集 系统 可 实现 1 6路 最 大 工作 频 率 为

4 2

基 于 DS P与 F GA 的高 速 数据 A的高速数据采集系统的设计

y t m B s d n DSP a d P a e o n F GA De i f Hi p e t qust n S se sgn o gh S e d Da a Ac iio i

5 0 SP 0 k S的模 拟信 号采 集 , 用于 电网信 号 的 高速 采 集 。 适 关 键 词 :P F GA, S 数 据采 集 D P,

Ab ta t sr c T s hi pa r i pe amed at h s or om ig of r dion l te h t c n ta t a daa c i t a quiio s sem , nsr t d a st n y t i co tuc a at ac iion y e qust s stm whih i c

结合FPGA与DSP实现对高速中频采样信号处理平台的设计详解

结合FPGA与DSP实现对高速中频采样信号处理平台的设计详解现代社会正向数字化、信息化方向高速发展,在这一过程中,往往需要高速信号的实时性数字化处理。

例如,随着科技的进步,现代雷达等应用信号的数字化处理上有了长足的发展,但也带来了新的问题,这些应用的数字信号处理具有海量运行需求的应用背景,如巡航导弹末制导雷达地形匹配、合成孔径雷达的成像处理、相控阵雷达的时空二维滤波处理等领域。

目前,单片DSP难以胜任许多信号处理系统的要求。

而常见的解决方案也是高速A/D采样与信号处理功能是在多块不同的板卡上实现,这给实际应用带来很多不便。

鉴于上述现有技术所存在的问题,本设计平台的目的是:

(1)实现高速中频信号(如雷达信号)的数字化处理并进行实时传输数据或进行数据的实时计算,并能通过输出电路进行结果显示;

(2)自定义控制总线可以实现对高速中频信号处理板进行灵活控制,具有较强的可配置性和丰富的灵活性;

(3)高速A/D采样与D/A回放及数据处理单元集成在一块板上,在集成度高的同时也降低了高速信号在传输过程中出现差错的概率。

1 平台设计方案高速中频采样信号处理平台由主控制电路、高速A/D与D/A电路、信号处理单元电路、光纤通道电路、时钟管理电路、存储单元和外部接口电路组成,其总体框图如图1所示。

在实际应用过程中,四路A/D通道可以接收不同的信号源的信号,D/A通路可以对外进行数据显示等多种功能,时钟管理电路管理内外时钟的使用及对板上系统供给工作时钟,两路光纤通道可以与其他高速设备相连接,自定义总线可以与CPU或主控制器相连接对平台进行有效灵活的控制。

1.1 高速A/D与D/A设计

四路高速A/D采样通道采用两片NS公司的ADC081000实现,每片有两个A/D通道,。

基于DSP+FPGA结构的高速数据采集模块

参考文献 H 略I

万方数据

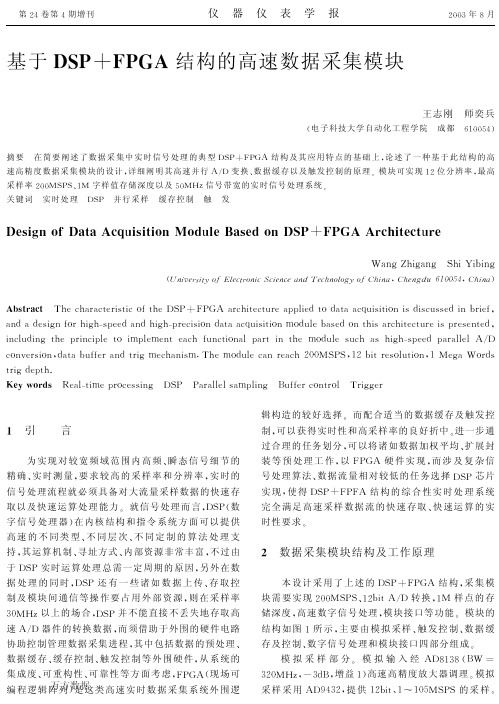

基于DSP+FPGA结构的高速数据采集模块

作者: 作者单位: 刊名: 英文刊名: 年,卷(期): 被引用次数: 王志刚, 师奕兵 电子科技大学自动化工程学院,成都,610054 仪器仪表学报 CHINESE JOURNAL OF SCIENTIFIC INSTRUMENT 2003,24(z2) 10次

, 引

言

制5 可以获得实时性和高采样率的良好折中 8 进一步通 可以将诸如数据加权平均 7 扩展封 过合理的任务划分 5 装 等 预 处 理 工 作5 以2 而涉及复杂信 1 3 4 硬 件 实 现5 数据流量相对较低的任务选择 / 号处理算法 7 0 1芯片 实 现5 使得 / $2 0 1 1 2 4结构的综合性实时处理系统 完全满足高速采样数据流的快速存取7 快速运算的实 时性要求 8

. 数据采集模块结构及工作原理

本设计采用了上述的 / 采集模 $2 0 1 1 3 4 结 构5 块需要实现 9 + + 7 * 9 * :0 1 0 W U x 46 /转 换5 : 样点的存 高速数字信号处理 5 模块接口等功能 8 模块的 储深度 5 结 构 如 图 *所 示 5 主 要 由 模 拟 采 样7 触 发 控 制7 数据缓 存及控制 7 数字信号处理和模块接口四部分组成 8

第9 -卷第 -

报

9 + + -年 /月

基于 ! $% " # # & ’ 结构的高速数据采集模块

王志刚

电子科技大学自动化工程学院 ( 摘要 成都

师奕兵

) * + + , .

在简要阐述了数据采集中实时信号处理的典型 / 论述了一种基于此结构的高 $2 0 1 1 3 4 结构及其应用特点的基础上5 详细阐明其高速并行 46 变换 数据缓存以及触发控制的原理 模块可实现 最高 速高精度数据采集模块的设计 5 7 8 * 9位分辨率 5 / 采样率 9 信号带宽的实时信号处理系统 8 + + 7 * + :0 1 0 : 字样值存储深度以及 , :;< 关键词 实时处理 / 0 1 并行采样 缓存控制 触 发

基于DSP+FPGA的高速采样系统设计

传感器 与微 系统 (Transducer and Microsystem Technologies)

47

DOI:10.13873/J.1000-9787(2018)09-0047-03

基 于 DSP+FPGA 的 高速 采样 系统 设 计

孙 畅 ,10027)

个采样点之问 的时 间间隔应小 于 4.69 s。

2)运算 控制模块性能要求

响应时 间,依据上文假设 ,飞轮转 子每 转 l圈,运算 控

制模块输 出 i次控制 信号 。飞 轮转 子每 圈耗时 0.6 ms,即

从 采 样 开 始 到 输 出 控 制 信 号 ,系 统 的 响应 时 间 须 小 于

slave design m ode,a multi—channel,high—speed sampling system realization m ethod based on DSP and FPGA is proposed.M odule function,hardware layout and software design of the system as well as control mode f or high— speed AD chip THS1207 are elaborated.It is proved by exper im ent that the desiged system can achieve requirements of multi—channel and high—speed sam pling.

摘 要 :对飞轮转子位移信息 的采样 检测是保 证飞轮储能系统 (FESS)高速 、稳定运 行 的关键 。利用数字 信号处理器 (DSP)的计算能力 和现场 可编程门阵列 (FPGA)的并行 处理 能力 ,采用 主从 设计方 式 ,提 出了 一 种基 于 DSP和 FPGA的多通道 、高速采样 系统的实现方法 ;阐述了系统的模块功能 、硬件布局 、软件设计 以及对高 速 AD芯片 THS1207的控制 方式 。实验证 明了设计 的系统能够 实现多通道 、高速采样 的要求 。 关键 词 :数字信号处理器 ;现场可编程 门阵列 ;THS1207芯片 ;高速采样 中图分类 号 :TP393 文献标识码 :A 文章编 号 :1000-9787(2018)09-0047-03

高速DSP数据采集的信号完整性问题

高速DSP数据采集的信号完整性问题高速DSP数据采集的信号完整性问题摘要:深入研究高速数字电路设计中的信号完整性问题;分析电路中破坏信号完整性的原因;结合一个实际的DSP数据采集系统、阐述实现信号完整性的具体方案。

关键词:信号完整性ADSP21161 数据采集噪声控制引言当前,日渐精细的半导体工艺使得晶体管尺寸越来越小,因而器件的信号跳变也就越来越快,高速数字系统的快斜率瞬变和极高的工作频率,以及很大的电路密集度,导致高速数字电路系统设计领域的信号完整性问题以及电磁兼容性问题日趋严重。

破坏了信号完整性将直接导致信号失真、定时错误,以及产生不正确数据、地址和控制信号,从而千万系统误工作甚至导致系统崩溃。

因此,信号完整性问题已经越来越引起高速数字电路设计人员的关注。

1信号完整性问题产生的机理信号完整性的问题主要包括传输线效应,如反射、时延、振铃、信号的过程与下冲以及信号之间的串扰等,涉及传输线上的信号质量及信号定时的准确性。

良好的信号质量是确保稳定时序的关键。

由于反射和串扰造成的信号质量问题都很可能带来时序的偏移和紊乱。

例如,串扰会影响信号的传播延迟,导致在时钟的上升沿或下降沿处采不到准确的逻辑;反射会造成数据信号在逻辑门限附近波动,从而影响信号上升沿或下降沿变化;时钟走线的干扰会造成一定的时钟偏移。

(范文先生网收集整理)信号完整性分析与设计是最重要的高速PCB板级和系统级分析与设计手段,在硬件电路设计中扮演着越来越重要的作用。

一个数字系统能否正确工作,其关键在于信号定时是否准确。

信号定时和信号在传输线上的传输延迟与信号波形的损坏程度密切相关。

信号传输延迟和波形破损的原因复杂多样,但主要是以下三种原因破坏了信号的完整性。

①电源、地址噪声。

它主要是源自于电源路径以及IC封装所造成的分布电感的存在。

当系统的速度愈快,同时转换逻辑状态的I/O引脚个数愈多时,会产生较大的瞬态电流,导致电源线上和地线睥电压波动和变化,这就是平进所说的接地反弹。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

时间 / n s

( ) 加人端接电阻 b 后的波形

口, 对它的处理是保证信号完整性的关键; 与F l s a h 、 F P G A接口 采用异步接口, 速率可以通过寄存器进行设置, 信号完整性要求 容易达到。另外, 时钟和电源电路也比较重要。 3 . 1 控制系统的反射

小的I C 封装技术, 表面贴片的封装技术通常会比D IP 封装技术 少3 0%的接地反弹, 在本系统的设计中除接擂件所有芯片均采 用了表面贴片封装; 其次还可以在 I C 的电源与地端引脚间加装 旁路电容, 这样当存在瞬态开关动作时, 可以提供瞬态涌动电流 所需的电子, 而不是从电源获取, 从而抑制了电平的抖动, 而且 还可以为电源和地之间的高频电路提供就近回路, 减少了电磁 辐射。在本系统中对 P R O M 、 S D R A M 、 n s a h 等存储型器件, 在芯 片的电源线( V c 。 ) 和地线( G N ) 间直接接人去藕电容。在 D D P s 的C V D D和 D V D D管脚与地之间通过合理布局, 共放置了4 8个

1 信号完整性问题及其产生原因

电路存在信号完整性问题时所表现出来的一些典型现象包

括:

①电路只能间断地工作, 但找不到间断工作的原因; ②电路原本能可靠工作, 但在更换 I C 供应商或者电路板制 造厂家后又不能正常工作; ③电路对电源和温度的变化非常敏感; ④电路在实验室可以正常工作, 但是在现场只能间断地工

驱动端 接收端

3 . 2 减小串扰 减小串扰的一般原则是尽量使用带状线以消除前向串扰; 利用重叠的层, 走线尽可能靠近它们的参考层; 避免互相平行的 走线布线, 提供走线间足够的间隔以最小化电感藕合; 相邻层上 的布线要相互垂直, 以防止层间的电容祸合。 由于异步信号和时钟信号更容易产生串扰, 因此在本系统 中时钟电路的抗串扰设计通过增大信号走线的线间距来达到。 时钟线与时钟线之间, 时钟线与其他信号线, 以及时钟线本身走 曲线时的线间距应该尽量大, 最小线间距不应小于2 0 而l (1 而1

端接阻抗匹配是最有效的减小反射方法。常用的有5 种端 接匹配方法: 串行匹配、 并行匹配、 戴维宁匹配、 R C网络匹配和 二极管匹配。一般来说, 对于 C M O S 器件信号的驱动端的输出 阻抗比较小, 为几十f l, 而接收端的输人阻抗比较大, 在信号源 端使用串行端接技术就会获得较好的效果。由于本系统采用的

动功能; F p G A 选用X i i l x公司的s n P ta x a n 一 1的x 3S C 4 0T 14, Q

完成逻辑时序控制、 A D和 D A接口以及数据的预处理, 最高工 作频率为2 0M 5 z; H D P 采用T s l公司的高性能浮点数字信号处 理器 T M 32 s 0C 6 7 3, 1 最高工作频率为 2 5M 2 H z , 使 灯D转换后 的数据在传输到上位机之前, 进行数据整理以及数字滤波运算。 由于系统具有很高的工作频率和电路密度, 如何处理高速电路

作。 当电路出现上述一些现象的时候就要考虑是否破坏了系统

收稿日 期: 2 07 一 2一 0 4 0 作者简介: 卑燕军( 1 9 1一) 8 , 男, 硕士研究生, 主要研究方向为信号处理 和嵌入式系统设计; 申功助( 1 9 5一) 3 , 男, 教授, 博士生导师, 主要研究方

向为导航制 导与控制 。

Ab S 扮皿 C t : T 、er e a s o n s fd o m 哈n a g s i ,a li n t e ht g ya e r

aa n l y z e d . A n d t h e n c o bi n l n e d 初t h h t e h i hs g P e ds i ,a lc o l l e c t i o n a n d p o r - c s e s i n g s y s t e mb a , do e n D Pa S n d 即G A, h t e d e a t i l 相s l o u t i o n s os t i 幼a li n 记 幼t yi s xP e at i a t e d . K 叮w or d s : 5 1 ,a l i n t e 幼t y ; D S P + F P G A ; r e l f e c t i o n ; c o r s s t l a k ; 脚u db n un o ce 当前的数字系统向着高密度和高速度的趋势不断地发展。 所谓高速其并不单单指时钟的速度, 还包括数字系统上升沿及 下降沿的跳变的速度。当上升时间减小到一定的程度, 电路板 上的寄生电容和寄生电感开始导致一些可能影响电路性能的噪 声信号和瞬态信号时, 就需要考虑信号完整性问题。破坏了信

要抑制接地反弹对系统的影响, 首先要采用分布电感量较 图2 申行端接匹配

因此对于 D P 的外数据总线、 S 地址总线和外存储器控制信 号线, 根据器件厂家推荐接人3 3 n的终端电阻。图3 ( )和图3 a ( b ) 是在时钟频率 l )M ( 0 H z 下, 使用M e n o t r G a r p h i c s 公司的H y -

万方数据

基于D S P + F P G A的高速信号采集与处理系统的信号完整性分析

的信号完整性的问题就变的尤为重要。

图1 为数据采集处理系统框图。

线的等长。

> 、 日留 净 、 进甚

一 2 . 0 0 0 0 . 0 0 0

图1 数据采集和处理系统框图

3 系统信号M F 时钟最高可以达 l I oM H : , D P S 以极高的速率与外设通信, D S P与 S D A M接口是同步高速接 R

A n a I y s i s o nS i g aI n I n t e g r i yo t fH i hS g P e e dS i g n iC a o I I e c i t o na d n P r o c e s i s n gS y t s m B e a s e do nD S Pa n dF P G A

厂 一 ) } 一 } { } 门 「 二 二 } 门 } 二 ] 口 \ \ 汀 人 l 仁 厅泞 刃 泞 医 口 泞赶 4 . 0 0 0网 l 门7 s e } }} } { 「 下 1 1 八 一 们 } 「 旧 j l〔 }} 环} I[ 亚 } [ 旧 l口 叮 l 旧 ) }困 }l j[ 胭 } /[ 犯j 下 l[ 下! j亚 l 盯 口 猛以 l「 刃l 厂 Ul / 「 刃} I /「 工 0 . 0 0 0 丫 门 习 } 习 ] 万 } } } 门 口 一 2 . 0 0 0 } } } } } } 1 厂 二 } } 一 一 匡 二

2 系统介绍

本系统为基于 D S P 十 F P G A结构的高速信号采集和处理系 统。D S P + PG F A 结构最大的特点是结构灵活, 有较强的通用 性, 适于模块化设计, 从而能够提高算法效率; 同时其开发周期 较短, 系统易于维护和扩展, 适合于实时数据采集和处理。实时 信号处理系统中, 低层的信号预处理算法处理的数据量大, 对处 理速度的要求高, 但运算结构相对比较简单, 适于用 F P G A进行 硬件实现, 这样能同时兼顾速度及灵活性。高层处理算法的特 点是所处理的数据量较低层算法少, 但算法的控制结构复杂, 适 于用运算速度高、 寻址方式灵活、 通信机制强大的D P 芯片来 S 实现。此系统分为模拟和数字两个部分, 是典型的数模混合系 统。 A D 采用的是1 6位 1 . Z M 别。 的串行 灯D转换器A m7 3, 2 用来采集传感器的微弱信号; D A采用的是 1 6 位的串 行D /A 转 换器A 55 D 2 提供模拟输出通道, 4 用于实现波形产生和模拟驱

p e r l x 的U n y e n i s m 进行的接人匹配电阻前后信号的仿真波形。

从图3 ( )可以看出, a 与驱动信号相比, 接收信号有明显的过冲, 这样的信号在实际中是不能使用的。图3 ( b ) 则显示接人串行 匹配电阻后信号的质量得到了明显的改善。另外, 由于 S D R A M 是高速器件, 布局时将它尽量靠近 D S P 芯片使得它与 D S P 之间 的布线尽可能短以便反射在短时间内达到稳态, 而且要注意布

6 ‘ 0 0 0

. 2

n 份 n 叶

么

0 一 0 0 0

n 叶 n } U

2 0 . 0 0 0

4 0 . 0 0 0

时间 / s n

( ) a

未加端接电阻时的波形

00 0 0

U n

2 0 . 0 0 0

4 00 0 0

《 侧拉技术》 2 07 年第2 6 卷第 1 2期

基于 D S P + F P G A的高速信号采集

与处理系统的信号完整性分析

邱燕军,申功勋

( 北京航空航天大学 宇航学院精密仪器系, 北京 1 0 以 ) 8 ) 3

摘要: 在分析各种破坏信号完整性的原因的基础上, 结合一个基于D P十 S F p G A结构的信号采集和处理系 统, 阐述了实现信 号完整性的具体方法。 关健词: 信号完整性; D P十 s F P G A ; 反射; 串 扰; 地弹 中图分类号: T N g l l . 6 文献标识码: A 文章编号: 1 ( K X ) 一 82 9( 2 0 0 7 ) 2一 1 仪 刃 8 一 3 0

Q I UY a n 一 u n , S H E NG on g 一 x u n

( 5 o b lo o fA s on r t a u i t c , , B e i h a n g U n i e v o i y t , B e j i i n g l ( 0 X 】 8 3 , C h i n ) a

④电源系统的稳定性。

号完整性将直接导致信号失真、 定时错误, 以及产生不正确数 据、 地址和控制信号, 从而造成系统错误运行甚至导致系统崩 溃。因此, 信号完整性问题已经在电路设计中越来越得到重视。 这里利用基于D P+ s F P G A的高速信号采集和处理系统为背景