SB050中文资料

高血压专科电子病历数据集标准 - 第 8 部分:高血压护理评估与计划(2018年版)

高血压专科电子病历数据集第 8 部分:高血压护理评估与计划1 范围T/CHIA 7.8-2018 的本部分规定了高血压患者护理评估与计划的数据集元属性和数据元属性。

本部分适用于指导高血压患者护理评估与计划基本信息的采集、存储、共享以及倍息系统的开发。

2 规范性引用文件下列文件对于本文件的应用是必不可少的。

凡是注日期的引用文件,仅注日期的版本适用于本文件,凡是不注日期的引用文件,其最新版本(包括所有的修改单)适用于本文件。

GB/T 2261.1-2003 个人基本信息分类与代码第1部分:人的性别代码GB/T 2261.2-2003 个人基本信息分类与代码第2部分:婚姻状况代码GB/T 2261.4-2003 个人基本信息分类与代码第4部分:职业类别代码GB/T 3304-1991 中国各民族名称的罗马字母拼写法和代码GB/T 4761-2008 家庭关系代码WS 218-2002 卫生机构(组织)分类与代码WS 364.12-2011 卫生信息数据元值域代码第12部分:计划与干预GB/T 14396-2016 疾病分类与代码WS 445-2014 电子病历基本数据集WS 365-2011 城乡居民健康档案基本数据集3术语和缩略语WS 370-2012 中界定的术语和定义适用于本文件4 数据集元数据属性数据集元数据属性见表1。

表1 数据集元数据属性5 数据元公用属性数据元公用属性描述见表2.表2 数据元公用属性6 数据元专用属性6.1入院评估记录子集入院评估记录子集的数据元专用属性描述见表3表3 入院评估记录子集数据元专用属性34566.2护理计划记录子集病危(重)护理记录子集的数据元专用属性描述见表4表4 护理计划记录子集数据元专用属性786.3出院评估与指导记录子集生命体征测量记录子集的数据元专用属性描述见表5表5 出院评估与指导记录子集数据元专用属性910T/CHIA 7.8-201811T/CHIA 7.8-2018 7 数据元值域代码表7.1护理等级代码表护理等级代码表规定了护理等级类型的分类代码,采用2位数字顺序代码,从01开始,按升序排列。

XCS05XL-4BG100I中文资料

© 2001 Xilinx, Inc. All rights reserved. All Xilinx trademarks, registered trademarks, patents, and disclaimers are as listed at /legal.htm .All other trademarks and registered trademarks are the property of their respective owners. All specifications are subject to change without notice.IntroductionThe Spartan ™ and the Spartan-XL families are a high-vol-ume production FPGA solution that delivers all the key requirements for ASIC replacement up to 40,000 gates.These requirements include high performance, on-chip RAM, core solutions and prices that, in high volume,approach and in many cases are equivalent to mask pro-grammed ASIC devices.The Spartan series is the result of more than 14 years of FPGA design experience and feedback from thousands of customers. By streamlining the Spartan series feature set,leveraging advanced process technologies and focusing on total cost management, the Spartan series delivers the key features required by ASIC and other high-volume logic users while avoiding the initial cost, long development cycles and inherent risk of conventional ASICs. The Spar-tan and Spartan-XL families in the Spartan series have ten members, as shown in T able 1.Spartan and Spartan-XL FeaturesNote: The Spartan series devices described in this data sheet include the 5V Spartan family and the 3.3V Spartan-XL family. See the separate data sheet for the 2.5V Spartan-II family.•First ASIC replacement FPGA for high-volume production with on-chip RAM•Density up to 1862 logic cells or 40,000 system gates •Streamlined feature set based on XC4000 architecture •System performance beyond 80MHz•Broad set of AllianceCORE ™ and LogiCORE ™ predefined solutions available •Unlimited reprogrammability •Low cost•System level features-Available in both 5V and 3.3V versions -On-chip SelectRAM ™ memory -Fully PCI compliant-Full readback capability for program verificationand internal node observability -Dedicated high-speed carry logic -Internal 3-state bus capability-Eight global low-skew clock or signal networks -IEEE 1149.1-compatible Boundary Scan logic -Low cost plastic packages available in all densities -Footprint compatibility in common packages•Fully supported by powerful Xilinx development system -Foundation Series: Integrated, shrink-wrapsoftware-Alliance Series: Dozens of PC and workstationthird party development systems supported-Fully automatic mapping, placement and routing Additional Spartan-XL Features• 3.3V supply for low power with 5V tolerant I/Os •Power down input •Higher performance •Faster carry logic•More flexible high-speed clock network•Latch capability in Configurable Logic Blocks •Input fast capture latch•Optional mux or 2-input function generator on outputs •12 mA or 24 mA output drive •5V and 3.3V PCI compliant •Enhanced Boundary Scan •Express Mode configuration •Chip scale packagingSpartan and Spartan-XL Families Field Programmable Gate ArraysDS060 (v1.6) September 19, 2001Product Specification T able 1: Spartan and Spartan-XL Field Programmable Gate Arrays1.Max values of Typical Gate Range include 20-30% of CLBs used as RAM.2DS060 (v1.6) September 19, 2001General OverviewSpartan series FPGAs are implemented with a regular, flex-ible, programmable architecture of Configurable Logic Blocks (CLBs), interconnected by a powerful hierarchy of versatile routing resources (routing channels), and sur-rounded by a perimeter of programmable Input/Output Blocks (IOBs), as seen in Figure 1. They have generous routing resources to accommodate the most complex inter-connect patterns.The devices are customized by loading configuration data into internal static memory cells. Re-programming is possi-ble an unlimited number of times. The values stored in thesememory cells determine the logic functions and intercon-nections implemented in the FPGA. The FPGA can either actively read its configuration data from an external serial PROM (Master Serial mode), or the configuration data can be written into the FPGA from an external device (Slave Serial mode).Spartan series FPGAs can be used where hardware must be adapted to different user applications. FPGAs are ideal for shortening design and development cycles, and also offer a cost-effective solution for production rates well beyond 50,000 systems per month.Figure 1: Basic FPGA Block DiagramSpartan series devices achieve high-performance, low-cost operation through the use of an advanced architecture and semiconductor technology. Spartan and Spartan-XL devices provide system clock rates exceeding 80MHz and internal performance in excess of150MHz. In contrast to other FPGA devices, the Spartan series offers the most cost-effective solution while maintaining leading-edge per-formance. In addition to the conventional benefit of high vol-ume programmable logic solutions, Spartan series FPGAs also offer on-chip edge-triggered single-port and dual-port RAM, clock enables on all flip-flops, fast carry logic, and many other features.The Spartan/XL families leverage the highly successful XC4000 architecture with many of that family’s features and benefits. T echnology advancements have been derived from the XC4000XLA process developments.Logic Functional DescriptionThe Spartan series uses a standard FPGA structure as shown in Figure1, page2. The FPGA consists of an array of configurable logic blocks (CLBs) placed in a matrix of routing channels. The input and output of signals is achieved through a set of input/output blocks (IOBs) forming a ring around the CLBs and routing channels.•CLBs provide the functional elements for implementing the user’s logic.•IOBs provide the interface between the package pins and internal signal lines.•Routing channels provide paths to interconnect the inputs and outputs of the CLBs and IOBs.The functionality of each circuit block is customized during configuration by programming internal static memory cells. The values stored in these memory cells determine the logic functions and interconnections implemented in the FPGA.Configurable Logic Blocks (CLBs)The CLBs are used to implement most of the logic in an FPGA. The principal CLB elements are shown in the simpli-fied block diagram in Figure2. There are three look-up tables (LUT) which are used as logic function generators, two flip-flops and two groups of signal steering multiplexers. There are also some more advanced features provided by the CLB which will be covered in the Advanced Features Description, page13.Function GeneratorsTwo 16x1 memory look-up tables (F-LUT and G-LUT) are used to implement 4-input function generators, each offer-ing unrestricted logic implementation of any Boolean func-tion of up to four independent input signals (F1 to F4 or G1 to G4). Using memory look-up tables the propagation delay is independent of the function implemented.A third 3-input function generator (H-LUT) can implement any Boolean function of its three inputs. Two of these inputs are controlled by programmable multiplexers (see box "A" of Figure2). These inputs can come from the F-LUT or G-LUT outputs or from CLB inputs. The third input always comes from a CLB input. The CLB can, therefore, implement cer-tain functions of up to nine inputs, like parity checking. The three LUTs in the CLB can also be combined to do any arbi-trarily defined Boolean function of five inputs.4DS060 (v1.6) September 19, 2001A CLB can implement any of the following functions:•Any function of up to four variables, plus any second function of up to four unrelated variables, plus any third function of up to three unrelated variablesNote: When three separate functions are generated, one of the function outputs must be captured in a flip-flop internal to the CLB. Only two unregistered function generator outputs are available from the CLB.•Any single function of five variables•Any function of four variables together with some functions of six variables•Some functions of up to nine variables.Implementing wide functions in a single block reduces both the number of blocks required and the delay in the signal path, achieving both increased capacity and speed. The versatility of the CLB function generators significantly improves system speed. In addition, the design-software tools can deal with each function generator independently.This flexibility improves cell usage.Flip-FlopsEach CLB contains two flip-flops that can be used to regis-ter (store) the function generator outputs. The flip-flops and function generators can also be used independently (see Figure 2). The CLB input DIN can be used as a direct input to either of the two flip-flops. H1 can also drive either flip-flop via the H-LUT with a slight additional delay.The two flip-flops have common clock (CK), clock enable (EC) and set/reset (SR) inputs. Internally both flip-flops are also controlled by a global initialization signal (GSR) which is described in detail in Global Signals: GSR and GTS ,page 20.Latches (Spartan-XL only)The Spartan-XL CLB storage elements can also be config-ured as latches. The two latches have common clock (K)and clock enable (EC) inputs. Functionality of the storage element is described in Table 2.Figure 2: Spartan/XL Simplified CLB Logic Diagram (some features not shown)Clock InputEach flip-flop can be triggered on either the rising or falling clock edge. The CLB clock line is shared by both flip-flops.However, the clock is individually invertible for each flip-flop (see CK path in Figure 3). Any inverter placed on the clock line in the design is automatically absorbed into the CLB. Clock EnableThe clock enable line (EC) is active High. The EC line is shared by both flip-flops in a CLB. If either one is left discon-nected, the clock enable for that flip-flop defaults to the active state. EC is not invertible within the CLB. The clock enable is synchronous to the clock and must satisfy the setup and hold timing specified for the device.Set/ResetThe set/reset line (SR) is an asynchronous active High con-trol of the flip-flop. SR can be configured as either set or reset at each flip-flop. This configuration option determines the state in which each flip-flop becomes operational after configuration. It also determines the effect of a GSR pulse during normal operation, and the effect of a pulse on the SR line of the CLB. The SR line is shared by both flip-flops. If SR is not specified for a flip-flop the set/reset for that flip-flop defaults to the inactive state. SR is not invertible within the CLB.CLB Signal Flow ControlIn addition to the H-LUT input control multiplexers (shown in box "A" of Figure 2, page 4) there are signal flow control multiplexers (shown in box "B" of Figure 2) which select the signals which drive the flip-flop inputs and the combinatorial CLB outputs (X and Y).Each flip-flop input is driven from a 4:1 multiplexer which selects among the three LUT outputs and DIN as the data source.Each combinatorial output is driven from a 2:1 multiplexer which selects between two of the LUT outputs. The X output can be driven from the F-LUT or H-LUT, the Y output from G-LUT or H-LUT .Control SignalsThere are four signal control multiplexers on the input of the CLB. These multiplexers allow the internal CLB control sig-nals (H1, DIN, SR, and EC in Figure 2 and Figure 4) to be driven from any of the four general control inputs (C1-C4 in Figure 4) into the CLB. Any of these inputs can drive any of the four internal control signals.T able 2: CLB Storage Element FunctionalityLegend:XDon ’t careRising edge (clock not inverted).SR Set or Reset value. Reset is default.0*Input is Low or unconnected (default value)1*Input is High or unconnected (default value)Figure 3: CLB Flip-Flop Functional Block Diagram6DS060 (v1.6) September 19, 2001The four internal control signals are:•EC: Enable Clock•SR: Asynchronous Set/Reset or H function generator Input 0•DIN: Direct In or H function generator Input 2•H1: H function generator Input 1.Input/Output Blocks (IOBs)User-configurable input/output blocks (IOBs) provide the interface between external package pins and the internal logic. Each IOB controls one package pin and can be con-figured for input, output, or bidirectional signals. Figure 6shows a simplified functional block diagram of the Spar-tan/XL IOB.IOB Input Signal PathThe input signal to the IOB can be configured to either go directly to the routing channels (via I1 and I2 in Figure 6) or to the input register. The input register can be programmed as either an edge-triggered flip-flop or a level-sensitive latch. The functionality of this register is shown in Table 3,and a simplified block diagram of the register can be seen in Figure 5.Figure 4: CLB Control Signal InterfaceFigure 5: IOB Flip-Flop/Latch Functional BlockDiagramTable 3: Input Register FunctionalityX Don ’t care.Rising edge (clock not inverted).SR Set or Reset value. Reset is default.0*Input is Low or unconnected (default value)1*Input is High or unconnected (default value)The register choice is made by placing the appropriate library symbol. For example, IFD is the basic input flip-flop (rising edge triggered), and ILD is the basic input latch (transparent-High). Variations with inverted clocks are also available. The clock signal inverter is also shown in Figure5 on the CK line.The Spartan IOB data input path has a one-tap delay ele-ment: either the delay is inserted (default), or it is not. The Spartan-XL IOB data input path has a two-tap delay ele-ment, with choices of a full delay, a partial delay, or no delay. The added delay guarantees a zero hold time with respect to clocks routed through the global clock buffers. (See Glo-bal Nets and Buffers, page12 for a description of the glo-bal clock buffers in the Spartan/XL families.) For a shorter input register setup time, with positive hold-time, attach a NODELAY attribute or property to the flip-flop.The output of the input register goes to the routing channels (via I1 and I2 in Figure6). The I1 and I2 signals that exit the IOB can each carry either the direct or registered input signal.The 5V Spartan input buffers can be globally configured for either TTL (1.2V) or CMOS (VCC/2) thresholds, using an option in the bitstream generation software. The Spartan output levels are also configurable; the two global adjust-ments of input threshold and output level are independent. The inputs of Spartan devices can be driven by the outputs of any 3.3V device, if the Spartan inputs are in TTL mode. Input and output thresholds are TTL on all configuration pins until the configuration has been loaded into the device and specifies how they are to be used. Spartan-XL inputs are TTL compatible and 3.3V CMOS compatible. Supported sources for Spartan/XL device inputs are shown in Table4.Spartan-XL I/Os are fully 5V tolerant even though the V CC is 3.3V. This allows 5V signals to directly connect to the Spar-tan-XL inputs without damage, as shown in Table4. In addi-tion, the 3.3V V CC can be applied before or after 5V signals are applied to the I/Os. This makes the Spartan-XL devices immune to power supply sequencing problems.Figure 6: Simplified Spartan/XL IOB Block Diagram8DS060 (v1.6) September 19, 2001Spartan-XL V CC ClampingSpartan-XL FPGAs have an optional clamping diode con-nected from each I/O to V CC . When enabled they clamp ringing transients back to the 3.3V supply rail. This clamping action is required in 3.3V PCI applications. V CC clamping is a global option affecting all I/O pins.Spartan-XL devices are fully 5V TTL I/O compatible if V CC clamping is not enabled. With V CC clamping enabled, the Spartan-XL devices will begin to clamp input voltages to one diode voltage drop above V CC . If enabled, TTL I/O com-patibility is maintained but full 5V I/O tolerance is sacrificed.The user may select either 5V tolerance (default) or 3.3V PCI compatibility. In both cases negative voltage is clamped to one diode voltage drop below ground.Spartan-XL devices are compatible with TTL, LVTTL, PCI 3V, PCI 5V and LVCMOS signalling. The various standards are illustrated in Table 5.Additional Fast Capture Input Latch (Spartan-XL only)The Spartan-XL IOB has an additional optional latch on the input. This latch is clocked by the clock used for the output flip-flop rather than the input clock. Therefore, two different clocks can be used to clock the two input storage elements.This additional latch allows the fast capture of input data,which is then synchronized to the internal clock by the IOB flip-flop or latch.T o place the Fast Capture latch in a design, use one of the special library symbols, ILFFX or ILFLX. ILFFX is a trans-parent-Low Fast Capture latch followed by an active High input flip-flop. ILFLX is a transparent Low Fast Capture latch followed by a transparent High input latch. Any of the clock inputs can be inverted before driving the library element,and the inverter is absorbed into the IOB.IOB Output Signal PathOutput signals can be optionally inverted within the IOB,and can pass directly to the output buffer or be stored in an edge-triggered flip-flop and then to the output buffer. The functionality of this flip-flop is shown in T able 6.T able 4: Supported Sources for Spartan/XL InputsT able 5: I/O Standards Supported by Spartan-XL FPGAsTable 6: Output Flip-Flop Functionality X Don ’t careRising edge (clock not inverted). SR Set or Reset value. Reset is default.0*Input is Low or unconnected (default value)1*Input is High or unconnected (default value)Z3-stateOutput Multiplexer/2-Input Function Generator (Spartan-XL only)The output path in the Spartan-XL IOB contains an addi-tional multiplexer not available in the Spartan IOB. The mul-tiplexer can also be configured as a 2-input function generator, implementing a pass gate, AND gate, OR gate, or XOR gate, with 0, 1, or 2 inverted inputs.When configured as a multiplexer, this feature allows two output signals to time-share the same output pad, effec-tively doubling the number of device outputs without requir-ing a larger, more expensive package. The select input is the pin used for the output flip-flop clock, OK.When the multiplexer is configured as a 2-input function generator, logic can be implemented within the IOB itself. Combined with a Global buffer, this arrangement allows very high-speed gating of a single signal. For example, a wide decoder can be implemented in CLBs, and its output gated with a Read or Write Strobe driven by a global buffer. The user can specify that the IOB function generator be used by placing special library symbols beginning with the letter "O." For example, a 2-input AND gate in the IOB func-tion generator is called OAND2. Use the symbol input pin labeled "F" for the signal on the critical path. This signal is placed on the OK pin — the IOB input with the shortest delay to the function generator. Two examples are shown in Figure7.Output BufferAn active High 3-state signal can be used to place the out-put buffer in a high-impedance state, implementing 3-state outputs or bidirectional I/O. Under configuration control, the output (O) and output 3-state (T) signals can be inverted. The polarity of these signals is independently configured for each IOB (see Figure6, page7). An output can be config-ured as open-drain (open-collector) by tying the 3-state pin (T) to the output signal, and the input pin (I) to Ground.By default, a 5V Spartan device output buffer pull-up struc-ture is configured as a TTL-like totem-pole. The High driver is an n-channel pull-up transistor, pulling to a voltage one transistor threshold below V CC. Alternatively, the outputs can be globally configured as CMOS drivers, with additional p-channel pull-up transistors pulling to V CC. This option, applied using the bitstream generation software, applies to all outputs on the device. It is not individually programma-ble.All Spartan-XL device outputs are configured as CMOS drivers, therefore driving rail-to-rail. The Spartan-XL outputs are individually programmable for 12mA or 24mA output drive.Any 5V Spartan device with its outputs configured in TTL mode can drive the inputs of any typical 3.3V device. Sup-ported destinations for Spartan/XL device outputs are shown in Table7.Three-State Register (Spartan-XL Only)Spartan-XL devices incorporate an optional register control-ling the three-state enable in the IOBs. The use of the three-state control register can significantly improve output enable and disable time.Output Slew RateThe slew rate of each output buffer is, by default, reduced, to minimize power bus transients when switching non-criti-cal signals. For critical signals, attach a FAST attribute or property to the output buffer or flip-flop.Spartan/XL devices have a feature called "Soft Start-up," designed to reduce ground bounce when all outputs are turned on simultaneously at the end of configuration. When the configuration process is finished and the device starts up, the first activation of the outputs is automatically slew-rate limited. Immediately following the initial activation of the I/O, the slew rate of the individual outputs is deter-mined by the individual configuration option for each IOB. Pull-up and Pull-down NetworkProgrammable pull-up and pull-down resistors are used fortying unused pins to V CC or Ground to minimize power con-sumption and reduce noise sensitivity. The configurablepull-up resistor is a p-channel transistor that pulls to V CC.The configurable pull-down resistor is an n-channel transis-tor that pulls to Ground. The value of these resistors is typi-cally 20KΩ − 100KΩ (See "Spartan DC Characteristics Figure 7: AND and MUX Symbols in Spartan-XL IOB10DS060 (v1.6) September 19, 2001Over Operating Conditions" on page 43.). This high value makes them unsuitable as wired-AND pull-up resistors.After configuration, voltage levels of unused pads, bonded or unbonded, must be valid logic levels, to reduce noise sensitivity and avoid excess current. Therefore, by default,unused pads are configured with the internal pull-up resistor active. Alternatively, they can be individually configured with the pull-down resistor, or as a driven output, or to be driven by an external source. To activate the internal pull-up, attach the PULLUP library component to the net attached to the pad. To activate the internal pull-down, attach the PULL-DOWN library component to the net attached to the pad.Set/ResetAs with the CLB registers, the GSR signal can be used to set or clear the input and output registers, depending on the value of the INIT attribute or property. The two flip-flops can be individually configured to set or clear on reset and after configuration. Other than the global GSR net, no user-con-trolled set/reset signal is available to the I/O flip-flops (Figure 5). The choice of set or reset applies to both the ini-tial state of the flip-flop and the response to the GSR pulse.Independent ClocksSeparate clock signals are provided for the input (IK) and output (OK) flip-flops. The clock can be independently inverted for each flip-flop within the IOB, generating eitherfalling-edge or rising-edge triggered flip-flops. The clock inputs for each IOB are mon Clock EnablesThe input and output flip-flops in each IOB have a common clock enable input (see EC signal in Figure 5), which through configuration, can be activated individually for the input or output flip-flop, or both. This clock enable operates exactly like the EC signal on the Spartan/XL CLB. It cannot be inverted within the IOB.Routing Channel DescriptionAll internal routing channels are composed of metal seg-ments with programmable switching points and switching matrices to implement the desired routing. A structured,hierarchical matrix of routing channels is provided to achieve efficient automated routing.This section describes the routing channels available in Spartan/XL devices. Figure 8 shows a general block dia-gram of the CLB routing channels. The implementation soft-ware automatically assigns the appropriate resources based on the density and timing requirements of the design.The following description of the routing channels is for infor-mation only and is simplified with some minor details omit-ted. For an exact interconnect description the designer should open a design in the FPGA Editor and review the actual connections in this tool.The routing channels will be discussed as follows;•CLB routing channels which run along each row and column of the CLB array.•IOB routing channels which form a ring (called a VersaRing) around the outside of the CLB array. It connects the I/O with the CLB routing channels.•Global routing consists of dedicated networks primarily designed to distribute clocks throughout the device with minimum delay and skew. Global routing can also be used for other high-fanout signals.CLB Routing ChannelsThe routing channels around the CLB are derived from three types of interconnects; single-length, double-length,and longlines. At the intersection of each vertical and hori-zontal routing channel is a signal steering matrix called a Programmable Switch Matrix (PSM). Figure 8 shows the basic routing channel configuration showing single-length lines, double-length lines and longlines as well as the CLBs and PSMs. The CLB to routing channel interface is shown as well as how the PSMs interface at the channel intersec-tions.T able 7: Supported Destinations for Spartan/XL OutputsNotes:1.Only if destination device has 5V tolerant inputs.CLB InterfaceA block diagram of the CLB interface signals is shown in Figure9. The input signals to the CLB are distributed evenly on all four sides providing maximum routing flexibility. In general, the entire architecture is symmetrical and regular. It is well suited to established placement and routing algo-rithms. Inputs, outputs, and function generators can freely swap positions within a CLB to avoid routing congestion during the placement and routing operation. The exceptions are the clock (K) input and CIN/COUT signals. The K input is routed to dedicated global vertical lines as well as four single-length lines and is on the left side of the CLB. The CIN/COUT signals are routed through dedicated intercon-nects which do not interfere with the general routing struc-ture. The output signals from the CLB are available to drive both vertical and horizontal channels.Programmable Switch MatricesThe horizontal and vertical single- and double-length lines intersect at a box called a programmable switch matrix (PSM). Each PSM consists of programmable pass transis-tors used to establish connections between the lines (see Figure10).For example, a single-length signal entering on the right side of the switch matrix can be routed to a single-length line on the top, left, or bottom sides, or any combination thereof, if multiple branches are required. Similarly, a dou-ble-length signal can be routed to a double-length line on any or all of the other three edges of the programmable switch matrix.Single-Length LinesSingle-length lines provide the greatest interconnect flexibil-ity and offer fast routing between adjacent blocks. There are eight vertical and eight horizontal single-length lines associ-ated with each CLB. These lines connect the switching matrices that are located in every row and column of CLBs. Single-length lines are connected by way of the program-mable switch matrices, as shown in Figure10. Routing con-nectivity is shown in Figure8.Single-length lines incur a delay whenever they go through a PSM. Therefore, they are not suitable for routing signals for long distances. They are normally used to conduct sig-nals within a localized area and to provide the branching for nets with fanout greater than one.Figure 8: Spartan/XL CLB Routing Channels and Interface Block DiagramFigure 9: CLB Interconnect Signals。

RV050中文资料

'(7(&725 /2* 9,'(2 $03/,),(56)($785(6Z)8// 0,/ 63(& 352'8&76Z'& &283/(' &: ,0081( 9$5,$176Z:,'( )5(48(1&< 5$1*(Z+,*+ '<1$0,& 5$1*(Z'(6,*16 &$1 %( &86720(5 63(&,),(')25 237,080 6<67(0 3(5)250$1&('(6&5,37,21'HWHFWRU ORJ 9LGHR $PSOLILHUV '/9$ V FRQYHUW DQ 5) VLJQDO LQWR DQ RXWSXW YROWDJH SURSRUWLRQDO WR WKH LQSXW SRZHU OHYHO ,Q RUGHU WR DFFRPRGDWH D ZLGH UDQJH RI LQSXW SRZHUV WKH RXWSXW LV ORJDULWKPLF WKLV JLYHV D OLQHDU UHODWLRQVKLS EHWZHHQ RXWSXW YROWDJH DQG 5) SRZHU LQ G% V)LOWURQLFV '& &RXSOHG '/9$ V ZRUN RYHU D ZLGH UDQJH RI IUHTXHQFLHV WR *+] RU WR *+] 7KHLU GHVLJQ DOORZV VLJQDO SURFHVVLQJ LQ OHVV WKDQ QV)LOWURQLF V&: ,PPXQH '/9$ V RIIHU PDQ\ RI WKH DGYDQWDJHV RI $& FRXSOHG '/9$ V EXW ZLWKRXW WKH GUDZEDFNV 7KH\ DUH FDSDEOH RI PHDVXULQJ SXOVHV ZKLOVW LQ WKH SUHVFHQFH RI &: EXW XQOLNH $& FRXSOHG '/9$ V WKH\ ZLOO ZRUN ZLWK XS WR GXW\ F\FOHV LQ PRVW HQYLURQPHQWV 8WLOLVLQJ D SURSULHWDU\ GHWHFWRU GHVLJQ WKH\ DUH DOVR DEOH WR RIIHU H[FHOOHQW GHYLFH WR GHYLFH PDWFKLQJ SURFHVV SXOVH ZLGWKV RI OHVV WKDQ QV)LOWURQLFV H[WHQGHG UDQJH '/9$ V RIIHU PDQ\ RI WKH DGYDQWDJHV RI 6'/9$ V DW D ORZHU FRVW 7KH\ SRVHVV XS WR G% G\QDPLF UDQJH G% OLQHDULW\ G% IODWQHVV QV ULVH WLPH DQG QV UHFRYHU\ WLPH ZLWK D 7VV RI GRZQ WR G%P'/9$ 6(/(&7,21 *8,'(,QFOXGHV YLGHR %,7( RVFLOODWRU'& FRXSOHG ZLWK EDVH OLQH UHVWRUDWLRQ 7KHVH DUH DFWXDO IUHTXHQF\ UDQJHV SURGXFHG WR GDWH 7KH IUHTXHQF\ UDQJH JLYHQ LV WKDW IRU ZKLFK WKH GHVLJQ LV FDSDEOH 7KHUH PD\ QRW EH D GHYLFH LQ PDQXIDFWXUH WKDW RSHUDWHV RYHU WKLV UDQJH7KH ORJ UDQJH LV WKDW IRU ZKLFK WKH DFFXUDF\ LV VSHFLILHG 7KHUH PD\ EH XVHDEOH SHUIRUPDQFH RXWVLGH RI WKHVH OLPLWV &RQVXOW IDFWRU\ IRU GHWDLOV1RWHVWRWR&:59WR WR '&59 WR WR '&59WR WR '&59 WR WR &:59 WR WR &:59 WR WR &:59WR WR '&59 WR WR '&59 WR WR '&59 WR WR &:59 WR WR &:59WR WR &:59 QRWHV)UHTXHQF\9DULDQWV *+]QRWH )UHTXHQF\ *+] QRWH 7VV G%P/RJ 6ORSH P9 G%/RJ 5DQJH G%P QRWH '& &RXSOHG &: ,PPXQH7\SH &RGH352'8&7 7(&+1,&$/ 63(&,),&$7,216。

PTH05000W中文资料

Features•Up to 6-A Output Current•5-V Input Voltage•Wide-Output Voltage Adjust (0.9 V to 3.6 V)•Efficiencies up to 94 %•160 W/in³ Power Density•On/Off Inhibit•Under-Voltage Lockout •Output Current Limit •Pre-Bias Startup Capability •Over-T emperature Protection •Surface Mountable •Operating T emp: –40 to +85 °C •Safety Agency Approvals (Pending):UL 1950, CSA 22.2 950, EN60950& VDE NOMINAL SIZE =0.75 in x 0.5 in (19,05 mm x 12,7 mm)Pin DescriptionsVin: The positive input voltage power node to the mod-ule, which is referenced to common GND.Vout: The regulated positive power output with respectto the GND node.GND: This is the common ground connection for the‘V in ’ and ‘V out ’ power connections. It is also the 0 VDC reference for the ‘Inhibit’ and ‘V o Adjust’ control input.Inhibit: The Inhibit pin is an open-collector/drain negativelogic input that is referenced to GND . Applying a low-level ground signal to this input disables the module’s output and turns off the output voltage. When the Inhibit control is active, the input current drawn by the regulator is significantly reduced. If the Inhibit pin is left open-circuit, the module will produce an output whenever a valid input source is applied.Vo Adjust: A 0.1 W 1 % resistor must be directly connected between this pin and the GND pin to set the output voltage to a value higher than 0.9 V. The temperature stability of the resistor should be 100 ppm/°C (or better). The set point range for the output voltage is from 0.9 V to 3.6 V .The resistor required for a given output voltage may be calculated from the following formula. If left open circuit,the output voltage will default to its lowest value. For further information on output voltage adjustment, consult the related application note.R set = 10 k Ω · 0.891 V – 3.24 k Ω V out – 0.9 V The specification table gives the preferred resistor values for a number of standard output voltages.Ordering InformationPackage Options (PTH05000x HH )(1)Code Description Pkg Ref. (2)AHHoriz. T/H (EUS)AS SMD, Standard (3)(EUT)Output Voltage (PTH05000H xx)CodeVoltage W 0.9 V – 3.6 V (Adjust)Notes:(1)Add “T” to end of part number for tape and reel on SMD packages only.(2)Reference the applicable package reference drawing for the dimensions and PC board layout(3)“Standard” option specifies 63/37, Sn/Pb pin solder material.Notes:(i)For operation below 0 °C the external capacitors must have stable characteristics. Use either a low ESR tantalum, Os-con, or ceramic capacitor.(ii)During reflow of SMD package version do not elevate peak temperature of the module, pins or internal components above the stated maximum.Notes:(1)See SOA curves or consult factory for appropriate derating.(2)The set-point voltage tolerance is affected by the tolerance and stability ofR SET. The stated limit is unconditionally met if R SET has a tolerance of 1 %with 100 ppm/°C or better temperature stability.(3)The Inhibit control (pin 3) has an internal pull-up to Vin, and if left open-circuit the module will operate when input power is applied. A small low-leakage (<100 nA) MOSFET is recommended to control this input. See application notes for more information.(4)The regulator requires a minimum of 330 µF input capacitor with a minimum 300 mArms ripple current rating. For further information, consult therelated application note on Capacitor Recommendations.(5)An external output capacitor is not required for basic operation. Adding 100 µF of distributed capacitance at the load will improve the transient response.(6)This is the calculated maximum. The minimum ESR limitation will often result in a lower value. Consult the application notes for further guidance.(7)This is the typical ESR for all the electrolytic (non-ceramic) output capacitance. Use 7 mΩ as the minimum when using max-ESR values to calculate.Note A: Characteristic data has been developed from actual products tested at 25 °C. This data is considered typical data for the Converter.Note B: SOA curves represent the conditions at which internal components are at or below the manufacturer’s maximum operating temperatures. Derating limits apply to modules soldered directly to a 4 in. × 4 in. double-sided PCB with 1 oz. copper.Typical CharacteristicsE f f i c i e n c y - %R i p p l e - m V P d - W a t t s 6-A, 5-V Input Non-IsolatedPTH05000WCapacitor Recommendations for the PTH05000W Wide-Output Adjust Power ModulesInput CapacitorThe recommended input capacitor(s) is determined by the 330 µF minimum capacitance and 300 mArms mini-mum ripple current rating.Ripple current, less than 300 mΩ equivalent series resis-tance (ESR), and temperature are the major considerations when selecting input capacitors. Unlike polymer tantalum, regular tantalum capacitors have a recommended mini-mum voltage rating of2 × (maximum DC voltage + AC ripple). This is standard practice to ensure reliability. For improved ripple reduction on the input bus, ceramic capacitors [2] may used to complement electrolytic types, and achieve the minimum required capacitance.Output Capacitors (Optional)For applications with load transients (sudden changes in load current), regulator response will benefit from an external output capacitance. The recommended output capacitance of 100 µF will allow the module to meet its transient response specification (see product data sheet). For most applications, a high quality computer-grade aluminum electrolytic capacitor is adequate. These capaci-tors provide decoupling over the frequency range, 2 kHz to 150 kHz, and are suitable for ambient temperatures above 0 °C. For operation below 0 °C tantalum, ceramic or Os-Con type capacitors are recommended. When using one or more non-ceramic capacitors, the calculated equiva-lent ESR should be no lower than 4 mΩ (7 mΩ using the manufacturer’s maximum ESR for a single capacitor). A list of preferred low-ESR type capacitors are identified in T able 1-1.Ceramic CapacitorsAbove 150 kHz the performance of aluminum electrolytic capacitors becomes less effective. T o further improve the reflected input ripple current [2] or the output transient response, multilayer ceramic capacitors can also be added. Ceramic capacitors have very low ESR and their resonant frequency is higher than the bandwidth of the regulator. When used on the output their combined ESR is not critical as long as the total value of ceramic capacitance does not exceed 300 µF. Also, to prevent the formation of local resonances, do not place more than five identical ce-ramic capacitors in parallel with values of 10 µF or greater. Tantalum CapacitorsT antalum type capacitors can be used at both the input and output, and are recommended for applications where the ambient operating temperature can be less than 0 °C. The AVX TPS, Sprague 593D/594/595 and Kemet T495/T510 capacitor series are suggested over many other tantalum types due to their higher rated surge, power dissipation, and ripple current capability. As a caution many general purpose tantalum capacitors have consid-erably higher ESR, reduced power dissipation and lower ripple current capability. These capacitors are also less reliable as they have lower power dissipation and surge current ratings. T antalum capacitors that do not have a stated ESR or surge current rating are not recommended for power applications.When specifying Os-Con and polymer tantalum capacitors for the output, the minimum ESR limit will be encoun-tered well before the maximum capacitance value is reached.Capacitor TableT able 1-1 identifies the characteristics of capacitors from a number of vendors with acceptable ESR and ripple current (rms) ratings. The recommended number of capacitors required at both the input and output buses is identified for each capacitor type.This is not an extensive capacitor list. Capacitors from other vendors are available with comparable specifications. Those listed are for guidance. The RMS ripple current rating and ESR (at 100 kHz) are critical parameters necessary to insure both optimum regulator performance and long capacitor life. Designing for Very Fast Load TransientsThe transient response of the DC/DC converter has been characterized using a load transient with a di/dt of 1 A/µs. The typical voltage deviation for this load transient is given in the data sheet specification table using the optional value of output capacitance. As the di/dt of a transient is increased, the response of a converter’s regu-lation circuit ultimately depends on its output capacitor decoupling network. This is an inherent limitation with any DC/DC converter once the speed of the transient exceeds its bandwidth capability. If the target application specifies a higher di/dt or lower voltage deviation, the requirement can only be met with additional output capacitor decoupling. In these cases special attention must be paid to the type, value and ESR of the capacitors selected.If the transient performance requirements exceed that specified in the data sheet, the selection of output ca-pacitors becomes more important. For further guidance consult the separate application note, “Selecting Output Capacitors for PTH Products in High-Performance Applica-tions.”PTH05000 SeriesTable 1-1: Input/Output Capacitors[1] A total capacitance of 300 µF is acceptable based on the surge current capability of ceramic capacitors.[2] A ceramic capacitor may be used to complement electrolytic types at the input to further reduce high-frequency ripple current./e p y T ,r o d n e V r o t i c a p a C )e l y t S (s e i r e S s c i t s i r e t c a r a h C r o t i c a p a C y t i t n a u Q gn i k r o W e g a t l o V )F µ(e u l a V RS E .x a M zH k 001t a e l p p i R .x a M C °58t a t n e r r u C )s m r I (e z i S l a c i s y h P )m m (t u p n I s u B t u p t u O s u B r e b m u N r o d n e V c i n o s a n a P )D M S (m u n i m u l A -y l o P ,A W )D M S (m u n i m u l A ,C F )D M S (m u n i m u l A ,K F )l a i d a R (m u n i m u l A ,C F V 01V 61V 61V 01F µ033F µ033F µ033F µ033.0530Ω051.0Ω061.0Ω711.0ΩA m 0082A m 076A m 006A m 0558×9.601×2.018×2.018×5.111111≤3≤3≤3≤3P 121A 1A W F E E P 133C 1C F V E E P 133C 1K F V E E 133A 1C F U E E n o C –i m e h C d e t i n U )D M S (m u l A -y l o P ,A X P )l a i d a R (n o c -s O ,S F )l a i d a R (m u n i m u l A ,Z X L )D M S (n u m i m u l A ,Z V M )l a i d a R (m u n i m u l A -y l o P ,A S P V 01V 01V 61V 52V 3.6033F µF µ033F µ033033F µF µ093420.0Ω520.0Ω021.0Ω071.0Ω800.0ΩA m 0773A m 0053A m 555A m 054A m 080501×7.701×5.018×218×018×5.1111111≤3≤3≤3≤3≤1P T 08J M 133C V 01A X P M 033S F 01L L 21x 8M 133B V 61Z X L P T 01H M 133C V 52Z V M 11H M 093B V 3.6A S P m u n i m u l A n o c i h c i N )D M S (G W )l a i d a R (M P V 61V 01033F µ033F µ051.0Ω061.0ΩA m 076A m 06401×018×5.1111≤3≤3S G 1R N M 133C 1G W U H H M 133A 1M P U o y n a S )D M S (n o c -s O ,P V S )l a i d a R (n o c -s O ,P S )D M S (r e m y l o P p a c s o P ,E P T V 01V 01V 3.6033F µF µ074F µ033520.0Ω510.0Ω520.0ΩA m 0073A m 0054A m 004201×801×5.01L 3.7×W 3.4111≤3≤2≤3X M 033P V S 01M 074P S 01L M 033E P T 6S P T m u l a t n a T X V A )D M S (V 01V 01F µ033F µ03301.00Ω060.0ΩA m 0011A m 0002L 3.7×W 3.4×H 1.411≤3≤30010R 010M 733V S P T 0600R 010M 733V S P T )D M S (t e m e K ,025T m u n i m u l A y l o P .m u l A -y l o P c i n a g r O ,035T V 01V 01F µ033F µ033040.0Ω510.0ΩA m 0021A m 0011L 3.7×W 7.5×H 0.411≤3≤2S A 010M 733X 025T S A 010M 733X 035T e u g a r p S -y a h s i V )D M S (m u l a t n a T ,D 495)D M S (m u l a t n a T ,D 595)D M S (n o c -s O ,P V S 49)l a i d a R (n o c -s O ,A S 49V 01V 01V 3.6V 3,6F µ033F µ033F µ033F µ033540.0Ω041.0Ω520.0Ω520.0ΩA m 0041A m 0001A m 0033A m 0053L 3.7×W 0.6×H 1.401×801×5.011111≤3≤3≤3≤3T 2R 0100X 733D 495T 2D 0100X 733D 5958F 3R 60X 733P V S 49P B F 3R 60X 733A S 49)D M S (R 5X c i m a r e C ,t e m e K V 61V3.60174200.0Ω200.0Ω—e s a c 0121m m 52231]2[1]2[≤3≤2C A P 4M 601C 0121C C A P 9K 674C 0121C c i m a r e C ,a t a r u M R 5X )D M S (V 3.6V 3.6V 61V61001742201200.0Ω—e s a c 0121m m 52233]1[1]2[1]2[1]2[1≤≤2≤3≤3M 701J 06R E 23M R G M 674J 06R E 23M R G K 622C 16R E 23M R G K 601C 16R D 23M R G c i m a r e C ,K D T R 5X )D M S (V 3.6V 3.6V 61V 61001742201200.0Ω—e s a c 0121mm 52233]1[1]2[1]2[1]2[1≤≤2≤3≤3T M 701J 0R 5X 5223C T M 674J 0R 5X 5223C T M 622C 1R 5X 5223C T M 601C 1R 5X 5223CAdjusting the Output Voltage of the PTH05000W Wide-Output Adjust Power ModulesThe V o Adjust control (pin 4) sets the output voltage of the PTH05000Wproduct. The adjustment range is from 0.9 V to 3.6 V . The adjustment method requires the addition of a single external resistor, R set , that must be connected directly between the V o Adjust and GND pins 1. T able 2-1 gives the preferred value of the external resistor for a number of standard voltages, along with the actual output voltage that this resistance value provides.For other output voltages the value of the required resistor can either be calculated using the following formula, or simply selected from the range of values given in T able 2-2.Figure 2-1 shows the placement of the required resistor.R set =10 k Ω ·0.891 V– 3.24 k ΩV out – 0.9 V Figure 2-1; V o Adjust Resistor PlacementNotes:e a 0.1 W resistor. The tolerance should be 1 %,with a temperature stability of 100 ppm/°C (or better).Place the resistor as close to the regulator as possible.Connect the resistor directly between pins 4 and 1using dedicated PCB traces.2.Never connect capacitors from V o Adjust to either GND or V out . Any capacitance added to the V o Adjust pin will affect the stability of the regulator.0.900Open 0.925353 k Ω0.950175 k Ω0.975116 k Ω1.00085.9 k Ω1.02568.0 k Ω1.05056.2 k Ω1.07547.7 k Ω1.10041.3 k Ω1.12536.4 k Ω1.15032.4 k Ω1.17529.2 k Ω1.20026.5 k Ω1.22524.2 k Ω1.25022.2 k Ω1.27520.5 k Ω1.30019.0 k Ω1.32517.7 k Ω1.35016.6 k Ω1.37515.5 k Ω1.40014.6 k Ω1.42513.7 k Ω1.45013.0 k Ω1.47512.3 k Ω1.5011.6 k Ω1.5510.5 k Ω1.609.49 k Ω1.658.64 k Ω1.707.90 k Ω1.757.24 k Ω1.806.66 k Ω1.856.14 k Ω1.905.67 k Ω1.95 5.25 k ΩV out (Standard)R set (Pref ’d Value)V out (Actual)3.3 V 475 Ω 3.298V 2.5 V 2.32 k Ω 2.502 V 2 V 4.87 k Ω 1.999 V 1.8 V6.65 k Ω 1.801 V 1.5 V 11.5 k Ω 1.504 V 1.2 V 26.1 k Ω 1.204 V 1 V 84.5 k Ω 1.001 V 0.9 V Open 0.9 V Table 2-1; Preferred Values of R set for Standard Output Voltages Table 2-2; Output Voltage Set-Point Resistor Values V a Req ’d R set V a Req ’d R set 2.00 4.86 k Ω2.05 4.51 k Ω2.10 4.19 k Ω2.15 3.89 k Ω2.20 3.61 k Ω2.25 3.36 k Ω2.30 3.12 k Ω2.35 2.90 k Ω2.40 2.70 k Ω2.45 2.51 k Ω2.50 2.33 k Ω2.55 2.16 k Ω2.60 2.00 k Ω2.65 1.85 k Ω2.70 1.71 k Ω2.75 1.58 k Ω2.80 1.45 k Ω2.85 1.33 k Ω2.90 1.22 k Ω2.95 1.11 k Ω3.00 1.00 k Ω3.05904 Ω3.10810 Ω3.15720 Ω3.20634 Ω3.25551 Ω3.30473 Ω3.35397 Ω3.40324 Ω3.45254 Ω3.50187 Ω3.55122 Ω3.6060 ΩPTH05000WOutput On/Off Inhibit For applications requiring output voltage on/off control,the PTH03000W & PTH05000W power modules in-corporate an output on/off Inhibit control (pin 3). The inhibit feature can be used wherever there is a require-ment for the output voltage from the regulator to be turned off.The power module functions normally when the Inhibit pin is left open-circuit, providing a regulated output whenever a valid source voltage is connected to V in with respect to GND .Figure 3-2 shows the typical application of the inhibit function. Note the discrete transistor (Q 1). The Inhibit control has its own internal pull-up to V in potential. An open-collector or open-drain device is recommended to control this input.T urning Q 1 on applies a low voltage to the Inhibit control pin and disables the output of the module. If Q 1 is thenturned off, the module will execute a soft-start power-up sequence. A regulated output voltage is produced within 20 msec. Figure 3-3 shows the typical rise in the out-put voltage, following the turn-off of Q 1. The turn off of Q 1 corresponds to the fall in the waveform, Q 1 V gs . The waveforms were measured with a 5-A resistive load.Figure 3-2Figure 3-3Power-Up CharacteristicsWhen configured per their standard application, the PTH03000 and PTH05000 series of power modules will produce a regulated output voltage following the appli-cation of a valid input source voltage. During power up,internal soft-start circuitry slows the rate that the output voltage rises, thereby limiting the amount of in-rush current that can be drawn from the input source. The soft-start circuitry introduces a short time delay (typi-cally 10 ms) into the power-up characteristic. This is from the point that a valid input source is recognized.Figure 3-1 shows the power-up waveforms for a PTH05000W (5-V input), with the output voltage set point adjusted for a 2-V output. The waveforms were measured with a 5-A resistive load. The initial rise in input current when the input voltage first starts to rise is the charge current drawn by the input capacitors.Figure 3-1Current Limit ProtectionThe PTHxx000W modules protect against load faults with a continuous current limit characteristic. Under a load fault condition the output current cannot exceed the current limit value. Attempting to draw current that exceeds the current limit value causes the output voltage to be progressively reduced. Current is continuously supplied to the fault until it is removed. Upon removal of the fault, the output voltage will promptly recover.Thermal ShutdownThermal shutdown protects the module’s internal circuitry against excessively high temperatures. A rise in tempera-ture may be the result of a drop in airflow, a high ambient temperature, or a sustained current limit condition. If the junction temperature of the internal components exceed 150 °C, the module will shutdown. This reduces the output voltage to zero. The module will start up automatically, by initiating a soft-start power up when the sensed temperature decreases 10 °C below the thermal shutdown trip point.PTH03000 & PTH05000 SeriesV Vo (1 V/Div)Q1 Vgs (10 V/Div)HORIZ SCALE: 5 ms/Div Vin (2 V/Div)Vo (1 V/Div)Iin (2 A/Div)HORIZ SCALE: 5 ms/DivPTH05000W Startup with Output Pre-BiasA pre-bias startup condition occurs as a result of an external voltage being present at the output of the power module prior to its output voltage rising. This often occurs in complex digital systems when current from another power source is backfed through a dual-supply logic component such as an FPGA or ASIC. Another path might be via clamp diodes (to a higher supply voltage) as part of a sequential power-up arrangement.An output prebias can cause problems with power modules that incorporate synchronous rectifiers. This is because under most operating conditions, they can sink as well as source ouput current. Although the PTH05000W (5-V input) power module can sink current under normal op-eration, it will not do so during startup. 1 This is true as long as certain conditions are maintained. 2 Figure 3-1shows an application schematic that demonstrates this capability. Figure 3-2 shows the waveforms of the circuit after input power is applied. Note that the module’s out-put current (I o ) is never negative. Only positive current is sourced. This occurs when the output voltage is raised above that which is backfed from the 5-V input supply, via the diodes D 1 through D 4. 3Notes1.Start up includes both the application of a valid inputsource voltage, or the removal of a ground signal from the Inhibit* control (pin 3) with a valid input source applied. The output of the regulator is effectively off (tri-state), during the period that the Inhibit* control is held low.Figure 3-2; Start-up with Output Pre-Bias Figure 3-1; Schematic Demonstrating Startup with Output Pre-Bias2.T o ensure that the regulator does not sink current, the input voltage must always be greater or equal to the output voltage throughout the power-up and power-down sequence.3.If during power up, the backfeeding source is greater than the module’s set-point voltage, the module’s output voltage will remain higher than its set point.The output will remain out of regulation until the back-feeding source is either reduced in voltage or removed.PTH05000WVin (1 V/Div)Vo (1 V/Div)Io (2 A/Div)HORIZ SCALE: 5 ms/DivV D 1 - D 4MUR4600.55 ΩResistiveIMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard warranty. T esting and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. T o minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements. Following are URLs where you can obtain information on other Texas Instruments products and application solutions:Products ApplicationsAmplifiers Audio /audioData Converters Automotive /automotiveDSP Broadband /broadbandInterface Digital Control /digitalcontrolLogic Military /militaryPower Mgmt Optical Networking /opticalnetwork Microcontrollers Security /securityTelephony /telephonyVideo & Imaging /videoWireless /wirelessMailing Address:Texas InstrumentsPost Office Box 655303 Dallas, Texas 75265Copyright 2004, Texas Instruments Incorporated。

优斯特(Opto)标准交流AC电机刹车包 SB50 技术参考手册说明书

Brake Pack for Standard AC MotorsA-180System Configuration A-182Features A-180Specifications A-182Brake Pack for Standard AC MotorsSB50The SB50provides instantaneous stop, forward/reverse operation, electromagnetic brake control and thermal-protector open-detection functions integrated into one unit.These brake packs can sense when the thermal protector is opened, further ensuring the safety of your equipment. The SB50can be used with induction motors, reversible motors,watertight motors and electromagnetic brake motors.SB50ⅥFeaturesⅷFour Functions in One Integrated UnitThe SB50provides instantaneous stop, forward/reverse operation, electromagnertic brake control and thermal protector open detection functions.✽Thermal protector open detection functionWhen the motor's thermal protector (overheat protection device) is activated, the SB50outputs an alarm signal and automatically cuts the power supply to the motor. The motor will not restart by itself, even when the temperature drops and the thermal protector recovers, until the power is cycled. (Available only when combined with a motor having a built-in thermal protector).ⅷInstantaneous StopThe electronic brake stops the motor instantly. A largebraking force causes the motor to stop in approximately 0.1seconds, allowing for an overrun of 1.0 to 1.5 revolutions.The braking current flows through the motor forapproximately 0.4 seconds, after which the power supply to the motor is cut off automatically (the motor will lose its holding brake force).ⅷLong Life, Simple Wiring and Maintenance-FreeThe electronic brake operates on current flow, so it lastslonger than the mechanically operated electromagnetic brake that is subject to wear. This makes the SB50ideal forindexing applications. The Electronic type input brake pack doesn’t use a power relay, so no maintenance is required.Wiring is easy, as well.To powersupply/motor ➝Electronic type input brake packSimple wiring ⅷWide Voltage Range of 100 to 230 VACThe SB50covers a single-phase voltage range of 100 to 230VAC ע10%, 50/60 Hz, accommodating all of the world's key voltage specifications.ⅷSupports Motors with 1W to 90W OutputThe SB50can be used with induction, reversible,electromagnetic brake and dust-resistant, watertight motors with an output range of 1W to 90W.ⅷBrake Pack with an Electromagnetic Brake MotorBy combining the SB50with a motor equipped with anelectromagnetic brake, you can link the electronic brake with the electromagnetic brake to allow the load to be held automatically following an instantaneous stop. Thisconfiguration is ideal for vertical applications in which the load must be held following the instantaneous stopping of themotor.SB50A-181Dimensions A-183Connection Diagrams A-186Characteristics A-183Induction Motors Synchronous MotorsTorque Motors Watertight Motors Magnetic BrakeClutch &Brake Brake Pack Reversible Motors Right-Angle Gearheads AccessoriesIntroductionBefore Using a Standard AC MotorⅥCharacteristics of Brake PackⅷHow to Read Braking Characteristics (reference values)The brake pack provides stable braking characteristics for the instantaneous stopping of the motor. The braking characteristics are illustrated by the braking curve, which indicates the amount of shaft overrun corresponding to the load inertia. The braking time is [4n/f] seconds or less (where n: overrun, f: power supply frequency).For example, if the 4IK25GN-AWU (single-phase 115VAC, 25 W) and SB50are used together to stop a load with an inertia of J = 1.37 oz-in 2(0.25 ϫ10-4kg ⅐m 2), the overrun and braking time required will be approximately 1.4revolutions and 0.1 second, respectively, at a power-supply frequency of 60 Hz. In the case of deceleration using a gearhead, see the braking characteristics curve after converting the load inertia at the gearhead shaft to its corresponding value at the motor shaft.Use the following formula to convert the load inertia at the gearhead shaft to its corresponding value at the motor shaft:J M : Load inertia converted to corresponding value at motor shaft J G : Load inertia at gearhead shaft i: Gear ratio of gearhead[oz-in 2]J Gi 2J M ϭⅥOther Brake MotorsIn addition to the brake pack, various brake motors are available to suit a variety of applications.ⅷHow to Select a Brake Motor◆Selecting based on stopping accuracy◆Selecting based on frequency of useNotes:●The operating cycles are based merely on brake response. The value specified above is the maximum, so it may not be possible to repeat braking operation at this frequency.●In an actual application, be certain the surface temperature of the motor case remains below 194°F (90˚C) by considering a rise in motor temperature.ⅷExample of Braking Characteristics with Brake PackBrake Pack: SB50Motor: 4IK25GN-AWUO v e r r u n [Ro t a t i o n s ][oz-in 2][ϫ10Ϫ4kg ⅐m 2]Load Inertia J 0.10.20.30.40.50.6ⅷStopping AccuracyThe figure to the right shows the stopping position error(variation in stopping position) when braking force is applied to the motor using the brake pack. The diagram shows an overrun distribution when braking is repeated 500 times under the same conditions. Varying stopping positions are caused by the power-supply phase when the switch is operated to apply the brake, which could generate amaximum delay of one cycle (power supply frequency) and variation in initial braking force. The sagging at the center reflects the slot-position relationship between the stator and rotor. Refer to the braking characteristics curve representing the average overrun.Brake Pack: SB50Motor: 4IK25GN-AWUJ: 1.37 oz-in 2(0.25ϫ10-4kg ⅐m 2)Overrun (Revolutions )N u m b e r o f b r a k i n g o p e r a t i o n sA-182System Configuration A-182Features A-180Specifications A-182Capacitor Cap(Included with motor)Flush Mounting Socket (Included with Brake Pack)Mounting Bracket (Accessories)Gearhead(Sold Separately)The system configuration shown is an example. Other combinations are available.ⅥApplicable ProductsⅥBraking CurrentWhen a motor is stopped suddenly, a large half-wave rectified current flows through the motor for 0.2 to 0.4 seconds. When connecting a circuit breaker, fuse or transformer, refer to the table below for the braking current (peak value) and select its current capacity.K Series 1 WInduction Motors Reversible MotorsWorld K Series ✽6 W ϳ90 W V Series 6 W ϳ90 W FPW Series 25 W ϳ90 WInduction Motors Reversible MotorsElectromagnetic Brake Motors Induction Motors Reversible MotorsElectromagnetic Brake Motors Induction Motors●List of Safety Standard Approved Products ➝Page G-14●The EMC value changes according to the wiring and layout. Therefore, the final EMC level must be checked with the Brake Pack incorporated in the user’s equipment.✽Excluding 2-pole typeA-183Dimensions A-183Connection Diagrams A-186Characteristics A-183Induction Motors Synchronous MotorsTorque MotorsWatertight Motors Magnetic BrakeClutch &BrakeBrake PackReversible Motors Right-AngleGearheads AccessoriesIntroduction Before Using a Standard AC MotorⅥDimensions Scale 1/4, Unit = inch (mm)ⅷFlush Mounting Socket Panel Cut-OutⅷFlush Mounting Socket (Included with brake pack)SB50Weight: 0.22 lb. (0.1 kg)ÇA092ⅥBraking Characteristics (Reference Values)ⅷV Series, World K Series, K SeriesO v e r r u n [R o t a t i o n s ]Induction Motors: 1 W(1/750 HP)[oz-in 2]J [ϫ10kg ⅐m ]Load Inertia 0.0050.0100.0150.0200.0250.0300O v e r r u n [R o t a t i o n s ]Induction Motors: 6 W(1/125 HP)[oz-in 2] J [ϫ10kg ⅐m ]Load Inertia0.0250.0500.0750.1000.1250O v e r r u n [R o t a t i o n s ]Induction Motors: 15 W(1/50 HP)[oz-in 2] J [ϫ10kg ⅐m ]Load Inertia0.050.100.150.200.250O v e r r u n [R o t a t i o n s ][oz-in 2] J [ϫ10kg ⅐m ]Load Inertia0.10.20.30.40.50.60Induction Motors: 25 W(1/30 HP)O v e r r u n [R o t a t i o n s ]Induction Motors: 40 W(1/19 HP)[oz-in2] J [ϫ10kg ⅐m ]Load Inertia 0.250.500.75 1.00 1.25O v e r r u n [R o t a t i o n s ]Induction Motors: 60 W(1/12 HP)[oz-in 2]J [ϫ10kg ⅐m ]Load Inertia0.51.0 1.52.00A-184System Configuration A-182Features A-180Specifications A-182O v e r r u n [R o t a t i o n s ]Induction Motors: 90 W(1/8 HP)[oz-in 2]J [ϫ10kg ⅐m ]Load Inertia0.51.0 1.52.00O v e r r u n [R o t a t i o n s ]Reversible Motors: 1 W(1/750 HP)[oz-in 2]J [ϫ10kg ⅐m ]Load Inertia 0.0050.0100.0150.0200.0250.0300O v e r r u n [R o t a t i o n s ]Reversible Motors: 6 W(1/125 HP)[oz-in 2] J [ϫ10kg ⅐m ]Load Inertia 0.0250.0500.0750.1000.1250O v e r r u n [R o t a t i o n s ]Reversible Motors: 15 W(1/50 HP)[oz-in 2] J [ϫ10kg ⅐m ]Load Inertia0.050.100.150.200.250O v e r r u n [R o t a t i o n s ]Reversible Motors: 25 W(1/30 HP)[oz-in 2] J [ϫ10kg ⅐m ]Load Inertia0.10.20.30.40.50.60O v e r r u n [R o t a t i o n s ]Reversible Motors: 40 W(1/19 HP)[oz-in 2] J [ϫ10kg ⅐m ]Load Inertia0.250.500.75 1.01.250O v e r r u n [R o t a t i o n s]Reversible Motors: 60 W(1/12 HP)[oz-in 2]J [ϫ10kg ⅐m ]Load Inertia0.51.0 1.52.00O v e r r u n [R o t a t i o ns ]Electromagnetic Brake Motors: 90 W(1/8 HP)[oz-in 2]J [ϫ10kg ⅐m ]Load Inertia0.51.0 1.52.00ⅷV Series, World K Series, K SeriesA-185Dimensions A-183Connection Diagrams A-186Induction Motors Synchronous MotorsTorque MotorsWatertight Motors Magnetic BrakeClutch &BrakeBrake Pack Reversible Motors Right-Angle Gearheads AccessoriesIntroductionBefore Using a Standard AC MotorO v e r r u n [R o t a t i o n s]Electromagnetic Brake Motors: 6 W(1/125 HP)[oz-in 2] J [ϫ10kg ⅐m ]Load Inertia 0.0250.0500.0750.1000.1250O v e r r u n [R o t a t i o n s ]Electromagnetic Brake Motors: 15 W(1/50 HP)[oz-in 2] J [ϫ10kg ⅐m ]Load Inertia0.050.100.150.200.250O v e r r u n [R o t a t i o n s ]Electromagnetic Brake Motors: 25 W(1/30 HP)[oz-in 2] J [ϫ10kg ⅐m ]Load Inertia0.10.20.30.40.50.60O v e r r u n [R o t a t i o n s]Electromagnetic Brake Motors: 40 W(1/19 HP)[oz-in 2] J [ϫ10kg ⅐m ]Load Inertia0.250.500.75 1.001.250O v e r r u n [R o t a t i on s ]Electromagnetic Brake Motors: 60 W(1/12 HP)[oz-in 2]J [ϫ10kg ⅐m ]Load Inertia0.51.0 1.52.00O v e r r u n [R o t a t i on s ]Electromagnetic Brake Motors: 90 W(1/8 HP)[oz-in 2]J [ϫ10kg ⅐m ]Load Inertia0.51.0 1.52.00O v e r r u n [R o t a t i o n s ]Watertight Motors: 25 W(1/30 HP)[oz-in 2]J [ϫ10kg ⅐m ]Load Inertia0.10.20.30O v e r r u n [R o ta t i o n s ]Watertight Motors: 40 W(1/19 HP)[oz-in 2]J [ϫ10kg ⅐m ]Load Inertia0.250.500.75ⅷFPW Series (Watertight Motors)ⅷV Series, World K SeriesA-186System Configuration A-182Features A-180Specifications A-182O v e r r u n [R o t a t i o n s ]Watertight Motors: 60 W(1/12 HP)0.250.500.75 1.001.250[oz-in 2] J [ϫ10kg ⅐m ]Load Inertia O v e r r u n [R o t a t i o n s]Watertight Motors: 90 W(1/8 HP)[oz-in2]J [ϫ10kg ⅐m ]Load Inertia 0.51.0 1.52.02.50ⅥConnection and OperationPOWER Indicator (Green)Lit when 24 VDC is supplied ALARM Indicator (Red)Lit when the ALARM output is "OFF"The white square section of the switch represents the switch lever position.ⅷConnection DiagramsSingle-Phase 220/230 VACBrake Pack Terminal No.✽ Single-Phase 110/115 VAC Single-Phase 220/230 VAC✽Brake Pack Terminal BoxFor the 6 W motor, there is no Protective Earth terminal.Colors in parentheses ( ) are for the lead wires of the reversible 1 W motor.Electromagnetic MotorsInduction Motors (except 1W), Reversible Motors◆V Series, World K Series, K SeriesⅷContact Capacity of SW1Single-phase 100-115 VAC: 125 VAC 5 A or more (Inductive load)Single-phase 200-230 VAC: 250 VAC 5 A or more (Inductive load)A-187Dimensions A-183Connection Diagrams A-186Characteristics A-183AC MotorsInduction Motors Synchronous MotorsTorque MotorsWatertight Motors Magnetic BrakeClutch &BrakeBrake PackReversible Motors Right-Angle Gearheads AccessoriesIntroductionBefore Using a Standard AC Motor◆K SeriesInduction Motors 1 W Type (0IK1GN-AUL, 0IK1A-AUL )CCW operation input is not used.ⅷContact Capacity of SW1Single-phase 100-115 VAC: 125 VAC 5 A or more (Inductive load)Single-phase 200-230 VAC: 250 VAC 5 A or more (Inductive load)Brake Pack ✽ Single-Phase 110/115 VAC Single-Phase 220/230 VAC◆FPW SeriesInduction Motors✽ Single-Phase 110/115 VACBrake Pack Counterclockwise Operation✽ Single-Phase 110/115 VACBrake Pack Clockwise Operation✽2Not used with an induction motor with four lead wires.✽3Only for motors with a built-in thermal protector.✽4Only for electromagnetic brake motors.Notes:●The input-signal voltage is 24 VDC Ϯ10% and 0.1 A or more.●Minimize the length of the motor cable and the input/output signal cable to reduce EMI.●Use a cable of AWG 18 or more in diameter for the motor cable and power cable.●Be sure to connect the GND terminal to GND (negative side) of the external controller, or the unit will not operate.ⅷI/O Signal Circuit᭜Input Circuit (Internal Circuit)The input-signal voltage is 24 VDC Ϯ10%.᭜Output Circuit (Internal Circuit)Output signals are open-collector outputs. Use a power source of 26.4VDC or less, and limit the output current to 10 mA or less.CW Operation CCW Operation Brake ReleaseⅷTiming Chart✽1✽2✽3Set the CW operation input, CCW operation input and brake release input toON after turning on the AC power.Setting these inputs to ON before turning on the AC power will not enablemotor operation. The ALARM indicator will light and ALARM output willswitch to "OFF."Only for motors with electromagnetic brakes.The induction motor will not accommodate instantaneous forward/reverse switching.Change the direction of motor rotation only after bringing the motor to a stop.ࡗCW Operation InputT urning the CW operation signal to “Photocoupler ON”causes the motor’s output shaft to turn in the CW direction.T urning it to “Photocoupler OFF” triggers an instantaneousstop.ࡗCCW Operation InputT urning the CCW operation signal to “Photocoupler ON”causes the motor’s output shaft to turn in the CCW direction.T urning it to “Photocoupler OFF” triggers an instantaneousstop.If both the CW and CCW operation signals aresimultaneously turned to “Photocoupler ON,” the CWoperation signal will take priority. Therefore, the wiring mustbe changed with an induction motor having four lead wires.ࡗBrake Release InputT urning the brake release signal to “Photocoupler ON”disables both the electronic brake and electromagneticbrake. When the CW and CCW operation signals are turnedto “Photocoupler OFF,” the motor operates via inertial forcebefore coming to a natural stop. When the motor isstationary, the electromagnetic brake does not operate, sothe motor’s output shaft can be moved freely.T urning the brake release signal to “Photocoupler OFF” (orleaving the signal unconnected) and turning the CW andCCW operation signals to “Photocoupler OFF” will activatethe electronic brake and electromagnetic brake, bringing themotor to an instantaneous stop. Once the motor stops, theelectronic brake will release automatically. However, theelectromagnetic brake will continue to operate and hold theload.ⅷOperating/Braking Repetition CycleThe repeated operation and braking of a motor will causeabout a temperature increase in the motor and brake pack,thereby limiting the continuous operating time. Observe therepetition cycle given in the table below for the operation andbraking of the motor. The motor may generate heatdepending on the conditions in which it is driven. Ensure thatthe temperature of the motor case does not exceed 194°F(90˚C).(A repetition cycle of two seconds represents operation for one second andstopping for one second.)ⅷThermal-Protector Open DetectionIf the built-in thermal protector is triggered to "open" duringoperation, the brake pack will turn the ALARM output to"OFF" and light the ALARM indicator lamp (red) on the panel(while the motor stops as the power goes off).With electromagnetic brake motors, the brake is activated inorder to hold the load in position.In the case of a motor which does not have a built-in thermalprotector, the ALARM output will not be turned to "OFF."When ALARM output is turned to "OFF," turn all power offand set input signals to "OFF."Use a power source of 26.4 VDC or less, and limit the output current to 10 mA or less.A-188。

SB540中文资料

100

10

Tj = 100°C

3

1.0

Tj = 25°C

2

1

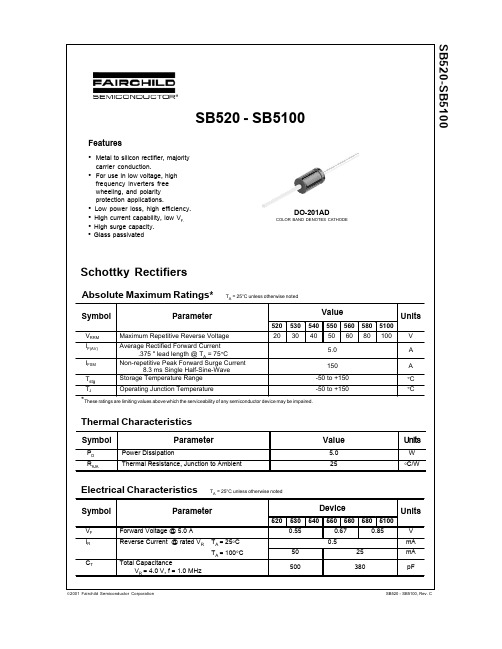

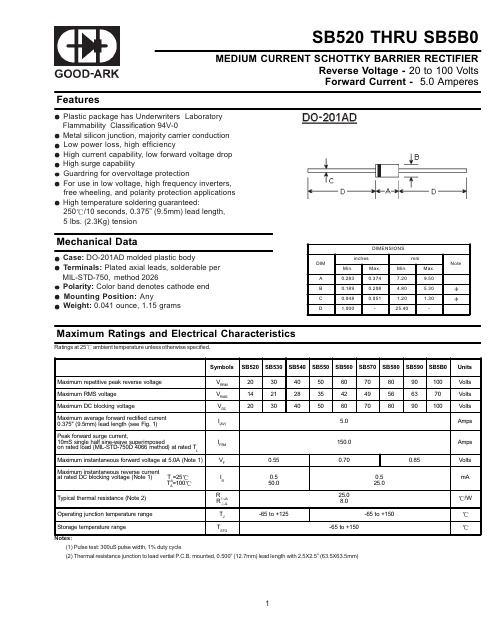

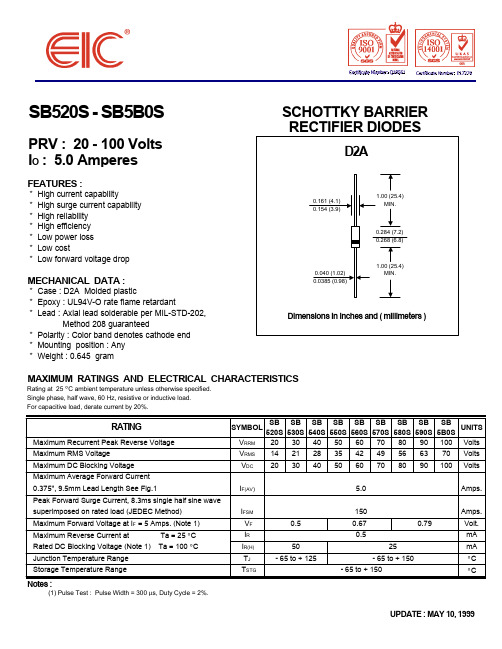

Resistive or Inductive Load 0.375” (9.5mm) lead length SB520 - SB540 SB550 & SB560

0.1

0 0 25 50 75 100 125 150

0.01 0 0.2 0.4 0.6 0.8 VF, INSTANTANEOUS FORWARD VOLTAGE (V) Fig. 2 Typical Forward Characteristics, SB520 - SB540

1. Measured at ambient temperature at a distance of 9.5mm from case. 2. Short duration test pulse used to minimize self-heating effect. 3. Thermal resistance junction to lead vertical P.C.B. mounted, 0.375" (9.5mm) lead length.

All Dimensions in mm

Maximum Ratings and Electrical Characteristics

Single phase, half wave, 60Hz, resistive or inductive load. For capacitive load, derate current by 20%. Characteristic Peak Repetitive Reverse Voltage Working Peak Reverse Voltage DC Blocking Voltage RMS Reverse Voltage Average Rectified Output Current (See Figure 1) (Note 1) Non-Repetitive Peak Forward Surge Current 8.3ms single half sine-wave superimposed on rated load (JEDEC Method) Forward Voltage (Note 2) Peak Reverse Current at Rated DC Blocking Voltage (Note 2) @ IF = 5.0A @ TA = 25°C @ TA = 100°C Symbol VRRM VRWM VR VR(RMS) IO IFSM VFM IRM RqJA RqJL Tj TSTG

MAA50-2K481515SBP中文资料

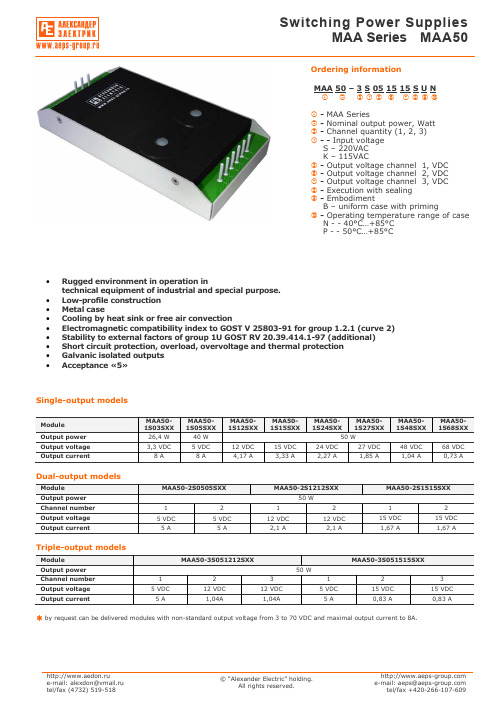

Switching on standart diagram

~In (L) ~In (N)

ground

FUin

~In (L) ~In (N)

+Out

Power module

Case

-Out

Сout1 Сout2

Rheat

FUin – current safety device 1A for input voltage 220VAC, 2A for input voltage 115VAC. Sout – ceramic condenser capacity 0,47-15 mcF with corresponding operating voltage to decrease high-frequency noise level. Sout2 – electronic condenser capacity 22-100 mcF in consideration with operating voltage and polarity. It makes for purpose to decrease

tel/fax +420-266-107-609

元器件交易网

Switching Power Supplies МАА Series MAA50

Output settings

№ pin Single-channel Dual-channel Triple-channel

1 case case case

Uout1 less than 20%

Output 2 and 3 multi-output execution (Inom 10 – 100%)

±13

Uout2&3 differs from

PSD-0505中文资料

Copyright PEAK electronics GmbH

Partnumbers

PART NO. INPUT VOLTAGE (VDC) INPUT CURRENT FULL LOAD OUTPUT VOLTAGE (VDC) OUTPUT CURRENT (max. mA) EFFICIENCY FULL LOAD (% TYP.)

PSD-3R305S PSD-053R3S PSD-0505S PSD-0509S PSD-0512S PSD-123R3S PSD-1205S PSD-1209S PSD-1212S PSD-1215S

3.3 5 5 5 5 12 12 12 12 12

450 171 246 254 252 73 100 105 103 100

5 3.3 5 9 12 3.3 5 9 12 15

200 200 200 110 84 200 200 110 84 67

70 77 81 78 80 75 81 78 81 83

元器件交易网

Telefon: +49 (0) 6135 931069 Telefax: +49 (0) 6135 931070 www.peak-eltronics.de

SMD SERIES

PSD-XXXXS 1KV ISOLATED 1W UNREGULATED SINGLE OUTPUT SMD

Ambient Temperature ° C 85

1.00 W

Pin # 1 3 7 8 14

Connection Single - V Input + V Input - V Output + V Output NC

B1205中文版的资料

O u tp u t P o w e r (W )

5V & 12V Input

1.5

24V & 48V Input 70° c 85° c

1

0.5

0 -40° c

0° c

50° c

100° c

150° c

A m b ie n t T e m p e ra tu re ( C )

Industry standard来自pinoutSELECTION GUIDE

Input Order Code Voltage (V) B0505S-1W B0509S-1W B0512S-1W B0515S-1W B0524S-1W B1205S-1W B1209S-1W B1212S-1W B1215S-1W B2405S-1W B2409S-1W B2412S-1W B2415S-1W B4805S-1W B4809S-1W B4812S-1W B4815S-1W 5 5 5 5 5 12 12 12 12 24 24 24 24 48 48 48 48 Output Voltage (V) 5 9 12 15 24 5 9 12 15 5 9 12 15 5 9 12 15 Output Current (mA) 200 111 83 66 42 200 111 83 66 200 111 83 66 200 111 83 66 Input Current (Rated Load) (mA) 289 260 256 250 248 120 115 110 115 60 56 52 52 30 28 26 26 Efficiency % 70 77 78 80 80 69 74 76 72 70 75 80 80 70 75 80 80 Isolation Capacitance pF 48 37 33 40 48 33 48 55 48 40 59 78 79 32 50 76 75 MTTF1 kHrs 290 1173 633 360 290 620 488 360 488 201 185 163 136 213 194 164 140 SIP Package Style

ABB功能码中文资料

第一章功能码概述一、专用术语·功能码(Function Code):Symphony 系统提供了一系列完成不同功能的软件模块,并对每个软件模块指定一个代码,称为功能码。

·功能码数据库(Function Code Library):指功能码的集合,它存放在各种控制器的只读存储器(ROM)中。

每一种控制器的ROM中只存放该控制器组态所能使用的功能码。

·功能块(Function Block):当选用一个功能码时,必需指定一个块号(即块地址),该选定了的功能码称为功能块。

·规格参数(Specification)指功能码的输入参数。

规格参数有两种类型:-地址类的规格参数;-内部规格参数。

·功能码组态:根据过程控制方案,选择一些合适的功能码,将其互相连接,并对每个功能码指定其具体功能,将其存放到控制器的NVRAM中的过程称为功能码组态。

二、功能块SYMPHONY系统是由一套运用微处理器执行控制功能的模件组成的。

通过组态“功能块”,在主模件上实现控制功能的选择和相互配合。

一个功能块仅仅是一个输入或输出,或者是一个输入或输出的操作。

这些功能块是一般的软件控制算法,可以用它们来执行在其它类型系统需要专门硬件完成的指定任务。

有四种类型功能块:1.执行块2.系统常数块3.输入/输出块4.用户组态块执行块包含影响模件综合操作的一些参数。

系统常数块例如是0、1和100.0等这样的一些数字量参数和模拟量参数。

当用这些通常所用的值进行模件组态时,只要可能就应尽量使用这些系统常数块。

它们要求的内存比手动设定常数块少。

输入/输出块是一些固定块地址,它们对应于一个模件通过端子单元和现场布线的现场输入和输出。

用户组态块不是预先指定的块,而是由用户设定,以执行用户特需功能从而实现控制逻辑。

每个SYMPHONY主模件都有一套供选择的预先定义的块地址。

功能块的最基本类型是输入和输出。

每个输入或输出都在该模件的固件中被赋予一个块号。

SB540_NL中文资料

40

SB520-SB540

20 10 Reverse Current, IR [mA]

SB520-SB540 SB550-SB5100 T A = 100 º C

Forward Current, IF [A]

10

SB580-SB5100

1

SB520-SB540 TA = 75º C

SB550-SB560

90

2

60

1

30

0

0

25

50 75 100 125 Ambient Temperature [ºC]

150

175

0

2

5 10 20 50 Number of Cycles at 60Hz

100

Figure 1. Forward Current Derating Curve

Figure 2. Non-Repetitive Surge Current

(continued)

Typical Characteristics

Average Rectified Forward Current, IF [A]

4

SB520-SB540 SB550-SB5100

Peak Forward Surge Current, IFSM [A]

5

150

120

3

SINGLE PHASE HALF WAVE 60HZ RESISTIVE OR INDUCTIVE LOAD .375" (9.00mm) LOAD LENGTHS

LIFE SUPPORT POLICY FAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein: 1. Life support devices or systems are devices or 2. A critical component is any component of a life systems which, (a) are intended for surgical implant into support device or system whose failure to perform can the body, or (b) support or sustain life, or (c) whose be reasonably expected to cause the failure of the life failure to perform when properly used in accordance support device or system, or to affect its safety or with instructions for use provided in the labeling, can be effectiveness. reasonably expected to result in significant injury to the user. PRODUCT STATUS DEFINITIONS Definition of Terms Datasheet Identification Advance Information Product Status Formative or In Design Definition This datasheet contains the design specifications for product development. Specifications may change in any manner without notice. This datasheet contains preliminary data, and supplementary data will be published at a later date. Fairchild Semiconductor reserves the right to make changes at any time without notice in order to improve design. This datasheet contains final specifications. Fairchild Semiconductor reserves the right to make changes at any time without notice in order to improve design.

LH0070-1H-MIL中文资料