P3057LCG中文资料

锂电池保护模块说明书 HT7Q1520

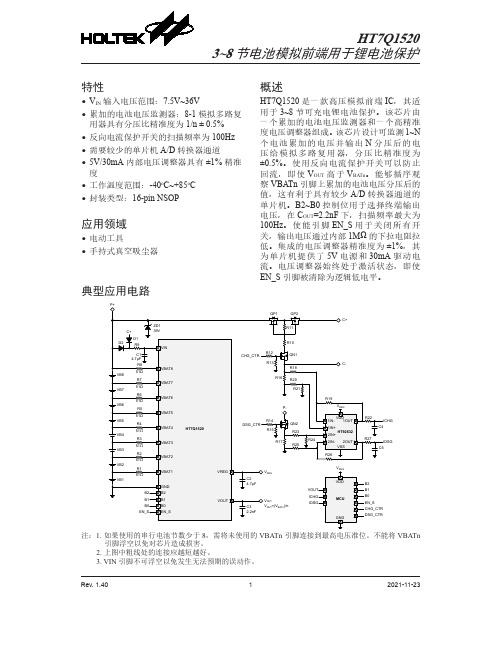

Rev. 1.4012021-11-23HT7Q15203~8节电池模拟前端用于锂电池保护特性•V IN 输入电压范围:7.5V~36V•累加的电池电压监测器:8-1模拟多路复用器具有分压比精准度为1/n ± 0.5% •反向电流保护开关的扫描频率为100Hz •需要较少的单片机A/D 转换器通道•5V/30mA 内部电压调整器具有±1%精准度•工作温度范围:-40o C~+85o C •封装类型:16-pin NSOP应用领域•电动工具•手持式真空吸尘器概述HT7Q1520是一款高压模拟前端IC ,其适用于3~8节可充电锂电池保护。

该芯片由一个累加的电池电压监测器和一个高精准度电压调整器组成。

该芯片设计可监测1~N 个电池累加的电压并输出N 分压后的电压给模拟多路复用器,分压比精准度为±0.5%。

使用反向电流保护开关可以防止回流,即使V OUT 高于V BATn 。

能够循序观察VBATn 引脚上累加的电池电压分压后的值,这有利于具有较少A/D 转换器通道的单片机。

B2~B0控制位用于选择终端输出电压,在C OUT =2.2nF 下,扫描频率最大为100Hz 。

使能引脚EN_S 用于关闭所有开关,输出电压通过内部1M Ω的下拉电阻拉低。

集成的电压调整器精准度为±1%,其为单片机提供了5V 电源和30mA 驱动电流。

电压调整器始终处于激活状态,即使EN_S 引脚被清除为逻辑低电平。

典型应用电路注:1. 如果使用的串行电池节数少于8,需将未使用的VBATn 引脚连接到最高电压准位。

不能将VBATn引脚浮空以免对芯片造成损害。

2. 上图中粗线处的连接应越短越好。

3. VIN 引脚不可浮空以免发生无法预期的误动作。

Rev. 1.4022021-11-23功能方框图VOUTVREG引脚图VBAT8VBAT7VBAT6VOUT B2B1B0EN_S VBAT1VBAT5VBAT4VBAT3VBAT2VIN VREGGNDHT7Q152016 NSOP-A16151413121110912345678极限参数建议工作范围注:极限参数表示超过所规定范围将可能对芯片造成损害。

THM3050 用户手册

TP3057B_整体式串行接口的PCM编解码器和过滤器]

![TP3057B_整体式串行接口的PCM编解码器和过滤器]](https://img.taocdn.com/s3/m/0b545a146edb6f1aff001f69.png)

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.TP3054B, TP3057B, TP13054B, TP13057BTP3054B, TP3057B, TP13054B, TP13057BTP3054B, TP3057B, TP13054B, TP13057BIMPORTANT NOTICETexas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI’s standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE (“CRITICAL APPLICATIONS”). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER’S RISK.In order to minimize risks associated with the customer’s applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI’s publication of information regarding any third party’s products or services does not constitute TI’s approval, warranty or endorsement thereof.Copyright © 1998, Texas Instruments Incorporated。

zl30109中文资料_数据手册_IC数据表

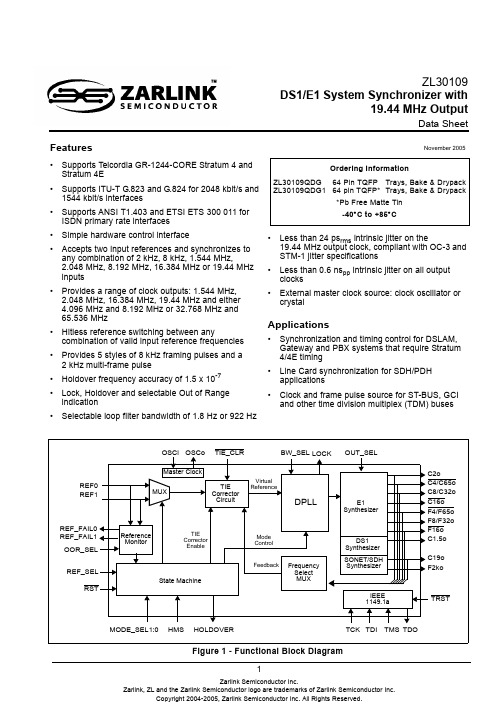

1Features•Supports Telcordia GR-1244-CORE Stratum 4 and Stratum 4E•Supports ITU-T G.823 and G.824 for 2048kbit/s and 1544kbit/s interfaces•Supports ANSI T1.403 and ETSI ETS 300 011 for ISDN primary rate interfaces •Simple hardware control interface•Accepts two input references and synchronizes to any combination of 2kHz, 8kHz, 1.544MHz,2.048MHz, 8.192MHz, 16.384MHz or 19.44MHz inputs•Provides a range of clock outputs: 1.544MHz, 2.048MHz, 16.384MHz, 19.44MHz and either 4.096MHz and 8.192MHz or 32.768MHz and 65.536MHz•Hitless reference switching between anycombination of valid input reference frequencies •Provides 5 styles of 8kHz framing pulses and a 2kHz multi-frame pulse•Holdover frequency accuracy of 1.5 x 10-7•Lock, Holdover and selectable Out of Range indication•Selectable loop filter bandwidth of 1.8Hz or 922Hz•Less than 24 ps rms intrinsic jitter on the19.44MHz output clock, compliant with OC-3 and STM-1 jitter specifications•Less than 0.6ns pp intrinsic jitter on all output clocks•External master clock source: clock oscillator or crystalApplications•Synchronization and timing control for DSLAM, Gateway and PBX systems that require Stratum 4/4E timing•Line Card synchronization for SDH/PDH applications•Clock and frame pulse source for ST-BUS, GCI and other time division multiplex (TDM) busesNovember 2005ZL30109DS1/E1 System Synchronizer with19.44MHz OutputData SheetFigure 1 - Functional Block DiagramReference MonitorMode ControlVirtual ReferenceIEEE 1149.1aFeedbackTIE Corrector EnableState MachineFrequency Select MUXTIE Corrector CircuitMODE_SEL1:0TCK REF1RSTREF_SELTIE_CLROSCo OSCi Master ClockTDOREF0TDI TMS TRSTHOLDOVER BW_SEL HMS LOCK REF_FAIL0REF_FAIL1DPLLOUT_SELMUXOOR_SEL C2oE1SynthesizerDS1SynthesizerSONET/SDH SynthesizerC4/C65o C8/C32o C16o F4/F65o F8/F32o C1.5o C19o F2koF16o Ordering InformationZL30109QDG 64 Pin TQFP Trays, Bake & Drypack ZL30109QDG164 pin TQFP*Trays, Bake & Drypack*Pb Free Matte Tin -40°C to +85°CZL30109Data Sheet DescriptionThe ZL30109 DS1/E1 System Synchronizer contains a digital phase-locked loop (DPLL), which provides timing and synchronization for multi-trunk DS1 and E1 transmission equipment. The 19.44MHz output makes the ZL30109 also suitable for SDH line card applications.The ZL30109 generates a 19.44MHz clock and ST-BUS and TDM bus clocks and framing signals that are phase locked to one of two input references. It helps ensure system reliability by monitoring its references for accuracy and stability and by maintaining stable output clocks during reference switching operations and during short periods when a reference is unavailable.The ZL30109 is intended to be the central timing and synchronization resource for network equipment that complies with Telcordia, ETSI, ITU-T and ANSI network specifications.ZL30109Data SheetTable of Contents1.0 Change Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .52.0 Physical Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .62.1 Pin Connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .62.2 Pin Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .73.0 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .103.1 Reference Select Multiplexer (MUX). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .103.2 Reference Monitor. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .103.3 Time Interval Error (TIE) Corrector Circuit. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .133.4 Digital Phase Lock Loop (DPLL). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .163.5 Frequency Synthesizers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .173.6 State Machine . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .173.7 Master Clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .174.0 Control and Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .174.1 Out of Range Selection. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .174.2 Loop Filter Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .184.3 Output Clock and Frame Pulse Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .184.4 Modes of Operation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .184.4.1 Freerun Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .184.4.2 Holdover Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .194.4.3 Normal Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .194.5 Reference Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .205.0 Measures of Performance. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .215.1 Jitter. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .215.2 Jitter Generation (Intrinsic Jitter). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .215.3 Jitter Tolerance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .215.4 Jitter Transfer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .215.5 Frequency Accuracy . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .225.6 Holdover Accuracy . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .225.7 Pull-in Range. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .225.8 Lock Range. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .225.9 Phase Slope . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .225.10 Time Interval Error (TIE) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .225.11 Maximum Time Interval Error (MTIE) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .225.12 Phase Continuity. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .225.13 Lock Time . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .226.0 Applications. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .236.1 Power Supply Decoupling. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .236.2 Master Clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .236.2.1 Clock Oscillator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .236.2.2 Crystal Oscillator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .246.3 Power Up Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .246.4 Reset Circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .257.0 Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .267.1 AC and DC Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .267.2 Performance Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .33ZL30109Data SheetList of FiguresFigure 1 - Functional Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 Figure 2 - Pin Connections (64 pin TQFP, please see Note 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6 Figure 3 - Reference Monitor Circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11 Figure 4 - Behaviour of the Dis/Re-qualify Timer. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 Figure 5 - DS1 Mode Out-of-Range Limits (OOR_SEL=0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 Figure 6 - E1 Mode Out-of-Range Limits (OOR_SEL=1). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13 Figure 7 - Timing Diagram of Hitless Reference Switching . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14 Figure 8 - Timing Diagram of Hitless Mode Switching. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15 Figure 9 - DPLL Block Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16 Figure 10 - Mode Switching in Normal Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20 Figure 11 - Reference Switching in Normal Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21 Figure 12 - Clock Oscillator Circuit. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23 Figure 13 - Crystal Oscillator Circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24 Figure 14 - Power-Up Reset Circuit. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25 Figure 15 - Timing Parameter Measurement Voltage Levels. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27 Figure 16 - Input to Output Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29 Figure 17 - Output Timing Referenced to F8/F32o . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31 Figure 18 - SONET/SDH Output Timing Referenced to F8/F32o . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32ZL30109Data Sheet1.0 Change SummaryChanges from July 2005 Issue to November 2005 Issue. Page, section, figure and table numbers refer to this current issue.Changes from November 2004 Issue to July 2005 Issue. Page, section, figure and table numbers refer to this current issue.Page Item Change1Features Added description for hitless reference switching.23Section 6.1Removed power supply decoupling circuit and includedreference to synchronizer power supply decoupling application note.Page Item Change8RST pin Specified clock and frame pulse outputs forced to high impedance.10REF0 pinSpecified seven possible reference input frequencies.27Table “DC Electrical Characteristics*“Corrected Schmitt trigger levels.33Table “Performance Characteristics* - Functional“Gave more detail on Lock Time conditions.ZL30109Data Sheet2.0 Physical Description2.1 Pin ConnectionsFigure 2 - Pin Connections (64 pin TQFP, please see Note 1)Note 1: The ZL30109 uses the TQFP shown in the package outline designated with the suffix QD, the ZL30109does not use the e-Pad TQFP .ZL3010934363840424446486462605856525054161412108642OSCo NC GND OUT_SEL C1.5o MODE_SEL1V DD AV DD IC NC RSTNC AGNDF4/F65o V DD REF1NC ICC 8/C 32o F 2k o C 2o A G N DA V D DC 19o F 8/F 32o C 4/C 65o REF_SEL1820222426303228C 16o F16o TIE_CLR OOR_SELICOSCi A V D DA V D DA V D DA V C O R EA G N D A G N D A G N D NC NC IC ICMODE_SEL0NC BW_SELREF0V C O R EL O C K H M ST R S T G N DT D O T M S H O L D O V E R I C T C K T D I V C O R EA V C O R EG N D R E F _F A I L 0R E F _F A I L 1ZL30109Data Sheet2.2 Pin DescriptionPin DescriptionPin # Name Description1GND Ground. 0 V.2V CORE Positive Supply Voltage. +1.8 V DC nominal.3LOCK Lock Indicator (Output). This output goes to a logic high when the PLL is frequencylocked to the selected input reference.4HOLDOVER Holdover (Output). This output goes to a logic high whenever the PLL goes intoholdover mode.5REF_FAIL0Reference 0 Failure Indicator (Output). A logic high at this pin indicates that the REF0 reference frequency has exceeded the out-of-range limit set by the OOR_SEL pin or thatit is exhibiting abrupt phase or frequency changes.6IC Internal bonding Connection. Leave unconnected.7REF_FAIL1Reference 1 Failure Indicator (Output). A logic high at this pin indicates that the REF1 reference frequency has exceeded the out-of-range limit set by the OOR_SEL pin or thatit is exhibiting abrupt phase or frequency changes.8TDO Test Serial Data Out (Output). JTAG serial data is output on this pin on the falling edge of TCK. This pin is held in high impedance state when JTAG scan is not enabled.9TMS Test Mode Select (Input). JTAG signal that controls the state transitions of the TAPcontroller. This pin is internally pulled up to V DD. If this pin is not used then it should beleft unconnected.10TRST Test Reset (Input). Asynchronously initializes the JTAG TAP controller by putting it in the Test-Logic-Reset state. This pin should be pulsed low on power-up to ensure thatthe device is in the normal functional state. This pin is internally pulled up to V DD. Ifthis pin is not used then it should be connected to GND.11TCK Test Clock (Input): Provides the clock to the JTAG test logic. If this pin is not used then it should be pulled down to GND.12V CORE Positive Supply Voltage. +1.8 V DC nominal.13GND Ground. 0 V.14AV CORE Positive Analog Supply Voltage. +1.8 V DC nominal.15TDI Test Serial Data In (Input). JTAG serial test instructions and data are shifted in on this pin. This pin is internally pulled up to V DD. If this pin is not used then it should be leftunconnected.16HMS Hitless Mode Switching (Input). The HMS circuit controls phase accumulation during the transition from Holdover or Freerun mode to Normal mode on the same reference. Alogic low at this pin will cause the ZL30109 to maintain the delay stored in the TIEcorrector circuit when it transitions from Holdover or Freerun mode to Normal mode. Alogic high on this pin will cause the ZL30109 to measure a new delay for its TIE correctorcircuit thereby minimizing the output phase movement when it transitions from Holdoveror Freerun mode to Normal mode.17MODE_SEL0Mode Select 0 (Input). This input combined with MODE_SEL1 determines the mode(Normal, Holdover or Freerun) of operation, see Table4 on page18.18MODE_SEL1Mode Select 1 (Input). See MODE_SEL0 pin description.ZL30109Data Sheet Pin Description (continued)Pin # Name Description19RST Reset (Input). A logic low at this input resets the device. On power up, the RST pin must be held low for a minimum of 300ns after the power supply pins have reachedthe minimum supply voltage. When the RST pin goes high, the device will transitioninto a Reset state for 3ms. In the Reset state all clock and frame pulse outputs will beforced into high impedance.20OSCo Oscillator Master Clock (Output). For crystal operation, a 20MHz crystal is connected from this pin to OSCi. This output is not suitable for driving other devices. For clockoscillator operation, this pin must be left unconnected.21OSCi Oscillator Master Clock (Input). For crystal operation, a 20MHz crystal is connected from this pin to OSCo. For clock oscillator operation, this pin must be connected to aclock source.22IC Internal Connection. Leave unconnected.23GND Ground. 0V.24NC No internal bonding Connection. Leave unconnected.25V DD Positive Supply Voltage. +3.3 V DC nominal.26OUT_SEL Output Selection (Input).This input selects the signals on the combined output clock and frame pulse pins, see Table3 on page18.27IC Internal Connection. Connect this pin to ground.28IC Internal Connection. Connect this pin to ground.29AV DD Positive Analog Supply Voltage. +3.3 V DC nominal.30NC No internal bonding Connection. Leave unconnected.31NC No internal bonding Connection. Leave unconnected.32C1.5o Clock 1.544MHz (Output). This output is used in DS1 applications.This clock output pad includes a Schmitt input which serves as a PLL feedback path;proper transmission-line termination should be applied to maintain reflections belowSchmitt trigger levels.33AGND Analog Ground. 0 V34AGND Analog Ground. 0 V35AV CORE Positive Analog Supply Voltage. +1.8 V DC nominal.36AV DD Positive Analog Supply Voltage. +3.3 V DC nominal.37AV DD Positive Analog Supply Voltage. +3.3 V DC nominal.38F2ko Multi Frame Pulse (Output). This is a 2kHz 51ns active high framing pulse, whichmarks the beginning of a multi frame.This clock output pad includes a Schmitt input which serves as a PLL feedback path;proper transmission-line termination should be applied to maintain reflections belowSchmitt trigger levels.ZL30109Data Sheet Pin Description (continued)Pin # Name Description39C19o Clock 19.44MHz (Output). This output is used in SONET/SDH applications.This clock output pad includes a Schmitt input which serves as a PLL feedback path;proper transmission-line termination should be applied to maintain reflections belowSchmitt trigger levels.40AGND Analog Ground.0V41AGND Analog Ground.0V42C4/C65o Clock 4.096MHz or 65.536MHz (Output). This output is used for ST-BUS operation at2.048Mbps, 4.096Mbps or 65.536MHz (ST-BUS 65.536Mbps). The output frequency isselected via the OUT_SEL pin.43C8/C32o Clock 8.192MHz or 32.768MHz (Output). This output is used for ST-BUS and GCIoperation at 8.192Mbps or for operation with a 32.768MHz clock. The output frequencyis selected via the OUT_SEL pin.44AV DD Positive Analog Supply Voltage. +3.3 V DC nominal.45AV DD Positive Analog Supply Voltage. +3.3 V DC nominal.46C2o Clock 2.048MHz (Output). This output is used for standard E1 interface timing and for ST-BUS operation at 2.048Mbps.This clock output pad includes a Schmitt input which serves as a PLL feedback path;proper transmission-line termination should be applied to maintain reflections belowSchmitt trigger levels.47C16o Clock 16.384MHz (Output). This output is used for ST-BUS operation with a16.384MHz clock.This clock output pad includes a Schmitt input which serves as a PLL feedback path;proper transmission-line termination should be applied to maintain reflections belowSchmitt trigger levels.48F8/F32o Frame Pulse (Output). This is an 8kHz 122ns active high framing pulse (OUT_SEL=0) or it is an 8kHz 31ns active high framing pulse (OUT_SEL=1), which marks thebeginning of a frame.This clock output pad includes a Schmitt input which serves as a PLL feedback path;proper transmission-line termination should be applied to maintain reflections belowSchmitt trigger levels.49F4/F65o Frame Pulse ST-BUS 2.048Mbps or ST-BUS at 65.536MHz clock (Output). Thisoutput is an 8kHz 244ns active low framing pulse (OUT_SEL=0), which marks thebeginning of an ST-BUS frame. This is typically used for ST-BUS operation at2.048Mbps and 4.096Mbps. Or this output is an 8kHz 15ns active low framing pulse(OUT_SEL=1), typically used for ST-BUS operation with a clock rate of 65.536MHz.50F16o Frame Pulse ST-BUS 8.192Mbps (Output). This is an 8kHz 61ns active low framing pulse, which marks the beginning of an ST-BUS frame. This is typically used for ST-BUSoperation at 8.192Mbps.51AGND Analog Ground.0V52IC Internal Connection. Connect this pin to ground.ZL30109Data Sheet Pin Description (continued)Pin # Name Description53REF_SEL Reference Select (Input). This input selects the input reference that is used forsynchronization, see Table5 on page20. This pin is internally pulled down to GND.54NC No internal bonding Connection. Leave unconnected.55REF0Reference (Input). This is one of two (REF0, REF1) input reference sources used forsynchronization. One of seven possible frequencies may be used: 2kHz, 8kHz,1.544MHz,2.048MHz, 8.192MHz, 16.384MHz, or 19.44MHz. This pin is internallypulled down to GND.56NC No internal bonding Connection. Leave unconnected.57REF1Reference (Input). See REF0 pin description.58NC No internal bonding Connection. Leave unconnected.59IC Internal Connection. Connect this pin to ground.60OOR_SEL Out Of Range Selection (Input). This pin selects the out of range reference rejection limits, see Table1 on page17.61V DD Positive Supply Voltage. +3.3 V DC nominal.62NC No internal bonding Connection. Leave unconnected.63TIE_CLR TIE Corrector Circuit Reset (Input). A logic low at this input resets the Time IntervalError (TIE) correction circuit resulting in a realignment of the input phase with the outputphase.64BW_SEL Filter Bandwidth Selection (Input). This pin selects the bandwidth of the DPLL loopfilter, see Table2 on page18. Set continuously high to track jitter on the input referenceclosely or set temporarily high to allow the ZL30109 to quickly lock to the input reference.3.0 Functional DescriptionThe ZL30109 is a DS1/E1 System Synchronizer providing timing (clock) and synchronization (frame) signals to interface circuits for DS1 and E1 Primary Rate Digital Transmission links and OC-3/STM-1 links, as well as a 19.44MHz output for SDH line card applications. Figure 1 is a functional block diagram which is described in the following sections.3.1 Reference Select Multiplexer (MUX)The ZL30109 accepts two simultaneous reference input signals and operates on their rising edges. One of them, the primary reference (REF0) or the secondary reference (REF1) signal can be selected as input to the TIE corrector circuit based on the reference selection (REF_SEL) input.3.2 Reference MonitorThe input references are monitored by two independent reference monitor blocks, one for each reference. The block diagram of a single reference monitor is shown in Figure 3. For each reference clock, the frequency is detected and the clock is continuously monitored for three independent criteria that indicate abnormal behavior of the reference signal, for example; long term drift from its nominal frequency or excessive jitter. To ensure proper operation of the reference monitor circuit, the minimum input pulse width restriction of 15nsec must be observed.ZL30109Data Sheet •Reference Frequency Detector : This detector determines whether the frequency of the reference clock is2kHz, 8kHz, 1.544MHz, 2.048MHz, 8.192MHz, 16.384MHz or 19.44MHz and provides this information to the various monitor circuits and the phase detector circuit of the DPLL.•Precise Frequency Monitor : This circuit determines whether the frequency of the reference clock is within the applicable out-of-range limits selected by the OOR_SEL pin, see Figure 5, Figure 6 and Table 1. It will take the precise frequency monitor up to 10 s to qualify or disqualify the input reference.•Coarse Frequency Monitor (CFM): This circuit monitors the reference frequency over intervals ofapproximately 30 µs to quickly detect large frequency changes.•Single Cycle Monitor (SCM): This detector checks the period of a single clock cycle to detect large phase hits or the complete loss of the clock.Figure 3 - Reference Monitor CircuitExceeding the thresholds of any of the monitors forces the corresponding REF_FAIL pin to go high. The single cycle and coarse frequency failure flags force the DPLL into Holdover mode and feed a timer that disqualifies the reference input signal when the failures are present for more than 2.5s. The single cycle and coarse frequency failures must be absent for 10s to let the timer re-qualify the input reference signal as valid. Multiple failures of less than 2.5s each have an accumulative effect and will disqualify the reference eventually. This is illustrated in Figure 4.Reference Frequency Detector Single Cycle Monitor Precise Frequency MonitorCoarse Frequency Monitor dis/requalify timerREF0 / REF1OR OR REF_DIS= reference disrupted.This is an internal signal.Mode select state machine HOLDOVERREF_DIS REF_FAIL0 / REF_FAIL1ZL30109Data SheetSCM or CFM failurecurrent REFtimer2.5 s10 sREF_FAILHOLDOVERFigure 4 - Behaviour of the Dis/Re-qualify TimerWhen the incoming signal returns to normal (REF_FAIL=0), the DPLL returns to Normal mode with the output signal locked to the input signal. Each of the monitors has a built-in hysteresis to prevent flickering of the REF_FAIL status pin at the threshold boundaries. The precise frequency monitor and the timer do not affect the mode (Holdover/Normal) of the DPLL.Figure 5 - DS1 Mode Out-of-Range Limits (OOR_SEL=0)。

OP07中文资料_数据手册_参数

绝对大额定值超过工作自由空气温度范围(除非另有说明) (1) MIN MAX单元 V CC + (2) 0 22电源电压 V V CC- (2) -22 0 差 分输入电压 (3) ±30 V V 我 输入电压范围(任一输入) (4) ±22 V 输出短路持续时间 (5)无限 T J操作虚拟结温度 150 C引线温 度距离壳体1.6毫米(1/16英寸),持续10秒 260 C (1)强调绝对大额定值以外列出的可能会导致设备永久性损坏.这些是压力评级只 有在这些或任何其他超出建议的操作条件下的条件下才能操作设备不暗示条件.暴露在绝对大额定条件下可能会影响器件的可靠性. (2) 除非另有说明,所有的电压值都是相对于V CC + 和V CC- 之间的中点 . (3)差分电压相对于IN处于IN + - . (4)输入电压的 大小决不能超过电源电压的大小或15 V,取其小者. (5)输出可能短路到地或任何一个电源. 7.2处理评级参数定义 MIN MAX单元 T STG存储温度范围 -65 150 C人体模型(HBM),根据ANSI / ESDA / JEDEC JS-001,全部 0 1000 (1)静电的 V (ESD) V卸货带电器 件型号(CDM),根据JEDEC规范JESD22- 0 1000 C101,所有引脚 (2) (1) JEDEC文件JEP??155指出,500V HBM允许采用标准 ESD控制过程进行安全制造. (2) JEDEC文件JEP??157指出,250V CDM允许使用标准ESD控制过程进行安全制造. 7.3推荐的操作条件 超过工作自由空气温度范围(除非另有说明) MIN MAX单元 V CC + 3 18电源电压 V CC- -3 -18 V V IC共模输入电压 V CC± =±15 V -13 13 T A.操作自由空气温度 0 70 C 7.4热量信息 温度计 (1) D P单元 RθJA结到环境热阻 97 85 °C / W (1)有关传统和新型散热指 标的更多信息 OP07Y精密运算放大器 SLOS099B - 1983年10月 - 修订于1996年8月五邮政信箱655303 ? 达拉斯,得克萨斯州75265 经营特色,V CC ±= ± 15 V,T A = 25°C参数测试 OP07C OP07D单元参数条件? MIN TYP MAX MIN TYP MAX单元 F = 10HZ 10.5 10.5 √ VN等效输入噪 声电压 F = 100HZ 10.2 10.3内华达州/ √HZ的 F = 1KHZ 9.8 9.8 VN(PP)峰峰值等效输入噪声电压 F = 0.1HZ至10HZ 0.38 0.38 μV F = 10HZ 0.35 0.35 √在等效输入噪声电流 F = 100HZ 0.15 0.15 PA / √HZ的 F = 1KHZ 0.13 0.13 IN(PP)峰峰值等效输入噪声电流 F = 0.1HZ 至10HZ 15 15 PA的 SR摆率 RL≥2KΩ 0.3 0.3 V /微秒 ?除非另有说明,所有特性均在开环条件下以零共模输入电压进行测量. 电气特 性,V CC ±= ± 15 V,T A = 25°C(除非另有说明)参数测试条件? OP07Y单元参数测试条件? MIN TYP MAX单元 VIO输入失调电 压 RS = 50Ω 60 150 μV输入失调电压的长期漂移见注6 0.5 μV/月偏移调整范围 RS = 20KΩ,见图1 ±4毫伏 IIO输入失调电流 0.8 6 NA 的 IIB输入偏置电流 ±2 ±12 NA的 VICR共模输入电压范围 ±13 ±14 V RL≤10KΩ ±12 ±13 VOM峰值输出电压 RL≤2KΩ ±11.5 ±12.8 V RL≤1KΩ ±12 AVD大信号L≤500KΩ 400 AVD大信号差分电压放大 VO = ±10 V, RL = 2KΩ 120 400 B1单位增益带宽 0.4 0.6兆赫 RI输入电阻 7 31中号 Ω CMRR共模输入电阻 VIC =±13 V, RS = 50Ω 94 110 D B KSVS电源电压抑制比( ΔVCC/ΔVIO) VCC ±=±3 V至±18 V, RS = 50Ω 7 32 μV/ V PD功

3057说明

一、概述SKS-3057型汽车传感器检测分析仪,依据汽车电控系统中各种传感器的工作原理研制而成。

该仪器具有电压、频率、计数、占空比测试功能,它可以对节气门位置传感器、空气流量传感器、曲轴与凸轮轴位置传感器、进气岐管压力传感器、氧传感器、温度传感器、爆震传感器等器件所产生信号的电压、频率、脉冲数、占空比、感应信号等进行准确的检测分析。

便于生产线检验人员快速检测器件性能,同时也是汽配商家和汽车维修技师在工作台上或现场对汽车传感器进行性能检测的实用仪器。

二、面板说明1 ——频率测量指示LED2 ——计数测量指示LED3 —— 5V电压测量指示LED4 —— 20V电压测量指示LED5 ——占空比测量指示LED6 ——频率与计数显示窗口7 ——电压与占空比显示窗口8 ——电压与占空比选择按键9 —— 5V与20V量程选择按键10 ——频率与计数测量选择按键11 ——计数扫描时间显示LED12 ——外部脉冲显示LED13 ——脉冲信号与氧信号选择按键14 ——计数复位按键15 ——公共接地插孔16 ——外部信号输入插孔17 —— +5V电源输出插孔18 —— +12V电源输出插孔19 —— 5V参考电压输出插孔20 ——氧信号输入插孔三、仪器功能使用说明1、脉冲信号频率测量将被测脉冲信号接入仪器的外部信号输入插孔EXT插孔(16),信号源的地与仪器的COM孔(17)相接;将频率与计数转换按键(10)弹起,此时,显示窗(6)所显数值为被测信号的频率(Hz)。

2、脉冲信号占空比测量将被测脉冲信号接入仪器的外部信号输入插孔EXT插孔(16),信号源的地与仪器的COM孔(17)相接;将电压与占空比转换按键(8)压下,此时,显示窗(7)LED光条点亮数目为被测信号的占空比(%)。

3、电压信号的测量将被测电压信号接入仪器的外部信号输入插孔EXT插孔(16),信号源的负极与仪器的COM孔(17)相接;将电压与占空比转换按键(8)弹起;根据被测电压信号的幅值,由电压量程选择按键(9)选择5V或20V量程;此时,显示窗(7)LED光条点亮数目为被测信号的电压值(V)。

TP3057简介

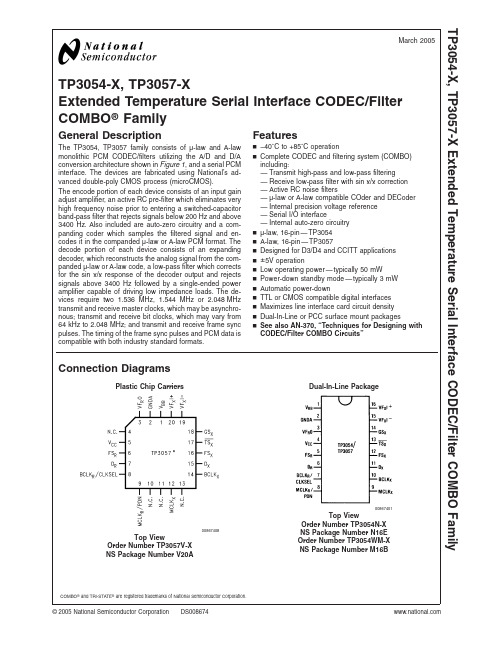

TP3057简介:本模块的核心器件是A律PCM编译码集成电路TP3057,它是CMOS工艺制造的专用大规模集成电路,片内带有输出输入话路滤波器,其引脚及内部框图如图1-4、图1-5所示。

引脚功能如下:图1-4TP3057引脚图(1) V一接-5V电源。

(2) GND接地。

(3) VFRO接收部分滤波器模拟信号输出端。

(4) V+接+5V电源。

(5) FSR接收部分帧同信号输入端,此信号为8KHz脉冲序列。

(6) DR接收部分PCM码流输入端。

(7) BCLKR/CLKSEL接收部分位时钟(同步)信号输入端,此信号将PCM码流在FSR上升沿后逐位移入DR端。

位时钟可以为64KHz到2.048MHz的任意频率,或者输入逻辑“1”或“0”电平器以选择1.536MHz、1.544MHz或2.048MHz用作同步模式的主时钟,此时发时钟信号BCLKX同时作为发时钟和收时钟。

(8) MCLKR/PDN接收部分主时钟信号输入端,此信号频率必须为1.536MHz、1.544MHz或2.048MHz。

可以和MCLKX异步,但是同步工作时可达到最佳状态。

当此端接低电平时,所有的内部定时信号都选择MCLKX信号,当此端接高电平时,器件处于省电状态。

(9) MCLKX发送部分主时钟信号输入端,此信号频率必须为1.536MHz、1.544MHz或2.048MHz。

可以和MCLKR异步,但是同步工作时可达到最佳状态。

(10) BCLKX发送部分位时钟输入端,此信号将PCM码流在FSX信号上升沿后逐位移出DX端,频率可以为64KHz到2.04MHz的任意频率,但必须与MCLKX 同步。

图1-5TP3057内部方框图(11) DX发送部分PCM码流三态门输出端。

(12) FSX发送部分帧同步信号输入端,此信号为8KHz脉冲序列。

(13) TSX漏极开路输出端,在编码时隙输出低电平。

(14) GSX发送部分增益调整信号输入端。

(15) VFXi-发送部分放大器反向输入端。

常用集成电路的型号和功能说明解读

常用集成电路的型号和功能说明型号功能资料ACP2371NI 多制式数字音频信号处理电路ACVP2205 梳状滤波、视频信号处理电路AN5071 波段转换控制电路AN5195K 子图像信号处理电路AN5265 伴音功率放大电路AN5274 伴音功率放大电路AN5285K 伴音前置放大电路AN5342K 图像水平轮廓校正、扫描速度调制电路AN5348K AI信号处理电路AN5521 场扫描输出电路AN5551 枕形失真校正电路AN5560 50/60Hz场频自动识别电路AN5612 色差、基色信号变换电路AN5836 双声道前置放大及控制电路AN5858K TV/AV切换电路AN5862K(AN5862S) 视频模拟开关AN5891K 音频信号处理电路AT24C02 2线电可擦、可编程只读存储器AT24C04 2线电可擦、可编程只读存储器AT24C08 2线电可擦、可编程只读存储器ATQ203 扬声器切换继电器电路BA3880S 高分辨率音频信号处理电路BA3884S 高分辨率音频信号处理电路BA4558N 双运算放大器BA7604N 梳状切换开关电路BU9252S 8bitA/D转换电路CAT24C16 2线电可擦、可编程只读存储器CCU-FDTV 微处理器CCU-FDTV-06 微处理器CD54573A/CD54573CS 波段转换控制电路CH0403-5H61 微处理器CH04801-5F43 微处理器CH05001(PCA84C841) 微处理器CH05002 微处理器CH7001C 数字NTSC/PAL编码电路CHT0406 微处理器CHT0803(TMP87CP38N*) 8bit微处理器CHT0807(TMP87CP38N) 8bit微处理器CHT0808(TMP87CP38N) 8bit微处理器CHT0818 微处理器CKP1003C 微处理器CKP1004S(TMP87CK38N) 微处理器CKP1006S(TMP87CH38N) 微处理器CKP1008S(TMP87CK38N/F) 微处理器CKP1009S(TMP87CH38N) 微处理器CKP1105S(Z90231) 微处理器CKP1301S(TMP87CH38N) 微处理器CKP1403S 微处理器CM0006CF 数字会聚校正电路CNX62A 光电耦合器CNX82A 光电耦合器CPF8598 存储器CTV222S.PRC1.2 微处理器CTV225S-PRC1 微处理器CTV591S.GW3 微处理器CXA1545AS TV/AV多路切换电路CXA1642P 背景歌声消除电路CXA1686M 时钟信号发生器CXA1779P 基色信号处理电路CXP1103S-9919EP 微处理器CXP750096 微处理器CXP85332-108A 微处理器DM8361 单片集成TV小信号处理电路DPU2553/DPU2554 偏转信号处理电路DTI2251 数字色信号过渡特性改善电路GAL16V8C 同步信号变换电路GD74LS10 三组3输入与非门GD74LS393 双4位二进制计数器GD74LS74A 双D触发器GM99200B 微处理器HA11508 图像及伴音信号转换控制电路HCF4046B 低功耗通用锁相环电路HCF4052B 双4选1模拟开关HCF4053BE 三组2路模拟开关HCT157 VGA信号与TV/AV同步信号切换电路HCT4046AD 低功耗通用锁相环电路HD14066 四组双向模拟开关HD14066B 四组双向模拟开关HD14066BP 四组双向模拟开关HEF4052 双4选1模拟开关HEF4053 三组2路模拟开关HEF4094 8级移位-存储总线寄存器HIC1015 开关电源稳压控制及保护电路HIC1016 开关电源稳压控制及保护电路HIC1026 保护模块HM4864P-12 随机存取存储器HPD6325C D/A转换电路HS0038 遥控信号接收电路IX0823GE 微处理器IX1763CEN1 单片集成TV小信号处理电路JLC1562BF 总线控制输入/输出口扩展电路K6274K/D 图像中频带通滤波器K9450M 伴音第一中频带通滤波器KA2107 音频控制电路KA2500 宽带视频放大电路KA3S0680R 开关电源专用厚膜电路KA3S0880RFB 开关电源专用厚膜电路KA7630 多路稳压输出电路KB2511B 数字偏转电路KONKA266(P83C266) 微处理器KS88C3216 微处理器KS88C8324 微处理器L7805 5V固定正稳压器L7808 8V固定正稳压器L7812 12V固定正稳压器L78LR05/L78LR05D/L78LR50-MA/L78M05F/L78M05FA/L78MR05/L78MR05FA 5V稳压复位电路L78OSO5FA 5V可控稳压电路L7912 9V固定负稳压器L7918 18V固定负稳压器LA2785 杜比逻辑处理电路LA4225 5W音频功率放大电路LA4261 立体声功率放大电路LA4270 6W×2音频功率放大电路LA4280 10W×2音频功率放大电路LA4282 10W×2音频功率放大电路LA4445 双声道音频功率放大电路LA6358 双运算放大器LA7016 电子开关LA7210 同步检测电路LA7222 二回路、二接点电子开关LA7406 画中画接口电路LA7575 图像中频放大电路LA76810 TV小信号处理电路LA76832N TV小信号处理电路LA7685 中频及图像信号处理电路LA7838 场扫描电路LA7840 场扫描输出电路LA7841 场扫描输出电路LA7845 场扫描输出电路LA7845N 场扫描输出电路LA7846N 场扫描输出电路LA7910 波段转换控制电路LA7950 场频识别控制电路LA7954 视频转换电路LC344250Z 多端动态存储器LC74401E 画中画(PIP)控制电路LC78815M 双通道16bitD/A变换电路LC863316A 微处理器LC863320A 微处理器LC863328A 微处理器LC863348A 微处理器LC864512 微处理器LC864512V-5D18 微处理器LC864512V-5C77 微处理器LC864525 微处理器LC864916A 微处理器LM317 稳压器LM324 四运算放大器LM358 双运算放大器LM567 锁相环电路LUKS-5140-M2 微处理器LV1010N 杜比逻辑处理电路M32L1632512A 同步图形存储器M34300N-587SP 微处理器M34300N4-555SP 微处理器M37210M3-508SP 微处理器M37210M3-800SP 多制式数字音频信号处理电路M37210M3-902SP 微处理器M37210M4-705SP 微处理器M37211M2-609SP 微处理器M37220M3 微处理器M37221M6-065SP 微处理器M37222M6-084SP 微处理器M37225 微处理器M37270MF-168SP 微处理器M37271MP-209SP 微处理器M37274EFSP 微处理器M37280 微处理器M37551MA-0545SP 微处理器M50436-688SP 微处理器M51131L 话筒演唱及混响音量控制电路M5218AP 双运算放大器M52340SP 单片集成TV小信号处理电路M52470AP 三通道4输入模拟开关M54573L 波段转换控制电路M62354FP 六通道8bitD/A转换电路M62438FP SRSM65839SP 数字式卡拉OK信号处理电路M66312P PIP控制电路M6M80011P 存储器M6M80041P 存储器MALF24C01 存储器MALF24C02 存储器MB3110A 超低音频信号处理电路MB81461-12RS 动态随机存储器MC14066BCP 四组双向模拟开关MC141625A 梳状滤波器MC141628 前置亮、色信号分离梳状滤波器MC144110P D/A转换电路MC14577C 双视频放大电路MC33064D5 复位用欠压检测电路MC44608 开关稳压电源电压模式控制器MC68HC16R1(SC43402CFC) 微处理器MCM6206BBE 32K×8bit快速静态随机存取存储器MCU2600 时钟信号发生器MM1031XS 宽带视频放大电路MM1053XS 多路信号高速切换电路MM1113XS 多路信号高速切换电路MM1495XD A/V切换电路MN1515TWE/TWP 微处理器MN152810TTD5 微处理器MN152811TIX 微处理器MN15282 微处理器MN1871675T6S 微处理器MN1871675T7M 微处理器MN1872432TWI 微处理器MN187-681 微处理器MN3868 1H基带延迟线电路MSP3410 多制式丽音解码电路MSP3410B 多制式丽音解码电路MSP3410D 多制式丽音解码电路MSP3410D-52 多制式丽音解码电路MSP3410D-CS 多制式丽音解码电路MSP3410D-PP-B4 多制式丽音解码电路MSP3410D-P0-B4 多制式丽音解码电路MSP3415D-AI I*IC总线控制多制式音频处理电路MSP3463G 音频信号处理电路NE5532N 内部补偿低噪声双运算放大器NE/SE567 音调与频率解码、锁相环电路NE567N 音调与频率解码、锁相环电路NJM2234L 伴音声道控制开关NJM2700L WOW音频处理电路NJW1103 杜比定向逻辑和音色选择电路NJW1132AL 伴音BBE处理电路NM24C04EN 存储器NN5099K/NN5199K 单片集成多制式TV小信号处理电路NP83C266BRNA 微处理器NV320P 数字视频信号处理电路NVM3060 存储器OM8361 单片集成TV小信号处理电路OM8361-VS0469 单片集成TV小信号处理电路OM8839 I*IC总线控制单片集成TV小信号处理电路OM8839PS I*IC总线控制单片集成TV小信号处理电路OM8839PS-K9G216 I*IC总线控制单片集成TV小信号处理电路ONWA KWEC42.2ONWA KWEC44.1OTT531 +5V稳压复位电路P83C266BDR 微处理器P87C766 微处理器P87C766BDR(CKP1401S) 微处理器P87C766DT 微处理器PC74HT241P 线性驱动数据缓冲电路PC713F6 光耦合器PCA841P-177 微处理器PCA84C122/PCA84C222/PCA84C422/PCA84C622/ PCA84C822 PCA84C440P/401 微处理器PCA84C641 微处理器PCA84C840P-054 微处理器PCA8516 字符形成电路PCA8521 遥控编码发射电路PCA8521BT 遥控编码发射电路PCF8581P 存储器PCF8582 存储器PCF8589C-2 存储器PCF8594C-2 存储器PCF8598 E2PROM存储器PCF8598C-2 E2PROM存储器PCF8598E E2PROM存储器PCX8598X-2 E2PROM存储器PIP2250 PIP信号处理电路PQ05RF 受控+5V稳压器PQ09RD11(78HR09) 受控+9V稳压器PQ12RF 受控+12V稳压器PQ12RF2 受控+12V稳压器S24C08A 存储器SAA3010T 遥控信号发射电路SAA4955TJ 场存储器SAA4955TS 数字式场存储器SAA4956TJ 具有降噪功能的场存储器SAA4961 PAL/NTSC兼容梳状滤波器SAA4977H 倍场频处理电路SAA4981 单片集成16:9压缩处理电路SAA4991WP 运动估算和补偿、降低行间闪烁、变焦和降噪电路SAA5284 多媒体视频数据捕获电路SAA5700GP 汉字系统图文电视(CCST)解码电路SAA7280P 丽音信号处理电路SAA7283ZP 丽音解调解码电路SAB9077H PIP控制电路SBX1765-01 数字梳状滤波器SDA9187 PIPSDA9187-2X PIPSDA9189X 1/4屏幕多画面PIP处理电路SDA9205 三路8bitA/D转换电路SDA9220 存储同步控制电路SDA9251 存储器SDA9257 时钟同步发生器SDA9280 显示信号处理电路SDA9288 PIP/POP信号处理电路SDA9288X PIP/POP信号处理电路SDA9290 数字图像处理电路SDA9361 DDC-PLUS偏转控制电路SDA9362 扫描小信号处理电路SDA9400 扫描变换处理电路SE110N 开关电源误差信号放大电路SE116E 开关电源误差信号放大电路SE140N/SE145N 开关电源误差信号放大电路SECL810 音频信号控制电路SID2500-DOBO R、G、B混合处理电路SKW011-829A2202 微处理器SMM-201N 微处理器ST24C02 2线电可擦、可编程只读存储器ST24C04 2线电可擦、可编程只读存储器ST63156 微处理器ST6367B1/FEJ 微处理器ST92196 微处理器STK392-040 三通道会聚校正放大电路STK392-110 三通道会聚校正放大电路STR-6658B 开关电源厚膜电路STR-D1005T 开关电源厚膜电路STR-F6454 开关电源厚膜电路STR-F6653 开关电源厚膜电路STR-F6654 开关电源厚膜电路STR-F6656 开关电源厚膜电路STR-F6658B 开关电源厚膜电路STR-F6707 开关电源厚膜电路STR-G8656 开关电源厚膜电路STR-M6529F04 开关电源厚膜电路STR-M6833BF04 开关电源厚膜电路STR-S5941 开关电源厚膜电路STR-S6308 开关电源厚膜电路STR-S6309 开关电源厚膜电路STR-S6709 开关电源厚膜电路STR-S6709A 开关电源厚膜电路STR-S6709AN 开关电源厚膜电路STR-Z3202 开关电源厚膜电路STR-Z4302 开关电源厚膜电路STR-Z4479 开关电源厚膜电路STV2116 视频解码电路STV2246 I*IC总线控制单片集成TV小信号处理电路STV2248 I*IC总线控制单片集成TV小信号处理电路STV5111 R、G、B高压视频放大电路STV5112 R、G、B高压视频放大电路STV9306 场扫描输出电路STV9379 场扫描输出电路T7808CT 8V固定正稳压器TA1216AN 三通道音频信号处理电路TA1218AN AV/TV切换电路TA1219AN AV/TV切换电路TA1219N AV/TV切换电路TA1222AN 多制式视频、色度、同步、偏转信号处理电路TA1222BN 多制式视频、色度、同步、偏转信号处理电路TA1226N 亮度信号瞬态校正电路TA1229N SECAM制解码电路TA1270BF PAL/NTSC视频和色信号处理电路TA1316AN 逐行扫描倍场频画质增强电路TA1318N 多制式扫描行场振荡电路TA2009P 数字信号滤波电路TA2047N 丽音系统模拟滤波电路TA2136F/N 声音重演信号(SRS)处理电路TA24C04/TA24C08/TL24C04 2线电可擦、可编程只读存储器TA7347P S端子切换电路TA7439 三波段数字控制音频信号切换及处理电路TA7508P 四运算放大器TA75393S 双电压比较器TA75458P 双运算放大器TA7555F/P 时间延时器TA75558P 双运算放大器TA75559P 双运算放大器TA7809S 9V固定正稳压器TA78L09AP 9V固定正稳压器TA8173AP 双声道立体环绕声处理电路TA8200AH 双声道音频功率放大电路TA8211AH 双声道音频功率放大电路TA8213K 重低音功率放大电路TA8218AH 音频功率放大电路TA8256H 6W×3通道音频功率放大电路TA8256HV 三通道音频功率放大电路TA8258H 双通道音频功率放大电路TA8403K 场扫描输出电路TA8427K 场扫描输出电路TA8445K 场扫描输出电路TA8615N 制式转换电路TA8628N 带电子音量控制的AV/TV开关电路TA8659BN 多制式视频、偏转、文字显示信号处理及制式转换电路TA8710S 伴音中频转换电路TA8720AN TV/AV(S-VHS)切换电路TA8765N SECAM解码电路TA8772AN PAL/NTSC/SECAM基带1H延迟电路TA8772CN PAL/NTSC/SECAM基带1H延迟电路TA8776N 环绕声信号处理电路TA8777NFA-1 PIP画面视频信号选择开关TA8795AF PIP画面多制式亮度、色度、同步信号处理电路TA8814N 彩色瞬态特性改善电路TA8815BN 模拟视频信号选择开关TA8851AN 双极型I*IC总线控制AV开关TA8851BN 双极型I*IC总线控制AV开关TA8851CN 双极型I*IC总线控制AV开关TA8859CP 枕形失真校正电路TA8859P 枕形失真校正电路TA8880CN 视频、色度、同步信号处理电路TA8889P I*IC总线控制白平衡调整电路TAIF24C04 存储器TB1204N 丽音信号处理电路TB1212N 丽音信号处理电路TB1227AN PAL/NTSC/SECAM视频、色度、扫描小信号处理电路TB1227N PAL/NTSC/SECAM视频、色度、扫描小信号处理电路TB1227 PAL/NTSC/SECAM视频、色度、扫描小信号处理电路TB1231N 视频、色度、扫描小信号处理电路TB1238AN 视频、色度、扫描小信号处理电路TB1238N 视频、色度、扫描小信号处理电路TB1240N I*IC总线控制TV信号处理电路TB1240AN I*IC总线控制TV信号处理电路TBA2800 遥控信号接收电路TC4052 双4选1模拟开关TC4052B 双4选1模拟开关TC4052BP 双4选1模拟开关TC4053 三组2路双向模拟开关TC4053AP/TC4053BP 三组2路双向模拟开关TC4066AF 四组双向模拟开关TC4094BP 端口扩展电路TC74HC4053AP 三组2路双向模拟开关TC74HC4066AF 四组双向模拟开关TC9028F 遥控信号发射电路TC9083F/P 单片PIP控制电路TC9089 数字Y/C信号分离电路TC9090AN 多制式3行数字Y/C信号分离电路TC9090CN 多制式3行数字Y/C信号分离电路TC9090N/F 多制式3行数字Y/C信号分离电路TC9097F 彩色信号处理电路TC90A49P 多制式3行数字Y/C信号分离电路TC9415N 数字卡拉OK电路TDA1521 双通道伴音功率放大电路TDA1521A 双通道伴音功率放大电路TDA1524A 立体声(音量/音调)控制电路TDA1543 数控变换电路TDA16846 开关电源厚膜电路TDA2007 6W×2音频功率放大电路TDA2007A 6W×2音频功率放大电路TDA2009A 10W×2双路音频功率放大电路TDA2030 14WTDA2595 行、场扫描及同步脉冲发生器TDA2616 带静音功能的12W×2TDA3504 视频控制、矩阵电路TDA3654 场扫描输出电路TDA3857 准分离伴音解码电路TDA4472 TV信号前置处理电路TDA4505 彩色电视小信号处理电路TDA4555 多制式色度解码电路TDA4565 亮度延迟、彩色暂态特性改善电路TDA4601 开关电源厚膜电路TDA4605 开关电源厚膜电路TDA4605-3 开关电源厚膜电路TDA4665 基带彩色信号延迟电路TDA4671 彩色瞬态改善(CTI)电路TDA4681 矩阵变换及亮度控制电路TDA4780 视频信号处理电路TDA4853/TDA4854 I*IC总线自同步偏转控制电路TDA5112 单片视频放大输出电路TDA5330T 高频调谐器专用贴片电路TDA6101Q 视频放大输出电路TDA6103Q 视频放大输出电路TDA6107Q 视频放大输出电路TDA6108JF 单片视频放大输出电路TDA6110Q 视频放大输出电路TDA6111Q 视频放大输出电路TDA6120Q 宽带视频放大输出电路TDA6151 卫星电视接收视频处理电路TDA7056A/TDA7056B 超重低音功率放大电路TDA7057AQ 双声道音频功率放大电路TDA7265 双通道音频功率放大电路TDA7297 双声道功率放大电路TDA7429S 立体声信号切换、处理电路TDA7496 带直流音量控制的双通道音频功率放大电路TDA8133 具有“禁止”和复位功能的+5.1V、+8V稳压器TDA8139 具有CPU复位功能的稳压电路TDA8145 光栅东/西失真校正电路TDA8170 场扫描输出电路TDA8172 场扫描输出电路TDA8177F 场扫描输出电路TDA8179 场扫描输出电路TDA8219 色度信号解码电路TDA8305A 图像中放电路TDA8310 PIPTDA8310A PIP全制式色度信号处理电路TDA8341 内载波中频信号处理电路TDA8350Q 直流耦合场偏转和东/西枕校输出电路TDA8351 场扫描输出电路TDA8351AQ 场扫描输出电路TDA8354 宽范围场扫描输出电路TDA8361 PAL/NTSC单片集成TV小信号处理电路TDA8362 单片集成全制式TV小信号处理电路TDA8366N3D 单片集成TV小信号处理电路TDA8376A I*IC总线控制多制式TV小信号处理电路TDA8395 SECAM色度解码电路TDA8425 Hi-Fi音频信号处理电路TDA8540 视频4×4开关矩阵切换电路TDA8732 丽音信号处理电路TDA8814N 亮度、色度信号处理电路TDA8838 I*IC总线控制单片集成TV小信号处理电路TDA8839 I*IC总线控制单片集成TV小信号处理电路TDA8841 I*IC总线控制多制式TV小信号处理电路TDA8843 I*IC总线控制PAL/NTSC制单片集成TV小信号处理电路TDA8844 I*IC总线控制多制式单片集成TV小信号处理电路TDA8944J Hi-Hi立体声功率放大电路TDA8945J 音频功率放大电路TDA9111 行、场扫描信号处理电路TDA9143 解码/同步信号处理电路TDA9151B 可编程扫描控制电路TDA9160 多制式解码/同步信号处理电路TDA9170 亮度改善和色度信号校正处理电路TDA9177 亮度、色差信号瞬态校正电路TDA9178 YUV画质改善处理电路TDA9181 多制式集成梳状滤波器TDA9302H 场扫描输出电路TDA9321 I*IC总线控制TV小信号处理电路TDA9321H 主画面TV信号处理电路TDA9332H I*IC总线控制TV显示处理电路TDA9370 CPU+TV超级电视信号处理电路TDA9380 MCU+VCD超级芯片电视信号处理电路TDA9383 CPU+TV超级电视信号处理电路TDA9429S 音频信号切换及处理电路TDA9801 中频锁相环解调和鉴频器TDA9808 准声像分离,PLL鉴频中频处理电路TDA9808T 准声像分离,PLL鉴频中频处理电路TDA9815 多路中频信号处理电路TDA9859 Hi-Fi音频信号处理电路TDA9860 Hi-Fi音频信号处理电路TDA9874A 数字伴音解调和解码电路TEA2014A 视频信号切换开关TEA5114A 视频信号切换开关TEA5170 同步、稳压电源电路TEA6415B I*IC总线控制视频矩阵开关TEA6415C I*IC总线控制视频矩阵开关TEA6420 I*IC总线控制音频矩阵开关TEA6430 I*IC总线控制音频矩阵开关TLC29321PWL 高效锁相环电路TLP621 光电耦合器TMP83C266BDR-100 微处理器TMP87CH33N 微处理器TMP87CH36 微处理器TMP87CH38N 微处理器TMP87CK38N-3644 微处理器TMP87CM36N 微处理器TMP87CM38N 微处理器TMP87CP38N 微处理器TMP87CS38N 微处理器TMP87PM36N-R0605 微处理器TMP87PS38N 微处理器TMS73C45TKY2 A1检测(模糊逻辑)电路TNY254P 5V待机电路TPU2735 图文电视处理电路TVSM5218L 双声道音频功率放大电路VCT3803A/01A CPU+TV超级电视信号处理电路VCU2133 视频A/D与D/A编解码电路VCU2136 数字视频信号处理电路VDP3108A 数字视频及偏转信号处理电路VDP3120C 数字视频、显示及偏转信号处理电路VPC3215C 数字视频信号处理电路VSP2860 数字视频及同步信号处理电路WH2000(WUHAN2000) 微处理器WH2000C 微处理器XR1075 BBE音响增强处理电路Z86227 微处理器Z90361 微处理器μPC1830GT 视频、色度及扫描小信号处理电路μPC1853 移相矩阵环绕声处理电路μPC1853-01 移相矩阵环绕声处理电路μPC1891Y/A 矩阵环绕声信号处理电路μPC2412HF +12V稳压电路μPD6124 红外线遥控发射电路μPD6325C 6位D/A转换电路μPD6336C 6位D/A转换电路μPD6375 D/A转换电路μPD6376 D/A转换电路10K2 SRS音效处理器14577B 双通道带宽放大电路24C08 存储器24C04-4A99A819 存储器24WC16P 存储器4052 双4选1模拟开关47-00001-42(29022306) 微处理器47C1638AU353 微处理器47C834N-RB11 微处理器74HC86/74HCT86 四组2输入异或门74HC157/74HCT157 四组2选1数据选择器74HC573D 三态输出8位透明D型锁存器74HC4046A/74HCT4046A 低功耗锁相环VCO电路74HC4066 双向模拟电子开关74HC4538D/74HCT4538D 双路可重新触发单稳态多谐振荡器74HCT241N 线性驱动数据缓冲器74LS9D 六路施密特触发倒向器74LS10 三组3输入与非门74LS74 双D触发器(带置位、复位、正触发)74LS393 双4位二进制计数器。

TP3057-X中文资料

TP3054-X,TP3057-XExtended Temperature Serial Interface CODEC/Filter COMBO ®FamilyGeneral DescriptionThe TP3054,TP3057family consists of µ-law and A-law monolithic PCM CODEC/filters utilizing the A/D and D/A conversion architecture shown in Figure 1,and a serial PCM interface.The devices are fabricated using National’s ad-vanced double-poly CMOS process (microCMOS).The encode portion of each device consists of an input gain adjust amplifier,an active RC pre-filter which eliminates very high frequency noise prior to entering a switched-capacitor band-pass filter that rejects signals below 200Hz and above 3400Hz.Also included are auto-zero circuitry and a com-panding coder which samples the filtered signal and en-codes it in the companded µ-law or A-law PCM format.The decode portion of each device consists of an expanding decoder,which reconstructs the analog signal from the com-panded µ-law or A-law code,a low-pass filter which corrects for the sin x/x response of the decoder output and rejects signals above 3400Hz followed by a single-ended power amplifier capable of driving low impedance loads.The de-vices require two 1.536MHz, 1.544MHz or 2.048MHz transmit and receive master clocks,which may be asynchro-nous;transmit and receive bit clocks,which may vary from 64kHz to 2.048MHz;and transmit and receive frame sync pulses.The timing of the frame sync pulses and PCM data is compatible with both industry standard formats.Featuresn −40˚C to +85˚C operationn Complete CODEC and filtering system (COMBO)including:—Transmit high-pass and low-pass filtering —Receive low-pass filter with sin x/x correction —Active RC noise filters—µ-law or A-law compatible COder and DECoder —Internal precision voltage reference —Serial I/O interface—Internal auto-zero circuitry n µ-law,16-pin —TP3054n A-law,16-pin —TP3057n Designed for D3/D4and CCITT applications n ±5V operationn Low operating power —typically 50mWn Power-down standby mode —typically 3mW n Automatic power-downn TTL or CMOS compatible digital interfaces n Maximizes line interface card circuit density n Dual-In-Line or PCC surface mount packagesn See also AN-370,“Techniques for Designing with CODEC/Filter COMBO Circuits”Connection DiagramsPlastic Chip Carriers00867408Top ViewOrder Number TP3057V-X NS Package Number V20ADual-In-Line Package00867401Top ViewOrder Number TP3054N-X NS Package Number N16E Order Number TP3054WM-X NS Package Number M16BCOMBO ®and TRI-STATE ®are registered trademarks of National Semiconductor Corporation.March 2005TP3054-X,TP3057-X Extended Temperature Serial Interface CODEC/Filter COMBO Family©2005National Semiconductor Corporation Pin DescriptionsSymbol FunctionV BB Negative power supply pin.V BB =−5V ±5%.GNDA Analog ground.All signals are referenced to this pin.VF R O Analog output of the receive power amplifier.V CC Positive power supply pin.V CC =+5V ±5%.FS RReceive frame sync pulse whichenables BCLK R to shift PCM data into D R .FS R is an 8kHz pulse train.See Figure 2and Figure 3for timing details.D RReceive data input.PCM data is shifted into D R following the FS R leading edge.Symbol FunctionBCLK R /CLKSEL The bit clock which shifts data into D Rafter the FS R leading edge.May vary from 64kHz to 2.048MHz.Alternatively,may be a logic input which selects either 1.536MHz/1.544MHz or 2.048MHz for master clock in synchronous mode and BCLK X is used for both transmit and receive directions (see Table 1).MCLK R /PDNReceive master clock.Must be 1.536MHz,1.544MHz or 2.048MHz.May be asynchronous with MCLK X ,but should be synchronous with MCLK X for best performance.When MCLK R isconnected continuously low,MCLK X is selected for all internal timing.When MCLK R is connected continuously high,the device is powered down.Block Diagram00867402FIGURE 1.T P 3054-X ,T P 3057-X 2Pin Descriptions(Continued)Symbol FunctionMCLK X Transmit master clock.Must be1.536MHz,1.544MHz or2.048MHz.May beasynchronous with MCLK R.Bestperformance is realized fromsynchronous operation.FS X Transmit frame sync pulse input whichenables BCLK X to shift out the PCMdata on D X.FS X is an8kHz pulsetrain,see Figure2and Figure3fortiming details.BCLK X The bit clock which shifts out the PCMdata on D X.May vary from64kHz to2.048MHz,but must be synchronouswith MCLK X.D X The TRI-STATE®PCM data outputwhich is enabled by FS X.TS X Open drain output which pulses lowduring the encoder time slot.GS X Analog output of the transmit inputed to externally set gain.VF X I−Inverting input of the transmit inputamplifier.VF X I+Non-inverting input of the transmit inputamplifier.Functional DescriptionPOWER-UPWhen power is first applied,power-on reset circuitry initial-izes the COMBO and places it into a power-down state.All non-essential circuits are deactivated and the D X and VF R O outputs are put in high impedance states.To power-up the device,a logical low level or clock must be applied to the MCLK R/PDN pin and FS X and/or FS R pulses must be present.Thus,2power-down control modes are available. The first is to pull the MCLK R/PDN pin high;the alternative is to hold both FS X and FS R inputs continuously low—the device will power-down approximately1ms after the last FS X or FS R pulse.Power-up will occur on the first FS X or FS R pulse.The TRI-STATE PCM data output,D X,will remain in the high impedance state until the second FS X pulse. SYNCHRONOUS OPERATIONFor synchronous operation,the same master clock and bit clock should be used for both the transmit and receive directions.In this mode,a clock must be applied to MCLK X and the MCLK R/PDN pin can be used as a power-down control.A low level on MCLK R/PDN powers up the device and a high level powers down the device.In either case, MCLK X will be selected as the master clock for both the transmit and receive circuits.A bit clock must also be applied to BCLK X and the BCLK R/CLKSEL can be used to select the proper internal divider for a master clock of1.536MHz, 1.544MHz or2.048MHz.For1.544MHz operation,the device automatically compensates for the193rd clock pulse each frame.With a fixed level on the BCLK R/CLKSEL pin,BCLK X will beselected as the bit clock for both the transmit and receivedirections.Table1indicates the frequencies of operationwhich can be selected,depending on the state of BCLK R/CLKSEL.In this synchronous mode,the bit clock,BCLK X,may be from64kHz to2.048MHz,but must be synchronouswith MCLK X.Each FS X pulse begins the encoding cycle and the PCMdata from the previous encode cycle is shifted out of theenabled D X output on the positive edge of BCLK X.After8bitclock periods,the TRI-STATE D X output is returned to a highimpedance state.With an FS R pulse,PCM data is latchedvia the D R input on the negative edge of BCLK X(or BCLK Rif running).FS X and FS R must be synchronous withMCLK X/R.TABLE1.Selection of Master Clock FrequenciesBCLK R/CLKSELMaster ClockFrequency SelectedTP3057TP3054Clocked 2.048MHz 1.536MHz or1.544MHz0 1.536MHz or 2.048MHz1.544MHz1 2.048MHz 1.536MHz or1.544MHzASYNCHRONOUS OPERATIONFor asynchronous operation,separate transmit and receiveclocks may be applied.MCLK X and MCLK R must be2.048MHz for the TP3057,or1.536MHz,1.544MHz for theTP3054,and need not be synchronous.For best transmis-sion performance,however,MCLK R should be synchronouswith MCLK X,which is easily achieved by applying only staticlogic levels to the MCLK R/PDN pin.This will automaticallyconnect MCLK X to all internal MCLK R functions(see PinDescription).For1.544MHz operation,the device automati-cally compensates for the193rd clock pulse each frame.FS X starts each encoding cycle and must be synchronouswith MCLK X and BCLK X.FS R starts each decoding cycleand must be synchronous with BCLK R.BCLK R must be aclock,the logic levels shown in Table1are not valid inasynchronous mode.BCLK X and BCLK R may operate from64kHz to2.048MHz.SHORT FRAME SYNC OPERATIONThe COMBO can utilize either a short frame sync pulse or along frame sync pulse.Upon power initialization,the deviceassumes a short frame mode.In this mode,both frame syncpulses,FS X and FS R,must be one bit clock period long,withtiming relationships specified in Figure2.With FS X highduring a falling edge of BCLK X,the next rising edge ofBCLK X enables the D X TRI-STATE output buffer,which willoutput the sign bit.The following seven rising edges clockout the remaining seven bits,and the next falling edgedisables the D X output.With FS R high during a falling edgeof BCLK R(BCLK X in synchronous mode),the next fallingedge of BCLK R latches in the sign bit.The following sevenfalling edges latch in the seven remaining bits.All four de-vices may utilize the short frame sync pulse in synchronousor asynchronous operating mode.TP3054-X,TP3057-X3Functional Description(Continued)LONG FRAME SYNC OPERATIONTo use the long frame mode,both the frame sync pulses,FS X and FS R ,must be three or more bit clock periods long,with timing relationships specified in Figure 3.Based on the transmit frame sync,FS X ,the COMBO will sense whether short or long frame sync pulses are being used.For 64kHz operation,the frame sync pulse must be kept low for a minimum of 160ns.The D X TRI-STATE output buffer is enabled with the rising edge of FS X or the rising edge of BCLK X ,whichever comes later,and the first bit clocked out is the sign bit.The following seven BCLK X rising edges clock out the remaining seven bits.The D X output is disabled by the falling BCLK X edge following the eighth rising edge,or by FS X going low,whichever comes later.A rising edge on the receive frame sync pulse,FS R ,will cause the PCM data at D R to be latched in on the next eight falling edges of BCLK R (BCLK X in synchronous mode).All four devices may utilize the long frame sync pulse in synchronous or asynchronous mode.In applications where the LSB bit is used for signalling,with FS R two bit clock periods long,the decoder will interpret the lost LSB as “1⁄2”to minimize noise and distortion.TRANSMIT SECTIONThe transmit section input is an operational amplifier with provision for gain adjustment using two external resistors,see Figure 4.The low noise and wide bandwidth allow gains in excess of 20dB across the audio passband to be realized.The op amp drives a unity-gain filter consisting of RC activepre-filter,followed by an eighth order switched-capacitor bandpass filter clocked at 256kHz.The output of this filter directly drives the encoder sample-and-hold circuit.The A/D is of companding type according to µ-law (TP3054)or A-law (TP3057)coding conventions.A precision voltage reference is trimmed in manufacturing to provide an input overload (t MAX )of nominally 2.5V peak (see table of Transmission Characteristics).The FS X frame sync pulse controls the sampling of the filter output,and then the successive-approximation encoding cycle begins.The 8-bit code is then loaded into a buffer and shifted out through D X at the next FS X pulse.The total encoding delay will be approximately 165µs (due to the transmit filter)plus 125µs (due to encod-ing delay),which totals 290µs.Any offset voltage due to the filters or comparator is cancelled by sign bit integration.RECEIVE SECTIONThe receive section consists of an expanding DAC which drives a fifth order switched-capacitor low pass filter clocked at 256kHz.The decoder is A-law (TP3057)or µ-law (TP3054)and the 5th order low pass filter corrects for the sin x/x attenuation due to the 8kHz sample/hold.The filter is then followed by a 2nd order RC active post-filter/power amplifier capable of driving a 600Ωload to a level of 7.2dBm.The receive section is unity-gain.Upon the occurrence of FS R ,the data at the D R input is clocked in on the falling edge of the next eight BCLK R (BCLK X )periods.At the end of the decoder time slot,the decoding cycle begins,and 10µs later the decoder DAC output is updated.The total decoder delay is ∼10µs (decoder update)plus 110µs (filter delay)plus 62.5µs (1⁄2frame),which gives approximately 180µs.T P 3054-X ,T P 3057-X 4Absolute Maximum Ratings(Note1)If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.V CC to GNDA7V V BB to GNDA−7V Voltage at any Analog Inputor Output V CC+0.3V to V BB−0.3V Voltage at any Digital Input orOutput V CC+0.3V to GNDA−0.3V Operating Temperature Range−55˚C to+125˚C Storage Temperature Range−65˚C to+150˚C Lead Temperature(Soldering,10sec.)300˚CElectrical CharacteristicsUnless otherwise noted,limits printed in BOLD characters are guaranteed for V CC=+5.0V±5%,V BB=−5.0V±5%;T A=−40˚C to+85˚C by correlation with100%electrical testing at T A=25˚C.All other limits are assured by correlation with other production tests and/or product design and characterization.All signals referenced to GNDA.Typicals specified at V CC=+5.0V,V BB=−5.0V,T A=25˚C.Symbol Parameter Conditions Min Typ Max Units DIGITAL INTERFACEV IL Input Low Voltage0.6V V IH Input High Voltage 2.2V V OL Output Low Voltage D X,I L=3.2mA0.4VSIG R,I L=1.0mA0.4VTS X,I L=3.2mA,Open Drain0.4V V OH Output High Voltage D X,I H=−3.2mA 2.4VSIG R,I H=−1.0mA 2.4V I IL Input Low Current GNDA≤V IN≤V IL,All Digital Inputs−1010µA I IH Input High Current V IH≤V IN≤V CC−1010µA I OZ Output Current in High Impedance D X,GNDA≤V O≤V CC−1010µAState(TRI-STATE)ANALOG INTERFACE WITH TRANSMIT INPUT AMPLIFIER(ALL DEVICES)I I XA Input Leakage Current−2.5V≤V≤+2.5V,VF X I+or VF X I−−200200nA R I XA Input Resistance−2.5V≤V≤+2.5V,VF X I+or VF X I−10MΩR O XA Output Resistance Closed Loop,Unity Gain13ΩR L XA Load Resistance GS X10kΩC L XA Load Capacitance GS X50pF V O XA Output Dynamic Range GS X,R L≥10kΩ−2.8 2.8V A V XA Voltage Gain VF X I+to GS X5000V/V F U XA Unity Gain Bandwidth12MHz V OS XA Offset Voltage−2020mV V CM XA Common-Mode Voltage CMRRXA>60dB−2.5 2.5V CMRRXA Common-Mode Rejection Ratio DC Test60dB PSRRXA Power Supply Rejection Ratio DC Test60dB ANALOG INTERFACE WITH RECEIVE FILTER(ALL DEVICES)R O RF Output Resistance Pin VF R O13ΩR L RF Load Resistance VF R O=±2.5V600ΩC L RF Load Capacitance500pF VOS R O Output DC Offset Voltage−200200mV POWER DISSIPATION(ALL DEVICES)I CC0Power-Down Current No Load(Note2)0.65 2.0mA I BB0Power-Down Current No Load(Note2)0.010.33mA I CC1Power-Up(Active)Current No Load(–40˚C to85˚C) 5.011.0mA I BB1Power-Up(Active)Current No Load(–40˚C to85˚C) 5.011.0mANote1:“Absolute Maximum Ratings”indicate limits beyond which damage to the device may occur.Operating Ratings indicate conditions for which the device is functional,but do not guarantee specific performance limits.Note2:I CC0and I BB0are measured after first achieving a power-up state.TP3054-X, TP3057-X 5Timing SpecificationsUnless otherwise noted,limits printed in BOLD characters are guaranteed for V CC =+5.0V ±5%,V BB =−5.0V ±5%;T A =−40˚C to +85˚C by correlation with 100%electrical testing at T A =25˚C.All other limits are assured by correlation with other production tests and/or product design and characterization.All signals referenced to GNDA.Typicals specified at V CC =+5.0V,V BB =–5.0V,T A =25˚C.All timing parameters are assured at V OH =2.0V and V OL =0.7V.See Definitions and Timing Conventions section for test methods information.Symbol ParameterConditionsMinTyp MaxUnits 1/t PMFrequency of Master ClocksDepends on the Device Used and the 1.536MHz BCLK R /CLKSEL Pin. 1.544MHz MCLK X and MCLK R2.048MHz t RM Rise Time of Master Clock MCLK X and MCLK R 50ns t FM Fall Time of Master Clock MCLK X and MCLK R50ns t PB Period of Bit Clock 48548815725ns t RB Rise Time of Bit Clock BCLK X and BCLK R 50ns t FB Fall Time of Bit Clock BCLK X and BCLK R 50ns t WMH Width of Master Clock High MCLK X and MCLK R 160ns t WML Width of Master Clock Low MCLK X and MCLK R 160ns t SBFMSet-Up Time from BCLK X High First Bit Clock after Short Frame100nsto MCLK X Falling Edgethe Leading Edge of FS XLong Frame125t SFFM Setup Time from FS X High to MCLK X Falling Edge Long Frame Only 100ns t WBH Width of Bit Clock High V IH =2.2V 160ns t WBL Width of Bit Clock Low V IL =0.6V 160ns t HBFL Holding Time from Bit Clock Long Frame OnlynsLow to Frame Sync t HBFS Holding Time from Bit Clock Short Frame OnlynsHigh to Frame Synct SFB Set-Up Time from Frame Sync Long Frame Only115nsto Bit Clock Lowt DBD Delay Time from BCLK X High Load=150pF plus 2LSTTL Loads140nsto Data Validt DBTS Delay Time to TS X Low Load=150pF plus 2LSTTL Loads 140ns t DZC Delay Time from BCLK X Low to C L =0pF to 150pF50165nsData Output Disabled t DZFDelay Time to Valid Data from C L =0pF to 150pF20165nsFS X or BCLK X ,Whichever Comes Latert SDB Set-Up Time from D R Valid to 50nsBCLK R/X Lowt HBD Hold Time from BCLK R/X Low to 50nsD R Invalidt SF Set-Up Time from FS X/R to Short Frame Sync Pulse (1Bit Clock 50nsBCLK X/R LowPeriod Long)t HF Hold Time from BCLK X/R Low Short Frame Sync Pulse (1Bit Clock 100nsto FS X/R LowPeriod Long)t HBFlHold Time from 3rd Period of Long Frame Sync Pulse (from 3to 8Bit 100nsBit Clock Low to Frame Sync Clock Periods Long)(FS X or FS R )t WFLMinimum Width of the Frame 64k Bit/s Operating Mode160nsSync Pulse (Low Level)T P 3054-X ,T P 3057-X 6T i m i n g D i a g r a m s00867403F IG U R E 2.S h o r t F r a m e S y n c T i m i n gTP3054-X,TP3057-X7T i m i n g D i a g r a m s(C o n t i n u e d )00867409F IG U R E 3.L o n g F r a m e S y n c T i m i n gT P 3054-X ,T P 3057-X8元器件交易网Transmission CharacteristicsUnless otherwise noted,limits printed in BOLD characters are guaranteed for V CC=+5.0V±5%,V BB=−5.0V±5%;T A=−40˚C to+85˚C by correlation with100%electrical testing at T A=25˚C.All other limits are assured by correlation with other production tests and/or product design and characterization.GNDA=0V,f=1.02kHz,V IN=0dBm0,transmit input amplifier connected for unity gain non inverting.Typicals are specified at V CC=+5.0V,V BB=−5.0V,T A=25˚C.Symbol Parameter Conditions Min Typ Max Units AMPLITUDE RESPONSEAbsolute Levels Nominal0dBm0Level is4dBm(Definition of nominal gain)(600Ω)0dBm0 1.2276Vrms t MAX Max Overload LevelTP3054(3.17dBm0) 2.501V PKTP3057(3.14dBm0) 2.492V PK G XA Transmit Gain,Absolute T A=25˚C,V CC=5V,V BB=−5VInput at GS x=0dBm0at1020Hz−0.150.15dB G XR Transmit Gain,Relative to G XA f=16Hz−40dBf=50Hz−30dBf=60Hz−26dBf=200Hz−1.8−0.1dBf=300Hz–3000Hz−0.150.15dBf=3152Hz−0.150.20dBf=3300Hz−0.350.1dBf=3400Hz−0.70dBf=4000Hz−14dBf=4600Hz and Up,Measure−32dBResponse from0Hz to4000HzG XAT Absolute Transmit Gain Variation Relative to G XA−0.150.15dBwith TemperatureG XAV Absolute Transmit Gain Variation Relative to G XA−0.050.05dBwith Supply VoltageG XRL Transmit Gain Variations with Sinusoidal Test MethodLevel Reference Level=−10dBm0VF X I+=−40dBm0to+3dBm0−0.20.2dBVF X I+=−50dBm0to−40dBm0−0.40.4dBVF X I+=−55dBm0to−50dBm0−1.2 1.2dB G RA Receive Gain,Absolute T A=25˚C,V CC=5V,V BB=−5VInput=Digital Code Sequencefor0dBm0Signal at1020Hz−0.200.20dB G RR Receive Gain,Relative to G RA f=0Hz to3000Hz−0.150.15dBf=3300Hz−0.350.1dBf=3400Hz−0.70dBf=4000Hz−14dB G RAT Absolute Receive Gain Variation Relative to G RA−0.150.15dBwith TemperatureG RAV Absolute Receive Gain Variation Relative to G RA−0.050.05dBwith Supply VoltageG RRL Receive Gain Variations with Sinusoidal Test Method;ReferenceLevel Input PCM Code Corresponds to anIdeally EncodedPCM Level=−40dBm0to+3dBm0−0.20.2dBPCM Level=−50dBm0to−40dBm0−0.40.4dBPCM Level=−55dBm0to−50dBm0−1.2 1.2dB TP3054-X, TP3057-X 9Transmission Characteristics(Continued)Unless otherwise noted,limits printed in BOLD characters are guaranteed for V CC =+5.0V ±5%,V BB =−5.0V ±5%;T A =−40˚C to +85˚C by correlation with 100%electrical testing at T A =25˚C.All other limits are assured by correlation with other production tests and/or product design and characterization.GNDA =0V,f =1.02kHz,V IN =0dBm0,transmit input amplifier connected for unity gain non inverting.Typicals are specified at V CC =+5.0V,V BB =−5.0V,T A =25˚C.Symbol ParameterConditionsMin TypMax Units AMPLITUDE RESPONSEV RO Receive Output Drive Level R L =600Ω−2.52.5V ENVELOPE DELAY DISTORTION WITH FREQUENCYD XA Transmit Delay,Absolute f=1600Hz 290315µs D XRTransmit Delay,Relative to D XAf=500Hz−600Hz 195220µs f=600Hz−800Hz 120145µs f=800Hz−1000Hz 5075µs f=1000Hz−1600Hz 2040µs f=1600Hz−2600Hz 5575µs f=2600Hz−2800Hz 80105µs f=2800Hz−3000Hz130155µs D RA Receive Delay,Absolute f=1600Hz 180200µs D RRReceive Delay,Relative to D RAf=500Hz−1000Hz −40−25µs f=1000Hz−1600Hz −30−20µs f=1600Hz−2600Hz 7090µs f=2600Hz−2800Hz 100125µs f=2800Hz−3000Hz145175µs NOISE N XC Transmit Noise,C Message TP30541216dBrnC0Weighted(Note 3)N XP Transmit Noise,P Message TP3057−74−67dBm0pWeighted(Note 3)N RC Receive Noise,C Message PCM Code is AlternatingWeightedPositive and Negative Zero —TP3054811dBrnC0N RP Receive Noise,P Message TP3057PCM Code Equals Positive WeightedZero —−82−79dBm0p N RS Noise,Single Frequency f=0kHz to 100kHz,Loop Around −53dBm0Measurement,VF X I +=0Vrms PPSR X Positive Power Supply Rejection,V CC =5.0V DC +100mVrms Transmitf=0kHz−50kHz (Note 4)40dBCNPSR X Negative Power Supply Rejection,V BB =−5.0V DC +100mVrms Transmitf=0kHz−50kHz (Note 4)40dBCPPSR RPositive Power Supply Rejection,PCM Code Equals Positive Zero ReceiveV CC =5.0V DC +100mVrms Measure VF R 0f=0Hz−4000Hz 38dBC f=4kHz−25kHz 38dB f=25kHz−50kHz35dBNPSR RNegative Power Supply Rejection,PCM Code Equals Positive Zero ReceiveV BB =−5.0V DC +100mVrms Measure VF R 0f=0Hz−4000Hz 38dBC f=4kHz−25kHz 38dB f=25kHz−50kHz35dBT P 3054-X ,T P 3057-X 10Transmission Characteristics(Continued)Unless otherwise noted,limits printed in BOLD characters are guaranteed for V CC=+5.0V±5%,V BB=−5.0V±5%;T A=−40˚C to+85˚C by correlation with100%electrical testing at T A=25˚C.All other limits are assured by correlation with other production tests and/or product design and characterization.GNDA=0V,f=1.02kHz,V IN=0dBm0,transmit input amplifier connected for unity gain non inverting.Typicals are specified at V CC=+5.0V,V BB=−5.0V,T A=25˚C.Symbol Parameter Conditions Min Typ Max Units NOISESOS Spurious Out-of-Band Signals Loop Around Measurement,0dBm0,−30dB at the Channel Output300Hz to3400Hz Input PCM CodeApplied at D R.4600Hz–7600Hz−30dB7600Hz–8400Hz−40dB8400Hz–100,000Hz−30dB DISTORTIONSTD X,Signal to Total Distortion Sinusoidal Test Method(Note6)STD R Transmit or Receive Level=3.0dBm033dBC Half-Channel=0dBm0to−30dBm036dBC=−40dBm0XMT28dBCRCV29dBC=−55dBm0XMT13dBCRCV14dBC SFD X Single Frequency Distortion,−43dB TransmitSFD R Single Frequency Distortion,−43dB ReceiveIMD Intermodulation Distortion Loop Around Measurement,−41dBVF X I+=−4dBm0to−21dBm0,TwoFrequencies in the Range300Hz−3400HzCROSSTALKCT X-R Transmit to Receive Crosstalk,f=300Hz−3400Hz−90−70dB 0dBm0Transmit Level D R=Quiet PCM Code(Note6)CT R-X Receive to Transmit Crosstalk,f=300Hz−3400Hz,VF X I=Multitone−90−70dB 0dBm0Receive Level(Note4)ENCODING FORMAT AT DXOUTPUTTP3054TP3057µ-Law A-Law(Includes Even Bit Inversion)V IN(at GS X)=+Full-Scale1000000010101010 V IN(at GS X)=0V11111111110101010111111101010101 V IN(at GS X)=−Full-Scale0000000000101010 Note3:Measured by extrapolation from the distortion test result at−50dBm0.Note4:PPSR X,NPSR X,and CT R–X are measured with a−50dBm0activation signal applied to VF X I+.Note5:TP3054/57are measured using C message weighted filter forµ-law and psophometric weighted filter for A-law.Note6:CT X–R@1.544MHz MCLK X freq.is−70dB max.50%±5%BCLK X duty cycle.TP3054-X, TP3057-X 11Applications InformationPOWER SUPPLIESWhile the pins of the TP3050family are well protected against electrical misuse,it is recommended that the stan-dard CMOS practice be followed,ensuring that ground is connected to the device before any other connections are made.In applications where the printed circuit board may be plugged into a “hot”socket with power and clocks already present,an extra long ground pin in the connector should be used.All ground connections to each device should meet at a common point as close as possible to the GNDA pin.This minimizes the interaction of ground return currents flowing through a common bus impedance.0.1µF supply decou-pling capacitors should be connected from this common ground point to V CC and V BB ,as close to device pins as possible.For best performance,the ground point of each CODEC/FILTER on a card should be connected to a common card ground in star formation,rather than via a ground bus.This common ground point should be decoupled to V CC and V BB with 10µF capacitors.RECEIVE GAIN ADJUSTMENTFor applications where a TP3050family CODEC/filter re-ceive output must drive a 600Ωload,but a peak swing lower than ±2.5V is required,the receive gain can be easily ad-justed by inserting a matched T-pad or π-pad at the output.Table 2lists the required resistor values for 600Ωtermina-tions.As these are generally non-standard values,the equa-tions can be used to compute the attenuation of the closest practical set of resistors.It may be necessary to use unequal values for the R1or R4arms of the attenuators to achieve a precise attenuation.Generally it is tolerable to allow a small deviation of the input impedance from nominal while still maintaining a good return loss.For example a 30dB return loss against 600Ωis obtained if the output impedance of the attenuator is in the range 282Ωto 319Ω(assuming a perfect transformer).T-Pad Attenuator00867411T P 3054-X ,T P 3057-X 12Applications Information(Continued)π-Pad Attenuator00867412Note:See Application Note 370for further details.TABLE 2.Attentuator Tables for Z1=Z2=300Ω(All Values in Ω)dB R1R2R3R40.1 1.726k 3.552k 0.2 3.513k 6.926k 0.3 5.28.7k 10.417.4k 0.4 6.9 6.5k 13.813k 0.58.5 5.2k 17.310.5k 0.610.4 4.4k 21.38.7k 0.712.1 3.7k 24.27.5k 0.813.8 3.3k 27.7 6.5k 0.915.5 2.9k 31.1 5.8k 1.017.3 2.6l 34.6 5.2k 234.4 1.3k 70 2.6k 351.3850107 1.8k 468650144 1.3k 584494183 1.1k 610040222490071153802697858379284317698914324437063010156211427527111681844905351218016155050013190142635473142001257204501521011081643016218989244131823377 1.17k 38620246611.5k366TP3054-X,TP3057-X13Typical Synchronous Application00867406FIGURE 4.T P 3054-X ,T P 3057-X 14Physical Dimensionsinches (millimeters)unless otherwise notedDual-In-Line Package (M)Order Number TP3054WM-X NS Package Number M16BMolded Dual-In-Line Package (N)Order Number TP3054N-X NS Package Number N16ETP3054-X,TP3057-X15。

笔记本常用供电芯片大全、故障实例

笔记本常用供电芯片大全、故障实例笔记本常用供电芯片大全线性稳压块:2951、LP2951、m5236、2950、AAT3200、AAT3680、AME8824、AMS1505、APL5912、APL5913、G9338、SC1565、MAX8863、MIC5205、SI9183、开机芯片:东芝TMP87PM48U、TMP48U、TMP87PH48UIBM:TB6805F、TB6806F、TB6807F TB6808F、TB62501F、、BD4175KV、I/O芯片:PC97338、PC87391、PC87392、pc87393、SMSC系列:FDC37N869、FDC37N958、FDC37N972、LPC47N227/217、LPC47N252、LPC47N25 3、LPC47N254、LPC47N354、LPC47N267键盘芯片:H8C/2471、H8/3434、H8/3431、H8S/2116VPC87541 PC87570、PC87591 PC87594 PC97551 PC97554键盘芯片:具有开机功能:H8/3434、H8/3437、H8/2147、H8/2149、H8/2161、H8/2168、PC87570、PC87591、H8S/XXX、M38857、M38867、M38869系统供电芯片:ISL6228 ISL6232MAX1630 MAX1631、MAX1632、MAX1633、MAX1634、MAX1635、MAX17003E、MAX1901、MAX1902、MAX1904、MAX1977、MAX1999、MAX785、MAX786、MAX8734、LTC1628、LT3728L、LT3728LX、SB3052、SC1402、SC1403、SC1404、SC2450、、TPS51020、TPS51120〈 MAX1631、MAX1634、MAX1904可互换〉〈 MAX1632、MAX1635、MAX1902可互换〉〈 MAX786、SB3052可互换_老机型〉〈MAX8734、MAX1999可互换〉SC1402 (与MAX1632一样)IBM R40用LTC1628(与MAX1632差不多)索尼常用MAX785(奔2机器)辅助供电芯片:ADP3160、ADP3167、ADP3168、APW7057、APW7060ISL6224、ISL6225、ISL6227、IPM6220A、MAXl540、MAXl541、MAX1623、MAX1626、MAX1627、MAX1644、MAX1710、MAX1711、MAXl712、MAX1714、MAX1715、MAX1717、MAX1718、MAX1809、MAX1844、MAX1845、MAX1992、MAXl993、MAX8505、MAX8550、MAX8632、MAX8743、MAX8794、SC1470、SC1474、SC1476、SC1485、SC1486、SCl486A、SC470、SI786LG、G2996、SWC1486、TPS51116、TPS51117、TPS51120、TPS51124、TPS54610、TPS54672、CPU供电芯片:ADP3166、ADP3170、ADP3180、ADP3181、ADP3203、ADP3421、AIC1567、ISL6215、ISL6218、ISL6223、ISL6227、ISL6260、ISL6262、LTC1436、LTC1736、LTC1709、LTC3716、LTC3735、MAX1532、MAX1710、MAX1711、MAX1712、MAX1714、MAX1717、MAX1718、MAX1830、MAXl831、MAX1897、MAX1907、MAX1987、MAX1988、MAX798、MAX8760、MAX8770、MAX8771、MAX8774、SC451、SC452、SC1474、SC1476、供电芯片搭配使用:ADP3203/ADP3415、ADP3205+ADP3415、ADP3410+ADP3421、ADP3410+ADP3422、ADP3207+ADP3419、ADP3208+ADP3419电池充/放电控制芯片:AAI3680、ADP3801、ADP3806、BQ24700、BQ2470l、BQ24702、BQ24703、DS2770、ISL6251、M61040FP、MAXl644 MAX1645、MAX1647、MAX1648、MAX745、MAX1736 MAX1772、MAX1773、MAX1870 MAX1873、MAX1908、MAX1909、MAX745、MAX8724、MAX8725、MAX8765、MB3878、MB3879、MB3887、MB39A126PFV、LT1505G、LTl505、LTC4008、TC490/591、TL494、TL594、OZ983、OZ985、笔记本电池电量检测芯片:BQ2040、BQ2060CPU温度控制芯片:MAX1617、MAX1020A、AD1020、AD1021、AD1030、AD1030A、AD1031、CM8500、MAX1989、AD1020A、MAX6654、ADM1032、G781、LM26、网卡芯片:RTL8100、RTL8139、Intel-DA82562ET、RC82540、3COM、BCM440、BCM5702KBGA、88E8001、88E8055、82562EZ网卡隔离器:LF8423、LF-H80P、H-0023、H0024/42、H0019、ATPL-119(内部是线圈,非电路)声卡芯片:ES1921、ESS1980S、STAC9704、AU8810、4299-JQ、4297-JQ、AD1885、AD1984、8552TS、8542TS、CS4239-KQ、AD1981、AD1981B、ADl888、ADl981、AD1986、ALC200、ALC201A、ALC202、ALC203、ALC258、ALC262、ALC655、ALC658、ALC660、ALC861、ALC880、ALC883、CMl9738、CS4205、CX20468、CX20549、CX20561 PT2353、(没声音,杂音,声小,查功放芯片)(开机时,没有声音,无声卡设备,查声卡芯片)音频功放芯片:APA2020、TPA0142、TPA0312、TPA6017、TPA0202、LM4835、LM4838、LM4861、LM4863、LM4880、LM4881、LM4882、LM4911、MAX9710、MAX9750、MAX9751、MAX9755、MAX9789、MAX9790、ESS1980S、8552TS、8542TS、TPA0302、AU8810、BA7786、AN1294、AN12941、AN12942B、AN12943、G1420、PC卡信号芯片:R5C551、R5C552、R5C476、R54472、R5C593、SN0301520、PCIXXX、PC卡供电芯片:TPS2205、TPS2206、TPS2216、TPS2211、TPS2224、PU2211、M2562A、M2563A、M2564A、OZ2206、超级I/O:PC8394TIO芯片:PC系列:PC87591S(VPCQ01)、PC 87591L(VPC01)、PC97317IBWPC87393 VGJ、PC87591E-VLB、PC87591E (-VPCI01)/(VPCQ01)、PC97551-VPC、PC87570-ICC/VPC、PC87391VGJ、PC8394T、PC87392、PC87541L、PC87541VPC87591E-VLB、TB系列:TB62501F、TB62506F、TB6808F、ENE系列:KB3910QB0、KB910SFC1、KB3910SF、KB910QF、KB910QB4、KB910LQF、KB910LQFA1其它系列:IT8510E、PS5130、W83L950D、LPC47N249-AQQ、PCI4510、LPC47N253-AQQ、LPC47N250-SD、LPC47N252-SG、LPC47N254-AQQ、(1)管理串口、并口、软驱、I/O:PC97338、MB87392、(2)管理键盘、鼠标、且带开机功能:H8/3437、H8。

4-7Wled驱动电源方案LNK305P

Io = 1 / 4 × N × I P × η

注:Io 为输出电流;N 为变压器匝比; η 为转换效率 辅助绕组电压值反映了系统的输出电压,其关系可表示为:

(1)

VA =

NA × (Vo + VD ) NS

(2)

其中 VD 是输出二极管的正向压降, VA 为辅助绕组电压,NA 为辅助绕组匝数,NS 为输出绕组匝数。系统将 辅助绕组的电压通过一个电阻分压电路,输入到芯片的反馈端 FB,芯片采样辅助绕组消磁时的电压,并将采 样的电压值一直保持到下一次采样。每次采样得到的电压会和芯片内部的基准电压 Vref 进行比较,得到放大的 误差信号。从而使误差放大器的输出脚 COMP 反映了负载情况,并且通过误差信号控制 PWM 的开关频率从而 调整输出电压,使得输出电压保持恒定。 当采样电压低于 Vref 时,误差放大器的输出电压 VCOMP 会达到最大值,开关频率由反馈采样电压控制,通过 输出电压来调整输出电流,从而获得稳定恒流电流。 � 恒流电流和输出功率调整 LNK305P 芯片的恒流点和最大输出功率可以通过在 CS 脚外接的电流检测电阻来调整,而输出功率随恒流 点变化而变化。当检测电阻增大,恒流点就会减小,输出功率就会降低,反之则相反。 � 工作频率 LNK305P 芯片开关频率由负载大小来控制,不需要外接频率设置元件。在最大输出功率时,开关频率由芯 片内部限制到 60KHz。在不连续模式的反激电源中,最大输出功率为:

-3-

深圳市钲铭科电子有限公司

LNK305P 芯片(4-7W)LED 电源方案

极限参数(极限参数(TA= 25℃)

符号 VDS(max) VDD IDDclamp VFB VCOMP VCS TA Tstg VESD Rθja 说明 芯片 DRAIN 脚最高耐压 芯片工作电压 芯片钳位电流 FB 输入电压 COMP 输入电压 CS 输入电压 工作温度 存储温度 人体放电模式 热阻 范围 -0.3~730 -0.3~34.0 10.0 -0.3~7.0 -0.3~7.0 -0.3~7.0 -20~85 -40~150 单位 V V mA V V V ℃ ℃ V 65 ℃/W

STK6037 中文版

V1 Nov 21, 4

QQ:252578936

Table of Contents

1 2 3 4

5 6

7

8

9

10

11

特点 ................................................................................................................................................................ 5 订货信息 订货信息......................................................................................................................................................... 6 功能模块图表 ................................................................................................................................................. 7 管脚信息.............................................................................................................................................

OP07C中文资料

OP07C中文资料篇一:op07中文资料详解op07中文资料时间:2019-05-16 07:42:22 来源:资料室作者:op07的功能介绍:Op07芯片是一种低噪声,非斩波稳零的双极性运算放大器集成电路。

由于OP07具有非常低的输入失调电压(对于OP07A最大为25μV),所以OP07在很多应用场合不需要额外的调零措施。

OP07同时具有输入偏置电流低(OP07A为±2nA)和开环增益高(对于OP07A为300V/mV)的特点,这种低失调、高开环增益的特性使得OP07特别适用于高增益的测量设备和放大传感器的微弱信号等方面。

特点:超低偏移:150μV最大。

低输入偏置电流:1.8nA 。

低失调电压漂移:0.5μV/℃。

超稳定,时间:2μV/month最大高电源电压范围:±3V至±22V图1 OP07外型图片图2 OP07 管脚图OP07芯片引脚功能说明:1和8为偏置平衡(调零端),2为反向输入端,3为正向输入端,4接地,5空脚6为输出,7接电源+图3OP07内部电路图ABSOLUTE MAXIMUM RATINGS 最大额定值Symbol符号Parameter参数Value数值Unit 单位VCC Vid Vi Toper TstgSupply Voltage 电源电压Differential Input Voltage差分输入电压Input Voltage 输入电压Operating Temperature 工作温度Storage Temperature 贮藏温度±22 ±30 ±22 -40 +105 -65 +150to toV V V ℃℃电气特性虚拟通道连接= ±15V ,Tamb = 25 ℃(除非另有说明)Symbol符号Parameter 参数及测试条件最小典型60最大Unit 单位150 250VioInput Offset Voltage 输入失调电压0℃≤Tamb ≤+70℃- μVLong Term Input Offset Voltage Stability-(note 1) 长期输入偏置电压的稳定性- 0.4 2 1.8 6 8 50 7 9 50 - - -μV/MoDVio Input Offset Voltage Drift 输入失调电压漂移- 0.5 μV/℃Iio Input Offset Current输入失调电流0℃≤Tamb≤+70℃- 0.8 nADIio Input Offset Current Drift 输入失调电流漂移- 15 1.8pA/℃Iib Input Bias Current输入偏置电流0℃≤Tamb ≤+70℃- nA DIib Ro Rid RicInput Bias Current Drift 输入偏置电流漂移Open Loop Output Resistance 开环输出电阻Differential Input Resistance 差分输入电阻Common Mode Input Resistance 共模输入电阻- - - -15 60 33 12pA/℃ΩMΩGΩVicmInput Common Mode Voltage Range输入共模电压范围0℃≤Tamb ≤+70℃±13 ±13 100 97 90 86 120 100 100 ±12 ±11.5±11 - -±13.5 120 104-dB -dB -VCMRCommon Mode Rejection Ratio (Vi =Vicm min)共模抑制比0℃≤Tamb ≤+70℃SVRSupply Voltage Rejection Ratio 电源电压抑制比(VCC = ±3to ±18V) 0℃≤Tamb ≤+70℃VCC = ±15, RL =2KΩ,VO =Large10V, Signal ±0℃≤Tamb ≤+105℃VCC = ±3V, RL = 500W,VO = ±0.5V RL = 10KΩ400400 ±13 ±12.8 ±12 - 0.17 0.5 2.7- - -V/mVAvd Voltage Gain 大信号电压增益VoppOutput Voltage Swing 输出电压摆幅RL= 2kΩRL= 1KΩ0℃≤Tamb ≤+70℃RL =2KΩ- VSR GBPSlew Rate 转换率(RL =2KΩ,CL = 100pF)Gain Bandwidth Product 带宽增益(RL =2KΩ,CL = 100pF, f = 100kHz)Supply Current -(no load) 电源电流(无负载)0℃≤Tamb ≤+70℃VCC = ±3V- - 5 6 1.3 20 13.5 11.5 0.9 0.3V/μS MHzIcc - 0.67mAf = 10HzEquivalent InputenNoise Voltage等效输入噪声电压f = 1kHz- 11f = 100Hz - 10.5√Hz- 10Equivalent InputinNoiseCurrent等效输入噪声电流f = 10Hz f = 100Hz f = 1kHz- - -0.3 0.2√Hz0.1 0.2图4 输入失调电压调零电路应用电路图:图5 典型的偏置电压试验电路篇二:OP07中文资料(内部)op07中文资料op07的功能介绍:Op07芯片是一种低噪声,非斩波稳零的双极性运算放大器集成电路。

ZY1730芯片说明书

http:// 广州致远电子有限公司

广州致远电子有限公司

技术支持

如果您对文档有所疑问,您可以在办公时间(星期一至星期五上午 8:30~11:50;下午 1:30~5:30;星期六上午 8:30~11:50)拨打技术支持电话或 E-mail 联系。

网 址: 联系电话: +86 (020) 22644358 22644359 22644360 22644361 E-mail: zlgmcu.support@

User Manual

UM070003

ZY1730 使用指南

Rev 1.0 Date: 2007/09/03

产品应用指南

文件信息 类别 关键词

摘要

内容

ZY1730 语音模块 本文主要详细介绍了 ZY1730 的特性、功能、管脚 描述、环形存储结构、按键工作模式、SPI 工作模式、 典型应用电路、封装尺寸等。

传真:(028)85437896

深圳周立功

武汉周立功

地址:深圳市深南中路 2070 号电子科技大厦 A 座 地址:武汉市洪山区广埠屯珞瑜路 158 号 12128 室(华

24 楼 2403 室

中电脑数码市场)

电话:(0755)83781788(5 线)

电话:(027)87168497 87168297 87168397

传真:(0755)83793285

传真:(027)87163755

上海周立功