R5F21226DFP中文资料

基于R5F212K单片机的洗衣机控制系统实例分析

基于R5F212K单片机的洗衣机控制系统实例分析作者:***来源:《现代信息科技》2020年第09期摘要:以實际工程设计为载体,通过教学化处理应用实例,激发学生对智能家电课程的学习兴趣和主观能动性,提升学院学生综合技能为目标,探讨了一种基于R5F212K单片机控制的洗衣机控制系统,通过剖析其电控系统构成、分析模块电路功能、反绘原理图,培养学生的电路设计能力和创新意识。

并总结了多个典型的维修实例来供技术人员参考,以提高整机检修效率。

关键词:R5F212K单片机;开关电源;串激式电机;故障检修中图分类号:TP368.1 文献标识码:A 文章编号:2096-4706(2020)09-0033-04An Example Analysis of Washing Machine Control SystemBased on R5F212K Single Chip MicrocomputerLU Zhonghua(Zhongshan Technician College,Zhongshan 528429,China)Abstract:Taking the practical engineering design as the carrier,through the example of teaching processing application,to stimulate the students’interest and initiative in learning the course of intelligent home appliances,and to improve the comprehensive skills of college students as the goal,this paper discusses a kind of washing machine control system based on R5F212K single-chip microcomputer control,through analyzing the composition of its electronic control system,analyzing the circuit function of the module,drawing the schematic diagram,and cultivating the students’electricity Road design ability and innovation awareness. Several typical maintenance examples are summarized for the reference of technicians to improve the efficiency of the whole machine maintenance.Keywords:R5F212K single chip microcomputer;switching power supply;series motor;trouble shooting0 引言中山市技师学院作为培养高技能人才的主阵地,针对满足企业用人需求、从实际工程应用角度进行教学化处理、更好地衔接专业教学,提高学生专业学习的主观能动性进行了深入的探讨。

电动二通阀

电动二通阀电动二通阀是专供中央空调风机盘管的配套产品,由驱动器与阀体两部分组成,驱动器由一个同步电机驱动,具备弹簧复位及手动开阀杠杆操纵功能。

阀体部分采用活塞式结构。

电动阀可与温控器配套使用,由温控器控制电动阀电机,使阀门开或关,实现管道冷水或热水的通或断,再通过风机盘管送风,以实现温度的自动调节。

目录• 电动二通阀-应用范围及产品特点• 工作原理• 电动二通阀-调试•电动二通阀技术参数驱动器规格型号和技术参数铜阀规格型号和技术参数电动二通阀安装尺寸电动二通阀-应用范围及产品特点1.用于控制冷水或热水空调系统管道的开启或关闭,达到控制室温之目的。

2.驱动器由单项磁滞同步马达驱动,阀门弹簧复位,阀门不工作时处于常闭状态,当需要工作时,由温控器提供一个开启信号,使电动阀接通交流电源而动作。

3..开启阀门,冷冻水或热水进入风机盘管,为房间提供冷气或暖气,当室温达到温控器设定值时,温控器令电动阀断电,复位弹簧使阀门关闭,从而截断进入风机盘管的水流,通过阀门关闭和开启,使室温始终保持在温控设定的温度范围内。

4..ZYFT系列电动阀的驱动器与阀门采用螺纹连接方式,可在阀门安装之后,再安装驱动器。

现场装配,接线灵活、方便。

驱动器之平面设计可以贴近墙面安装,占用空间小,产品可靠耐用,工作噪音低,并能在隐蔽式风机盘管装置内常出现的高温高湿环境可靠工作。

执行器选用铸铝支架及塑料外壳,体积小、重量轻★选用永磁同步电机,并带有磁滞离合机构,具有可靠的自我保护功能★适合多种控制信号:增量(浮点)、电压(0~10V)、电流(4~20mA)★具有0~10V或4~20mA反馈信号(选配)★传动齿轮采用金属齿轮,大大提高了驱动器的使用寿命★功耗低、输出力大、噪音小★阀体有铸铜、铸铁、铸钢、不锈钢多种材质可供选择,以适合不同工作介质及温度的要求★阀体有螺纹连接和法兰连接两种,安装方便,其构造符合IEC国际标准★阀体结构形式有两通阀(单座)、两通平衡阀(平衡式)、三通合流和三通分流阀它分为直动式和先导式2种。

神州鲲泰 KunTai R522 快速指南

123神州鲲泰KunTai R522快速指南版权所有©北京神州数码云科信息技术有限公司2021。

保留一切权利。

非经本公司书面许可,任何单位和个人不得擅自摘抄、复制本文档内容的部分或全部,并不得以任何形式传播。

北京神州数码云科信息技术有限公司地址:北京市海淀区上地九街9号数码科技广场邮编:100085网址:1简介KunTai R522是北京神州数码云科信息技术有限公司新一代数据中心2U 双路ARM 服务器,基于华为鲲鹏处理器。

KunTai R522系列包含R2220、R2230、R2220-C、R2230-C、R522-3、R522-4。

单个风扇失效可能会影响节点性能,或者出现温度告警,更换失效的风单个风扇失效可能会影响节点性能,或者出现温度告警,更换失效的风扇后可恢复正常。

湿度●工作湿度:8%RH~90%RH(无冷凝)●存储湿度:5%RH~95%RH(无冷凝)●长时间存放湿度:30%~69%●最大湿度变化率:20%每小时海拔高度工作海拔高度:≤3050m 按照ASHRAE 2015标准:●配置满足ASHRAE Class A1、A2时,海拔高度超过900m,工作温度按每升高300m 降低1℃计算。

●配置满足ASHRAE Class A3时,海拔高度超过900m,工作温度按每升高175m 降低1℃计算。

●配置满足ASHRAE Class A4时,海拔高度超过900m,工作温度按每升高125m 降低1℃计算。

2准备工具防静电手套浮动螺母安装条十字螺丝刀梯子(高处安装时使用)3安装●安装人员使用工具时,务必按照正确的操作方式进行,以免危及人身安全。

●当设备的安装位置超过安装人员的肩部时,请使用梯子、抬高车等工具辅助安装,安装人员使用梯子时,必须有专人看护,禁止单独作业,避免设备滑落导致人员受伤或设备损坏。

●在接触设备前,应佩戴防静电手套,去除身体上携带的易导电物体(如首饰、手表等),以免被电击或灼伤。

无叶风扇R5F212L4 0C062高压无刷板程序方案电路

UnRegistered

本方案的电路非常成熟稳定,市场上已经大批量采用。 瑞萨(NEC)方案 R5F212L4(国内很多是自己丝印上去的好像是0C062)芯片开发的电动车 无刷控制器全套方案,包括 C 语言的源程序,原理图,PCB 文件,BOM 表,装配工艺图,方案,和市 场上供应的贴片板引脚兼容,本程序都能用,功能齐全,

无叶风扇瑞萨 R5F212 无板程序技术方案

技术支持请联系:QQ:2374125461 TEL:15502038190 本方案采用瑞萨(NEC)的 R5F212L4 高稳定性能超低价芯片设计,硬件电路和市场上大

量批量流通的电路兼容,实验学习生产方便,因此目前市场有大量的无叶风扇无刷控制板卡 大部分都市采用该芯片做主控 MCU 芯片,下面分别就目前市场的批量板的 PCB 文件和实 物板做些说明:为广大技术人员提供设计方向。

1、采用模拟正弦波驱动无霍尔无刷直流电机噪音低,启动平稳,无抖动。 2、抗干扰强:红外接收距离大于10米 3、多重保护:过流过载、堵转保护 4、技术指标: 电压 空载电流 负载电流 空载转速 负载转速 220V/110V 50mA±5% 100 mA±5% 10000转/分 8300转/分钟

,欢迎各位工程师共同探讨无刷技术。本人专业长期从事无刷机电类研发和升级。

轻型风管机商用产品介绍

能效对比-EER 1HP 1.5HP 2HP 2.5HP 3HP

TICA标称 2.99 2.87 2.78 3.09 3.03

M牌标称 2.55 2.65 2.60 2.62 2.65

10

中、高静压风管机

(1)机型型谱

系列 匹数 型号 压缩机 静压

中静压风管机

高静压风管机

5HP

6HP

5HP

6HP

TSA/R50KR(D)BE1 TSA/R50KR(D)BE2 TSA/R60KR(D)BE2 TSA/R50KR(D)HE2 TSA/R60KR(D)HE2

涡旋

转子

转子

涡旋

转子

30、50、70、100Pa

(3)极致静音

2、多重静音设计(室外机)

➢流线型格栅,避免出风涡流,音质柔和;

➢室外机大直径风叶设计 φ421/φ500mm, 降低转速,降低噪音;

➢多孔吸附型消音棉+消音器, 有效隔离压缩机外传噪音, 实测降低2分贝;

➢室外机有墙隔挡,可以降低5分贝噪音以上; ➢针对机体振动、风声、冷媒声进行充分测试评估,避免传入室内。

2匹热泵 920*450*200

2.5匹热泵 1140*450*200

9-14

★静音 ★净化 ★小巧

卧室

12-18

★静音 ★净化 ★小巧

卧室

17-26

★静音 ★净化 ★小巧

客餐厅

22-33

★静音 ★净化 ★高能效

客餐厅

适用于家居、酒店、店铺、餐饮等各种场所; 内机小巧轻薄,厚度仅为200mm,便于安装;

R410A比热容比R22高约30%~40%,吸热性能更强,提 高在低温环境下空气中吸收的热量。

rc522产品手册

rc522产品手册一、概述RC522是一款广泛应用的非接触式射频识别(RFID)读写器芯片,专为高频(13.56 MHz)射频通信设计。

由于其高效性能、低功耗及易于集成等特性,RC522在物联网、电子门锁、智能支付等领域有着广泛的应用。

本手册将详细介绍RC522的主要功能、技术规格、使用方法及常见问题解答。

二、产品特性工作频率:13.56 MHz。

支持ISO14443A/MIFARE标准。

高集成度:将射频前端、解调器、安全逻辑和EEPROM 存储器集成于单芯片中。

低功耗:在待机状态下电流消耗仅为170μA,读写时为3.3mA。

高速数据传输:支持高达848 kbps的通信速率。

多种接口选择:可与SPI、I2C、UART等接口进行连接。

安全性:支持加密和解密功能,确保数据传输的安全性。

三、使用方法硬件连接:根据所选接口,将RC522与微控制器或其他设备进行连接。

注意确保天线连接良好,以获得最佳的通信效果。

电源供应:为RC522提供稳定的电源,建议电压范围为3.3-5V。

寄存器配置:根据需求,通过SPI、I2C或UART接口对RC522的寄存器进行配置。

这包括设置通信参数、选择工作模式等。

读写操作:使用配置好的寄存器参数,对RFID标签进行读写操作。

数据处理:对从RFID标签读取的数据进行解码和安全性验证,确保数据的准确性和安全性。

四、常见问题及解答1.RC522支持哪些类型的RFID标签?答:RC522支持ISO14443A标准和MIFARE系列标签,可读写多种类型的RFID 标签。

2.为什么无法读取RFID标签?答:可能的原因包括天线连接不良、标签与读卡器之间的距离过远、存在干扰等。

请检查天线连接和工作环境,确保符合通信要求。

3.如何配置RC522的寄存器?答:根据需要,通过SPI、I2C或UART接口对RC522的寄存器进行配置。

具体配置方法可参考相关开发文档或手册。

RU-Stick仿真器使用指南_20111220

使用说明目录:1、驱动程序的安装2、Flash Development tools 烧写使用说明3、HEW中仿真设置4、支持型号欢迎访问麒麟电子淘宝店:/一、驱动程序安装1.连接到电脑之后出现如下的对话框2.选择第三个:否,暂时不,点击“下一步”3.出现对话框4.选择第二个:从列表或指定位置安装,点击“下一步”5.出现如下对话框:6.选择第一个,并选择在搜索中包括这个位置,软后点击浏览,找到驱动程序的位置然后下一步即可完成驱动程序的安装7.可以看到设备管理器中的信息,可以看到是COM2断口号,如果不是尽量修改到10以内的端口号,否则大于10的端口号有可能不行。

如何修改断口号见下一步8.上一步的红色划线部分点击“右键”,选择属性,在出现的对话框中选择断口设置,点击高级9、在出现的对话框中,选择新的端口号,选择好之后,确定就行二、Flash Development tools 烧写使用说明1、在开始程序中选择如下图标:选择Flash Development Toolkit 4.07 Basic其中,4.07是版本号,根据你电脑中安装的版本号,不同而不同2、出现如下的界面3、选择好芯片,这里以R5F212A7为例如下图:点击下一步4、出现如下的对话框,端口号根据前边的端口号进行设置,设置好之后下一步5、出现如下的对话框,把Use Default对话框中的对号去掉,点击下拉箭头,选择9600,再次选择下一步:6、在出现的对话框不做修改,直接点击完成,出现如下的对话框,确认1,2红框中的,芯片与端口号是正确的,如果不正确重新设置。

选中3,4,点击5中的箭头,选择好烧写代码。

点击Program FlashDisconnect图标,断开链接就行了。

三、HEW中仿真设置1、需要安装的软件,NC30,HEW,M16cFousbDebuggerV103R00.exe,R8C_UART_MCU_INST_E.exe。

保护IC参数

保护IC技术参数表(25℃)

品牌 型号

Mark

保护电压 过充保护电压 过充恢复电压 过放保护电压 过放恢复电压 4.13±0.05V 2.6±0.080V 2.50±0.080V 2.30±0.080V 2.30±0.080V 2.50±0.05V 2.30±0.05V 2.30±0.05V 2.30±0.05V 2.50±0.05V 3.00±0.05V 2.30±0.05V 2.40±0.08V 2.30±0.08V 2.40±0.08V 2.4±0.10V 2.4±0.10V 2.4±0.10V 2.35±0.10V 2.90±0.08V 3.00±0.10V 3.00±0.10V 3.00±0.10V 3.00±0.10V 3.00±0.10V 3.00±0.10V 2.90±0.10V 3.00±0.08V 2.90±0.08V 3.10±0.10V 2.90±0.10V 3.00±0.10V 2.30±0.10V 2.90±0.05V 2.40±0.05V 2.30±0.05V 2.30±0.05V 2.90±0.05V 3.00±0.05V

Mark

保护电压 过充保护电压 过充恢复电压 过放保护电压 过放恢复电压 4.28±0.025V 4.25±0.025V 4.35±0.025V 3.98±0.05V 4.05±0.05V 4.15±0.05V 2.30±0.058V 2.50±0.063V 2.50±0.063V 3.10±0.08V 3.10±0.08V 3.10±0.08V

0.13 0.14 0.18 0.13

0.15 0.15 0.2 0.15

0.17 0.16 0.22

1 1 250

125 24 20 15

8 12 12 15

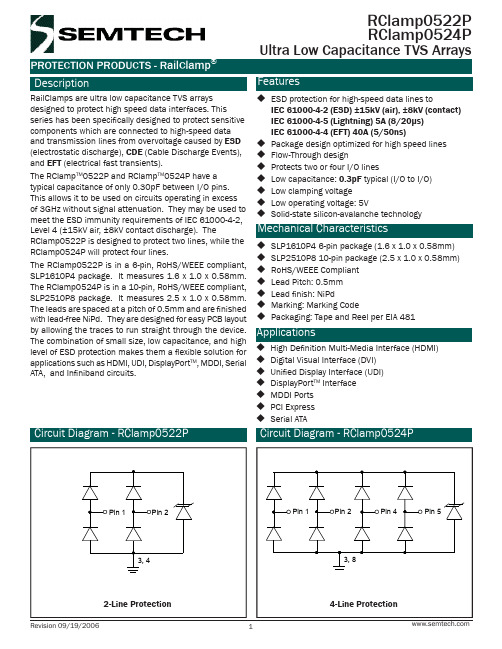

RCLAMP0522P中文资料

Applications

High Definition Multi-Media Interface (HDMI) Digital Visual Interface (DVI) Unified Display Interface (UDI) DisplayPortTM Interface MDDI Ports PCI Express Serial ATA

RClamp0522P RClamp0524P

PRELIMINARY

Power Derating Curve

110 100 90 80 70 60 50 40 30 20 10 0

PROTECTION PRODUCTS Typical Characteristics

Non-Repetitive Peak Pulse Power vs. Pulse Time

Pin 1

Pin 2

Pin 1

Pin 2

Pin 4

Pin 5

3, 4

3, 8

Circuit Diagram

Circuit Diagram

Ordering Information

Part Number RClamp0522P.TCT RClamp0524P.TCT Number of Lines Qty per Reel Reel Size 7 Inch 7 Inch

PRELIMINARY

RClamp0522P RClamp0524P

RClamp0524P

10 9 8 7 6

1

Pin 1-2 5-6 3-4

2

3

Identification Input Lines Output Lines (No Internal Connection) Ground Pin

FC221系列温控器说明书

产品简介:FC221系列温控器主要用于中央空调采暖和制冷系统。

系统通过检测环境温度与设定温度进行比较产生控制信号,自动调节水阀开度,达到能量供需平衡,同时控制风机的开停状态。

本产品有5个继电器输出,用于控制三速风机及水阀。

电器参数:额定电压:24DC/AC负载电压:<3A测温度范围:1-50℃精度:±1℃(@21℃)输入:外置感温探头(NTC10K),窗磁,房卡,露点探头输出:2路(0-10V)模拟量输出和3路继电器输出工作环境:0-50℃外形尺寸:86*86*50mm注意事项:1、由专业技术人员安装,安装前请确认已经切断电源;2、本产品应安装在空气流通较好的常温环境里,远离热源,远离 门窗避免太阳直射。

3、安装时,不可在温控器上任意打孔,请勿用硬物撞击液晶显示 屏以及用猛力按压显示屏四周,以免液晶屏破裂;4、请严格按照接线图接线,否则有可能损坏温控器。

1、在安装及返修时,一定要确保温控器是处于关机状态;2、用一字螺丝刀插入,轻轻撬动即可分开前后盖,拔下显示板上 的16芯线。

3、将挂板固定在86底盒上;4、将电源板上的16芯线连接到面板上,扣上温控器前盖。

安装步骤:接线图:安装建议/尺寸(MM)GNDCOM GNDESI/DP OCCAC/DC 24Vmax.AC250V/5A12345678910111213141516NTC 10KA BLOMEHI AB(-)(+)功能描述:显示说明:通讯地址码1 (247)工厂默认值1通信接口RS485通信协议Modbus-RTU波特率4800bps/9600bps/19200bps/38400bps 字节8bit 校验码无校验奇校验偶校验工厂默认值工厂默认值无校验Modbus 通信停止位2bit9600bps上键下键开关机键模式键风速键风速等级符号制冷模式符号通风模式符号制热模式符号自动模式符号四段温区符号星期符号modbus通信冷水阀符号热水阀符号露点符号摄氏度符号防冻激活符号华氏度符号门磁符号延时符号按键锁节能符号故障提示符号警示符号内部或外部传感器故障符号管制符号设置温度房间温度WiFi图标时间显示或阀值显示定时开机符号定时关机符号电加热符号来电方式在设备启动期间,版本和类型号会在开始屏幕上短暂显示。

AT26DF321资料

Features Array•Single 2.7V - 3.6V Supply•Serial Peripheral Interface (SPI) Compatible–Supports SPI Modes 0 and 3•66 MHz Maximum Clock Frequency•Flexible, Uniform Erase Architecture–4-Kbyte Blocks–32-Kbyte Blocks–64-Kbyte Blocks–Full Chip Erase•Individual Sector Protection with Global Protect/Unprotect Feature–Sixty-Four 64-Kbyte Physical Sectors•Hardware Controlled Locking of Protected Sectors•Flexible Programming–Byte/Page Program (1 to 256 Bytes)•JEDEC Standard Manufacturer and Device ID Read Methodology•Low Power Dissipation–7 mA Active Read Current (Typical)–4 µA Deep Power-Down Current (Typical)•Endurance: 100,000 Program/Erase Cycles•Data Retention: 20 Years•Complies with Full Industrial Temperature Range•Industry Standard Green (Pb/Halide-free/RoHS Compliant) Package Options –8-lead SOIC (200-mil wide)–16-lead SOIC (300-mil wide)1.DescriptionThe AT26DF321 is a serial interface Flash memory device designed for use in a wide variety of high-volume consumer based applications in which program code is shad-owed from Flash memory into embedded or external RAM for execution. The flexible erase architecture of the AT26DF321, with its erase granularity as small as 4-Kbytes, makes it ideal for data storage as well, eliminating the need for additional data storage EEPROM devices.The physical sectoring and the erase block sizes of the AT26DF321 have been opti-mized to meet the needs of today's code and data storage applications. By optimizing the size of the physical sectors and erase blocks, the memory space can be used much more efficiently. Because certain code modules and data storage segments must reside by themselves in their own protected sectors, the wasted and unused memory space that occurs with large sectored and large block erase Flash memory devices can be greatly reduced. This increased memory space efficiency allows addi-tional code routines and data storage segments to be added while still maintaining thesame overall device density.23633C–DFLASH–08/06AT26DF321 [Preliminary]The AT26DF321 also offers a sophisticated method for protecting individual sectors against erroneous or malicious program and erase operations. By providing the ability to individually pro-tect and unprotect sectors, a system can unprotect a specific sector to modify its contents while keeping the remaining sectors of the memory array securely protected. This is useful in applica-tions where program code is patched or updated on a subroutine or module basis, or in applications where data storage segments need to be modified without running the risk of errant modifications to the program code segments. In addition to individual sector protection capabili-ties, the AT26DF321 incorporates Global Protect and Global Unprotect features that allow the entire memory array to be either protected or unprotected all at once. This reduces overhead during the manufacturing process since sectors do not have to be unprotected one-by-one prior to initial programming.Specifically designed for use in 3-volt systems, the AT26DF321 supports read, program, and erase operations with a supply voltage range of 2.7V to 3.6V. No separate voltage is required for programming and erasing.2.Pin Descriptions and PinoutsTable 2-1.Pin DescriptionsSymbolName and FunctionAsserted StateTypeCS CHIP SELECT : Asserting the CS pin selects the device. When the CS pin is deasserted, thedevice will be deselected and normally be placed in standby mode (not Deep Power-Down mode), and the SO pin will be in a high-impedance state. When the device is deselected, data will not be accepted on the SI pin.A high-to-low transition on the CS pin is required to start an operation, and a low-to-high transition is required to end an operation. When ending an internally self-timed operation such as a program or erase cycle, the device will not enter the standby mode until the completion of the operation.Low InputSCK SERIAL CLOCK : This pin is used to provide a clock to the device and is used to control the flow of data to and from the device. Command, address, and input data present on the SI pin is always latched on the rising edge of SCK, while output data on the SO pin is always clocked out on the falling edge of SCK.InputSI SERIAL INPUT : The SI pin is used to shift data into the device. The SI pin is used for all data input including command and address sequences. Data on the SI pin is always latched on the rising edge of SCK.InputSO SERIAL OUTPUT : The SO pin is used to shift data out from the device. Data on the SO pin is always clocked out on the falling edge of SCK.OutputWP WRITE PROTECT : The WP pin controls the hardware locking feature of the device. Please refer to “Protection Commands and Features” on page 11 for more details on protection features and the WP pin.The WP pin is internally pulled-high and may be left floating if hardware controlled protection will not be used. However, it is recommended that the WP pin also be externally connected to V CC whenever possible.Low InputV CC DEVICE POWER SUPPLY : The V CC pin is used to supply the source voltage to the device.Operations at invalid V CC voltages may produce spurious results and should not be attempted.Power GNDGROUND : The ground reference for the power supply. GND should be connected to the system ground.Power33633C–DFLASH–08/06AT26DF321 [Preliminary]3.Block Diagram4.Memory ArrayTo provide the greatest flexibility, the memory array of the AT26DF321 can be erased in four lev-els of granularity including a full chip erase. In addition, the array has been divided into physical sectors of uniform size, of which each sector can be individually protected from program and erase operations. The size of the physical sectors is optimized for both code and data storage applications, allowing both code and data segments to reside in their own isolated regions.Figure 4-1 on page 4 illustrates the breakdown of each erase level as well as the break-down of each physical sector.Figure 2-1.8-SOIC Top ViewFigure 2-2.16-SOIC Top View43633C–DFLASH–08/06AT26DF321 [Preliminary]Figure 4-1.Memory Architecture Diagram53633C–DFLASH–08/06AT26DF321 [Preliminary]5.Device OperationThe AT26DF321 is controlled by a set of instructions that are sent from a host controller, com-monly referred to as the SPI Master. The SPI Master communicates with the AT26DF321 via the SPI bus which is comprised of four signal lines: Chip Select (CS), Serial Clock (SCK), Serial Input (SI), and Serial Output (SO).The SPI protocol defines a total of four modes of operation (mode 0, 1, 2, or 3) with each mode differing in respect to the SCK polarity and phase and how the polarity and phase control the flow of data on the SPI bus. The AT26DF321 supports the two most common modes, SPI Modes 0 and 3. The only difference between SPI Modes 0 and 3 is the polarity of the SCK signal when in the inactive state (when the SPI Master is in standby mode and not transferring any data). With SPI Modes 0 and 3, data is always latched in on the rising edge of SCK and always output on the falling edge of SCK.Figure 5-1.SPI Mode 0 and 3mands and Addressingpin has been asserted, the SPI Master must then clock out a valid 8-bit opcode on the SPI bus.Following the opcode, instruction dependent information such as address and data bytes would then be clocked out by the SPI Master. All opcode, address, and data bytes are transferred with Opcodes not supported by the AT26DF321 will be ignored by the device and no operation will be started. The device will continue to ignore any data presented on the SI pin until the start of the next operation (CS pin being deasserted and then reasserted). In addition, if the CS pin is deas-serted before complete opcode and address information is sent to the device, then no operation will be performed and the device will simply return to the idle state and wait for the next operation.Addressing of the device requires a total of three bytes of information to be sent, representing address bits A23-A0. Since the upper address limit of the AT26DF321 memory array is 3FFFFFh, address bits A23-A22 are always ignored by the device.63633C–DFLASH–08/06AT26DF321 [Preliminary]Table 6-1.Command ListingCommandOpcodeAddress BytesDummy BytesData BytesRead CommandsRead Array0Bh 0000 1011311+Read Array (Low Frequency)03h0000 001131+Program and Erase CommandsBlock Erase (4-KBytes)20h 0010 0000300Block Erase (32-KBytes)52h 0101 0010300Block Erase (64-KBytes)D8h 1101 1000300Chip Erase60h 0110 0000000C7h 1100 0111000Byte/Page Program (1 to 256 Bytes)02h0000 001031+Protection CommandsWrite Enable 06h 0000 0110000Write Disable 04h 0000 0100000Protect Sector 36h 0011 0110300Unprotect Sector 39h0011 10013Global Protect/Unprotect Use Write Status Register commandRead Sector Protection Registers 3Ch 0011 110031+Status Register CommandsRead Status Register 05h 0000 0101001+Write Status Register 01h0000 00011Miscellaneous CommandsRead Manufacturer and Device ID 9Fh 1001 111100 1 to 4Deep Power-DownB9h 1011 1001000Resume from Deep Power-DownABh1010 101173633C–DFLASH–08/06AT26DF321 [Preliminary]7.Read Commands7.1Read ArrayThe Read Array command can be used to sequentially read a continuous stream of data from the device by simply providing the SCK signal once the initial starting address has been speci-fied. The device incorporates an internal address counter that automatically increments on every clock cycle.Two opcodes, 0Bh and 03h, can be used for the Read Array command. The use of each opcode depends on the maximum SCK frequency that will be used to read data from the device. The 0Bh opcode can be used at any SCK frequency up to the maximum specified by f SCK . The 03h opcode can be used for lower frequency read operations up to the maximum specified by f RDLF .To perform the Read Array operation, the CS pin must first be asserted and the appropriate opcode (0Bh or 03h) must be clocked into the device. After the opcode has been clocked in, the three address bytes must be clocked in to specify the starting address location of the first byte to read within the memory array. If the 0Bh opcode is used, then one don’t care byte must also be clocked in after the three address bytes.After the three address bytes (and the one don’t care byte if using opcode 0Bh) have been clocked in, additional clock cycles will result in serial data being output on the SO pin. The data is always output with the MSB of a byte first. When the last byte (3FFFFFh) of the memory array has been read, the device will continue reading back at the beginning of the array (000000h). No delays will be incurred when wrapping around from the end of the array to the beginning of the array.ance state. The CS pin can be deasserted at any time and does not require that a full byte of data be read.Figure 7-1.Read Array – 0Bh OpcodeFigure 7-2.Read Array – 03h Opcode83633C–DFLASH–08/06AT26DF321 [Preliminary]8.Program and Erase Commands8.1Byte/Page ProgramThe Byte/Page Program command allows anywhere from a single byte of data to 256 bytes of data to be programmed into previously erased memory locations. An erased memory location is one that has all eight bits set to the logical “1” state (a byte value of FFh). Before a Byte/Page Program command can be started, the Write Enable command must have been previously issued to the device (see Write Enable command description) to set the Write Enable Latch (WEL) bit of the Status Register to a logical “1” state.To perform a Byte/Page Program command, an opcode of 02h must be clocked into the device followed by the three address bytes denoting the first byte location of the memory array to begin programming at. After the address bytes have been clocked in, data can then be clocked into the device and will be stored in an internal buffer.If the starting memory address denoted by A23-A0 does not fall on an even 256-byte page boundary (A7-A0 are not all 0), then special circumstances regarding which memory locations will be programmed will apply. In this situation, any data that is sent to the device that goes beyond the end of the page will wrap around back to the beginning of the same page. For exam-ple, if the starting address denoted by A23-A0 is 0000FEh, and three bytes of data are sent to the device, then the first two bytes of data will be programmed at addresses 0000FEh and 0000FFh while the last byte of data will be programmed at address 000000h. The remaining bytes in the page (addresses 000001h through 0000FDh) will be unaffected and will not change.In addition, if more than 256 bytes of data are sent to the device, then only the last 256 bytes sent will be latched into the internal buffer.When the CS pin is deasserted, the device will take the data stored in the internal buffer and pro-gram it into the appropriate memory array locations based on the starting address specified by A23-A0 and the number of complete data bytes sent to the device. If less than 256 bytes of data were sent to the device, then the remaining bytes within the page will not be altered. The pro-gramming of the data bytes is internally self-timed and should take place in a time of t PP .The three address bytes and at least one complete byte of data must be clocked into the device before the CS pin is deasserted; otherwise, the device will abort the operation and no data will be programmed into the memory array. In addition, if the address specified by A23-A0 points to a memory location within a sector that is in the protected state (see “Protect Sector” on page 12), then the Byte/Page Program command will not be executed, and the device will return to the idle state once the CS pin has been deasserted. The WEL bit in the Status Register will be reset back to the logical “0” state if the program cycle aborts due to an incomplete address being sent,an incomplete byte of data being sent, or because the memory location to be programmed is protected.While the device is programming, the Status Register can be read and will indicate that the device is busy. For faster throughput, it is recommended that the Status Register be polled rather than waiting the t PP time to determine if the data bytes have finished programming. At some point before the program cycle completes, the WEL bit in the Status Register will be reset back to the logical “0” state.93633C–DFLASH–08/06AT26DF321 [Preliminary]Figure 8-1.Byte ProgramFigure 8-2.Page Program8.2Block EraseA block of 4K-, 32K-, or 64K-bytes can be erased (all bits set to the logical “1” state) in a single operation by using one of three different opcodes for the Block Erase command. An opcode of 20h is used for a 4K-byte erase, an opcode of 52h is used for a 32K-byte erase, and an opcode of D8h is used for a 64K-byte erase. Before a Block Erase command can be started, the Write Enable command must have been previously issued to the device to set the WEL bit of the Sta-tus Register to a logical “1” state.52h, or D8h) must be clocked into the device. After the opcode has been clocked in, the three address bytes specifying an address within the 4K-, 32K-, or 64K-byte block to be erased must be clocked in. Any additional data clocked into the device will be ignored. When the CS pin is deasserted, the device will erase the appropriate block. The erasing of the block is internally self-timed and should take place in a time of t BLKE .Since the Block Erase command erases a region of bytes, the lower order address bits do not need to be decoded by the device. Therefore, for a 4K-byte erase, address bits A11-A0 will be ignored by the device and their values can be either a logical “1” or “0”. For a 32K-byte erase,address bits A14-A0 will be ignored, and for a 64K-byte erase, address bits A15-A0 will be ignored by the device. Despite the lower order address bits not being decoded by the device, the complete three address bytes must still be clocked into the device before the CS pin is deas-serted; otherwise, the device will abort the operation and no erase operation will be performed.103633C–DFLASH–08/06AT26DF321 [Preliminary]If the address specified by A23-A0 points to a memory location within a sector that is in the pro-tected state, then the Block Erase command will not be executed, and the device will return to The WEL bit in the Status Register will be reset back to the logical “0” state if the erase cycle aborts due to an incomplete address being sent or because a memory location within the region to be erased is protected.While the device is executing a successful erase cycle, the Status Register can be read and will indicate that the device is busy. For faster throughput, it is recommended that the Status Regis-ter be polled rather than waiting the t BLKE time to determine if the device has finished erasing. At some point before the erase cycle completes, the WEL bit in the Status Register will be reset back to the logical “0” state.Figure 8-3.Block Erase8.3Chip EraseThe entire memory array can be erased in a single operation by using the Chip Erase command.Before a Chip Erase command can be started, the Write Enable command must have been pre-viously issued to the device to set the WEL bit of the Status Register to a logical “1” state.Two opcodes, 60h and C7h, can be used for the Chip Erase command. There is no difference in device functionality when utilizing the two opcodes, so they can be used interchangeably. To perform a Chip Erase, one of the two opcodes (60h or C7h) must be clocked into the device.Since the entire memory array is to be erased, no address bytes need to be clocked into the device, and any data clocked in after the opcode will be ignored. When the CS pin is deasserted,the device will erase the entire memory array. The erasing of the device is internally self-timed and should take place in a time of t CHPE .wise, no erase will be performed. In addition, if any sector of the memory array is in the protected state, then the Chip Erase command will not be executed, and the device will return to the idle state once the CS pin has been deasserted. The WEL bit in the Status Register will be reset back to the logical “0” state if a sector is in the protected state.While the device is executing a successful erase cycle, the Status Register can be read and will indicate that the device is busy. For faster throughput, it is recommended that the Status Regis-ter be polled rather than waiting the t CHPE time to determine if the device has finished erasing. At some point before the erase cycle completes, the WEL bit in the Status Register will be reset back to the logical “0” state.AT26DF321 [Preliminary] Figure 8-4.Chip Erase9.Protection Commands and Features9.1Write EnableThe Write Enable command is used to set the Write Enable Latch (WEL) bit in the Status Regis-ter to a logical “1” state. The WEL bit must be set before a program, erase, Protect Sector,Unprotect Sector, or Write Status Register command can be executed. This makes the issuanceof these commands a two step process, thereby reducing the chances of a command beingaccidentally or erroneously executed. If the WEL bit in the Status Register is not set prior to theissuance of one of these commands, then the command will not be executed.must be clocked into the device. No address bytes need to be clocked into the device, and anythe Status Register will be set to a logical “1”. The complete opcode must be clocked into thestate of the WEL bit will not change.Figure 9-1.Write Enable9.2Write DisableThe Write Disable command is used to reset the Write Enable Latch (WEL) bit in the Status Reg-ister to the logical “0” state. With the WEL bit reset, all program, erase, Protect Sector, UnprotectSector, and Write Status Register commands will not be executed. The Write Disable commandis also used to exit the Sequential Program Mode. Other conditions can also cause the WEL bitto be reset; for more details, refer to the WEL bit section of the Status Register description onpage 20.must be clocked into the device. No address bytes need to be clocked into the device, and anythe Status Register will be reset to a logical “0”. The complete opcode must be clocked into thestate of the WEL bit will not change.Figure 9-2.Write Disable9.3Protect SectorEvery physical sector of the device has a corresponding single-bit Sector Protection Registerthat is used to control the software protection of a sector. Upon device power-up or after adevice reset, each Sector Protection Register will default to the logical “1” state indicating that allsectors are protected and cannot be programmed or erased.Issuing the Protect Sector command to a particular sector address will set the correspondingSector Protection Register to the logical “1” state. The following table outlines the two states ofthe Sector Protection Registers.Table 9-1.Sector Protection Register ValuesValue Sector Protection Status0Sector is unprotected and can be programmed and erased.1Sector is protected and cannot be programmed or erased. This is the default state.Before the Protect Sector command can be issued, the Write Enable command must have beenpreviously issued to set the WEL bit in the Status Register to a logical “1”. To issue the ProtectSector command, the CS pin must first be asserted and the opcode of 36h must be clocked intothe device followed by three address bytes designating any address within the sector to belocked. Any additional data clocked into the device will be ignored. When the CS pin is deas-serted, the Sector Protection Register corresponding to the physical sector addressed by A23-A0 will be set to the logical “1” state, and the sector itself will then be protected from programAT26DF321 [Preliminary] and erase operations. In addition, the WEL bit in the Status Register will be reset back to the log-ical “0” state.serted; otherwise, the device will abort the operation, the state of the Sector Protection Registerwill be unchanged, and the WEL bit in the Status Register will be reset to a logical “0”.As a safeguard against accidental or erroneous protecting or unprotecting of sectors, the SectorProtection Registers can themselves be locked from updates by using the SPRL (Sector Protec-tion Registers Locked) bit of the Status Register (please refer to “Status Register Commands”on page 19 for more details). If the Sector Protection Registers are locked, then any attempts toissue the Protect Sector command will be ignored, and the device will reset the WEL bit in thedeasserted.Figure 9-3.Protect Sector9.4Unprotect SectorIssuing the Unprotect Sector command to a particular sector address will reset the correspond-ing Sector Protection Register to the logical “0” state (see Table 9-1 on page 12 for SectorProtection Register values). Every physical sector of the device has a corresponding single-bitSector Protection Register that is used to control the software protection of a sector.Before the Unprotect Sector command can be issued, the Write Enable command must havebeen previously issued to set the WEL bit in the Status Register to a logical “1”. To issue theUnprotect Sector command, the CS pin must first be asserted and the opcode of 39h must beclocked into the device. After the opcode has been clocked in, the three address bytes designat-ing any address within the sector to be unlocked must be clocked in. Any additional data clockedtor Protection Register corresponding to the sector addressed by A23-A0 will be reset to thelogical “0” state, and the sector itself will be unprotected. In addition, the WEL bit in the StatusRegister will be reset back to the logical “0” state.serted; otherwise, the device will abort the operation, the state of the Sector Protection Registerwill be unchanged, and the WEL bit in the Status Register will be reset to a logical “0”.As a safeguard against accidental or erroneous locking or unlocking of sectors, the Sector Pro-tection Registers can themselves be locked from updates by using the SPRL (Sector ProtectionRegisters Locked) bit of the Status Register (please refer to “Status Register Commands” onpage 19 for more details). If the Sector Protection Registers are locked, then any attempts toissue the Unprotect Sector command will be ignored, and the device will reset the WEL bit in theStatus Register back to a logical “0” and return to the idle state once the CS pin has beendeasserted.Figure 9-4.Unprotect Sector9.5Global Protect/UnprotectThe Global Protect and Global Unprotect features can work in conjunction with the Protect Sec-tor and Unprotect Sector functions. For example, a system can globally protect the entirememory array and then use the Unprotect Sector command to individually unprotect certain sec-tors and individually reprotect them later by using the Protect Sector command. Likewise, asystem can globally unprotect the entire memory array and then individually protect certain sec-tors as needed.Performing a Global Protect or Global Unprotect is accomplished by writing a certain combina-tion of data to the Status Register using the Write Status Register command (see “Write StatusRegister” section on page 21 for command execution details). The Write Status Register com-mand is also used to modify the SPRL (Sector Protection Registers Locked) bit to controlhardware and software locking.To perform a Global Protect, the appropriate WP pin and SPRL conditions must be met and thesystem must write a logical “1” to bits 5, 4, 3, and 2 of the Status Register. Conversely, to per-form a Global Unprotect, the same WP and SPRL conditions must be met but the system mustwrite a logical “0” to bits 5, 4, 3, and 2 of the Status Register. Table 9-2 details the conditionsnecessary for a Global Protect or Global Unprotect to be performed.AT26DF321 [Preliminary]Essentially, if the SPRL bit of the Status Register is in the logical “0” state (Sector Protection Registers are not locked), then writing a 00h to the Status Register will perform a Global Unpro-tect without changing the state of the SPRL bit. Similarly, writing a 7Fh to the Status Register will perform a Global Protect and keep the SPRL bit in the logical “0” state. The SPRL bit can, of course, be changed to a logical “1” by writing an FFh if software-locking or hardware-locking is desired along with the Global Protect.Table 9-2.Valid SPRL and Global Protect/Unprotect ConditionsWP StateCurrent SPRL Value New Write Status Register Data Protection OperationNew SPRL Value Bit7 6 5 4 3 2 1 000 x 0 0 0 0 x x 0 x 0 0 0 1 x x↕0 x 1 1 1 0 x x 0 x 1 1 1 1 x x1 x 0 0 0 0 x x 1 x 0 0 0 1 x x↕1 x 1 1 1 0 x x 1 x 1 1 1 1 x xGlobal Unprotect – all Sector Protection Registers reset to 0No change to current protection.No change to current protection.No change to current protection.Global Protect – all Sector Protection Registers set to 1Global Unprotect – all Sector Protection Registers reset to 0No change to current protection.No change to current protection.No change to current protection.Global Protect – all Sector Protection Registers set to 100000111111x x x x x x x xNo change to the current protection level. All sectors currentlyprotected will remain protected and all sectors currently unprotected will remain unprotected.The Sector Protection Registers are hard-locked and cannot bechanged when the WP pin is LOW and the current state of SPRL is 1. Therefore, a Global Protect/Unprotect will not occur. In addition, the SPRL bit cannot be changed (the WP pin must be HIGH in order to change SPRL back to a 0).10 x 0 0 0 0 x x 0 x 0 0 0 1 x x↕0 x 1 1 1 0 x x 0 x 1 1 1 1 x x1 x 0 0 0 0 x x 1 x 0 0 0 1 x x↕1 x 1 1 1 0 x x 1 x 1 1 1 1 x x Global Unprotect – all Sector Protection Registers reset to 0No change to current protection.No change to current protection.No change to current protection.Global Protect – all Sector Protection Registers set to 1Global Unprotect – all Sector Protection Registers reset to 0No change to current protection.No change to current protection.No change to current protection.Global Protect – all Sector Protection Registers set to 10000011111110 x 0 0 0 0 x x 0 x 0 0 0 1 x x↕0 x 1 1 1 0 x x 0 x 1 1 1 1 x x1 x 0 0 0 0 x x 1 x 0 0 0 1 x x↕1 x 1 1 1 0 x x 1 x 1 1 1 1 x xNo change to the current protection level. All sectors currently protected will remain protected, and all sectors currently unprotected will remain unprotected.The Sector Protection Registers are soft-locked and cannot be changed when the current state of SPRL is 1. Therefore, a Global Protect/Unprotect will not occur. However, theSPRL bit can be changed back to a 0 from a 1 since the WP pin is HIGH. To perform a Global Protect/Unprotect, the Write Status Register command must be issued again after the SPRL bit has been changed from a 1 to a 0.0000011111。

R5F212A7SNFA中文资料

A/D Converter

10-bit resolution × 12 channels, includes sample and hold function

D/A Converter Flash Memory

8-bit resolution × 2 circuits • Programming and erasure voltage: VCC = 2.7 to 5.5 V

Timer RC

shot generation mode

16 bits × 1 (with 4 capture/compare registers) Timer mode (input capture function, output compare function), PWM mode

Timer RD

Memory

ROM, RAM

Power Supply Voltage detection

Voltage

ciperation mode: Single-chip mode (address space: 1 Mbyte) Refer to Table 1.5 Product List for R8C/2A Group. • Power-on reset • Voltage detection 2

Table 1.1 Specifications for R8C/2A Group (1)

Item CPU

Function

Specification

Central processing R8C/Tiny series core

unit

• Number of fundamental instructions: 89

circuits

艾默生PEX系列精密空调技术手册

风量/洁净度控制:计算机及交换机工作时产生大量的显热,为了能迅速地排除这些热量,要求空调具有足够大的冷却循环风量和足够远的送风距离。机房空调要求每3.5kW制冷量配850~1020m3/h的风量。同时,机房对空气洁净度的严格需求要求空调机组应提供相当于30次/小时换气次数的风量,以便对空气进行过滤。这是民用空调无法处理的。

目录toco22hzt标题11标题33篇题1附录标题11附录标题33第一章前言111机房环境的特殊要求112pex系列空调机房的专业空调1第二章产品介绍221外观介绍222型号说明323主要特点324标准部件4241室内机4242室外机适用风冷系列6243控制系统725选配部件8第三章技术参数931风冷机组技术参数9311上出风风冷机组技术参数9312下出风风冷机组技术参数1532水冷机组技术参数22321上出风水冷机组技术参数22322下出风水冷机组技术参数2433使用条件27第四章尺寸参数2841机械尺寸28411室内机28412室外机3242安装底座尺寸3443风帽尺寸3544维护空间36第五章应用指导3751制冷剂管路37511一般原则37512布管38513接管3952水冷系统40521一般原则40522布管41523接管4153风冷系统42531一般原则42532布管4254控制器43541主电路连接43542控制器连接43543多机群控44前言本章主要介绍机房环境的特殊要求和liebertpex系列空调以下简称pex系列空调的特点和优势等内容

水冷系列采用高效板式换热器,具有结构紧凑、能效比高、对室外环境噪音污染少等优点。

电容式限位开关 minicap FTC260,FTC262 说明书

L1 N P E or L+ L-

U~~20...253V U... 20...55V

Minicap三 线 制 DC供 电 ; 晶 体 管 PNP输 出: F: 细 径 保 险 丝

5 00 mA。 R: 带 负 载 , 如

P LC, PC S继 电 器等。 M: 与 料 仓 或 料 仓 上的金属元件 相连的接地 线。 E:接 地 。

f) 侧面 安装 。

c) 机械 负载 : 在进行低 物位探测时,必须注意探 测的拉力 和仓顶的承截压力,特别 是那些重 量大、粉状块且易形成粘 附的材质 ,在出料口会产生很大的 拉力,在 出料口处的拉力远远大于 仓壁 处的拉力。用于低物位探测 时 ,Minicap FTC 262只 能 用 于 重量

测量系统

Min icap是一 个电 子 开关 ,完 整 的测 量系 统由 以下 部 件组成: ·Mi n ic ap F TC2 60或F TC 262 ·电源 ·控 制器 、开关 设备、信号 变送器 (如 , 灯、 报警 器 、PC S、P LC等 )

固体 料仓的 限 位监测

测量原理

限位 监 测

FTC 260: 等 级 Ⅱ ,F TC 2 62: 等级 Ⅰ

参考条件 (塑 料 罐)

大 气 温度23℃ ,工 作 温 度2 3℃ ,工 作压 力P e=0b ar, 介 质 :介 电常 数 = 2.6,电 导率<1μs, 灵 敏 度设 置:C

迟滞

FTC 26 0 水平 :4 mm, 垂直 :7 mm

Minicap有 反 极 性 保护,如果接线反 向,则指示待机的 绿灯熄灭。

FTC 260无 接 地 线 (PE)或 等 势 线 (PAL) 。

R5F212AASDFP资料

R8C/2A Group, R8C/2B GroupRENESAS MCU1.Overview1.1FeaturesThe R8C/2A Group and R8C/2B Group of single-chip MCUs incorporates the R8C/Tiny Series CPU core,employing sophisticated instructions for a high level of efficiency. With 1 Mbyte of address space and is capable of executing instructions at high speed. In addition, the CPU core boasts a multiplier for high-speed operation processing.Power consumption is low, and the supported operating modes allow additional power control. These MCUs also use an anti-noise configuration to reduce emissions of electromagnetic noise and are designed to withstand EMI.Integration of many peripheral functions, including multifunction timer and serial interface, reduces the number of system components.Furthermore, the R8C/2B Group has on-chip data flash (1 KB × 2 blocks).The difference between the R8C/2A Group and R8C/2B Group is only the presence or absence of data flash. Their peripheral functions are the same.1.1.1ApplicationsElectronic household appliances, office equipment, audio equipment, consumer equipment, etc.REJ03B0182-0100Rev.1.00Feb 09, 20071.1.2SpecificationsTables 1.1 and 1.2 outlines the Specifications for R8C/2A Group and Tables 1.3 and 1.4 outlines the Specifications for R8C/2B GroupTable 1.1Specifications for R8C/2A Group (1)Item Function SpecificationCPU Central processingunit R8C/Tiny series core•Number of fundamental instructions: 89•Minimum instruction execution time:50 ns (f(XIN) = 20 MHz, VCC = 3.0 to 5.5 V)100 ns (f(XIN) = 10 MHz, VCC = 2.7 to 5.5 V)200 ns (f(XIN) = 5 MHz, VCC = 2.2 to 5.5 V)•Multiplier: 16 bits × 16 bits → 32 bits•Multiply-accumulate instruction: 16 bits × 16 bits + 32 bits → 32 bits •Operation mode: Single-chip mode (address space: 1 Mbyte)Memory ROM, RAM Refer to Table 1.5 Product List for R8C/2A Group.Power Supply Voltage Detection Voltage detectioncircuit•Power-on reset•Voltage detection 2I/O Ports Programmable I/Oports •Input-only: 2 pins•CMOS I/O ports: 55, selectable pull-up resistor •High current drive ports: 8Clock Clock generationcircuits 3 circuits: XIN clock oscillation circuit (with on-chip feedback resistor),On-chip oscillator (high-speed, low-speed)(high-speed on-chip oscillator has a frequency adjustment function),XCIN clock oscillation circuit (32 kHz)•Oscillation stop detection: XIN clock oscillation stop detection function •Frequency divider circuit: Dividing selectable 1, 2, 4, 8, and 16•Low power consumption modes:Standard operating mode (high-speed clock, low-speed clock, high-speed on-chip oscillator, low-speed on-chip oscillator), wait mode, stop modeInterrupts•External: 5 sources, Internal: 23 sources, Software: 4 sources•Priority levels: 7 levelsWatchdog Timer15 bits × 1 (with prescaler), reset start selectableTimer Timer RA8 bits × 1 (with 8-bit prescaler)Timer mode (period timer), pulse output mode (output level inverted everyperiod), event counter mode, pulse width measurement mode, pulse periodmeasurement modeTimer RB8 bits × 1 (with 8-bit prescaler)Timer mode (period timer), programmable waveform generation mode (PWMoutput), programmable one-shot generation mode, programmable wait one-shot generation modeTimer RC16 bits × 1 (with 4 capture/compare registers)Timer mode (input capture function, output compare function), PWM mode(output 3 pins), PWM2 mode (PWM output pin)Timer RD16 bits × 2 (with 4 capture/compare registers)Timer mode (input capture function, output compare function), PWM mode(output 6 pins), reset synchronous PWM mode (output three-phasewaveforms (6 pins), sawtooth wave modulation), complementary PWM mode(output three-phase waveforms (6 pins), triangular wave modulation), PWM3mode (PWM output 2 pins with fixed period)Timer RE8 bits × 1Real-time clock mode (count seconds, minutes, hours, days of week), outputcompare modeTimer RF16 bits × 1 (with capture/compare register pin and compare register pin)Input capture mode, output compare modeNOTES:1.I 2C bus is a trademark of Koninklijke Philips Electronics N. V.2.Specify the D version if D version functions are to be used.Table 1.2Specifications for R8C/2A Group (2)Item Function SpecificationSerial Interface UART0, UART1, UART2Clock synchronous serial I/O/UART × 3Clock Synchronous Serial I/O with Chip Select (SSU) 1 (shared with I 2C-bus)I 2C bus (1) 1 (shared with SSU)LIN Module Hardware LIN: 1 (timer RA, UART0)A/D Converter 10-bit resolution × 12 channels, includes sample and hold function D/A Converter 8-bit resolution × 2 circuitsFlash Memory•Programming and erasure voltage: VCC = 2.7 to 5.5 V •Programming and erasure endurance: 100 times •Program security: ROM code protect, ID code check•Debug functions: On-chip debug, on-board flash rewrite function Operating Frequency/Supply Voltagef(XIN) = 20 MHz (VCC = 3.0 to 5.5 V)f(XIN) = 10 MHz (VCC = 2.7 to 5.5 V)f(XIN) = 5 MHz (VCC = 2.2 to 5.5 V)Current consumption12 mA (VCC = 5.0 V, f(XIN) = 20 MHz)5.5 mA (VCC = 3.0 V, f(XIN) = 10 MHz)2.1 µA (VCC =3.0 V, wait mode (f(XCIN) = 32 kHz))0.65 µA (VCC = 3.0 V, stop mode)Operating Ambient Temperature -20 to 85°C (N version)-40 to 85°C (D version)(2)Package64-pin LQFP•Package code: PLQP0064KB-A (previous code: 64P6Q-A)•Package code: PLQP0064GA-A (previous code: 64P6U-A)Table 1.3Specifications for R8C/2B Group (1)Item Function SpecificationCPU Central processingunit R8C/Tiny series core•Number of fundamental instructions: 89•Minimum instruction execution time:50 ns (f(XIN) = 20 MHz, VCC = 3.0 to 5.5 V)100 ns (f(XIN) = 10 MHz, VCC = 2.7 to 5.5 V)200 ns (f(XIN) = 5 MHz, VCC = 2.2 to 5.5 V)•Multiplier: 16 bits × 16 bits → 32 bits•Multiply-accumulate instruction: 16 bits × 16 bits + 32 bits → 32 bits •Operation mode: Single-chip mode (address space: 1 Mbyte)Memory ROM, RAM Refer to Table 1.6 Product List for R8C/2B Group.Power Supply Voltage Detection Voltage detectioncircuit•Power-on reset•Voltage detection 2I/O Ports Programmable I/Oports •Input-only: 2 pins•CMOS I/O ports: 55, selectable pull-up resistor •High current drive ports: 8Clock Clock generationcircuits 3 circuits: XIN clock oscillation circuit (with on-chip feedback resistor),On-chip oscillator (high-speed, low-speed)(high-speed on-chip oscillator has a frequency adjustment function),XCIN clock oscillation circuit (32 kHz)•Oscillation stop detection: XIN clock oscillation stop detection function •Frequency divider circuit: Dividing selectable 1, 2, 4, 8, and 16•Low power consumption modes:Standard operating mode (high-speed clock, low-speed clock, high-speed on-chip oscillator, low-speed on-chip oscillator), wait mode, stop modeInterrupts•External: 5 sources, Internal: 23 sources, Software: 4 sources•Priority levels: 7 levelsWatchdog Timer15 bits × 1 (with prescaler), reset start selectableTimer Timer RA8 bits × 1 (with 8-bit prescaler)Timer mode (period timer), pulse output mode (output level inverted everyperiod), event counter mode, pulse width measurement mode, pulse periodmeasurement modeTimer RB8 bits × 1 (with 8-bit prescaler)Timer mode (period timer), programmable waveform generation mode (PWMoutput), programmable one-shot generation mode, programmable wait one-shot generation modeTimer RC16 bits × 1 (with 4 capture/compare registers)Timer mode (input capture function, output compare function), PWM mode(output 3 pins), PWM2 mode (PWM output pin)Timer RD16 bits × 2 (with 4 capture/compare registers)Timer mode (input capture function, output compare function), PWM mode(output 6 pins), reset synchronous PWM mode (output three-phasewaveforms (6 pins), sawtooth wave modulation), complementary PWM mode(output three-phase waveforms (6 pins), triangular wave modulation), PWM3mode (PWM output 2 pins with fixed period)Timer RE8 bits × 1Real-time clock mode (count seconds, minutes, hours, days of week), outputcompare modeTimer RF16 bits × 1 (with capture/compare register pin and compare register pin)Input capture mode, output compare modeNOTES:1.I 2C bus is a trademark of Koninklijke Philips Electronics N. V.2.Specify the D version if D version functions are to be used.Table 1.4Specifications for R8C/2B Group (2)Item Function SpecificationSerial Interface UART0, UART1, UART2Clock synchronous serial I/O/UART × 3Clock Synchronous Serial I/O with Chip Select (SSU) 1 (shared with I 2C-bus)I 2C bus (1) 1 (shared with SSU)LIN Module Hardware LIN: 1 (timer RA, UART0)A/D Converter 10-bit resolution × 12 channels, includes sample and hold function D/A Converter 8-bit resolution × 2 circuitsFlash Memory•Programming and erasure voltage: VCC = 2.7 to 5.5 V•Programming and erasure endurance: 10,000 times (data flash)1,000 times (program ROM)•Program security: ROM code protect, ID code check•Debug functions: On-chip debug, on-board flash rewrite function Operating Frequency/Supply Voltagef(XIN) = 20 MHz (VCC = 3.0 to 5.5 V)f(XIN) = 10 MHz (VCC = 2.7 to 5.5 V)f(XIN) = 5 MHz (VCC = 2.2 to 5.5 V)Current consumption12 mA (VCC = 5.0 V, f(XIN) = 20 MHz)5.5 mA (VCC = 3.0 V, f(XIN) = 10 MHz)2.1 µA (VCC =3.0 V, wait mode (f(XCIN) = 32 kHz))0.65 µA (VCC = 3.0 V, stop mode)Operating Ambient Temperature -20 to 85°C (N version)-40 to 85°C (D version)(2)Package64-pin LQFP•Package code: PLQP0064KB-A (previous code: 64P6Q-A)•Package code: PLQP0064GA-A (previous code: 64P6U-A)1.2Product ListTable 1.5 lists Product List for R8C/2A Group, Figure 1.1 shows a Part Number, Memory Size, and Package of R8C/2A Group, Table 1.6 lists Product List for R8C/2B Group, and Figure 1.2 shows a Part Number, Memory Size, and Package of R8C/2B Group.Table 1.5Product List for R8C/2A Group Current of Feb. 2007 Part No.ROM Capacity RAM Capacity Package Type RemarksR5F212A7SNFP48 Kbytes 2.5 Kbytes PLQP0064KB-A N versionR5F212A7SNFA48 Kbytes 2.5 Kbytes PLQP0064GA-AR5F212A8SNFP64 Kbytes 3 Kbytes PLQP0064KB-AR5F212A8SNFA64 Kbytes 3 Kbytes PLQP0064GA-AR5F212AASNFP (D)96 Kbytes7 Kbytes PLQP0064KB-AR5F212AASNFA (D)96 Kbytes7 Kbytes PLQP0064GA-AR5F212ACSNFP (D)128 Kbytes7.5 Kbytes PLQP0064KB-AR5F212ACSNFA (D)128 Kbytes7.5 Kbytes PLQP0064GA-AR5F212A7SDFP (D)48 Kbytes 2.5 Kbytes PLQP0064KB-A D versionR5F212A7SDFA (D)48 Kbytes 2.5 Kbytes PLQP0064GA-AR5F212A8SDFP (D)64 Kbytes 3 Kbytes PLQP0064KB-AR5F212A8SDFA (D)64 Kbytes 3 Kbytes PLQP0064GA-AR5F212AASDFP (D)96 Kbytes7 Kbytes PLQP0064KB-AR5F212AASDFA (D)96 Kbytes7 Kbytes PLQP0064GA-AR5F212ACSDFP (D)128 Kbytes7.5 Kbytes PLQP0064KB-AR5F212ACSDFA (D)128 Kbytes7.5 Kbytes PLQP0064GA-A(D): Under development(D): Under developmentTable 1.6Product List for R8C/2B GroupCurrent of Feb. 2007Part No.ROM CapacityRAMCapacity Package TypeRemarksProgram ROM Data flash R5F212B7SNFP 48 Kbytes 1 Kbyte × 2 2.5 Kbytes PLQP0064KB-A N version R5F212B7SNFA 48 Kbytes 1 Kbyte × 2 2.5 Kbytes PLQP0064GA-A R5F212B8SNFP 64 Kbytes 1 Kbyte × 2 3 Kbytes PLQP0064KB-A R5F212B8SNFA 64 Kbytes 1 Kbyte × 2 3 Kbytes PLQP0064GA-A R5F212BASNFP (D)96 Kbytes 1 Kbyte × 27 Kbytes PLQP0064KB-A R5F212BASNFA (D)96 Kbytes 1 Kbyte × 27 Kbytes PLQP0064GA-A R5F212BCSNFP (D)128 Kbytes 1 Kbyte × 27.5 Kbytes PLQP0064KB-A R5F212BCSNFA (D)128 Kbytes 1 Kbyte × 27.5 Kbytes PLQP0064GA-AR5F212B7SDFP (D)48 Kbytes 1 Kbyte × 2 2.5 Kbytes PLQP0064KB-A D version R5F212B7SDFA (D)48 Kbytes 1 Kbyte × 2 2.5 Kbytes PLQP0064GA-A R5F212B8SDFP (D)64 Kbytes 1 Kbyte × 2 3 Kbytes PLQP0064KB-A R5F212B8SDFA (D)64 Kbytes 1 Kbyte × 2 3 Kbytes PLQP0064GA-A R5F212BASDFP (D)96 Kbytes 1 Kbyte × 27 Kbytes PLQP0064KB-A R5F212BASDFA (D)96 Kbytes 1 Kbyte × 27 Kbytes PLQP0064GA-A R5F212BCSDFP (D)128 Kbytes 1 Kbyte × 27.5 Kbytes PLQP0064KB-A R5F212BCSDFA (D)128 Kbytes 1 Kbyte × 27.5 KbytesPLQP0064GA-A1.3 Block DiagramFigure 1.3 shows a Block Diagram.1.4Pin AssignmentFigure 1.4 shows Pin Assignment (Top View). Tables 1.7 and 1.8 outlines the Pin Name Information by Pin Number.NOTE:1.Can be assigned to the pin in parentheses by a program.Table 1.7Pin Name Information by Pin Number (1)PinNumber Control PinPort I/O Pin Functions for of Peripheral ModulesInterruptTimer SerialInterfaceSSU I 2C busA/D Converter,D/A Converter1P3_3SSI 2P3_4SCS SDA3MODE 4XCIN P4_35XCOUT P4_46RESET 7XOUT P4_78VSS/AVSS9XIN P4_610VCC/AVCC11P5_4TRCIOD 12P5_3TRCIOC 13P5_2TRCIOB14P5_1TRCIOA/TRCTRG15P5_0TRCCLK 16P2_7TRDIOD117P2_6TRDIOC118P2_5TRDIOB119P2_4TRDIOA120P2_3TRDIOD021P2_2TRDIOC022P2_1TRDIOB023P2_0TRDIOA0/TRDCLK24P1_7INT1TRAIO25P1_6CLK026P1_5(INT1)(1)(TRAIO)(1)RXD027P1_4TXD028P8_629P8_5TRFO1230P8_4TRFO1131P8_3TRFO10/TRFI 32P8_2TRFO0233P8_1TRFO0134P8_0TRFO0035P6_0TREO 36P4_5INT0INT037P6_6INT2TXD138P6_7INT3RXD139P6_5(CLK1)(1)/CLK240P6_4RXD241P6_3TXD242P3_1TRBO 43P3_0TRAO44P3_6(INT1)(1)45P3_2(INT2)(1)Table 1.8Pin Name Information by Pin Number (2)Pin Number Control Pin PortI/O Pin Functions for of Peripheral ModulesInterrupt TimerSerialInterfaceSSU I2C busA/D Converter,D/A Converter46P1_3Kl3AN11 47P1_2KI2AN10 48P1_1KI1AN9 49P1_0KI0AN8 50P0_0AN7 51P0_1AN6 52P0_2AN5 53P0_3AN4 54P0_4AN3 55P6_256P6_157P0_5CLK1AN2 58P0_6AN1/DA0 59VSS/AVSS60P0_7AN0/DA1 61VREF62VCC/AVCC63P3_7SSO64P3_5SSCK SCL1.5Pin FunctionsTables 1.9 and 1.10 list Pin Functions.I: Input O: Output I/O: Input and output NOTE:1.Refer to the oscillator manufacturer for oscillation characteristics.Table 1.9Pin Functions (1)ItemPin Name I/O TypeDescriptionPower supply input VCC, VSS −Apply 2.2 V to 5.5 V to the VCC pin. Apply 0 V to the VSS pin.Analog power supply input AVCC, AVSS −Power supply for the A/D converter.Connect a capacitor between AVCC and AVSS.Reset input RESET I Input “L” on this pin resets the MCU.MODE MODE I Connect this pin to VCC via a resistor.XIN clock input XIN I These pins are provided for XIN clock generation circuit I/O.Connect a ceramic resonator or a crystal oscillator between the XIN and XOUT pins (1). To use an external clock, input it to the XIN pin and leave the XOUT pin open.XIN clock output XOUT O XCIN clock input XCIN I These pins are provided for XCIN clock generation circuit I/O.Connect a crystal oscillator between the XCIN and XCOUT pins (1). To use an external clock, input it to the XCIN pin and leave the XCOUT pin open.XCIN clock output XCOUT O INT interrupt input INT0 to INT3I INT interrupt input pins.INT0 is timer RD input pin. INT1 is timer RA input pin.Key input interrupt KI0 to KI3I Key input interrupt input pins Timer RA TRAIO I/O Timer RA I/O pin TRAO O Timer RA output pin Timer RB TRBO O Timer RB output pin Timer RCTRCCLK I External clock input pin TRCTRGI External trigger input pin TRCIOA, TRCIOB,TRCIOC, TRCIODI/O Timer RC I/O pins Timer RDTRDIOA0, TRDIOA1, TRDIOB0, TRDIOB1, TRDIOC0, TRDIOC1, TRDIOD0, TRDIOD1I/OTimer RD I/O pinsTRDCLK I External clock input pin Timer RE TREO O Divided clock output pin Timer RFTRFII Timer RF input pin TRFO00 to TRFO02, TRFO10 to TRFO12O Timer RF output pins Serial interface CLK0, CLK1, CLK2I/O Transfer clock I/O pins RXD0, RXD1, RXD2I Serial data input pins TXD0, TXD1, TXD2O Serial data output pins I 2C bus SCL I/O Clock I/O pin SDA I/O Data I/O pin SSUSSI I/O Data I/O pinSCS I/O Chip-select signal I/O pin SSCK I/O Clock I/O pin SSOI/O Data I/O pinReference voltage inputVREFIReference voltage input pin to A/D converter and D/A converterTable 1.10Pin Functions (2)Item Pin Name I/O Type Description A/D converter AN0 to AN11I Analog input pins to A/D converter D/A converter DA0 to DA1O D/A converter output pinsI/O port P0_0 to P0_7,P1_0 to P1_7,P2_0 to P2_7,P3_0 to P3_7,P4_3 to P4_5,P5_0 to P5_4,P6_0 to P6_7,P8_0 to P8_6I/O CMOS I/O ports. Each port has an I/O select direction register, allowing each pin in the port to be directed for inputor output individually.Any port set to input can be set to use a pull-up resistor or notby a program.P2_0 to P2_7 also function as LED drive ports.Input port P4_6, P4_7I Input-only portsI: Input O: Output I/O: Input and output2.Central Processing Unit (CPU)Figure 2.1 shows the CPU Registers. The CPU contains 13 registers. R0, R1, R2, R3, A0, A1, and FB configure a register bank. There are two sets of register bank.2.1Data Registers (R0, R1, R2, and R3)R0 is a 16-bit register for transfer, arithmetic, and logic operations. The same applies to R1 to R3. R0 can be split into high-order bits (R0H) and low-order bits (R0L) to be used separately as 8-bit data registers. R1H and R1L are analogous to R0H and R0L. R2 can be combined with R0 and used as a 32-bit data register (R2R0). R3R1 is analogous to R2R0.2.2Address Registers (A0 and A1)A0 is a 16-bit register for address register indirect addressing and address register relative addressing. It is also used for transfer, arithmetic, and logic operations. A1 is analogous to A0. A1 can be combined with A0 and as a 32-bit address register (A1A0).2.3Frame Base Register (FB)FB is a 16-bit register for FB relative addressing.2.4Interrupt Table Register (INTB)INTB is a 20-bit register that indicates the start address of an interrupt vector table.2.5Program Counter (PC)PC is 20 bits wide and indicates the address of the next instruction to be executed.2.6User Stack Pointer (USP) and Interrupt Stack Pointer (ISP)The stack pointers (SP), USP, and ISP, are each 16 bits wide. The U flag of FLG is used to switch betweenUSP and ISP.2.7Static Base Register (SB)SB is a 16-bit register for SB relative addressing.2.8Flag Register (FLG)FLG is an 11-bit register indicating the CPU state.2.8.1Carry Flag (C)The C flag retains carry, borrow, or shift-out bits that have been generated by the arithmetic and logic unit.2.8.2Debug Flag (D)The D flag is for debugging only. Set it to 0.2.8.3Zero Flag (Z)The Z flag is set to 1 when an arithmetic operation results in 0; otherwise to 0.2.8.4Sign Flag (S)The S flag is set to 1 when an arithmetic operation results in a negative value; otherwise to 0.2.8.5Register Bank Select Flag (B)Register bank 0 is selected when the B flag is 0. Register bank 1 is selected when this flag is set to 1.2.8.6Overflow Flag (O)The O flag is set to 1 when an operation results in an overflow; otherwise to 0.2.8.7Interrupt Enable Flag (I)The I flag enables maskable interrupts.Interrupt are disabled when the I flag is set to 0, and are enabled when the I flag is set to 1. The I flag is set to 0 when an interrupt request is acknowledged.2.8.8Stack Pointer Select Flag (U)ISP is selected when the U flag is set to 0; USP is selected when the U flag is set to 1.The U flag is set to 0 when a hardware interrupt request is acknowledged or the INT instruction of software interrupt numbers 0 to 31 is executed.2.8.9Processor Interrupt Priority Level (IPL)IPL is 3 bits wide and assigns processor interrupt priority levels from level 0 to level 7.If a requested interrupt has higher priority than IPL, the interrupt is enabled.2.8.10Reserved BitIf necessary, set to 0. When read, the content is undefined.3.Memory3.1R8C/2A GroupFigure 3.1 is a Memory Map of R8C/2A Group. The R8C/2A group has 1 Mbyte of address space from addresses 00000h to FFFFFh.The internal ROM is allocated lower addresses, beginning with address 0FFFFh. For example, a 48-Kbyte internal ROM area is allocated addresses 04000h to 0FFFFh.The fixed interrupt vector table is allocated addresses 0FFDCh to 0FFFFh. They store the starting address of each interrupt routine.The internal RAM is allocated higher addresses, beginning with address 00400h. For example, a 2.5-Kbyte internal RAM area is allocated addresses 00400h to 00DFFh. The internal RAM is used not only for storing data but also for calling subroutines and as stacks when interrupt requests are acknowledged.Special function registers (SFRs) are allocated addresses 00000h to 002FFh. The peripheral function control registers are allocated here. All addresses within the SFR, which have nothing allocated are reserved for future use and cannot be accessed by users.3.2R8C/2B GroupFigure 3.2 is a Memory Map of R8C/2B Group. The R8C/2B group has 1 Mbyte of address space from addresses 00000h to FFFFFh.The internal ROM (program ROM) is allocated lower addresses, beginning with address 0FFFFh. For example, a 48-Kbyte internal ROM area is allocated addresses 04000h to 0FFFFh.The fixed interrupt vector table is allocated addresses 0FFDCh to 0FFFFh. They store the starting address of each interrupt routine.The internal ROM (data flash) is allocated addresses 02400h to 02BFFh.The internal RAM area is allocated higher addresses, beginning with address 00400h. For example, a 2.5-Kbyte internal RAM is allocated addresses 00400h to 00DFFh. The internal RAM is used not only for storing data but also for calling subroutines and as stacks when interrupt requests are acknowledged.Special function registers (SFRs) are allocated addresses 00000h to 002FFh. The peripheral function control registers are allocated here. All addresses within the SFR, which have nothing allocated are reserved for future use and cannot be accessed by users.4.Special Function Registers (SFRs)An SFR (special function register) is a control register for a peripheral function. Tables 4.1 to 4.12 list the special function registers.Table 4.1SFR Information (1)(1)Address Register Symbol After reset0000h0001h0002h0003h0004h Processor Mode Register 0PM000h0005h Processor Mode Register 1PM100h0006h System Clock Control Register 0CM001101000b0007h System Clock Control Register 1CM100100000b0008h Module Operation Enable Register MSTCR00h0009h000Ah Protect Register PRCR00h000Bh000Ch Oscillation Stop Detection Register OCD00000100b000Dh Watchdog Timer Reset Register WDTR XXh000Eh Watchdog Timer Start Register WDTS XXh000Fh Watchdog Timer Control Register WDC00X11111b0010h Address Match Interrupt Register 0RMAD000h0011h00h0012h00h0013h Address Match Interrupt Enable Register AIER00h0014h Address Match Interrupt Register 1RMAD100h0015h00h0016h00h0017h0018h0019h001Ah001Bh001Ch Count Source Protection Mode Register CSPR00h10000000b(6) 001Dh001Eh001Fh0020h0021h0022h0023h High-Speed On-Chip Oscillator Control Register 0FRA000h0024h High-Speed On-Chip Oscillator Control Register 1FRA1When shipping0025h High-Speed On-Chip Oscillator Control Register 2FRA200h0026h0027h0028h Clock Prescaler Reset Flag CPSRF00h0029h002Ah002Bh High-Speed On-Chip Oscillator Control Register 6FRA6When Shipping0030h0031h Voltage Detection Register 1(2)VCA100001000b0032h Voltage Detection Register 2(2)VCA200h(3)00100000b(4) 0033h0034h0035h0036h Voltage Monitor 1 Circuit Control Register(5)VW1C00001000b0037h Voltage Monitor 2 Circuit Control Register(5)VW2C00h0038h Voltage Monitor 0 Circuit Control Register(2)VW0C0000X000b(3)0100X001b(4) 0039h003Ah003Bh003Ch003Dh003Eh003FhX: UndefinedNOTES:1.The blank regions are reserved. Do not access locations in these regions.2.Software reset, watchdog timer reset, voltage monitor 1 reset, or voltage monitor 2 reset do not affect this register.3.The LVD0ON bit in the OFS register is set to 1 and hardware reset.4.Power-on reset, voltage monitor 0 reset, or the LVD0ON bit in the OFS register is set to 0 and hardware reset.5.Software reset, watchdog timer reset, voltage monitor 1 reset, or voltage monitor 2 reset do not affect b2 and b3.6.The CSPROINI bit in the OFS register is set to 0.Table 4.2SFR Information (2)(1)Address Register Symbol After reset 0040h0041h0042h0043h0044h0045h0046h0047h Timer RC Interrupt Control Register TRCIC XXXXX000b 0048h Timer RD0 Interrupt Control Register TRD0IC XXXXX000b 0049h Timer RD1 Interrupt Control Register TRD1IC XXXXX000b 004Ah Timer RE Interrupt Control Register TREIC XXXXX000b 004Bh UART2 Transmit Interrupt Control Register S2TIC XXXXX000b 004Ch UART2 Receive Interrupt Control Register S2RIC XXXXX000b 004Dh Key Input Interrupt Control Register KUPIC XXXXX000b 004Eh004Fh SSU/IIC Interrupt Control Register(2)SSUIC / IICIC XXXXX000b 0050h Compare 1 Interrupt Control Register CMP1IC XXXXX000b 0051h UART0 Transmit Interrupt Control Register S0TIC XXXXX000b 0052h UART0 Receive Interrupt Control Register S0RIC XXXXX000b 0053h UART1 Transmit Interrupt Control Register S1TIC XXXXX000b 0054h UART1 Receive Interrupt Control Register S1RIC XXXXX000b 0055h INT2 Interrupt Control Register INT2IC XX00X000b 0056h Timer RA Interrupt Control Register TRAIC XXXXX000b 0057h0058h Timer RB Interrupt Control Register TRBIC XXXXX000b 0059h INT1 Interrupt Control Register INT1IC XX00X000b 005Ah INT3 Interrupt Control Register INT3IC XX00X000b 005Bh Timer RF Interrupt Control Register TRFIC XXXXX000b 005Ch Compare 0 Interrupt Control Register CMP0IC XXXXX000b 005Dh INT0 Interrupt Control Register INT0IC XX00X000b 005Eh A/D Conversion Interrupt Control Register ADIC XXXXX000b 005Fh Capture Interrupt Control Register CAPIC XXXXX000b 0060h0061h0062h0063h0064h0065h0066h0067h0068h0069h006Ah006Bh006Ch006Dh006Eh006Fh0070h0071h0072h0073h0074h0075h0076h0077h0078h0079h007Ah007Bh007Ch007Dh007Eh007FhX: UndefinedNOTES:1.The blank regions are reserved. Do not access locations in these regions.2.Selected by the IICSEL bit in the PMR register.Table 4.3SFR Information (3)(1)Address Register Symbol After reset 0080h0081h0082h0083h0084h0085h0086h0087h0088h0089h008Ah008Bh008Ch008Dh008Eh008Fh0090h0091h0092h0093h0094h0095h0096h0097h0098h0099h009Ah009Bh009Ch009Dh009Eh009Fh00A0h UART0 Transmit/Receive Mode Register U0MR00h00A1h UART0 Bit Rate Register U0BRG XXh00A2h UART0 Transmit Buffer Register U0TB XXh00A3h XXh00A4h UART0 Transmit/Receive Control Register 0U0C000001000b 00A5h UART0 Transmit/Receive Control Register 1U0C100000010b 00A6h UART0 Receive Buffer Register U0RB XXh00A7h XXh00A8h UART1 Transmit/Receive Mode Register U1MR00h00A9h UART1 Bit Rate Register U1BRG XXh00AAh UART1 Transmit Buffer Register U1TB XXh00ABh XXh00ACh UART1 Transmit/Receive Control Register 0U1C000001000b 00ADh UART1 Transmit/Receive Control Register 1U1C100000010b 00AEh UART1 Receive Buffer Register U1RB XXh00AFh XXh00B0h00B1h00B2h00B3h00B4h00B5h00B6h00B7h00B8h SS Control Register H / IIC bus Control Register 1(2)SSCRH / ICCR100h00B9h SS Control Register L / IIC bus Control Register 2(2)SSCRL / ICCR201111101b 00BAh SS Mode Register / IIC bus Mode Register(2)SSMR / ICMR00011000b 00BBh SS Enable Register / IIC bus Interrupt Enable Register(2)SSER / ICIER00h00BCh SS Status Register / IIC bus Status Register(2)SSSR / ICSR00h / 0000X000b 00BDh SS Mode Register 2 / Slave Address Register(2)SSMR2 / SAR00h00BEh SS Transmit Data Register / IIC bus Transmit Data Register(2)SSTDR / ICDRT FFh00BFh SS Receive Data Register / IIC bus Receive Data Register(2)SSRDR / ICDRR FFhX: UndefinedNOTES:1.The blank regions are reserved. Do not access locations in these regions.2.Selected by the IICSEL bit in the PMR register.。

目前市场可破解的部分瑞萨RENESAS R5F21系列解密型号

目前市场可破解的部分瑞萨RENESAS R5F21系列解密型号三菱单片机现属于瑞萨所有,因此很多公司在解密服务供应上会把三菱和瑞萨相混淆,作为全球半导体行业领导品牌之一,瑞萨科技的MCU市场占有率始终处于领跑水平,为了进一步开拓中国这个庞大的新兴市场,瑞萨科技正在以一种更加积极的态度来利用其日益进步的本土科技力量,公司内部采用中国本土化研发人员,并积极同许多高等院校、科研机构、整机厂家以及第三方合作伙伴开展合作。

瑞萨RENESAS芯片解密R5F212系列解密R5F21206JFP R5F21206KFP R5F21207JFP R5F21207KFPR5F21208JFP R5F21208KFP R5F2120AJFP R5F2120AKFPR5F2120CJFP R5F2120CKFP R5F21216JFP R5F21216KFPR5F21216JFP R5F21217KFP R5F21218JFP R5F21218KFPR5F2121AJFP R5F2121AKFP R5F2121CJFP R5F2121CKFPR5F21226JFP R5F21226KFP R5F21227JFP R5F21227KFPR5F212228JFP R5F21228KFP R5F2122AJFP R5F2122AKFPR5F2122CJFP R5F2122CKFP R5F21236JFP R5F21236KFPR5F21237JFP R5F21237KFP R5F21238JFP R5F21238KFPR5F2123AJFP R5F2123AKFP R5F2123CJFP R5F2123CKFPR5F21244SDFP R5F21244SNFP R5F21245SDFP R5F21245SNFPR5F21246SDFP R5F21246SNFP R5F21247SDFP R5F21247SNFPR5F21248SDFP R5F21248SNFP R5F21254SDFP R5F21254SNFPR5F21256SDFP R5F21256SNFP R5F21257SDFP R5F21257SNFPR5F21258SDFP R5F21258SNFP R5F21262DFP R5F21262JFPR5F21262KFP R5F21262NFP R5F21262SDFP R5F21262SJFPR5F21262SKFP R5F21262SNFP R5F21264DFP R5F21264JFPR5F21264KFP R5F21264NFP R5F21264SDFP R5F21264SJFPR5F21264SKFP R5F21264SNFP R5F21265DFP R5F21265JFPR5F21265KFP R5F21265NPF R5F21265SDFP R5F21265SJFPR5F21265SKFP R5F21265SNFP R5F21266DFP R5F21266JFPR5F21266KFP R5F21266NFP R5F21266SDFP R5F21266SJFPR5F21266SKFP R5F21266SNFP R5F21272DFP R5F21272JFPR5F21272KFP R5F21272NFP R5F21272SDFP R5F21272SJFPR5F21272SKFP R5F21272SNFP R5F21274DFP R5F21274JFPR5F21274KFP R5F21274NFP R5F21274SDFP R5F21274SJFPSRF21274SKFP R5F21274SNFP R5F21275DFP R5F21275JFPR5F21275KFP R5F21275NFP R5F21275SDFP R5F21275SJFPR5F21275SKFP R5F21276DFP R5F21276JFP R5F21276KFPR5F21276NFP R5F21276SDFP R5F21276SJFP R5F21276SKFPR5F21276SNFP R5F21282DSP R5F21282JSP R5F21282KSPR5F21282NSP R5F21282SDSP R5F21282SJSP R5F21282SKSPR5F21282SNSP R5F21284DSP R5F21284JSP R5F21284KSPR5F21284NSP R5F21284SDSP R5F21284SJSP R5F21284SKSP R5F21284SNSP R5F21292DSP R5F21292JSP R5F21292KSPR5F21292NSP R5F21292SDSP R5F21292SJSP R5F21292SKSP R5F21292SNSP R5F21294DSP R5F21294JSP R5F21294KSPR5F21294NSP R5F21294SDSP R5F21294SJSP R5F21291SJSPR5F21294SKSP R5F21294SNSP R5F212A7SDFA R5F212A7SDFP R5F212A7SNFP R5F212A7SNFP R5F212A8SDFA R5F212A8SDFP R5F212A8SNFA R5F212A8SNFP R5F212AASDFP R5F212AASDFP R5F212AASNFA R5F212AASNFP R5F212ACSDFA R5F212ACSDFP R5F212ACSNFA R5F212ACSNFP R5F212B7SDFA R5F212B7SDFP R5F212B7SNFP R5F212B7SNFP R5F212B8SDFA R5F212B8SDFP R5F212B8SNFA R5F212B8SNFP R5F212BASDFA R5F212BASDFP R5F212BASNFA R5F212BASNFP R5F212BCSDFA R5F212BCSDFP R5F212BCSNFP R5F212C7SDFP R5F212C7SNFP R5F212C8SDFP R5F212C8SNFP R5F212CASDFP R5F212CASNFP R5F212CCSDFP R5F212CCSNFP R5F212D7SDFP R5F212D7SNFP R5F212D8SDFP R5F212D8SNFP R5F212DASDFP R5F212DASNFP R5F212DCSDFP R5F212DCSNFP R5F212G4SDFP R5F212G4SNFP R5F212G5SDFP R5F212G5SNFP R5F212G6SDFP R5F212G6SNFP R5F212H1SDSP R5F212H1SNSP R5F212H2SDSP R5F212H2SNSP R5F212J0SDSP R5F212J0SNSP R5F212J1SDSP R5F212J1SNSP R5F212K2SDFPR5F212K2SNFP R5F212K4SDFP R5F212K4SNFP R5F212L2SDFP R5F212L2SNFP R5F212L4SDFP R5F212L4SNFP ……。

R5F21228JFP资料