RDS82580XXOO中文资料

RDA5807FP datasheet_v1.2

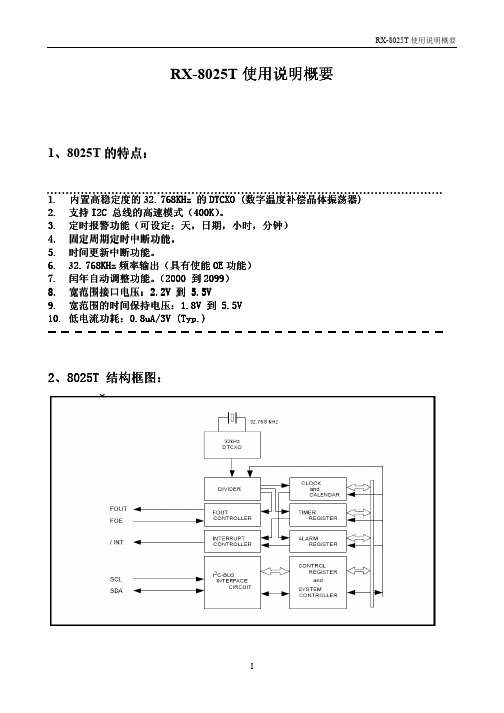

RDA5807FP S INGLE-C HIP B ROADCAST FM R ADIO T UNER Rev.1.2–April.2012 1The RDA5807FPThe RDA5807FP1.1 Features●●●50 -108 MHz●Support flexible channel spacing mode100KHz, 200KHz, 50KHz and 25KHz ●Support RDS/RBDS●Digital low-IF tunerImage-reject down-converterHigh performance A/D converterIF selectivity performed internally●Fully integrated digital frequency synthesizerFully integrated on-chip RF and IF VCOFully integrated on-chip loop filter●Autonomous search tuning●Support 32.768KHz crystal oscillator●Digital auto gain control (AGC) ●Bass boost●Volume control and mute●I2●Line-level analog output voltageS digital output interface●32.768 KHz 12M,24M,13M,26M,19.2M,38.4MHzReference clock●Only support 2-wire bus interface●Directly support 32Ω resistance loading●Integrated LDO regulator2.7 to3.3 V operation voltage●SOP16 package.1.2 Applications●Cellular handsets ●MP3, MP4 players ●Portable radios●PDAs, Notebook2 Table of Contents1General Description (1)1.1 Features (1)1.2Applications (2)2Table of Contents (3)3Functional Description (4)3.1 FM Receiver (4)3.2 Synthesizer (4)3.3 Power Supply (4)3.4 RESET and Control Interface select (4)3.5 Control Interface (5)3.6 I2S Audio Data Interface (5)3.7 GPIO Outputs (5)4Electrical Characteristics (6)5Receiver Characteristics (7)6Serial Interface (8)6.1 I2C Interface Timing (8)7Register Definition (9)8Pins Description (15)9Application Diagram (17)9.1 RDA5807FP Common Application : (17)9.1.1 Bill of Materials: (17)10Physical Dimension (18)11PCB Land Pattern: (19)12Change List (22)Contact Information (23)3 Functional Description3.1Thestrong adjacent channels.The multi-phase mixer array down converts theLNA output differential RF signal to low-IF, it also has image-reject function and harmonic tones rejection.The PGA amplifies the mixer output IF signal and then digitized with ADCs.The DSP core finishes the channel selection, FM demodulation, stereo MPX decoder and output audio signal. The MPX decoder can autonomous switch from stereo to mono to limit the output noise.The DACs convert digital audio signal to analog and change the volume at same time. The DACs has low-pass feature and -3dB frequency is about 3.3 Power SupplyThe RDA5807FP integrated one LDO which supplies power to the chip. The external supply voltage range is 2.7-3.3 V.3.4 RESET and Control Interface selectThe RDA5807FP is RESET itself When VDD is Power up. And also support soft reset by trigger 02H BIT1 from 0 to 1. T h e RDA5807FP only support I2C control interface bus mode.3.5 Control InterfaceThe RDA5807FP only supports I 2The I C control interface.2C interface is compliant to I 2C Bus Specification 2.1. It includes two pins: SCLK andSDIO. A I 2C interface transfer begins with START condition, a command byte and data bytes, each byte has a followed ACK (or NACK) bit, and ends with STOP condition. The command byte includes a 7-bit chip address (0010000b) and a R/W bit. The ACK (or NACK) is always sent out by receiver. When in write transfer, data bytes is written out from MCU, and when in read transfer, data bytes3.6 I out NACK for last data byte, and then RDA5807FP will return the bus to MCU, and MCU will give out STOP condition. 2The RDA5807FP supports I S Audio Data Interface2S (Inter_IC Sound Bus) audio interface. The interface is fullycompliant with I 2S bus specification. When setting I2SEN bit high, RDA5807FP will output SCK, WS,SD signals from GPIO3, GPIO1, GPIO2 as I 2S master and transmitter, the sample rate is 48Kbps ,44.1kbps,32kbps….. RDA5807FP alsosupport as I 2S slaver mode and transmitter, the sample rate is less than 100kbps. SCKWS4 Electrical CharacteristicsTable 4-1 DC Electrical Specification (Recommended Operation Conditions):5 Receiver CharacteristicsTable 5-1Receiver Characteristics(VDD = 3 V, T A = 25 °C, unless otherwise specified)Notes:1. F in =65 to 115MHz; F mod 2. ∆f=22.5KHz; 3. B =1KHz; de-emphasis=75µs; MONO=1; L=R unless noted otherwise;AF = 300Hz to 15KHz, RBW <=10Hz; 4. |f 2-f 1|>1MHz, f 0=2xf 1-f 2, AGC disable, F in 5. P =76 to 108MHz; RF =60dB U V; 6. ∆f=75KHz,fpilot=10% 7. Measured at V EMF = 1 m V, f RF 8. At LOUT and ROUT pins 9. Adjustable = 65 to 108MHz6 Serial Interface6.1 I 2Table 6-1I C Interface Timing2(VDD = 3.0 V, T C Interface Timing CharacteristicsA = 25°C, unless otherwise specified)Figure 6-1. I 2C Interface Write Timing DiagramSCLKSDIOSTARTACKdata high byte ACKr/waddressdata low byteNACKSTOP STARTtFigure 6-2. I 2C Interface Read Timing Diagram7 Register Definition1If 0x07h_bit<9> ( band )=1, 65-76MHz; =0, 50-76MHz2This value is SNR threshold for seeking, and the default value 1000 is about 32dB SNR.3 This function is open when I2S_Enabled=1.40x20H_bit<14:12>, Seek_Mode register. Default value is 000; When = 001, will add the 5807SP seek mode.The information contained herein is the exclusive property of RDA and shall not be distributed, reproduced, or disclosed in whole or in8 Pins Description12345678161514131211109Table 8-2 Internal Pin Configuration9 Application Diagram9.1 RDA5807FP Common Application :10 Physical DimensionFigure 10-1illustrates the package details for the RDA5807FP. The package is lead-free and RoHS-compliant.Figure 10-1. 16 PIN SOP PCB Land Pattern 11 PCB Land Pattern:Table-I Classification Reflow ProfilesTable – II SnPb Eutectic Process – Package Peak Reflow TemperaturesNote 3:Package volume excludes external terminals(balls, bumps, lands, leads) and/or non integral heat sinks.Note 4: The maximum component temperature reached during reflow depends on package the thickness and volume. The use of convection reflow processes reduces the thermal gradients between packages. However, thermal gradients due to differences in thermal mass of SMD package may sill exist.Note 5: Components intended for use in a “lead-free” assembly process shall be evaluated using the “lead free” classification temperatures and profiles defined in Table-I II III whether or not lead free.RoHS CompliantThe product does not contain lead, mercury, cadmium, hexavalent chromium, polybrominated biphenyls (PBB) or polybrominated diphenyl ethers (PBDE), and are therefore considered RoHS compliant.ESD SensitivityIntegrated circuits are ESD sensitive and can be damaged by static electricity. Proper ESD techniques should be used when handling these devices.12 Change ListContact InformationRDA Microelectronics (Shanghai), Inc.Suite 1108 Block A, e-Wing Center, 113 Zhichun Road Haidian District, Beijing Tel: 86-10-62635360Fax: 86-10-82612663Postal Code: 100086Suite 302 Building 2, 690 Bibo Road Pudong District, ShanghaiTel: 86-21-50271108Fax: 86-21-50271099Postal Code: 201203Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner.。

LDEExxxx中文资料

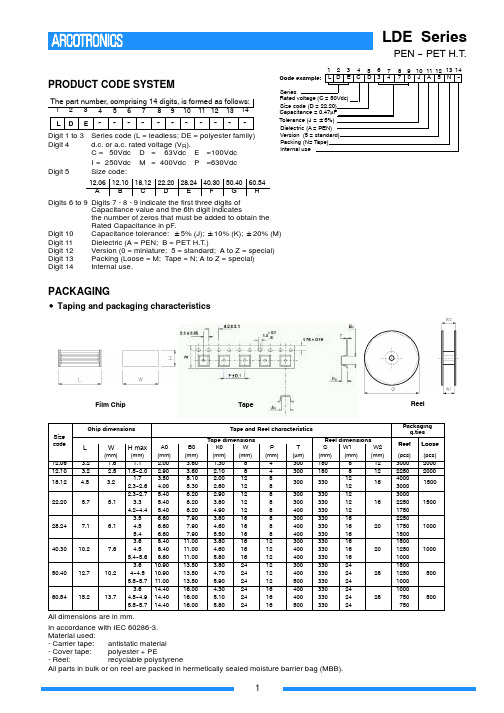

Series Rated voltage (C = 50Vdc) Size code (D = 22.20) Capacitance = 0.47μF Tolerance (J = 5%) Dielectric (A = PEN) Version (5 = standard) Packing (N= Tape) Internal use

28.24

7.1

6.1

1000

40.30

10.2

7.6

1000

50.40

12.7

10.2

500

60.54

15.2

13.7

500

All dimensions are in mm. In accordance with IEC 60286-3. Material used: - Carrier tape: antistatic material - Cover tape: polyester + PE - Reel: recyclable polystyrene All parts in bulk or on reel are packed in hermetically sealed moisture barrier bag (MBB).

L

3.2 3.2 4.5 5.7

W

(mm) 1.6 2.5 3.2 5.1

H max

(mm) 1.1 1.5--2.0 1.7 2.3--2.6 2.3--2.7 3.3 4.2--4.4 3.5 4.5 5.4 3.6 4.5 5.4--5.6 3.6 4--4.5 5.5--5.7 3.6 4.5--4.9 5.5--5.7

25AA1024中文资料

7

pF TA = 25°C, CLK = 1.0 MHz,

VCC = 5.0V (Note)

10

mA VCC = 5.5V; FCLK = 20.0 MHz;

SO = Open

5

mA VCC = 2.5V; FCLK = 10.0 MHz;

SO = Open

7

mA VCC = 5.5V

5

mA VCC = 2.5V

† NOTICE: Stresses above those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operational listings of this specification is not implied. Exposure to maximum rating conditions for an extended period of time may affect device reliability.

25AA256_07中文资料

• Block Write Protection:

- Protect none, 1/4, 1/2 or all of array

• Built-In Write Protection:

- Power-on/off data protection circuitry

- Write enable latch

-0.3

— 0.3 VCC V

-0.3

— 0.2 VCC V

D004 VOL D005 VOL

Low-level output voltage

—

—

0.4

V

—

—

0.2

V

D006 VOH

High-level output

VCC -0.5 —

—

V

voltage

D007 ILI

Input leakage current —

VCC = 5.5V; FCLK = 10.0 MHz; SO = Open VCC = 2.5V; FCLK = 5.0 MHz; SO = Open VCC = 5.5V VCC = 2.5V CS = VCC = 5.5V, Inputs tied to VCC or VSS, 125°C CS = VCC = 5.5V, Inputs tied to VCC or VSS, 85°C

DS21822F-page 2

© 2007 Microchip Technology Inc.

元器件交易网

25AA256/25LC256

TABLE 1-2: AC CHARACTERISTICS

AC CHARACTERISTICS

Industrial (I): TA = -40°C to +85°C Automotive (E): TA = -40°C to +125°C

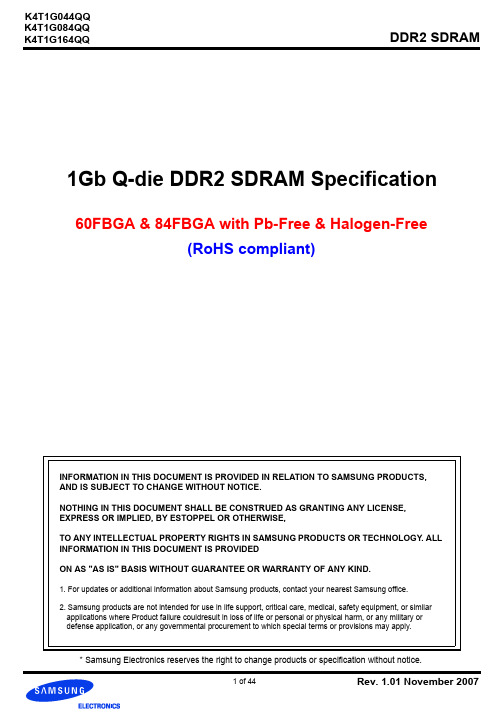

K4T1G164QQ资料

1Gb Q-die DDR2 SDRAM Specification60FBGA & 84FBGA with Pb-Free & Halogen-Free(RoHS compliant)INFORMATION IN THIS DOCUMENT IS PROVIDED IN RELATION TO SAMSUNG PRODUCTS, AND IS SUBJECT TO CHANGE WITHOUT NOTICE.NOTHING IN THIS DOCUMENT SHALL BE CONSTRUED AS GRANTING ANY LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE,TO ANY INTELLECTUAL PROPERTY RIGHTS IN SAMSUNG PRODUCTS OR TECHNOLOGY. ALL INFORMATION IN THIS DOCUMENT IS PROVIDEDON AS "AS IS" BASIS WITHOUT GUARANTEE OR WARRANTY OF ANY KIND.1. For updates or additional information about Samsung products, contact your nearest Samsung office.2. Samsung products are not intended for use in life support, critical care, medical, safety equipment, or similar applications where Product failure couldresult in loss of life or personal or physical harm, or any military or defense application, or any governmental procurement to which special terms or provisions may apply.* Samsung Electronics reserves the right to change products or specification without notice.Table of Contents1.0 Ordering Information (4)2.0 Key Features (4)3.0 Package Pinout/Mechanical Dimension & Addressing (5)3.1 x4/x8 package pinout (Top View) : 60ball FBGA Package (5)3.2 x16 package pinout (Top View) : 84ball FBGA Package (6)3.3 FBGA Package Dimension (x4/x8) (7)3.4 FBGA Package Dimension (x16) (8)4.0 Input/Output Functional Description (9)5.0 DDR2 SDRAM Addressing (10)6.0 Absolute Maximum DC Ratings (11)7.0 AC & DC Operating Conditions (11)7.1 Recommended DC Operating Conditions (SSTL - 1.8) (11)7.2 Operating Temperature Condition (12)7.3 Input DC Logic Level (12)7.4 Input AC Logic Level (12)7.5 AC Input Test Conditions (12)7.6 Differential input AC logic Level (13)7.7 Differential AC output parameters (13)8.0 ODT DC electrical characteristics (13)9.0 OCD default characteristics (14)10.0 IDD Specification Parameters and Test Conditions (15)11.0 DDR2 SDRAM IDD Spec Table (17)12.0 Input/Output capacitance (18)13.0 Electrical Characteristics & AC Timing for DDR2-800/667 (18)13.1 Refresh Parameters by Device Density (18)13.2 Speed Bins and CL, tRCD, tRP, tRC and tRAS for Corresponding Bin (18)13.3 Timing Parameters by Speed Grade (19)14.0 General notes, which may apply for all AC parameters (21)15.0 Specific Notes for dedicated AC parameters (23)Revision HistoryRevision Month Year History1.0September2007 - Initial Release1.01November2007 - Typo CorrectionSpeed DDR2-800 5-5-5DDR2-800 6-6-6DDR2-667 5-5-5Units CAS Latency 565tCK tRCD(min)12.51515ns tRP(min)12.51515ns tRC(min)57.56060nsNote :1. Speed bin is in order of CL-tRCD-tRP.2. RoHS Compliant.3. “H” of Part number(12th digit) stand for RoHS compliant and Halogen-free products.Org.DDR2-800 5-5-5DDR2-800 6-6-6DDR2-667 5-5-5Package 256Mx4K4T1G044QQ-HC(L)E7K4T1G044QQ-HC(L)F7K4T1G044QQ-HC(L)E660 FBGA 128Mx8K4T1G084QQ-HC(L)E7K4T1G084QQ-HC(L)F7K4T1G084QQ-HC(L)E660 FBGA 64Mx16K4T1G164QQ-HC(L)E7K4T1G164QQ-HC(L)F7K4T1G164QQ-HC(L)E684 FBGA•JEDEC standard 1.8V ± 0.1V Power Supply •VDDQ = 1.8V ± 0.1V•333MHz f CK for 667Mb/sec/pin, 400MHz f CK for 800Mb/sec/pin •8 Banks •Posted CAS•Programmable CAS Latency: 3, 4, 5, 6•Programmable Additive Latency: 0, 1, 2, 3, 4, 5•Write Latency(WL) = Read Latency(RL) -1•Burst Length: 4 , 8(Interleave/nibble sequential)•Programmable Sequential / Interleave Burst Mode •Bi-directional Differential Data-Strobe (Single-ended data-strobe is an optional feature)•Off-Chip Driver(OCD) Impedance Adjustment •On Die Termination•Special Function Support- PASR(Partial Array Self Refresh)- 50ohm ODT- High Temperature Self-Refresh rate enable •Average Refresh Period 7.8us at lower than T CASE 85°C, 3.9us at 85°C < T CASE < 95 °C •All of Lead-free products are compliant for RoHSThe 1Gb DDR2 SDRAM is organized as a 32Mbit x 4 I/Os x 8banks, 16Mbit x 8 I/Os x 8banks or 8Mbit x 16 I/Os x 8 banks device. This synchronous device achieves high speed double-data-rate transfer rates of up to 800Mb/sec/pin (DDR2-800) for general applications.The chip is designed to comply with the following key DDR2SDRAM features such as posted CAS with additive latency, write latency = read latency - 1, Off-Chip Driver(OCD) impedance adjustment and On Die Termination.All of the control and address inputs are synchronized with a pair of externally supplied differential clocks. Inputs are latched at the crosspoint of differential clocks (CK rising and CK falling). All I/Os are synchronized with a pair of bidirectional strobes (DQS and DQS) in a source synchronous fashion. The address bus is used to convey row, column, and bank address information in a RAS/CAS multiplexing style. For example, 1Gb(x8) device receive 14/10/3 addressing.The 1Gb DDR2 device operates with a single 1.8V ±0.1V power supply and 1.8V ±0.1V VDDQ.The 1Gb DDR2 device is available in 60ball FBGAs(x4/x8) and in 84ball FBGAs(x16).Note : The functionality described and the timing specifications included in this data sheet are for the DLL Enabled mode of operation.Note : This data sheet is an abstract of full DDR2 specification and does not cover the common features which are described in “DDR2 SDRAM Device Operation & Timing Diagram”.1.0 Ordering Information2.0 Key FeaturesNote:1. Pins B3 and A2 have identical capacitance as pins B7 and A8.2. For a read, when enabled, strobe pair RDQS & RDQS are identical in function and timing to strobe pair DQS & DQS and input masking function is disabled.3. The function of DM or RDQS/RDQS are enabled by EMRS command.4. VDDL and VSSDL are power and ground for the DLL.A B C D E F G H J K LVDD NU/VSSDQ6VSSQ VDDQ VDDQ VDDQ VSSQ VSSQ DQS DQS DQ7DQ0VDDQ DQ2VSSQ DQ5VSSDL VDD CK RAS CK CAS CS A2A6A4A11A8NCA13NCA12A9A7A5A0VDD A10/APVSSVDDQ VSSQ DQ1DQ3DQ4VDDLA1A3BA1VREF VSS CKEWE BA01 2 3 7 8 9VDDVSS ODTBA2Ball Locations (x4/x8): Populated Ball +: Depopulated BallTop View (See the balls through the Package)++++++++++++++++++++++++++++++123456789A B C D E F G H J K L++++++++DM /RDQSRDQS+3.1 x4/x8 package pinout (Top View) : 60ball FBGA Package3.0 Package Pinout/Mechanical Dimension & AddressingNote :1. VDDL and VSSDL are power and ground for the DLL.2. In case of only 8 DQs out of 16 DQs are used, LDQS, LDQSB and DQ0~7 must be used.A B C D E F G H J K L VDD NC VSS DQ14VSSQ UDM VDDQ VDDQ VDDQ VSSQ VSSQ UDQS UDQS DQ15DQ8VDDQ DQ10VSSQ DQ13VSSQ VDDQ RAS CK CAS CS A2A6A4A11A8NCNCNCA12A9A7A5A0VDDA10/APVSSVDDQ VSSQ DQ9DQ11DQ12VDD A1A3BA1NC VSS CKEWE BA0 1 2 3 7 8 9VDDVSSODTBA2Ball Locations (x16): Populated Ball +: Depopulated BallTop View (See the balls through the Package)M N P RDQ6VSSQ LDM VDDQ VDDQ VSSQ LDQS DQ7DQ0VDDQ DQ2VSSQ DQ5VSSDL VDD CK VDDQ VSSQ DQ1DQ3DQ4VDDLVREF VSS LDQS 123456789++++++++++++++++++++++++++++++++++++++++++++++++++A B C D E F G H J K L M N P R+3.2 x16 package pinout (Top View) : 84ball FBGA Package3.3 FBGA Package Dimension (x4/x8)A B CD E F H J K LG3.4 FBGA Package Dimension (x16)A B C D E FH J K L M N P RGSymbol Type FunctionCK, CK Input Clock:CK and CK are differential clock inputs. All address and control input signals are sampled on the crossing of the positive edge of CK and negative edge of CK. Output (read) data is referenced to the crossings of CK and CK (both directions of crossing).CKE Input Clock Enable: CKE HIGH activates, and CKE Low deactivates, internal clock signals and device input buffers and out-put drivers. Taking CKE Low provides Precharge Power-Down and Self Refresh operation (all banks idle), or Active Power-Down (row Active in any bank). CKE is synchronous for power down entry and exit, and for self refresh entry. CKE is asynchronous for self refresh exit. After V REF has become stable during the power on and initialization swquence, it must be maintained for proper operation of the CKE receiver. For proper self-refresh entry and exit, V REF must be maintained to this input. CKE must be maintained high throughout read and write accesses. Input buffers, excluding CK, CK, ODT and CKE are disabled during power-down. Input buffers, excluding CKE, are disabled during self refresh.CS Input Chip Select: All commands are masked when CS is registered HIGH. CS provides for external Rank selection on sys-tems with multiple Ranks. CS is considered part of the command code.ODT Input On Die Termination: ODT (registered HIGH) enables termination resistance internal to the DDR2 SDRAM. When enabled, ODT is only applied to each DQ, DQS, DQS, RDQS, RDQS, and DM signal for x4/x8 configurations. For x16 configuration ODT is applied to each DQ, UDQS/UDQS, LDQS/LDQS, UDM, and LDM signal. The ODT pin will be ignored if the Extended Mode Register (EMRS(1)) is programmed to disable ODT.RAS, CAS, WE Input Command Inputs: RAS, CAS and WE (along with CS) define the command being entered.DM Input Input Data Mask: DM is an input mask signal for write data. Input data is masked when DM is sampled HIGH coinci-dent with that input data during a Write access. DM is sampled on both edges of DQS. Although DM pins are input only, the DM loading matches the DQ and DQS loading. For x8 device, the function of DM or RDQS/RDQS is enabled by EMRS command.BA0 - BA2Input Bank Address Inputs: BA0, BA1 and BA2 define to which bank an Active, Read, Write or Precharge command is being applied. Bank address also determines if the mode register or extended mode register is to be accessed during a MRS or EMRS cycle.A0 - A13Input Address Inputs: Provided the row address for Active commands and the column address and Auto Precharge bit for Read/Write commands to select one location out of the memory array in the respective bank. A10 is sampled during a Precharge command to determine whether the Precharge applies to one bank (A10 LOW) or all banks (A10 HIGH). If only one bank is to be precharged, the bank is selected by BA0, BA1. The address inputs also provide the op-code dur-ing Mode Register Set commands.DQ Input/Out-putData Input/ Output: Bi-directional data bus.DQS, (DQS)(LDQS), (LDQS) (UDQS), (UDQS) (RDQS), (RDQS)Input/Out-putData Strobe: output with read data, input with write data. Edge-aligned with read data, centered in write data. For the x16, LDQS corresponds to the data on DQ0-DQ7; UDQS corresponds to the data on DQ8-DQ15. For the x8, an RDQS option using DM pin can be enabled via the EMRS(1) to simplify read timing. The data strobes DQS, LDQS, UDQS, and RDQS may be used in single ended mode or paired with optional complementary signals DQS, LDQS, UDQS, and RDQS to provide differential pair signaling to the system during both reads and writes. An EMRS(1) control bit enables or disables all complementary data strobe signals.In this data sheet, "differential DQS signals" refers to any of the following with A10 = 0 of EMRS(1)x4 DQS/DQSx8 DQS/DQS if EMRS(1)[A11] = 0x8 DQS/DQS, RDQS/RDQS, if EMRS(1)[A11] = 1x16 LDQS/LDQS and UDQS/UDQS"single-ended DQS signals" refers to any of the following with A10 = 1 of EMRS(1)x4 DQSx8 DQS if EMRS(1)[A11] = 0x8 DQS, RDQS, if EMRS(1)[A11] = 1x16 LDQS and UDQSNC No Connect: No internal electrical connection is present.V DD/V DDQ Supply Power Supply: 1.8V +/- 0.1V, DQ Power Supply: 1.8V +/- 0.1V V SS/V SSQ Supply Ground, DQ GroundV DDL Supply DLL Power Supply: 1.8V +/- 0.1VV SSDL Supply DLL GroundV REF Supply Reference voltage4.0 Input/Output Functional Description5.0 DDR2 SDRAM Addressing1Gb AddressingConfiguration256Mb x4128Mb x 864Mb x16 # of Bank888Bank Address BA0 ~ BA2BA0 ~ BA2BA0 ~ BA2Auto precharge A10/AP A10/AP A10/APRow Address A0 ~ A13A0 ~ A13A0 ~ A12Column Address A0 ~ A9,A11A0 ~ A9A0 ~ A9 * Reference information: The following tables are address mapping information for other densities.256MbConfiguration64Mb x432Mb x 816Mb x16 # of Bank444Bank Address BA0,BA1BA0,BA1BA0,BA1Auto precharge A10/AP A10/AP A10/APRow Address A0 ~ A12A0 ~ A12A0 ~ A12Column Address A0 ~ A9,A11A0 ~ A9A0 ~ A8512MbConfiguration128Mb x464Mb x 832Mb x16 # of Bank444Bank Address BA0,BA1BA0,BA1BA0,BA1Auto precharge A10/AP A10/AP A10/APRow Address A0 ~ A13A0 ~ A13A0 ~ A12Column Address A0 ~ A9,A11A0 ~ A9A0 ~ A92GbConfiguration512Mb x4256Mb x 8128Mb x16 # of Bank888Bank Address BA0 ~ BA2BA0 ~ BA2BA0 ~ BA2Auto precharge A10/AP A10/AP A10/APRow Address A0 ~ A14A0 ~ A14A0 ~ A13Column Address A0 ~ A9,A11A0 ~ A9A0 ~ A9 4GbConfiguration 1 Gb x4512Mb x 8256Mb x16 # of Bank888Bank Address BA0 ~ BA2BA0 ~ BA2BA0 ~ BA2Auto precharge A10/AP A10/AP A10/APRow Address A0 - A15A0 - A15A0 - A14 Column Address/page size A0 - A9,A11 A0 - A9 A0 - A9Note :1. Stresses greater than those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.2. Storage Temperature is the case surface temperature on the center/top side of the DRAM.Symbol ParameterRating Units Notes V DD Voltage on V DD pin relative to V SS - 1.0 V ~ 2.3 V V 1V DDQ Voltage on V DDQ pin relative to V SS - 0.5 V ~ 2.3 V V 1V DDL Voltage on V DDL pin relative to V SS - 0.5 V ~ 2.3 V V 1V IN, V OUT Voltage on any pin relative to V SS - 0.5 V ~ 2.3 V V1T STGStorage Temperature-55 to +100°C 1, 2Note : There is no specific device V DD supply voltage requirement for SSTL-1.8 compliance. However under all conditions V DDQ must be less than or equalto V DD .1. The value of V REF may be selected by the user to provide optimum noise margin in the system. Typically the value of V REF is expected to be about 0.5 x V DDQ of the transmitting device and V REF is expected to track variations in V DDQ .2. Peak to peak AC noise on V REF may not exceed +/-2% V REF (DC).3. V TT of transmitting device must track V REF of receiving device.4. AC parameters are measured with V DD , V DDQ and V DDL tied together.Symbol ParameterRatingUnits NotesMin.Typ. Max.V DD Supply Voltage 1.7 1.8 1.9V V DDL Supply Voltage for DLL 1.7 1.8 1.9V 4V DDQ Supply Voltage for Output 1.7 1.8 1.9V 4V REF Input Reference Voltage 0.49*V DDQ 0.50*V DDQ0.51*V DDQ mV 1,2V TTTermination VoltageV REF -0.04V REFV REF +0.04V37.0 AC & DC Operating Conditions6.0 Absolute Maximum DC Ratings7.1 Recommended DC Operating Conditions (SSTL - 1.8)7.2 Operating Temperature Condition1.Operating Temperature is the case surface temperature on the center/top side of the DRAM.2.At 85 - 95 °C operation temperature range, doubling refresh commands in frequency to a 32ms period ( tREFI=3.9 us ) is required, and to enter to self refresh mode at this temperature range, an EMRS command is required to change internal refresh rate.7.3 Input DC Logic Level7.4 Input AC Logic Level7.5 AC Input Test ConditionsNote :1. Input waveform timing is referenced to the input signal crossing through the V IH/IL (AC) level applied to the device under test.2. The input signal minimum slew rate is to be maintained over the range from V REF to V IH (AC) min for rising edges and the range from V REF to V IL (AC)max for falling edges as shown in the below figure.3. AC timings are referenced with input waveforms switching from V IL (AC) to V IH (AC) on the positive transitions and V IH (AC) to V IL (AC) on the negative transitions.Symbol Parameter Rating UnitsNotesTOPEROperating Temperature0 to 95°C 1, 2Symbol Parameter Min.Max.Units NotesV IH (DC)DC input logic high V REF + 0.125V DDQ + 0.3V V IL (DC)DC input logic low- 0.3V REF - 0.125VSymbol ParameterDDR2-667, DDR2-800Units Min.Max.V IH (AC)AC input logic high V REF + 0.200V V IL (AC)AC input logic lowV REF - 0.200VSymbol Condition Value Units Notes V REF Input reference voltage0.5 * V DDQV 1V SWING(MAX)Input signal maximum peak to peak swing1.0V 1SLEWInput signal minimum slew rate1.0V/ns2, 3V DDQ V IH (AC) minV IH (DC) min V REFV IL (DC) max V IL (AC) maxV SS< AC Input Test Signal Waveform >V SWING(MAX)delta TRdelta TFV REF - V IL (AC) maxdelta TFFalling Slew =Rising Slew =V IH (AC) min - V REFdelta TRV DDQCrossing pointV SSQV TR V CPV IDV IX or V OX< Differential signal levels >7.6 Differential input AC logic LevelNote :1. V ID (AC) specifies the input differential voltage |V TR -V CP | required for switching, where V TR is the true input signal (such as CK, DQS, LDQS or UDQS) and V CP is the complementary input signal (such as CK, DQS, LDQS or UDQS). The minimum value is equal to V IH (AC) - V IL (AC).2. The typical value of V IX (AC) is expected to be about 0.5 * VDDQ of the transmitting device and V IX (AC) is expected to track variations in VDDQ . V IX (AC) indicates the voltage at which differential input signals must cross.7.7 Differential AC output parametersNote :1. The typical value of V OX (AC) is expected to be about 0.5 * VDDQ of the transmitting device and V OX (AC) is expected to track variations in VDDQ . V OX (AC) indicates the voltage at which differential output signals must cross.Symbol ParameterMin.Max.Units Notes V ID(AC)AC differential input voltage 0.5V DDQ + 0.6V 1V IX(AC)AC differential cross point voltage0.5 * VDDQ - 0.1750.5 * VDDQ + 0.175V2Symbol ParameterMin.Max.Units Note V OX (AC)AC differential cross point voltage0.5 * VDDQ - 0.1250.5 * VDDQ + 0.125V1Note : Test condition for Rtt measurementsMeasurement Definition for Rtt(eff):Apply V IH (ac) and V IL (ac) to test pin separately, then measure current I(V IH (ac)) and I( V IL (ac)) respectively. V IH (ac), V IL (ac), and VDDQ values defined in SSTL_18Measurement Definition for VM: Measure voltage (V M ) at test pin (midpoint) with no load.PARAMETER/CONDITIONSYMBOL MIN NOM MAX UNITS NOTES Rtt effective impedance value for EMRS(A6,A2)=0,1; 75 ohm Rtt1(eff)607590ohm 1Rtt effective impedance value for EMRS(A6,A2)=1,0; 150 ohm Rtt2(eff)120150180ohm 1Rtt effective impedance value for EMRS(A6,A2)=1,1; 50 ohm Rtt3(eff)405060ohm 1Deviation of VM with respect to VDDQ/2delta VM- 6+ 6%1Rtt(eff) =V IH (ac) - V IL (ac)I(V IH (ac)) - I(V IL (ac))delta VM =2 x Vm VDDQx 100%- 18.0 ODT DC electrical characteristicsNote :1. Absolute Specifications (0°C ≤ T CASE ≤ +95°C; VDD = +1.8V ±0.1V, VDDQ = +1.8V ±0.1V)2. Impedance measurement condition for output source dc current: VDDQ = 1.7V; VOUT = 1420mV; (VOUT-VDDQ)/Ioh must be less than 23.4 ohms for values of VOUT between VDDQ and VDDQ- 280mV. Impedance measurement condition for output sink dc current: VDDQ = 1.7V; VOUT = 280mV; VOUT/Iol must be less than 23.4 ohms for values of VOUT between 0V and 280mV.3. Mismatch is absolute value between pull-up and pull-dn, both are measured at same temperature and voltage.4. Slew rate measured from V IL (AC) to V IH (AC).5. The absolute value of the slew rate as measured from DC to DC is equal to or greater than the slew rate as measured from AC to AC. This is guaranteed by design and characterization.6. This represents the step size when the OCD is near 18 ohms at nominal conditions across all process and represents only the DRAM uncertainty. Output slew rate load :7. DRAM output slew rate specification applies to 667Mb/sec/pin and 800Mb/sec/pin speed bins.8. Timing skew due to DRAM output slew rate mis-match between DQS / DQS and associated DQs is included in tDQSQ and tQHS specification.DescriptionParameterMinNomMaxUnit Notes Output impedanceNormal 18ohmsSee full strength default driver characteristics ohms 1,2Output impedance step size for OCD calibration 0 1.5ohms 6Pull-up and pull-down mismatch 04ohms 1,2,3Output slew rateSout 1.55V/ns1,4,5,6,7,825 ohmsV TTOutput (V OUT)Reference Point9.0 OCD default characteristics(IDD values are for full operating range of Voltage and Temperature, Notes 1 - 5)Symbol Proposed Conditions Units NotesIDD0Operating one bank active-precharge current;t CK = t CK(IDD), t RC = t RC(IDD), t RAS = t RASmin(IDD); CKE is HIGH, CS\ is HIGH between valid commands;Address bus inputs are SWITCHING; Data bus inputs are SWITCHINGmAIDD1Operating one bank active-read-precharge current;IOUT = 0mA; BL = 4, CL = CL(IDD), AL = 0; t CK = t CK(IDD), t RC = t RC (IDD), t RAS = t RASmin(IDD), t RCD =t RCD(IDD); CKE is HIGH, CS\ is HIGH between valid commands; Address businputs are SWITCHING; Data pat-tern is same as IDD4WmAIDD2P Precharge power-down current;All banks idle; t CK = t CK(IDD); CKE is LOW; Other control and address bus inputs are STABLE; Data bus inputs are FLOATINGmAIDD2Q Precharge quiet standby current;All banks idle; t CK = t CK(IDD); CKE is HIGH, CS\ is HIGH; Other control and address bus inputsare STABLE; Databus inputs are FLOATINGmAIDD2N Precharge standby current;All banks idle; t CK = t CK(IDD); CKE is HIGH, CS\ is HIGH; Other control and address bus inputs are SWITCHING;Data bus inputs are SWITCHINGmAIDD3P Active power-down current;All banks open; t CK = t CK(IDD); CKE is LOW; Other control and address businputs are STABLE; Data bus inputs are FLOATINGFast PDN Exit MRS(12) = 0mASlow PDN Exit MRS(12) = 1mAIDD3N Active standby current;All banks open; t CK = t CK(IDD), t RAS = t RASmax(IDD), t RP = t RP(IDD); CKE is HIGH, CS\ is HIGH between valid commands; Other control and address bus inputs are SWITCHING; Data bus inputs are SWITCHINGmAIDD4W Operating burst write current;All banks open, Continuous burst writes; BL = 4, CL = CL(IDD), AL = 0; t CK = t CK(IDD), t RAS = t RASmax(IDD), t RP= t RP(IDD); CKE is HIGH, CS\ is HIGH between valid commands; Address bus inputs are SWITCHING; Data businputs are SWITCHINGmAIDD4R Operating burst read current;All banks open, Continuous burst reads, IOUT = 0mA; BL = 4, CL = CL(IDD), AL = 0; t CK = t CK(IDD), t RAS = t RAS-max(IDD), t RP = t RP(IDD); CKE is HIGH, CS\ is HIGH between valid commands; Address bus inputs are SWITCH-ING; Data pattern is same as IDD4WmAIDD5B Burst auto refresh current;t CK = t CK(IDD); Refresh command at every t RFC(IDD) interval; CKE is HIGH, CS\ is HIGH between valid com-mands; Other control and address bus inputs are SWITCHING; Data bus inputs are SWITCHINGmAIDD6Self refresh current;CK and CK\ at 0V; CKE ≤ 0.2V; Other control and address bus inputs areFLOATING; Data bus inputs are FLOATINGNormal mALow Power mAIDD7Operating bank interleave read current;All bank interleaving reads, IOUT = 0mA; BL = 4, CL = CL(IDD), AL = t RCD(IDD)-1*t CK(IDD); t CK = t CK(IDD), t RC= t RC(IDD), t RRD = t RRD(IDD), t FAW = t FAW(IDD), t RCD = 1*t CK(IDD); CKE is HIGH, CS\ is HIGH between valid commands; Address bus inputs are STABLE during DESELECTs; Data pattern is same as IDD4R; Refer to the fol-lowing page for detailed timing conditionsmA10.0 IDD Specification Parameters and Test ConditionsNote :1. IDD specifications are tested after the device is properly initialized2. Input slew rate is specified by AC Parametric Test Condition3. IDD parameters are specified with ODT disabled.4. Data bus consists of DQ, DM, DQS, DQS\, RDQS, RDQS\, LDQS, LDQS\, UDQS, and UDQS\. IDD values must be met with all combinations of EMRS bits 10 and 11.5. Definitions for IDD LOW is defined as Vin ≤ VILAC(max) HIGH is defined as Vin ≥ VIHAC(min)STABLE is defined as inputs stable at a HIGH or LOW level FLOATING is defined as inputs at VREF = VDDQ/2 SWITCHING is defined as:inputs changing between HIGH and LOW every other clock cycle (once per two clocks) for address and controlsignals, and inputs changing between HIGH and LOW every other data transfer (once per clock) for DQ signals not including masks or strobes.For purposes of IDD testing, the following parameters are utilizedDetailed IDD7The detailed timings are shown below for IDD7.Legend: A = Active; RA = Read with Autoprecharge; D = DeselectIDD7: Operating Current: All Bank Interleave Read operationAll banks are being interleaved at minimum t RC(IDD) without violating t RRD(IDD) and t FAW(IDD) using a burst length of 4. Control and address bus inputs are STABLE during DESELECTs. IOUT = 0mATiming Patterns for 8bank devices x4/ x8-DDR2-667 5/5/5 : A0 RA0 D A1 RA1 D A2 RA2 D A3 RA3 D D A4 RA4 D A5 RA5 D A6 RA6 D A7 RA7 D D-DDR2-800 6/6/6 : A0 RA0 D A1 RA1 D A2 RA2 D A3 RA3 D D D A4 RA4 D A5 RA5 D A6 RA6 D A7 RA7 D D D -DDR2-800 5/5/5 : A0 RA0 D A1 RA1 D A2 RA2 D A3 RA3 D D D A4 RA4 D A5 RA5 D A6 RA6 D A7 RA7 D D DTiming Patterns for 8bank devices x16-DDR2-667 5/5/5 : A0 RA0 D D A1 RA1 D D A2 RA2 D D A3 RA3 D D D A4 RA4 D D A5 RA5 D D A6 RA6 D D A7 RA7 D D D-DDR2-800 6/6/6 : A0 RA0 D D A1 RA1 D D A2 RA2 D D A3 RA3 D D D D A4 RA4 D D A5 RA5 D D A6 RA6 D D A7 RA7 D D D D -DDR2-800 5/5/5 : A0 RA0 D D A1 RA1 D D A2 RA2 D D A3 RA3 D D D D A4 RA4 D D A5 RA5 D D A6 RA6 D D A7 RA7 D D D DDDR2-800DDR2-800DDR2-667Units Parameter 5-5-56-6-65-5-5CL(IDD)565tCK t RCD(IDD)12.51515ns t RC(IDD)57.56060ns t RRD(IDD)-x4/x87.57.57.5ns t RRD(IDD)-x16101010ns t CK(IDD) 2.5 2.53ns t RASmin(IDD)454545ns t RP(IDD)12.51515ns t RFC(IDD)127.5127.5127.5ns(T A=0o C, VDD= 1.9V)Symbol256Mx4 (K4T1G044QQ)Unit Notes 800@CL=5800@CL=6667@CL=5CE7LE7CF7LF7CE6LE6IDD0757570mAIDD1858580mAIDD2P158158158mAIDD2Q303030mAIDD2N353535mAIDD3P-F353535mAIDD3P-S181818mAIDD3N555550mAIDD4W110110100mAIDD4R130130115mAIDD5140140135mAIDD6156156156mAIDD7245245225mA(T A=0o C, VDD= 1.9V)Symbol128Mx8 (K4T1G084QQ)Unit Notes 800@CL=5800@CL=6667@CL=5CE7LE7CF7LF7CE6LE6IDD0757570mAIDD1858580mAIDD2P158158158mAIDD2Q303030mAIDD2N353535mAIDD3P-F353535mAIDD3P-S181818mAIDD3N555550mAIDD4W115115105mAIDD4R135135120mAIDD5145145140mAIDD6156156156mAIDD7250250230mA11.0 DDR2 SDRAM IDD Spec Table(T A=0o C, VDD= 1.9V)Symbol64Mx16 (K4T1G164QQ)Unit Notes 800@CL=5800@CL=6667@CL=5CE7LE7CF7LF7CE6LE6IDD0909085mA IDD110010095mA IDD2P158158158mA IDD2Q303030mA IDD2N353535mA IDD3P-F353535mA IDD3P-S181818mA IDD3N555550mA IDD4W130130115mA IDD4R175175155mA IDD5145145140mA IDD6156156156mA IDD7265265245mASpeedDDR2-800(E7)DDR2-800(F7)DDR2-667(E6)UnitsBin (CL - tRCD - tRP)5-5-56-6-65 - 5 - 5Parameter min max min max min max tCK, CL=358--58ns tCK, CL=4 3.758 3.758 3.758ns tCK, CL=5 2.583838ns tCK, CL=6-- 2.58--ns tRCD 12.5-15-15-ns tRP 12.5-15-15-ns tRC 57.5-60-60-ns tRAS457000045700004570000ns ParameterSymbol DDR2-667DDR2-800Units Min Max Min Max Input capacitance, CK and CK CCK 1.0 2.0 1.0 2.0pF Input capacitance delta, CK and CK CDCK x 0.25x 0.25pF Input capacitance, all other input-only pins CI 1.0 2.0 1.0 1.75pF Input capacitance delta, all other input-only pins CDI x 0.25x 0.25pF Input/output capacitance, DQ, DM, DQS, DQS CIO 2.5 3.5 2.5 3.5pF Input/output capacitance delta, DQ, DM, DQS, DQSCDIOx0.5x0.5pF13.0 Electrical Characteristics & AC Timing for DDR2-800/667(0 °C < T OPER < 95 °C; V DDQ = 1.8V + 0.1V; V DD = 1.8V + 0.1V)13.1 Refresh Parameters by Device DensityParameterSymbol256Mb 512Mb 1Gb 2Gb 4Gb Units Refresh to active/Refresh command time tRFC 75105127.5195327.5ns Average periodic refresh intervaltREFI0 °C ≤ T CASE ≤ 85°C 7.87.87.87.87.8µs 85 °C < T CASE ≤ 95°C3.93.93.93.93.9µs13.2 Speed Bins and CL, tRCD, tRP, tRC and tRAS for Corresponding Bin 12.0 Input/Output capacitance。

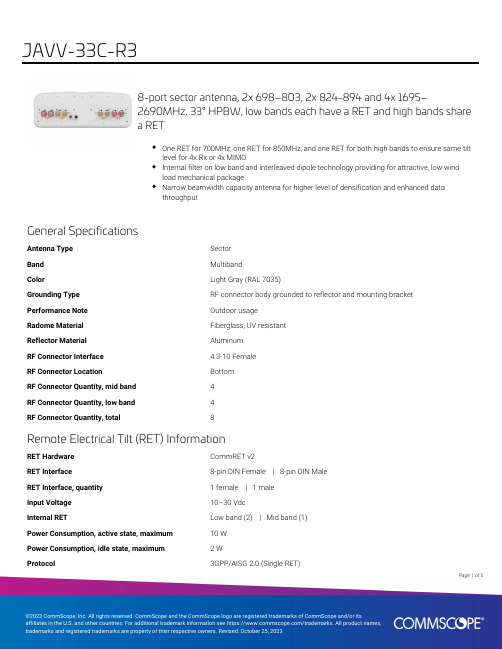

CommScope 8-口扇区押发器说明书

8-port sector antenna, 2x 698–803, 2x 824-894 and 4x 1695–2690MHz, 33° HPBW, low bands each have a RET and high bands sharea RETOne RET for 700MHz, one RET for 850MHz, and one RET for both high bands to ensure same tiltlevel for 4x Rx or 4x MIMOInternal filter on low band and interleaved dipole technology providing for attractive, low windload mechanical packageNarrow beamwidth capacity antenna for higher level of densification and enhanced datathroughputGeneral SpecificationsAntenna Type SectorBand MultibandColor Light Gray (RAL 7035)Grounding Type RF connector body grounded to reflector and mounting bracketPerformance Note Outdoor usageRadome Material Fiberglass, UV resistantReflector Material AluminumRF Connector Interface 4.3-10 FemaleRF Connector Location BottomRF Connector Quantity, mid band4RF Connector Quantity, low band4RF Connector Quantity, total8Remote Electrical Tilt (RET) InformationRET Hardware CommRET v2RET Interface8-pin DIN Female | 8-pin DIN MaleRET Interface, quantity 1 female | 1 maleInput Voltage10–30 VdcInternal RET Low band (2) | Mid band (1)Power Consumption, active state, maximum10 WPower Consumption, idle state, maximum 2 WProtocol3GPP/AISG 2.0 (Single RET)15Page ofPage of 25DimensionsWidth 640 mm | 25.197 in Depth 235 mm | 9.252 in Length2438 mm | 95.984 in Net Weight, antenna only64 kg | 141.096 lbArray LayoutPort ConfigurationElectrical SpecificationsImpedance50 ohmOperating Frequency Band1695 – 2690 MHz | 698 – 803 MHz | 824 – 894 MHzPolarization±45°Total Input Power, maximum800 W @ 50 °CElectrical SpecificationsFrequency Band, MHz698–803824–8941695–18801850–19901920–22002300–2690Gain, dBi18.3192020.320.821.7353134343327Beamwidth, Horizontal,degreesBeamwidth, Vertical, degrees9.98.7 5.8 5.4 5.1 4.4Beam Tilt, degrees0–100–102–122–122–122–12Horizontal Sidelobe, dB212019171716USLS (First Lobe), dB171818171820323634353736Front-to-Back Ratio at 180°,dBIsolation, Cross Polarization,252525252525dBIsolation, Inter-band, dB30303030303035Page ofVSWR | Return loss, dB 1.5 | 14.0 1.5 | 14.0 1.5 | 14.0 1.5 | 14.0 1.5 | 14.0 1.5 | 14.0PIM, 3rd Order, 2 x 20 W, dBc-153-153-153-153-153-153150150250250250200Input Power per Port at 50°C,maximum, wattsElectrical Specifications, BASTAFrequency Band, MHz698–803824–8941695–18801850–19901920–22002300–269018.118.819.620.120.421.3Gain by all Beam Tilts,average, dBi±0.4±0.4±0.7±0.3±0.5±0.5Gain by all Beam TiltsTolerance, dB±3.3±0.7±3.3±1±1.6±2.3Beamwidth, HorizontalTolerance, degrees±0.5±0.4±0.3±0.2±0.3±0.3Beamwidth, VerticalTolerance, degrees171716171717USLS, beampeak to 20° abovebeampeak, dB282829303030Front-to-Back Total Power at180° ± 30°, dBCPR at Boresight, dB181718212021CPR at 10 dB Horizontal81613141312Beamwidth, dBMechanical SpecificationsWind Loading @ Velocity, frontal954.0 N @ 150 km/h (214.5 lbf @ 150 km/h)Wind Loading @ Velocity, lateral355.0 N @ 150 km/h (79.8 lbf @ 150 km/h)Wind Loading @ Velocity, maximum1,434.0 N @ 150 km/h (322.4 lbf @ 150 km/h)Wind Loading @ Velocity, rear1,086.0 N @ 150 km/h (244.1 lbf @ 150 km/h)Wind Speed, maximum241 km/h (150 mph)Packaging and WeightsWidth, packed752 mm | 29.606 inDepth, packed382 mm | 15.039 inLength, packed2590 mm | 101.969 inWeight, gross88 kg | 194.007 lbRegulatory Compliance/CertificationsAgency Classification45Page ofCHINA-ROHS Above maximum concentration valueISO 9001:2015Designed, manufactured and/or distributed under this quality management system ROHS Compliant/ExemptedUK-ROHSCompliant/ExemptedIncluded ProductsBSAMNT-4–Wide Profile Antenna Downtilt Mounting Kit for 2.4 - 4.5 in (60 - 115 mm) OD round members.Kit contains one scissor top bracket set and one bottom bracket set.BSAMNT-M4–Middle Downtilt Mounting Kit for Long Antennas for 2.4 - 4.5 in (60 - 115 mm) OD roundmembers. Kit contains one scissor bracket set.* FootnotesPerformance Note Severe environmental conditions may degrade optimum performancePage of55。

Transcend 8X Slim Portable CD DVD Writer TS8XDVDS

User’s Manual Slim Portable CD/DVD WriterTS8XDVDS(Version 1.1)Table of ContentsIntroduction︱ (1)Features︱ (2)System Requirements︱ (2)General Use (2)Writing Data (3)Power (3)Reminders (4)Product Overview︱ (5)Basic Operation︱ (6)Plugging in the CD/DVD Writer (6)Inserting a Disc (6)Ejecting a Disc (9)Disconnecting from a Computer︱ (11)Software Download︱ (11)Troubleshooting︱ (13)System Requirements︱ (14)Ordering Information︱ (14)Recycling & Environmental Considerations︱ (15)Two-year Limited Warranty︱ (16)Introduction︱Congratulations on purchasing Transcend’s 8X Slim Portable CD/DVD Writer.This slim, elegant high-speed portable CD/DVD writer is perfect for playing, backing up your vital data and discs. With its slim easy-to-carry size and advanced high-speed media writing capabilities, the CD/DVD Writer is ideal for playing movies, installing software, or backing up your files, folders, documents, photos, music and videos when using a compact notebook computer or netbook. In addition, the CD/DVD Writer comes with a full-version of CyberLink’s extremely useful Power2Go* software that lets you easily create your own CDs and DVDs. This User’s Manual is designed to help you get the most from your new device. Please read it in detail before using the CD/DVD Writer.*Power2Go is a registered trademark of CyberLink®. This software can be only used in Windows®XP, Windows Vista® , Windows®7 and Windows®8.Features︱USB 2.0 interface for high-speed data transfer8x DVD±R read/write, 24x CD-R/RW read/writeCompatible with CD-R/RW, DVD±R, DVD±RW, DVD±R DL, DVD-RAM mediaReads and writes Dual Layer discsUSB powered –No external power adapter neededElegant slim modern design with rounded edgesCompact and easy-to-carryEasy Plug and Play installationAnti-slip rubber feetSystem Requirements︱Desktop or notebook computer with two working USB ports.One of following Operating Systems:•Windows®XP•Windows Vista®•Windows® 7•Windows® 8•Mac OS® X 10.4 or laterSafety Precautions︱These usage and safety guidelines are IMPORTANT! Please follow them carefully.Please ensure that you connect the USB cable to the CD/DVD Writer and your computer correctly (small end CD/DVD Writer, large end PC)General Use•During operation, avoid exposing your CD/DVD writer to extreme temperatures above 40℃or below 5℃.•Never drop your CD/DVD Writer.•Only use the CD/DVD Writer face-up, on a stable flat surface•Do not allow your CD/DVD Writer to come in contact with water or any other liquids.•Do not use a damp/wet cloth to wipe or clean the exterior case.•Never look directly into the laser lens, as it can be harmful to your eyes.•Do not attempt to open the outer case (doing so will void your product warranty).•Do not store your CD/DVD Writer in any of the following environments:o Direct sunlighto Next to an air conditioner, electric heater or other heat sourceso In a closed car that is in direct sunlighto In an area with strong magnetic fields or excessive vibration• Never touch the laser lens.Writing Data• Do not touch, pick up, or move the CD/DVD Writer during the write process. This candamage the device and will cause errors on the disc being written• Transcend does not take any responsibility for data loss or damage resulting fromuse of this product . If using this product to backup data, we strongly advise using high-quality recordable media, and that you fully test and verify the contents of all written discs. It is also a good idea to regularly backup important data to a different computer or other storage medium.• To ensure High-Speed USB 2.0 data transfer rates when using your CD/DVD Writer witha computer, please check that the computer has the relevant USB drivers. If you are unsure about how to check this, please consult the computer or motherboard User’sManual for USB driver information.Power• The CD/DVD Writer is powered directly from your computer’s USB port. However, theUSB ports of certain computers may not supply enough power to use the CD/DVD Writer when using a single USB port. Please make sure to connect both large connector ends of the provided USB Cable to the USB ports on your computer. This will ensure the CD/DVD Writer receives adequate power for stable operation.• Only use the USB cable that came with the CD/DVD Writer to connect it to a computer,and always ensure that the cable is in good condition. NEVER use a cable that is frayedThe second USB connector provides additional power forthe CD/DVD Writer. Please make sure to connect bothUSB connectors to your computer’s USB ports.or damaged.•Ensure nothing is resting on the USB cable and that the cable is not located where it can be tripped over or stepped on.•If you have connected all ends of the USB cable and still have power-related problems while reading / writing data, we recommend that you purchase a Transcend USB Power Adapter (TS-PA2A) to provide the power necessary to operate the CD/DVD Writer.Reminders•Always follow the procedures in the “Disconnecting from a Computer” section to remove the CD/DVD Writer from your computer.Product Overview︱A Disc TrayB Read/Write Activity IndicatorC Eject ButtonD Emergency EjectE Anti-slip Rubber FeetF USB ConnectorBasic Operation︱Plugging in the CD/DVD Writer1. Plug the small end of the USB Cable into the Mini USB port on the CD/DVD Writer.2. Plug the large end(s) of the cable into available USB ports on your desktop computer, notebookor netbook.Note: Please be sure to connect the CD/DVD Writer to two USB ports on your computer using the provided USB Cable.3. When the CD/DVD Writer is successfully connected to a computer, a new drive with a newlyassigned drive letter will appear in the My Computer window, and a Removable Hardwareicon will appear on the Windows System Tray.*D: is an example drive letter. The letter in your "My Computer" window may differ4. Once properly connected, you can use the CD/DVD Writer as an optical device to read CDsand DVDs, and create/write your own discs with the included Power2Go software.Inserting a Disc1. Press the Eject Button on the front of the CD/DVD Writer to release the disc tray.2. Gently pull the disc tray out until it stops.3. Place a CD or DVD onto the tray.4. Using two or more fingers, press down on the center of the disc until it snaps into place.5. Push the disc tray back into the CD/DVD Writer. When completely closed, the LED indicatorwill flash.Ejecting a Disc1. Press the Eject Button on the front of the CD/DVD Writer to release the disc tray.2. Gently pull the disc tray out until it stops.3. Place your thumb on the spindle and use your other fingers to gently pry the disc upwards untilit pops free.Disconnecting from a Computer︱NEVER disconnect the CD/DVD Writer from a Computer when the disc is spinning.1. Select the Hardware icon on the system tray.2. The Safely Remove Hardware pop-up window will appear. Select it to continue.3. A window will appear stating, “The ‘USB Mass Storage Device’ device can now be safelyremoved from the system.”Always use this procedure to safely remove the device from a Windows computer.Software Download︱The free software download includes: CyberLink® Power2Go (LE Version) and CyberLink®MediaShow (trial version).Note: CyberLink®Power2Go and MediaShow can only be installed in Windows® XP/Vista/7/8.Make sure that the DVDS is connected to your computer before installing:1. Download the CyberLink Media Suite 10 from Transcend’s online Download Center at/downloads.2. Double click on the CyberLink.Media.Suite.10.zip Zip file you have just downloaded fromthe Transcend website.3. Extract the file to a temporary directory on your hard disk and double click on the fileCyberLink.Media.Suite.10.exe to run the setup program.4. Follow the on-screen instructions to complete the installation process.CyberLink Power2Go: Power2Go lets you burn music, data, video and even bootable discs in a variety of CD and DVD formats. CyberLink Power2Go also includes several handy discutilities and an express mode that makes burning convenient and easy.CyberLink MediaShow: MediaShow is a useful tool for compiling, arranging, and producing media files with a simple and straightforward software interface.Troubleshooting︱If a problem occurs with your CD/DVD Writer,please check the information listed below before sending your CD/DVD Writer in for repair. If you are unable to remedy a problem after trying the following suggestions, please consult your dealer, service center, or local Transcend branch office. We also have FAQ and Support services on our website at .Operating system cannot detect the CD/DVD WriterCheck the following:1. Is your CD/DVD Writer properly connected to the USB port? If not, unplug it and plug it inagain. If it is properly connected, try using another available USB port.2. Are you using the USB cable that came in the CD/DVD Writer package? If not, try using theTranscend-supplied USB cable to connect the CD/DVD Writer to your computer.3. The CD/DVD Writer is powered directly via a computer USB port; however, the power suppliedby the USB port on some older computers is below the 5V DC required to power the CD/DVD Writer. Please make sure to connect the USB cable to both USB ports on your computer. This will provide the additional power necessary to run the drive.Both USB connectors are required to provide adequate power.4. Is the USB port enabled? If not, refer to the user’s manual of your computer (or motherboard)to enable it.5. If you have connected all ends of the USB cable and still have power-related problems whilereading / writing data, we recommend that you purchase a Transcend USB Power Adapter (TS-PA2A) to provide the power necessary to operate the CD/DVD Writer. (Please see the Transcend Website or contact your local dealer for availability)My computer does not recognize CD/DVD Writer1. A single USB port may not provide enough power for the CD/DVD Writer to function. Makesure you plug both large ends of the USB cable directly into your computer’s USB ports.2. Avoid connecting the CD/DVD Writer through a USB hub.The CD/DVD Writer does not Power On (LED does not flash)Check the following:1. Ensure that the CD/DVD Writer is properly connected to the USB port(s) on your computer.2.Ensure that the USB port is working properly. If not, try using an alternate USB port.The CD/DVD Writer Cannot Read a DiscThe disc may be dirty, scratched or damaged. Try cleaning the disc with water or a CD/DVDcleaning solution.Writing to a Blank Disc FailsIn most cases, this problem is a result of trying to write to poor quality recordable media. For best results, please use only retail-packaged name brand recordable discs.System Requirements ︱Hardware CPU: Intel Pentium III 800 MHz or equivalent (minimum )Intel Pentium IV 2.0 GHz or higher (recommended )Memory: 256MB or greaterHard Drive: 20GB of free space requiredSoftwareOperating System: Windows ® XP , Windows Vista ® , Windows ® 7 or Windows ® 8Ordering Information ︱Device Description Transcend P/N USB Power Adapter TS-PA2ARecycling & Environmental Considerations︱Recycling the Product (WEEE): Your product is designed and manufactured with high quality materials and components, which can be recycled and reused. When you see the crossed-out wheel bin symbol attached to a product, it means the product is covered by the European Directive 2002/96/EC:Never dispose of your product with other household waste. Please inform yourself about the local rules on the separate collection of electrical and electronic products. The correct disposal of your old product helps prevent potential negative consequences on the environment and human health.Battery Disposal: Your product contains a built-in rechargeable battery covered by the European Directive 2006/66/EC, which cannot be disposed of with normal household waste.Please inform yourself about the local rules on separate collection of batteries. The correct disposal of batteries helps prevent potentially negative consequences on the environment and human health.For products with non-exchangeable built in batteries: The removal of (or the attempt to remove) the battery invalidates the warranty. This procedure is only to be performed at the end of the product’s life.Two-year Limited Warranty︱This product is covered by a Two-year Limited Warranty.Should your product fail under normal use within two years from the original purchase date, Transcend will provide warranty service pursuant to the terms of the Transcend Warranty Policy. Proof of the original purchase date is required for warranty service. Transcend will inspect the product and in its sole discretion repair or replace it with a refurbished product or functional equivalent. Under special circumstances, Transcend may refund or credit the current value of the product at the time the warranty claim is made. The decision made by Transcend shall be final and binding upon you. Transcend may refuse to provide inspection, repair or replacement service for products that are out of warranty, and will charge fees if these services are provided for out-of-warranty products.LimitationsAny software or digital content included with this product in disc, downloadable, or preloaded form, is not covered under this Warranty. This Warranty does not apply to any Transcend product failure caused by accident, abuse, mishandling or improper usage (including use contrary to the product description or instructions, outside the scope of the product’s intended use, or for tooling or testing purposes), alteration, abnormal mechanical or environmental conditions (including prolonged exposure to humidity), acts of nature, improper installation (including connection to incompatible equipment), or problems with electrical power (including undervoltage, overvoltage, or power supply instability). In addition, damage or alteration of warranty, quality or authenticity stickers, and/or product serial or electronic numbers, unauthorized repair or modification, or any physical damage to the product or evidence of opening or tampering with the product casing will also void this Warranty. This Warranty shall not apply to transferees of Transcend products and/or anyone who stands to profit from this Warranty without Transcend’s prior written authorization. This Warranty only applies to the product itself, and excludes integrated LCD panels, rechargeable batteries, and all product accessories (such as card adapters, cables, earphones, power adapters, and remote controls). Transcend Warranty PolicyPlease visit /warranty to view the Transcend Warranty Policy.By using the product, you agree that you accept the terms of the Transcend Warranty Policy, which may be amended from time to time.Online registrationTo expedite warranty service, please access /register to register your Transcend product within 30 days of the purchase date.Transcend Information, Inc.*The Transcend logo is a registered trademark of Transcend Information, Inc.*The specifications mentioned above are subject to change without notice.*All logos and marks are trademarks of their respective companies.。

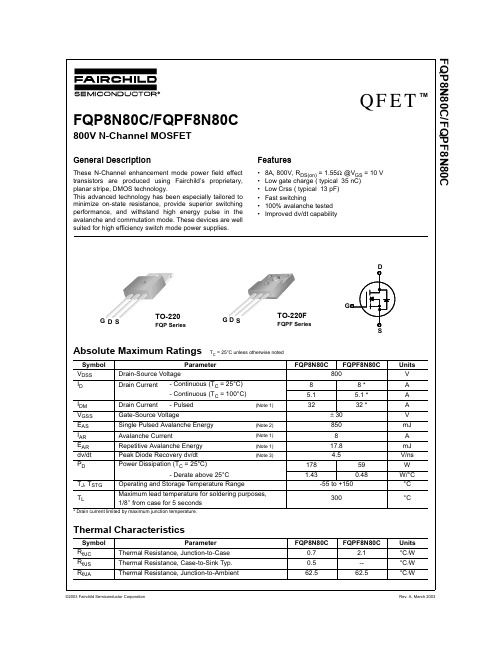

SPW17N80C3中文资料

IGSS

VGS=20V, VDS=0V

-

- 100 nA

Drain-source on-state resistance RDS(on) VGS=10V, ID=11A,

Ω

Tj=25°C

- 0.25 0.29

Tj=150°C

- 0.78 -

Gate input resistance

RG

f=1MHz, open Drain

ID

TC = 25 °C

TC = 100 °C

Pulsed drain current, tp limited by Tjmax

ID puls

Avalanche energy, single pulse

EAS

ID = 3.4 A, VDD = 50 V

Avalanche energy, repetitive tAR limited by Tjmax1) EAR

Values

Unit

min. typ. max.

Drain-source breakdown voltage V(BR)DSS VGS=0V, ID=0.25mA 800

-

Drain-Source avalanche

V(BR)DS VGS=0V, ID=17A

-

870

breakdown voltage

Symbol

Value

Unit Symbol

Value

typ.

typ.

Thermal resistance

Thermal capacitance

Rth1 Rth2 Rth3 Rth4 Rth5 Rth6

0.00812 0.016 0.031 0.114 0.135 0.059

wap-223_101-httpsm-20010928-a