vlsi设计cad工具Chapter11 Chip Assemble

(整理)用PressCAD软体设计模具之流程

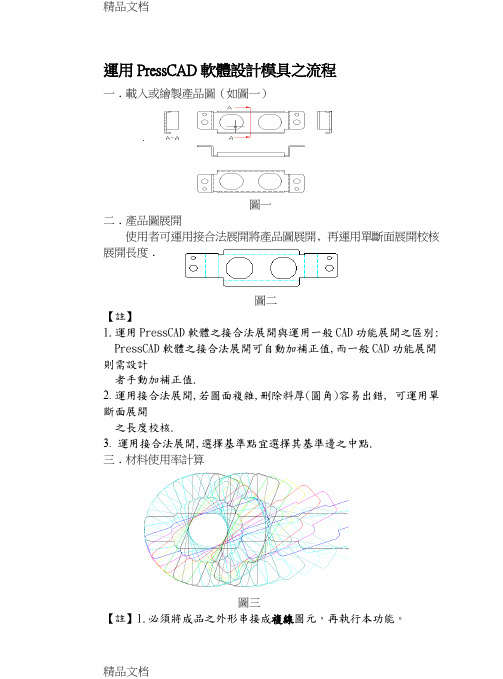

運用PressCAD軟體設計模具之流程一﹒載入或繪製產品圖(如圖一)圖一二﹒產品圖展開使用者可運用接合法展開將產品圖展開﹐再運用單斷面展開校核展開長度﹒圖二【註】1.運用PressCAD軟體之接合法展開與運用一般CAD功能展開之區別: PressCAD軟體之接合法展開可自動加補正值,而一般CAD功能展開則需設計者手動加補正值.2.運用接合法展開,若圖面複雜,刪除料厚(圓角)容易出錯,可運用單斷面展開之長度校核.3.運用接合法展開,選擇基準點宜選擇其基準邊之中點.三﹒材料使用率計算圖三【註】1.必須將成品之外形串接成複線圖元,再執行本功能。

2.每次步進角度必須設>0,若設定為<=0則系統會自動改成1。

3.執行本指令產生的數據資料,系統將自動儲存,供給<料條排列>指令抓取使用。

四﹒料帶排列圖四【註】1)執行本指令,不必將成品展開圖之外形串接成複線(Pline)圖元。

2)執行本指令,須先執行使用率計算指令,求出最佳"節距"及"旋轉角度"值供系統進行料條排列。

3)系統即依所有設定值自動於料帶層(MATER)繪出料帶圖。

五﹒料帶製作圖五料帶製作是連續模設計之核心環節,需要經驗豐富的設計師來完成,任何設計軟體都不能替代,當料條排列好後,設計師開始構思工站佈置,依照料帶圖於輔助圖層繪製輔助線,定出沖頭之外形。

【註】以下是工站佈置過程中應考慮的事項(僅供參考):(1)配合製品之形狀及精度等要求,選擇適正的沖壓加工方法.(2)配合製品形狀及精度要求規劃加工工程之順序.(3)沖壓加工製程條件及模具強度或剛性等之檢討.(4)沖壓加工進行時,製品取出及廢料排出之對策處理檢討.(5)模具之調整性和維護保護便利性等方面之考慮及檢討.(6) 考慮模具設計之變更及工程追加之可能性.六﹒模具總設定料帶製作OK後,設計師開始構思模具結構,設定模板厚度、材質和硬度,設定模板零件的固定方式、位置排列及其間隙配合。

vlsi设计cad工具Chapter10 SocEncounter P&R

Chapter10SOC EncounterPlace and RouteP LACE AND ROUTE is the process of taking a structuralfile(Verilog in our case)and making a physical chip from that description.Itinvolves placing the cells on the chip,and routing the wiring con-nections between those cells.The structural Verilogfile gives all the in-formation about the circuit that should be assembled.It is simply a list of standard cells and the connections between those cells.The cell layouts are used to place the cells physically on the chip.More accurately,the abstract views of the cells are used.The abstracts have only information about the connection points of the cells(the pins),and routing obstructions in those cells.Obstructions are simply layers of material in the cell that conflict with the layers that the routing tool wants to use for making the connections.Es-sentially it is a layout view of the cell that is restricted to pins and metal routing layers.This reduces the amount of information that’s required by the place and route tool,and it also lets the vendor of the cells to keep other details of their cells(like transistor information)private.It’s not need for place and route,so it’s not included in the abstract view.Thefiles required before starting place and route are:Cell characterization data:This should be in a liberty(or<filename>.lib) formattedfile.It is the detailed timing,power,and functionality infor-mation that you derived through the characterization process(Chap-ter7).It’s possible that you might have up to three different.libfileswith typ,worst,and best timing,but you can complete the processwith only a single.libfile.It is very important that your.libfile in-clude footprints for all cells.In particular you will need to know thefootprint of inverter,buffer,and delay cells(delay cells can just bebuffers or inverters).If you have special buffers/inverters for buildingCHAPTER10:SOC EncounterPlace and Route Draft October16,2006clock trees,those should use a different footprint than the“regular”buffers and inverters.If you have multiple drive strengths of any cellswith the same functionality,those cells should have the same foot-print.This enables certain timing optimizations in the place and routetool.You might have multiple.libfiles if your structural Verilog uses cellsfrom multiple libraries.Cell abstract information:This is information that you generated through the abstract process(Chapter9),and is contained in a LEF(or<filename>.lef)file.The LEFfile should include technology information and macroinformation about all the cells in your library.You might have multiple.leffiles if your structural Verilog uses cellsfrom multiple different libraries.Structural Verilog:Thisfile defines the circuit that you want to have as-sembled by the place and route tool.It should be a purely structuraldescription that contains nothing but instantiations of cells from yourlibrary or libraries.If your design is hierarchical you might have multiple Verilogfilesthat describe the complete design.That is,some Verilog modulesmight include instantiations of other modules in addition to just cells.In any case you should know the name of the top-level module that isthe circuit that you want to place and route.Delay constraint information:This is used by the place and router dur-ing timing optimization and clock tree generation.It describes thetiming and loading of primary inputs and outputs.It also defines theclock signal and the required timing of the clock signal.Thisfilewill have been generated by the Synopsys synthesis process,and is<filename>.sdc.You can also generate this by hand since it’s just atextfile,but it’s much easier to let Synopsys generate thisfile based onthe timing constraints you specified as part of the synthesis procedure(Chapter8).If you have all thesefiles you can proceed to use the place and routetool to assemble that circuit on a chip.In our case we’ll be using the SOC Encounter tool from Cadence.My recommendation is to make a new directory from which to run the tool.I’ll make an IC CAD/soc direc-tory,and in fact,under that I’ll usually make eachproject I’m running through the soc tool.In this example I’ll be using asimple counter that is synthesized from the behavioral Verilog code in Fig-ure10.1so I’ll make an IC CAD/soc/count directory to run this ex-ample.Inside this directory I’ll make copies or links to the.lib and.lef292Draft October16,200610.1:Encounter GUI module counter(clk,clr,load,in,count);parameter width=8;input clk,clr,load;input[width-1:0]in;output[width-1:0]count;reg[width-1:0]tmp;always@(posedge clk or negedge clr)beginif(!clr)tmp=0;else if(load)tmp=in;elsetmp=tmp+1;endassign count=tmp;endmoduleFigure10.1:Simple counter behavioral Verilog codefiles I’ll be using.In this case I’ll use example.lib and example.lef from the small library example from Chapters7and9.The structural Verilog file(count struct.v)generated from Synopsys(Chapter8)is shown in Fig-ure10.2,and the timing constraintsfile,count struct.sdc is shown in Fig-ure10.3.This is generated from the synthesis process and encodes the tim-ing constraints used in synthesis.Once I have all thesefiles in place I can begin.10.1Encounter GUIAs afirst tutorial example of using the SOC Encounter tool,I’ll describe how to use the tool from the GUI.Most things that you do in the GUI can also be done in a script,but I think it’s important to use the tool interactively so that you know what the different steps are.Also,even if you script the optimization phases of the process,it’s probably vital that you do thefloor planning by hand in the GUI for complex designs before you set the tool loose on the optimization phases.First make sure that you have all thefiles you need in the directory you will use to run SOC Encounter.I’m using the counter from the previous Figures so I have:count struct.v:The structuralfile generated by Synopsyscount struct.sdc:The timing constraintsfile generated by Synopsys293CHAPTER10:SOC EncounterPlace and Route Draft October16,2006module counter(clk,clr,load,in,count);input[7:0]in;output[7:0]count;input clk,clr,load;wire n39,n40,n41,n42,n43,N5,N6,N7,N8,N9,N10,N11,N12,N13,N14, N15,N16,N17,N18,N19,N20,n2,n3,n4,n5,n6,n7,n8,n9,n10,n11,n12,n13,n14,n15,n16,n17,n18,n19,n20,n21,n22,n23,n24,n25,n26,n27,n28,n30,n31,n32,n33,n34,n36,n37;DFF tmp_reg_0_(.D(N12),.G(clk),.CLR(clr),.Q(n43));DFF tmp_reg_1_(.D(N13),.G(clk),.CLR(clr),.Q(n42));DFF tmp_reg_2_(.D(N14),.G(clk),.CLR(clr),.Q(n41));DFF tmp_reg_3_(.D(N15),.G(clk),.CLR(clr),.Q(n40));DFF tmp_reg_4_(.D(N16),.G(clk),.CLR(clr),.Q(n39));DFF tmp_reg_5_(.D(N17),.G(clk),.CLR(clr),.Q(count[5]));DFF tmp_reg_6_(.D(N18),.G(clk),.CLR(clr),.Q(count[6]));DFF tmp_reg_7_(.D(N19),.G(clk),.CLR(clr),.Q(count[7]));MUX2_INV U13(.A(N20),.B(in[5]),.S(load),.Y(n4));MUX2_INV U14(.A(N9),.B(in[4]),.S(load),.Y(n5));MUX2_INV U15(.A(N8),.B(in[3]),.S(load),.Y(n6));MUX2_INV U16(.A(N7),.B(in[2]),.S(load),.Y(n7));MUX2_INV U17(.A(N6),.B(in[1]),.S(load),.Y(n8));MUX2_INV U18(.A(N5),.B(in[0]),.S(load),.Y(n9));INVX1U5(.A(n4),.Y(N17));INVX1U9(.A(n8),.Y(N13));INVX4U19(.A(n27),.Y(n15));NAND2U20(.A(n23),.B(n20),.Y(n10));INVX1U21(.A(n10),.Y(n21));INVX1U22(.A(n30),.Y(n12));MUX2_INV U23(.A(count[0]),.B(N5),.S(n11),.Y(N6));XOR2U24(.A(n25),.B(count[2]),.Y(N7));NAND2U25(.A(count[2]),.B(n25),.Y(n14));MUX2_INV U26(.A(n40),.B(n13),.S(n14),.Y(N8));XOR2U27(.A(count[4]),.B(n15),.Y(N9));MUX2_INV U28(.A(count[5]),.B(n16),.S(n28),.Y(N20));NOR2U29(.A(n27),.B(n32),.Y(n17));XOR2U30(.A(count[6]),.B(n17),.Y(N10));INVX1U31(.A(count[7]),.Y(n18));INVX1U32(.A(count[6]),.Y(n19));NOR2U33(.A(n19),.B(n16),.Y(n20));NOR2U34(.A(n31),.B(n22),.Y(n23));NAND2U35(.A(n12),.B(count[2]),.Y(n22));INVX1U36(.A(n26),.Y(n24));NAND2U37(.A(n40),.B(count[2]),.Y(n26));NAND2U38(.A(n12),.B(n24),.Y(n27));NOR2U39(.A(N5),.B(n11),.Y(n25));NAND2U40(.A(count[4]),.B(n15),.Y(n28));MUX2_INV U41(.A(n18),.B(count[7]),.S(n21),.Y(N11));INVX1U42(.A(N5),.Y(count[0]));INVX1U43(.A(n42),.Y(n11));NAND2U44(.A(n43),.B(n42),.Y(n30));INVX1U45(.A(n40),.Y(n13));NAND2U46(.A(count[4]),.B(n40),.Y(n31));INVX1U47(.A(n33),.Y(n32));NOR2U48(.A(n37),.B(n16),.Y(n33));INVX1U49(.A(n43),.Y(N5));INVX1U50(.A(count[5]),.Y(n16));INVX1U51(.A(n41),.Y(n34));INVX4U52(.A(n34),.Y(count[2]));INVX1U53(.A(n11),.Y(count[1]));INVX1U54(.A(n13),.Y(count[3]));INVX1U55(.A(n39),.Y(n37));INVX1U56(.A(load),.Y(n36));INVX1U57(.A(n7),.Y(N14));MUX2_INV U58(.A(in[7]),.B(N11),.S(n36),.Y(n2));INVX4U59(.A(n37),.Y(count[4]));INVX1U60(.A(n5),.Y(N16));INVX1U61(.A(n6),.Y(N15));MUX2_INV U62(.A(in[6]),.B(N10),.S(n36),.Y(n3));INVX1U63(.A(n9),.Y(N12));INVX1U64(.A(n3),.Y(N18));INVX1U65(.A(n2),.Y(N19));endmoduleFigure10.2:Simple counter structural Verilog code using the example.lib cell library294Draft October16,200610.1:Encounter GUI####################################################################Created by write_sdc on Sun Oct817:14:102006################################################################### set sdc_version 1.6set_driving_cell-lib_cell INVX4-library example[get_ports clr]set_driving_cell-lib_cell INVX4-library example[get_ports load]set_driving_cell-lib_cell INVX4-library example[get_ports{in[7]}] set_driving_cell-lib_cell INVX4-library example[get_ports{in[6]}] set_driving_cell-lib_cell INVX4-library example[get_ports{in[5]}] set_driving_cell-lib_cell INVX4-library example[get_ports{in[4]}] set_driving_cell-lib_cell INVX4-library example[get_ports{in[3]}] set_driving_cell-lib_cell INVX4-library example[get_ports{in[2]}] set_driving_cell-lib_cell INVX4-library example[get_ports{in[1]}] set_driving_cell-lib_cell INVX4-library example[get_ports{in[0]}] set_load-pin_load0.0659802[get_ports{count[7]}]set_load-pin_load0.0659802[get_ports{count[6]}]set_load-pin_load0.0659802[get_ports{count[5]}]set_load-pin_load0.0659802[get_ports{count[4]}]set_load-pin_load0.0659802[get_ports{count[3]}]set_load-pin_load0.0659802[get_ports{count[2]}]set_load-pin_load0.0659802[get_ports{count[1]}]set_load-pin_load0.0659802[get_ports{count[0]}]create_clock[get_ports clk]-period3-waveform{0 1.5}set_input_delay-clock clk0.25[get_ports clr]set_input_delay-clock clk0.25[get_ports load]set_input_delay-clock clk0.25[get_ports{in[7]}]set_input_delay-clock clk0.25[get_ports{in[6]}]set_input_delay-clock clk0.25[get_ports{in[5]}]set_input_delay-clock clk0.25[get_ports{in[4]}]set_input_delay-clock clk0.25[get_ports{in[3]}]set_input_delay-clock clk0.25[get_ports{in[2]}]set_input_delay-clock clk0.25[get_ports{in[1]}]set_input_delay-clock clk0.25[get_ports{in[0]}]set_output_delay-clock clk0.25[get_ports{count[7]}]set_output_delay-clock clk0.25[get_ports{count[6]}]set_output_delay-clock clk0.25[get_ports{count[5]}]set_output_delay-clock clk0.25[get_ports{count[4]}]set_output_delay-clock clk0.25[get_ports{count[3]}]set_output_delay-clock clk0.25[get_ports{count[2]}]set_output_delay-clock clk0.25[get_ports{count[1]}]set_output_delay-clock clk0.25[get_ports{count[0]}] Figure10.3:Timing information(.sdcfile)for the counter example295CHAPTER10:SOC EncounterPlace and Route Draft October16,2006example.lib:A link to my cell library’s characterized data in.lib format.Make sure thisfile has footprint information for all cells. example.lef:A link to my cell library’s abstract data in.lef form.Make sure that you have correctly appended the TechHeader.lef informa-tion in front of the MACRO definitions.After connecting to your directory(I’m using IC CAD/soc/counter) you can start the SOC Encounter tool using the cad-soc script.You’ll see the main encounter window as seen in Figure10.4.This Figure is annotated to describe the different areas of the screen.The pallete on the right lets you choose what is currently visible in the design display area. The Design Views change how you see that design.From left to right the Design Views are:Floorplan View:This view shows the overallfloorplan of your chip.It lets you see the area that is generated for the standard cells,and how the different pieces of your design hierarchyfit into that standard cell area.For thisfirst example there is no hierarchy in the design so the entire counter will be placed inside the cell area.For a more complex design you can manually place the different pieces of the design in the cell area if you wish.Amoeba View:This view shows information related to the Amoeba place-ment and routing of the cells.It gives feedback on cell placement, density,and congestion.Physical View:This view shows the actual cells as they are placed,and the actual wires as they are routed by the tool.All three views are useful,but I generally start out with thefloorplan view during,as you might guess,floorplanning,then toggle between the that view and the physical view once the place and route gets under way. 10.1.1Reading in the DesignOnce the tool is started you need to read all your designfiles into the tool. Select the Design→Design Import...menu choice to get the Design Im-port dialog box.This box has multiplefields in multiple tabs that you need tofill in.Firstfill in the Basicfields with the following(see Figure10.5): Verilog Netlist:Your structural Verilogfile orfiles.You can either let SOC Encounter pick the top cell,or you can provide the name of the top level module.296Draft October16,200610.1:Encounter GUIFigure10.4:Main SOC Encounter gui297CHAPTER10:SOC EncounterPlace and Route Draft October16,2006Figure10.5:Design Import dialog box-basic tabTiming Libraries:Your.libfile orfiles.If you have only onefile it should be entered into the Common Timing Libraries line.If you have best, typ,worst timing libraries,they should be entered into the otherfields with the worst case entered into the maxfield,the best case into the minfield,and the typical case in the commonfield.This is optional and the process works justfine with only one library in the common field.LEF Files:Enter your.leffile orfiles.Timing Constraint File:Enter your.sdcfile.Now,move to the Advanced tab and make the following entries:IPO/CTS:This tab provides information for the IPO(In Place Optimiza-tion)and CTS(Clock Tree Synthesis)procedures by letting SOC En-counter know which buffer and inverter cells it can use when optimiz-ing things.Enter the name of the footprints for buffer,delay,inverter, and CTS cells.Leave any blank that you don’t have.I’m entering inv as the footprint for delay,inverter,and CTS,and leaving buffer blank as shown in Figure10.6.Your library may be different.Power:Enter the names of your power and ground nets.If you’re follow-ing the class design requirements this will be vdd!and gnd!(Fig-ure10.7).298Draft October16,200610.1:Encounter GUIFigure10.6:Design Import IPO/CTS tabFigure10.7:Design Import Power tab299CHAPTER10:SOC EncounterPlace and Route Draft October16,2006Now you can press OK and read all this information into SOC En-counter.The comments(and potential warnings and errors)will show upin the shell window in which you invoked cad-soc.You should look atthem carefully to make sure that things have imported correctly.If they didyou will see the SOC Encounter window has been updated to show a set ofrows in which standard cells will be placed.10.1.2FloorplanningFloorplanning is the step where you make decisions about how denselypacked the standard cells will be,and how the large pieces of your designwill be placed relative to each other.Because there is only one top-levelmodule in the counter example,this is automatically assumed to cover theentire standard cell area.If your design had mode structure in terms of hi-erarchical modules,those modules would be placed to the side of the cellplacement area so that you could place them as desired inside the cell area.The default is just to let the entire top-level designfill the standard cell areawithout further structuring.In practice this spreads out the entire designacross the entire area which,for large systems with significant structure,may result in lower performance.For a system with significant structure acareful placement of the major blocks can have a dramatic impact on systemperformance.But,for this example,what we really care about is cell density and other area parameters related to the design.Select Floorplan→Specify Floor-plan...to get thefloorplanning dialog box(Figure10.8).In this dialog boxyou can change various parameters related to thefloorplan:Aspect Ratio:This sets the(rectangular)shape of the cell.An aspect ofclose to1is close to square.An aspect of.5is a rectangle with thevertical edge half as long as the horizontal,and1.5is a rectangle withthe vertical edge twice the horizontal.This is handy if you’re tryingto make a subsystem tofit in a larger project.For now,just for fun,I’ll change the aspect ratio to0.5.Note that the tool will adjust thisnumber a little based on the anticipated cell sizes.Core Utilization:This lets the tool know how densely packed the coreshould be with standard cells.The default is around70%which leavesroom for in place optimization and clock tree synthesis,both ofwhich may add extra cells during their operation.For a large complexdesign you may even have to reduce the utilization percentage belowthis.Core Margins:These should be set by Core to IO Boundary and are All measurements areassumed to be inmicrons.300to leave room for the power and ground rings that will be generated around your cell.All the Core to ...values should be set to 30.Note that even though you specify 30,when you apply those values they may change slightly according to SOC Encounter’s measurements.Others:Other spots in the Specify Floorplan dialog can be left as de-fault.In particular you want the standard cell rows to be Double-back Rows ,and you can leave the Row Spacing as zero to leave no space between the rows.If your design proves hard to route you can start again and leave extra space between the rows for routing.After adjusting the floorplan,the main SOC Encounter window looks like Figure 10.9.The rows in which cells will be placed are in the center with the little corner diagonals showing how the cells in those rows will be flipped.The dotted line is the outer dimension of the final cell.The power and ground rings will go in the space between the cells and the outer boundary.Saving the DesignThis is a good spot in which to save the current design.There are lots of I like to save the design at each major step so that I can go back if I need to try something different at that step.Be aware that there’s no general “undo”function in Encounter.steps in the process that are not “undo-able.”It’s nice to save the design at various points so that if you want to try something different you can reload the design and try other things.Save the design with Design →Save De-sign...and name the saved file <filename >.enc .In my case I’ll name it floorplan.enc so that I can restore to the point where I have a floorplan if I want to start over from this point.Saved designs are restored into the tool using the Design →Restore Design...menu.10.1.3Power PlanningNow it’s time to put the power and ground ring around your circuit,and connect that ring to the rows so that your cells will be connected to power and ground when they’re placed in the row.Start with Power →Power Planning →Add Rings .From this dialog box (Figure 10.10)you can control how the power rings are generated.The fields of interest are:Remember that all thesizes and spacings youspecify must be divisibleby the basic lambda unit of our underlyingtechnology.That is,everything is measured in units of 0.3microns,so values should bedivisible by 0.3.Ring Type:The defaults are good here.You should have the Core ring(s)contouring:set to Around core boundary .Ring Configuration:You can select the metal layers you want to use for the ring,their width,and their spacing.I’m making the top and bottom of the ring horizontal metal1,and the right and left vertical 301Place and Route Draft October16,2006Figure10.8:The Specify Floorplan dialog box302303Place and Route Draft October16,2006metal2to match our routing protocol.Change the width of each side of the ring to9.9and the spacing should be set to1.8because of the extra spacing required for wide metal.Finally,the offset can be left alone or changed to center in channel.If it’s left alone it should probably be changed to1.8to match the wide metal spacing.When you click OK you will see the power and ground rings generated around your cell.You can also zoom in and see that the tool has generated arrays of vias where the wide horizontal and vertical wires meet.Now,for this simple small design,this would be enough,but for a larger design you would want to add power stripes in addition to the power rings. Stripes are additional vertical power and ground connections that turn the power routing into more of a mesh.Add stripes using the Power→Power Planning→Add Stripes...menu(Figure10.11.Thefields of interest are: Set Configuration:Make sure that all your power and ground signals are in the Net(s)field(vdd!and gnd!in our case).Choose the layer you want to the stripes to use.In our case the stripes are vertical so it makes sense to have them in the normal vertical routing layer of metal2.Change the width and spacing as desired(I’m choosing4.8 for the width and1.8for the spacing-remember that they need to be multiples of0.3).Set Pattern:This section determines how much distance there is between the sets of stripes,how many different sets there are,and other things.You can leave the Set-to-set distance to the default of100.Stripe Boundary:Unless you’re doing something different,leave the de-fault to have the stripes generated for your Core ring.First/Last Stripe:Choose how far from the left(or right)you want your first stripe.I’m using75from the left in this example so that the stripes are roughly spaced equally in the cell.Note that this is proba-bly overkill from a power distribution point of view.For a larger cell 250micron spacing might be a more reasonable choice. Advanced Tab-Snap Wire to Routing Grid:Change this from None to Grid.The issue here is that our cells are designed so that if two cells are placed right next to each other,no geometry in one cell will causea design rule violation in the other cell.That’s the reason that nocell geometry(other than the well)is allowed within0.6µfrom the prBoundary.That way layers,such as metal layers,are at least1.2µfrom each other when cells are abutted.However,the power stripes don’t have that restriction and if you don’t center the power stripes on the grid,a cell could be placed right next to a power grid and cause a304Figure10.10:Dialog box for adding power and ground rings around your cell305Place and Route Draft October 16,2006Figure 10.11:Dialog box for planning power stripesmetal spacing DRC violation when the metal of the stripe is now only 0.6µfrom the metal in the cell.Centering the stripe on a grid keeps this from happening by placing the metal of the stripe in a position so that the next legal cell position isn’t directly abutting with the power stripe.Clicking Apply will apply the stripes to your design.If you don’t like the looks of them you can select and delete them and try again with different parameters.Or you can select OK and be finished.Once you have the stripes placed you can connect power to the rows Now is another good time to save the cell again.This time I’ll save it as powerplan.enc .where the cells will be placed.Select Route →Special Route to route the power wires.Make sure that all your power supplies are listed in the Net(s)306307Place and Route Draft October16,2006Figure10.13:Floorplan after power rings and stripes have been generated and connected to the cell rowsfield(vdd!and gnd!in our case).Otherfields don’t need to be changed unless you have specific reasons to change them.Click OK and you will see the rows have their power connections made to the ring/stripe grid as seen in Figure reffig:soc-pp4.Zoom in to any of the connections and you’ll see that an array of vias has been generated tofill the area of the connection. 10.1.4Placing the Standard CellsNow you want the tool to place the standard cells in your design into that floorplan.Select Place→Standard Cells and Blocks....Leave the defaults in the dialog box as seen in Figure10.14.You definitely want to use timing driven placement and pre-place optimization.After pressing OK your cells will be placed in the rows of thefloorplan. This might take a while for a large design.When it’sfinished the screen won’t look any different.Change to the physical view(the rightmost design view widget-see Figure10.15)and you’ll see where each of your cells has been placed.The placed counter looks like that in Figure10.16.308Figure10.14:Placement dialog boxFigure10.15:Widget for changing to the physical view of the cell309Place and Route Draft October16,2006Figure10.16:View after placement of the cells310If your design had more than onefloorplan elements you could go back to thefloorplan view and select one of the elements.Then moving to the physical view you would see where all the cells from that element had ended up.This is an interesting way of seeing how the placement has partitioned things.10.1.5First Optimization PhaseNow you can perform thefirst timing and optimization step.At this stage of the process there are no wires so the timing step will do a trial route to estimate the wiring.This is a low-effort not-necessarily-correct routing of the circuit just for estimation.Select Timing→Optimization.Notice that under Design Stage you should select pre-CTS to indicate that this analysis is before any clock tree has been generated(Figure10.17).You’re also doing analysis only on setup time of the circuit.Click OK and you’ll see the result of the timing optimization and analysis in the shell window.If you refresh the screen you’ll also see that it looks like the circuit has been routed!But,this is just a trial route.These wires will be replaced with real routing wires later.In this case the timing report(shown in Figure10.18)shows that we are not meeting timing.In particular,there are7violating paths and the worst negative slack is-1.757ns.The timing was specified in the.sdcfile and came from the timing requirements at synthesis time.In this case the desired timing is an(overly aggressive)3ns clock period just to demonstrate how things work.Note that you can always re-run the timing analysis after trying things by selecting Timing→Timing Analysis from the menu.Make sure to select the correct Design Stage to reflect where you are in the design process.At this point,for example,I am in Pre-CTS stage.10.1.6Clock Tree SynthesisNow we can synthesize a clock tree which will(hopefully)help our timing situation.In a large design this will have a huge impact on the timing.In this small example design it will be less dramatic.Select Clock→Cre-ate Clock Tree Spec to start.You shouldfill in the footprint information that the CTS process can use to construct a clock tree.This should have beenfilled in with the information from our original design import but it’s not for some reason.I’mfilling in inv as the inverter footprint and another for buffers because my library doesn’t have non-inverting buffers(see Fig-ure10.19).Your library may be different.Clicking OK will generate a clock tree specification in the(default)counter.ctstchfile.311。

用VLISP开发AutoCAD

首页 上页 返回 下页 结束 11

A u t o C A D 定 制 与 开 发

2、AutoLISP基本函数

赋值与计算函数 如:(Setq a 3.0 ) (Sin 1.0) 逻辑运算函数 如:(< 20 10) 程序分支与循环函数 (> 20 10) 如:(setq s 0 a 1) 字符串与类型转换函数 (repeat 100 如:(strlen “abc”) (setq s (+ s a)) 表处理函数 (float 10) 如:(car „(a b c)) (setq a (+ a 1)) 交互输入输出函数 (length „(a b ) c)) 如:(getpoint [pt] [msg]) 文件处理函数 (getreal [msg]) 如:(close file-desc) 与AutoCAD直接相关的函数 (findfile filename) 如:(command "circle" p0 r) 实体与选择集操作函数 (setvar varname value) 如:(ssget “w” „(0 0) „(5 5)) 有关函数的函数

VLSI系统设计PPT学习教案

保证足够的P+接触区 保证P管源漏区完整注入 保证NMOS源区尺寸 防止P+注入到N+区

保证足够的N+接触区 保证N管源漏区完整注入 保证PMOS源区尺寸 防止N+注入到P+区

保证与金属接触良好 有利于接触孔的成品率 保证长孔的良好接触 防止源漏区与栅短路 防止PN结漏电和短路 防止漏电和短路

保证互连的良好电导 防止连条 保证接触 防止连条

NMOS模型中描述例句

TOX = toxn

XL

= '3E-8 + dxl'

XW

= '0 + dxw'

VTH0 = '0.4321336+dvthn'

CJ

= cjn

CJSW = cjswn

CGDO = 'cgon'

CGSO = 'cgon'

CJSWG = cjgaten

3.3.3 模型参数的离散及仿真方法

(21)

.4

第20页/共42页

3.4.1 几何设计规则描述

描述方法:一是以最小单位λ的倍数表 示,几 何设计 规则中 的所有 数据都 以λ的 倍数表 示,如3λ、5λ 。λ是最 小沟道 长度L的一半 ,是具 体的数 值。这 种描述 方法称 为λ设计 规则。 二是用 具体的 数值进 行描述 ,数值 单位是 微米, 被称为 微米设 计规则 。

版图设计规则是一组几何尺寸,是 对加工 精度( 如最细 线条) ;寄生 效应( 如寄生 晶体管 );特 性保障 (如可 控硅效 应抑制 );加 工质量 控制( 如成品 率)等 多方面 的抽象 。

(11)

.2

第10页/共42页

超大规模集成电路CAD 第二章 VLSI设计方法

2014-4-21

15

第2章 VLSI概述设计方法

路 漫 漫 其 修 远 兮 吾 将 上 下 而 求 索

布线通道

图2-2

2014-4-21

Macro Cell–Based

16

第2章 VLSI概述设计方法

基于单元的IC的特点

All mask layers are customized— transistors and interconnect : IC 的所有 掩膜层,包括晶体管和连线都是特意设计的。 Custom blocks can be embedded:宏单元可以 根据需要嵌入到IC版图中,与其它宏单元以及 标准单元一起连线。 基于标准单元的ASIC设计快于全定制设计 仍需要制作全部的掩膜 Manufacturing lead time is about eight weeks.

定义 What is Sem-Custom? 所谓半定制电路设计: 是指以预先设计并经过验证的单元为基础,从事具体电 路的有关设计。也就是说,厂家预先把一些基本门或其 它单元的功能级电路与版图设计好,并提供给系统设计 者,作为他们从事电路设计的基本单元。这样设计者就 不涉及单元电路内部器件之间的互连,而只要把这些基 本单元进行合理的布局和相互连线就可以了。因此,半 定制设计方法是一种面向逻辑级设计。(设计者在厂家 提供的半成品基础上继续完成最终的设计,一般是在成 熟的通用母片基础上追加某些互连线或某些专用电路的 互连线掩膜,因此设计周期短。)N-Si NhomakorabeaP阱

(a ) 掩膜版 2

薄氧化层 N-Si

(b )

多晶硅栅

掩膜版 3

N-Si

2014-4-21

(c)

20

VLSI设计基础12-2

CL , KPVdd

τN =

CL , KNVdd

αP =

VTP , Vdd

αN =

VTN Vdd

1 1+ x arcth( x) = ln 2 1− x

|VT/Vdd|:0.1~0.4; [-----]:1.4~2.8

VLSI设计基础VLSI设计基础-2 .2 设计基础

(21) )

东南大学电子科学与工程学院

IDSN = KN [ 2(VGS −VTN )VDS −VDS ]

2

I DSN = KN (VGS −VTN )2

I DSN = 0

IP

IN

RN

如果NMOS和PMOS相应电流相等,则上升时 和 相应电流相等, 如果 相应电流相等 间和下降时间相同。 间和下降时间相同。

VLSI设计基础VLSI设计基础-2 设计基础

VLSI设计基础VLSI设计基础-2 .2 设计基础

(15) )

东南大学电子科学与工程学院

2.2.1 CMOS倒相器设计 倒相器设计

积木: 积木:

S/D

S/D

G

衬底

G

D/S 衬底 MOSFET

D/S

数字逻辑等效电路模型

数字逻辑行为模型

VLSI设计基础VLSI设计基础-2 .2 设计基础

(16) )

为什么保持临界 =VD’S 饱和时的值? 饱和时的值? VGD’=VTN

D

S

D’

+

V

厄莱电压

沟道长度调制效应

VLSI设计基础VLSI设计基础-2 .1 设计基础

(7) )

东南大学电子科学与工程学院

2.1.1 MOS晶体管结构及基本工作原理 晶体管结构及基本工作原理

中文版AutoCAD 2011 室内装潢设计

2021/8/17

16

二、设置绘图环境

使用选项(options)命令可以对系统选项进行设置,改变这些设置可以改变 系统的一些操作界面、属性及文件配置等属性。选择“工具”|“选项”命

令

2021/8/17

17

三、设置图层

图层中包含颜色、线型、打印样式、线 宽等特性,设置了图层的特性后,系统 的默认设置为每个对象的特性跟所属的 图层一样。选择“格式”|“图层”命

AutoCAD 2011拥有强大的功能,主要分 为以下几个方面: 绘图功能 编辑功能 辅助功能 设置功能 文件管理功能 三维功能 开放式体系结构 数据库的管理与连接

2021/8/17

3

二、AutoCAD 2011界面

第一次启动AutoCAD 2011后,弹出“新 功能专题研习”对话框,从对话框提供 的三个单选项中选择一个,单击“确定 ”按钮,进入AutoCAD 2011工作界面,

(1)单击“绘图”工具栏中的“直线”按钮,系统会给出下面 的命令提示

(2) 在命令行中输入line并按Enter键,可进入同一命令。 (3) 在命令行中输入L并按Enter键,也可进入同一命令。 (4) 选择窗口菜单中的“绘图”|“直线”命令,也可进入同 一命令。

2021/8/17

6

三、命令调用方法

方式。

2021/8/17

AutoCAD中文版机械设计教程

AutoCAD中文版机械设计教程(ji

标注(biāo zhù)输入

启用标注输入(shūrù),当命令行提示输入(shūrù)第二点时,提示工具栏将

距离和角度值,该值将随着光标的移动而改变。按

键可以移动

到要更改的值,单击“标注输入”栏下的

按钮,打开“标

注输入的设置”对话框,可以根据需要设置相关的选项。

清华大学出版社

AutoCAD 中文版机械设计教程(ji

应用(yìngyòn通g)过举(例tōngguò)输入坐标绘制四边

利用 (直线)命令绘制四边形。

结合坐标输入方法绘制的四边形

电脑基础 ·实例 ·上机系列丛

第三十页,共34页。

清华大学出版社

AutoCAD 中文版机械设计教程(

绘图命令的使用(shǐyòng)方法

要,在绘制图形前应做好相关的设置和准备。首先

应了解机械图样的基本常识、常用图纸的大小长度

单位以及

的常用坐标系,并掌握设置精

确绘图辅助功能的方法。

本章首先将详细介绍

绘图单位和图形界

限的设置,然后讲解栅格的显示、捕捉工具等精确

绘图辅助命令的使用,最后综合介绍常用于机械设

计的坐标系统和绘图命令的使用方法。

设置图形界限

设置栅格显示

应用举例 设置图形界限并显示栅格

电脑基础 ·实例·上机系列丛

第七页,共34页。

清华大学出版社

AutoCAD中文版机械设计教程(j

设置图形(túxíng)界限

绘制(huìzhì)完的 机械图纸通常要打印在

规格为 ~ 号的图纸( ~ )上,所以

应根据图纸的大小设置相应绘图范围。

在

中,可以使用(shǐyòng)多种方

VLSI电路与系统

全定制设计的产品必须有非常大的产量 才能使每块芯片成本下降。通用的微处 理器芯片等都是以全定制设计方法设计 制造的。这是因为制造厂商在设计初期 就预测到这些微处理器芯片需求量极大, 从而希望它们有尽可能好的工作性能和 最小芯片面积。

半定制设计方法

这种设计方法是厂商以给定的工艺将硅 大圆片事先制成半成品。这种半成品有 时称为母片。例如做成门阵列,这些电 路通常在芯片上排列成矩阵形式,相互 之间尚未实现电气连接。 电路设计师根据产品要求将半成品芯片 上的电路完成恰当的互连以制成产品。 门阵列设计方法中通常只需设计少数几 张掩模来完成母片上的金属电气连接。

大企业已不再可能简单地凭借以雄厚财 力为基础的大规模生产垄断IC市场。许 多有志于涉足IC的小公司凭借智力的优 势在短期内也可以为自己开辟出收益颇 丰的园地。

集成电路已是各类电子系统发 展的基础技术

计算机的发展就直接依赖于VLSI技术。 通信技术特别是电话通信(包括有线电话 和移动通信)也是受VLSI影响很大的又一 领域。 信号处理技术近年来都成为集成电路特 别是专用集成电路应用的重要领域。

①系统设计阶段; ②电路设计阶段; ③CAD设计阶段; ④样片生产阶段; ⑤批量生产阶段。

在系统设计阶段,系统设计者要提出系 统的总体指标,其中包括关键功能、子 系统划分、各子系统功能特点以及重要 的端口特性、功率消耗、封装要求以及 主要的接口要求。 既然是在系统总体规划阶段进行设计, 只宜对关键特性指标作出具体规定,其 余细节部分不作苛求,以利后面设计阶 段有较大的回旋余地。

日用电子技术和产品 军事和航天技术的发展对集成电路提出 子更为苛刻和更为迫切的要求 在为提高人们健康水平的医疗保健技术 领域内,也愈来愈多地使用了各种医用 电子设备和ቤተ መጻሕፍቲ ባይዱ成电路产品。 娱乐消费类产品。

cad工程制图第十一章

11.1.2 创建布局

1.使用“布局向导”指定布局设置

调用方法 命令:LAYOUTWIZARD 菜单:工具→向导→创建布局向导

插入→布局→创建布局 激活LAYOUTWIZARD命令,弹出 “创建布局”对话框,如图所示。

“创建布局”对话框

2.使用“来自样板的布局”创建布局 (1)调用方法 命令:LAYOUT →T 菜单:插入→布局→来自样板的布局 右击“布局”选项卡,从快捷菜单中选择“来自样板”。 (2)创建新布局过程 使用“来自样板的布局”创建新布局的步骤如下。 ① 激活“来自样板的布局”命令。 ② 在“选择文件”对话框中,选择 DWT 或 DWG 文件以从中输入布 局。 ③ 单击“打开”按钮。 ④ 在“插入布局”对话框中,选择要输入的布局。 ⑤ 新布局选项卡即被创建。要切换到新布局,请单击布局选项。 3.布局的管理 在AutoACD中,可以对“布局”进行复制、删除、重命名等操作。

11.2 视口

11.2.1.创建平铺视口

(1)功能 在模型空间或图纸空间中创建多个视口。 (2)调用方法 命令:VPORTS 菜单:视图→视口→子菜单中相应选项 图标:视口工具栏中的 (单个视口)、 (多边形视口)

2.将图形对象转变为视口

AutoCAD可以将封闭的图形对象转变为视口,操作步骤如下。 (1)在布局中绘制一个封闭的图形。 (2)单击视口工具栏中的 (将对象转换为视口)按钮。

11.1 布局

11.1.1模型空间和布局空间

1. 模型空间

模型空间是绘图和设计图纸时使用的工作空间,在该空间 中可以创建物体的视图模型以及二维或者三维造型,并且可 根据需求用多个二维或三维视图来表示物体,同时配有必要 的尺寸标注和注释等辅助工具,来完成所需要的全部绘图工 作。

利用CAD软件进行部件设计的技巧与方法

利用CAD软件进行部件设计的技巧与方法在现代工业制造中,计算机辅助设计(CAD)软件在部件设计中扮演着重要的角色。

利用CAD软件,工程师能够快速、准确地完成部件设计,并进行数字化仿真,以确保设计的可行性和优化性能。

本文将介绍一些利用CAD软件进行部件设计的技巧和方法,帮助读者更好地应用CAD软件。

1. 精确的尺寸参数设置部件设计的第一步是精确地设置尺寸参数。

CAD软件提供了各种工具和功能来帮助工程师进行尺寸参数设置,如线条、圆弧、角度等。

通过正确设置尺寸参数,可以确保设计的准确性和可行性。

2. 使用元件库CAD软件通常提供了一个元件库,其中包含了各种标准部件的模型。

利用元件库,工程师可以选择适合自己设计的部件,并进行修改和定制。

这样可以节省大量时间和精力,同时确保设计符合标准。

3. 应用曲面建模曲面建模是CAD软件中常用的功能,可以创建复杂的曲面形状。

在部件设计中,曲面建模可以用于创建流线型外形、平滑的曲面等。

掌握曲面建模的技巧,可以提高部件设计的质量。

4. 切割和布尔运算在部件设计中,切割和布尔运算是常用的操作。

通过切割和布尔运算,可以将一个部件分割成多个部分,或者将多个部分合并成一个整体。

这些操作可以帮助工程师更好地进行部件设计和组装。

5. 实时渲染和仿真CAD软件通常还提供了实时渲染和仿真功能,可以在设计过程中提供视觉反馈和性能评估。

通过实时渲染和仿真,工程师可以更直观地了解部件的外观和性能,从而进行优化和改进。

6. 参考和引用功能CAD软件的参考和引用功能可以帮助工程师在不同设计中进行快速复用和修改。

通过引用已有的部件设计和参数设置,可以提高工作效率和一致性。

7. 文件管理和版本控制CAD软件的文件管理和版本控制功能非常重要,可以帮助工程师更好地管理设计文件和变更记录。

合理使用文件管理和版本控制功能,可以避免设计错误和冲突,并确保设计的可追溯性。

总结起来,利用CAD软件进行部件设计需要掌握一些技巧和方法。

第11章-AutoCAD产品设计方法及装配图

练习1:打开附盘文件“\dwg\第11章\11-1.dwg”,如下图所示,由部件 装配图拆画零件图。

1.创建新图形文件,文件名为“筒体.dwg”。 2.切换到文件“11-1.dwg”,在图形窗口中单击鼠标右键,弹出快捷菜单, 选择【带基点复制】选项,然后选择筒体零件并指定复制的基点为A点, 如下图所示。

(1)绘制重要定位线及作图基准线。 (2)绘制出主要零部件的大致形状。 (3)确定主要零部件间的位置关系。 (4)确定传动方案及传动路线。

11.1.2 设计方案的对比及修改

绘制了初步的总体方案图后,就要对方案进行广泛且深入的讨论,发现 问题,进行修改。对于产品的关键结构及重要功能,更要反复细致地讨论, 争取获得较为理想的解决方案。 在方案讨论阶段,可复制原有方案,然后对原方案进行修改。将修改后的 方案与旧方案放在一起进行对比讨论,效果会更好。下图显示了原设计方 案与修改后的方案。

3.切换到图形“装配检验.dwg”,在图形窗口中单击鼠标右键,弹出快捷菜 单,选择【粘贴】选项,结果如下图所示。

4.切换到图形“11-2-B.dwg”,关闭标注层。在图形窗口中单击鼠标右键, 弹出快捷菜单,选择【带基点复制】选项,复制零件主视图。

5.切换到图形“装配检验.dwg”,在图形窗口中单击鼠标右键,弹出快捷 菜单,选择【粘贴】选项,结果如左图所示。

3.切换到文件“筒体.dwg”,在图形窗口中单击鼠标右键,弹出快捷菜单, 选择【粘贴】选项,结果如下图所示。

4.对筒体零件进行必要的编辑,结果如下图所示。

11.1.5 “装配”零件图以检验配合尺寸 的正确性

复杂机器设备常常包含成百上千个零件,这些零件要正确 地装配在一起,就必须保证所有零件配合尺寸的正确性,否则 就会产生干涉。若技术人员按一张张图纸去核对零件的配合尺 寸,工作量非常大,且容易出错。怎样才能更有效地检查配合 尺寸的正确性呢?可先通过AutoCAD的复制及粘贴功能将零 件图“装配”在一起,然后通过查看“装配”后的图样就能迅 速判定配合尺寸是否正确。

CAD软件中的组件设计和装配技巧

CAD软件中的组件设计和装配技巧CAD(Computer-Aided Design,计算机辅助设计)软件是现代工程领域中不可或缺的工具。

在CAD软件中,组件设计和装配是其中的重要环节。

本文将介绍一些CAD软件中的组件设计和装配技巧,帮助读者更加高效地使用CAD软件。

首先,组件设计是CAD软件中的基础步骤。

在进行组件设计时,首先要明确设计的目标和要求。

根据设计要求选择适当的几何图形,并进行绘制。

在CAD软件中,可以利用绘图工具绘制直线、圆弧、多边形等几何图形。

绘制完成后,可以对几何图形进行编辑,包括缩放、旋转、移动和镜像等操作。

通过这些编辑功能,可以快速调整组件的形状和尺寸。

其次,装配是CAD软件中的另一个重要环节。

在进行装配时,需要将不同的组件组合在一起,形成一个完整的装配体。

在CAD软件中,可以通过装配功能实现组件的对位和连接。

首先,需要设置装配体的参考坐标系,以便准确定位组件。

然后,通过装配功能可以将组件按照设计要求进行定位和连接。

在装配过程中,可以利用CAD软件提供的对位和约束功能,确保组件之间的相对位置和运动。

此外,CAD软件还提供了一些高级的组件设计和装配技巧,进一步提高工作效率和设计质量。

其中之一是参数化设计技术。

通过参数化设计,可以将组件的尺寸和形状与参数关联起来,便于后续的修改和调整。

在CAD软件中,可以通过定义参数、应用公式和设置约束等方式实现参数化设计。

另外,CAD软件还支持组件的属性管理。

可以给组件添加属性信息,包括名称、材料、重量等,便于后续的管理和查询。

在使用CAD软件进行组件设计和装配时,也要注意一些常见的问题和注意事项。

首先,要保持良好的组织结构和命名规范。

在进行组件设计时,应该根据功能和用途合理地划分组件,并给组件命名。

这样可以方便后续的管理和维护。

另外,要定期进行文件的备份和版本管理,以防数据丢失或混乱。

此外,要保持CAD软件的更新和升级,以获得更好的功能和性能。

VLSI设计与制造

第一章VLSI工艺设计基础概念1.为什么CMOS(含BiCMOS)工艺成为VLSI主流工艺?其最大特点是什么?在微电子技术领域中,集成电路的制造有两个主要的实现技术:双极技术和MOS技术。

CMOS以其结构简单,集成度高,耗散功率小等优点,成为当今VLSI制造的主流技术。

其最大的特点是耗散功率小。

2.双极工艺还有用武之地吗?双极技术是以NPN和PNP 晶体管为基本元件,融合其他的集成元件构造集成电路的技术方法。

双极器件以其速度高和驱动能力大,高频、低噪声等优良特性,在集成电路的设计制造领域,尤其是模拟集成电路的设计制造领域,占有一席之地。

但双极器件的耗散功率比较大,限制了它在VLSI系统中的应用。

3.以你的体会,你认为集成电路设计师应具备哪些基本技术基础?设计者必须具备下列的技术基础:电路与逻辑设计技术基础,器件与工艺技术基础,版图设计技术基础和集成电路计算机辅助设计技术基础。

除此之外,设计者还应具备对电路、逻辑、器件、工艺和版图的分析能力。

4.简要说明描述集成电路技术水平5大指标的含义,当前国内和国际上集成电路产业在特征尺寸及晶园尺寸方面各达到什么水平?集成度是以一个IC芯片所包含的元件(晶体管或门数)来衡量;特征尺寸,特征尺寸定义为器件中最小线宽(对MOS 器件而言,通常指器件栅电极所决定的沟道长度的几何长度);芯片面积大小;晶片直径大小;封装引脚数多少。

5.微米级、亚微米级、深亚微米级各指什么尺寸,举例说明。

微米(micro-M)(3um、2um[1985年],1.5um、1um[1989年])亚微米(submicro-SM)(0.7um、0.5um[1993年])深亚微米(deep submicro-DSM)(0.35um [1997年],0.25um、0.18[2001年],0.13um)超深亚微米级(very deep submicro-VDSM)或亚0.1um [2005]6.简要说明深亚微米电路设计对设计流程的影响。

CAD产品设计学习目录

CAD产品设计学期计划第1章建模流程1.1 快速入门1.1.1 开始一个Autodesk Inventor的设计进程1.1.2 Autodesk Inventor工作流程概念1.1.3 Autodesk Inventor工作流程1.1.4 零件文件1.1.5 部件文件1.1.6 表达视图文件1.1.7 工程图文件1.1.8 使用模板文件1.2 Autodesk Inventor中的项目1.2.1 项目概念1.2.2 项目文件1.2.3 项目设置1.2.4 创建项目1.2.5 编辑项目练习1-1 Autodesk Inventor中的项目1.3 用户界面1.3.1 浏览器1.3.2 工具面板1.3.3 工具栏1.3.4 菜单构成1.3.5 快捷键1.3.6 三维指示器练习1-2 用户界面第2章草图应用基础2.1 创建草图2.1.1 草图环境2.1.2 草图工具2.1.3 创建草图原则2.1.4 草图坐标系2.1.5 精确输入2.1.6 编辑草图练习2-1 创建草图2.2 约束草图2.2.1 Autodesk Inventor中的草图约束2.2.2 几何约束2.2.3 规划约束2.2.4 显示或删除约束2.2.5 在草图中使用构造几何图元练习2-2 约束草图2.3 标注草图2.3.1 参数化尺寸2.3.2 计算尺寸2.3.3 添加尺寸的一些选项2.3.4 自动标注尺寸2.3.5 显示尺寸2.3.6 草图标注尺寸原则练习2-3 标注草图尺寸2.4 “二维草图”工具2.4.1 二维几何图元线型和尺寸样式2.4.2 创建二维几何图元线型和尺寸样式的工具2.4.3 如何使用二维几何图元草图工具?练习2-4 “二维草图”工具栏练习2-5 草图挑战练习第3章创建草图特征3.1 草图特征简介3.1.1 简单的草图特征3.1.2 退化和未退化的草图3.1.3 草图和轮廓3.1.4 共享草图的特征练习3-1 草图特征初步3.2 使用草图平面3.2.1 草图工具3.2.2 在实体表面上定义草图3.2.3 直接参考模型边界3.2.4 创建参考几何图元练习3-2 应用草图平面3.3 创建拉伸特征3.3.1 拉伸特征概述3.3.2 “拉伸”工具3.3.3 特征间的布尔运算——添加、切削、求交3.3.4 指定终止方式3.3.5 编辑特征练习3-3 创建拉伸特征3.4 创建旋转特征3.4.1 简单旋转轮廓3.4.2 旋转工具3.4.3 创建旋转特征3.4.4 特征关系——添加、切削、求交3.4.5 编辑旋转特征练习3-4 创建旋转特征练习3-5 创建草图特征第4章创建工作特征4.1 工作平面4.1.1 默认的工作平面4.1.2 工作平面命令4.1.3 工作平面示例4.1.4 工作平面的显示属性练习4-1 工作平面4.2 工作轴4.2.1 默认工作轴4.2.2 工作轴命令4.2.3 工作轴示例4.2.4 工作特征显示特性练习4-2 工作轴4.3 工作点4.3.1 原点工作点4.3.2 工作点命令4.3.3 固定工作点4.3.4 其他工作点的创建练习4-3 工作点第5章创建放置特征5.1 圆角特征5.1.1 倒圆工具5.1.2 等半径模式5.1.3 变半径模式5.1.4 过渡模式5.1.5 “圆角”对话框中的扩展选项 5.1.6 创建等半径圆角的过程5.1.7 创建变半径圆角的过程5.1.8 编辑圆角特征练习5-1 圆角特征5.2 孔和螺纹特征5.2.1 关于孔特征5.2.2 使用打孔工具建立孔的好处5.2.3 打孔工具5.2.4 创建孔特征5.2.5 螺纹特征练习5-2 创建螺纹特征5.3 抽壳特征5.3.1 抽壳工具5.3.2 建立壳特征的过程练习5-3 抽壳特征5.4 阵列特征5.4.1 什么是阵列?5.4.2 环形阵列工具5.4.3 创建环形阵列5.4.4 矩形阵列工具5.4.5 创建矩形阵列练习5-4 阵列特征5.5 创建和使用颜色样式练习5-5 创建和使用颜色样式第6章装配建模基础6.1 装配模型基础6.1.1 装配模型概念6.1.2 装配环境6.1.3 部件工具面板练习6-1 装配模型基础6.2 装配浏览器6.2.1 在位激活6.2.2 可见性控制6.2.3 装配重排序6.2.4 装配重新构造6.2.5 浏览器过滤器6.2.6 浏览器显示模式6.2.7 启用零部件6.2.8 固定零部件练习6-2 装配浏览器6.3 在装配中装入零部件6.3.1 装入零部件工具6.3.2 定位零部件来源6.3.3 替换零部件练习6-3 在装配中装入零部件6.4 在装配中创建零部件6.4.1 创建在位零部件6.4.2 在装配中使用工作特征6.4.3 使用二维草图6.4.4 使用投影边和特征练习6-4 在装配中创建零部件6.5 移动零部件6.5.1 自由度6.5.2 自由拖动6.5.3 约束拖动6.5.4 约束驱动6.6 移动和旋转零部件练习6-5 移动零部件6.7 约束零部件6.7.1 添加约束6.7.2 基本约束6.7.3 查看约束6.7.4 编辑装配约束练习6-6 约束零部件6.8 自适应零部件6.8.1 自适应特征简介6.8.2 创建自适应零部件的方法 6.8.3 自适应草图6.8.4 自适应特征6.8.5 装配中的自适应情况6.8.6 使用装配约束6.8.7 使用自适应零件的注意要点练习6-7 自适应零部件6.9 装配分析6.9.1 干涉分析工具6.9.2 面分析工具6.9.3 搜索定位零部件练习6-8 装配分析6.10 表达视图6.10.1 创建表达视图6.10.2 创建位置参数和轨迹6.10.3 播放表达视图练习6-9 表达视图练习6-10 装配模型基础第7章创建工程图7.1 设置制图标准7.1.1 制图标准7.1.2 文本样式7.1.3 尺寸样式7.1.4 文档设置7.1.5 工程图模板练习7-1 设置制图标准7.2 图层7.2.1 什么是图层?7.2.2 创建和管理图层工具7.2.3 如何创建和使用图层?练习7-2 图层的控制7.3 工程图资源7.3.1 编辑默认图纸7.3.2 选用图纸格式作为图纸布局 7.3.3 创建多张图纸7.3.4 创建图纸格式7.3.5 创建自定义图框7.3.6 创建自定义图框的过程7.3.7 标题栏格式7.3.8 编辑标题栏格式7.3.9 编辑标题栏格式7.3.10 定义一个标题栏7.3.11 编辑定义的标题栏练习7-3 工程图资源7.4 投影视图7.4.1 创建基础视图7.4.2 创建投影视图7.4.3 编辑基础视图和投影视图练习7-4 基础视图和投影视图7.5 剖视图7.5.1 创建剖视图7.5.2 装配剖视图7.5.3 编辑剖视图练习7-5 剖视图7.6 局部视图7.6.1 创建局部视图7.6.2 创建局部视图的过程7.6.3 编辑局部视图练习7-6 局部视图7.7 斜视图7.7.1 创建斜视图7.7.2 创建斜视图的过程7.7.3 编辑斜视图7.7.4 重对齐斜视图练习7-7 斜视图7.8 打断视图7.8.1 创建打断视图7.8.2 创建打断视图的过程7.8.3 编辑打断视图练习7-8 打断视图7.9 局部剖视图7.9.1 创建局部剖视图7.9.2 编辑局部剖视图练习7-9 局部剖视图7.10 管理视图7.10.1 对齐视图7.10.2 删除视图7.10.3 在图纸间复制视图7.10.4 在图纸间移动视图练习7-10 管理视图7.11 工程图标注7.11.1 检索模型尺寸7.11.2 创建尺寸练习7-11 标注视图7.12 放置通用注释7.12.1 标注孔7.12.2 标注中心线和中心标记 7.12.3 文本和指引线练习7-12 放置通用注释7.13 明细表7.13.1 缺省的明细表样式7.13.2 如何创建明细表7.13.3 手动放置引出序号7.13.4 自动引出序号7.13.5 自动引出序号工具7.13.6 怎样添加自动引出序号?练习7-13 创建明细表第8章高级草图应用8.1 共享草图8.1.1 共享草图8.1.2 创建共享草图几何图元的过程练习8-1 共享草图8.2 切片观察8.2.1 切片观察8.2.2 使用“切片观察”模式的过程练习8-2 使用“切片观察”模式8.3 创建草图8.3.1 在其他零件表面上创建草图8.3.2 参考跨零件的几何图元8.3.3 与跨零件几何投影有关的选项应用8.3.4 静态和关联参考几何图元的特点8.3.5 静态跨零件投影几何的过程8.3.6 关联跨零件投影的过程练习8-3 在其他零件的表面上创建草图8.4 尺寸显示、关系式和等式(参数)8.4.1 尺寸显示8.4.2 建立尺寸关系式8.4.3 函数、前缀和代数运算符练习8-4 使用等式和不同的尺寸显示样式8.5 二维样条曲线8.5.1 样条曲线的附加用途8.5.2 如何创建样条曲线8.5.3 样条曲线编辑选项练习8-5 创建和编辑二维样条曲线8.6 三维草图8.6.1 创建三维直线和三维样条曲线8.6.2 过渡工具8.6.3 包含几何图元工具8.6.4 三维相交工具8.6.5 三维草图约束8.6.6 三维草图环境中的定位特征练习8-6 创建和使用三维草图几何图元第9章高级零件建模9.1 加强筋和隔板9.1.1 什么是加强筋和隔板?9.1.2 如何创建加强筋和隔板?练习9-1 创建加强筋和隔板特征9.2 放样特征9.2.1 什么是放样?9.2.2 如何创建放样特征?练习9-2 创建放样特征9.3 分割特征9.3.1 分割零件或面9.3.2 如何使用分割工具?练习9-3 分割零件或零件面9.4 镜像特征9.4.1 镜像零件特征9.4.2 如何创建镜像零件特征?练习9-4 镜像零件特征9.5 曲面9.5.1 什么是曲面?9.5.2 输入三维几何图元9.5.3 如何输入三维几何图元?9.5.4 如何在零件模型环境中使用曲面?练习9-5 输入并使用曲面9.6 可视化9.6.1 零件或零件面的颜色9.6.2 纹理图和零件材料9.6.3 阴影和背景图像9.6.4 透视观察练习9-6 使用颜色纹理图和阴影9.7 iPart9.7.1 什么是iPart?9.7.2 创建iPart练习9-7 创建和使用iPart9.8 iFeature 4029.8.1 什么是iFeature?9.8.2 iFeature存储在哪里?9.8.3 如何创建iFeature?9.8.4 如何插入iFeature?练习9-8 创建和使用iFeature9.9 创建凸雕特征9.9.1 什么是凸雕特征?9.9.2 如何创建凸雕/凹雕特征?练习9-9 创建凸雕特征9.10 创建贴图9.10.1 什么是贴图特征?9.10.2 如何创建贴图特征?练习9-10 创建贴图特征第10章高级装配建模10.1 设计视图表达10.1.1 什么是设计视图表达?10.1.2 设计视图表达中存储的信息10.1.3 设计视图表达的菜单选项10.1.4 在子装配中应用设计视图表达10.1.5 创建和使用设计视图表达10.2 标准件库练习10-1 使用标准件库10.3 阵列零部件10.3.1 什么是阵列零部件?10.3.2 如何创建阵列零部件?练习10-2 创建零部件阵列10.4 自适应设计技术10.4.1 什么是自适应?10.4.2 怎样创建自适应零件?10.4.3 如何在特征特性中设置自适应?10.4.4 何时适用或不适用自适应?10.4.5 关闭自适应以改进性能10.4.6 零件在装配中是否使用过自适应练习10-3 创建自适应零件10.5 模拟运动10.5.1 什么是运动约束?10.5.2 运动约束工具10.5.3 如何创建过渡约束?10.5.4 如何驱动装配约束?练习10-4 驱动约束10.6 衍生零部件10.6.1 什么是衍生零部件?10.6.2 衍生零部件工具10.6.3 如何创建衍生零件或部件?练习10-5 创建衍生零件10.7 装配特征10.7.1 什么是装配特征?10.7.2 如何创建装配特征?10.7.3 编辑装配特征练习10-6 装配特征10.8 焊接件10.8.1 什么是焊接件?10.8.2 焊接环境和工具练习10-7 创建焊接件10.9 资源中心10.9.1 关于资源中心10.9.2 访问“资源中心”中的零件10.9.3 插入“资源中心”的零件第11章设计加速器11.1 创建螺栓联接11.1.1 关于螺栓联接11.1.2 创建螺栓联接11.1.3 如何创建和放置螺栓联接件?11.2 编辑螺栓联接11.2.1 修改螺栓联接11.2.2 如何修改螺栓联接?11.3 轴零部件生成器11.3.1 关于轴零部件11.3.2 轴工具11.3.3 创建和编辑轴零部件11.4 设计加速器中的计算器11.4.1 工程和机械计算器11.4.2 访问设计加速器工具第12章钣金设计基础12.1 如何设计钣金件?12.1.1 使用Autodesk Inventor设计钣金零件12.1.2 钣金设计基础12.1.3 钣金零件设计的共同要求12.2 钣金的概念和术语12.2.1 钣金件的概念和术语12.2.2 钣金加工设备12.2.3 Autodesk Inventor中用于钣金设计的工具12.3 钣金件设计方法12.3.1 钣金件的设计方法12.3.2 使用两种不同的设计方法练习12-1 创建钣金零件第13章专业模块简介13.1 三维管路设计简介13.1.1 使用三维布管功能可以执行哪些任务?13.1.2 三维布管部件与标准Inventor部件有哪些不同?13.1.3 管件、管材和软管管线能否在其他附加模块应用程序部件中运行?13.1.4 标准Autodesk Inventor安装如何处理三维布管数据?13.2 三维电缆设计简介13.2.1 可以在三维布线环境中执行哪些任务?13.2.2 在部件中放置和创建线束对象的操作过程是什么?13.2.3 三维布线浏览器的装配层次13.3 应力分析概述13.3.1 了解应力分析的工作方式13.3.2 应力分析使用环境13.3.3 应力分析的过程第14章 Inventor Studio14.1 关于Inventor Studio14.1.1 定义14.1.2 “渲染图像”工具14.2 使用Inventor Studio演示动画14.2.1 Inventor Studio动画14.2.2 如何创建渲染动画?。

CAD软件中的装配设计技巧

CAD软件中的装配设计技巧CAD软件是工程师在设计和制造过程中的得力助手。

在CAD软件中,装配设计是一个关键的环节,它涉及多个零件的组合和配合。

本文将介绍一些CAD软件中的装配设计技巧,帮助工程师们更高效地进行设计工作。

1. 使用模块化设计方法:模块化设计方法是将整个装配过程划分为若干个独立的模块,每个模块负责一部分功能。

通过模块化设计,可以减少装配时的冲突和错误,同时提高设计的可重复性。

在CAD软件中,可以使用组件库来管理和组织模块,这样可以方便地进行装配和修改。

2. 设计标准化零件库:在CAD软件中,建立一个标准化的零件库是非常重要的。

通过建立零件库,可以提高零部件的共享和复用,减少设计时间和成本。

在零件库中,应该包含常用的标准零件、常用的连接件以及各种常见的配件。

通过使用零件库,可以快速地进行设计和装配工作。

3. 使用装配约束:在CAD软件中,装配约束是非常重要的。

通过使用装配约束,可以确保装配件之间的准确配合和运动关系。

可以使用各种类型的装配约束,例如:定位约束、对齐约束、角度约束等。

在设置装配约束时,应注意各个装配部件之间的相互关系和功能要求。

4. 进行动态分析和碰撞检测:在进行装配设计时,动态分析和碰撞检测是非常重要的。

通过进行动态分析和碰撞检测,可以预测装配件之间的碰撞和冲突,并及时进行修正。

在CAD软件中,可以使用动态模拟和碰撞检测工具来进行分析和检测。

通过使用这些工具,可以避免装配过程中的错误和问题。

5. 进行装配顺序规划:在进行装配设计时,合理的装配顺序规划是非常重要的。

通过合理的装配顺序规划,可以减少装配过程中的冲突和错误,并提高装配效率。

在CAD软件中,可以使用装配顺序规划工具来进行规划和优化。

通过使用这些工具,可以优化装配顺序,提高装配效率。

6. 进行装配分解和分组:在进行复杂装配设计时,装配分解和分组是非常有帮助的。

通过装配分解和分组,可以将复杂的装配任务分解为多个简单的装配任务,并进行独立的设计和装配。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Chapter11Chip AssemblyT HE PROCESS of wiring up pre-designed modules to make a complete chip core,or taking afinished core and routing it to the chip padsis known as chip assembly.Cadence has yet another tool that is designed specifically for this set of tasks known as the Cadence Chip As-sembly Router(ccar)which is part of the IC Craftsman(ICC)tool set. This tool will route between large pre-designed blocks which are not placed on a regular grid.This makes it fundamentally different than SOC En-counter which wants to place small cells on afixed grid.The blocks that are routed by ccar could be blocks that are placed and routed by SOC En-counter,or could also be blocks that are designed by hand or by other tools (i.e.custom datapath circuits,memories,or other dense regular arrays).Al-though there are certainly more features of ccar then are described here,we use ccar strictly for routing.That is,the user places the blocks by hand, connects the global power and ground nets,then uses ccar to connect the signal wires between those large blocks.The ccar tool is also used to route betweenfinished cores and the pad ring.11.1Module Routing with ccarThe ccar tool,unlike other tools we’ve used so far,is not invoked directly. Instead it is used in conjunction with the Cadence Composer and Virtuoso tools.The overall process is:1.Make a schematic that contains your modules connected together.In-put and output pins should be used to indicate signals that enter and leave the collection of modules.e Virtuoso-XL to generate a new layout based on that schematic.CHAPTER11:Chip Assembly Draft October30,20063.Place the modules by hand in the layout view.4.Place the IO pins that were defined in the schematic(and generated inthe layout)in the desired spots in the layout.5.Connect vdd!and gnd!so that the modules are connected to a com-mon power network.6.Export the layout view to ccar for signal routing7.Route the signal nets in ccar8.Import the routed module back to Virtuoso-XL.Then DRC,extract,and LVS.So,to start out you need:1.The modules that you will be connecting need to have layout viewsthat have all the connection points marked with shape pins of the right type(metal1,metal2,or metal3)and named the same things as on the symbol(blocks routed by SOC Encounter already have these).2.For each cell you also need a symbol view of that cell that has thesame pins on the interface of the symbol that are in the layout(cell blocks imported from the structural Verilog view generated by SOC Encounter have these symbols too).3.You need a schematic showing the connection of parts that you wantto route together.That is,you make a schematic that includes in-stances of the parts that you want to use,and all the connections be-tween them.This is a good thing to have in general because you’ll need it to simulate the functionality of the schematic and for LVS anyway.It’s also what tells ccar which signals it should route and to where.4.A rulesfile for the IC Craftsman(icc)ccar router called icc.rul.Copy thisfile from/uusoc/facility/cad common/local/class/6710/cadence/ICC to the di-rectory from which you start cad-ncsu.5.Also copy the do.dofile from that same class directory to the directoryfrom which you start cad-ncsu.You’ll need both of these later when you start up ccar.What this process will do is generate a connected layout that corre-sponds to the schematic.You will do the placement by hand,but the router340Draft October30,200611.1:Module Routing with ccarFigure11.1:Starting schematic showing the three connected modules will connect everything.For this example I’ll take three modules that I’ve previously placed and routed with SOC Encounter:the moore example from Chapter8,the counter example from Chapter10,and the controller state machine from the MIPS example in the Harris/Weste CMOS text-book[1].Connecting these cells together makes absolutely no functional sense,but it does show how three pre-assembled modules can be connected together with ccar.Each of these three examples has been imported into icfb using the procedure described in Chapter10,Section10.1.12.This means that I have(among other things)layout,schematic,and symbol views of each of these modules that I can use to make my new schematic as a starting point.The example starting schematic is shown in Figure11.1. Note that this schematic can be in a whole new library if you like in order to keep things separated.11.1.1Preparing a Placement with Virtuoso-XLIn this part of the process you will generate a layout from the schematic and drag the components to where you want them placed.Start by opening the schematic view.From the schematic view select Tools→Design Synthesis →Virtuoso-XL.Virtuoso-XL is just Virtuoso with some extra features enabled.In this step you will be asked if you want to open an existing341CHAPTER11:Chip Assembly Draft October30,2006cellview or make a new one.It’s talking about the layout view that it’s aboutto generate.I’m assuming that you have no layout for the current schematicyet so you’ll want to make a new one.If you have an existing layout butwant to start over,this is where you can start over with a new layout view.This command will open a new Virtuoso-X window,and resize and replacethe other windows on your screen.You may need to move things aroundafter this process to see everything.In the new Virtuoso-XL window select Design→Gen From Source...This will generate an initial layout based on the schematic as the sourcefile.The dialog box is shown in Figure11.2.The dialog lets you pick alayer for each external IO pin.This will determine what layer the end of thewire will be when the router creates it.If you have a lot of pins it’s fasterto choose one layer as default and apply that default to everything.Youcan then change individual pins to something else if you like.Make sureyou choose a reasonable routing layer for your pins like one of the metallayers.The default layer before you change things is likely to be somethingunreasonable like nwell.After you execute the Gen From Source you will see that the layout has a large purple box which defines the placement area(it’s a box of typeprBoundary),and your cells scattered outside that box.This view is shownin Figure11.3.You can’t see them until you zoom in,but all the IO pins de-fined in your schematic are just below the lower left corner of the prBound-ary box.Now that you have in initial layout in the Virtuoso-XL window you You may need to makeprBoundary an active layer using the Edit→Set Valid Layers menu in the LSW(LayerSelection Window)in order to resize that layer.can pick them up and move them to where you want them.Your job is to place both the modules and the IO pins inside the prBoundary square. You can also resize the prBoundary if you’d like a smaller or differently shapedfinal module.When you move the cells connecting lines show up that show you how this component is connected to the other.Also,when you select a cell in the layout window that same cell is highlighted in the schematic window.This is very handy forfiguring out which cell in one window corresponds to which cell in the other.Placing the IO pins is a little tricky just because they’re likely to be very small compared with the modules.Ifind that it’s easiest if I zoom in to the lower left corner of the prBoundary where the pins are and select a pin. Then use the move hotkey(m)to indicate that you’re about to move the pin and click near the pin to define a starting point.Now you can use f and the zoom keys(Z and ctl-z)to change views while you’re still moving the pin.You can also see the connecting line which shows where the pin will eventually be connected which can guide you to a good placement.When you’ve placed all the modules and pins you can look at the con-342Draft October30,200611.1:Module Routing with ccarFigure11.2:The Gen From Source dialog box343CHAPTER11:Chip Assembly Draft October30,2006Figure11.3:Initial layout before module and IO placement344Draft October30,200611.1:Module Routing with ccarFigure11.4:A placement of modules and IO pins with unrouted nets turned onnectivity using the Connectivity→Show Incomplete Nets option in Virtuoso-XL.Because nothing is routed yet,this shows all the connections that will eventually be made by ccar.A placement of the modules and pins is shownin Figure11.4.Now you should connect the power and ground nets of the various mod-ules in your layout.If you don’t do this now you might run out of spaceto do it later once the signals are routed.In Figure11.5I’ve connected the rings of the modules together with fat9.9micron wires to match the pitchof the power and ground rings that were placed by SOC Encounter.Notice that I’ve kept the routing conventions intact.That is,metal1is used hori-zontally and metal2is used as a vertical routing layer.Because ccar will also use these conventions it’s important to keep that in mind so as not to restrict the routing channels.At this point you should save the layout and run DRC to make sure that everything is all right before you send the layout345CHAPTER11:Chip Assembly Draft October30,2006to the router tool.Make sure that your module placement,IO pin placement,prBoundary size and shape,and power routing is how you want it.You can play aroundwith this a lot to get things looking just right before you send it to the router.The router willfill in the rest of the signal routing for you.Of course,ifyou’ve made your prBoundary too small and left too little room for signalrouting you might have to redo thefloorplan later!11.1.2Invoking the ccar routerNow that you have a placed and power-routed layout you can send this tothe e the Routing→Export to Router command.The dialogbox is shown in Figure11.6.Everything should befilled in correctly,but Remember to copyicc.rul and do.do from the class ICC directory before you run this step.make sure that the Use Rules File box is checked and that the icc.rulfile is specified.Also make sure that the Router that is specified is Cadence chip assembly router.Clicking OK will start up ccar on your cell.A new ccar window will pop up that shows your layout with the not-yet-connected nets shown as in Figure11.7.Look at the log information that show up in the shell you used to start cad-ncsu and make sure that there are no issues with ccar as it starts up. Unless you have specified your pins strangely back in the Gen From Source step,it’s unlikely that there will be issues here,but you should always check.Thefirst thing you should do is execute a dofile.This will set up aThis may not actually bestrictly necessary,but it has seemed to ease some problems in the past sofor historical reasonsI’m leaving thisinstruction in.few things in the icc tool so you won’t have to do them by hand.Select File →Execute Do File and tell it to execute do.do(which you have already copied into your current directory).Now,if you want to,you can select the layers used by ccar to do the routing.Everything is set up so that the router will use metal1as a horizontal layer,metal2as a vertical layer,and metal3as a horizontal layer.If you want to change this,or restrict the router to not use a certain layer,you can do that now.Select the layer icon,which is the icon with the three rectangles overlapping on the left side of the ccar window.The pop-up will look like Figure11.8.The icons next to the metal1,metal2,and metal3layers show what direction they will be routed in.If you want to change the direction or restrict the router from using that layer,you can change that icon.The circle with the slash means not to use that layer as a routing layer.Note that the vias are marked as don’t use This doesn’t mean that the router won’t put in vias(it will),it just means it won’t make a wire out of the via layer.There’s really nothing you need to change here unless you want to.The next thing you might want to do is change the costs of various rout-ing features.This is a mechanism to control how the router does the routing.346Draft October30,200611.1:Module Routing with ccarFigure11.5:Layout showing placement and power routing before routing347CHAPTER11:Chip Assembly Draft October30,2006Figure11.6:Export to Router dialog box348Draft October30,200611.1:Module Routing with ccarFigure11.7:Initial ccar window349CHAPTER11:Chip Assembly Draft October30,2006Figure11.8:Layer configuration dialog box350Draft October30,200611.1:Module Routing with ccarFigure11.9:Routing cost factor dialog boxChoose Rules→Cost/taxes and you can modify the relative costs of vari-ous routing features.The dialog box is shown in Figure11.9.The-1means that there is no penalty.Putting in any number raises the cost penalty in the routing algorithm and makes it less likely that the router will behave in that way.For example,if you feel strongly that the routing layers should stick with the h-v-h routing plan,then add some penalty for wrong-way routing.I haven’t played with this enough to know how changing this really affects the circuit.Feel free to play around here and see what happens.Leaving it alone will result in good,generic results.Normally you want ccar to route all the signal pins.However,if you want it to leave some wires unrouted(because you want to route them by hand for some reason)you can use the Edit→[UN]Fix Nets tofix the nets that you don’t want ccar to route.There are clearly many many more options that you can play with,but these are the basics.Feel free to explore the others.Once you’vefinished setting things up you can tell ccar to route the nets.This is a multi-step process:1.Select Autoroute→Global Route→Local Layer Direction andtell it to get its layer directions from the Layer Panel.2.Now select Autoroute→Global Route→Global Route and tell351CHAPTER11:Chip Assembly Draft October30,2006it how many routing passes you’d like it to try before giving up(the default of3is probablyfine unless you have a very congested cir-cuit).This may not look like it’s doing anything if the layout is small.It’s making some notes for the global routing of signals.If you get warnings about non-optimal results,go ahead and click OK.3.Now select Autoroute→Detail Route→Detail Router to get allthe detailed wires.Again you tell it how many passes to take.The tighter the layout and the smaller the area you’ve specified,the more passes it’s likely to take to get a successful route.If you have lots of room then it will probably only take1-5passes.A tighter routing situation may require25or more passes.This is a fun step because you get to watch as the router tries to connect everything.4.If you don’t get a successful route,you’ll have go to the costs andreduce the costs of some of the routing features,or go back to the lay-ers window and give it more layers to use.You may even need to go back to the layout and give the router some more room by increasing the space around the modules or increasing the size of the prBound-ary.This example has(relatively speaking)acres of routing room so there’s no problem.In fact,it routes correctly in the second pass.5.If you do get a successful route you need to clean up after the route.The router may have introduced errors in the circuit and the routes may be a little crooked with unnecessary jogs.Select Autoroute→Clean to clean up things.This will take a post-pass on the routing and clean up messy bits.6.You also need to remove notches.These are little gaps in the routingthat got left in because of corners being turned,or other features of the routing.Select Autoroute→Postroute→Remove Notches.Thefinal routed circuit is shown in Figure11.10.Now you’re done.Save the routed circuit by selecting File→Write→Session.You want to save your work as a session so that you can import it back into Virtuoso and use it as layout.Once you’ve saved your session you can quit ccar.You can see that this isn’t the best looking routing in the world,but it is connected according to the connections shown in the schematic,and it was done automatically.When you saved the session in ccar you should have seen the routing updated in the Virtuoso-XL layout window.If it didn’t you can import it with the Routing→Import from Router menu.You should save this view in Virtuoso-XL.This is now just like any other layout view.You can use it in your chip,or generate a symbol and use it at another level of your hierarchy,and even use it with ccar at another level of the hierarchy.The352Draft October30,200611.1:Module Routing with ccarFigure11.10:Final routed circuit(shown in Virtuoso window)353CHAPTER11:Chip Assembly Draft October30,2006only difference between this and a layout view that you did by hand is thatafter you did a placement of the cells by hand in this example,the ChipAssembly Router did the interconnect for you.Once you have the layout back in Virtuoso,you will want to do the usual things to it:DRC and LVS for example.Thefirst thing you should do is runDRC to make sure that the autorouted circuit does not have any new DRCerrors in it.Although the autorouter is good,it’s not perfect and it may leavea few small errors around.In particular,you may get metal spacing errorsat the point where the autorouted wires connect to the SOC-routed block.This is because the connections that SOC uses are shape pins that use pintype material instead of drawing type material.You can see this if you openthe SOC-routed layout and zoom in close to one of the IO pins.The IO SOC uses pin layers forthe IO pins that itgenerates,and an extracted view uses net purpose layers for theextracted nets.pin that SOC put in looks different than real metal.Each of the layers in Cadence is really a layer-purpose pair.That is,there is a set of layers,and a set of purposes,and each layer can be paired with a purpose.Normally you’re using drawing purpose.The layers in your LSW have a little dg after them to show that they’re drawing-purpose layers.If you do have metal spacing errors,you canfix them by hand by putting a small piece of metal over the mistake,or you canfix them by editing your SOC layout.To do this,open the SOC layout.Then use the Edit→Search dialog tofind all rectangles on layer metal1pn(or metal2pn or metal3pn depending on where you put your pins),and change them to layer their dg versions.This will convert them to drawing purpose layers and the DRC process should stop complaining.If you have any other DRC errors,you need to check them out andfix them.Now you can LVS against the schematic that you used to define the connectivity in thefirst place.This is done in the usual way generate an extracted view,LVS the extracted against the schematic.The only thing you need to be careful of here is to make sure vdd!and gnd!were connected before you try to LVS.You will need to connect these supply nets by hand (which you should have done before you routed the module).11.2Core to Pad Frame Routing with ccarIn this section I will walk through the procedure for using icc to connectActually,it does matterfor a grade in the class.Everyone should connect their core to the pads for thefinal report even if the core isn’t working completely yet!your chip core to a pad frame.Before you start the process of connecting your core,you need a complete core!A complete core is the complete guts of your chip with all the components connected,all the vdd!and gnd!lines connected,and simulated for functionality.If you don’t have a functional, simulated,complete core,then it doesn’t matter whether it has pads around354Draft October30,200611.2:Core to Pad Frame Routing with ccarFigure11.11:Symbol for the Three Blocks example coreit!For this example,I’ll start with a core made up of the three blocks from the previous Section which were placed by hand in Virtuoso-XL and routed by ccar.Your core may be completely placed and routed by SOC,or it might include blocks routed by ccar or it might be completely custom.The point is to start with a completed core.A complete core should have(at least)layout,schematic,and symbol views,should have vdd!and gnd! connected in the core,and should pass DRC and LVS.The three-block ex-ample from Section11.1has all of these characteristics.The layout was seen in Figure11.10and the schematic in Figure11.1.The symbol was created using Design→Create Cellview→From Cellview and is seen in Figure11.11.11.2.1Copy the Pad FrameThefirst step is to copy the pad frame that you want to use from the UofU Pads library into your own library.You need to copy the frame because you’re going to modify the frame to contain the pads you want to use.The frame defines the placement of the pads,but you can adjust which type of pad you want in each pad ing the pre-designed frames is very impor-tant.The frames are designed to be the exact outside dimensions allowed by MOSIS for class fabrication.Making the frames one micron bigger would double the cost.Our“cost”is measured in Tiny Chip Units or TCUs. Each TCU is1500X1500microns in outside dimensions.It’s possible to use multiple TCUs together to make larger chips.But,because we have a limited TCU budget,you should definitely try tofit your core in the smallest frame you can.The available frames are:Frame138:A single tiny chip(1TCU)frame with38signal pins(plus355CHAPTER11:Chip Assembly Draft October30,20061-vdd and1-gnd).Usable core area is approximately900X900mi-crons.Frame2h70:A two-tiny-chip(2TCU)frame with70signal pins(plus1-vdd and1-gnd).The core a horizontal rectangle(long edges on top and bottom).Usable core area is approximately2300X900microns.If you aren’t using all the signal pad locations and want to add extra power and ground pads you can add them as follows:vdd on pads16 and33,gnd on pads48and74.Frame2v70:A two-tiny-chip(2TCU)frame with70signal pins(plus1-vdd and1-gnd).The core a vertical rectangle(long edges on right and left).Usable core area is approximately900X2300microns.If you aren’t using all the signal pad locations and want to add extra power and ground pads you can add them as follows:vdd on pads16and 33,gnd on pads48and74.Frame478:A four-tiny-chip frame with78signal pins(plus3-vdd and 3-gnd).Usable core area is approximately2300X2300microns.For this example I’ll use the Frame138.I’ll copy that cell from the UofU Pads library to my own library so that I can modify for the needs of the core.11.2.2Modify the Frame schematic viewOnce the frame of your choice is copied into the library you are using for chip assembly,you need to replace pads that are in the frame with the pads you want.The frames have vdd and gnd pads in the correct places for the tester so DO NOT change the location of the vdd and gnd pads!All the other pads in the frame are pad nc for no-connect.You should replace the pad nc cells with the pads you want.The cells available are:pad bidirhe:A bidirectional(tri-state)pad with high-enable.From the core to the pad the signals are DataOut and EN.These are outputs from your core,and inputs to the pad cell.From the pad to the core the signals are DataIn and DataInB.These are outputs from the pad and inputs to your core.The pad itself is connected to an inout pin called pad.pad in:An input pad meaning from the outside world to your core.The signals are DataIn and DataInB going from the pad to your core.The pad itself is on an input pin called pad.356Draft October30,200611.2:Core to Pad Frame Routing with ccar pad out:An output pad,meaning going from your core out to the outside world.The signal that comes from your core is called DataOut,and the pad itself is on an output pin called pad.pad nc:This is a pad that does not connect to your core.If you are not using all the pads in the pad ring make sure that the ones you’re not using are pad nc so that the vdd and gnd are connected in the pad ring, and so that MOSIS doesn’t get confused by the number of bonding areas that it expects to see.pad vdd:A vdd pad.These are in the right spots for our test board so you should not move them!There are no pins because the global vdd!Label is used inside the pad schematic.There is a vdd connection in the layout view.pad gnd:Same thing,but for gnd.pad corner:You shouldn’t have to mess with these.They are layout-only and provide vdd and gnd connectivity for the pad ring.They are placed in the correct locations in the pad frame layout views.pad io:An analog input/output pad with a series resistor in the io signal path.You shouldn’t have to use this!Don’t confuse this for the pad bidirhe!pad io nores:An analog pad with no series resistor.You shouldn’t have to use this either!At this point I should choose which pad locations get which signals and which pad type.This depends somewhat on the physical placement of the pins on the core layout,and somewhat on how you want your external pins to map to the package.Anything will work,but you may want to be more deterministic about where each pin goes.In this example I’m picking pin locations somewhat randomly.I’ll map the signals to pins and pad types as follows:Pin Name Pad Numberclk15pad inclr27pad inzero37pad inaluop<1:0>79,78pad outalusrcb<1:0>73,72pad outc<7:6>70,69pad outirwrite<3:0>11,10,9,8pad outout155pad outout254pad out357CHAPTER11:Chip Assembly Draft October30,2006This involves changing the appropriate pad nc cells into pad in and pad out cells in the schematic view.You can use the q Object Properties It’s possible that theorigins of the cells may be in different spots and you may have to move things around to keepthings looking neat.menu to change which cell is instantiated in that spot without moving the cell.Once I’ve made the cell type changes,I will add wires and pins to the ap-propriate cell inputs and outputs.What we’re aiming for is to define the in-put and output signals of the frame,collect this into a symbol view,and then make another schematic that has our core and frame connected together. This will be the starting point for the ccar router to route the signal pins to the pads.Now add input,output,and inout(if you have bidirectional pads)pins (and wires)to your frame schematic.There are two types of pins that you need to add:signals coming from the outside world to your pad ring(these connect to the pad pins on the pad cells as if you were wiring the external signals to the pads),and signals going between your pad ring and your core (connecting to the DataIn,DataInB,and DataOut pins on the pad cells). The pad frame for this example is shown in Figure11.12.Make sure to get the directions right!Remember that going from your core to the pad frame is an output as far as the overall chip is concerned,but that will be an input to the frame cell because it’s coming in to the frame from your core.Likewise,a signal going from your pad frame to the core is an input to your core because it’s coming into your core from the outside world,but it’s an output with respect to your frame cell.Think of the frame as a doughnut with the core in the hole.Outputs from your core go into the inside edge of the doughnut and emerge at the pads on the outside edge of the doughnut.I like to name the pins that go between the core and the pad frame to be the names of the signals with a i suffix for“internal,”and use the existing “real”signal names on the signals that are on the pads.That way I can keep track of which signals are internal and which are on the pads and connect to the outside world.It also lets me use the same testbench on the version with pads as with just the core itself.Of course you can come up with your own naming scheme.An example of my naming scheme is seen in Fig-I modified the framesymbol slightly to position the pins of the symbol in a“nice”way with respect to the coresymbol.ure11.13.An automatically generated frame symbol is seen in Figure11.14 where it is connected to the core macro in a core-with-pads schematic view that I’ll call wholechip.The frame symbol was generated automatically us-ing the Design→Create Cellview→From Cellview menu.Note that I’ve collected some of the buses into bus pins in the frame schematic,and left some expanded as individual wires just to show that both are possible.When I save the wholechip schematic I get some warnings about the DataInB signals beingfloating outputs.I didn’t connect them because I wasn’t using them,so I’ll ignore those warnings.Unconnected outputs are358。