ATAK5753-43P3-S中文资料

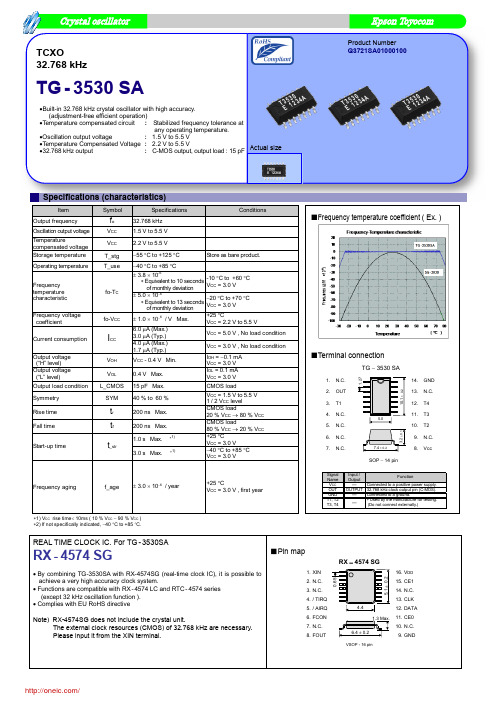

TG-3530SA;中文规格书,Datasheet资料

13. 12. 11. 10.

tr tf t_str

N.C. N.C. N.C.

7.40.2

3.20.1

9. 8.

3.0sMax.

1)

SOP14 pin

Signal Name VCC OUT GND T1,T2 T3,T4 Input / Function Output Connected to a positive power supply. OUTPUT 32.768kHzclock output pin (C-MOS). Connected to a ground. Used by the manufacture for testing. (Do not connect externally.)

15. CE1 14. N.C. 13. CLK 12. DATA 11. CE0 10. N.C. 9. GND

Note) RX-4574SG does not include the crystal unit. The external clock resources (CMOS) of 32.768 kHz are necessary. Please input it from the XIN terminal.

1)

Conditions

fo

VCC VCC T_stg T_use

■Frequency temperature coefficient(Ex.)

Store as bare product.

-10Cto +60C VCC=3.0V 20Cto+70C VCC=3.0V +25C VCC=2.2Vto5.5 V VCC=5.0V,No load condition VCC=3.0V,No load condition IOH=0.1mA VCC=3.0V IOL=0.1mA VCC=3.0V CMOS load VCC=1.5Vto5.5 V 1/2VCC level CMOS load 20%VCC80%VCC CMOS load 80%VCC20%VCC +25C VCC=3.0V 40Cto+85C VCC=3.0V

家电维修-TCL-CRT背投电视介绍

技术前沿

T C L - C R T 背投电视介绍 下

李培仁

5.CRT 背投的信号流程 TCL-CRT 背投目前所用的机心主要 有以下四种 HiD435B.r机心 属60Hz逐 行扫描机心 HiD432机心 属低价60Hz 逐行扫描机心 HiD438SB.r 属85Hz逐 行扫描机心 HiD43P9机心 属100Hz逐 行扫描机心 1 HiD435B.r HiD435B.r 机心采用 PHILIPS 的 TDA9321 电视信号解调和 TDA9332 显示 处理芯片 nDSP 公司的 NV320 逐行处理 芯片 实现 60Hz 逐行扫描 CPU 芯片为 东芝 TMP87PS38 在生产批量不大时使 用 OTP 方式将软件烧写到芯片上 便于 根据生产和市场反馈有可能对软件作修 改 画中画功能板 会聚功能板均设计成 有屏蔽罩的模块形式 其中会聚模块每 机必有 画中画模块可随机型功能的变 化选配 HiD435B.r机心将普通电视扫描行数 加倍 PAL制可支持60Hz数字逐点成像 画面不闪烁 图像更细腻 清晰 无行结 构线 可连接 PC 以电脑画面玩休闲软 件 游玩网络世界 支持 VGA 640 480/60Hz HiD435B.r主板流程图如图6所示

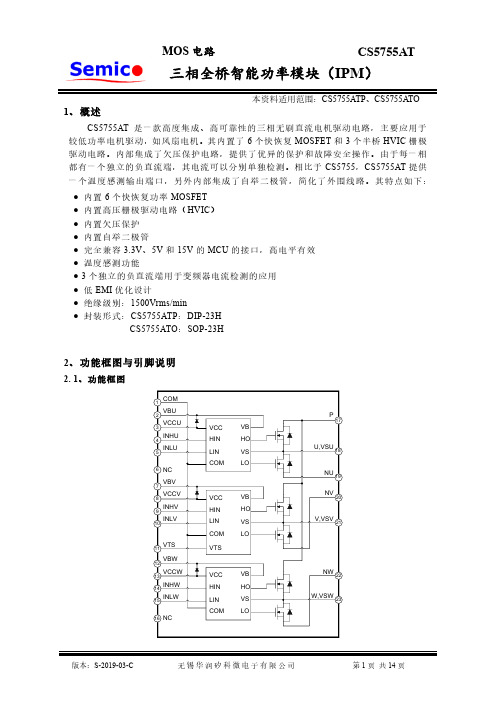

CS5755AT 三相全桥智能功率模块说明书

MOS电路CS5755AT三相全桥智能功率模块(IPM)1、概述CS5755AT是一款高度集成、高可靠性的三相无刷直流电机驱动电路,主要应用于较低功率电机驱动,如风扇电机。

其内置了6个快恢复MOSFET和3个半桥HVIC栅极驱动电路。

内部集成了欠压保护电路,提供了优异的保护和故障安全操作。

由于每一相都有一个独立的负直流端,其电流可以分别单独检测。

相比于CS5755,CS5755AT提供一个温度感测输出端口,另外内部集成了自举二极管,简化了外围线路。

其特点如下:●内置6个快恢复功率MOSFET●内置高压栅极驱动电路(HVIC)●内置欠压保护●内置自举二极管●完全兼容3.3V、5V和15V的MCU的接口,高电平有效●温度感测功能● 3个独立的负直流端用于变频器电流检测的应用●低EMI优化设计●绝缘级别:1500Vrms/min● 封装形式:CS5755ATP:DIP-23HCS5755ATO:SOP-23H2、功能框图与引脚说明2. 1、功能框图2. 2、功能描述该电路内置了6个快恢复MOSFET 和3个半桥HVIC 栅极驱动电路,如上图所示。

每一个半桥HVIC 栅极驱动电路功能框图及描述如下:该HVIC 栅极驱动主要由高低电平转换器、互锁逻辑、延时逻辑、脉冲发生器、脉冲过滤器、欠压保护逻辑和高低侧端驱动级等模块构成。

LIN 输入信号通过一个由内部稳压供电(门限电压不受外压影响)的施密特触发器后输入给内部稳压-外部低压供电VCC 之间的电平转换,再通过用于控制死区时间的延时电路,最后输入到驱动级。

HIN 输入信号同样通过一个由内部稳压供电的施密特触发器后输入给内部稳压-外部低压供电VCC 间进行电平转换,然后输入延时电路,输出由低压通道欠压保护模块的输出信号控制产生两路固定相位差的定频短脉冲,然后通过VCC-VS 电平转换将脉冲电平变换为VB-VS 之间,再通过脉冲过滤模块,和高压通道欠压保护模块的输出信号一起输入给RS 触发器,最后输出控制高压通道的驱动级。

1.5KE43CA(SynSemi)中文数据手册「EasyDatasheet」

P,D稳态功耗0 0

25

50 75 100 125 150 175 200

TL,引线温度(℃)

图5 -脉冲波形

RMS Tr = 10µs

100

Peak Value

IRMS

TJ=25 °C Pulse Width (tp) is defined as that point where the peak current decays to 50% of IRSM

94.0

1.5KE120A 1.5KE120CA

114

126

1.0

102

1.5KE130A 1.5KE130CA

124

137

1.0

111

1.5KE150A 1.5KE150CA

143

158

1.0

128

1.5KE160A 1.5KE160CA

152

168

1.0

136

1.5KE170A 1.5KE170CA

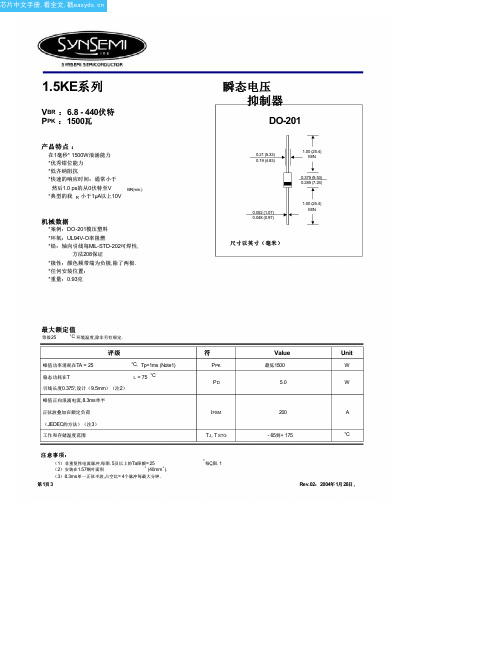

瞬态电压 抑制器

DO-201

0.21 (5.33) 0.19 (4.83)

0.052 (1.07) 0.048 (0.97)

1.00 (25.4) MIN.

0.375 (9.53) 0.285 (7.24)

1.00 (25.4) MIN.

尺寸以英寸(毫米)

最大额定值

等级25

°C 环境温度,除非另有规定.

1.0

25.6

1.5KE33A

1.5KE33CA

31.4

34.7

1.0

28.2

1.5KE36A

1.5KE36CA

34.2

37.8

1.0

30.8

FNK MOS管型号参数大全

12 10 4.5 4.5 2.8 4.5 4.2 1.8 16 6 20 210 5.5 5 15 6.5 3.3 6.5 5 3.2 22 8 28 350 7 7 20 7 19 17 17 15 21 23 24 24 21 27 24 22 22 20 26 6 3.2 6 5.2 2.3 19 8 27 310 7 7 20

Vcesat(15V) (V) Typ Max

Assembly SOT-23 DFN2X26L SOT-23 SOT-23 SOP8 Double SOP8 Double SOP-8 SOT-23 SOT-23 SOT-23 SOT-23 SOT-23 SOT23-3L SOT-23 SOT23-3L SOT-23 SOP-8 SOP-8 SOP-8 SOP-8 SOP-8 SOP-8 SOP-8 Double SOP-8 TO-252 SOP-8 SOP-8 SOP-8 SOP-8 DFN5X68L TO-251 TO-251 TO-252 TO-220 SOP-8 SOT23-3L SOP-8 SOP-8 TO-252 TO-252 TO-252 TO-252 SOP-8 TO-220 TO-252 TO-220 TO-252 TO-220 TO-220 TO-220 TO-220 TO-220 TO-220 TO-263 TO-220 SOT-23 SOT-23 SOT-23 SOT-23 SOT23-6 Single SOT23-6 Single TSSOP-8 Single TSSOP-8 Single TSSOP-8 Single SOP-8 Single SOP-8 Single SOP-8 Single SOP-8 Double SOP-8 Double SOP-8 SOP8 TO-251 TO-251 TO-252 TO-252 PDFN5*6 TSSOP-8 SOP-8 SOT23 SOT-523 TSSOP-8 SOP-8 TSSOP-8 Single TSSOP-8 Single FDFN3.3*3.3 TSSOP-8 SOT23-6 SOT23-6 SOT23

SA575中文资料

TEST CONDITIONS

SA575

UNITS

MIN

TYP

MAX

For compandor, including summing amplifier

VCC

Supply voltage1

ICC VREF

Supply current Reference voltage2

RL

Summing amp output load

GBW

Bandwidth

ENI PSRR

Input voltage noise Power supply rejection ratio

1kHz, 0dB, CREF = 220µF

RL = 10kΩ 1kHz

VIN = 0.5V to 4.5V

RL = 10kΩ Unity gain Unity gain BW = 20kHz 1kHz, 250mV

VCC +5V

0.1µF

VREF

VOUT

C3

+

10µF

+ CRECT

2.2µF

GND VIN

C6

10µF +

+

10µF

GND

GND

1+

575

20

VCC

2–

OP AMP

+ 19

3

– 18

OP AMP

C15

R13 10k

10µF

+

C14

GND VIN

VREF

4

3.8k

5

Σ

6

7

10k

17

16

3.8k

C11

• 600Ω drive capability • Single or split supply operation • Wide input/output swing capability • 3000V ESD protection

T5754_07中文资料

Features Array•Integrated PLL Loop Filter•ESD Protection also at ANT1/ANT2(4kV HBM/200V MM; Except Pin2: 4kV HBM/100V MM)•High Output Power (7.5dBm) with Low Supply Current(9.0mA)•Modulation Scheme ASK/ FSK–FSK Modulation is Achieved by Connecting an Additional Capacitor Between the XTAL Load Capacitor and the Open Drain Output of the Modulating Microcontroller •Easy to Design-in Due to Excellent Isolation of the PLL from the PA and Power Supply •Single Li-cell for Power Supply•Supply Voltage 2.0V to 4.0V in the Temperature Range of –40°C to 85°C/125°C •Package TSSOP8L•Single-ended Antenna Output with High Efficient Power Amplifier•CLK Output for Clocking the Microcontroller•One-chip Solution with Minimum External Circuitry•125°C Operation for Tire Pressure Systems1.DescriptionThe T5754 is a PLL transmitter IC which has been developed for the demands of RF low-cost transmission systems at data rates up to 32kBaud. The transmitting frequency range is 429MHz to 439MHz. It can be used in both FSK and ASK systems.Figure 1-1.System Block Diagram24511I–RKE–02/07T57542.Pin ConfigurationFigure 2-1.Pinning TSSOP8L34511I–RKE–02/07T5754Figure 2-2.Block Diagram44511I–RKE–02/07T57543.General DescriptionThis fully integrated PLL transmitter allows particularly simple, low-cost RF miniature transmit-ters to be assembled. The VCO is locked to 32f XTAL hence a 13.56MHz crystal is needed for a 433.92MHz transmitter. All other PLL and VCO peripheral elements are integrated.The XTO is a series resonance oscillator so that only one capacitor together with a crystal con-nected in series to GND are needed as external elements.The crystal oscillator together with the PLL needs typically < 1ms until the PLL is locked and the CLK output is stable. There is a wait time of ≥1ms until the CLK is used for the microcontroller and the PA is switched on.The power amplifier is an open-collector output delivering a current pulse which is nearly inde-pendent from the load impedance. The delivered output power is hence controllable via the connected load impedance.This output configuration enables a simple matching to any kind of antenna or to 50Ω. A high power efficiency of η=P out /(I S,PA V S ) of 36% for the power amplifier results when an optimized load impedance of Z Load =(166+j223)Ω is used at 3V supply voltage.4.Functional DescriptionIf ENABLE =L and the PA_ENABLE =L, the circuit is in standby mode consuming only a very small amount of current so that a lithium cell used as power supply can work for several years. With ENABLE =H the XTO, PLL and the CLK driver are switched on. If PA_ENABLE remains L only the PLL and the XTO is running and the CLK signal is delivered to the microcontroller. The VCO locks to 32 times the XTO frequency.With ENABLE =H and PA_ENABLE =H the PLL, XTO, CLK driver and the power amplifier are on. With PA_ENABLE the power amplifier can be switched on and off, which is used to perform the ASK modulation.4.1ASK TransmissionThe T5754 is activated by ENABLE =H. PA_ENABLE must remain L for t ≥1ms, then the CLK signal can be taken to clock the microcontroller and the output power can be modulated by means of pin PA_ENABLE. After transmission PA_ENABLE is switched to L and the microcon-troller switches back to internal clocking. The T5754 is switched back to standby mode with ENABLE =L.4.2FSK TransmissionThe T5754 is activated by ENABLE =H. PA_ENABLE must remain L for t ≥1ms, then the CLK signal can be taken to clock the microcontroller and the power amplifier is switched on with PA_ENABLE =H. The chip is then ready for FSK modulation. The microcontroller starts to switch on and off the capacitor between the XTAL load capacitor and GND with an open-drain output port, thus changing the reference frequency of the PLL. If the switch is closed, the output frequency is lower than if the switch is open. After transmission PA_ENABLE is switched to L and the microcontroller switches back to internal clocking. The T5754 is switched back to standby mode with ENABLE =L.The accuracy of the frequency deviation with XTAL pulling method is about ±25% when the fol-lowing tolerances are considered.54511I–RKE–02/07T5754Figure 4-1.Tolerances of Frequency ModulationUsing C 4=9.2pF ±2%, C 5=6.8pF ±5%, a switch port with C Switch =3pF ±10%, stray capaci-tances on each side of the crystal of C Stray1=C Stray2=1pF ±10%, a parallel capacitance of the crystal of C 0=3.2pF ±10% and a crystal with C M =13fF ±10%, an FSK deviation of ±21kHz typical with worst case tolerances of ±16.3kHz to ±28.8kHz results.4.3CLK OutputAn output CLK signal is provided for a connected microcontroller, the delivered signal is CMOS compatible if the load capacitance is lower than 10pF.4.3.1Clock Pulse Take-overThe clock of the crystal oscillator can be used for clocking the microcontroller. Atmel ®’s ATARx9x has the special feature of starting with an integrated RC-oscillator to switch on the T5754 with ENABLE =H, and after 1ms to assume the clock signal of the transmission IC, so that the message can be sent with crystal accuracy.4.3.2Output Matching and Power SettingThe output power is set by the load impedance of the antenna. The maximum output power is achieved with a load impedance of Z Load,opt =(166+j223)Ω. There must be a low resistive path to V S to deliver the DC current.The delivered current pulse of the power amplifier is 9mA and the maximum output power is delivered to a resistive load of 465Ω if the 1.0pF output capacitance of the power amplifier is compensated by the load impedance.An optimum load impedance of:Z Load =465Ω||j/(2×π1.0pF)=(166+j223)Ω thus results for the maximum output power of 7.5dBm.The load impedance is defined as the impedance seen from the T5754’s ANT1, ANT2 into the matching network. Do not confuse this large signal load impedance with a small signal input impedance delivered as input characteristic of RF amplifiers and measured from the application into the IC instead of from the IC into the application for a power amplifier.Less output power is achieved by lowering the real parallel part of 465Ω where the parallel imag-inary part should be kept constant.Output power measurement can be done with the circuit of Figure 4-2 on page 6. Note that the component values must be changed to compensate the individual board parasitics until the T5754 has the right load impedance Z Load,opt =(166+j223)Ω. Also the damping of the cable used to measure the output power must be calibrated out.64511I–RKE–02/07T5754Figure 4-2.Output Power Measurement4.4Application CircuitFor the supply-voltage blocking capacitor C 3 a value of 68nF/X7R is recommended (see Figure 4-3 on page 7 and Figure 4-4 on page 8). C 1 and C 2 are used to match the loop antenna to the power amplifier where C 1 typically is 8.2pF/NP0 and C 2 is 6pF/NP0 (10pF +15pF in series);for C 2 two capacitors in series should be used to achieve a better tolerance value and to have the possibility to realize the Z Load,opt by using standard valued capacitors.C 1 forms together with the pins of T5754 and the PCB board wires a series resonance loop that suppresses the 1st harmonic, hence the position of C 1 on the PCB is important. Normally the best suppression is achieved when C 1 is placed as close as possible to the pins ANT1 and ANT2.The loop antenna should not exceed a width of 1.5mm, otherwise the Q-factor of the loop antenna is too high.L 1 ([50nH to 100nH) can be printed on PCB. C 4 should be selected that the XTO runs on the load resonance frequency of the crystal. Normally, a value of 12pF results for a 15pF load-capacitance crystal.74511I–RKE–02/0784511I–RKE–02/07T575494511I–RKE–02/07T5754Figure 4-5.ESD Protection Circuit5.Absolute Maximum RatingsStresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.Parameters Symbol MinimumMaximumUnit Supply voltage V S 5V Power dissipation P tot 100mW Junction temperature T j 150°C Storage temperature T stg –55125°C Ambient temperature T amb –55125°C Input voltage V maxP A_ENABLE–0.3(V S + 0.3)(1)VNote:1.If V S + 0.3 is higher than 3.7V , the maximum voltage will be reduced to 3.7V .6.Thermal ResistanceParameters Symbol Value Unit Junction ambientR thJA170K/W7.Electrical CharacteristicsV S = 2.0V to 4.0V , T amb = –40°C to 125°C unless otherwise specified.T ypical values are given at V S = 3.0V and T amb = 25°C. All parameters are referred to GND (pin 7).ParametersTest ConditionsSymbolMin.Typ.Max.Unit Supply currentPower downV ENABLE <0.25V , –40°C to 85°CV PA-ENABLE <0.25V , –40°C to +125°C V PA-ENABLE <0.25V , 25°C (100% correlation tested)I S_Off< 103507nA µA nA Supply current Power up, P A off, V S = 3V ,V ENABLE >1.7V ,V PA-ENABLE <0.25V I S 3.7 4.8mA Supply current Power up, V S = 3.0V ,V ENABLE >1.7V ,V PA-ENABLE >1.7V I S_T ransmit 911.6mA Output power V S =3.0V , T amb =25°C,f = 433.92 MHz, Z Load = (166 + j233)ΩP Ref5.57.510dBmNote:1.If V S is higher than 3.6V , the maximum voltage will be reduced to 3.6V .104511I–RKE–02/07T5754Output power variation for the full temperature rangeT amb = –40°C to +85°C,V S = 3.0V V S = 2.0V∆P Ref ∆P Ref –1.5–4.0dB dB Output power variation for the full temperature rangeT amb = –40°C to +125°C,V S = 3.0V V S = 2.0VP Out = P Ref + ∆P Ref∆P Ref ∆P Ref –2.0–4.5dB dB Achievable output-power rangeSelectable by load impedance P Out_typ07.5dBmSpurious emissionf CLK = f 0/128Load capacitance at pin CLK = 10pF f O ±1×f CLK f O ±4×f CLKother spurious are lower–55–52dBc dBcOscillator frequency XTO(= phase comparator frequency)f XTO = f 0/32f XTAL = resonant frequency of the XT AL, C M ≤10fF , load capacitance selected accordinglyT amb = –40°C to +85°C T amb = –40°C to +125°C f XTO–30–40f XT AL +30+40ppm ppm PLL loop bandwidth250kHz Phase noise of phase comparator Referred to f PC = f XT0,25 kHz distance to carrier –116–110dBc/Hz In loop phase noise PLL 25 kHz distance to carrier –86–80dBc/Hz Phase noise VCO at 1MHz at 36MHz–94–125–90–121dBc/Hz dBc/Hz Frequency range of VCO f VCO429439MHz Clock output frequency (CMOS microcontroller compatible)f 0/128MHz Voltage swing at pin CLK C Load ≤10pFV 0h V 0l V S ×0.8V S ×0.2V V Series resonance R of the crystal Rs110ΩCapacitive load at pin XT07pF FSK modulation frequency rate Duty cycle of the modulation signal = 50%032kHz ASK modulation frequency rate Duty cycle of the modulation signal = 50%032kHz ENABLE inputLow level input voltage High level input voltage Input current high V Il V Ih I In 1.70.2520V V µA P A_ENABLE input Low level input voltage High level input voltage Input current highV Il V Ih I In1.70.25V S (1)5V V µA7.Electrical Characteristics (Continued)V S = 2.0V to 4.0V , T amb = –40°C to 125°C unless otherwise specified.T ypical values are given at V S = 3.0V and T amb = 25°C. All parameters are referred to GND (pin 7).ParametersTest Conditions Symbol Min.Typ.Max.Unit Note:1.If V S is higher than 3.6V , the maximum voltage will be reduced to 3.6V .T57548.Ordering InformationExtended Type Number Package RemarksT5754-6AQJ TSSOP8L Taped and reeled, Marking: T574, Pb-freeT5754-6APJ TSSOP8L Taped and reeled, Marking: T574, small reel, Pb-free9.Package Information1112T575410.Revision HistoryPlease note that the following page numbers referred to in this section refer to the specific revision mentioned, not to this document.Revision No.History4711I-RKE-02/07• Put datasheet in a new template • Pb-free logo on page 1 deleted4711H-RKE-09/05• Pb-free logo on page 1 added• Ordering Information on page 11 changed4711G-RKE-05/05• Put datasheet in a new template• Package Information (page 11): Replace old package drawing through current version4711F-RKE-07/04• Abs. Max. Ratings table (page 9): row “Input voltage” added • Abs. Max. Ratings table (page 9): table note 1 added• El. Char. table (pages 9 to 10): row “P A_ENABLE input“ changed • El. Char. table (pages 9 to 10): table note 1 added• Ordering Information table (page 11): Remarks changedDisclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise,to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN ATMEL ’S TERMS AND CONDI-TIONS OF SALE LOCATED ON ATMEL ’S WEB SITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDEN-TAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel’s products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.Atmel CorporationAtmel Operations2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311Fax: 1(408) 487-2600Regional HeadquartersEuropeAtmel SarlRoute des Arsenaux 41Case Postale 80CH-1705 Fribourg SwitzerlandTel: (41) 26-426-5555Fax: (41) 26-426-5500AsiaRoom 1219Chinachem Golden Plaza 77 Mody Road Tsimshatsui East Kowloon Hong KongTel: (852) 2721-9778Fax: (852) 2722-1369Japan9F, Tonetsu Shinkawa Bldg.1-24-8 ShinkawaChuo-ku, Tokyo 104-0033JapanTel: (81) 3-3523-3551Fax: (81) 3-3523-7581Memory2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311Fax: 1(408) 436-4314Microcontrollers2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311Fax: 1(408) 436-4314La Chantrerie BP 7060244306 Nantes Cedex 3, France Tel: (33) 2-40-18-18-18Fax: (33) 2-40-18-19-60ASIC/ASSP/Smart CardsZone Industrielle13106 Rousset Cedex, France Tel: (33) 4-42-53-60-00Fax: (33) 4-42-53-60-011150 East Cheyenne Mtn. Blvd.Colorado Springs, CO 80906, USA Tel: 1(719) 576-3300Fax: 1(719) 540-1759Scottish Enterprise Technology Park Maxwell BuildingEast Kilbride G75 0QR, Scotland Tel: (44) 1355-803-000Fax: (44) 1355-242-743RF/AutomotiveTheresienstrasse 2Postfach 353574025 Heilbronn, Germany Tel: (49) 71-31-67-0Fax: (49) 71-31-67-23401150 East Cheyenne Mtn. Blvd.Colorado Springs, CO 80906, USA Tel: 1(719) 576-3300Fax: 1(719) 540-1759BiometricsAvenue de Rochepleine BP 12338521 Saint-Egreve Cedex, France Tel: (33) 4-76-58-47-50Fax: (33) 4-76-58-47-60Literature Requests/literature© 2007 Atmel Corporation . All rights reserved. Atmel ®, logo and combinations thereof, Everywhere You Are ® and others are registered trade-marks or trademarks of Atmel Corporation or its subsidiaries. Other terms and product names may be trademarks of others.。

APM7313中文资料

(T A

=

25°C

unless

otherwise

noted)

Symbol VDSS VGSS

Parameter Drain-Source Voltage Gate-Source Voltage

Rating

Unit

30 V

±20

ANPEC reserves the right to make changes to improve reliability or manufacturability without notice, and advise customers to obtain the latest version of relevant information to verify before placing orders.

元器件交易网

APM7313

Typical Characteristics (Cont.)

ISD-Source Current (A)

Source-Drain Diode Forward Voltage

100

10

1

TJ=125°C

TJ=-55°C

Normalized Transient Thermal Transient Impedence, Junction to Ambient

1

Duty Cycle=0.5

D=0.2

D=0.1

0.1

D=0.05

D=0.02

0.01 1E-4

SINGLE

1E-3

1. Duty Cycle , D=t1/t2

元器件交易网

APM7313

Packaging Information

ATA-3040功率放大器型号参数指标

简介

输出保护

应用领域

ATA-3040 是一款理想的可放大交直 流信号的单通道的功率信号放大器。 最大输出 360W 功率,可以驱动功率 型负载。增益数控可调,一键保存常

过压保护: 当输出电压超出该高压放大器的最大 电压 90Vp-p (±45V)时,输出将自 动断开,并提醒您此时为过压保护状

压电陶瓷 磁性材料的磁化特性(B-H 曲线)测量 声纳系统 超声波探伤

TesTtesFtuFtuurteure

ATA-3040 功率放大器

360W 单通道

• 输出电压 90Vp-p (±45V) • 输出电流 8A • 功率 360W • 带宽(-3dB)DC~100KHz • 压摆率 50V/μs • 低失真 • 增益数控 0~30(0.1step)可调 • 输入阻抗 50Ω/5KΩ可调 • 一键保存设置(Sa 采用的是增益数控 0~30 倍 可调的方式,具体分为粗调(1step)

当输出端正负极发生短路时,输出将 自动断开,并提醒您此时为短路保护 状态。

和细调(0.1 step)两种。结合液晶面

板增益的显示,能够快速调整至您需

要的电压增益值。

用设置,为您提供了方便简洁的操作 态;

EMC 信号加注

选择,可与主流的信号发生器配套使 过流保护:

MEMS 实验

用,实现信号的完美放大。

当输出电流超出该高压放大器的最大

液晶显示

电流 8A 时,输出将自动断开,并提

ATA-3040 采用液晶屏显示,操作界 醒您此时为过流保护状态;

面一目了然,简洁易懂。

2SK3541中文资料

TransistorSmall switching (30V, 0.1A)2SK3541!ApplicationsInterfacing, switching (30V , 100mA)!Features1) Low on-resistance.2) Fast switching speed.3) Low voltage drive (2.5V) makes this device ideal for portable equipment.4) Easily designed drive circuits.5) Easy to parallel.!StructureSilicon N-channel MOSFET!External dimensions (Units : mm)!Absolute maximum ratings (T a=25°C)ParameterDrain-source voltage Gate-source voltage Drain current Total power dissipation (Tc =25°C)Channel temperature Storage temperatureV DSS V GSS I DR P D∗2Tch 30V V mA mA mW °C ±20100I D I DRP ∗1mA I DP ∗1Continuous Pulsed Continuous PulsedmA 400100400150150Tstg°C−55~+150Symbol Limits Unit ∗1 Pw ≤10µs, Duty cycle <1%∗2 With each pin mounted on the recommended lands.Reverse drain current!Equivalent circuit∗A pr otection diode is included between the gateand the source terminals to protect the diodeagainst static electricity when the product is in e a protection circuit when the fixed voltages are exceeded.Transistor!Electrical characteristics (T a=25°C)!Packaging specificationsT2R 80002SK3541TypePackageCodeBasic ordering unit (pieces)Taping !Electrical characteristic curvesD RA I N C U R R E N T : I D (A )DRAIN-SOURCE VOLTAGE : V DS (V)Fig.1 Typical output characteristicsD R A I N C U R RE N T : I D (A )GATE-SOURCE VOLTAGE : V GS (V)Fig.2 Typical transfer characteristicsG A T E T H R E S H O L D V O L T A G E : V G S (t h ) (V )CHANNEL TEMPERATURE : Tch (°C)Fig.3 Gate threshold voltage vs.channel temperatureTransistorS T A T I C D R A I N -S O U R C E O N -S T A T E R E S I S T A N C E : R D S (o n ) (Ω)DRAIN CURRENT : I D (A)Fig.4 Static drain-source on-stateresistance vs. drain current (Ι)S T A T I C D R A I N -S O U R C E O N -S T A T E R E S I S T A N C E : R D S (o n ) (Ω)DRAIN CURRENT : I D (A)Fig.5 Static drain-source on-stateresistance vs. drain current (ΙΙ)GATE-SOURCE VOLTAGE : V GS (V)S T A T I C D R A I N -S O U RC E O N -S T A T E R E S I S T A N C E : RD S (o n ) (Ω)Fig.6 Static drain-sourceon-state resistance vs. gate-source voltageCHANNEL TEMPERATURE : Tch (°C)S T A T I C D R A I N -S O U R C E O N -S T A T E R E S I S T A N C E : R D S (o n )(Ω)Fig.7 Static drain-source on-stateresistance vs. channel temperatureF O R W A R D T R A N S F E R A D M I T T A N C E : |Y f s | (S )DRAIN CURRENT : I D (A)Fig.8 Forward transferadmittance vs. drain currentR E V E R S E D R A I N C U R R E N T : I D R (A )SOURCE-DRAIN VOLTAGE : V SD (V)Fig.9 Reverse drain current vs.source-drain voltage (Ι)R E V E R S E D R A I N C U R R E N T : I D R (A )SOURCE-DRAIN VOLTAGE : V SD (V)Fig.10 Reverse drain current vs.source-drain voltage (ΙΙ)C A P A C I T A N C E : C (p F )DRAIN-SOURCE VOLTAGE : V DS (V)Fig.11 Typical capacitance vs.drain-source voltageS W I T H I N G T I M E : t (n s )DRAIN CURRENT : I D (mA)Fig.12 Switching characteristics(See Figures 13 and 14 for the measurement circuit and resultant waveforms)Transistor!Switching characteristics measurement circuitFig.13 Switching time measurement circuitFig.14 Switching time waveformsAppendixAbout Export Control Order in JapanProducts described herein are the objects of controlled goods in Annex 1 (Item 16) of Export Trade ControlOrder in Japan.In case of export from Japan, please confirm if it applies to "objective" criteria or an "informed" (by MITI clause)on the basis of "catch all controls for Non-Proliferation of Weapons of Mass Destruction.Appendix1-Rev1.0。

CD4543中文资料

Data sheet acquired from Harris Semiconductor SCHS086IMPORTANT NOTICETexas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI’s standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE (“CRITICAL APPLICATIONS”). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER’S RISK.In order to minimize risks associated with the customer’s applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI’s publication of information regarding any third party’s products or services does not constitute TI’s approval, warranty or endorsement thereof.Copyright © 1998, Texas Instruments Incorporated。

5833中文资料

5833中⽂资料Designed to reduce logic supply current, chip size, and system cost, the UCN5833A/EP integrated circuits offer high-speed operation for thermal printers. These devices can also be used to drive multi-plexed LED displays or incandescent lamps within their 125 mA peak output current rating. The combination of bipolar and MOS technolo-gies gives BiMOS II smart power ICs an interface flexibility beyond the reach of standard buffers and power driver circuits.These 32-bit drivers have bipolar open-collector npn Darlington outputs, a CMOS data latch for each of the drivers, a 32-bit CMOS shift register, and CMOS control circuitry. The high-speed CMOS shift registers and latches allow operation with most microprocessor-based systems at data input rates above 3.3 MHz. Use of these drivers with TTL may require input pull-up resistors to ensure an input logic high.The UCN5833A is supplied in a 40-pin dual in-line plastic package with 0.600" (15.24 mm) row spacing. At an ambient temperature of +75°C, all outputs of the DlP-packaged device will sustain 50 mA continuously. For high-density applications, the UCN5833EP is available. This 44-lead plastic chip carrier (quad pack) is intended for surface-mounting on solder lands with 0.050" (1.27 mm) centers.CMOS serial data outputs permit cascading for applications requiring additional drive lines.FEATURESI To 3.3 MHz Data Input Rate I 30 V Minimum Output Breakdown I Darlington Current-Sink Outputs I Low-Power CMOS Logic and LatchesBiMOS II 32-BIT SERIAL-INPUT,LATCHED DRIVERAlways order by complete part number:Part Number Package UCN5833A 40-Pin DIP UCN5833EP 44-Lead PLCCData Sheet 26185.16A*58335833BiMOS II 32-BIT SERIAL-INPUT,LATCHED DRIVER115 Northeast Cutoff, Box 15036Worcester, Massachusetts 01615-0036 (508) 853-5000SERIAL DATA IN POWER STROBE OUT OUT OUT OUT OUT OUT 123456OUT7OUT 8OUT 9OUTOUT OUTOUT OUTLOGIC SUPPLY OUT OUT Dwg. No. A-13,051TYPICAL OUTPUT DRIVERSUBOUT115 Northeast Cutoff, Box 15036Worcester, Massachusetts 01615-0036 (508) 853-5000Copyright ? 1986, 1995, Allegro MicroSystems, Inc.5833BiMOS II 32-BIT SERIAL-INPUT,LATCHED DRIVERTRUTH TABLEL = Low Logic Level H = High Logic Level X = Irrelevant P = Present State R = Previous StateELECTRICAL CHARACTERISTICS at T A = +25°C, V DD = 5 V (unless otherwise noted).Limits CharacteristicSymbol Test Conditions Min.Max.Units Output Leakage Current I CEX V OUT = 30 V, T A = 70°C —10µA Collector-Emitter V CE(SAT)l OUT = 50 mA — 1.2V l OUT = 100 mA— 1.7V Input VoltageV IN(1) 3.5 5.3V V IN(0)-0.3+0.8V Input Currentl IN(1)V IN = 5.0 V — 1.0µA l IN(0)V IN = 0 V —-1.0µA Serial Output VoltageV OUT(1)I OUT = -200 µA 4.5—V V OUT(0)I OUT = 200 µA—0.3V Supply Currentl DD One output ON, l OUT = 100 mA — 1.0mA All outputs OFF—50µA Output Rise Time t r l OUT = 100 mA, 10% to 90%—500ns Output Fall Timet fl OUT = 100 mA, 90% to 10%—500nsNOTE: Positive (negative) current is defined as going into (coming out of) the specified device pin.Saturation Voltage5833BiMOS II 32-BIT SERIAL-INPUT,LATCHED DRIVER115 Northeast Cutoff, Box 15036Worcester, Massachusetts 01615-0036 (508) 853-5000TIMING CONDITIONS(V DD = 5.0 V, Logic Levels are V DD and Ground)A.Minimum Data Active Time Before Clock Pulse(Data Set-Up Time)..........................................................................75 ns B.Minimum Data Active Time After Clock Pulse(Data Hold Time).............................................................................75 ns C.Minimum Data Pulse Width ................................................................150 ns D.Minimum Clock Pulse Width...............................................................150 nsE.Minimum Time Between Clock Activation and Strobe.......................300 nsF.Minimum Strobe Pulse Width .............................................................100 nsG.Typical Time Between Strobe Activation andOutput Transition ...........................................................................500 nsDwg. No. A-12,276ASerial Data present at the input is transferred to the shift register on the logic “0” to logic “1” transition of the CLOCK input pulse. On succeeding CLOCK pulses, the registers shift data information towards the SERIAL DATA OUTPUT. The SERIAL DATA must appear at the input prior to the rising edge of the CLOCK input waveform.Information present at any register is transferred to its respective latch when the STROBE is high (serial-to-parallel conversion). The latches will continue to accept new data as long as the STROBE is held high. Applications where the latches are bypassed (STROBE tied high) will require that the OUTPUT ENABLE input be low during serial data entry.When the OUTPUT ENABLE input is low, all of the output buffers are disabled (OFF) without affecting the information stored in the latches or shift register. With the OUTPUT ENABLE input high, the outputs are controlled by the state of the latches.CLOCK DATA INSTROBE NOUTPUT ENABLEOUT5833BiMOS II 32-BIT SERIAL-INPUT,LATCHED DRIVERNOTES:1.Exact body and lead configuration at vendor’s option within limits shown.2.Lead spacing tolerance is non-cumulative.3.Lead thickness is measured at seating plane or below.UCN5833ADimensions in Inches (controlling dimensions)Dimensions in Millimeters (for reference only)123Dwg. MA-003-40 mm20421123Dwg. MA-003-40 in2045833BiMOS II 32-BIT SERIAL-INPUT,LATCHED DRIVER115 Northeast Cutoff, Box 15036Worcester, Massachusetts 01615-0036 (508) 853-5000UCN5833EPDimensions in Inches (controlling dimensions)Dimensions in Millimeters (for reference only)Dwg. MA-005-44A mm0.53340Dwg. MA-005-44A in0.021740NOTES:1.Exact body and lead configuration at vendor’s option within limits shown.2.Lead spacing tolerance is non-cumulative.5833BiMOS II 32-BITSERIAL-INPUT,LATCHED DRIVERThe products described here are manufactured under one or more U.S. patents or U.S. patents pending.Allegro MicroSystems, Inc. reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.Allegro products are not authorized for use as critical components in life-support devices or systems without express written approval.The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems, Inc. assumes no responsi-bility for its use; nor for any infringement of patents or other rights of third parties which may result from its use. 5833BiMOS II 32-BIT SERIAL-INPUT,LATCHED DRIVER115 Northeast Cutoff, Box 15036Worcester, Massachusetts 01615-0036 (508) 853-5000POWERINTERFACE DRIVERSFunctionOutput Ratings*Part Number ?SERIAL-INPUT LATCHED DRIVERS8-Bit (saturated drivers)-120 mA 50 V?58958-Bit 350 mA 50 V 58218-Bit 350 mA 80 V 58228-Bit 350 mA 50 V?58418-Bit 350 mA 80 V?58428-Bit (constant-current LED driver)75 mA 17 V 62758-Bit (DMOS drivers)250 mA 50 V 65958-Bit (DMOS drivers)350 mA 50 V?6A5958-Bit (DMOS drivers)100 mA 50 V 6B59510-Bit (active pull-downs)-25 mA 60 V 5810-F and 6809/1012-Bit (active pull-downs)-25 mA 60 V 5811 and 681116-Bit (constant-current LED driver)75 mA 17 V 627620-Bit (active pull-downs)-25 mA 60 V 5812-F and 681232-Bit (active pull-downs)-25 mA 60 V 5818-F and 681832-Bit100 mA 30 V 583332-Bit (saturated drivers)100 mA 40 V 5832PARALLEL-INPUT LATCHED DRIVERS4-Bit350 mA 50 V?58008-Bit -25 mA 60 V 58158-Bit350 mA 50 V?58018-Bit (DMOS drivers)100 mA 50 V 6B2738-Bit (DMOS drivers)250 mA 50 V 6273SPECIAL-PURPOSE DEVICESUnipolar Stepper Motor Translator/Driver 1.25 A 50 V?5804Addressable 8-Bit Decoder/DMOS Driver 250 mA 50 V6259Addressable 8-Bit Decoder/DMOS Driver 350 mA 50 V?6A259Addressable 8-Bit Decoder/DMOS Driver 100 mA 50 V 6B259Addressable 28-Line Decoder/Driver 450 mA30 V6817*Current is maximum specified test condition, voltage is maximum rating. See specification for sustaining voltagelimits.Negative current is defined as coming out of (sourcing) the output.Complete part number includes additional characters to indicate operating temperature range and package style. Internal transient-suppression diodes included for inductive-load protection.。

CS4353资料

Preliminary Product InformationThis document contains information for a new product.Cirrus Logic reserves the right to modify this product without notice.3.3V Stereo Audio DAC with 2V RMS Line OutputFeaturesMulti-bit Delta-Sigma Modulator 106dB A-wt Dynamic Range -93dB THD+NSingle-ended Ground Centered AnalogArchitecture–No DC-blocking Capacitors Required–Integrated Step-up/Inverting Charge Pump –Filtered Line-level Outputs–Selectable 1 or 2V RMS Full-scale OutputLow Clock-jitter Sensitivity Low-latency Digital FilteringSupports Sample Rates up to 192kHz 24-bit Resolution+3.3V Charge Pump and Core Logic, +3.3VAnalog, and +0.9 to 3.3V Interface Power SuppliesLow Power Consumption24-pin QFN, Lead-free AssemblyDescriptionThe CS4353 is a complete stereo digital-to-analog sys-tem including digital interpolation, fifth-order multi-bit delta-sigma digital-to-analog conversion, digital de-em-phasis, analog filtering, and on-chip 2V RMS line-level driver from a 3.3V supply.The advantages of this architecture include ideal differ-ential linearity, no distortion mechanisms due to resistor matching errors, no linearity drift over time and temper-ature, high tolerance to clock jitter, and a minimal set of external components.The CS4353 is available in a 24-pin QFN package in both Automotive (-40°C to +105°C) and Commercial (-40°C to +85°C) grades. The CDB4353 Customer Demonstration Board is also available for device evalu-ation and implementation suggestions. Please see “Ordering Information” on page 26 for complete details.These features are ideal for cost-sensitive, 2-channel audio systems including video game consoles, DVD players and recorders, A/V receivers, set-top boxes,digital TVs, mini-component systems, and mixing consoles.CS4353TABLE OF CONTENTS1. PIN DESCRIPTIONS (4)2. CHARACTERISTICS AND SPECIFICATIONS (6)RECOMMENDED OPERATING CONDITIONS (6)ABSOLUTE MAXIMUM RATINGS (6)DAC ANALOG CHARACTERISTICS (COMMERCIAL - CNZ) (7)DAC ANALOG CHARACTERISTICS (AUTOMOTIVE - DNZ) (8)COMBINED INTERPOLATION & ON-CHIP ANALOG FILTER RESPONSE (9)SWITCHING SPECIFICATIONS - SERIAL AUDIO INTERFACE (10)DIGITAL INTERFACE CHARACTERISTICS (11)INTERNAL POWER-ON RESET THRESHOLD VOLTAGES (11)DC ELECTRICAL CHARACTERISTICS (12)3. TYPICAL CONNECTION DIAGRAM (13)4. APPLICATIONS (14)4.1.1 Ground-Centered Outputs (14)4.1.2 Full-Scale Output Amplitude Control (14)4.1.3 Pseudo-Differential Outputs (14)4.8.1 Power-Up Sequences (20)4.8.1.1 External RESET Power-Up Sequence (20)4.8.1.2 Internal Power-On Reset Power-Up Sequence (20)4.8.2 Power-Down Sequences (20)4.8.2.1 External RESET Power-Down Sequence (20)4.8.2.2 Internal Power-On Reset Power-Down Sequence (20)4.9.1 Capacitor Placement (21)5. DIGITAL FILTER RESPONSE PLOTS (22)6. PARAMETER DEFINITIONS (24)7. PACKAGE DIMENSIONS (25)8. ORDERING INFORMATION (26)9. REVISION HISTORY (27)LIST OF FIGURESFigure 1.Serial Input Timing (10)Figure 2.Power-On Reset Threshold Sequence (11)Figure 3.Typical Connection Diagram (13)Figure 4.Stereo Pseudo-Differential Output (14)Figure 5.I²S, up to 24-Bit Data (16)Figure 6.Left-Justified up to 24-Bit Data (16)Figure 7.De-Emphasis Curve, Fs = 44.1 kHz (17)Figure 8.Internal Power-On Reset Circuit (17)Figure 9.Initialization and Power-Down Sequence Diagram (19)Figure 10.Single-Speed Stopband Rejection (22)Figure 11.Single-Speed Transition Band (22)Figure 12.Single-Speed Transition Band (detail) (22)Figure 13.Single-Speed Passband Ripple (22)Figure 14.Double-Speed Stopband Rejection (22)Figure 15.Double-Speed Transition Band (22)Figure 16.Double-Speed Transition Band (detail) (23)Figure 17.Double-Speed Passband Ripple (23)Figure 18.Quad-Speed Stopband Rejection (23)Figure 19.Quad-Speed Transition Band (23)Figure 20.Quad-Speed Transition Band (detail) (23)Figure 21.Quad-Speed Passband Ripple (23)LIST OF TABLESTable 1. Power-On Reset Threshold Voltages (11)Table 2. Digital I/O Pin Characteristics (12)Table 3. CS4353 Operational Mode Auto-Detect (15)Table 4. Single-Speed Mode Standard Frequencies (15)Table 5. Double-Speed Mode Standard Frequencies (15)Table 6. Quad-Speed Mode Standard Frequencies (15)Table 7. Digital Interface Format (16)1. PIN DESCRIPTIONSPin Name Pin #Pin DescriptionSCLK 1Serial Clock (Input ) - Serial clock for the serial audio interface.MCLK 2Master Clock (Input ) - Clock source for the delta-sigma modulator and digital filters. VL 3Serial Audio Interface Power (Input ) - Positive power for the serial audio interface DGND 4Digital Ground (Input ) - Ground reference for the digital section.FLYP+FLYP-75Step-Up Charge Pump Cap Positive/Negative Nodes (Output) - Positive and Negative nodes for the step-up charge pump’s flying capacitor.VCP 6Charge Pump and Digital Core Logic Power (Input ) - Positive power supply for the step-up and invert-ing charge pumps as well as the digital core logic sections.VFILT+8Step-Up Charge Pump Filter Connection (Output) - Power supply from the step-up charge pump that provides the positive rail for the output amplifiersFLYN+FLYN-911Inverting Charge Pump Cap Positive/Negative Nodes (Output) - Positive and Negative nodes for the inverting charge pump’s flying capacitor.CPGND 10Charge Pump Ground (Input ) - Ground reference for the Charge Pump section.VFILT-12Inverting Charge Pump Filter Connection (Output) - Power supply from the inverting charge pump that provides the negative rail for the output amplifiers.AOUTB AOUTA 1315Analog Outputs (Output ) - The full-scale analog line output level is specified in the Analog Characteris-tics table.AOUT_REF 14Pseudo Diff. Analog Output Reference (Input ) - Ground reference for the analog output amplifiers. This pin must be at the same nominal DC voltage as the AGND pin.AGND16Analog Ground (Input ) - Ground reference for the low voltage analog section.S D I NL R C KI ²S /L JD E M1_2V R M SR E S E TF L Y P +V F I L T +F L Y N +C P G N DF L Y N -SCLK MCLKVL DGND FLYP-VBIAS VA AGND AOUT_REF AOUTBVCPV F I L T -AOUTAVA17Low Voltage Analog Power (Input) - Positive power supply for the analog section. VBIAS18Positive Voltage Reference (Output) - Positive reference voltage for the internal DAC.RESET19Reset (Input) - Optional connection for an external reset control. The device enters a powered-down state when this pin is set low (GND) OR when the VCP supply falls below the V off threshold (see Table1). This pin should be set high (VL) during normal operation.1_2VRMS201 or 2V RMS Select (Input) - Selects the analog output full-scale voltage. Setting this pin low (GND) selects 1V RMS, while setting it high (VL) selects 2V RMS.DEM21De-emphasis (Input) - Selects the standard 50µs/15µs digital de-emphasis filter response for 44.1 kHz sample rates when enabled.I²S/LJ22Digital Interface Format (Input) - Selects the serial audio interface format. Setting this pin low (GND) selects I²S, while setting it high (VL) selects Left-Justified.LRCK23Left / Right Clock (Input) - Determines which channel, Left or Right, is currently active on the serial audio data line.SDIN24Serial Audio Data Input (Input) - Input for two’s complement serial audio data.Thermal Pad-Thermal Relief Pad - This pad may be soldered to the board, however it MUST be electrically isolated from all board connections.2.CHARACTERISTICS AND SPECIFICATIONS RECOMMENDED OPERATING CONDITIONSAGND = DNGD = CPGND = 0V; all voltages with respect to ground.Notes:1.VCP and VA must be supplied with the same nominal voltage. Additional current draw will occur if the sup-ply voltages applied to VCP and VA differ by more than 0.5V.ABSOLUTE MAXIMUM RATINGSAGND = DNGD = CPGND = 0V; all voltages with respect to ground.WARNING:Operation at or beyond these limits may result in permanent damage to the device. Normal operationis not guaranteed at these extremes.ParametersSymbol Min TypMaxUnitsDC Power SupplyCharge Pump and Digital Core power (Note 1)Low Voltage Analog power (Note 1)Interface powerVCP VA VL 3.133.130.85 3.33.30.9 to 3.33.473.473.47V V V Ambient Operating Temperature (Power Applied)-CNZ-DNZT A T A-40-40--+85+105°C °CParametersSymbolMinMaxUnitsDC Power SupplyCharge Pump and Digital Core Logic PowerLow Voltage Analog Power Supply Voltage DifferenceInterface PowerVCP VA |VCP - VA|VL -0.3-0.3--0.3 3.633.630.53.63V V V V Input Current, Any Pin Except Supplies I in -±10mA Digital Input Voltage Digital Interface V IN-L -0.3V L + 0.4V Analog Input Voltage AOUT_REF V IN-A -0.30.5V Ambient Operating Temperature (Power Applied)T A -55+125°C Storage Temperature T stg-65+150°CTest conditions (unless otherwise specified): T A = 25°C; VCP =VA =3.3V; AOUT_REF =AGND = DGND =CPGND = 0V; VBIAS, +/-VFILT, and FLYP/N+/- capacitors as shown in Figure 3 on page 13; input test signal is a 997Hz sine wave at 0dBFS; measurement bandwidth 10Hz to 20kHz.Notes:2.Measured between the AOUTx and AOUT_REF pins.3.One-half LSB of triangular PDF dither is added to data.4.Measured with the specified minimum AC-Load Resistance present on the AOUTx pins. Additional im-pedance between the AOUTx pin and the load will lower the voltage delivered to the load.5.V PP is the controlling specification. V RMS specification valid for sine wave signals only.Note that for sine wave signals:6.Measured with AOUT_REF connected directly to ground. Additional impedance between AOUT_REFand ground will lower the AOUT_REF rejection.7.SDIN =0. AOUT_REF input test signal is a 60Hz, 50mVpp sine wave. Measured by applying the testsignal into the AOUT_REF pin and measuring the resulting output amplitude on the AOUTx pin. Spec-ification calculated by: 1_2VRMS =01_2VRMS =1ParameterSymbol MinTypMaxMinTypMaxUnitDynamic Performance, Fs = 48, 96, and 192kHz (Notes 2, 3)Dynamic Range24-bit A-Weightedunweighted 16-bit A-Weightedunweighted9491--100979289----10097--1061039895----dB dB dB dB Total Harmonic Distortion + Noise24-bit 0dB-20dB-60dB 16-bit 0dB-20dB-60dB THD+N--------93-77-37-93-75-29-87-71-31-----------93-83-43-93-75-35-87-77-37---dB dB dB dB dB dB Idle Channel Noise / Signal-to-Noise Ratio (A-wt)-100--106-dB Interchannel Isolation(1kHz)-115--115-dB Analog Output (Note 2)Full Scale AOUTx Output Voltage (Notes 4, 5)0.98 1.05 1.12 1.96 2.10 2.25V RMS 2.772.973.17 5.54 5.94 6.36V pp Max Current Draw from an AOUTx Pin I OUTmax-575--575-µA Interchannel Gain Mismatch -0.1--0.1-dB Output Offset -±5±8-±5±8mV Gain Drift-100--100-ppm/°C Output Impedance Z OUT -100--100-ΩAC-Load Resistance R L 5--5--k ΩLoad Capacitance C L --1000--1000pF AOUT_REF Rejection (Notes 6, 7)AOR-40--40-dB Analog Reference Input AOUT_REF Input Voltage(Note 8)--0.2--0.2VppV RMS V pp22---------=AOR dB 20log 10AOUT _REFAOUT _REF AOUTx–---------------------------------------------------------⎝⎠⎛⎞⋅=Test conditions (unless otherwise specified): TA = -40 to +85°C; VCP =VA =3.13V to 3.47V; AOUT_REF = AGND = DGND =CPGND = 0V; VBIAS, +/-VFILT, and FLYP/N+/- capacitors as shown in Figure 3 on page 13; input test signal is a 997Hz sine wave at 0dBFS; measurement bandwidth 10Hz to 20kHz.8.Applying a DC voltage on the AOUT_REF pin will cause a DC offset on the DAC output. See Section4.1.3 for more information.1_2VRMS =01_2VRMS =1ParameterSymbol MinTypMaxMinTypMaxUnitDynamic Performance, Fs = 48, 96, and 192kHz (Notes 2, 3)Dynamic Range24-bit A-Weightedunweighted 16-bit A-Weightedunweighted9491--100979289----10097--1061039895----dB dB dB dB Total Harmonic Distortion + Noise24-bit 0dB-20dB-60dB 16-bit 0dB-20dB-60dB THD+N--------93-77-37-93-75-29-87-71-31-----------93-83-43-93-75-35-87-77-37---dB dB dB dB dB dB Idle Channel Noise / Signal-to-Noise Ratio (A-wt)-100--106-dB Interchannel Isolation(1kHz)-115--115-dB Analog Output (Note 2)Full Scale AOUTx Output Voltage (Notes 4, 5)0.98 1.05 1.12 1.96 2.10 2.25V RMS 2.772.973.17 5.54 5.94 6.36V pp Max Current Draw from an AOUTx Pin I OUTmax-575--575-µA Interchannel Gain Mismatch -0.1--0.1-dB Output Offset -±5±8-±5±8mV Gain Drift-100--100-ppm/°C Output Impedance Z OUT -100--100-ΩAC-Load Resistance R L 5--5--k ΩLoad Capacitance C L --1000--1000pF AOUT_REF Rejection (Notes 6, 7)AOR-40--40-dB Analog Reference Input AOUT_REF Input Voltage(Note 8)--0.2--0.2VppCOMBINED INTERPOLATION & ON-CHIP ANALOG FILTER RESPONSEThe filter characteristics have been normalized to the sample rate (Fs) and can be referenced to the desired sam-ple rate by multiplying the given characteristic by Fs. Notes:9.Response is clock-dependent and will scale with Fs.10.For Single- and Double-Speed Mode, the Measurement Bandwidth is from stopband to 3 Fs.For Quad-Speed Mode, the Measurement Bandwidth is from stopband to 1.34 Fs.11.De-emphasis is available only in Single-Speed Mode.12.Amplitude vs. Frequency plots of this data are available in “Digital Filter Response Plots” on page 22.ParameterMin TypMaxUnitSingle-Speed Mode - 48kHzPassband (Note 9)to -0.01dB corner to -3dB corner00--.454.499Fs Fs Frequency Response 10Hz to 20kHz -0.01-+0.01dB StopBand0.547--Fs StopBand Attenuation(Note 10)102--dB Total Group Delay (Fs = Sample Rate)-9.4/Fs -s Intra-channel Phase Deviation --±0.56/Fss Inter-channel Phase Deviation--0s De-emphasis Error (Note 11)(Relative to 1kHz)Fs = 44.1 kHz --±0.14dB Double-Speed Mode - 96kHzPassband (Note 9)to -0.01dB corner to -3dB corner00--.430.499Fs Fs Frequency Response 10Hz to 20kHz -0.01-0.01dB StopBand.583--Fs StopBand Attenuation(Note 10)80--dB Total Group Delay (Fs = Sample Rate)- 4.6/Fs -s Intra-channel Phase Deviation --±0.03/Fss Inter-channel Phase Deviation--0s Quad-Speed Mode - 192kHzPassband (Note 9)to -0.01 dB cornerto -3dB corner00--.105.490Fs Fs Frequency Response 10Hz to 20kHz -0.01-0.01dB StopBand.635--Fs StopBand Attenuation(Note 10)90--dB Total Group Delay (Fs = Sample Rate)- 4.7/Fs-sSWITCHING SPECIFICATIONS - SERIAL AUDIO INTERFACEParametersSymbol MinMaxUnitsMCLK Frequency 2.04851.2MHz MCLK Duty Cycle4555%Input Sample Rate (Auto selection)Single-Speed Mode Double-Speed Mode Quad-Speed ModeFs Fs Fs 88417054108216kHz kHz kHz LRCK Duty Cycle 4060%SCLK Pulse Width Low t sclkl 20-ns SCLK Pulse Width High t sclkh20-ns SCLK PeriodSingle-Speed Mode -s Double-Speed Mode -s Quad-Speed Mode-s SCLK rising to LRCK edge delay t slrd 20-ns SCLK rising to LRCK edge setup time t slrs 20-ns SDIN valid to SCLK rising setup time tsdlrs 20-ns SCLK rising to SDIN hold timet sdh20-nsFigure 1. Serial Input Timing1128()Fs ---------------------164()Fs ------------------164()Fs ------------------DIGITAL INTERFACE CHARACTERISTICSTest conditions (unless otherwise specified): AGND = DGND = CPGND = 0V; all voltages with respect to ground.INTERNAL POWER-ON RESET THRESHOLD VOLTAGESTest conditions (unless otherwise specified): AGND = DGND = CPGND = 0V; all voltages with respect to ground.Table 1. Power-On Reset Threshold VoltagesFigure 2. Power-On Reset Threshold SequenceParametersSymbolMin TypMaxUnitsHigh-Level Input Voltage 1.2V < VL ≤ 3.3V 0.9V ≤ VL ≤ 1.2V V IH V IH 0.7xVL 0.9xVL ----V V Low-Level Input Voltage 1.2V < VL ≤ 3.3V 0.9V ≤ VL ≤ 1.2VV IL V IL ----0.3xVL 0.1xVL V V Input Leakage Current I in--±10µA Input Capacitance-8-pFParametersSymbolMin Typ Max Units Internal Reset Asserted at Power-On V on1- 1.00-V Internal Reset Released at Power-On V on2- 2.14-V Internal Reset Asserted at Power-OffV off-2.00-VDC ELECTRICAL CHARACTERISTICSTest conditions (unless otherwise specified): VCP =VA =VL =3.3V; AGND = DGND = CPGND = 0V; SDIN =0; all voltages with respect to ground.Notes:13.Current consumption increases with increasing sample rate and increasing MCLK frequency. Typicalvalues are based on Fs =48kHz and MCLK =12.288MHz. Maximum values are based on highest sample rate and highest MCLK frequency; see Switching Specifications - Serial Audio Interface . Vari-ance between speed modes is small.14.Power-down is defined as RESET pin = Low with all clock and data lines held static low. All digital inputshave a weak pull-down (approximately 50k Ω) which is only present during reset. Opposing this pull-down will slightly increase the power-down current.15.Valid with the recommended capacitor value on VBIAS as shown in the typical connection diagram inSection 3.16.Typical voltage shown for “Initialization State”, see Section 4.7. Typical voltage may be up to 1.5V lowerduring normal operation.2.1Digital I/O Pin CharacteristicsInput and output levels and associated power supply voltage are shown in Table 2. Logic levels should not exceed the corresponding power supply voltage.Table 2. Digital I/O Pin CharacteristicsParametersSymbol Min Typ Max UnitsPower SuppliesPower Supply Current (Note 13)Normal OperationPower-Down, All Supplies (Note 14)I VCPI VA I VL I PD----362.40.1654330.2-mA mA mA µA Power Dissipation (All Supplies)Normal Operation, 1_2VRMS =0(Note 13)Power-Down (Note 14)--1271152-mW mW Power Supply Rejection Ratio (Note 15) (1 kHz)(60 Hz)PSRR --6060--dB dB DC Output VoltagesPin VoltageFLYP+ to FLYP-VFILT+ to GND (Note 16)FLYN+ to FLYN-GND to VFILT- (Note 16)VA to VBIAS-----3.36.66.66.62.1-----V V V V VPin Name Power SupplyI/O Driver ReceiverRESET VLInput -0.9V - 3.3V, with HysteresisMCLK Input -0.9V - 3.3V LRCK Input -0.9V - 3.3V SCLK Input -0.9V - 3.3V SDIN Input -0.9V - 3.3V DEM Input -0.9V - 3.3V I²S/LJ Input -0.9V - 3.3V 1_2VRMSInput-0.9V - 3.3V3.TYPICAL CONNECTION DIAGRAMFigure 3. Typical Connection Diagram4.APPLICATIONS4.1Line Outputs4.1.1Ground-Centered OutputsAn on-chip charge pump creates both positive and negative high-voltage supplies, which allows the full-scale output swing to be centered around ground. This eliminates the need for large DC-blocking capac-itors which create audible pops at power-on, allows the CS4353 to deliver a larger full-scale output at low-er supply voltages, and provides improved bandwidth frequency response.4.1.2Full-Scale Output Amplitude ControlThe full-scale output voltage amplitude is selected via the 1_2VRMS pin. When the pin is connected to VL, the full-scale output voltage at the AOUTx pins is approximately 2V RMS. When the pin is connected to GND, the full-scale output voltage at the AOUTx pins is approximately 1V RMS. Additional impedance between the AOUTx pin and the load will lower the voltage delivered to the load. See the DAC Analog Characteristics (Commercial - CNZ) or DAC Analog Characteristics (Automotive - DNZ) table for the com-plete specifications of the full-scale output voltage.4.1.3Pseudo-Differential OutputsThe CS4353 implements a pseudo-differential output stage. The AOUT_REF input is intended to be used as a pseudo-differential reference signal. This feature provides common mode noise rejection with single-ended signals. Figure4 shows a basic diagram outlining the internal implementation of the pseudo-differ-ential output stage, including a recommended stereo pseudo-differential output topology. If pseudo-differ-ential output functionality is not required, simply connect the AOUT_REF pin to ground next to the CS4353. If a split-ground design is used, the AOUT_REF pin should be connected to AGND. See the Ab-solute Maximum Ratings table for the maximum allowable voltage on the AOUT_REF pin. Applying a DC voltage on the AOUT_REF pin will cause a DC offset on the DAC output.Figure 4. Stereo Pseudo-Differential Output4.2Sample Rate Range/Operational Mode DetectThe CS4353 operates in one of three operational modes. The device will auto-detect the correct mode when the input sample rate (Fs), defined by the LRCK frequency, falls within one of the ranges illustrated in Table 3. Sample rates outside the specified range for each mode are not supported. In addition to a valid LRCK frequency, a valid serial clock (SCLK) and master clock (MCLK) must also be applied to the device for speed mode auto-detection; see Figure 9.Table 3. CS4353 Operational Mode Auto-Detect4.3System ClockingThe device requires external generation of the master (MCLK), left/right (LRCK) and serial (SCLK) clocks.The left/right clock, defined also as the input sample rate (Fs), must be synchronously derived from the MCLK signal according to specified ratios. The specified ratios of MCLK to LRCK, along with several stan-dard audio sample rates and the required MCLK frequency, are illustrated in Tables 4-6.Refer to Section 4.4 for the required SCLK timing associated with the selected Digital Interface Format and to “Switching Specifications - Serial Audio Interface” on page 10 for the maximum allowed clock frequen-cies.Table 4. Single-Speed Mode Standard FrequenciesTable 5. Double-Speed Mode Standard FrequenciesTable 6. Quad-Speed Mode Standard FrequenciesInput Sample Rate (Fs)Mode8 kHz - 54 kHz Single-Speed Mode 84 kHz - 108 kHz Double-Speed Mode 170 kHz - 216 kHzQuad-Speed ModeSample Rate(kHz)MCLK (MHz)256x384x512x768x1024x328.192012.288016.384024.576032.768044.111.289616.934422.579233.868845.15844812.288018.432024.576036.864049.1520Sample Rate(kHz)MCLK (MHz)128x192x256x384x512x88.211.289616.934422.579233.868845.15849612.288018.432024.576036.864049.1520Sample Rate(kHz)MCLK (MHz)128x192x256x176.422.579233.868845.158419224.576036.864049.15204.4Digital Interface FormatThe device will accept audio samples in either I²S or Left-Justified digital interface formats, as illustrated in Table 7.The desired format is selected via the I²S/LJ pin. For an illustration of the required relationship between the LRCK, SCLK and SDIN, see Figures 5-6. For all formats, SDIN is valid on the rising edge of SCLK. Also,SCLK must have at least 32 cycles per LRCK period in the Left-Justified format.For more information about serial audio formats, refer to Cirrus Logic Application Note AN282: The 2-Chan-nel Serial Audio Interface: A Tutorial , available at .Table 7. Digital Interface FormatFigure 5. I²S, up to 24-Bit DataFigure 6. Left-Justified up to 24-Bit DataI²S/LJDescriptionFigure0I²S, up to 24-bit Data51Left-Justified, up to 24-bit Data64.5De-Emphasis ControlThe device includes on-chip digital de-emphasis. Figure 7 shows the de-emphasis curve for Fs equal to 44.1kHz. The frequency response of the de-emphasis curve scales with changes in the sample rate, Fs.The de-emphasis error will increase for sample rates other than 44.1kHz.When the DEM pin is connected to VL, the 44.1kHz de-emphasis filter is activated. When the DEM pin is connected to GND, the de-emphasis filter is turned off.Note: De-emphasis is only available in Single-Speed Mode.4.6Internal Power-On ResetThe CS4353 features an internal power-on reset (POR) circuit. The POR circuit allows the RESET pin to be connected to VL during power-up and power-down sequences if the external reset function is not needed.This circuit monitors the VCP supply and automatically asserts or releases an internal reset of the DAC’s digital circuitry when the supply reaches defined thresholds (see “Internal Power-On Reset Threshold Volt-ages” on page 11). No external clocks are required for the POR circuit to function.Figure 8. Internal Power-On Reset CircuitWhen power is first applied, the POR circuit monitors the VCP supply voltage to determine when it reaches a defined threshold, V on1. At this time, the POR circuit asserts the internal reset low, resetting all of the digital circuitry. Once the VCP supply reaches the secondary threshold, V on2, the POR circuit releases the internal reset.Figure 7. De-Emphasis Curve, Fs = 44.1 kHzNote:For correct operation of the internal POR circuit, the voltage on VL must rise before or simulta-neously with VCP.When power is removed and the VCP voltage reaches a defined threshold, V off, the POR circuit asserts the internal reset low, resetting all of the digital circuitry.4.7InitializationWhen power is first applied, the DAC enters a reset (low power) state at the beginning of the initialization sequence. In this state, the AOUTx pins are weakly pulled to ground and VBIAS is connected to VA.The device will remain in the reset state until the RESET pin is brought high. Once the RESET pin is high, the internal digital circuitry is reset and the DAC enters a power-down state until MCLK is applied. Alterna-tively, if no external reset control is required, the internal power-on reset can be used by tying the RESET pin to VL (see Section 4.6).Once MCLK is valid, the device enters an initialization state in which the charge pump powers up and charg-es the capacitors for both the positive and negative high-voltage supplies.Once LRCK and SCLK are valid, the number of MCLK cycles is counted relative to the LRCK period to de-termine the MCLK/LRCK frequency ratio. Next, the device enters the power-up state in which the interpo-lation and decimation filters and delta-sigma modulators are turned on, the internal voltage reference, VBIAS, powers up to normal operation, the analog output pull-down resistors are removed, and power is applied to the output amplifiers.After this power-up state sequence is complete, normal operation begins and analog output is generated.If valid MCLK, LRCK, and SCLK are applied to the DAC before RESET is set high, the total time from RE-SET being set high to the analog audio output from AOUTx is less than 50ms.See Figure9 for a diagram of the device’s states and transition conditions.Figure 9. Initialization and Power-Down Sequence Diagram4.8Recommended Power-Up and Power-Down Sequences4.8.1Power-Up Sequences4.8.1.1External RESET Power-Up SequenceFollow the power-up sequence below if the external RESET pin is used:1.Hold RESET low while the power supplies are turned on.2.Set the I²S/LJ, 1_2VRMS, and DEM configuration pins to the desired state.3.Provide the correct MCLK, LRCK, and SCLK signals locked to the appropriate frequencies asdiscussed in Section 4.3.4.After the power supplies, configuration pins, and clock signals are stable, bring RESET high. Thedevice will initiate the power-up sequence seen in Figure9. The sequence will complete and audiowill be output from AOUTx within 50ms after RESET is set high.4.8.1.2Internal Power-On Reset Power-Up SequenceFollow the power-up sequence below if the internal power-on reset is used:1.Hold RESET high (connected to VL) while the power supplies are turned on. The power-on resetcircuitry will function as described in Section 4.6.2.Set the I²S/LJ, 1_2VRMS, and DEM configuration pins to the desired state.3.After the power supplies and configuration pins are stable, provide the correct MCLK, LRCK, andSCLK signals to progress from the ‘Power-Down State’ in the power-up sequence seen in Figure9.The sequence will complete and audio will be output from the AOUTx pins within 50ms after validclocks are applied.4.8.2Power-Down Sequences4.8.2.1External RESET Power-Down SequenceFollow the power-down sequence below if the external RESET pin is used:1.For minimal pops, set the input digital data to zero for at least 8192 consecutive samples.2.Bring RESET low.3.Remove the power supply voltages.4.8.2.2Internal Power-On Reset Power-Down SequenceFollow the power-down sequence below if the internal power-on reset is used:1.For minimal pops, set the input digital data to zero for at least 8192 consecutive samples.2.Remove the MCLK signal without applying any glitched pulses to the MCLK pin.3.Remove the power supply voltages.Note: A glitched pulse is any pulse that is shorter than the period defined by the minimum/maximum MCLK signal duty cycle specification and the nominal frequency of the input MCLK signal. A transient may occur on the analog outputs if the MCLK signal duty cycle specification is violated when the MCLK signal is removed during normal operation; see “Switching Specifications - Serial Audio Interface” on page10.。

BD6753KV中文资料

Japan / (Internal Sales)

Tokyo Yokohama Nagoya Kyoto 2-1-1, Yaesu, Chuo-ku, Tokyo 104-0082 TEL : +81(3)5203-0321 FAX : +81(3)5203-0300 2-4-8, Shin Yokohama, Kohoku-ku, Yokohama, Kanagawa 222-8575 TEL : +81(45)476-2131 FAX : +81(45)476-2128 Dainagayo Building 9F 3-28-12, Meieki, Nakamura-ku, Nagoya,Aichi 450-0002 TEL : +81(52)581-8521 FAX : +81(52)561-2173 579-32 Higashi Shiokouji-cho, Karasuma Nishi-iru, Shiokoujidori, Shimogyo-ku, Kyoto 600-8216 TEL : +81(75)311-2121 FAX : +81(75)314-6559 TEL : +81(45)476-9270 FAX : +81(045)476-9271

Please contact our sales offices for details ;

U.S.A / San Diego Atlanta Dallas Germany / Dusseldorf TEL : +1(858)625-3630 TEL : +1(770)754-5972 TEL : +1(972)312-8818 TEL : +49(2154)9210 FAX : +1(858)625-3670 FAX : +1(770)754-0691 FAX : +1(972)312-0330 FAX : +49(2154)921400 FAX : +44(1)908-282-528

常见发烧CD机光头、芯片对照表