频率合成器地设计

基于DDS数字频率合成信号发生器的设计

S(n) S(t)

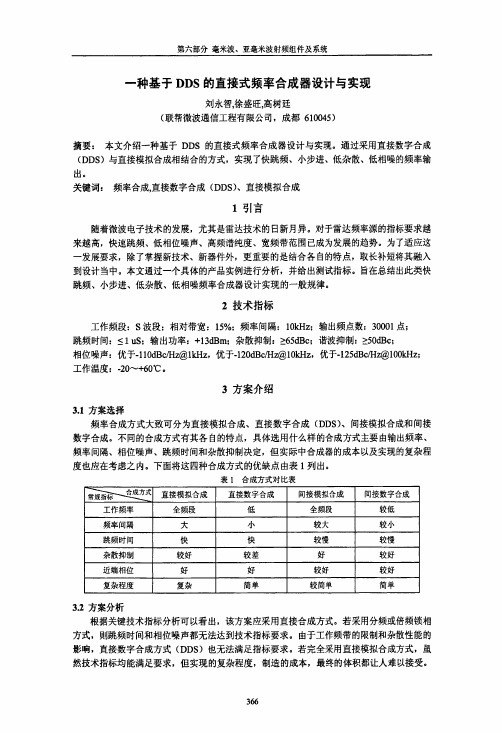

DDS基本原理

相位累 加器

相位地址 寄存器

参考信号fc

正弦查 表(ROM)

D/A

LPF

图一

典型DDS的原理框图

频 率 控 制 字 K

N位

S(n)

S(t)

相位累 加器

相位地址 寄存器

参考信号fc

正弦查 表(ROM)

D/A

LPF

工作过程为: 3 、最后经 D/A转换和滤波将波形数据转换成所需要的波 12 、 根据参考信号 fc的时钟脉冲,N位累加器将频率 、波形表根据这个地址值输出相应的波形数据 S(n) 形。 K循环累加,把相加后的结果通过相位寄存 控制字

+5V

入

端

+5V

VCC

3.9K

R

1

10uF/10V

EC02

1

1

1

1

1

0.1uF

C

4

3

2

1

0

9

8

7

6

5

4

3

2

1

2

AD9850

U

Q

QOUTB

RSET

A

A

CLK_IN

FQ_UD

W_CLK

D

D

D

D

D

D

1

O

V

G

V

G

0

1

2

3

U

D

N

D

N

T

D

D

DDBiblioteka 0.1uFC3

0.1uF

C

G

4 N DACBL IOUTB A A RESET

第4章数字频率合成器的设计讲解

第 4 章数字频率合成器的设计随着通信、雷达、宇航和遥控遥测技术的不断发展,对频率源的频率稳定度、频谱纯度、频率范围和输出频率的个数提出越来越高的要求。

为了提高频率稳定度,经常采用晶体振荡器等方法来解决,但它不能满足频率个数多的要求,因此,目前大量采用频率合成技术。

频率合成是通信、测量系统中常用的一种技术,它是将一个或若干个高稳定度和高准确度的参考频率经过各种处理技术生成具有同样稳定度和准确度的大量离散频率的技术。

频率合成的方法很多,可分为直接式频率合成器、间接式频率合成器、直接式数字频率合成器( DDS) 。

直接合成法是通过倍频器、分频器、混频器对频率进行加、减、乘、除运算,得到各种所需频率。

该方法频率转换时间快(小于100ns),但是体积大、功耗大,目前已基本不被采用。

锁相式频率合成器是利用锁相环( PLL )的窄带跟踪特性来得到不同的频率。

该方法结构简化、便于集成,且频谱纯度高,目前使用比较广泛。

直接数字频率合成器(Direct Digital Frequency Synthesis简称:DDS)是一种全数字化的频率合成器,由相位累加器、波形ROM,D/A 转换器和低通滤波器构成, DDS 技术是一种新的频率合成方法, 它具有频率分辨率高、频率切换速度快、频率切换时相位连续、输出相位噪声低和可以产生任意波形等优点。

但合成信号频率较低、频谱不纯、输出杂散等。

这里将重点研究锁相式频率合成器。

本章采用锁相环, 进行频率合成器的设计与制作4.1设计任务与要求1.设计任务:利用锁相环,进行频率合成器的设计与制作2.设计指标:(1)要求频率合成器输出的频率范围f0为1kHz〜99kHz;(2)频率间隔f为1kHz;(3)基准频率采用晶体振荡频率,要求用数字电路设计,频率稳定度应优于10一4;(4)数字显示频率;(5)频率调节采用计数方式。

3•设计要求:(1)要求设计出数字锁相式频率合成器的完整电路。

(2)数字锁相式频率合成器的各部分参数计算和器件选择。

基于MC145151-2PPL频率合成器的设计

一

频 率 合 成 器 的 频 率分 辨 率 。 改 变 R数值 的 大 小 ,

准 频率源相组合 ,就能产生与标准信号源有相 同的频率稳定度、准确度的众多频率点。

可改变频率合成器的分辨率。由以上可以看 出 当环路锁定后,压控振荡器的输出频率严格 与 输入 频率 行相等 。同时在 一定 范围 内跟踪 输 入信号频率变化 ,具有 良好 的跟踪特性 。只要 L P F通频带设计合理,整个环路就具有 良好的

窄带滤波特性。

1 M C 1 4 5 1 5 1 - 2 锁相环 简介

MC1 4 5 1 5 1 - 2是 一 块 双 列 直 插 式 C M OS大 规 模 集 成 电路 , 由 4位 总 线 输 入 、 锁 存 器 选 通

个 高 稳 定度 的 标 准 频 率 f s , 经 参 考 分 频 器 进

:

R A 2 R A 1 R A o M c 1 4 5 1 5 1 — 2

: : M A X 3 0 8

;

随 着 移 动 通 信 、雷 达 技 术 以及 遥 测 、 遥

感测控技术不断发展 ,各种 系统对频 率源 的要 求越来越高 , 不但 要求频率稳定度和准确度高, 而且还要求能方便 的改变 收发频率。特别是无

图一 1 基 本锁相 环 频率合 成 器组 成框 图

【 关键词 】频率合成 V C O 锁相环 频率 源 分

频 器

广 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 1 广 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 1

数字频率合成器设计实例

数字频率合成器设计实例数字频率合成器设计实例数字频率合成器(Digital Frequency Synthesizer)是一种能够产生不同频率信号的设备。

它通过使用数字技术和数学算法来合成所需的频率,具有高精度和稳定性。

在本文中,我们将逐步介绍数字频率合成器的设计过程。

1. 设定所需频率范围:首先,确定所需合成的频率范围。

这取决于具体应用,例如音频处理、无线通信等。

假设我们的频率范围为1Hz到10kHz。

2. 确定采样率:采样率是指每秒钟对信号进行采样的次数。

根据香农抽样定理,采样率应大于信号最高频率的两倍。

在我们的例子中,最高频率为10kHz,因此选择采样率为至少20kHz。

3. 选择数字信号处理器(DSP):为了实现数字频率合成器,我们需要选择一种适合的DSP芯片。

DSP芯片能够高效地执行数字信号处理任务,例如信号生成和滤波。

选择一款性能强大且易于编程的DSP 芯片,以满足所需的合成要求。

4. 设计频率控制模块:频率控制模块是数字频率合成器的核心部分,用于生成所需频率的数字信号。

它通常由相位锁定环(PLL)和数字控制振荡器(NCO)组成。

a. 相位锁定环(PLL):PLL是一种控制系统,通过比较输入信号的相位和参考信号的相位差异来产生所需频率的输出信号。

通过调整参考信号的频率和相位,PLL可以实现精确的频率合成。

b. 数字控制振荡器(NCO):NCO是一种可编程振荡器,能够生成具有可变频率的数字信号。

通过调整输入的控制参数,NCO能够实现不同频率的信号合成。

5. 编程实现:根据DSP芯片的编程手册和软件开发工具,编写相应的代码实现频率控制模块。

通过配置PLL和NCO的参数,以及设置合适的参考信号,实现所需频率的合成。

6. 验证和调试:使用示波器或频谱分析仪等测试工具,验证合成的频率是否符合要求。

如果发现频率偏差或其他问题,可以通过调整PLL和NCO的参数来进行调试和校准。

7. 优化和改进:根据实际应用需求和反馈,对数字频率合成器进行优化和改进。

简易频率合成器课程设计

简易频率合成器课程设计一、课程目标知识目标:1. 学生能理解频率合成器的基本原理,掌握其组成部分及功能。

2. 学生能掌握简易频率合成器的搭建方法,了解不同类型频率合成技术的优缺点。

3. 学生能运用所学的电子技术知识,分析并解决简易频率合成器中可能出现的问题。

技能目标:1. 学生能够独立完成简易频率合成器的搭建,提高动手实践能力。

2. 学生能够运用所学知识,对简易频率合成器进行调试和优化,提升问题解决能力。

3. 学生能够通过小组合作,提高沟通与协作能力。

情感态度价值观目标:1. 学生对电子技术产生兴趣,培养探究精神和创新意识。

2. 学生在实践过程中,树立安全意识,养成严谨的科学态度。

3. 学生通过课程学习,认识到电子技术在现实生活中的应用,增强学以致用的意识。

课程性质:本课程为电子技术实践课程,以理论为基础,侧重实践操作。

学生特点:学生为高中年级,具备一定的电子技术基础知识,对实践操作有较高的兴趣。

教学要求:结合学生特点,注重理论与实践相结合,提高学生的动手实践能力和问题解决能力。

通过课程目标的实现,使学生在知识、技能和情感态度价值观方面得到全面提升。

在教学过程中,将目标分解为具体的学习成果,便于教学设计和评估。

二、教学内容1. 理论知识:- 频率合成器的基本原理及其应用场景- 频率合成器的分类及各类型优缺点- 简易频率合成器的组成部分及其功能- 相关电子元器件的特性和选型2. 实践操作:- 简易频率合成器的搭建方法与步骤- 频率合成器的调试与优化技巧- 故障分析与问题解决方法3. 教学大纲:- 第一课时:导入频率合成器的基本概念,介绍其应用场景,学习相关电子元器件知识。

- 第二课时:学习频率合成器的分类及优缺点,分析简易频率合成器的组成部分。

- 第三课时:讲解简易频率合成器的搭建方法,进行实践操作。

- 第四课时:对搭建的简易频率合成器进行调试与优化,学习故障分析与问题解决方法。

教材章节关联:本教学内容与教材中“频率合成器”章节相关,涉及的知识点包括频率合成器原理、分类、搭建与调试等。

频率合成器的设计与制作

频率合成器的设计与制作这次课程设计的主要内容是频率合成器的设计与制作,首先了解什么是频率合成器。

它有哪几个部分组成,哪些参数对它的技术指标有影响,然后是选择元器件,搭试电路,排版安装,测试数据,分析结果。

随着通信、雷达、宇航和遥控遥测技术的不断发展,对频率源的频率稳定度、频谱纯度、频率范围和输出频率的个数提出越来越高的要求。

为了提高频率稳定度,经常采用晶体振荡器等方法来解决,但它不能满足频率个数多的要求,因此,目前大量采用频率合成技术。

频率合成器:通过对频率进行加、减、乘、除的运算,可从一个高稳定度和高准确度的标准频率源,产生大量的具有同一稳定度和准确度的不同频率。

频率合成的方法很多,大致可分为直接合成法和间接合成法俩种。

直接合成法是通过倍频器、分频器、混频器对频率进行加、减、乘、除运算,得到各种所需频率。

直接合成法的优点是频率转换时间短,并能产生任意小的频率增量。

但它也存在一些不可克服的缺点,用这种方法合成的频率范围将受到限制。

更重要的是由于大量的倍频,混频等电路,就要有不少滤波电路,使合成器的设备十分复杂,而且输出端的谐波、噪声及寄生频率难以抑制。

而间接合成法就是利用锁相环路的窄带跟踪特性来得到不同的频率。

频率合成器是从一个或多个参考频率中产生多种频率的器件。

它在信息通信方面得到了广泛的应用,并有新的发展。

频率合成器的核心组成是锁相环路(PLL)。

锁相的意义是一种相位负反馈控制系统,它利用相位的稳定来实现频率锁定,即“锁相”。

控制电路是利用反馈原理实现对自身的调节与控制。

AGC、AFC、PLL 分别对交流信号的三个参数振幅、频率、相位进行自动控制。

能够完成两个电信号相位同步的自动控制闭环系统叫做锁相环,简称PLL。

实现锁相的方法称为“锁相技术”。

锁相环路广泛应用于广播通信、频率合成、自动控制及时钟同步等技术领域。

这里首先对锁相环路作一个简单介绍。

9.1 锁相环路的基本组成及工作原理9.1.1 锁相环路的基本组成锁相环路的基本组成框图如图9.1.1所示。

一种基于DDS的直接式频率合成器设计与实现

4实验结果及分析

通过以上的分析,设计出具体的电路。利用相位噪声测试仪可测出该频率合成器的输 出相位噪声,图2给出S波段相噪测试曲线。

H孙搬№i铀10.00d吖R西嘞冉抽IB洳

’’_‘~r

一一L

锄.∞.6e.O畦il№}2l土9'll

≈jh啪^h

k}醢

潞∥

7l程 璐裂罟嬲簇勰; 一

耩 :嚣i

一i,,

1引言

随着微波电子技术的发展,尤其是雷达技术的日新月异。对于雷达频率源的指标要求越 来越高,快速跳频、低相位噪声、高频谱纯度、宽频带范围已成为发展的趋势。为了适应这 一发展要求,除了掌握新技术、新器件外,更重要的是结合各自的特点,取长补短将其融入 到设计当中。本文通过一个具体的产品实例进行分析,并给出测试指标。旨在总结出此类快 跳频、小步进、低杂散、低相噪频率合成器设计实现的一般规律。

2技术指标

工作频段:S波段;相对带宽:15%:频率间隔:10kHz;输出频点数:30001点; 跳频时间:5

l

uS;输出功率:+13dBm;杂散抑制:>65dBc;谐波抑制:>50dBc;

相位噪声:优于一1 10dBc/Hz@IkHz,优于-120dBc/Hz@10kHz,优于一125dBc/Hz@100kHz; 工作温度:.20~+60℃。

^屑依

由图1方案可知最终输出频率:Tout=厶慨+等},其中M为谐波发生器的倍频次数。

Z

为了得到密集频率覆盖,要求DDS输出带宽必须大于等于晶振信号频率的一半,即 BWDDS>__fi'/2。其工作过程如下,当频率合成器在同一BWDDS内进行频率转换时,通过控制

367

第六部分毫米波、亚毫米波射频组件及系统

然技术指标均能满足要求,但实现的复杂程度,制造的成本,最终的体积都让人难以接受。

基于ADF4360-1的2.4G频率合成器设计

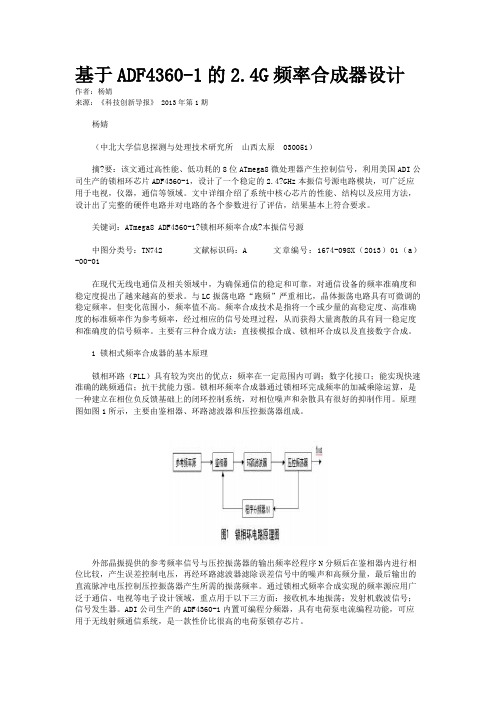

基于ADF4360-1的2.4G频率合成器设计作者:杨婧来源:《科技创新导报》 2013年第1期杨婧(中北大学信息探测与处理技术研究所山西太原 030051)摘?要:该文通过高性能、低功耗的8位ATmega8微处理器产生控制信号,利用美国ADI公司生产的锁相环芯片ADF4360-1,设计了一个稳定的2.4?GHz本振信号源电路模块,可广泛应用于电视,仪器,通信等领域。

文中详细介绍了系统中核心芯片的性能、结构以及应用方法,设计出了完整的硬件电路并对电路的各个参数进行了评估,结果基本上符合要求。

关键词:ATmega8 ADF4360-1?锁相环频率合成?本振信号源中图分类号:TN742 文献标识码:A 文章编号:1674-098X(2013)01(a)-00-01在现代无线电通信及相关领域中,为确保通信的稳定和可靠,对通信设备的频率准确度和稳定度提出了越来越高的要求。

与LC振荡电路“跑频”严重相比,晶体振荡电路具有可微调的稳定频率,但变化范围小,频率值不高。

频率合成技术是指将一个或少量的高稳定度、高准确度的标准频率作为参考频率,经过相应的信号处理过程,从而获得大量离散的具有同一稳定度和准确度的信号频率。

主要有三种合成方法:直接模拟合成、锁相环合成以及直接数字合成。

1 锁相式频率合成器的基本原理锁相环路(PLL)具有较为突出的优点:频率在一定范围内可调;数字化接口;能实现快速准确的跳频通信;抗干扰能力强。

锁相环频率合成器通过锁相环完成频率的加减乘除运算,是一种建立在相位负反馈基础上的闭环控制系统,对相位噪声和杂散具有很好的抑制作用。

原理图如图1所示,主要由鉴相器、环路滤波器和压控振荡器组成。

外部晶振提供的参考频率信号与压控振荡器的输出频率经程序N分频后在鉴相器内进行相位比较,产生误差控制电压,再经环路滤波器滤除误差信号中的噪声和高频分量,最后输出的直流脉冲电压控制压控振荡器产生所需的振荡频率。

通过锁相式频率合成实现的频率源应用广泛于通信、电视等电子设计领域,重点用于以下三方面:接收机本地振荡;发射机载波信号;信号发生器。

频率合成器的设计3-5-2

• 3.VCO的调谐范围 的调谐范围

因为频率覆盖范围是36~57MHz,根据变容二极管的 根据变容二极管的 因为频率覆盖范围是 调谐范围,应采用分段方案实现 调谐范围,应采用分段方案实现 • 第一频段 36~46MHz • 第二频段 46~57MHz

N 1max = 46 MHz N 2max = 57 MHz

• 5.确定自然角频率 ω n 确定自然角频率

根据技术要求,应能通过音频调相信号 故 根据技术要求 应能通过音频调相信号,故 应能通过音频调相信号 先确定带宽,即截止频率 先确定带宽 即截止频率 ω

c

ωc = 2π f = 2π × 3 × 103 rad s

则

ωn = ωc

[2ξ + 1 + (2ξ + 1) + 1]

K0 Kd R1C = τ 1 = 2 N maxω n

K0 Kd 2.83 × 10−6 R1 = = 2 N maxω n C C

取电容标称值 C = 0.15 µ F 则 R1 = 1887Ω

§3-5-2

频率合成器的设计实例

取标称值 R1 = 1.8 K Ω 而

2ξ R2 = = 17575Ω ω nC

§3-5-2

频率合成器的设计实例

§3-5-2

频率合成器的设计实例

• [例]设计一个能输出音频调相信号的数字式频 例 设计一个能输出音频调相信号的数字式频 率合成器. 率合成器 • 一.技术指标 技术指标 • 1.工作频率 工作频率 f = 36 57 MHz

0

• 2.输出频率间隔 输出频率间隔 • 3.转换时间 转换时间

K0 =

2π × (46 − 36) × 106 rad 10V

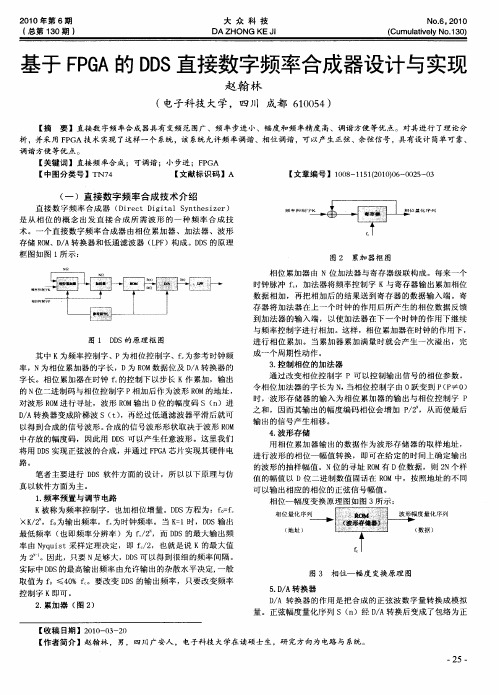

基于FPGA的DDS直接数字频率合成器设计与实现

图 5

期只采样 2点,难 以保证输出精度 。为了保证输 出精度 ,规 定最低每 周期采样 8 点,此时 K 2/ = 2 ,则 :f = = 8 18 … K×

f/ 1 . 2 H c2= 6 5 M z 5

( )最 小步长的正弦波 ( 6 1 图 )

频 率 控 制 字 : 00 0 0 0 00001 相 位 控 制 字 : 00 0 0 0 00000

r — V v\ 1 / 厂 八 八八 / / ^厂 r u 厂 九 \ ^\ 、

图7

仿 真测得正弦波频率为:2 2 . 8 8 7 s2 .6 s /( 0 3 76 u 一 0 2 u )≈ 1. 4 3 H ,与计算参 数相 近,误差来 自于仿真测量时的显 5 6 1M z

2 波形存储 .

本设计 中波形存储 为连续存储 ,对正 弦波进行采样 利用 O a ts制造 一个 R M ,进 行 查值 操 作 , 波 形 的 存 储 方 法 ur u O表 在 上可 以有两种 方案 ,一个是对正弦波从 0到 2 进行采样 ,在 兀 这 次 设计 和 以上 的 参 数 选 取 上 均 基 于 这 种 方 案 ,这 个 方 案 的

示 误差 。

正弦波幅值的获得 ,可通过 C语言编程得到,将 C程序

所 得 结 果 导 出 到一 个 文 件 中 便 可 得 到 正 弦波 幅 值 。 3 系 统 设计 . 由波 形 存 储 模 式 ,设 计 系统 模 型 框 图 4 :

( )最 大 步 长 的 正 弦波 ( 7 2 图 ) 频 率 控 制 字 : 0 10 0 0 00000 相 位 控 制 字 :0 0 0 0 0 0 0 0 00

优 点 是 实现 简 单 ,思 路 清 晰 ;另一 种 方 案 是 对 正 弦波 从 0到

频率合成器设计

题目:频率合成器——基于4046的锁相环频率合成器一、课程设计目的:1.熟悉期间4046的基本原理和性能。

2.掌握频率合成器的原理和合成技术。

3.熟悉和掌握所学的各个器件,芯片,以及熟练的应用。

4.理解入锁和失锁的概念和原理。

5.融会贯通所学的高频知识,能够灵活的应用和设计。

6.理解和熟练分析基本的电路。

二、课程设计题目描述和要求:频率合成是以一个或少量的高准确度和高稳定度的标准频率作为参考频率,由此导出多个或大量的输出频率,这些输出的准确度与稳定度与参考频率是一致的。

锁相的意义是相位同步的自动控制,能够完成两个电信号相位同步的自动控制闭环系统叫做锁相环,简称PLL。

它广泛应用于广播通信、频率合成、自动控制及时钟同步等技术领域。

锁相环主要由相位比较器(PC)、压控振荡器(VCO)、低通滤波器三部分组成。

频率合成器有直接式频率合成器、直接数字式频率合成器及锁相频率合成器三种基本模式,前两种属于开环系统,因此是有频率转换时间短,分辨率较高等优点,而锁相频率合成器是一种闭环系统,其频率转换时间和分辨率均不如前两种好,但其结构简单,成本低。

并且输出频率的准确度不逊色与前两种,因此采用锁相频率合成。

频率合成器是一个系统,最初产生的一系列频率为参考频率的整数倍,参考频率通常是固定的。

这样的合成器称为整数N频率合成器。

频率合成器技术也不断前进,出现也很多新型的频率合成电路,并在通信电路中得到广泛应用。

锁相环由鉴相器、环路滤波器和压控振荡器组成。

频率合成一个或少量的高准确度高稳定的标准频率作为参考频率,由此导出多个或大量的输出频率.这些输出频率的准确度和稳定度与参考频率是一致的,频率合成器就是用来产生这些频率的部件.技术要求:1.达到输出为4-10M赫兹。

2.频率间隔为5K 赫兹。

3.基于4046芯片的设计。

三、课程设计报告内容及原理:原理框图如下,锁相环路对稳定度的参考振动器锁定,环内串接可编程的分频器,通过改变分频器的分配比N ,从而就得到N 倍参考频率的稳定输出。

仿真频率合成器课程设计

仿真频率合成器课程设计一、课程目标知识目标:1. 学生能够理解频率合成器的基本原理,掌握仿真频率合成器的组成及各部分功能。

2. 学生能够运用所学知识,分析并设计简单的仿真频率合成器电路。

3. 学生掌握相关电子元器件的特性和选型方法,并能应用于仿真频率合成器的设计。

技能目标:1. 学生能够运用仿真软件进行频率合成器电路的设计、搭建和调试。

2. 学生具备独立分析和解决频率合成器实际问题的能力。

情感态度价值观目标:1. 学生通过课程学习,培养对电子工程技术的兴趣,提高创新意识和实践能力。

2. 学生养成合作、探究的学习态度,培养严谨、踏实的科学精神。

3. 学生能够认识到频率合成器在通信、雷达等领域的重要应用,增强国家使命感和社会责任感。

课程性质:本课程为电子技术与实践课程,旨在帮助学生掌握频率合成器的基本原理和设计方法,培养实践操作能力。

学生特点:学生处于高中年级,已具备一定的电子基础知识和实践能力,对新技术和新知识充满好奇心。

教学要求:结合学生特点,注重理论与实践相结合,充分调动学生的主观能动性,提高学生的动手能力和创新能力。

通过课程学习,使学生能够达到上述课程目标,为后续相关专业课程打下坚实基础。

二、教学内容本课程依据课程目标,结合教材相关章节,组织以下教学内容:1. 频率合成器原理:介绍频率合成器的基本概念、工作原理及性能指标,重点讲解锁相环(PLL)和直接数字合成器(DDS)的原理及其在频率合成中的应用。

(对应教材第3章)2. 仿真频率合成器设计:分析仿真频率合成器的组成部分,包括振荡器、分频器、混频器等,讲解各部分的设计方法和选型原则。

(对应教材第4章)3. 电子元器件选型与应用:介绍常用电子元器件的特性和选型方法,如晶体振荡器、集成运算放大器等,并举例说明其在频率合成器中的应用。

(对应教材第5章)4. 仿真软件操作与实践:指导学生使用Multisim、Proteus等仿真软件进行频率合成器电路的设计、搭建和调试,培养学生的实践操作能力。

频率合成器设计指南

频率合成器设计指南嘿,朋友们!今天咱来聊聊频率合成器设计这档子事儿。

你说频率合成器像不像一个神奇的魔法盒子呀!它能变出各种我们想要的频率来。

这可太重要啦,不管是在通信领域,还是在其他好多地方,都少不了它的身影呢。

咱设计频率合成器的时候,就好像是在搭积木一样,得一块一块地精心挑选和摆放。

首先得想好咱要实现啥样的功能,是要高精度呢,还是要宽范围呀?这就好比你要盖房子,得先确定是盖个小别墅还是大高楼。

然后呢,选器件可不能马虎。

这就跟你挑衣服似的,得找质量好、合适的。

那些电阻、电容啥的,都得好好琢磨琢磨,它们可关系到整个合成器的性能呢。

要是选得不好,那可就像穿了件不合身的衣服,别扭得很。

还有啊,电路的设计也特别关键。

这就像是给合成器画一幅蓝图,得把每条线、每个节点都考虑清楚。

不能这儿多一块,那儿少一块的,不然最后出来的东西可就没法用啦。

再说说调试吧,这可真是个需要耐心的活儿。

就跟你调校一个精密仪器似的,得一点点地试,一点点地调。

有时候可能调了半天也没啥效果,但别灰心呀,说不定下一次就成功了呢。

设计频率合成器可不是一朝一夕就能搞定的事儿,这得靠咱的经验和智慧呀。

就好像学骑自行车,一开始可能会摔跟头,但慢慢地就熟练了。

咱在设计的过程中也会遇到各种问题,但别怕呀,办法总比困难多嘛。

你想想,当你成功地设计出一个性能超棒的频率合成器的时候,那得多有成就感呀!就好像你自己亲手打造了一件绝世珍宝一样。

所以呀,朋友们,大胆地去尝试设计频率合成器吧!别担心会失败,失败了咱就再来一次。

只要咱坚持下去,就一定能设计出属于我们自己的优秀频率合成器!加油吧!。

基于adf4351的频率合成器设计

Liang Jun (Guangzhou Haige Communication Group Co., Ltd.,Guangzhou Guangdong,510000)

Abstract: First, the basic principle of PLL is introduced, then a broadband frequency synthesizer chip adf4351 integrated with VCO is introduced, and a frequency synthesizer with the output of 154.8mhz212.775mhz is designed with this chip. The measured phase noise and spurious index can meet the design requirements well, and can meet the needs of various communication systems for signal sources. Key words: frequency synthesizer; broadband; low phase noise; low spurious

成芯片,它结合外部环路滤波器和外部参考频率使用时,可 实现小数 N 分频或者整数 N 分频锁相环(PLL)频率合成器。 ADF4351 的基波输出频率范围是 2200MHz 到 4400MHz。此外, 利用 1/2/4/8/16/32 分频电路,用户可以产生低至 35MHz 的 RF 输出频率。其结构框图如图 3 所示。

开始端口配置液晶显示按键检测电机驱动初始化霍尔传感器信号检测及处理按键检测及处理液晶显示驱动图6单片机控制流程图4结论本文研究和设计的霍尔传感器转速测量电路可实现霍尔传感器信号和电机转速的测量模拟被测物体转动的直流电机转速的调节可通过液晶显示器直观显示测量误差很小

Ka波段频率合成器设计

K a 波段频率合成器设计柴 俊,张必龙(中国船舶重工集团公司第七二三研究所,江苏扬州225101)摘要:提出了一种K a 波段低杂散㊁捷变频频率合成器设计方案㊂该方案采用直接数字合成(D D S )+直接上变频的频率合成模式,D D S 1产生360~600MH z 低杂散中频信号,D D S 2产生波形信号㊂经过4次上变频㊁分段滤波㊁放大后,该方案实现了宽带㊁低杂散㊁捷变频频率合成器的设计,为系统提供本振信号㊁激励信号等㊂根据设计方案,制作了实物㊂实测该频率合成器输出杂散小于-75d B c ,频率切换时间小于200n s ,带宽2G H z ,步进1MH z ,35G H z 载波处相噪约-95d B c /H z @1k H z㊂该频率合成器不仅可广泛应用于雷达㊁对抗㊁通信等领域,也为其他类似需求频率合成器提供了参考㊂关键词:频率合成器;杂散;毫米波中图分类号:T N 74 文献标识码:A 文章编号:C N 32-1413(2021)01-0087-05D O I :10.16426/j .c n k i .jc d z d k .2021.01.018D e s i g n o f K a -b a n d F r e q u e n c y S yn t h s i z e r C H A I J u n ,Z H A N G B i -l o n g(T h e 723I n s t i t u t e o f C S I C ,Y a n gz h o u 225101,C h i n a )A b s t r a c t :A d e s i g n s c h e m e o f K a -b a n d l o w -c l u t t e r f r e q u e n c y s y n t h e s i z e r o f f r e q u e n c y a g i l i t yi s p r o -p o s e d i n t h i s p a p e r .T h e s c h e m e a d o p t s t h e f r e q u e n c y s y n t h e s i z e r m o d e o f d i r e c t d i g i t a l s yn t h e s i s (D D S )+d i r e c t u p c o n v e r s i o n .T h e 360~600MH z i n t e r m e d i a t e f r e q u e n c y (I F )s i gn a l w i t h l o w c l u t t e r i s c r e a t e d b y D D S 1,a n d t h e s i g n a l o f t r a n s m i t t i n g w a v e f o r m i s c r e a t e d b y DD S 2.I n t h e s c h e m e ,a l o w c l u t t e r b r o a d b a n d f r e q u e n c y s y n t h e s i z e r o f f r e q u e n c y a g i l i t yi s r e a l i z e d a f t e r 4t i m e s u p c o n v e r s i o n ,s e g m e n t f i l t e r i n g a n d a m p l i f i c a t i o n ,w h i c h p r o v i d e s l o c a l o s c i l l a t o r (L O )s i gn a l ,e x c i t i n g s i g n a l ,e t c ..A c c o r d i n g t o t h e d e s i g n s c h e m e ,t h e r e a l s y n t h e s i z e r i s m a d e .M e a s u r e d r e -s u l t s s h o w t h a t :t h e o u t p u t c l u t t e r i s l e s s t h a n -75d B c ,f r e q u e n c y sw i t c h t i m e i s l e s s t h a n 200n s ,b a n d w i d t h i s 2G H z ,s t e pi s 1MH z a n d t h e p h a s e n o i s e i s a b o u t -95d B c /H z @1k H z a t 35G H z c a r r i e r w a v e .T h i s s y n t h e s i z e r n o t o n l y c a n b e a p pl i e d t o r a d a r ,e l e c t r o n i c c o u n t e r m e a s u r e ,c o mm u -n i c a t i o n ,e t c .,b u t a l s o o f f e r s a r e f e r e n c e f o r o t h e r s y n t h e s i z e r s w i t h s i m i l a r r e q u i r e m e n t s .K e y wo r d s :f r e q u e n c y s y n t h e s i z e r ;c l u t t e r ;m i l l i m e t e r w a v e 收稿日期:202011270 引 言现代电子系统对射频信号提出了高稳定㊁高精确度等性能要求㊂为了使射频信号达到这些性能,我们必须对频率合成技术进行深入的研究㊂这样才能研制出高稳定㊁高频率稳定度㊁高频谱纯度㊁快速捷变的频率合成器㊂同时由于接收系统要求,对本振信号也同样提出了这些要求㊂我们在设计频率合成器的时候需要兼顾考虑本振信号以及激励信号之间的关系㊂由于频带宽㊁波束窄以及多普勒频移较大等,毫米波信号受到越来越广泛的关注㊂本文介绍了一种K a 频段的捷变频㊁低杂散㊁低相噪的频率合成器的设计方案㊂该合成器采用直接数字式频率合成技术与模拟直接式相结合的方案,取得了较满意的效果㊂2021年2月舰船电子对抗F e b .2021第44卷第1期S H I P B O A R D E L E C T R O N I C C O U N T E R M E A S U R EV o l .44N o .11 频率合成器的设计某毫米波频率合成器要求输出全相参的K a 波段第一本振f 1,第二本振f 2以及激励信号f 3等信号,且能实现频率捷变㊁低杂散等要求㊂1.1 方案选择频率合成技术主要有以下3种:直接模拟合成式,间接合成式㊁直接数字合成式[1]㊂直接模拟合成技术的的主要优点是频率切换快㊁相位噪声低,但是由于杂散的要求,往往设备量较大㊁成本高㊁体积大以及功耗较大㊂间接合成技术具有成本低㊁切换频率方便等优点,缺点是切换时间比较长㊂直接数字合成技术的优势是分辨率高㊁频率切换速度快,缺点是输出频率低[2]㊂因此现代频率合成技术往往将上述3种合成技术混合利用,吸取各种合成技术的优点,避开其缺点㊂结合以上合成技术的优缺点,本文提出了基于直接数字合成(D D S )+直接模拟合成(D A S)混合频率合成的方案㊂该方案中射频电路分为以下3个部分:基准源电路㊁f 1产生电路㊁f 3产生电路㊁激励波形产生电路(兼顾频率合成器的控制)㊂基准源电路:基准源电路主要是利用高精度㊁高稳定㊁低相位噪声的晶体振荡器作为基准信号,通过锁相或者倍频的方式产生其他各部分电路所需要的单一频率信号,同时还产生f 2信号,f 2信号输出2路信号,一路作为接收机的第二本振信号,一路作为f 3产生电路中的本振信号㊂f 1产生电路:D D S 1输出带宽为360~600MH z 的低杂散中频信号,经过第1次混频,输出带宽为1.2G H z 的低杂散射频信号,滤波放大后再次上混频至K a 波段;通过开关滤波器组进行滤波并放大,同时将带宽拓展到2G H z 以上,并功分2路,一路信号作为系统需要的f 1,另一路作为f 3产生电路的本振信号㊂激励波形产生电路:D D S 2模块采用D D S 芯片,根据整机命令产生各种需要的激励波形信号,其中心频率与系统所需要的中频频率相同㊂根据系统需求,输出波形包括单脉冲信号㊁线性调频信号等㊂f 3产生电路:D D S 2输出的激励波形信号,先和f 2信号混频,后再与f 1混频,每一级混频后都有滤波放大电路,以保证输出信号的频谱纯度㊂该频率源的设计难度:满足1μs 以内的宽带捷变频以及超低杂散之间的协调㊂1.2 主要技术分析1.2.1 低杂散直接数字合成(D D S)技术D D S 主要由相位累加器㊁查表(相位幅度转换)㊁数模转换器(D A C )以及低通滤波器组成,在同一个时钟作用下,相位累加器完成相位的叠加,查表完成相位到幅度的转换,D A C 完成数字信号到模拟信号的转换,低通滤波器完成信号的提纯[3]㊂如果需要实现线性调频信号,往往还需要在相位累加器之前增加频率累加器㊂需要实现相位编码信号,需要在相位累加器后端增加1个加法器,使得输出信号在规定的时间内偏移1个固定的相位㊂图1是1个完整的D D S 芯片的主要结构拓扑图,可以实现线性调频㊁相位编码等多种形式的波形㊂图1 数字频率合成器技术采用改进的数字技术后,D D S 具有以下特点:(1)极高的频率分辨率;D D S 输出频率为:f 0=W f ˑf c l k2N(1)式中:f 0为输出信号频率;W f 为频率控制字;f c l k为输入时钟频率;N 为相位累加器的位数㊂频率控制字是介于0和(2N-1)之间的整数㊂当W f =1时,输出频率就是D D S 的最小步进㊂一般情况下,步进小于1H z,几乎可以实现任意步进的需求㊂88舰船电子对抗第44卷(2)相对带宽比较宽,但是实际频率较低㊂根据奈奎斯特采样定理的限制,一般情况下D D S输出频率范围为D C~40%ˑf c l k㊂如果有低杂散的需要,能够使用的带宽更低㊂(3)频率切换快,一般在100n s左右㊂(4)灵活的调制性能,只要对相应的控制字进行设置,就可以输出调频或者相位编码的波形㊂这些特点决定了D D S在电子系统频率合成器中具有特殊的地位㊂一般情况下往往需要使用2个D D S,其中一个作为激励波形发生器,另一个作为本振频率细步进产生单元,使得系统在工作时,可以灵活设置工作频率㊂由于D D S的数字结构带来的信号带内杂散也制约频率合成器输出信号的杂散性能㊂其杂散主要来源有:相位截断误差㊁幅度量化误差以及数模转换器转换的非线性误差㊂一般来说,D A C转换的非线性引起的杂散与相位截断误差以及幅度量化误差相比,是最严重的㊂但是其杂散一般遵循与f C L K/2产生混叠的规律,而且主要落在0~f C L K/2的奈奎斯特频带内[4]㊂因此现在选取D D S输出频率范围时可以参照混叠的规律,使得输出信号的杂散尽量低,而且需要使用实物测试来验证计算结果㊂本文中D D S选取A D I公司的A D9914芯片,该芯片内部集成了12b i t D A C,具有自动线性和非线性频率扫描,可以实现初始相位调谐㊂时钟频率高达3.5G H z,宽带无杂散动态范围达到-50d B c等特点㊂在D D S1中选取输出频率范围是360MH z~ 600MH z,在D D S2中输出频率范围是60MH zʃ10MH z,这2段的近端以及带内杂散可以达到-76d B c以下,远端的杂散可以通过带通滤波器滤除㊂1.2.2带宽拓展虽然D D S输出相对带宽较宽,但是其绝对带宽还是比较窄,需要进行带宽的拓展以实现宽带性能指标㊂常用的带宽拓展方案有2种:(1)倍频拓展方案,如图2所示㊂直接对D D S 输出信号进行倍频,电路结构虽然简单,但是由于信号通过倍频器后谐波分量较多,能够实现的信号带宽也不能很宽㊂如果需要实现宽带信号,则倍频后的滤波器实现较为困难,甚至需要分段滤波,才能保证倍频后的杂散满足系统需求㊂而且会引起杂散与相位噪声的恶化,步进也会变宽㊂理想倍频器的相位噪声的恶化量可表示为20l g N,其中N为倍频系数,且杂散恶化程度与此一致㊂图2倍频扩展方案(2)混频扩展方案,如图3所示㊂通过多个本振频率可以混出不同的射频频段,然后通过开关滤波器组将多个频段组合起来,以达到带宽扩展的目的㊂由于混频会产生的高阶交调与本振泄露,需要通过计算混频器的本振频率和中频频率,以确保混频器输出所需要的信号远离组合谐波㊂设计合适的滤波器以确保高阶交调和本振泄露被滤除,确保频段扩展后的射频信号杂散不会恶化㊂此外,对于理想混频器,其输出信号相位噪声功率谱密度为2个输入信号相位噪声功率谱密度之和,实际混频器本身也存在附加相位噪声㊂图3毫米波频率源设计原理图L(f)=10l g(Sφ1(f)+Sφ2(f))(2)本频率合成器对杂散指标要求较高,如果采用直接倍频,会引起杂散和相位噪声的恶化,无法达到指标要求㊂在本方案中,对于D D S输出信号,第1次变频时选取5个本振频率进行混频,混频后通过开关滤波器组实现第1次频率拓展,带宽达到1.2G H z㊂在二次变频时,选取2个本振频率进行混频,将带宽扩展至2G H z,同时信号上变频至K a 波段㊂1.2.3捷变频设计影响频率合成器频率变换时间主要有以下几个因素:现场可编程门阵列(F P G A)的解算㊁D D S信号的延时㊁开关滤波器组中滤波器的延时以及开关切98第1期柴俊等:K a波段频率合成器设计换速度㊁各本振频率的切换延时等㊂开关滤波器组的原理框图如图4所示,其延时的主要原因是开关的切换速度和滤波器的延时㊂现在微波开关的延时,一般在50n s 以内,且与D D S 延时是同时进行的,只有信号通过滤波器延时会叠加在总延时中㊂本方案设计的带通滤波器延时都在10n s 以内㊂图4 开关滤波器组原理框图为了达到快速切换的目的,本方案所选取的本振信号也全部是快速切换的㊂本振信号的选取是通过多个单频点的锁相环加射频开关的形式实现㊂在频率合成器加电初始,各锁相环全部工作在其需要的频率上,因此各混频器的本振频率切换时间全部受限于射频开关㊂综上,本频率合成器的频率切换时间参照图5进行计算:F P G A 的结算时间约80n s ,D D S 信号的延时约130n s,开关滤波器组中滤波器延时小于10n s ,最大延时可控制在250n s 以内㊂图5 频率切换时间图2 频率合成器主要指标设计以及测试验证本方案通过2次混频的方法来扩展射频带宽,其输出杂散㊁镜像信号㊁本振泄露等与输出频段存在重叠,严重影响输出信号的杂散指标,需采用开关滤波器组对信号分段滤波㊂在设计过程当中进行了大量仿真计算,由于篇幅关系,不全部列出㊂图6所示为D D S 1输出信号经过2次上变频获得f 1输出的A D S 仿真电路模型,第1级混频后是1个开关滤波器组包含5个滤波器,第2级开关后的开关滤波器组包含2个滤波器㊂图6 f 1产生电路仿真电路图图7是输出信号的频谱图㊂图8是输出信号典型的相位噪声曲线㊂从图7可以看出,滤波器只要滤除本振泄露就可以满足频率合成器指标要求㊂图8的相位噪声曲线比较理想,在实际情况中会有一些干扰和噪声,但是应该在可控范围内㊂图7 输出信号频谱图图8 输出信号相位噪声曲线图根据实施方案进行了设计,在电路以及结构设计中针对以下几项必须认真考虑,并在实现过程中加以注意,否则频率合成器的最终指标将难以实现㊂(1)电磁兼容设计是保证频率合成器指标实现的基本需求㊂本频率合成器首先对输入的直流电源有较高的要求,直流电压必须满足低纹波㊁低噪声的要求,在电源输入端口必需采取良好的去耦滤波措施㊂在电路中必须将数字地和模拟地隔开,在远端再连接,以免数字信号对射频信号产生干扰㊂在1个电路板上,射频信号不能形成环路,以免产生自激9舰船电子对抗第44卷信号㊂(2)低相噪设计㊂为了满足方案要求和低相噪的要求,首先需要选择稳定度比较好的恒温晶振,合理设计相关锁相环电路㊁混频电路等,选取附加相位噪声低的放大器,确保信号经过这些电路后,相位噪声的恶化量最低㊂(3)信号通道隔离设计㊂为了确保输出信号的杂散以及各路信号之间不产生互相串扰,必须在电路设计中采取有效的隔离措施,各盒体之间需要保证良好的屏蔽性能㊂(4)低杂散设计㊂为了达到低杂散要求,除了信道隔离之外,各部件的频率设计也非常关键,尤其是混频器的本振和射频信号的频率关系需要一个合适的混频比,使得混频器输出信号远离干扰频率,使得混频器后的滤波器设计相对容易㊂各部件输入输出的功率电平选择对信号杂散影响也较大,需要合适的功率电平,尽量让信号信噪比和相位噪声不恶化㊂本频率合成器的测试结果:(1)输出信号杂散㊂各路毫米波信号杂散均优于-65d B c㊂(2)输出相位噪声㊂各路信号的相位噪声杂散均优于-95d B c/H z@1k H z㊂(3)波形满足设计需求㊂(4)频率捷变时间达到设计指标㊂图9~11选取了部分典型信号的频谱和相位噪声曲线㊂图12是频率切换时间曲线㊂图9杂散实测结果3结束语本文提出了一种K a波段低杂散捷变频频率合成器的设计方案,该方案通过2次上变频,将D D S 输出的低杂散中频信号上变频至K a波段,作为系统接收机本振信号,再将激励波形信号通过2次上图10相位噪声实测结果图11激励线性调频实测频谱图12频率切换时间实测曲线变频获得激励信号㊂同时总带宽扩展为2G H z㊂在频率合成器设计过程中,使用A D S软件仿真了整级射频链路的功率㊁杂散㊁相位噪声情况,对频率合成器的设计过程中的注意事项进行了总结㊂实测结果满足系统的使用要求㊂与其他同类捷变频频率合成器相比,本文方案在杂散控制方面具有优势,达到-65d B c,带宽为2G H z,频率切换时间小于200n s㊂此类基于D D S +D A S技术的频率合成器技术可以在其他电子设备中应用,既能作为宽带快速本振应用于无线通信系统中,也能方便地实现各种数字化的调制方式,拓展其在雷达㊁对抗㊁通信等领域的应用㊂(下转第107页)19第1期柴俊等:K a波段频率合成器设计图6 2种方法在扫描空域边缘的比较根据正弦空间内波位排列样式,可以得到被探测空域各个仰角层在正弦空间内的椭圆方程,随后在正弦空间内利用2.2.2节提出的方法进行每层波位的设计,计算各个俯仰层波束的方位位置,最终根据相关的准则确定属于探测空域内的波位,并转换至雷达距离方位俯仰坐标系中完成波位设计㊂图7给出了使用本文方法的针对典型低空搜索场景的波位设计仿真结果㊂低空搜索空域方位覆盖[-45ʎ,45ʎ],俯仰覆盖[0ʎ,9ʎ],雷达半功率波束宽度为2ʎ,各个波位间的排列方式采用交错排列㊂可以看到本文提出的方法可能应用于一定俯仰厚度的低空搜索空域内的波位设计,在被探测空域边缘处实现良好的覆盖度㊂图7 低空搜索场景的波位设计3 结束语运用搜索屏对目标进行远程预警是相控阵雷达反导工作模式下常见的搜索监视策略㊂搜索屏内良好的波位设计是实现快速有效发现目标的重要条件之一㊂本文利用正弦空间内天线波束宽度不变的特性,提出了主要针对雷达远程预警搜索屏的一种波位设计方法,利用数值方法实现波位坐标的快速计算㊂仿真结果显示本文提出的方法可有效完成典型远程预警搜索屏内的波位设计㊂与传统方法相比,在减少了覆盖搜索屏所需的波位数目的同时,提高了搜索屏边缘的覆盖程度㊂最后还对该方法进行改进,以应用于低空监视空域的波位设计㊂参考文献[1] 卡里拉斯P J .电扫描雷达系统设计手册[M ].北京:国防工业出版社,1979.[2] 束咸荣,何炳发,高铁.相控阵雷达天线[M ].北京:国防工业出版社,2007.[3] 李文臣,刘付兵,袁翔宇,等.地基相控阵雷达的天线扫描空间分析[J ].雷达科学与技术,2004,2(5):309314.[4] 周颖,王雪松,王国玉,等.相控阵雷达最优波位编排的边界约束算法研究[J ].电子学报,2004,32(6):9971000.[5] 王雪松,汪连栋,肖顺平,等.相控阵雷达天线最佳波位研究[J ].电子学报,2003,31(6):805808.[6] 刘洋,申立勇.判别平面上两个椭圆位置关系的代数条件[J ].计算机辅助设计与图形学学报,2003,15(5):555560.[7] 李庆扬,王能超,易大义.数值方法[M ].5版.北京:清华大学出版社,2008.(上接第91页)参考文献[1] 高树廷,高峰,徐盛旺,等.合成频率源工程与设计[M ].北京:兵器工业部出版社,2008.[2] MA N A S S E W I T S C H V.频率合成原理与设计[M ].3版.何松柏,宋亚梅,鲍景富,等译.北京:电子工业出版社,2011.[3] 白居宪,低噪声频率合成[M ].西安:西安交通大学出版社,1995.[4] 吴永洪.低杂散捷变频频率合成技术研究[D ].电子科技大学,2008.701第1期陈稳:一种相控阵雷达预警搜索屏波位快速设计方法。

频率合成器设计

摘要频率合成器是利用一个或多个标准信号,通过各种技术途径产生大量离散频率信号的设备。

本文系统地阐述了锁相环频率合成器的基本工作原理,较深入地分析了锁相环路的组成和工作过程,建立其相位模型以及动态方程,并且对环路滤波器和各组成部分进行了详细的分析。

在此基础上,针对CD4046系统的技术特点,以集成数字锁相芯片为核心精心设计了频率合成电路,构成了多频点输出频率合成器。

为了改善环路的捕获性能,进一步抑制鉴相器输出电压中的载频分量和高频噪声,降低由VCO控制电压的不纯而引起的寄生输出以及其他各种杂散噪声,对环路滤波器进行了重点设计,合理选择和计算了环路的参数,进而使得集成锁相环频率合成电路的功能得到了充分发挥,为CD4046系统提供了良好的本振源。

关键词:频率合成器锁相环路CD4046目录引言 (3)第一章频率合成基本原理 (4)1.1 频率合成的概念 (4)1.2 频率合成器的主要技术指标 (5)1.3 锁相频率合成器 (5)第二章锁相环路的基本工作原理和CD4046的介绍 (6)2.1 锁相环路的工作原理 (6)2.2 锁相环路各组成部分的作用 (6)2.3 数字式锁相环路CD4046 (7)2.4 CD4046的介绍 (8)2.5 CD4046工作原理 (9)2.6 CD4046典型应用电路 (9)第三章频率合成器的设计与制作 (11)3.1 实验的设计指标和要求 (11)3.2 设计步骤 (11)3.3 设计电路图 (12)3.4 电路板制作 (12)总结 (14)参考文献 (15)引言频率合成是以一个或少量的高准确度和高稳定度的标准频率作为参考频率,由此导出多个或大量的输出频率,这些输出频率的准确度与稳定度与参考频率是一致的。

频率合成在通信、雷达、测控、仪器仪表等电子系统中有广泛的应用,频率合成器有直接式频率合成器、直接数字式频率合成器及锁相频率合成器三种基本模式。

前两种属于开环系统,具有频率转换时间短,分辨率较高等优点。

简易DDS频率合成器设计

目录第一章系统分析与设计方案 (1)1.1 DDS设计原理介绍 (1)1.2直接数字式频率合成器(DDS)的基本结构 (1)1.3基本DDS结构的常用参量计算 (1)1.3.1 DDS的输出频率f out 。

(1)1.3.2 DDS产生的相位。

(1)1.3.3 DDS的频率分辨率。

(1)1.3.4 DDS的频率输入字FW计算。

(2)1.4 DDS的工作原理 (2)1.4.1相位累加器与频率控制字FW (2)1.4.2 相位控制字PW (2)第二章软件设计 (3)2.1 Verilog HDL程序 (3)2.1.1 8位加法器程序代码 (3)2.1.2 16位加法器程序代码 (3)2.1.3 8位寄存器程序代码 (3)2.1.4 16位寄存器程序代码 (4)2.1.5 dds代码程序 (4)2.1.6 ROM的创建 (4)第三章实验仿真 (5)3.1 原理图 (5)3.1.1 ROM (5)3.1.2 八位加法器 (5)3.1.3 十六位加法器 (5)3.1.4 八位寄存器 (6)3.1.5 十六位寄存器 (6)3.2 仿真波形 (6)3.3 D/A转换电路 (9)3.3.1 DAC0832结构及工作原理 (9)3.3.2 D/A转换电路模块 (10)3.4 实验结果 (10)3.5 调试过程 (10)3.5.1对adder8、adder16、reg8、reg16的调试 (10)3.5.2. D/A转换电路的调试 (10)3.5.3.输出波形的调试 (10)第四章心得体会 (11)第五章参考文献 (12)第一章系统分析与设计方案1.1 DDS设计原理介绍DDS即Direct Digital Synthesizer数字频率合成器,是一种基于全数字技术,从相位概念出发直接合成所需波形的一种频率合成技术,是一种新型的数字频率合成技术。

具有相对带宽大、频率转换时间短、分辨力高、相位连续性好等优点,很容易实现频率、相位和幅度的数控调制,广泛应用于通讯领域。

频率合成器的设计

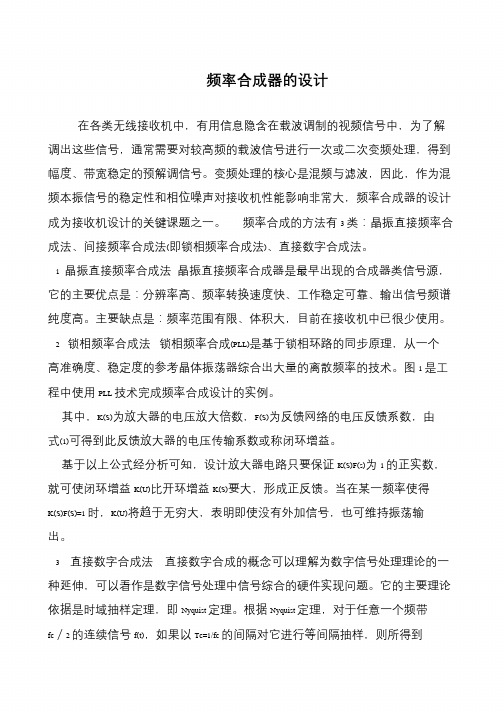

频率合成器的设计在各类无线接收机中,有用信息隐含在载波调制的视频信号中,为了解调出这些信号,通常需要对较高频的载波信号进行一次或二次变频处理,得到幅度、带宽稳定的预解调信号。

变频处理的核心是混频与滤波,因此,作为混频本振信号的稳定性和相位噪声对接收机性能影响非常大,频率合成器的设计成为接收机设计的关键课题之一。

频率合成的方法有3 类:晶振直接频率合成法、间接频率合成法(即锁相频率合成法)、直接数字合成法。

1 晶振直接频率合成法晶振直接频率合成器是最早出现的合成器类信号源,它的主要优点是:分辨率高、频率转换速度快、工作稳定可靠、输出信号频谱纯度高。

主要缺点是:频率范围有限、体积大,目前在接收机中已很少使用。

2 锁相频率合成法锁相频率合成(PLL)是基于锁相环路的同步原理,从一个高准确度、稳定度的参考晶体振荡器综合出大量的离散频率的技术。

图1 是工程中使用PLL 技术完成频率合成设计的实例。

其中,K(S)为放大器的电压放大倍数,F(S)为反馈网络的电压反馈系数,由式(1)可得到此反馈放大器的电压传输系数或称闭环增益。

基于以上公式经分析可知,设计放大器电路只要保证K(S)F(s)为1 的正实数,就可使闭环增益K(U)比开环增益K(S)要大,形成正反馈。

当在某一频率使得K(S)F(S)=1 时,K(U)将趋于无穷大,表明即使没有外加信号,也可维持振荡输出。

3 直接数字合成法直接数字合成的概念可以理解为数字信号处理理论的一种延伸,可以看作是数字信号处理中信号综合的硬件实现问题。

它的主要理论依据是时域抽样定理,即Nyquist 定理。

根据Nyquist 定理,对于任意一个频带fc/2 的连续信号f(t),如果以Tc=1/fc 的间隔对它进行等间隔抽样,则所得到。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

前言频率合成器是现代无线通信设备中一个重要的组成部分,直接影响着无线通信设备的性能。

频率合成技术历经了早期的直接合成技术(DS)和锁相合成技术(PLL),发展到如今的直接数字合成技术(DDS)。

直接数字合成技术具有分辨率高,转换速度快,相位噪声低等优点,在无线通信中发挥着越来越重要的作用。

随着大规模集成电路的发展,利用锁相环频率合成技术研制出了很多频率合成集成电路。

频率合成器是电子系统的心脏,是决定电子系统性能的关键设备,随着通信、数字电视、卫星定位、航空航天、雷达和电子对抗等技术的发展,对频率合成器提出了越来越高的要求。

频率合成技术是将一个或多个高稳定、高精确度的标准频率经过一定变换,产生同样高稳定度和精确度的大量离散频率的技术。

频率合成理论自20世纪30年代提出以来,已取得了迅速的发展,逐渐形成了目前的4种技术:直接频率合成技术、锁相频率合成技术、直接数字式频率合成技术和混合式频率合成技术。

本文是以如何设计一个锁相环频率合成器为重点,对频率合成器做了一下概述,主要介绍了锁相环这一部分,同时也对锁相环频率合成器的设计及调试等方面进行了阐述。

1 总体方案设计实现频率合成的方法有多种,可用直接合成,锁相环式,而锁相环式的实现方法又有多种,例如可变晶振,也可变分频系数M,还可以用单片机来实现等等。

下面列出了几种用锁相法实现频率合成的方案。

1.1方案一图1.1 方案一原理框图如图1.1所示,在VCO的输出端和鉴相器的输入端之间的反馈回路中加入了一个÷N的可变分频器。

高稳定度的参考振荡器信号fR经R次分频后,得到频率为fr的参考脉冲信号。

同时,压控振荡器的输出经N次分频后,得到频率为fd的脉冲信号,两个脉冲信号在鉴频鉴相器进行频率或相位比较。

当环路处于锁定状态时,输出信号频率:fo=N*fd。

只要改变分频比N,即可实现输出不同频率的fo,从而实现由fr合成fo的目的。

其输出频率点间隔Δf=fr。

1.2方案二图1.2 方案二原理框图如图1.2所示,首先由晶体振荡器产生20KHZ的频率,即fi为20KHZ。

按键1按下时,分频比M为1,N的值通过单片机编程预置,并可通过“N加1键”和“N减1键”作相应改变。

然后经单片机的I/O口输出作为1~N分频电路的数据输入。

再经过锁相环CC4046,因此可实现输出频率从20K~200KHZ,频率间隔为20KHZ。

M和N的值确定后,由公式f0=fi*N/M可计算出产生频率的具体值。

经软件编程计算后由单片机输出显示。

同理,当按键2按下时,由于晶振产生的信号经过了十分频,M为10。

当按键3按下时,M为100,其余部分不变。

通过改变M的值实现了三个不同的频段和频率间隔。

1.3方案三图1.3 方案三原理框图如图1.3所示,首先由三个晶体振荡器分别产生20KHZ,2KHZ和200HZ的频率,然后通过三个按键选择频率通断,被选择的频率送入锁相环输入端作为基准频率。

由此实现频段的选择。

由1~N分频电路实现不同的频率间隔。

可用一个十进制可逆计数器实现1~N分频电路的数据预置。

从锁相环输出的频率经数字频率计测频后由LED显示。

1.4方案比较上面三个方案都是锁相式频率合成器,本质上相同。

只是实现方法上有差别。

方案一采用变模分频来实现频率合成。

方案二用一个晶振经两次分频分别作为锁相环的输入信号。

方案三用了三个晶振。

方案一从整体上看流程简单明了,思路清晰,实现起来比较简单。

方案二用了单片机完成N分频电路数据输入和最后频率的换算,并送至LED作显示。

方案三没有使用单片机,采用十进制可逆计数器实现1~N分频电路的数据预置。

最后用了测频电路将产生的频率输出显示。

比较之下,方案一的电路较简单,容易实现。

方案三是直接式频率合成器。

直接模拟频率合成器容易产生过多的杂散分量以及设备量大因而体积大,价格昂贵不便于集成化是其主要缺点。

优点是频率捷变速度快,相位噪声低。

1.5方案选择经过对三个方案从各方面的比较,我选择了第一种方案。

原因是方案一相对其它两个方案较简单,容易实现。

方案二加入了单片机模块,但一旦使用单片机就对整个电路的系统协调能力要求更高,而且对程序部分也要求很高,实现比较困难;方案三采用直接式频率合成器,而直接模拟频率合成器存在产生过多的杂散分量以及设备量大因而体积大,价格昂贵等缺点,因此最终我选择了方案一来作为本次设计的方案。

2 单元模块设计2.1频率源频率源电路如图2.1,采用74LS04串联晶体振荡电路图2.1 频率源电路图反馈电阻Rf主要的作用是让74LS04芯片的反相器静态时工作在放大状态,晶体和电容C构成正反馈网络。

只要NOT1门或者NOT2门的输入或者输出电压有微小的变化都回被晶体和电容构成的正反馈网络反馈回去,进行放大而引起振荡。

由于NOT1门和NOT2门的振荡输出电压波形不是很好,要经过NOT3门整形输出形状标准的方波。

根据74LS04芯片的非门电压传输特性,Rf在这里取值100kOhm,C=100pF,晶体的标称频率是2.000MHz。

2.2分频器1.二分频将D触发器的Q非端和D端连接就可以构成一个最常用的二分频电路。

如下图:图2.2 二分频电路2.变模多频将74LS161的进位输出端C经过反相后接到预置端LD就可以通过进位信号的变化来控制分频器的模值。

预置端直接接上四位拨码开关。

TTL的芯片引脚悬空等价于高电平,所以尽可能地简便,省去了上拉电阻。

如下图:图2.3 变模多频电路2.3环路滤波器整个4046芯片的外围元件并不多,关键的部分是环路滤波器,他的性能能决定整个锁相环电路的工作性能。

环路滤波器可以采用:1.RC积分滤波器;2.无源比例积分滤波器;3.有源滤波器。

从本次设计的要求来看,用无源比例积分滤波器比较简单合适。

如下图:图2.5 环路滤波器电路环路滤波器的截止频率公式:Wc=1/[(R3+R4)C2]环路滤波器的带宽在1KHz左右,在这里R3=50K可调,R4=1k,C2=1uf。

可以通过R3调节来实现最佳锁相性能。

2.4芯片介绍1. 集成锁相环HC4046HC4046芯片是设计频率合成器的核心。

单片集成锁相环HC4046采用CMOS电路工艺,特点是电源电压范围宽(3~18 V),输入阻抗高(约100 MΩ),动态功耗小。

在电源电压VDD=15 V时最高频率可达1.2 MHz,常用在中、低频段。

HC4046内部集成了相位比较器Ⅰ、相位比较器Ⅱ、压控振荡器以及线性放大器、源跟随器、整形电路等。

相位比较器Ⅰ采用异或门结构,使用时要求输入信号占空比为50%。

当两路输入信号的高低电平相异时,输出信号为高电平,反之,输出信号为低电平。

相位比较器Ⅰ的捕捉能力和滤波器有关,选择合适的滤波器可以得到较宽的捕捉范围。

相位比较器Ⅱ由一个信号的上升沿控制,他对输入信号的占空比要求不高,允许输入非对称波形,具有很宽的捕捉范围。

相位比较器Ⅱ的输出和两路输入信号的频率高低有关,当14脚的输入信号比3脚的比较信号频率低时,输出为逻辑"0",反之则输出逻辑"1"。

如果两信号的频率相同而相位不同,当输人信号的相位滞后于比较信号时,相位比较器Ⅱ输出的为正脉冲,当相位超前时则输出为负脉冲。

而当两个输入脉冲的频率和相位均相同时,相位比较器Ⅱ的输出为高阻态。

压控振荡器需要外接电阻R1,R2和电容C1。

R1,C1是充放电元件,电阻R2起到频率补偿作用。

VCO的振荡频率不仅和R1,R2以及C1的取值有关,还和电源电压有关,电源电压越高振荡频率越高。

如图2.6为HC4046的内部及外围电路图和引脚图。

其中,1脚相位输出端,环路人锁时为高电平,环路失锁时为低电平。

2脚相位比较器Ⅰ的输出端。

3脚比较信号输入端。

4脚压控振荡器输出端。

5脚禁止端,高电平时禁止,低电平时允许压控振荡器工作。

6、7脚外接振荡电容。

8、16脚电源的负端和正端。

9脚压控振荡器的控制端。

10脚解调输出端,用于FM解调。

11、12脚外接振荡电阻。

13脚相位比较器Ⅱ的输出端。

14脚信号输入端。

15脚内部独立的齐纳稳压负极。

图2.6 HC4046的内部及外围电路图和引脚图2.集成反相器74LS0474LS04芯片是六个独立的反相器(6个非门)。

供电电压5V,电压范围在4.75~5.25V内可以正常工作。

门数6,每门输入输出均为TTL电平(<0.8V低电平 >2v高电平),低电平输出电流-0.4mA,高电平输出电流8mA。

每路从输入倒相到输出是有一定延时的(9~15ns)。

其引脚图如下:图2.7 74LS04引脚图3. 集成触发器74LS7474LS74芯片是双D集成触发器,是上升边沿触发的边沿触发器。

表2.9为其功能表。

它采用维持阻塞结构,是上升边沿触发的边沿触发器,即在CP脉冲上升沿(“0→1”)触发翻转。

触发器的次态取决于CP脉冲的上升来到之前D的状态,即Qn+1 = D。

由于电路具有维持阻塞作用,所以在CP=1 期间, D 端的状态变化不会影响触发器输出的状态。

分别是直接置“0”和置“1”端。

当不需要直接置“0”和置“1”时,都应置高电平。

其引脚图如下:图2.8 74LS74引脚图其功能表如下:图2.9 74LS74功能表4. 同步计数器74LS16174LS161是四位二进制同步计数器,该计数器能同步并行预置数,异步清零,具有清零、置数、计数和保持四种功能,且具有进位信号输出端,可串接计数使用。

它的引脚图和逻辑功能表分别见图2.10和表2.11。

图2.10 74LS161引脚图EP ET CP 功能0 ××××清零1 0 ××↑预置数1 1 1 1 ↑计数1 1 0 ××保持1 1 ×0 ×保持QCC=0表2.11 74LS161功能表2.5锁相环的基本组成许多电子设备要正常工作,通常需要外部的输入信号与内部的振荡信号同步,利用锁相环路就可以实现这个目的。

锁相环路是一种反馈控制电路,简称锁相环(PLL,Phase-Locked Loop)。

锁相环的特点是:利用外部输入的参考信号控制环路内部振荡信号的频率和相位。

因锁相环可以实现输出信号频率对输入信号频率的自动跟踪,所以锁相环通常用于闭环跟踪电路。

锁相环在工作的过程中,当输出信号的频率与输入信号的频率相等时,输出电压与输入电压保持固定的相位差值,即输出电压与输入电压的相位被锁住,这就是锁相环名称的由来。

锁相环通常由鉴相器(PD,Phase Detector)、环路滤波器(LF,Loop Filter)和压控振荡器(VCO,Voltage Controlled Oscillator)三部分组成,锁相环组成的原理框图如下图所示。