Lattice XO中文使用教程

Lattice展示基于FPGA的安防和监控解决方案

距 离延 伸至 1 0 i n, 并 实现 高达 l 0 8 0 P的 分 辨 率 。

在 图像 信 号处 理 方 面 , L a t t i c e的 第 三 方 He l i o n公 司 推 出 了基 于 L a t t i c e F P G A的 9 0多 个 独 立 的 图 像 信 号 处 理方面 的 I P, 可 实现 高动 态 范 围成 像 ( HD R) 、 H. 2 6 4编 码器 、 自动对 焦 和 视频 分 析( 人 数 统计 、 入 侵 检 测 、目标 检 测 以及 摄 像 机 篡 改 检 测 ) 等, 客户可 根 据需求 定 制 I P,

( 本 刊供 稿)

S T公布 2 0 1 2年 i N E Mo 校 园设 计 大 赛 中国地 区获奖名 单

近1 3, 意 法半 导 体 宣 布 , 西 安 电 子科 技 大学 “ D r a g o n

器人以 S T M 3 2微 控 制 器 为 上 层 控 制 单 元 ,通 过 i N E M 0

板 载 加 速 度 计 、陀 螺 仪 和 地 磁 计 采 集 数 据 ,然 后 运 用 K a h n a n扩 展 滤 波 算 法 对 这 三 类 数 据 进 行 融 合 处 理 , 根 据 处 理 结 果 并 采 用 多 种 控 制 策 略 ,通 过 l 6路 舵 机 控 制 蛇 形 机器 人的每 个关节 , 使 机 器 人 在 复 杂 水 域 环 境 中 保 持 运 动稳定 性 , 从 而 实 现 了 对 蛇 形 机 器 人 的 闭 环 控 制 。 此

L a t t i c e展示 基于 F P G A的安 防和监控解 决方案

Quattro Micro中文操作手册

Quattro Micro 操作手册目录开启控制软件MassLynx二、以设定溶液开始质谱调谐,确定质谱仪的状态三、信号提取四、查看文件五、液相色谱操作程序六、测试送检样品之标准操作程序七、子离子扫描模式八、质量校正九、当长时间停电或移机必须关机时,关闭电源,和泄真空的程序一、开启控制软件MassLynx:1. 从桌面以鼠标左键双击MassLynx图示打开文件。

2. 开启后将自动开启的预设页面,如图示:3. 单击质谱调谐图示(MS Tune)以开启质谱控制页面4. 开启后质谱调谐页面如下:5. 该画面即为调谐和信号提取的主要画面。

二、以设定溶液(setup solution)开始质谱调谐,确定质谱仪的状态1. 在质谱调谐页面(MS Tune)选择扫描模式和扫描离子质量范围:选中全部四个扫描功能,选择全扫描(MS Scan),设定扫描质量(Mass)为175.1、609.3、1080.8、2034.6,扫描范围(Span)为10(或5)。

2. 以注射针筒抽取设定溶液(setup solution),以直接进样(infusion)的方式连接注射针和管路,让样品得以被注射针泵推送,直接进入质谱仪分析。

3. 在质谱调谐页面(MS Tune)以鼠标左键单击氮气(API GAS)和注射针的图示,接着单击开始操作键(Press for Operate),直到原本红灯的图标显示为绿灯(此时该图标所显示的文字为Press for Standby)。

单击注射针图示则注射针泵会开始运作而推送样品;单击氮气会开始供应三方面的氮气:雾化气体(nebulizing gas)、去溶剂气体(desolvation gas)、气帘气体(cone gas),可以确保样品的气化;而单击操作键之后会开始供应电压,使得样品带电形成离子并使离子通过质谱仪分析。

4. 在质量分析器页面(Analyzer)设定以下的数值,括号内的数值即为设定值:LM Resolution 1(15.0)、HM Resolution 1(15.0)、Ion Energy 1(0.0)、Entrance(50)、Collision(2)、Exit(50)、LM Resolution 2(15.0)、HM Resolution 2(15.0)、Ion Energy 2(3.0),此为配合质谱扫描的参数。

Lattice的ISPlever使用教程

Lattice的ISPlever使用教程Lattice的ISPlever使用教程ispLEVER使用教程目录第一节 ispLEVER 简介第二节 ispLEVER开发工具的原理图输入第三节设计的编译与仿真第四节硬件描述语言和原理图混合输入第五节 ispLEVER工具中VHDL和Verilog语言的设计方法第六节 ispVM System-在系统编程的软件平台第七节约束条件编辑器(Constraint Editor)的使用方法附录一 ispLEVER System上机实习题附录二 ispLEVER软件中文件名后缀及其含义第一节 ispLEVER 简介ispLEVER 是Lattice 公司最新推出的一套EDA软件。

设计输入可采用原理图、硬件描述语言、混合输入三种方式。

能对所设计的数字电子系统进行功能仿真和时序仿真。

编译器是此软件的核心,能进行逻辑优化,将逻辑映射到器件中去,自动完成布局与布线并生成编程所需要的熔丝图文件。

软件中的Constraints Editor工具允许经由一个图形用户接口选择I/O设置和引脚分配。

软件包含Synolicity公司的“Synplify”综合工具和Lattice 的ispVM器件编程工具。

ispLEVER软件提供给开发者一个简单而有力的工具,用于设计所有Lattice可编程逻辑产品。

软件支持所有Lattice公司的ispLSI 、MACH、ispGDX、ispGAL、GAL器件。

ispLEVER工具套件还支持Lattice新的ispXPGATM和ispXPLDTM产品系列,并集成了Lattice ORCA Foundry设计工具的特点和功能。

这使得ispLEVER的用户能够设计新的ispXPGA和ispXPLD产品系列,ORCA FPGA/FPSC系列和所有Lattice的业界领先的CPLD 产品而不必学习新的设计工具。

软件主要特征:1. 输入方式* 原理图输入* ABEL-HDL输入* VHDL输入* Verilog-HDL输入* 原理图和硬件描述语言混合输入2. 逻辑模拟* 功能模拟* 时序模拟3. 编译器* 结构综合、映射、自动布局和布线4. 支持的器件* 含有支持ispLSI器件的宏库及MACH器件的宏库、TTL库* 支持所有ispLSI、MACH、ispGDX、ispGAL、GAL、ORCA FPGA/FPSC、ispXPGA和ispXPLD 器件5. Constraints Editor工具* I/O参数设置和引脚分配6. ispVM工具* 对ISP器件进行编程软件支持的计算机平台:PC: Windows 98/NT/2000/XP第二节 ispLEVER开发工具的原理图输入I. 启动ispLEVER(按Start=>Programs=>Lattice Semiconductor=>ispLEVER Project Navigator)II. 创建一个新的设计项目A. 选择菜单File。

lattice 产品介绍

XP2 系列

LFXP2-17ELFXP2-17E-5FT256C

SC 系列

LFSCM3GA25EP1LFSCM3GA25EP1-5FN900C

SC 系统芯片在业 界领先的FPGA 体 系中集成了4到32 个3.8G Serdes , 可灵活配置成 GE/10GE.PCIE,OC12/48,Fiber channel,业界最 高速率2Gbps的 I/O接口,以及创 新的把结构化Asic 的MACO 块嵌入 了内部,因此和同 类产品相比,性能 更高,集成度更强

Low-Cost FPGAs

• Mainstream FPGA Features/Performance at Lower Cost – DDR/DDR2 – Full-Featured DSP – SERDES

System FPGAs

• Full System-level Solution for Communications Applications – World Class SERDES – Embedded Hard IP

Lattice 第一代通用 型FPGA,低成本, 外围配置芯片可采 用spi flash ,含有 dsp 模块,支持 DDR memory , 是实现简单算法设 计最好的选择

ECP2 系列

LFE2-6ELFE2-6E-5TN144C

ECP2 是业界最低成本 的90 nm的FPGA,以 前只有高端器件才有的 特点和性能,比如说pll 和dll的支持,高速的源 同步I/O,DDR,DDR2, 128Bit AES算法加密, 双端口dual-boot启动, SPI FLASH 加载,近 乎完美

XP 是单芯片,可以单 电源供电的FPGA,应用 于对安全性,单板面积 有要求的场合,而且 lattice 特有的TFR技 术,可以远程的不掉电 系统升级 XP2 也是单芯片的 FPGA ,但是加入了dsp 模块和供用户自己使用 的memory ,成本相比 xp也有降低,

Lattice XO2内部RAM使用手册

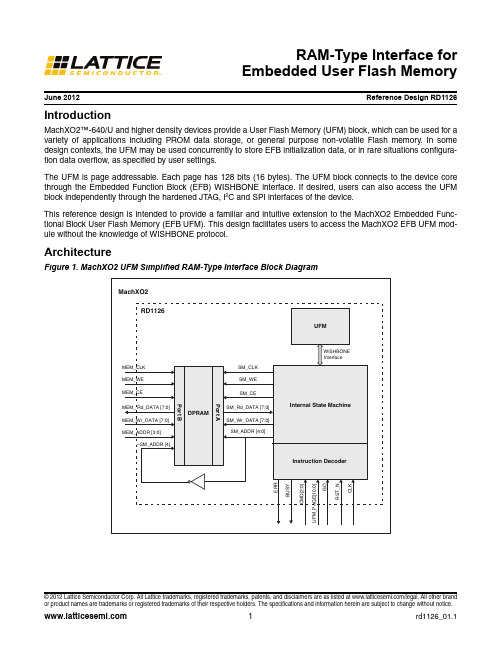

June 2012Reference Design RD1126© 2012 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at /legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.IntroductionMachXO2™-640/U and higher density devices provide a User Flash Memory (UFM) block, which can be used for a variety of applications including PROM data storage, or general purpose non-volatile Flash memory. In some design contexts, the UFM may be used concurrently to store EFB initialization data, or in rare situations configura-tion data overflow, as specified by user settings.The UFM is page addressable. Each page has 128 bits (16 bytes). The UFM block connects to the device core through the Embedded Function Block (EFB) WISHBONE interface. If desired, users can also access the UFM block independently through the hardened JTAG, I 2C and SPI interfaces of the device.This reference design is intended to provide a familiar and intuitive extension to the MachXO2 Embedded Func-tional Block User Flash Memory (EFB UFM). This design facilitates users to access the MachXO2 EFB UFM mod-ule without the knowledge of WISHBONE protocol.ArchitectureFigure 1. MachXO2 UFM Simplified RAM-Type Interface Block DiagramRAM-Type Interface forEmbedded User Flash MemoryPort DescriptionsTable 1. Port DescriptionsPort Direction Width (Bits)DescriptionCLK Input1Clock input1RST_N Input1Active low reset signalCommand InterfaceGO Input1High (‘1’) starts command process. GO is ignored if BUSY is asserted. CMD Input3Command operationUFM_P AGE Input11Target UFM PageBUSY Output1Status bit. Indicates operation in progress.ERR Output1Error bit. The last operation failed. Will be cleared on subsequent GO. Data InterfaceMEM_CLK Input1Clock for the DPRAM moduleMEM_WE Input1Write enable for the DPRAM moduleMEM_CE Input1Clock enable for the DPRAM moduleMEM_ADDR Input4DPRAM addressMEM_Wr_DA T A Input8DPRAM write dataMEM_Rd_DA T A Output8DPRAM read data1.Modify the design parameter READ_DELAY when CLK > 16.6 MHz. See discussion below.Functional DescriptionThis design facilitates user access to the MachXO2 EFB UFM module without the knowledge of WISHBONE proto-col. The user has to provide the necessary command sequence with UFM page address. A GO signal will trigger the interface to perform the necessary WISHBONE transactions to read or write the UFM.UFMThe User Flash Memory of the MachXO2 device features non-volatile storage in a single sector. Other features include:•Non-volatile storage up to 256Kbits•100K write cycles•Write access is performed page-wise; each page has 128 bits (16 bytes)•Auto-increment addressingTypical of Flash technology, the array must be cleared (erased) before data can be overwritten. The erased state of the UFM bits is ‘0’. The smallest erasable unit is the entire sector. Thus, any data which must be preserved (e.g. Config data overflow, or EBR init data) must be read out and stored in another available memory (e.g. EBR) prior to the Erase command. After the erase is complete, the data is written back to the UFM. The user is responsible for performing the storage operation. This requirement, along with limited erase cycles and long erase/program times, renders the UFM a poor solution for ‘scratch pad’ RAM (or similar) applications. MachXO2 Embedded Block RAM (EBR) is the recommended on-board memory type for high-churn, volatile data storage.In the design’s default configuration, the internal UFM read operation has been optimized for lower CLK rates. For CLK rates exceeding 16.6 MHz, this design must be configured to insert additional Retrieval Delay into the state machine which generates the UFM read command. A parameter, READ_DELAY, is provided for this purpose. The source file “UFM_WB_top.v” can be modified directly or the parameter passed in the module instantiation. The min-imum value for READ_DELAY can be calculated as follows:READ_DELAY(min) = 240/PERIOD - 4where PERIOD = CLK period in nsExample, for CLK = 47MHz, PERIOD = 21.28ns thus READ_DELAY >= 8 (7.28 rounded up)Refer to the “Reading Flash Pages” section of TN1204, MachXO2 Programming and Configuration Usage Guide for more information on the Read UFM command structure and timing requirements.DPRAMThe design incorporates a 32-byte (2 UFM page), byte addressable True Dual port RAM. The internal state machine accesses one port of the DPRAM. During the UFM write operation the state machine reads data from the DPRAM and writes it to the UFM. During UFM read operations the data read from the UFM is stored in the DPRAM.The second DPRAM port is accessed by the user to exchange data to or from the UFM. The DPRAM memory is divided into two pages of 16 bytes data each. The Most Significant Bit (MSB) of the DPRAM addresses are con-trolled by the internal state machine for page swapping. Thus, only one page (16 bytes) of the DPRAM is available through the user port at any given time. The available page is synchronized by the reference design and optimized for maximum throughput.During a UFM write operation, the DPRAM page swap happens once a GO is recognized. For higher throughput in back-to-back writes, this allows the user to immediately start loading the next page to be transferred to the UFM. During a read operation, the DPRAM page swap happens at the end of a read UFM operation and the user can start reading the DPRAM data once BUSY signal is low. In the case of back-to-back Read operations, the data remains available in the DPRAM until the subsequent Read is complete, allowing for higher throughput operation. CommandsTable 2. List of CommandsCommand Operation BUSY Signal Page Swap 000Read 1 page Clear when finished End of transaction001Read next page Clear when finished End of transaction010Write 1 page Clear upon UFM busy clear.Beginning of transaction011Write next page Clear upon UFM busy clear Beginning of transaction100Enable UFM access Clear upon UFM busy clear.N/A101Disable UFM access Clear when finished N/A110(undefined)––111Erase UFM Clear upon UFM busy clear N/ACommand Descriptions•Enable UFM access (100) – Required to enable UFM read/write access. Exercising this command will tempo-rarily disable certain features of the device, notably GSR, User SPI port and Power Controller. These features are restored when UFM access is disabled using Disable UFM access command (101). See TN1246, MachXO2 EFB User’s Guide, for more information on this behavior. BUSY is asserted until the devices internal Flash pumps are fully charged.•Write 1 page (010) – The 16 bytes of data from DPRAM is written into the UFM page specified by UFM_PAGE. The internal UFM page pointer is auto incremented at the completion of the command. Make sure that 16 bytes of data that has to be written to the UFM is loaded to the DPRAM prior to issuing a GO. BUSY will be asserted as soon as a GO is recognized and will be de-asserted when programming is complete.•Write next page (011) – The 16 bytes of data from DPRAM are written into the subsequent UFM page pointed by the internal UFM page pointer. The internal UFM page pointer is auto-incremented at the completion of thecommand. Make sure that 16 bytes of data that has to be written to the UFM is loaded to the DPRAM prior to issuing a GO. BUSY will be asserted as soon as a GO is recognized and will be de-asserted when programming is complete.•Read 1 page (000) – 16 bytes of data is read back from the UFM page specified by UFM_PAGE and stored in the DPRAM. The internal UFM page pointer is auto-incremented at the completion of the command. Following a Read command, the 16 bytes of UFM data can be read from the DPRAM after BUSY de-asserts.•Read next page (011) – The subsequent UFM page pointed by the internal UFM page pointer is read and stored into the DPRAM. The internal UFM page pointer is auto-incremented at the completion of the command. Follow-ing a Read command, the 16 bytes of UFM data can be read from the DPRAM after BUSY de-asserts.•Disable UFM access (101) – This command disables UFM interface for change access.•Erase UFM (111) – This command is issued to completely erase (set to ‘0’) the UFM. BUSY is asserted until era-sure is complete.Typical Command SequencesNotes:• A GO will be ignored when BUSY is asserted.•Any UFM read/write or erase command while UFM is disabled will assert the ERR signal.Write to UFMThe following sequence explains the necessary commands to be followed for a UFM write operation. The sequence assumes the target UFM row is in the erased state.1.Enable UFM access (100) – Check for BUSY signal to be low and issue enable UFM command on theCMD bus and issue a GO. BUSY signal is asserted once a GO is recognized.2.Write 1 page (010) – Load the DPRAM with one page (16 bytes) of data to be written to the UFM. Checkfor BUSY signal to be low, issue the Write 1 Page command on the CMD bus, UFM page address on the UFM_PAGE bus and issue a GO. The DPRAM page swap happens once a GO is recognized so that the user can load the next page to be written to the UFM into the DPRAM while the first page is being trans-ferred to the UFM.3.Write next page (011) – Wait for the previous page to be transferred to the UFM successfully and theBUSY signal goes low. Now issue a write next page command and issue GO. The internal UFM pagepointer is auto-incremented.4.Repeat steps 2 and 3 until all desired pages are written. Figure 2 illustrates steps 2 and 3.5.Disable UFM access (101) – Check for BUSY signal to be low and issue disable UFM command on theCMD bus and issue a GO. BUSY signal is asserted once a GO is recognized.Figure 2. Write to UFM Waveform DescriptionRead from UFMThe following sequence explains the necessary commands to be followed for a UFM read operation.1.Enable UFM access (100) – Check for the BUSY signal to be low and issue an enable UFM commandon the CMD bus and issue a GO. BUSY signal is asserted once a GO is recognized.2.Read 1 page (000) – Check for BUSY signal to be low, issue the Read 1 Page command on the CMDbus, UFM page address on the UFM_PAGE bus and issue a GO. Data read from UFM will be loaded in the DPRAM and user can access the data once BUSY signal goes low.3.Read next page (011) – Check for the BUSY signal to be low, issue the read next page command on theCMD bus and issue a GO. The internal UFM page pointer is auto. Data read from UFM will be loaded in the DPRAM and user can access the data once the BUSY signal goes low.4.Repeat steps 2 and 3 until all desired pages have been read. Figure 3 illustrates steps 2 and 3.5.Disable UFM access (101) – Check for the BUSY signal to be low and issue a disable UFM commandon the CMD bus and issue a GO. The BUSY signal is asserted once a GO is recognized.Figure 3. Read from UFM Waveform DescriptionRead Modify Write Back to UFMThe page read from UFM can be retained in the DPRAM and data modification may be performed directly on the DPRAM, followed by a Write 1 Page operation. The following sequence explains the necessary commands to be followed in order to modify the contents of UFM.Note: The modified data cannot be arbitrary. Only erased bits/bytes (=‘0’) of the UFM can be given new values. This sequence is provided to support applications where small amounts of data, or data unaligned to UFM page boundaries, is accumulated over time (e.g. a data logger application).1.Enable UFM access (100) – Check for BUSY signal to be low and issue an enable UFM command onthe CMD bus and issue a GO. BUSY signal is asserted once a GO is recognized.2.Read 1 page (000) – Check for BUSY signal to be low, issue the Read 1 Page command on the CMDbus, UFM page address on the UFM_PAGE bus and issue a GO. Data read from the UFM will be loaded in the DPRAM and is available to read or edit once the BUSY signal goes low.3.Modify DPRAM data as needed. The DPRAM data is byte addressable. The user may modify theintended byte(s) directly in the DPRAM. Alternatively, the data may be read from, and re-written to, theDPRAM.4.Write 1 page (010) – Once the data in the DPRAM has been modified or re-written, check for the BUSYsignal to be low, issue the Write 1 Page command on the CMD bus, set the UFM page address on theUFM_PAGE bus and issue a GO. Note that UFM page address must be specified for both read and write.5.Repeat steps 2 through 4 until all desired pages have been modified. Figure 4 illustrates steps 2through 4.6.Disable UFM access (101) – Check for the BUSY signal to be low and issue a disable UFM commandon the CMD bus and issue a GO. BUSY signal is asserted once a GO is recognized.Figure 4. Read-Modify and Write Back to UFM Waveform DescriptionHDL Simulation and VerificationEnable CommandFigure 5. Enable Command HDL Simulation WaveformWrite CommandFigure 6. Loading of DPRAM HDL Simulation WaveformFigure 7. Write to UFM Command Sequence HDL Simulation WaveformRead CommandFigure 8. Read from UFM Command Sequence HDL Simulation WaveformDisable CommandFigure 9. Disable Command HDL Simulation WaveformImplementationTable 3. Performance and Resource UtilizationTechnical Support AssistanceHotline:1-800-LATTICE (North America)+1-503-268-8001 (Outside North America)e-mail:techsupport@ Internet:Revision HistoryFamily Language Speed GradeUtilization fmax (MHZ)I/Os Architecture Resources MachXO21Verilog-3239 LUTs>50421- EFB1- EBR1. Performance and utilization characteristics are generated using LCMXO2-1200ZE-3TG100C with Lattice Diamond ® 1.4 design software.Date Version Change SummaryApril 201201.0Initial release.June 201201.1Updated design and document to include READ_DELAY parameteriza-tion.Appendix A. UFM Command SequencesThe following table explains the different UFM internal command structure involved for the various operations of this reference design.Table 4. MachXO2 Embedded Function Block CommandsOperation Command (Hex)Operand (Hex)Write Data Read Data Enable UFM Access (100)Enable UFM74 08 00 00——Status check F000 00 00— 1 byte status data Write One Page (010)Set Address B400 00 0040 00 aa aa1—Write UFM C900 00 0116 bytes data fromDPRAM—Status check F000 00 00— 1 byte status data Write Next Page (011)Write UFM C900 00 0116 bytes data fromDPRAM—Status check F000 00 00— 1 byte status data Read One Page (000)Set Address B400 00 0040 00 aa aa1—Read UFM CA10 00 01—16 bytes data from UFM Read Next Page (011)Read UFM CA10 00 01—16 bytes data from UFM Disable UFM Access (101)Disable UFM2600 00 00——Bypass FF FF FF FF——Erase UFM (111)Erase UFM0E08 00 00——Status check F000 00 00— 1 byte status data 1.The aa aa value is copied from the 11-bit UFM_PAGE module input.。

利用LatticeXP评估板使用LatticeMico8微控制器

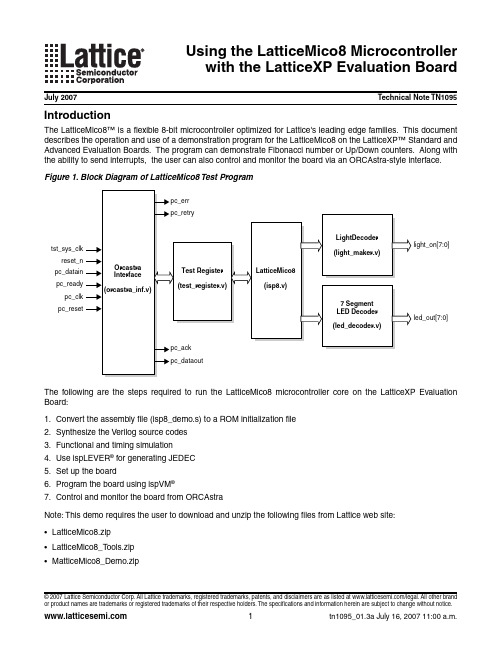

Usin g the LatticeMico8 Microcontrollerwith the LatticeXP Evaluation BoardJuly 2007Technical Note TN1095 IntroductionThe LatticeMico8™ is a flexible 8-bit microcontroller optimized for Lattice's leading edge families. This document describes the operation and use of a demonstration program for the LatticeMico8 on the LatticeXP™ Standard and Advanced Evaluation Boards. The program can demonstrate Fibonacci number or Up/Down counters. Along with the ability to send interrupts, the user can also control and monitor the board via an ORCAstra-style interface. Figure 1. Block Diagram of LatticeMico8 Test ProgramThe following are the steps required to run the LatticeMico8 microcontroller core on the LatticeXP Evaluation Board:1.Convert the assembly file (isp8_demo.s) to a ROM initialization file2.Synthesize the Verilog source codes3.Functional and timing simulatione ispLEVER® for generating JEDEC5.Set up the board6.Program the board using ispVM®7.Control and monitor the board from ORCAstraNote: This demo requires the user to download and unzip the following files from Lattice web site:•LatticeMico8.zip•LatticeMico8_T ools.zip•MatticeMico8_Demo.zip© 2007 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at /legal. All other brandUsin g the LatticeMico8 Microcontroller Lattice Semiconductor with the LatticeXP Evaluation Board Step 1: Convertin g the Assembly File to a ROM Initialization fileFollow the instructions below to convert the assembly file.•Copy all the files in the directory LatticeMico8_Tools to directoryC:\<your_directory>\LatticeMico8_Demo\test•Open a DOS command window•Change the directory to C:\<your_directory>\LatticeMico8_Demo\test•In the command line, type: isp8asm_win -o prom_init.v -l -ve ..\asm\isp8_demo.s• A new ROM initialization file (prom_init.v) is generatedStep 2: Synthesizin g the Verilo g Source CodesAfter obtaining the prom_init.v file, the next step is to synthesize the Verilog source codes. The file name for the memory initialization file remains unchanged as prom_init.v since the file isp8.v will call the prom_init.v directly.•Open Synplify Synthesis•Add these files in the following order:~/LatticeMico8/ver2.4/models/xp/sim/dpram32x8.v~/LatticeMico8/ver2.4/models/xp/sim/prom.v~/LatticeMico8/ver2.4/models/xp/sim/spram32x8.v~/LatticeMico8/ver2.4/models/xp/sim/spram16x8.v~/LatticeMico8/ver2.4/models/xp/sim/spram16x9.v~/LatticeMico8/ver2.4/models/xp/syn/xp.v~/LatticeMico8/source/isp8.v~/LatticeMico8_Demo/source/test_register/test_register.v~/LatticeMico8_Demo/source/orcastra_inf/orcastra_inf.v~/LatticeMico8_Demo/source/led_decoder/led_decoder.v~/LatticeMico8_Demo/source/light_maker/light_maker.v~/LatticeMico8_Demo/source/top/isp8_top_system.v•Add the following source directory in the Include path:~/LatticeMico8_Demo/source/config3~/LatticeMico8_Demo/test•In the Implementation Options dialog box set the following options under Device tab:–Lattice T echnology = LATTICE XP–Part = LFXP10C–Speed = -5–Package = F256C (Standard Board) / F388C (Advanced Board)•Click RunNote: The above procedure is for synthesizing LatticeMico8 and the demo source codes. Users can synthesize LatticeMico8 (isp8.v) by itself from the LatticeMico8 directory by using the Tcl script located in the Synthesis direc-tory. Before using this Tcl script, please modify the PROJP A TH variable in the Tcl script to resemble the current project directory.Step 3: Functional and Timin g Simulation•Open ModelSim Simulator•From the menu bar, select File -> Chan g e Directory, and set the folder to ~/LatticeMico8_Demo/simula-tionUsin g the LatticeMico8 Microcontroller Lattice Semiconductor with the LatticeXP Evaluation Board •For functional simulation, from the menu bar, select Tools -> TCL -> Execute Macro, click on the Script direc-tory and select demo_func_sim.do•For timing simulation, the .vo and .sdf files must already be generated by ispLEVER Project Navigator and located at ~/LatticeMico8_Demo/par/top. From the menu bar, select Tools -> TCL -> Execute Macro, click on the Script directory and select demo_time_sim.do.Note: The demo_time_sim.do may need to be modified to match the .vo and .sdf file names.Step 4: Usin g ispLEVER for Generatin g JEDEC•Open ispLEVER Project Navigator•T o set the target device, in the Device Selector dialog box, select the following:–Family = LatticeXP–Device = LFXP10C or LFXP10E–Speed Grace = -5–Package T ype = FPBGA256 (Standard Board) / FPBGA388 (Advanced Board)–Operating Conditions = Commercial•From the Project Navigator, double click on Pre-Map Preference Editor to set the pin types and pin locations Table 1. Pin Assignment for LatticeXP Advanced & Standard BoardsSi g nal NamePin LocationI/O Type Standard Board Advanced Boardtst_sys_clk A7A10LVCMOS33 reset_n L12H3LVCMOS33 light_on_0D5H1LVCMOS33 light_on_1A3B16LVCMOS33 light_on_2B3B18LVCMOS33 light_on_3B2C18LVCMOS33 light_on_4A2C19LVCMOS33 light_on_5B1C20LVCMOS33 light_on_6F5W16LVCMOS33 light_on_7C5A16LVCMOS33 led_out_0J14D2LVCMOS33 led_out_1K16F3LVCMOS33 led_out_2K15F1LVCMOS33 led_out_3L14E2LVCMOS33 led_out_4L13E1LVCMOS33 led_out_5K13D1LVCMOS33 led_out_6N16F2LVCMOS33 pc_err H16B4LVCMOS33 pc_retry H12C4LVCMOS33 pc_ack F13A18LVCMOS33 pc_dataout G14C3LVCMOS33 pc_clk C15A3LVCMOS33 pc_ready F16B3LVCMOS33 pc_datain E14A2LVCMOS33 pc_reset C16A4LVCMOS33Usin g the LatticeMico 8 Microcontroller Lattice Semiconductorwith the LatticeXP Evaluation Board•Double click on Generate Timin g Simulation Files . This process will generate .vo and .sdf files that can be used for timing simulation•Double click on Generate Data File (JEDEC) to get the .jed file that will be used later with ispVM System to pro-gram the evaluation boardStep 5: Settin g up the BoardFor the LatticeXP Standard Evaluation Board:•Set the VCCIO pins of all banks of eight jumpers (JP1, JP2, JP12, JP11, JP13, JP14, JP10, and JP3) to 3.3V •The VCC core is set and defaulted to 1.2 V . Don’t change the setting of the VCC core, but keep it as its original setting at 1.2V•Use a 1.2 power supply and a 3.3V power supply that can provide adequate current to the board •T o interface with ORCAstra software, connect the parallel port pins as mentioned in T able 2Note: Unlike the LatticeXP Advanced Board, the Standard board does not have seven-segment display on the board. However, user can easily get a regular seven-segment display such as HDSP7501 and connect it with the pins mentioned in T able 1.For the LatticeXP Advanced Evaluation Board:•Set the V CCIO pins of all banks to 3.3 V by putting all eight jumpers J2-J4 to J1•Use a 5V power supply that can provide adequate current to the board•T o interface with ORCAstra software, connect the following parallel port pins to the board pins Table 2. ORCAstra Interface ConnectionsStep 6: Pro g rammin g the Board Usin g ispVM SystemThe following are the steps for programming the LatticeXP Evaluation Board:•Connect your PC to the target board using a Lattice ispDOWNLOAD ® Cable •Launch ispVM System software •Click File -> New •Click Edit -> Add DeviceParallel Port PinsSi g nal Name DirectionBoard/Pin LocationsStandard BoardAdvanced Board2(tied to 15) 6 PC_Data_InPC Out E14A27PC_Clk PC Out C15A38PC_Reset PC Out C16A49PC_Ready PC Out F16B310PC_Err PC In H16B411PC_Data_Out PC In G14C312PC_Retry PC In H12C413PC_Ack PC In F13A1815(tied to 2)———18-25GND———•Click Select and select LatticeXP-ES for Device Family, LFXP10E_ES for Device, 256_ball fpBGA (Standard board) / 388_ball fpBGA (Advanced board) for Package and then click OK•Click Browse under the Data File field and point to the JEDEC file previously created by the ispLEVER Project Navigator•Highlight Flash Pro g rammin g Mode from the Device Access Options field selection list•Highlight FLASH Erase, Pro g ram, Verify from the Operation field selection list•Click on the OK button•Click GO to program to LatticeXP deviceStep 7: Controllin g and Monitorin g the Evaluation Board from ORCAstraWith ORCAstra, users can control and monitor the evaluation board by writing and reading the registers in the test_register module inside the LatticeXP device.Download the latest ORCAstra software from the Lattice web site at the following address:/products/designsoftware/orcastra.cfm.After downloading ORCAstra, follow these steps to set it up with the board environment:•Launch ORCAstra•On menu bar, click on Device and select Zero No Device•In the same menu bar, click on Interface and select FPGA User Master via Parallel Port•From the menu bar, click on LPT:Port and select 2 0x378Figure 2. ORCAstra System Bus Control GUIThe demo files also come with an additional GUI specially created to support LatticeMico8. This GUI enables users to view the value of all the 32 registers together by clicking on the Read All Re g isters button.T o open the LatticeMico8 GUI from ORCAstra software (v112 or later):•From the menu bar, select Custom Pro g rammability --> Visual Window• A new smaller window will appear titled Custom Visual Interface•Select File --> Open from its menu bar•Browse and select isp 8_g ui.vis file located in LatticeMico8_Demo/gui directory A new window with LatticeMico8 logo will appear.Figure 3. LatticeMico8 GUI Derived From ORCAstraThe assembly file that was converted to a ROM initialization file in Step 1 contains a program that will determine the Fibonacci number and the Up/down counter based on the command that is given from ORCAstra.T able 3 lists the addresses and data that are accepted by the program based on the assembly code (isp8_demo.s).Table 3. List of Demo CommandsThe program will act accordingly based on the address and data written by the user from ORCAstra. For example,by typing Adrs = 00003 and Data = 11 in the ORCAstra GUI and pressing the WR button, the Fibonacci function will be run. The program will generate the first 12 Fibonacci numbers and store the results in Register 0 through Register 12. The value of one of these registers can be read by typing its address. For example, to read Register 0,type 00020 in the Adrs field and press the Rd button. The value will be shown in the Data field.Adrs (Address)Data Type of FunctionSpeed 0000311Fibonacci 1 (Very Slow)0000312Fibonacci 2 (Slow)0000313Fibonacci 3 (Medium)0000314Fibonacci 4 (Fast)0000321Up/Down Counter 1 (Very Slow)0000322Up/Down Counter 2 (Slow)0000323Up/Down Counter 3 (Medium)0000324Up/Down Counter 4 (Fast)0000201Sending Interrupt—Below is the list of registers and their corresponding addresses.Re g ister Name Re g0Re g1Re g2Re g3Re g4Re g5Re g6Re g7Address (hex)0002000021000220002300024000250002600027Re g ister Name Re g8Re g9Re g10Re g11Re g12Re g13Re g14Re g15Address (hex)00028000290002a0002b0002c0002d0002e0002fRe g ister Name Re g16Re g17Re g18Re g19Re g20Re g21Re g22Re g23Address (hex)0003000031000320003300034000350003600037Re g ister Name Re g24Re g25Re g26Re g27Re g28Re g29Re g30Re g31Address (hex)00038000390003a0003b0003c0003d0003e0003fTechnical Support AssistanceHotline:1-800-LA TTICE (North America)+1-503-268-8001 (Outside North America)e-mail:techsupport@Internet:Revision HistoryDate Version Chan g e SummaryJuly 200501.0Initial release.August 200601.2Updated to include LatticeXP Standard Evaluation Board.July 200701.3Updated block diagram (changed pc_data_in signal to read pc_datain).Updated file names in Step 2: Synthesizing theVerilog Source Codes.Clarified some of the menu selections in Step 3: Functional and TimingSimulation.Updated information on how to download ORCAstra software in Step 7:Controlling and Monitoring the Evaluation Board from ORCAstra.。

LatticeXO中文使用教程

LatticeXO中⽂使⽤教程Lattice MachXO TM设计指南v1.11.介绍 (4)1.1特征 (4)1.2产品系列和器件选择⼿册 (5)1.3性能分析 (6)2.体系结构 (7)2.1M ACH XO结构概述 (7)2.1.1PFU结构 (7)2.1.2Slice结构 (8)2.1.3布线资源 (9)2.2结构特征 (9)2.2.1时钟/控制信号⽹络 (9)2.2.2锁相环PLL (10)2.2.3⽚内时钟振荡器 (11)2.2.4嵌⼊块RAM (EBR) (11)2.2.5I/O特性 (11)2.2.6休眠模式 (13)2.2.7器件编程 (13)3.设计综合&实现 (14)3.1开发流程 (14)3.2设置约束项 (16)3.2.1设置I/O位置 &属性 (16)3.2.2设置时钟频率|周期 (16)3.2.3设置建⽴&保持时间 (17)3.2.4设置Tco时间 (19)3.2.5设置MutiCycles | MaxDelay | Tpd (20)3.2.6时序约束例外(BLOCK) (20)3.2.7信号分组 (20)4.器件应⽤要点 (21)4.1M ACH XO系列器件V CC,V CCAUX,V CCIO作⽤和连接 (21) 4.2M ACH XO系列器件各电源上电顺序及要求 (21)4.3M ACH XO热插拔应⽤注意事项 (21)4.4如何使⽤全局复位功能 (22)4.5如何使⽤全局输出三态功能 (22)4.6如何使⽤全局时钟 (23)4.7如何使⽤TFR功能(透明现场升级) (23)4.8如何使⽤M ACH XO的差分信号 (24)4.9如何接⼝5V输⼊信号 (25)4.10如何在同⼀B ANK使⽤不同I/O⼝电平标准 (25)4.11如何减⼩T CO时间 (26)4.12什么-M速度级别? (27)4.13如何获得时序分析结果? (27)4.14如何知道资源利⽤率 (28)4.15如何使⽤M ACH XO的块RAM(EBR) (28)4.16如何利⽤PFU⽣成移位寄存器和分布式RAM (29)4.17如何使⽤锁相环(PLL) (30)4.18下载接⼝(TAP)的连接建议 (30)4.19如何设置加密位和⽤户代码 (30)4.20如何使⽤P OWER C ACULTOR估计功耗 (31)4.21如何快速建⽴器件原理图库? (32)4.22如何选择综合⼯具? (32)4.23关于约束⽂件 (32)4.24如何使⽤M ODELSIM 进⾏仿真 (33)5.相关资料 (33)1.介绍MachXO器件是 Lattice 公司基于FLASH+SRAM技术CPLD器件。

使用lattice进行数据可视化--面板函数

使⽤lattice进⾏数据可视化--⾯板函数使⽤lattice进⾏⾼级绘图-- ⾯板函数每⼀个⾼⽔平的画图函数都采⽤了默认的函数来绘制⾯板图。

默认函数遵循命名规则panel.graph_function,其中graph_function指的是⾼⽔平的函数。

例如:xyplot(mpg~wt|displacement, data=mtcars)也可以写成:xyplot(mpg~wt|displacement, data=mtcars, panel=panel.xyplot)这是⼀个强⼤的功能,因为它可以让我们⽤⾃⼰设计的默认函数来代替默认的⾯板函数。

前⾯,我们画出了以汽车发动机排量为条件的汽车重量的油耗。

如果你想加上回归线、地毯图和⽹格线,需要做什么呢?我们可以通过创建⾃⼰的⾯板函数来实现它,代码如下:(1)⾃定义⾯板函数xyplotlibrary(lattice)displacement <- equal.count(mtcars$disp, number=3, overlap=0)#将四个独⽴的构件函数集成到⾃⼰的mypanel()函数中mypanel <- function(x, y) {panel.xyplot(x, y, pch=19)panel.rug(x, y)panel.grid(h=-1, v=-1) #panel.grid()函数添加⽔平和垂直的⽹格线(使⽤负数迫使其⽤轴标签排队)。

panel.lmline(x, y, col="red", lwd=1, lty=2)}xyplot(mpg~wt|displacement, data=mtcars,layout=c(3, 1),aspect=1.5,main = "Miles per Gallon vs. Weight by Engine Displacement",xlab = "Weight",ylab = "Miles per Gallon",panel = mypanel) #⾃定义⾯板函数,通过xyplot()函数中的panel=option选项使它⽣效结果分析:panel.xyplot()函数使⽤⼀个填充的圆(pch=19)产⽣散点图,也就是实⼼圆,panel.grid()函数添加⽔平和垂直的⽹格线(使⽤负数迫使其⽤轴标签排队),如图中的灰⾊⽹格线,panel.rug()函数把地毯图加到x轴和y轴的每个标签上,如图中的青绿⾊和蓝⾊短线条。

Lattice Reveal逻辑分析仪使用指南

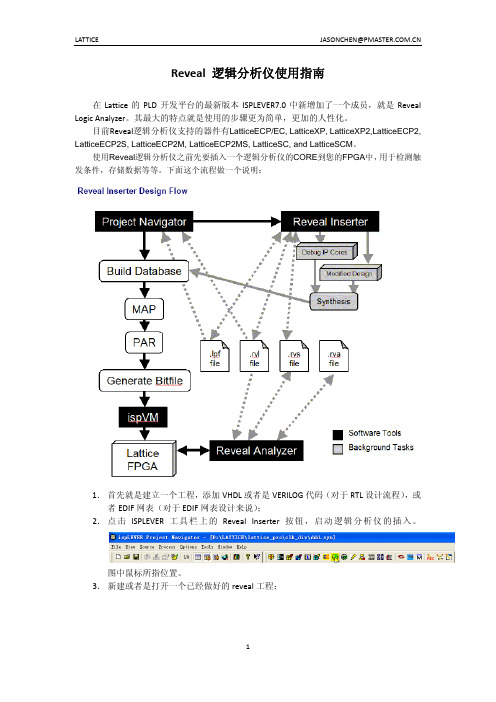

Reveal 逻辑分析仪使用指南在Lattice的PLD开发平台的最新版本ISPLEVER7.0中新增加了一个成员,就是Reveal Logic Analyzer。

其最大的特点就是使用的步骤更为简单,更加的人性化。

目前Reveal逻辑分析仪支持的器件有LatticeECP/EC, LatticeXP, LatticeXP2,LatticeECP2, LatticeECP2S, LatticeECP2M, LatticeECP2MS, LatticeSC, and LatticeSCM。

使用Reveal逻辑分析仪之前先要插入一个逻辑分析仪的CORE到您的FPGA中,用于检测触发条件,存储数据等等。

下面这个流程做一个说明:1.首先就是建立一个工程,添加VHDL或者是VERILOG代码(对于RTL设计流程),或者EDIF网表(对于EDIF网表设计来说);2.点击ISPLEVER工具栏上的Reveal Inserter按钮,启动逻辑分析仪的插入。

图中鼠标所指位置。

3.新建或者是打开一个已经做好的reveal工程;在datasets下面可以建立多个CORE,每个CORE的内容可以不一样,最多16个CORE。

在SMAPLE CLOCK中加入您要作为采样时钟的时钟信号。

采样时钟也是可以不一样的,这就允许多时钟域的调试。

数据采样模式可以是单次,也可以是多次,取决于需要。

设置好测样的深度以及是否要包含触发信号。

加入需要作为触发的信号,或者是要观察的信号,设置好条件。

最多支持256个触发条件,操作类型支持==, !=, >=, >, <, =<, rising edge, falling edge, serial compare。

可以在左边的信号节点列表直接拖拽到触发单元列表中。

在触发单元中有一个radix,就是数的进制,其中有一个token类型,这是一个自定义的类型,可以自己编辑使用来观察状态机的。

LATTICE开发板原理图测试代码软件使用以及中文资料2

MachXO培训教程2005 年8 月英文网址:中文网址:或MachXO系列MachXO系列是新一代的跨越式可编程逻辑器件,支持传统上由高密度的CPLD或者低容量的FPGA所实现的应用,并且拥有更全面和高性能价格比的结构和工艺。

通过采用130nm的非易失性嵌入式Flash处理工艺,以及用于逻辑实现的业界标准,4-输入查找表(LUT)的方法,这些新的器件能让系统设计者在单位逻辑功能上降低50%的成本,而且在特性上有了很大的提升。

MachXO器件不仅能用来处理传统的CPLD应用,在该系列的所有成员中都增加了分布式存贮器、一种低待机功耗的睡眠模式以及通过莱迪思特有的TransFR技术来透明地更新逻辑配置的功能。

此外,在较大的系列成员中,增加了对嵌入式RAM(EBR)和锁相环(PLL)时钟电路以及PCI和LVDS I/O的支持,提供了通常仅在传统的FPGA结构中才有的功能。

与此同时,还保留了莱迪思前几代CPLD(如流行的MACH®器件)的瞬时上电、单片和高速的优点。

MachXO逻辑器件建立在低成本的130nm嵌入式Flash处理工艺上。

它能够在单芯片中瞬时工作,这种特性对于许多CPLD应用来说是十分重要的。

高达3.5ns的管脚至管脚的延时使得器件能够满足当代系统设计的高速要求。

MachXO有两种类型, “E”型和“C”型。

“E”型MachXO器件采用了1.2V逻辑核技术,适用于超低功耗的应用。

一个片上的电压调整器使得“C”型MachXO器件可以支持1.8V, 2.5V或3.3V的外部电压,从而支持传统的系统电源要求。

在每个器件的内核中是一个查找表阵列,可以用来实现逻辑和小型的分布式存储器。

这个阵列被灵活的I/O所包围,这些I/O能够实现多种流行的I/O标准,如LVCMOS。

在大一些的器件中,还支持PCI和LVDS。

器件的睡眠模式可减少100倍的待机功耗,支持那些要求低功耗的应用。

该器件还支持莱迪思特有的TransFR(透明的现场重新配置)技术,能够在器件使用SRAM配置存储器继续正常工作的情况下,对Flash配置存储器进行透明的编程。

图解CTEX入门

图解CTEX入门oliyiyi发表于 2014-12-3 21:57:52 |只看作者|倒序本帖最后由 oliyiyi 于 2016-10-18 10:32 编辑昨天,我给研一学弟学妹讲解latex,主要是围绕CTEX中文套装的使用。

因为我自己了解不多,所以高深的东西我就不讲了,例如自定义命令之类,我自己也不是很清楚,我只讲我当时作为一个初学者所碰的硬壁,那些匪夷所思莫名其妙的问题,这些基本的问题构成了学习Latex的门槛。

我自己为了跨过这个门槛,花费了大量的精力,最后,我是以随机事件的形式解决了这些问题。

我想通过我的讲解,让他们很快跨过这个门槛,把精力用到文本的编写上,写出更漂亮的pdf文本。

现在,我把我的经验分享在这里,希望我的经验对客官您有所帮助。

如果看完这篇文档,你也能写出一个中文pdf的话,那对我而言,是件很开心的事!下载CTEX为了方便中国人学习LATEX,已经就有了LATEX的中文套装CTEX,目前这是对中文支持最好的版本。

用CTEX套装,很多复杂的编译命令都简化为几个简单的命令按钮,整个编译也全部以后台形式运行。

客官只需要关注如何编辑文本就行了。

CTEX可以从这里下载,如下图,最好下载中间那个比较大的,因为这个包比较全,功能比较多。

下载后,像安装其他程序一样,大胆安装就行,要耗费一段时间的。

初识CTEX安装完成后,程序就出现在了开始菜单的程序列表里了。

如下图。

CTEX,下拉菜单下内容还很多,诸如FontSetup,MixTex之类。

我们用的只是其中的一个编辑器–“WinEdit”。

以后我们的所有工作,都是基于这个编辑器。

这个编辑器,把几乎全部的Latex功能都给套装起来,并且以菜单的形式,没错,就是大家特别钟爱的那种形式。

以下是,你打开WinEdit见到的操作界面(有英文版的,还有中文版的,我这里是中文版的)。

其实和word差不多,都有菜单栏、快捷命令按钮。

比较特殊地,WinEdit还带有公式快捷命令。

Lattice USB下载设置

Lattice USB 下载线的设置方法

分两种情况

一、如果是ispVM System 17.6 以下的版本,请安装光盘中的最新版软件ispVM System 18.1,安装好软件后,连接USB下载器,系统会自动找到并安装USB下载器的驱动,你只需按提示就可以了。

二、如果是ispVM System 17.6以上的版本,没有安装过USB驱动,请按以下步骤进行安装。

1、打开ispVM;

2、按下图所示,装载USB 下载线的驱动程序,在弹出的对话框内点

完成安装;

3、安装完成后,按提示要求重新启动电脑;

4、将下载线的 VCC、TDO、TDI、TMS、GND、TCK与板上相应的管脚接好;

5、将 USB 端接入电脑的 USB 口内;

6、此时,电脑会显示找到USB 设备,显示出:

7、点下一步,会出现:

8、点仍然继续,

9、点完成;

10、按下图所示,进入下载线端口设置界面:

11、点按钮 ,会扫描到USB 下载线,

12、点OK。

13、再点 即可以扫描到器件。

以下以一块EC20 的板子为例:

14、点Scan 后,扫出器件,

15、双击上图的鼠标处,弹出下图列表,选择LFEC20E,

16、在弹出对话框内,

点 [Browse] 指定 JED 文档(XP,CPLD)或Bit 文档(EC/ECP)的路径, 在 [Device Access Option] 中选择下载的方式“JTAG 1532 Mode”, 在 [Operation] 中选择操作的类型“Fast Program”。

17、设置好后,点OK,再点工具栏上的 开始下载。

18、会显示出进度条:

19、成功后始可显示 。

LATTICE开发板原理图测试代码软件使用以及中文资料3

LatticeXP系列培训教程上海莱迪思半导体公司市场部2005 年 5月英文网址:中文网址:或LatticeXP系列器件的主要特性•非易失,无限次重构-瞬时上电,数毫秒-无外部配置存储器-很高的设计安全性,不能截取位流-用数毫秒重构基于SRAM的逻辑-通过系统配置和JTAG口对SRAM和非易失存储器编程-支持非易失存储器的后台编程•很高的密度并有多种封装•嵌入式和分布式存储器•灵活的I/O缓冲器•专用DDR存储器支持•系统时钟PLL•系统级的支持表1 LatticeXP系列产品选择指南产品简介LatticeXP系列FPGA在单一结构里组成了逻辑门、嵌入式存储器和I/O,器件是非易失的和能够无限次重新编程,它支持节省成本的系统设计。

LatticeXP系列中使用的重复编程、非易失技术是下一代ispXP技术。

采样这种技术,就不再需要昂贵的外部配置存储器,设计没有未经许可的读回风险。

借助莱迪思的ispLEVER®设计工具可以使LatticeXP系列高效地实现大型复杂设计。

ispLEVER设计工具提供支持LatticeXP的时尚逻辑综合工具的综合库。

ispLEVER工具采用综合工具的输出结果,并且配合其自己的floor planning 工具的约束条件,在LatticeXP器件中进行布局布线。

ispLEVER工具从布线中提取时序信息,并将它们反注到设计中来进行时序验证。

莱迪思还提供许多用于LatticeXP系列的预先设计的IP(Intellectual Property,知识产权)ispLeverCORE™模块。

采用这些IP标准模块,设计者可以将精力集中于自己设计中的特色部分,从而提高工作效率。

器件结构LatticeXP器件的中间是逻辑块阵列,器件的四周是可编程I/O单元(Program I/O Cell,简称PIC)。

在逻辑块的行之间分布着嵌入式RAM块(sysMEM Embedded Block RAM,简称EBR)。

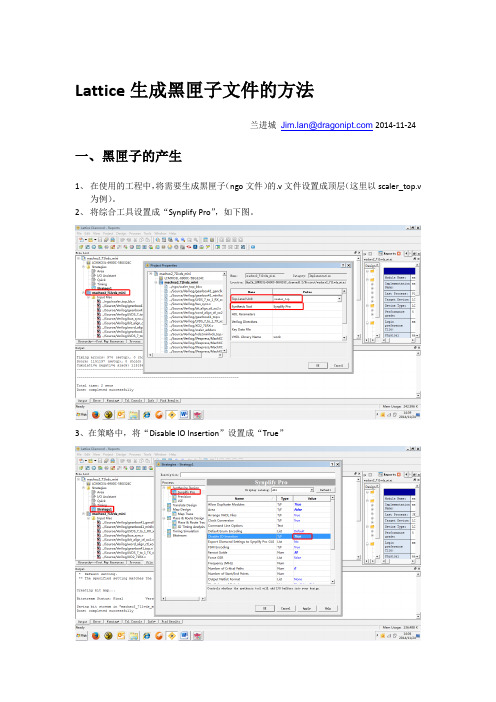

Lattice生成黑匣子的方法

Lattice生成黑匣子文件的方法

兰进城n@2014-11-24

一、黑匣子的产生

1、在使用的工程中,将需要生成黑匣子(ngo文件)的.v文件设置成顶层(这里以scaler_top.v

为例)。

2、将综合工具设置成“Synplify Pro”,如下图。

3、在策略中,将“Disable IO Insertion”设置成“True”

3、编译,运行Translate Design

4、在当前工程目录下,打开文件名根工程名一样的文件夹(这里使用的工程名是

machxo2_71lvds_mini),找到一个.ngo文件。

将这个文件名改成scaler_top.ngo,

5、新建一个scaler_top_bb.v的文件,文件内容为scaler_top.v文件的端口列表。

如下图:

6、在策略中,将“Disable IO Insertion”改回来,设置成“false”

7、到这里,生成两个文件,scaler_top_bb.v和scaler_top.ngo,成功产生黑匣子!

二、黑匣子的使用

1、将scaler_top_bb.v文件添加到当前工程。

2、scaler_top.ngo可以放到与当前工程目录下,这样不需要做额外的设置。

如果不是,则需要另外指定路径,指定方法如下图:

3、在顶层文件中,调用scaler_top模块。

模块名使用scaler_top,(注意不是scaler_top_bb)如下图。

4、编译顶层文件。

完。

LATTICEDIAMOND软件使用说明

LATTICEDIAMOND软件使用说明Lattice Diamond TutorialJune 2012CopyrightCopyright ? 2012 Lattice Semiconductor Corporation.This document may not, in whole or part, be copied, photocopied, reproduced, translated, or reduced to any electronic medium or machine-readable form without prior written consent from Lattice Semiconductor Corporation.TrademarksLattice Semiconductor Corporation, L Lattice Semiconductor Corporation (logo), L (stylized), L (design), Lattice (design), LSC, CleanClock, Custom Movile Device, DiePlus, E2CMOS, Extreme Performance, FlashBAK, FlexiClock, flexiFLASH, flexiMAC, flexiPCS, FreedomChip, GAL, GDX, Generic Array Logic, HDL Explorer, iCE Dice, iCE40, iCE65, iCEcable, iCEchip, iCEcube, iCEcube2, iCEman, iCEprog, iCEsab, iCEsocket, IPexpress, ISP, ispATE, ispClock, ispDOWNLOAD, ispGAL, ispGDS, ispGDX, ispGDX2, ispGDXV, ispGENERATOR, ispJTAG, ispLEVER, ispLeverCORE, ispLSI, ispMACH, ispPAC, ispTRACY, ispTURBO, ispVIRTUAL MACHINE, ispVM, ispXP, ispXPGA, ispXPLD, Lattice Diamond, LatticeCORE, LatticeEC, LatticeECP, LatticeECP-DSP, LatticeECP2, LatticeECP2M, LatticeECP3, LatticeECP4, LatticeMico, LatticeMico8, LatticeMico32, LatticeSC, LatticeSCM, LatticeXP, LatticeXP2, MACH, MachXO, MachXO2, MACO, mobileFPGA, ORCA, PAC, PAC-Designer, PAL, Performance Analyst, Platform Manager, ProcessorPM, PURESPEED, Reveal, SiliconBlue, Silicon Forest, Speedlocked, Speed Locking, SuperBIG, SuperCOOL, SuperFAST, SuperWIDE, sysCLOCK, sysCONFIG, sysDSP, sysHSI,sysI/O, sysMEM, The Simple Machine for Complex Design, TraceID, TransFR, UltraMOS, and specific product designations are either registered trademarks or trademarks of Lattice Semiconductor Corporation or its subsidiaries in the United States and/or other countries. ISP, Bringing the Best Together, and More of the Best are service marks of Lattice Semiconductor Corporation.Other product names used in this publication are for identification purposes only and may be trademarks of their respective companies.DisclaimersNO WARRANTIES: THE INFORMATION PROVIDED IN THIS DOCUMENT IS “AS IS” WITHOUT ANY EXPRESS OR IMPLIED WARRANTY OF ANY KIND INCLUDING WARRANTIES OF ACCURACY, COMPLETENESS, MERCHANTABILITY, NONINFRINGEMENT OF INTELLECTUAL PROPERTY, OR FITNESS FOR ANY PARTICULAR PURPOSE. IN NO EVENT WILL LATTICE SEMICONDUCTOR CORPORATION (LSC) OR ITS SUPPLIERS BE LIABLE FOR ANY DAMAGES WHATSOEVER (WHETHER DIRECT, INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL, INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OF OR INABILITY TO USE THE INFORMATION PROVIDED IN THIS DOCUMENT, EVEN IF LSC HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. BECAUSE SOME JURISDICTIONS PROHIBIT THE EXCLUSION OR LIMITATION OF CERTAIN LIABILITY, SOME OF THE ABOVE LIMITATIONS MAY NOT APPLY TO YOU.LSC may make changes to these materials, specifications, or information, or to the products described herein, at any timewithout notice. LSC makes no commitment to update this documentation. LSC reserves the right to discontinue any product or service without notice and assumes no obligation to correct any errors contained herein or to advise any user of this document of any correction if such be made. LSC recommends its customers obtain the latest version of the relevant information to establish, before ordering, that the information being relied upon is current.Type Conventions Used in This DocumentConvention Meaning or UseBold Items in the user interface that you select or click. Text that you type into the user interface.Variables in commands, code syntax, and path names.Ctrl+L Press the two keys at the same time.Courier Code examples. Messages, reports, and prompts from the software. ...Omitted material in a line of code.Omitted lines in code and report examples....[ ]Optional items in syntax descriptions. In bus specifications, the brackets are required.( )Grouped items in syntax descriptions.{ }Repeatable items in syntax descriptions.| A choice between items in syntax descriptions.ContentsLattice Diamond Tutorial 1Learning Objectives1Time to Complete This Tutorial2System Requirements2Accessing Online Help2About the Tutorial Design2About the Tutorial Data Flow2Task 1: Create a New Project4Task 2: Running Analysis Tools8Task 3: Inspect Strategy Settings10Task 4: Examine Resources11Task 5: Set Timing and Location Assignments13Task 6: Running Place and Route17Task 7: Examine Post Place and Route Results18Task 8: Adjust Static Timing Constraints and Review Results20 Task 9: Comparing Multiple Place and Route Runs21Task 10: Running Export Utility Programs23Task 11: Download a Bitstream to an FPGA24Task 12: Convert a File Using Deployment T ool26C ONTENTSLattice Diamond TutorialThe next generation design tool for FPGA design, Lattice Diamond, isdesigned to address the needs of high-density FPGA designers.This tutorial leads you through all the basic steps of designing andimplementing a mixed VHDL, Verilog, and Edif design targeted to the LatticeECP3 device family. It shows you how to use several processes, tools, andreports from the Lattice Diamond software to import sources, run designanalysis, view design hierarchy, and inspect strategy settings.The tutorialthen proceeds to step through the processes of adding and editing a strategy,specifying the synthesis requirements, examining the device resources,setting timing and location assignments, and editing preferences to configurethe filter to implement the design to the target device.Learning ObjectivesWhen you have completed this tutorial, you should be able to do the following:◆Set up a mixed VHDL, Verilog, and EDIF project◆View and Analyze the design◆Inspect Strategy Settings◆Examine Design Resources◆Se t Timing and Location Assignments◆Place and Route◆Create an Implementation◆Set an Active Implementation◆Compare Multiple Place and Route Runs◆Examine Post Place and Route ResultsL ATTICE D IAMOND T UTORIAL:Time to Complete This TutorialTime to Complete This TutorialThe time to complete this tutorial is about 60 minutes.System RequirementsThe following software is required to complete the tutorial:◆Lattice Diamond software◆(Optional) LatticeECP3 Versa Development KitAccessing Online HelpYou can find online help information on any tool included in the tutorial at anytime by choosing Help > Lattice Diamond Help.About the Tutorial DesignThe design in this tutorial consists of a Verilog HDL module, two VHDLmodule and one EDIF module. The design that you create is targeted toLattice ECP3 device families.About the Tutorial Data FlowThe following figure illustrates the tutorial data flow through the system. Youmay find it helpful to refer to this diagram as you move through the tutorialtasks.L ATTICE D IAMOND T UTORIAL :About the Tutorial Data FlowTutorial Data Flow Design filesTranslate & MapDesignManage ProjectAnalyze design?Yes NoEnter DesignAnalyze DesignSynthesize DesignAnalyze design?[RTL]Analyze design?Yes PAR Design[EDIF][NCD]Analyze or ECOYes ECO design ECO DesignProgram DeviceNo NoECO device?YesAnalyze & ECODevice NoData filedesign?Analyze ElseL ATTICE D IAMOND T UTORIAL :Task 1: Create a New Project Task 1: Create a New ProjectProjects are used to manage input files, preferences, and optimization optionsrelated to an FPGA implementation. While there are a number of tasks youcan perform independent of a project, most designs start with creating a newproject.To create a new project:1.On Windows, select the Lattice Diamond icon or Start > Programs >Lattice Diamond 2.0 > Lattice Diamond .The Lattice Diamond Design Environment appears.The initial layout provides a Start Page which provides a list of commonProject actions like Open... to open a pre-existing project and New.... torun the New Project Wizard. Hyperlinks in the right pane of the Start Pageprovide access to user guides, reference material, and online resourcesavailable from .2.From the Start Page, click Project > New , or from the Diamond mainwindow choose File > New > Project. You can also click the New iconfrom the toolbar and then choose Project .The New Project overview dialog box appears.3.Click Next . The New Project dialog appears.NoteSeveral design entry and analysis features of LatticeDiamond are availablewithout a source file as part of the project, for example, you may wish to defineand generate an IP core or a microprocessor platform using the Diamond interfaceand use the result later in one or more projects. Also the power analysis featuresin Diamond do not require source files to perform estimation .L ATTICE D IAMOND T UTORIAL:Task 1: Create a New Project4.Specify Project name: mixedcounterNoteFile names for Diamond projects and project source files must start with a letter (A-Z, a-z) and must contain only alphanumeric characters (A-Z, a-z, 0-9) and underscores (_).5.Click Browse... to specify a directory on your local PC other than theDiamond installation directory, for example,.NoteYou will have to store your tutorial files in a directory other than your LatticeDiamond installation directory. You do not have the write permission to theDiamond installation directory.6.Enter an implementation name. For this tutorial, enter verilog_vhdl_edif.Implementations are comprised of source and constraint files. You may create or add multiple Implementations per project when you want tocompare multiple place and route runs.By default, when you specify the project name, the implementation name is simultaneously specified the same. For this tutorial, change theimplementation name to verilog_vhdl_edif. The directory to store the implementation will be automatically displayed in the Location area.We will talk about creating a new implementation later in this tutorial.7.Click Next >. The Add Source dialog appears.8.Click Add Source... The Import File dialog appears.9.Select the folder where the source files are located<drive:\diamond_install_directory\version#\examples\mixe dcounter\sourc< p="">e>. Choose count8.edn, count16.vhd, topcount.v, typepackge.vhd in theL ATTICE D IAMOND T UTORIAL:Task 1: Create a New Project directory and click Open. The Add Source step of the Wizard appear withall the selected source added.10.Enable Copy source to implementation directory and click Next. TheSelect Device dialog appears.11.Select the following device options:Family: LatticeECP3Device: LFE3-35EAPerformance Grade: 8Package type: FPBGA484Operating Conditions: CommercialPart Names: LFE3-35EA-8FN484CClick Next.The Project Information dialog appears. The project informationincluding project name, location, implementation name, device, etc. arelisted.12.Click Finish.The File List view is populated with the Process view and the Reportsview.Note◆If you have run Design > Auto Generate Hierarchy and Design > Auto RunBKM Check in a Lattice Diamond session before starting this tutorial, you willalso see the Module Library view, Dictionary view, Hierarchy view displayedbeside the Process view. And the Design view of the HDL Diagram will beopened to the right of the Reports view.◆The File List view, Process view, Module Library view, Dictionary view, andHierarchy view are dockable. You can drag and drop them anywhere in theDiamond main window or even outside the main window.The File List view displays the components of the project.Project name:mixedcounterTarget device:LFE3-35EA-8FN484CStrategies:Strategy1Design Implementation:verilog_vhdl_edifNoteYou can also see Area, I/O Assistant, Quick, Timing listed in the Strategies folderin the File List view. These are predefined strategies supplied by LatticeSemiconductor. They are designed to solve particular types of design. For detailsof these predefined strategies, refer to the online Help.L ATTICE D IAMOND T UTORIAL:Task 1: Create a New ProjectThe imported VHDL, Verilog, and EDIF files appear in the Input Files folder in the File List view. The File List organizes project files by categories: Strategies, Implementation including Input Files, Constraint Files, Debug Files, Script Files, and Analysis Files. You may adjust file order by dragging/dropping of the filenames in the list. Properties of each file are accessed by highlighting a file, clicking the right mouse button, and selecting Properties from the pop up menu.The Process view lists all the processes available, such as synthesize design, translate design, map design, place and route design, and export files.The Reports view provides a way to examine and print process reports. Reports view displays reports for the major processes. There are two panes in the Reports view. The left pane lists the design summary information including the reports types. The reports in detail are displayed in the right pane. You can navigate the reports quickly by using the Find function.Section DescriptionProject Summary Lists the summary information of the project includingmodule name, synthesis tool chosen, implementationname, strategy name, target device, device family, devicetype, package type, performance grade, operatingconditions, logic preference file, software product version, project file name, and location, etc.L ATTICE D IAMOND T UTORIAL:Task 2: Running Analysis ToolsSection DescriptionProcess Reports Lists the synthesis, map, place and route, signal/pad,bitstream reports in HTML format.Analysis Reports Lists the map trace, place and route trace, I/O timinganalysis, IO SSO analysis reports.Log messages are displayed in the Output frame of the Diamond mainwindow.Next you will learn how to explore and analyze the HDL design.Task 2: Running Analysis ToolsDiamond provides an HDL visualization and rule-checks to detect coding styleviolations that may lead to pre-/post-synthesis simulation mismatches.To analyze and view the HDL design:1.Choose Design > Generate Hierarchy or click the Generate Hierarchyicon .The file list is scanned and a syntax check is performed. The ModuleLibrary, Dictionary, Hierarchy views, as well as the HDL Diagram appearin the Diamond main window and are populated with details about theVHDL modules and other symbols like signals and ports of the HDLdesign.The Module Library view is a standard tree-list view that shows all themodules in the loaded design, used and unused. You canopen the entriesin this view to browse the complete port, signal, behavioral block, andinstance hierarchies within each module of the loaded design.The Dictionary view shows a sorted list of all the elements in the design.Within the list, design elements are grouped by name instead of by type.This view is very useful for finding design elements.The Hierarchy view is a mirror of the current view of the HDL Diagram andpresents Ports, Signals, Instances, and Continuous Assignments for thecurrent level of hierarchy.NoteBy default, only modules and instances are displayed in the Module Library view,Hierarchy view, and the Dictionary view. If you want to have a full display of thehierarchy of the design, turn off the Simplified Hierarchy Display option from theOptions dialog (Tools > Options from the Diamond main window) the HDLDiagram section.The Design view shows a graphical display of the HDL module hierarchyof the design.Details about the scan appear in the Output frame.L ATTICE D IAMOND T UTORIAL:Task 2: Running Analysis Tools 2.Choose Design > Run BKM Check. Best Known Methods(BKM)analysis is run.Best Known Methods (BKM) are design guidelines that HDL Diagram uses to analyze your design. BKM checks include the following:Connectivity –Checks the pin connectivity of instances throughout the design.Synthesis –Checks for violations of the Sunburst Design coding styles, as well as other potential synthesis problems.Structural Fan-Out – Checks for maximum structural fan-out violations.Coding Styles – Colors modules based on their line count, colors pins and ports based on their width, validates module names, and also performs big-endian or little-endian checks on all ports.Verification – Validates the existence and timestamps of VCD files. Aseries of Lint-like RTL rule checks are run. Modules that have ruleviolations are color coded in the HDL Diagram view.The checks performed during a BKM run can be customized in theOptions dialog (Tools > Options from the Diamond main window) HDL Diagram section.It is a good practice to run RTL analysis before synthesis to detect coding style that could lead to mismatches between pre-synthesis and post-synthesis simulation results. The analysis views are also excellentdocumentation output for your design.3.After running the BKM check, you might encounter warning and errormessages. Error and warning messages are displayed in the Output,L ATTICE D IAMOND T UTORIAL:Task 3: Inspect Strategy SettingsWarning, and Error frames. In the Output, Error, or Warning frames, if youdouble click the message, the very source indicated in the message willbe opened in the associated editor. This cross-probing function can easeyour check of the source file.For this tutorial, there is no error and warning after running the BKMcheck.4.Double click the topcount block from the HDL DiagramDesign view, orright-click the topcount block and choose View Connectivity. TheConnectivity view appears as a new tab. You can click the Detach Toolicon on the upper right corner the HDL Diagram to make it a separatewindow. The Connectivity view shows signal flow between module ports,internal instances and the behavioral blocks within a particular instance ormodule. It enables you to explore the signal connectivity—signals andbundles—between instances and behavioral blocks within the currentmodule.5.When you finish checking the signal connectivity, you can chooseWindow > Attach Window from the separated HDL Diagramto make itback to the Diamond main window.6.After running the design analysis tool, you can see the top-level sourcetopcount is bold-faced in the File List view.Task 3: Inspect Strategy SettingsA strategy is a collection of settings for controlling the different stages of theimplementation process (synthesis, map, place & route, and so on).Strategies can control whether the design is optimized for area or speed, howlong place and route takes, and many other factors. Diamond provides adefault strategy, which may be a good collection to start with, and somevariations that you can try. You can modify Strategy1 and create otherstrategies to experiment with or to use in different circumstances.L ATTICE D IAMOND T UTORIAL:Task 4: Examine Resources To adjust synthesis settings:1.From the File List view, double-click Strategy1. The Strategies -Strategy1 dialog appears. Browse to Synthesize Design > Synplify Pro.A set of default global synthesis timing constraints and optimizationsettings appear in the panel. Synplify Pro settings are displayed as thedefault in the dialog.For information on SDC file usage in Synplify, see the Synplify andSynplify Pro for Lattice Reference Manual in the Synplify Pro for Latticeinstallation directory.2.Specify the following setting for Synplify Pro:Number of Critical Paths: 10NoteWhen each strategy is selected, descriptive text appears in the lower panel of thedialog.3.Choose OK. Global synthesis options are now set for the design.Task 4: Examine ResourcesDiamond provides visualization tools to help you understand and documentthe physical resources of the target device and the utilization of resources.You can browse and locate device features independent of the project’ssource files. After synthesis, you can view the calculated resource utilization.L ATTICE D IAMOND T UTORIAL:Task 4: Examine Resources To browse device resources:1.Choose T ools > Device View. The Device view appears. Click the DetachTool icon on the upper right corner the Device view to make it aseparate window. An index of the physical resources of the target deviceappear.2.Click the icon to expand the Device folder. Several folders organized byfeature type appear.3.Expand the sysDSP Blocks and sysMEM Blocks folders.4.Type EBR_R17C11 into the Find entry box at the top of the Device View.The first occurrence of an EBR design symbol is highlighted.5.Select the EBR_R17C11 in the list. Right-click EBR_R43C11 and chooseShow in > Floorplan View.Floorplan View provides a large-component layout of your design. Itdisplays user constraints from the logical preference file (.lpf) andplacement and routing information.L ATTICE D IAMOND T UTORIAL:T ask 5: Set Timing and Location6.Close the Floorplan view and the Device view.After synthesis, you can view the calculated utilization of resources.To synthesize the design and examine resource utilization:1.From the Process View, double-click Synthesize Design.2.When the synthesis process is complete, select View > Show Views >Post Synthesis Resources. Select the Hierarchy –Post SynthesisResources tab.The Post-Synthesis Hierarchy View displays the number of logicalresources within each level of the design.Task 5: Set Timing and Location AssignmentsTiming and location assignments constrain logic synthesis, as well as back-end map, place, and route programs to help meet your design requirements.A well constrained design helps optimization algorithms work as efficiently aspossible. In this section you'll set default timing constraints for the operatingfrequency and I/O timing then assign package pins tospecific I/O signals.To set timing and location assignments:1.From the Process view, double-click Translate Design and then MapDesign. The batch interface to logic synthesis, EDIF translation, and thedesign mapper run. Report files appears in the Reports view. To view eachprocess report, select the process in the Design Summary pane.Each major stage of an FPGA implementation is illustrated as a milestonein the Process view: Synthesize Design, Translate Design, Map Design,Place&Route Design, and Export Files. The status of any stage isrepresented by the following color-coded icons:◆Completed (Green check mark) - The stage completed successfullyand produced output.◆Warning (Yellow Exclamation mark) - The stage completed withwarning messages generated. You can go to the Warning panel toview the warning messages.</drive:\diamond_install_directory\version#\examples\mixe dcounter\sourc<>。

LATTICE_非常详细的时序约束(中文教程)

©LATTICE SEMICONDUCTOR CORPORATIONPage 1Achieving Timing ClosureJohn LiAgenda•Timing closure的概念•Timing closure的步骤•采用合适的Coding Style •进行适当的综合约束•管脚锁定•实施Lattice constrains •Map•布局布线•控制place and route •Floorplanning the design©LATTICE SEMICONDUCTOR CORPORATIONPage 2Timing closure的概念•当前FPGA的设计规模越来越大,复杂程度日益增加,同时要求系统的Perfromace也越来越高。

•获得Timing目标越来越困难.•设计者必须采用各种技术提升系统性能以满足设计的Timing要求.©LATTICE SEMICONDUCTOR CORPORATIONPage 3Timing closure procedure• 1.采用合适的coding style • 2.进行适当的综合约束• 3.管脚锁定• 4.实施Lattice constrains • 5.Map• 5.布局布线•7.控制place and route •8.Floorplanning the design©LATTICE SEMICONDUCTOR CORPORATIONPage 4关于提升FPGA系统性能,工程师最容易想到的方法就是通过进行综合约束、布局布线约束、和其他的优化技术提升系统性能,当然这些都是设计过程中所必需的,但所有这些优化方法对于系统性能的提升都是有限的,系统的性能最终还是取决于工程师的设计(coding style),其中同步设计是最重要的一点. 下面讨论一些具体的coding 技术,合理的运用这些coding技术能够尽可能的减小两级寄存器之间的延时从而获得更高的系统速度.-通用的coding style--Hierarchical Coding---Team Based的设计:多个工程师可以同时参与到一个复杂设计中来。

Vector Magic汉化版及中文使用教程

位图转矢量软件Vector Magic汉化版及中文使用教程它是一个可以自动描募的软件,可以把JPG、BMP、PNG、GIF等位图图像精确地转换为AI可以编辑的矢量格式,并且此软件容易操作,可以以全自动的方式运行转换。

此软件比AI和CDR自带的实时描募和位图转矢量图工具要强大的多。

一、载入图像:可以选择从一个文件夹载入、通过剪贴板载入,最简单的办法是把需要载入的图像直接拖拉到面板上的左边。

二、如果不太熟悉软件,可以在向导界面单击“全自动”按钮,系统会自动计算,然后弹出完成界面。

点击上步的完成按钮,弹出保存页面,可以点击另存按钮保存文件,系统提供了三种文件保存方法:另存、拖放和快速,可另存为AI、DXF、EPS、PDF等格式文件。

三、选择软件“基本”模式,选择这个模式后,要回答几个问题即可。

1、图像类型,有三种选择(1)照片模式:如数码相机获取的人物或风景图像。

(2)制品用混合边:如经过防锯齿处理的图形。

如果不确定类型,可以选择这个。

(3)作品无混合边:图像边缘生硬,指没有经过防锯齿处理的图形。

2、输入质量,也有三种选择(1)高:图像干净、清晰,无噪点。

(2)中:图像有少许噪点,比较的是经过JPEG压缩过的图像。

(3)低:图像不清晰,噪点比较多,或者是扫描分辨率比较低。

*对于一般扫描质量比较好的图,可以选择中等质量。

但在转矢量图之前,必须要在PS 中进行处理。

3、颜色模式也有三种选择(1)两色:比较典型的代表是黑白图像。

(2)自定义颜色:颜色由用户指定。

程序会提供建议的调色板,用户可进行编辑。

(3)多种颜色:使用所有必要的颜色,对有渐变的图像比较好。

*如果选择了(1)或(3)时,程序会直接进行矢量化过程。

但如果选择了自定义颜色,则程序会进入下一步“选择色板”,让用户指定、编辑颜色。

4、选择色板(1)建议的调色板:程序会自动分析,提供建议的色板供用户选择。

并在推荐的调色板前面用双箭头或单箭头标记。

用户还可以使用AddAdditional palette面板来增加另外的色板。

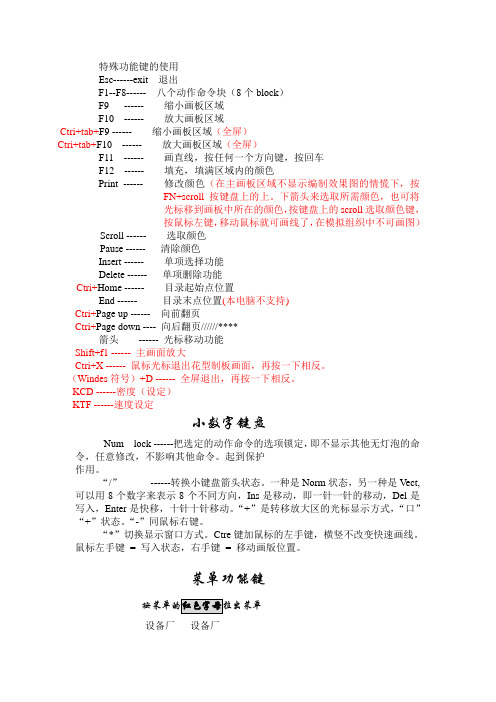

胜歌绘图中文操作

特殊功能键的使用Esc------exit 退出F1--F8------ 八个动作命令块(8个block)F9 ------ 缩小画板区域F10 ------ 放大画板区域Ctri+tab+F9 ------ 缩小画板区域(全屏)Ctri+tab+F10 ------ 放大画板区域(全屏)F11 ------ 画直线,按任何一个方向键,按回车F12 ------ 填充,填满区域内的颜色Print ------ 修改颜色(在主画板区域不显示编制效果图的情慌下,按FN+scroll按键盘上的上。

下箭头来选取所需颜色,也可将光标移到画板中所在的颜色,按键盘上的scroll选取颜色键,按鼠标左键,移动鼠标就可画线了,在模拟组织中不可画图)Scroll ------ 选取颜色Pause ------ 清除颜色Insert ------ 单项选择功能Delete ------ 单项删除功能Ctri+Home ------ 目录起始点位置End ------ 目录末点位置(本电脑不支持)Ctri+Page up ------ 向前翻页Ctri+Page down ---- 向后翻页//////****箭头------ 光标移动功能Shift+f1 ------ 主画面放大Ctri+X ------ 鼠标光标退出花型制板画面,再按一下相反。

(Windes符号)+D ------ 全屏退出,再按一下相反。

KCD ------密度(设定)KTF ------速度设定小数字键盘Num lock ------把选定的动作命令的选项锁定,即不显示其他无灯泡的命令,任意修改,不影响其他命令。

起到保护作用。

“/”------转换小键盘箭头状态。

一种是Norm状态,另一种是Vect,可以用8个数字来表示8个不同方向,Ins是移动,即一针一针的移动,Del是写入,Enter是快移,十针十针移动。

“+”是转移放大区的光标显示方式,“口”“+”状态。

凯瑞软件快速入门操作手册

凯瑞汽车美容维修管理软件快速入门操作手册本教程为快速入门教程,不对所有的项进行详细说明讲解,具体详细的功能说明,请查看帮助手册或下载视频教程!1、数据清零【系统管理】┅【数据清零】(1)进入如图1所示的窗口,单击要清零的项目(如:员工档案)(2)弹出如图2所示的窗口,单击是(Y)按钮即可清除员工档案的数据。

其他项目的清零也是如此操作。

2、系统管理设置【系统管理】┅【公司设置】针对系统的一些使用环境进行设置,如如公司基本信息,系统设置(设置单号编号规则、小数位数、默认仓库、售价、进价选择),单据设置(单据类型、命名规则、前缀),自定义字段(自定义字段名称、批次),系统中80%设置已无须更改按默认设置即可,之所以放在第二步,是因为很多情况用到后面发现很多功能无法执行等,都是和设置有关,详细的每一项功能说明,请查看软件上面的帮助。

(1)公司信息设置【系统管理】┅【公司设置】,打开如下图所示的窗口,填写好公司的名称、电话传真号码和地址,保存。

填写好的公司信息会在以后的单据打印中显示出来。

(2)系统设置【系统管理】┅【公司设置】┅【系统设置】,打开如下图所示的窗口,填写好相关信息(金额保留小数位,数量保留小数位,销售单价选择,采购单价选择,默认仓库选择,编号项目的前缀设置,出库数量是否禁止超过实际库存数的设置),保存。

(3)单据设置【系统管理】┅【公司设置】┅【单据设置】,打开如下图所示的窗口,选择单号命名规则,单击单号前缀可对单据单号前缀进行修改。

(4)自定义字段设置【系统管理】┅【公司设置】┅【自定义字段】,打开如下图所示的窗口,选择单据类型,自定义中文字段名可以自行定义字段名称。

设置好之后点击保存按钮。

3、用户设置(1)用户管理【系统设置】┅【用户管理】,打开如下图所示的窗口,点击增加按钮打开创建窗口,录入操作用户的信息(用户名,登陆密码,所属公司,是否有查看进价的权限),设置好之后点击保存按钮保存。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Lattice MachXO TM设计指南v1.11.介绍 (4)1.1特征 (4)1.2产品系列和器件选择手册 (5)1.3性能分析 (6)2.体系结构 (7)2.1M ACH XO结构概述 (7)2.1.1PFU结构 (7)2.1.2Slice结构 (8)2.1.3布线资源 (9)2.2结构特征 (9)2.2.1时钟/控制信号网络 (9)2.2.2锁相环PLL (10)2.2.3片内时钟振荡器 (11)2.2.4嵌入块RAM (EBR) (11)2.2.5I/O特性 (11)2.2.6休眠模式 (13)2.2.7器件编程 (13)3.设计综合&实现 (14)3.1开发流程 (14)3.2设置约束项 (16)3.2.1设置I/O位置 &属性 (16)3.2.2设置时钟频率|周期 (16)3.2.3设置建立&保持时间 (17)3.2.4设置Tco时间 (19)3.2.5设置MutiCycles | MaxDelay | Tpd (20)3.2.6时序约束例外(BLOCK) (20)3.2.7信号分组 (20)4.器件应用要点 (21)4.1M ACH XO系列器件V CC,V CCAUX,V CCIO作用和连接 (21)4.2M ACH XO系列器件各电源上电顺序及要求 (21)4.3M ACH XO热插拔应用注意事项 (21)4.4如何使用全局复位功能 (22)4.5如何使用全局输出三态功能 (22)4.6如何使用全局时钟 (23)4.7如何使用TFR功能(透明现场升级) (23)4.8如何使用M ACH XO的差分信号 (24)4.9如何接口5V输入信号 (25)4.10如何在同一B ANK使用不同I/O口电平标准 (25)4.11如何减小T CO时间 (26)4.12什么-M速度级别? (27)4.13如何获得时序分析结果? (27)4.14如何知道资源利用率 (28)4.15如何使用M ACH XO的块RAM(EBR) (28)4.16如何利用PFU生成移位寄存器和分布式RAM (29)4.17如何使用锁相环(PLL) (30)4.18下载接口(TAP)的连接建议 (30)4.19如何设置加密位和用户代码 (30)4.20如何使用P OWER C ACULTOR估计功耗 (31)4.21如何快速建立器件原理图库? (32)4.22如何选择综合工具? (32)4.23关于约束文件 (32)4.24如何使用M ODELSIM 进行仿真 (33)5.相关资料 (33)1.介绍MachXO器件是 Lattice 公司基于FLASH+SRAM技术CPLD器件。

FLASH存储用户配置程序,SRAM运行用户逻辑。

上电后,或者在JTAG命令控制下,MachXO自动执行FLASH到SRAM的传输。

MachXO集成了FPGA器件灵活性和传统CPLD器件的非易失特性于一身,为用户提供嵌入式RAM块(EBR),锁相环(PLL),差分I/O等特性。

并且支持不中断业务的现场升级能力(TFR技术)。

1.1特征·器件使用 .13μm SRAM + FLASH 工艺,有E版(1.2V)和C版(1.8/2.5/3.3V)两个版本 。

·非易失器件,瞬间上电( <1ms ),高安全性,单片解决方案。

·TFR技术保证现场升级过程I/O状态受控。

·高性能:系统性能超过250MHz,t PD=3.5ns。

·芯片由FLASH,可编程功能单元PFU,布线网络,嵌入式块RAM,锁相换PLL,I/O单元组成。

·FLASH存储用户程序,支持后台更新。

·PFU可实现逻辑,Ripple①,也可配置为分布式RAM,ROM。

·锁相环支持分频,倍频,移相。

周期抖动小于125ps。

·I/O可配为LVTTL,LVCMOSxx,LVDS,PCI。

·支持输出电流可调,输出边沿斜率可调,集电极开路,总线保持功能,内部上拉,下拉等。

·热插拔支持②。

·兼容IEEE 1149.1边界扫描标准(JTAG),IEEE 1532在系统编程标准。

·低的静态功耗2~10mA。

·休眠模式省电达100倍。

Note:① Ripple模式下,可高效的实现小的运算功能。

如2位计数,2位加减,2位比较等功能。

② 非True LVDS引脚,I DK < 1mA ( 0 < V IN <= V IHMAX ).True LVDS引脚, I DK < 1mA ( V IN <= V CCIO ).True LVDS引脚, I DK = 35mA ( V IN > V CCIO ).1.2产品系列和器件选择手册Table 1. MachXO 系列器件选择手册LCMXO256 LCMXO640 LCMXO1200 LCMXO2280 注查找表256 640 1200 2280 LUTs分布式RAM( Kbits) 2.0 6.0 6.25 7.5 Dist.嵌入式块RAM(Kbits) 0 0 1´ 9 3´ 9 EBR VCC电压 1.2/1.8/2.5/3.3V ①锁相环PLL 0 0 1 2最大I/O 78 159 211 271Package100-TQ (14X14) 78 74 73 73144-TQ (20X20) 113 113 113csBGA 100 (8X8) 78 74csBGA 132 (8X8) 101 101 101fpBGA 256 (17X17) 159 211 211fpBGA 324 (19X19) 271注:① XO器件有三组供电电压,分别为内核电源V CC,辅助电源V CCAUX ,I/O电源V CCIO .E版本器件V CC =1.2V, V CCAUX=3.3V, V CCIO =1.2/1.8/2.5/3.3V.C版本器件V CC =1.2/1.8/2.5/3.3V, V CCAUX=3.3V, V CCIO =1.2/1.8/2.5/3.3V.② MachXO 系列器件不同密度、相同封装的器件是引脚兼容的。

详情咨询技术支持。

③ MachXO 系列为dual mark 芯片,例如LCMXO640E-4F256C ,在此芯片上同时也被标注为-3I也就是说此芯片既可作为-4 commercial 芯片用,也可作-3 industrial 芯片用。

1.3性能分析下表列举了MachXO和Altera MAX II 以及 Lattice传统4k CPLD的指标对比。

Attribute MachXO MAX II 4000工艺130nm 180nm 180nm密度256~2280 LUTs 240~2210 LUTs 32~512 MicroCell Max I/O 78~271 80~272 32~208t PD 3.5ns (smallest device) 3.6ns(smallest device) 2.5~3.5nsI/O 标准LVTTLLVCMOSPCILVDSLVPECL LVTTLLVCMOSPCILVTTLLVCMOSPCI5V容忍-- -- Yes架构PFU阵列.每个PFU有 8个LUT4和8个寄存器组成.部分PFU可配置为分布式RAM. LAB阵列.每个LAB有10个LUT4和10个寄存器组成.所有LAB均不能配置为分布式RAM .GLB阵列.每个GLB有36输入,83乘积项,16个宏单元.没有分布式RAM.Block RAM 0~27.6Kbits None None PLLs 0~2 None None配置支持后台 FLASH编程.FLASH到SRAM的更新过程中I/O受控支持后台 FLASH编程.FLASH到SRAM的更新过程中I/O三态FLASH编程过程中I/O状态受控静态电流2~10mA(<100uA sleep) 2~10mA 2~13mA13~32uA(Z系列)操作电压 1.2V or 1.8/2.5/3.3V 1.8V or 2.5/3.3V 1.8V/ 2.5V/3.3VMachXO器件结合了FPGA和传统CPLD器件的优点,非常适合于逻辑容量介于高密度CPLD和低密度FPGA的之间交叉应用。

与竞争对手相比,先进的工艺和技术使得Lattice MachXO提供更低的成本和更好的特性。

2. 体系结构2.1MachXO 结构概述MachXO 系列器件由可编程功能单元(PFU),可编程I/O单元(sysIO),布线网络,嵌入式RAM块(EBR),模拟锁相环(PLL)等组成。

其中,XO256 不带锁相环,没有RAM块。

I/O分2个Bank.XO640 不带锁相环,没有RAM块。

I/O分4个Bank.XO1200一个锁相环,一个RAM块。

I/O分8个Bank.XO2280两个锁相环,三个RAM块。

I/O分8个Bank.Figure 1. XO2280结构框图2.1.1PFU结构MachXO的内核有PFU块和PFF块组成。

通过编程,PFU块可以实现逻辑,Ripple,分布式RAM和ROM等功能。

PFF除了不能实现分布式RAM外,等同于PFU。

以后将统称PFU。

每个PFU包含4 个slice。

PFU的输入和输出信号全部来自布线网络。

共有53个输入信号,25输出信号。

Figure2.PFU框图2.1.2Slice结构Slice有四种工作模式:逻辑, Ripple, 分布式RAM 或者分布式ROM。

逻辑模式下,LUT4 可实现任意4输入变量的逻辑式,LUT4的输出可以馈给对应的寄存器。

寄存器可工作在FF或者Latch模式下。

另外,还有附加的逻辑使得通过把LUT4组合,实现更宽输入的查找表(LUT5, LUT6, LUT7, LUT8)。

Ripple模式下,可高效的实现小的运算功能。

如2位计数,2位加减,2位比较等功能。

PFU(不含PFF)的LUT4可以配置为16位分布式RAM。

Figure3. Slice框图2.1.3布线资源布线资源有开关电路,缓冲器(buffer),金属线构成。

PFU之间的连接方式分为三种类型,X1类,X2类和X6类。

X1类连接相邻的PFU,提供了最小的延时;X2,X6类连接为跨越2个 PFU和6个PFU的PFU提供连接。

X2,X6类连接路径上插入了buffer,较X1 要慢些。

布局布线工具能够自动完成最佳路径的选择,布线资源的优化,无需人工干预。

用户也可以通过EPIC工具察看布线,并允许手动调整。

2.2结构特征2.2.1时钟/控制信号网络MachXO系列由4个初级全局时钟(primary)和4个次级全局时钟(secondary)。