原理图与PCB的封装和网表的比较

pcb设计知识点大全

pcb设计知识点大全1. 什么是PCB设计?PCB设计(Printed Circuit Board Design)又称印刷电路板设计,是指利用专业电路设计软件根据电路原理图和布局需求,通过布线、电路元器件的放置和连接等步骤来设计电子产品中的印刷电路板。

PCB设计是电子产品制造过程中的一项重要环节,决定了电路板的功能、性能和可靠性。

2. PCB设计流程PCB设计流程包括原理图设计、封装库维护、网络表生成、布局设计、布线设计、设计规则检查、信号完整性分析等多个环节。

其中,原理图设计是整个设计流程的基础,通过绘制完整的原理图,明确电路板上的元器件连接关系。

封装库维护负责维护元器件的封装库文件,确保使用正确的封装。

网络表生成将原理图转化为电路网表,用于后续的布局和布线设计。

布局设计是根据电路板上的元器件尺寸和布局要求,确定元器件的相对位置。

布线设计则是将各个元器件之间的连接线进行布线,确保信号传输的可靠性。

设计规则检查和信号完整性分析则是在布线完成后进行的,用于验证设计是否符合规范并优化信号传输的品质。

3. PCB设计注意事项在进行PCB设计时,需要注意以下几点:(1) 元器件布局:合理安排元器件的位置,减少信号干扰和电磁辐射。

(2) 信号走线:注意信号线的长度、走向和宽度,避免信号串扰和阻抗失配。

(3) 电源和地线:保持电源和地线的宽度足够,避免电源噪声和接地回流问题。

(4) 高速信号处理:对于高速信号,需要特别注意信号完整性和时序约束。

(5) 散热设计:对于功率较大的元器件,需考虑散热问题,合理设计散热器和散热通路。

(6) EMI设计:合理规划PCB布局,减少电磁干扰问题。

4. 常用的PCB设计软件PCB设计软件根据不同的需求和使用习惯,有多种选择。

以下是常用的PCB设计软件:(1) Altium Designer:功能强大,适用于中小规模的电路板设计。

(2) Eagle:易于上手,适用于初学者,拥有大量的元器件库文件。

原理图和pcb的区别

原理图和pcb的区别

原理图和PCB是电子线路设计中的两个重要概念。

首先,原理图是一种用图形符号表示电子元件之间连接关系的图纸。

它展示了电路中各个元件的类型、数值和连接方式。

原理图是设计师用来构思和设计电路的工具,它能够清晰地展示不同元件之间的连接关系,并帮助设计师理解电路功能和工作原理。

而PCB(Printed Circuit Board,印刷电路板)是原理图的物理

实现。

它是一种用于支持和连接电子元件的基板,通常由绝缘材料如玻璃纤维增强塑料制成。

PCB上布局了原理图中各个

元件和连接线的物理位置和路径。

通过将元件焊接在PCB上,电子线路得以实现。

原理图和PCB的区别主要在于功能和表现形式不同。

原理图

是设计电路的理论框架,只通过符号展示元件之间的连接关系;而PCB是实际电路的物理实现,通过布局和焊接来实现电子

元件的连接。

原理图更侧重于电路设计和分析,而PCB更侧

重于电路的制造和组装。

综上所述,原理图和PCB在电子线路设计中各有其重要作用,原理图是电路设计的理论基础,而PCB是原理图的物理实现。

它们一起协作,使得电子线路设计能够顺利地从理论到实践。

CADENCE原理图与PCB设计说明

CADENCE原理图与PCB设计说明内部资料请勿外传CADENCE原理图与PCB设计说明(第1版)⽬录⽬录序⾔ (1)第⼀章系统简介 (2)1.1 系统组成 (2)1.1.1 库 (2)1.1.2 原理图输⼊ (2)1.1.3 设计转换和修改管理 (2)1.1.4 物理设计与加⼯数据的⽣成 (3)1.1.5 ⾼速PCB规划设计环境 (3)1.2 Cadence设计流程 (3)第⼆章Cadence安装 (4)2.1安装步骤 (4)2.2 LICENSE设置 (7)2.3 库映射 (7)2.4 修改cds.lib⽂件,设置原理图库: (8)2.5 编辑ENV⽂件,设置PCB库: (9)第三章CADENCE库管理 (11)3.1 中兴EDA库管理系统 (11)3.2 CADENCE库结构 (13)3.2.1 原理图(Concept HDL)库结构: (13)3.2.2 PCB库结构: (13)第四章项⽬管理器 (15)4.1 项⽬管理的概念 (15)4.2 创建或打开⼀个项⽬ (15)4.3 原理图库的添加: (16)4.4 填写设计(Design)名称 (17)4.5 增加新的Design(设计) (18)- I -CADENCE原理图与PCB设计说明4.6 项⽬的⽬录结构 (18)第五章原理图设计 (20)5.1 图纸版⾯设置 (20)5.1.1 图纸统⼀格式设置 (20)5.1.2 栅格设置 (22)5.2Concept-HDL的启动 (23)5.3添加元件 (24)5.3.1 逻辑⽅式添加器件 (24)5.3.2 物理⽅式添加器件 (25)5.4画线 (26)5.4.1 Draw⽅式 (26)5.4.2 Route⽅式 (27)5.5 添加信号名 (27)5.6 画总线 (28)5.7 信号名命名规则 (29)5.8 元件位号 (31)5.8.1 元件位号⼿⼯标注 (31)5.8.2 元件位号的⾃动标注 (32)5.8.3 元件位号的⾃动排序 (33)5.9 Cadence属性 (34)5.10 组操作 (36)5.10.1 组定义: (36)5.10.2 组命名 (36)5.10.3 组操作 (37)5.11 常⽤命令 (38)5.11.1 常⽤的快捷键 (38)5.11.2 检查连接关系 (39)5.11.3 点画命令 (39)5.11.4 查找元件和⽹络 (39)5.11.5 两个不同⽹络名的⽹络连接的⽅法 (40)5.11.6 错误检查 (40)5.11.7 检查Cadence原理图单个⽹络名 (40)- II -⽬录5.11.8 对隐藏了电源和地腿的器件定义电源和地信号 (41)5.12 增加新的原理图页 (41)5.13 原理图多页⾯操作 (42)5.14 信号的页区位置交叉标注(Cross Reference) (42)5.14.1 信号的页区位置交叉标注(Cross Reference)的作⽤ (42) 5.14.2 交叉标注需注意的⼏点: (43)5.14.3 信号的交叉标注(Cross Refrence)的⽅法 (43)5.14.4 层次设计中出模块信号的交叉标注 (43)5.14.5 出页信号的交叉标注的要求 (44)5.15 在不同的project下实现原理图拷贝 (44)5.16 打印图纸 (47)5.17 ⾃动⽣成料单 (48)5.18 原理图归档 (50)5.19 原理图评审 (51)第六章从原理图到PCB (52)6.1从原理图到PCB的实现 (52)6.1 .1 原理图到PCB的转换过程: (52)第七章PCB设计 (55)7.1 导⼊数据 (55)7.2 Allegro⽤户界⾯ (55)7.2.1 控制⾯板的作⽤ (56)7.2.2 ⼯具栏的显⽰ (57)7.3 Layout准备 (58)7.3.1 创建PCB图的物理外形 (58)7.3.1.2 在Allegro界⾯下创建板外框: (61) 7.3.2 设置板图尺⼨参数 (62)7.3.3 设置版图的栅格值: (63)7.3.4 设置板图选项 (63)7.3.5 设置PCB板的叠层 (64)7.3.6 设置约束条件 (65)7.3.6.1 设置板的缺省间距: (65)- III -CADENCE原理图与PCB设计说明7.3.6.2 设置扩展的距离规则 (66)7.3.6.3 设置扩展的物理规则 (69)7.3.6.4 编辑属性 (69)7.3.7 可视性和颜⾊设置 (70)7.4 PCB布局 (70)7.5 PCB布线: (73)7.6 添加过孔和替换过孔 (74)7.6.1 添加过孔 (74)7.6.2 替换过孔 (75)7.7 优化⾛线 (76)7.8 覆铜处理 (77)7.8.1 阴版覆铜 (77)7.8.2 阳版覆铜 (78)7.9 分割电源平⾯ (80)7.10 位号标注 (83)7.11 加测试点 (83)7.12 DRC检查 (83)7.13 ⽣成报告⽂件 (84)7.14 V ALOR检查 (85)7.15 ⽣成光绘⽂件和钻孔⽂件 (85)7.15.1 ⽣成光圈⽂件(art-aper.txt),即D码表 (85)7.15.2 ⽣成钻孔⽂件 (86)7.15.3 ⽣成光绘⽂件 (86)7.15.3.1 在Artwork中加⼊所需的层 (86)7.15.3.2 ⽣成光绘⽂件 (90)7.16 PCB评审 (93)第⼋章公司的PCB设计规范 (94)- IV -序⾔序⾔Cadence软件是我们公司统⼀使⽤的原理图设计、PCB设计、⾼速仿真的EDA⼯具。

电路原理图和pcb的应用区别

电路原理图和pcb的应用区别1. 电路原理图电路原理图是一种用于描述电路连接关系和元件功能的图形表示方法。

它通过使用符号来代表不同的电子元件和连接线,清晰地展示了电路的结构和工作原理。

电路原理图通常用于电路设计和分析阶段。

以下是电路原理图的主要特点和应用:•符号表示:电路原理图使用一系列标准化的符号来代表各种电子元件,如电阻、电容、电感、晶体管等。

这些符号通常简化了实际元件的物理结构,使电路设计人员更容易理解和分析。

•连接关系:电路原理图表示电子元件之间的连接关系。

通过线段(连接线)和交叉点表示不同元件之间的连接方式。

这有助于设计人员理解信号的流动和相互作用。

•电路分析:电路原理图用于进行电路分析和计算。

通过应用基本的电路定律和理论,可以通过电路原理图来计算电流、电压、功率和其他关键参数。

•教学和学习:电路原理图被广泛应用于电子工程教学和学习中。

它提供了一种直观的方式,帮助学生理解电路的结构和工作原理。

•电路模拟:基于电路原理图,可以使用电路模拟软件进行电路仿真。

这种仿真可以帮助设计人员验证电路的功能和性能。

2. PCB(Printed Circuit Board)PCB(印刷电路板)是一种用于支持和连接电子元件的可靠基板。

它通过使用导电轨道、孔径、焊盘和引脚,将电子元件进行连接和固定。

以下是PCB的主要特点和应用:•机械支持: PCB提供了一个固定和支持电子元件的机械平台。

通过PCB上的孔径和引脚,电子元件可以轻松插入、安装和固定在正确的位置上。

•电气连接: PCB通过导电轨道(通常是镀铜)将不同的电子元件连接起来。

这些导电轨道可以在不同的层次上布置,以实现不同电子元件之间的连接。

•布线和层次: PCB允许设计人员在不同的层次上进行电路布线。

通过在不同层上设计和布置导电轨道,可以实现更紧凑、更复杂的电路结构。

•可靠性和生产: PCB具有良好的可靠性和生产性。

它可以通过自动化的生产流程进行大规模制造,从而提高生产效率和质量。

原理图与PCB的封装和网表的比较

原理图与PCB的封装和网表的比较

原理图与PCB的封装和网表的比较

1.打开原理图,在原理图的任何一页点击鼠标右键并点击Creat netlist,如下图:

2.在net creation中选择参数,在Preferences中的Output Format中选择“PADS ASCII”,Net Identiffer Scope中选择“Net Labels and Ports Global”,Sheets to Netlist中选择“Active project”,其余均不用设置,然后点击“OK”,如下图所示:

3.原理图会生成.PRT(器件封装)和.NET文档,并把这两个文档导出原理图并保存,如下图所示:

4.用UltraEdit工具把.PRT(器件封装)和.NET文档同时打开,并把.NET删去首行和.PRT删去尾行并保存,再把.NET所有文字拷贝,并粘贴到.PRT文档的下面,如下图:

5.并把当前的.PRT文档另存为.asc文档,如下图:

6.打开PADS Layout工具,并导入.asc文档,如下图所示:

7.在PADS Layout的主菜单T ools中点击Compare/ECO T ools,进行参数设置,如下图所示:

8.执行“RUN”命令,运行完毕后弹出Process Status命令框,点击“Show Report”就能看到原理图和PCB封装和网表不同的地方,如下图所示:

9.把生成的Layout.rep发给负责的PCB Layout工程师,以达到网表和封装高度一致。

设计指导AltiumDesigner原理图和PCB设计

▪ 战略合作伙伴: Altera, Atmel, Analog Devices, Infineon Technology, Intel, Mitsubishi, Philips, Renesas Technology, STMicroelectronics, and Xilinx

原理图设计

▪ 原理图输出 – 支持多种网表格式

原理图设计 ▪ 原理图打印

Altium Designer Training

▪ Altium Designer主要特点 ▪ DXP系统平台介绍 ▪ 原理图设计 ▪ PCB设计

PCB设计

▪ 提供了完整的由规则驱动的PCB设计环境 ▪ Situs™拓扑自动布线系统性能经过了实质性的完善 ▪ 支持高速设计,具有成熟的布线后信号完整性分析工具 ▪ 布线和可视化功能,从而能更快地实现电路板布局 ▪ Orcad®、PADS、AutoCAD和其它软件的文件导入和导出功能 ▪ 完整的ODB++ / Gerber CAM-系统使得用户可以重新设计原有的设计,弥补设计和制造之间的差

Corporate information 奥腾公司简介

Altium 理念

▪ Altium’s Vision "Historically, the most advanced, state of the art design tools have been prohibitively priced, with access being limited to engineers based in the few companies that could afford them. The Altium vision – unchanged since the company’s inception – is to break down these barriers to innovation and technological advancement and provide every engineer and system designer with easy access to the best possible design tools.“ “长久以来,大多数高端的设计工具以其昂贵的价格,限制了工程师只能在少数公司中使用。而 Altium公司一贯的理念就是打破传统的价格束缚,以先进的技术为广大工程师及系统设计人员提供 最适合的设计工具。”

第16章 版图与电路图网表

9

Backup Files

LVS automatically creates a backup of each verification database file, using the same filename as the original, but with a .vdo extension. Each time you modify the .vdb file, LVS will overwrite the previous backup of that file.

7

LVS writes the verification results to an optional output file with the extension .out. The program can also produce an optional node and element list with the extension .lst. Information required for the verification run— input and output files, plus verification options—is referred to as a verification setup. LVS saves a setup to a verification database (.vdb) file. Multiple verification setups can be exported to a batch (.bat) file for subsequent invocation from a DOS command prompt.

Commands for creating, opening, saving, and printing files Commands for displaying or hiding elements of the user interface

原理图和PCB图的常见错误

一、原理图和PCB图的常见错误1.原理图常见错误:(1)ERC报告管脚没有接入信号:a. 创建封装时给管脚定义了I/O属性;b.创建元件或放置元件时修改了不一致的grid属性,管脚与线没有连上;c. 创建元件时pin方向反向,必须非pin name端连线。

(2)元件跑到图纸界外:没有在元件库图表纸中心创建元件。

(3)创建的工程文件网络表只能部分调入pcb:生成netlist时没有选择为global。

(4)当使用自己创建的多部分组成的元件时,千万不要使用annotate.2.PCB中常见错误:(1)网络载入时报告NODE没有找到:a. 原理图中的元件使用了pcb库中没有的封装;b. 原理图中的元件使用了pcb库中名称不一致的封装;c. 原理图中的元件使用了pcb库中pin number不一致的封装。

如三极管:sch中pin numb er 为e,b,c, 而pcb中为1,2,3。

(2)打印时总是不能打印到一页纸上:a. 创建pcb库时没有在原点;b. 多次移动和旋转了元件,pcb板界外有隐藏的字符。

选择显示所有隐藏的字符,缩小p cb, 然后移动字符到边界内。

(3)DRC报告网络被分成几个部分:表示这个网络没有连通,看报告文件,使用选择CONNECTED COPPER查找。

另外提醒朋友尽量使用WIN2000, 减少蓝屏的机会;多几次导出文件,做成新的DDB文件,减少文件尺寸和PROTEL僵死的机会。

如果作较复杂得设计,尽量不要使用自动布线。

在PCB设计中,布线是完成产品设计的重要步骤,可以说前面的准备工作都是为它而做的,在整个PCB中,以布线的设计过程限定最高,技巧最细、工作量最大。

PCB布线有单面布线、双面布线及多层布线。

布线的方式也有两种:自动布线及交互式布线,在自动布线之前,可以用交互式预先对要求比较严格的线进行布线,输入端与输出端的边线应避免相邻平行,以免产生反射干扰。

必要时应加地线隔离,两相邻层的布线要互相垂直,平行容易产生寄生耦合。

Altium与PADS的比较

关于AD的原理图,本来还想说一下他的自动元件编号的特点,算了。

转载一个AD和PADS对比的帖子,个人水平(尤其画板水平)有限,只为提供一个视角,不代表个人观点。

一、原理图部分1、库⑴ DxDesigner 的原理图库与PCB的库是相互独立的,而且每个原理图符号库都是一个文件,很难实现统一管理;AD可以使用集成库来统一管理,不仅是原理图符号库与PCB封装库,还能把混合电路仿真库、信号完整性分析模型库以及3D模型库一起实现统一管理。

⑵ DxDesigner 在建库时有建立向导,可以引导使用者迅速建立元器件符号库,在向导中可以从Office文档中拷贝器件的Database,从而一次性完成管脚的输入;AD虽然没有向导功能,但是可以使用smart grid paste/insert功能可以达到同样的效果。

⑶ DxDesigner在做Fracture符号库时必须添加关联属性,而且在调用时选择不方便,尤其在放到原理图上以后不方便换,AD在做Fracture符号库很方便只要选择Add part就可,而且符号库放到原理图上以后非常方便更换。

⑷ DxDesigner只能实现与ODBC数据库的关联,不能创建真正的数据库,而AD两者都可以。

2、原理图编辑⑴ DxDesigner和AD 都支持层次化原理图设计,但是DxDesigner 不支持多通道设计,在DxDesigner里面必须使用拷贝复制功能来实现多路设计,而AD只需添加Repeat属性即可。

⑵ DxDesigner在设计界面下没有查找功能,只能到数据表格中去查找,查找后批量修改比较麻烦,AD 可以通过find similar 功能灵活实现全局查找,而且修改不同的参数也非常方便。

⑶ AD中有Snippets摘录功能,实现同一项目及不同项目的拷贝复用,DxDesigner同一项目中只能使用简单的复制,不同项目中只能对整张原理图进行复用。

⑷ AD 中支持器件的管脚交换、与FPGA设计的链接(如原理图器件的管脚定义可以直接来源于FPGA器件商的引脚约束文件),DxDesigner必须使用中间工具IO Designer来完成与FPGA器件的引脚约束文件的同步。

原理图封装与PCB封装有何区别?

原理图封装与PCB封装有何区别?课程介绍详解“设计原理图并对应datasheet加载PCB封装”主要涉及的几个问题第一个问题是把如何把原理图库里面的电气符号转到pcb板上的焊盘?第二个问题就是原理图封装与PCB封装有何区别?第三部分是如何从原理图导入到PCB?整个系列的课程流程是这样的:首先,我们需要清楚原理图和PCB封装的定义,然后学习建立元件库,通过老师的分步演示认识不同元件的封装已经摆放技巧,最后学习电路的连线,完成PCB的封装。

我们在整个课程中,不仅仅是一个学习设计原理图并对应datasheet加载PCB封装的过程。

我们同样注重如何通过分解电路思考来完成课题研究,案达到实验目的,一个系统的学习方式能梳理出每个设计学习的重点难点,这对于每个进行电路设计的学习者都是十分受用的。

学习获得:通过这个课程你可以:掌握优化设计原理图的方法;快速高效学会把原理图对应datasheet加载PCB封装;了解PCB封装的技巧;提升技术,升职加薪。

适宜学习人群:1、对电路设计感兴趣的同学(含电子信息类的大学生,工程研发技术人员,电子爱好者等);2、只会设计电路但对原理却感觉模糊的同学;3、工作中需要用到电路控制相关知识的人群;4、希望提升技术水平,获得更高薪水的工程师。

专栏课程27个课时(点击教程即可观看)如何从彩扩机项目的原理入手展开实践设计详细讲解有刷马达如何控制一个学习三极管开关电路的设计教程分享从四个方面,详细讲解三态电路详细讲解三极管的原理和控制的参数如何计算确定从三个部分详细讲解开关尖峰的处理如何设计点两个灯的逻辑电路快速高效了解N型三极管如何作为开关管用P型三极管涉及哪些问题,如何作为开关管用?详细讲解P管的开关控制电路(上)详细讲解P管的开关控制电路(下)温度开关控制电路如何设计如何提高P管的开关速度详细讲解电感的4大特性详细讲解马达控制电路的电流回路详细讲解桥式电路实现马达正反转如何设计一个桥式电路(上)如何优化一个桥式电路(下)优化整个电路设计的原理图(上)优化整个电路设计的原理图(下)各个元器件的参数计算功率计算三极管延时电路的设计和各参数的计算电路器件功率的计算和桥式电路的特点优化设计三极管开关电路的导通速度现场一边设计原理图并对应datasheet一边演示加载PCB封装(上)现场一边设计原理图并对应datasheet一边演示加载PCB封装(下)原理图设计完成,叫你导入到PCB文件。

原理图和PCB变更对比

原理图和PCB更改点核对在新版原理图完成以及新板PCB完成以后,除了检查重点更改的地方,还需要其他非重点关注的网络的变化以及由于“不小心”导致的误更改。

同时为了能够系统的回顾和记录更改点,也非常有必要进行原理图和PCB的更改核对。

以下只针对OrCAD capture 以及Allegro。

一、 OrCAD 16.6原理图核对优点:直观体现原理图中所有的更改点;可根据需要选择要对比的差异点;步骤1. OrCAD Capture CIS 16.6版本软件(低版本无对比功能)步骤2. 打开Tcl/Tk Applications Dashboard窗口选中Compare and merge two Capture designs Launch在Compare and merge two Capture designs 窗口中,导入所需要对比的两份原理图单击Compare后弹出对比界面后,步骤3-2 的Tcl/Tk Applications Dashboard窗口可以关掉步骤3.对比界面,单击箭头处三角号可展开各页的对比情况在页列表,可以选中页(页码前方框打勾),直接弹出所选页原理图对比对比结果1)当页原理图中,不同处自动高亮显示(如下图A435C V2.0)2)当页原理图中,不同处自动高亮显示(如下图A435C V3.0)在页列表,单击展开页,显示当前页有变动的网络及器件• 网络走线位置变动;• 器件属性如值\封装\位置等等变更;• 标识文字,标题栏;如下setting菜单栏可进行不同点颜色设定、过滤不需要对比的选项等二、 基于Allegro PCB Design的PCB修改点核对优点:可直观对比显示不同的网络点;不足:若修改点较多的话,核对的时间较长;且需要返回原理图查看修改点;仅对网表进行核对;步骤1. 打开旧版本PCB导出XML文档步骤2. 在新版本PCB中,打开Design Compare窗口(同步骤1)步骤3. 新版本PCB的Design Compare窗口中导入旧版本PCB的XML文档;步骤4. 导入旧版本PCB的XML文档后界面如下• 左侧一列为当前PCB的网络表,右侧一列为导入的网络表;• Netlist前面的黄色圆圈表示两份PCB有网络连接不一致步骤5. 单击Netlist前面的圆点可以将网络展开;• 黄色圆圈表示新旧版本中该网络连接有不一致的;• 绿色圆圈表示新旧版本中该网络连接一样;• 红色圆圈表示该网络当前PCB有,而所对比的PCB没有;• 继续展开可显示该网络所连接的器件位号及Pin号三、 采用UltraEdit的PCB网表核对优点:直观显示不同网络;不足:有变更的网络中,无法直观区分增删的器件;仅对网表进行核对;步骤1. 打开旧版本PCB导出Net List Report步骤2. 打开新版本PCB导出Net List Report(同步骤1)步骤3.在UltraEdit软件中,打开步骤2-1及步骤2-2导出的.htm文件步骤4.在UltraEdit软件中比较两份.htm文档步骤5. 对比界面• 下图左右两列中红色字体为不同网络的部分;• 单击红圈中的向下键可以看其他不同的网络。

PCB封装图文并解

自从美国Intel公司1971年设计制造出4位微处理器芯片以采,在20多年时间内,CPU从Intel4004,80286,80386,80486发展到Pentium和Pentium4从4位、8位、16位,32位发展到64位。

CPU芯片里集成的晶体管数由2000个跃升到500万个以上。

半导体制造技术的规模由SSI,MSI,LSI,VLSI达到ULSI。

封装的输入/输出(I/0)引脚从几十根,渐增加到几百根,在今后的10年内可能达两千根。

这一切是一个翻天覆地的变化。

所谓元件的封装,是指安装半导体集成电路芯片用的外壳,具有实际的电子元件或集成电路的外型尺寸、管脚排列方式、管脚直径、管脚间距等参数,它是使实际元件引脚与印制电路板上的焊盘保持一致的依据。

它不仅起着安放、固定、密封、保护芯片和增强电热性能的作用,而且还是沟通芯片内部世界与外部电路的桥梁———芯片上的接点用导线连接到封装外壳的引脚上,这些引脚又通过印制板上的导线与其他器件建立连接。

不同的元件可能有相同的封装,相同的元件可能有不同的封装。

所以在设计印制电路板时,不仅要知道元件的名称、型号,还要知道元件的封装。

芯片的元件的封装技术已经历了好几代的变迁,从DIP,OFP,PGA,BGA到CSP, 再到MCM,技术指标一代比一代先进,包括芯片面积与封装面积之比越来越接近于1,适用频率越来越高,耐温性能越来越好,引脚数增多,引脚间距减小,重量减小,可靠性提高,使用更加方便等等。

二、插针式封装和表贴式封装元件的封装分为插针式封装和表面粘贴式(SMT)封装两大类。

插针式封装与表面粘贴式封装相比体积稍大,在印制电路板上所占的面积也大一些,但是元件焊接方式上比较灵活,既可以手工焊接也可以使用设备自动焊接。

表面粘贴封装在印制电路板上所占的空间和面积都比较小,但是手工焊接比较困难,元器件的更换也有一定难度。

1 插针式封装插针式封装元件的PCB封装外观如图1-11所示。

Cadence中Capture向Allegro中导入网表时的常见错误

Cadence中Capture向Allegro中导⼊⽹表时的常见错误⼀、Capture⽣成netlist的时候报错:1.Unable to open c:\Cadence\PSD_14.2\tools\capture\allegro.cfg for reading. Please correct the above error(s) to proceed错误解释:allegro.cfg⽂件找不到或allegro.cfg⽂件不能打开,这个问题的根源是,有可能每台电脑上安装Allegro的的位置不⼀样,allegro.cfg ⽂件找不到是理所当然的。

处理办法:点⽣成netlist,点setup,修改路径为capture\allegro.cfg所在路径,把allegro.cfg⽂件的位置选择你现在安装⽬录的⽂件位置。

2. Spawning... "C:\Cadence\PSD_15.1\tools\capture\pstswp.exe" -pst -d "F:\gcht\CC2430\Projects\mysch.dsn" -n"C:\CADENCE\PSD_15.1\TOOLS\PROJECTS" -c"C:\Cadence\PSD_15.1\tools\capture\allegro.cfg" -v 3 -j"CC2430_DEMO"#1 Error [ALG0012] Property "PCB Footprint" missing from instance U3: SCHEMATIC1, PAGE1 (2.00, 2.10).#2 Error [ALG0012] Property "PCB Footprint" missing from instance C2: SCHEMATIC1, PAGE1 (2.30, 0.30).#17 Aborting Netlisting... Please correct the above errors and retry.错误解释:Error [ALG0012] Property "PCB Footprint" missing from part : , ( ,A PCB Footprint (JEDEC_TYPE in Allegro) is required for all parts in Allegro. Therefore all parts without this property are listed before aborting the netlisting. You can add the PCB Footprint property by selecting the part listed, then choosing Edit Properties from the pop-up menu and placing a value, such as dip14_3, on the part.在Allegro中,每个器件都需要⼀个PCB封装。

pcb元器件最全的封装详细介绍

史上最全的芯片封装介绍芯片封装,简单点来讲就是把Foundry生产出来的集成电路裸片(Die)放到一块起承载作用的基板上,再把管脚引出来,然后固定包装成为一个整体。

它可以起到保护芯片的作用,相当于是芯片的外壳,不仅能固定、密封芯片,还能增强其电热性能。

因此,封装对CPU和其他LSI集成电路而言,非常重要。

封装的类型,大致可以分为DIP双列直插和SMD贴片封装两种。

从结构方面,封装经历了最早期的晶体管TO(如TO-89、TO92)封装发展到了双列直插封装,随后由PHILIP公司开发出了SOP小外型封装,以后逐渐派生出SOJ (J型引脚小外形封装)、TSOP(薄小外形封装)、VSOP(甚小外形封装)、 SSOP (缩小型SOP)、TSSOP(薄的缩小型SOP)及SOT(小外形晶体管)、SOIC(小外形集成电路)等。

从材料介质方面,包括金属、陶瓷、塑料、塑料,很多高强度工作条件需求的电路如军工和宇航级别仍有大量的金属封装。

以下为小编整理的主流封装类型:常见的10大芯片封装类型1、DIP双列直插式封装DIP是指采用双列直插形式封装的集成电路芯片,绝大多数中小规模集成电路(IC)均采用这种封装形式,其引脚数一般不超过100个。

采用DIP封装的IC有两排引脚,需要插入到具有DIP结构的芯片插座上。

当然,也可以直接插在有相同焊孔数和几何排列的电路板上进行焊接。

DIP封装的芯片在从芯片插座上插拔时应特别小心,以免损坏引脚。

DIP封装图DIP封装具有以下特点:1、适合在PCB(印刷电路板)上穿孔焊接,操作方便。

2、芯片面积与封装面积之间的比值较大,故体积也较大。

DIP是最普及的插装型封装,应用范围包括标准逻辑IC,存储器和微机电路等。

2、QFP/ PFP类型封装QFP/PFP封装的芯片引脚之间距离很小,管脚很细,一般大规模或超大型集成电路都采用这种封装形式。

用这种形式封装的芯片必须采用SMD(表面安装设备技术)将芯片与主板焊接起来。

AD(DXP)的PCB封装的区别

1、B GA(ball grid array)球形触点陈列,表面贴装型封装之一。

在印刷基板的背面按陈列方式制作出球形凸点用以代替引脚,在印刷基板的正面装配LSI 芯片,然后用模压树脂或灌封方法进行密封。

也称为凸点陈列载体(PAC)。

引脚可超过200,是多引脚LSI 用的一种封装。

封装本体也可做得比QFP(四侧引脚扁平封装)小。

例如,引脚中心距为1.5mm 的360 引脚 BGA 仅为31mm 见方;而引脚中心距为0.5mm 的304 引脚QFP 为40mm 见方。

而且BGA 不用担心QFP 那样的引脚变形问题。

该封装是美国Motorola 公司开发的,首先在便携式电话等设备中被采用,今后在美国有可能在个人计算机中普及。

最初,BGA 的引脚(凸点)中心距为1.5mm,引脚数为225。

现在也有一些LSI 厂家正在开发500 引脚的BGA。

BGA 的问题是回流焊后的外观检查。

现在尚不清楚是否有效的外观检查方法。

有的认为,由于焊接的中心距较大,连接可以看作是稳定的,只能通过功能检查来处理。

美国Motorola 公司把用模压树脂密封的封装称为OMPAC,而把灌封方法密封的封装称为GPAC(见OMPAC 和GPAC)。

2、BQFP(quad flat package with bumper)带缓冲垫的四侧引脚扁平封装。

QFP 封装之一,在封装本体的四个角设置突起(缓冲垫) 以防止在运送过程中引脚发生弯曲变形。

美国半导体厂家主要在微处理器和ASIC 等电路中采用此封装。

引脚中心距0.635mm,引脚数从84 到196 左右(见QFP)。

3、碰焊PGA(butt joint pin grid array)表面贴装型PGA 的别称(见表面贴装型PGA)。

4、C-(ceramic)表示陶瓷封装的记号。

例如,CDIP 表示的是陶瓷DIP。

是在实际中经常使用的记号。

5、Cerdip用玻璃密封的陶瓷双列直插式封装,用于ECL RAM,DSP(数字信号处理器)等电路。

CADENCE原理图与PCB设计说明

内部资料请勿外传CADENCE原理图与PCB设计说明(第1版)目录序言 (1)第一章系统简介 (2)1.1系统组成 (2)1.1.1库 (2)1.1.2原理图输入 (2)1.1.3设计转换和修改管理 (2)1.1.4物理设计与加工数据的生成 (3)1.1.5高速PCB规划设计环境 (3)1.2Cadence设计流程 (3)第二章Cadence安装 (4)2.1安装步骤 (4)2.2 LICENSE设置 (7)2.3 库映射 (7)2.4 修改cds.lib文件,设置原理图库: (8)2.5 编辑ENV文件,设置PCB库: (9)第三章CADENCE库管理 (11)3.1 中兴EDA库管理系统 (11)3.2 CADENCE库结构 (13)3.2.1 原理图(Concept HDL)库结构: (13)3.2.2 PCB库结构: (13)第四章项目管理器 (15)4.1 项目管理的概念 (15)4.2 创建或打开一个项目 (15)4.3 原理图库的添加: (16)4.4 填写设计(Design)名称 (17)4.5 增加新的Design(设计) (18)4.6 项目的目录结构 (18)第五章原理图设计 (20)5.1 图纸版面设置 (20)5.1.1 图纸统一格式设置 (20)5.1.2 栅格设置 (22)5.2Concept-HDL的启动 (23)5.3添加元件 (24)5.3.1 逻辑方式添加器件 (24)5.3.2 物理方式添加器件 (25)5.4画线 (26)5.4.1Draw方式 (26)5.4.2Route方式 (27)5.5 添加信号名 (27)5.6 画总线 (28)5.7 信号名命名规则 (29)5.8 元件位号 (31)5.8.1元件位号手工标注 (31)5.8.2元件位号的自动标注 (32)5.8.3 元件位号的自动排序 (33)5.9 Cadence属性 (34)5.10 组操作 (36)5.10.1 组定义: (36)5.10.2 组命名 (36)5.10.3 组操作 (37)5.11 常用命令 (38)5.11.1 常用的快捷键 (38)5.11.2 检查连接关系 (39)5.11.3 点画命令 (39)5.11.4 查找元件和网络 (39)5.11.5两个不同网络名的网络连接的方法 (40)5.11.6 错误检查 (40)5.11.7 检查Cadence原理图单个网络名 (40)5.11.8 对隐藏了电源和地腿的器件定义电源和地信号 (41)5.12 增加新的原理图页 (41)5.13 原理图多页面操作 (42)5.14 信号的页区位置交叉标注(Cross Reference) (42)5.14.1 信号的页区位置交叉标注(Cross Reference)的作用 (42)5.14.2 交叉标注需注意的几点: (43)5.14.3 信号的交叉标注(Cross Refrence)的方法 (43)5.14.4 层次设计中出模块信号的交叉标注 (43)5.14.5 出页信号的交叉标注的要求 (44)5.15 在不同的project下实现原理图拷贝 (44)5.16 打印图纸 (47)5.17 自动生成料单 (48)5.18 原理图归档 (50)5.19 原理图评审 (51)第六章从原理图到PCB (52)6.1从原理图到PCB的实现 (52)6.1.1 原理图到PCB的转换过程: (52)第七章PCB设计 (55)7.1 导入数据 (55)7.2 Allegro用户界面 (55)7.2.1 控制面板的作用 (56)7.2.2工具栏的显示 (57)7.3 Layout准备 (58)7.3.1 创建PCB图的物理外形 (58)7.3.1.2 在Allegro界面下创建板外框: (61)7.3.2 设置板图尺寸参数 (62)7.3.3 设置版图的栅格值: (63)7.3.4 设置板图选项 (63)7.3.5 设置PCB板的叠层 (64)7.3.6 设置约束条件 (65)7.3.6.1 设置板的缺省间距: (65)7.3.6.2 设置扩展的距离规则 (66)7.3.6.3 设置扩展的物理规则 (69)7.3.6.4编辑属性 (69)7.3.7 可视性和颜色设置 (70)7.4 PCB布局 (70)7.5 PCB布线: (73)7.6 添加过孔和替换过孔 (74)7.6.1 添加过孔 (74)7.6.2 替换过孔 (75)7.7 优化走线 (76)7.8 覆铜处理 (77)7.8.1 阴版覆铜 (77)7.8.2 阳版覆铜 (78)7.9 分割电源平面 (80)7.10 位号标注 (83)7.11 加测试点 (83)7.12 DRC检查 (83)7.13 生成报告文件 (84)7.14 V ALOR检查 (85)7.15 生成光绘文件和钻孔文件 (85)7.15.1 生成光圈文件(art-aper.txt),即D码表 (85)7.15.2 生成钻孔文件 (86)7.15.3 生成光绘文件 (86)7.15.3.1 在Artwork中加入所需的层 (86)7.15.3.2 生成光绘文件 (90)7.16 PCB评审 (93)第八章公司的PCB设计规范 (94)序言Cadence软件是我们公司统一使用的原理图设计、PCB设计、高速仿真的EDA工具。

AD_PROTEL99SE的原理图用AD设计PCB需要生成网表文件来做

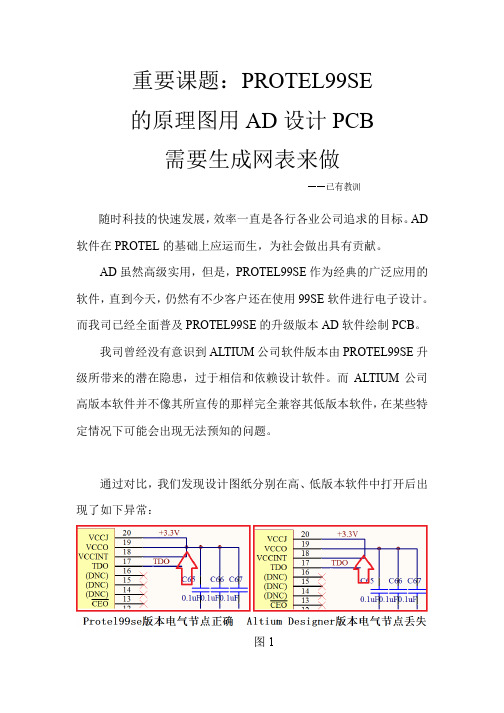

重要课题:PROTEL99SE的原理图用AD设计PCB需要生成网表来做——已有教训随时科技的快速发展,效率一直是各行各业公司追求的目标。

AD 软件在PROTEL的基础上应运而生,为社会做出具有贡献。

AD虽然高级实用,但是,PROTEL99SE作为经典的广泛应用的软件,直到今天,仍然有不少客户还在使用99SE软件进行电子设计。

而我司已经全面普及PROTEL99SE的升级版本AD软件绘制PCB。

我司曾经没有意识到ALTIUM公司软件版本由PROTEL99SE升级所带来的潜在隐患,过于相信和依赖设计软件。

而ALTIUM公司高版本软件并不像其所宣传的那样完全兼容其低版本软件,在某些特定情况下可能会出现无法预知的问题。

通过对比,我们发现设计图纸分别在高、低版本软件中打开后出现了如下异常:图1如上图图1所示:采用高版本软件打开底版本原理图时,出现不可预知的错误——电气节点丢失,从而导致“开路”现象。

结论是:PROTEL及其升级版本软件AD之间存在无法预知的兼容性问题。

措施:1、使用PROTEL软件打开同级版本的文件(原理图),生成相应的网表文件;再导出该网表文件到AD中进行PCB设计。

2、设计完成后,依然用正确的网表文件进行“PCB——网表”对比,以确认连接的正确性。

PCB—网表对比的具体方法如下:第一步:生成网表文件。

首先要向客户确认是否是PROTEL99版本的原理图。

如果是PROTEL99版本的原理图,则向客户要求提供最新的DDB文件。

用“Protel 99 SE”打开DDB工程文件,并打开DDB中所有的99SE原理图文件。

注意是打开所有原理图文件。

在行网络表的生成菜单(在其中一张SCH界面):Design—Create Netlist…执行上述菜单后出现下图。

图1.0 Design—Create Netlist…菜单网表文件输出格式选择Protel格式。

网络标号(标识符)来源一般选择默认的Net Labels and Ports G lobal(具体区别有待进一步研究)。

Altium与Cadence比较

一体化

可以实现原理图-PCB-FPGA三者的完全同步,根据实际项目情况和使用习惯轻松调用各种FPGA厂商工具来完成设计。

需要和FPGA厂商密切配合,提高Incisive与FPGA厂商设计的集成性。

验证平台

可重新配置的硬件平台NanoBoard是业界第一块基于FPGA的、支持LiveDesign开发模式的开发板,它能够无风险地进行芯片级系统集成、软硬件并行设计和调试。同时还支持和客户的产品及预研发的目标板进行协同调试,有效缩短客户的调试时间。

Cadence还有约束管理系统,用于电气约束,管理和分析

兼容性

支持和其他主流PCB格式的导入和导出

allegro能导入很多其它不同pcb图纸格式,但却不能导出

FPGA工具

Altium Designer

Incisive

特性

一个全面的、独立于FPGA供应商的电子设计解决方案

致力于验证

适用群体

电子产品设计厂商

完整性分析(SI)

布线前、布线后信号完整性分析工具,它基于成熟的传输线计算方法,以及I/O缓冲宏模型(IBIS)进行仿真,使用完全可靠的算法,可以获得准确的仿真结果。它有助于高速、高密度板的设计验证。

Cadence电路板SI包括七个主要的组件:模型完整性、SigXplorer拓

扑探索环境、SigNoise模拟子系

·通用调试板。可解决复杂FPGA系统的仿真速度问题,实时验证的通用调试板无需制作专用测试板,省时省力省钱;

·LiveDesign的设计理念。通用调试板和虚拟仪器构成个人电子实验室,设计+实时验证的方式大大提高了效率和可靠性。对于嵌入式系统,真正的软、硬件的协同设计、调试更是工程师梦寐以求的目标。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

原理图与PCB的封装和网表的比较

1.打开原理图,在原理图的任何一页点击鼠标右键并点击Creat netlist,如下图:

2.在net creation中选择参数,在Preferences中的Output Format中选择“PADS ASCII”,Net Identiffer Scope中选择“Net Labels and Ports Global”,Sheets to Netlist中选择“Active project”,其余均不用设置,然后点击“OK”,如下图所示:

3.原理图会生成.PRT(器件封装)和.NET文档,并把这两个文档导出原理图并保存,如下图所示:

4.用UltraEdit工具把.PRT(器件封装)和.NET文档同时打开,并把.NET删去首行和.PRT删去尾行并保存,再把.NET所有文字拷贝,并粘贴到.PRT文档的下面,如下图:

5.并把当前的.PRT文档另存为.asc文档,如下图:

6.打开PADS Layout工具,并导入.asc文档,如下图所示:

7.在PADS Layout的主菜单Tools中点击Compare/ECO Tools,进行参数设置,如下图所示:

8.执行“RUN”命令,运行完毕后弹出Process Status命令框,点击“Show Report”就能看到原理图和PCB封装和网表不同的地方,如下图所示:

9.把生成的Layout.rep发给负责的PCB Layout工程师,以达到网表和封装高度一致。