半导体工艺技术薄膜淀积 PPT

合集下载

半导体制造技术—第四讲:淀积工艺

化学淀积工艺可以应用于半导体制造中的各 种薄膜制备如氧化物、氮化物、金属等

提供反应物质:反应气体是淀积过程中形成薄膜的主要物质来源 控制反应速率:反应气体的浓度和流量可以控制反应速率从而影响薄膜的厚度和质量 影响薄膜性质:反应气体的种类和比例可以影响薄膜的性质如导电性、光学性能等 参与化学反应:反应气体在淀积过程中参与化学反应形成所需的薄膜材料

半导体制造技术之淀 积工艺

汇报人:

目录

添加目录标题

淀积工艺概述

淀积工艺的原理

淀积工艺的应用

淀积工艺的优缺点

淀积工艺的未来展 望

添加章节标题

淀积工艺概述

淀积工艺是半导体制造过程中的关键步骤之一 主要目的是在硅晶圆上沉积一层或多层薄膜 薄膜可以是金属、氧化物、氮化物等 淀积工艺包括化学气相淀积(CVD)、物理气相淀积(PVD)等方法

研究方向:新型材料、新工艺、新设备 技术挑战:提高性能、降低成本、提高可靠性 研发目标:实现更高性能、更低成本、更可靠的淀积工艺 研发成果:新型材料、新工艺、新设备的研发和应用

太阳能电池:利用淀积工艺制造高效太阳能电池提高光电转换效率 燃料电池:利用淀积工艺制造高性能燃料电池提高能源转换效率 储能设备:利用淀积工艺制造高性能储能设备提高储能效率和稳定性 电动汽车:利用淀积工艺制造高性能电动汽车电池提高续航里程和充电速度

物理淀积的优 点是沉积速度 快沉积层厚度 均匀沉积层质

量高

化学淀积是一种通过化学反应在半导体 表面形成薄膜的过程

化学淀积可以分为气相化学淀积和液相 化学淀积两种类型

气相化学淀积是通过化学反应在半导体 表面形成薄膜的过程

液相化学淀积是通过化学反应在半导体 表面形成薄膜的过程

化学淀积工艺可以应用于半导体制造中的各 种薄膜制备如氧化物、氮化物、金属等

提供反应物质:反应气体是淀积过程中形成薄膜的主要物质来源 控制反应速率:反应气体的浓度和流量可以控制反应速率从而影响薄膜的厚度和质量 影响薄膜性质:反应气体的种类和比例可以影响薄膜的性质如导电性、光学性能等 参与化学反应:反应气体在淀积过程中参与化学反应形成所需的薄膜材料

半导体制造技术之淀 积工艺

汇报人:

目录

添加目录标题

淀积工艺概述

淀积工艺的原理

淀积工艺的应用

淀积工艺的优缺点

淀积工艺的未来展 望

添加章节标题

淀积工艺概述

淀积工艺是半导体制造过程中的关键步骤之一 主要目的是在硅晶圆上沉积一层或多层薄膜 薄膜可以是金属、氧化物、氮化物等 淀积工艺包括化学气相淀积(CVD)、物理气相淀积(PVD)等方法

研究方向:新型材料、新工艺、新设备 技术挑战:提高性能、降低成本、提高可靠性 研发目标:实现更高性能、更低成本、更可靠的淀积工艺 研发成果:新型材料、新工艺、新设备的研发和应用

太阳能电池:利用淀积工艺制造高效太阳能电池提高光电转换效率 燃料电池:利用淀积工艺制造高性能燃料电池提高能源转换效率 储能设备:利用淀积工艺制造高性能储能设备提高储能效率和稳定性 电动汽车:利用淀积工艺制造高性能电动汽车电池提高续航里程和充电速度

物理淀积的优 点是沉积速度 快沉积层厚度 均匀沉积层质

量高

化学淀积是一种通过化学反应在半导体 表面形成薄膜的过程

化学淀积可以分为气相化学淀积和液相 化学淀积两种类型

气相化学淀积是通过化学反应在半导体 表面形成薄膜的过程

液相化学淀积是通过化学反应在半导体 表面形成薄膜的过程

化学淀积工艺可以应用于半导体制造中的各 种薄膜制备如氧化物、氮化物、金属等

半导体制造技术—第四讲:淀积工艺

5. 氧化还原反应: 反应3与4地组合,反应后形成两

种新的化合物。

半导体知识人

以上5中基本反应中,有一些特定的 化学气相淀积反应用来在硅片衬底上淀 积膜。对于某种特定反应的选择通常要 考虑淀积温度、膜的特性以及加工中的 问题等因素。 例如,用硅烷和氧气通过氧化反应 淀积 SiO 2 膜。反应生成物 SiO2 淀积在硅 片表面,副产物事是氢。 SiH4 + O2 SiO2 + 2H2

半导体知识人

连续加工的APCVD 反应炉

反应气体 1 惰性分隔气体 膜 反应气体 2 硅片

半导体知识人

ULSI硅片上的多层金属化

钝化层

ILD-6

压点金属

ILD-5 M-4 ILD-4 M-3 ILD-3 M-2 ILD-2 M-1 Via Poly gate LI metal n+ p+ n-well p+ LI oxide STI n+ p-well n+ p+ ILD-1

p- Epitaxial layer

半导体知识人

在更低的反应温度和压力下,由于只有更 少的能量来驱动表面反应,表面反应速度会降 低。最终反应物达到硅片表面的速度将超过表 面化学反应的速度。在这种情况下。淀积速度 是受化学反应速度限制的,此时称表面反应控 制限制。

CVD 气流动力学

CVD气流动力学对淀积出均匀的膜很重要。 所谓气体流动,指的是反应气体输送到硅片表 面的反应区域(见下图)。CVD气体流动的主 要因素包括,反应气体从主气流中到硅片表面 的输送以及在表面的化学反应速度。

第四讲:淀积工艺

半导体知识人

概

述

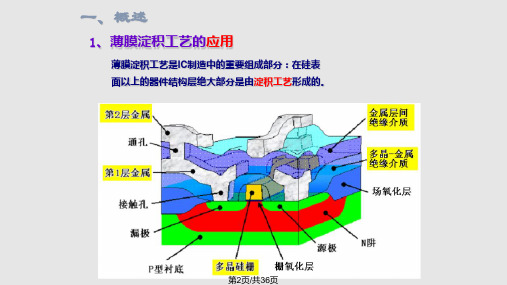

薄膜淀积是芯片加工过程中一个至关重要 的工艺步骤,通过淀积工艺可以在硅片上生长 导各种导电薄膜层和绝缘薄膜层。 各种不同类型的薄膜淀积到硅片上,在某 些情况下,这些薄膜成为器件结构中的一个完 整部分,另外一些薄膜则充当了工艺过程中的 牺牲品,并且在后续的工艺中被去掉。 本章将讨论薄膜淀积的原理、过程和所 需的设备,重点讨论SiO2和Si3N4等绝缘材料薄 膜以及多晶硅的淀积。金属和金属化合物薄膜 的淀积将在第13章中介绍。

半导体工艺技术薄膜淀积

F1 hG (CG C S )

hG 是质量输运系数(cm/sec)

半导体工艺技术

13

F2 ksCS

ks 是表面化学反应系数(cm/sec) 在稳态,两类粒子流密度应相等。这样得到

F F1 F2

可得:

ks CS CG 1 hG

1

第九章 薄膜淀积

设

半导体工艺技术

第九章 薄膜淀积

半导体工艺技术

5

除了CVD和PVD外,制备薄膜的方法还有:

旋涂Spin-on 镀/电镀electroless plating/electroplating

铜互连是由电镀工艺制作

第九章 薄膜淀积

外延硅应用举例

半导体工艺技术

6

外延:在单晶衬底上生长一层新

的单晶层,晶向取决于衬底

第九章 薄膜淀积

解决办法:等离子增强化学气相 淀积 PECVD

第九章 薄膜淀积

半导体工艺技术

30

多晶硅淀积方法

LPCVD,主要用硅烷法,即在600-650 ℃温度下,由硅 烷热分解而制成,总体化学反应(overall reaction) 方程是:SiH4→Si(多晶)+2H2 低于575 ℃所淀积的硅是无定形或非晶硅(amorphous Si); 高于600 ℃淀积的硅是多晶,通常具有柱状结构(column structure); 当非晶经高温(>600 ℃)退火后,会结晶(crystallization); 柱状结构多晶硅经高温退火后,晶粒要长大(grain growth)。

斜率与激活 能Ea成正比

第九章 薄膜淀积

半导体工艺技术

26

低压化学气相淀积 (LPCVD) 在质量输运控制区域:

hG 是质量输运系数(cm/sec)

半导体工艺技术

13

F2 ksCS

ks 是表面化学反应系数(cm/sec) 在稳态,两类粒子流密度应相等。这样得到

F F1 F2

可得:

ks CS CG 1 hG

1

第九章 薄膜淀积

设

半导体工艺技术

第九章 薄膜淀积

半导体工艺技术

5

除了CVD和PVD外,制备薄膜的方法还有:

旋涂Spin-on 镀/电镀electroless plating/electroplating

铜互连是由电镀工艺制作

第九章 薄膜淀积

外延硅应用举例

半导体工艺技术

6

外延:在单晶衬底上生长一层新

的单晶层,晶向取决于衬底

第九章 薄膜淀积

解决办法:等离子增强化学气相 淀积 PECVD

第九章 薄膜淀积

半导体工艺技术

30

多晶硅淀积方法

LPCVD,主要用硅烷法,即在600-650 ℃温度下,由硅 烷热分解而制成,总体化学反应(overall reaction) 方程是:SiH4→Si(多晶)+2H2 低于575 ℃所淀积的硅是无定形或非晶硅(amorphous Si); 高于600 ℃淀积的硅是多晶,通常具有柱状结构(column structure); 当非晶经高温(>600 ℃)退火后,会结晶(crystallization); 柱状结构多晶硅经高温退火后,晶粒要长大(grain growth)。

斜率与激活 能Ea成正比

第九章 薄膜淀积

半导体工艺技术

26

低压化学气相淀积 (LPCVD) 在质量输运控制区域:

《半导体材料制备技术》培训课件:半导体薄膜的生长与淀积

2 、淀积薄膜对衬底的附着力更高,致密性更 好,淀积速率较高。

3、若不能有效控制等离子体中高能带电粒子 对生长表面的轰击,会影响薄膜结构完整性。

光CVD和LCVD:低温又不存在重离子轰击

光CVD方法利用气体分子对特定波长光的强吸 收作用提供反应动力

特点:参与反应和淀积的物质都有很强的选择性, 且淀积温度很低,因而薄膜不仅结构完美,纯度 也很高

V族源

Ⅴ族元素的化合物一般都采用砷烷(AsH3) 、磷烷(PH3) ,两 者均系剧毒气体。因此研究毒性较小的有机砷来代替实属必要。 有机砷化合物的毒性,随分子中含H 原子数目减小而降低,然而 使用毒性最低的TMAs ,将在淀积膜中引入大量C 沾污,因此,含 有2个H原子的叔丁基砷化氢(TBAs) ,被认为是目前较好的AsH3 的取代物;而取代PH3 以叔丁基磷化氢(TBP) 最有希望。

不经过固-液相变或固-气相变,直接或 通过同样也是固体的中间介质向生长界面 输运生长物质的外延生长。

两种可能的形式:一种是固体生长源直接 与生长表面接触;一种是固体生长源与生 长表面之间隔一层由其他固体物质构成的 输运介质。

离子注入的退火

锗核辐射探测器 欧姆接触的制作

非晶体 晶体

非晶体 晶体

器件工艺中主要用来制作金属接触;II-VI族化合 物;氧化物半导体 。

真空蒸发法原理

在任何温度下,材料表面都存在蒸汽,当材料的温 度低于熔化温度时,产生蒸汽的过程称为升华,而 熔化时产生蒸汽的过程称为蒸发。

真空蒸发:真空条件下,加热蒸发源,使原子或分 子从蒸发源表面逸出,形成蒸汽流入射到衬底表面, 凝结成固态薄膜

SiCl4 + 2H2 = Si + 4HCl SiCl4氢还原法的反应温度偏高,该方法并不十分

3、若不能有效控制等离子体中高能带电粒子 对生长表面的轰击,会影响薄膜结构完整性。

光CVD和LCVD:低温又不存在重离子轰击

光CVD方法利用气体分子对特定波长光的强吸 收作用提供反应动力

特点:参与反应和淀积的物质都有很强的选择性, 且淀积温度很低,因而薄膜不仅结构完美,纯度 也很高

V族源

Ⅴ族元素的化合物一般都采用砷烷(AsH3) 、磷烷(PH3) ,两 者均系剧毒气体。因此研究毒性较小的有机砷来代替实属必要。 有机砷化合物的毒性,随分子中含H 原子数目减小而降低,然而 使用毒性最低的TMAs ,将在淀积膜中引入大量C 沾污,因此,含 有2个H原子的叔丁基砷化氢(TBAs) ,被认为是目前较好的AsH3 的取代物;而取代PH3 以叔丁基磷化氢(TBP) 最有希望。

不经过固-液相变或固-气相变,直接或 通过同样也是固体的中间介质向生长界面 输运生长物质的外延生长。

两种可能的形式:一种是固体生长源直接 与生长表面接触;一种是固体生长源与生 长表面之间隔一层由其他固体物质构成的 输运介质。

离子注入的退火

锗核辐射探测器 欧姆接触的制作

非晶体 晶体

非晶体 晶体

器件工艺中主要用来制作金属接触;II-VI族化合 物;氧化物半导体 。

真空蒸发法原理

在任何温度下,材料表面都存在蒸汽,当材料的温 度低于熔化温度时,产生蒸汽的过程称为升华,而 熔化时产生蒸汽的过程称为蒸发。

真空蒸发:真空条件下,加热蒸发源,使原子或分 子从蒸发源表面逸出,形成蒸汽流入射到衬底表面, 凝结成固态薄膜

SiCl4 + 2H2 = Si + 4HCl SiCl4氢还原法的反应温度偏高,该方法并不十分

半导体制造技术11-淀积

本章将讨论薄膜淀积的原理、过程和所需 的设备,重点讨论SiO2和Si3N4等绝缘材料薄膜 以及多晶硅的淀积。

11.1 概述

引言

顶层

垫氧化层

Poly

n+

金属前氧化层 侧墙氧化层

栅氧化层

ILD 场氧化层

n+

p- epi layer

氮化硅

氧化硅

氧化硅 多晶

p+

金属

金属

p+

n-well

p+ silicon substrate

11.2 化学汽相淀积 CVD化学过程

化学气相淀积过程有5种基本的化学反应: 1.高温分解: 通常在无氧的条件下,通过加热化合 物分解(化学键断裂); 2. 光分解: 利用辐射使化合物的化学键断裂分解; 3.还原反应: 反应物分子和氢发生的反应; 4. 氧化反应: 反应物原子或分子和氧发生的反应; 5.氧化还原反应: 反应3与4地组合,反应后形成两 种新的化合物。

均匀厚度

共形台阶覆盖

非共形台阶覆盖

11.1 概述

高的深宽比间隙

可以用深宽比来描述一个小间隙(如槽或孔), 深宽比定义为间隙的深度和宽度的比值(见下图)

深宽比 = 深度 宽度

深宽比 = 500 Å = 2 250 Å 1

D W

500 Å

250 Å

11.1 概述

高的深宽比间隙

Photograph courtesy of Integrated Circuit Engineering

在化学气相淀积中,气体先驱物传输到硅片

表面进行吸附作用和反应。例如,下面的三个反

膜,薄膜淀积是指任何在硅片衬底上物理淀积一 层膜的工艺,属于薄膜制造的一种工艺,所淀积 的薄膜可以是导体、绝缘材料或者半导体材料。 比如二氧化硅(SiO2)、氮化硅(Si3N4)、多 晶硅以及金属(Cu、W).

11.1 概述

引言

顶层

垫氧化层

Poly

n+

金属前氧化层 侧墙氧化层

栅氧化层

ILD 场氧化层

n+

p- epi layer

氮化硅

氧化硅

氧化硅 多晶

p+

金属

金属

p+

n-well

p+ silicon substrate

11.2 化学汽相淀积 CVD化学过程

化学气相淀积过程有5种基本的化学反应: 1.高温分解: 通常在无氧的条件下,通过加热化合 物分解(化学键断裂); 2. 光分解: 利用辐射使化合物的化学键断裂分解; 3.还原反应: 反应物分子和氢发生的反应; 4. 氧化反应: 反应物原子或分子和氧发生的反应; 5.氧化还原反应: 反应3与4地组合,反应后形成两 种新的化合物。

均匀厚度

共形台阶覆盖

非共形台阶覆盖

11.1 概述

高的深宽比间隙

可以用深宽比来描述一个小间隙(如槽或孔), 深宽比定义为间隙的深度和宽度的比值(见下图)

深宽比 = 深度 宽度

深宽比 = 500 Å = 2 250 Å 1

D W

500 Å

250 Å

11.1 概述

高的深宽比间隙

Photograph courtesy of Integrated Circuit Engineering

在化学气相淀积中,气体先驱物传输到硅片

表面进行吸附作用和反应。例如,下面的三个反

膜,薄膜淀积是指任何在硅片衬底上物理淀积一 层膜的工艺,属于薄膜制造的一种工艺,所淀积 的薄膜可以是导体、绝缘材料或者半导体材料。 比如二氧化硅(SiO2)、氮化硅(Si3N4)、多 晶硅以及金属(Cu、W).

薄膜淀积工艺上.pptx

吸附过程

a 代表被吸附的物质

表面总反应

■ 吸附在硅表面的H2被解吸附,留下

空位,使反应可继续进行。

■

被吸附的SiH2在硅片表面扩散,直

到找到空位成键。

■

表面扩散长度长时,淀积均匀;表

面扩散长度短时,淀积不均匀。

温度上升,扩散长度提高

淀积均匀性提高

图13.3 Si CVD过程中硅片表面模型

第22页/共36页

对于高纯净环境,采用干泵以避免油蒸汽污染。

(2)

高真空泵:

抽吸腐蚀性和有毒气体,或大容量气体时,采用动量转移

型泵,如扩散泵和涡轮分子泵;

抽吸小容量气体,或需要超高洁净度时,采用气体吸附型泵,

如冷泵(低温泵)等。

7、真空密封:O形圈(低中真空)、金属法兰(高真空)

8、气压测量:电容压力计、热传导规表(低中真空)、离子

体材料的淀积,如二氧化硅、多晶硅、氮化硅等。

(2) 物理气相淀积(Physical Vapor Deposition):利用物理

机制制备所需薄膜材料,常用于金属薄膜的制备淀积,

如铝、钨、钛等。

(3) 其他的淀积技术还包括:旋转涂布法、电解电镀法等

SOG(Spin on Glass)

第3页/共36页

金属Cu的淀积

(7) 副产物离开反应器的输运

1、反应腔内的气体流动

最慢的步骤决定了淀积薄膜的速率

第23页/共36页

2、反应腔内的化学反应

4、反应腔内的化学反应:

化学平衡与质量作用定律

(1) 假设:在小的体积元内温度和气体化学组分是均匀的,

且只进行一种反应,如:

(2) 化学平衡时,每种物质的浓度维持固定不变

a 代表被吸附的物质

表面总反应

■ 吸附在硅表面的H2被解吸附,留下

空位,使反应可继续进行。

■

被吸附的SiH2在硅片表面扩散,直

到找到空位成键。

■

表面扩散长度长时,淀积均匀;表

面扩散长度短时,淀积不均匀。

温度上升,扩散长度提高

淀积均匀性提高

图13.3 Si CVD过程中硅片表面模型

第22页/共36页

对于高纯净环境,采用干泵以避免油蒸汽污染。

(2)

高真空泵:

抽吸腐蚀性和有毒气体,或大容量气体时,采用动量转移

型泵,如扩散泵和涡轮分子泵;

抽吸小容量气体,或需要超高洁净度时,采用气体吸附型泵,

如冷泵(低温泵)等。

7、真空密封:O形圈(低中真空)、金属法兰(高真空)

8、气压测量:电容压力计、热传导规表(低中真空)、离子

体材料的淀积,如二氧化硅、多晶硅、氮化硅等。

(2) 物理气相淀积(Physical Vapor Deposition):利用物理

机制制备所需薄膜材料,常用于金属薄膜的制备淀积,

如铝、钨、钛等。

(3) 其他的淀积技术还包括:旋转涂布法、电解电镀法等

SOG(Spin on Glass)

第3页/共36页

金属Cu的淀积

(7) 副产物离开反应器的输运

1、反应腔内的气体流动

最慢的步骤决定了淀积薄膜的速率

第23页/共36页

2、反应腔内的化学反应

4、反应腔内的化学反应:

化学平衡与质量作用定律

(1) 假设:在小的体积元内温度和气体化学组分是均匀的,

且只进行一种反应,如:

(2) 化学平衡时,每种物质的浓度维持固定不变

第四章半导体器件工艺学之淀积

一、薄膜特性(质量参数要求)

高密度:连续的 不含孔隙 厚度一致(均匀性) 对台阶的覆盖好 高的深宽比间隙填充能力 高纯度 合适的化学剂量 低的膜应力 对下层材料的粘附性

台阶覆盖

间隙填充能力

用深宽比来描述一个间隙(孔或槽) 深宽比=深/宽 高的深宽比典型值一般为3 有时是5或更大 一般膜淀积时槽的底部和边缘比较薄

类似于真空蒸发淀积,是用来淀积外延层 可达到原子分辨率的一种方法 MBE系统提供电磁场使硅原子蒸发,这些 硅原子束离开硅源,流动通过腔体,淀积 在单晶硅片上 特点:低温,减少了自掺杂和外扩散 生长速度慢 膜形成易控制,可实现单层增量控制 产率低,花费高

§4-4金属化与平坦化

什么是金属化 基本概念: 互连 接触 通孔 栓塞

常压CVD(APCVD) 低压CVD(LPCVD) 等离子体辅助CVD(PECVD)

1.常压CVD(APCVD)

属于质量传输限制:反应速度可以保证 反应气体的量不充足 特点: 淀积速度快 台阶覆盖能力差 气体消耗量大 低产出率 应用:淀积SiO2和掺杂的氧化硅,用于层间 绝缘、保护性覆盖物、表面平坦化等功能 的

金属热蒸发台

真空蒸发法结构示意图

电子束蒸发法结构示意图

溅射

高能粒子撞击靶,撞击出原子,沉积在基 片上,形成薄膜 特点: 可在大晶圆上控制淀积均匀的薄膜 膜厚均匀,台阶覆盖能力好 保持复杂合金原组分 能淀积高熔点和难溶金属 能够在淀积金属前清除硅片表面沾污和本 身的氧化层(原位溅射)

溅射机制

3.等离子体辅助CVD(PECVD)

在LPCVD基础上,加高频电场,使反应气 体电离成等离子体,发生反应,沉积成膜 特点:低压,可与LPCVD比拟 低温 快速淀积 好的台阶覆盖能力 要求RF系统 成本高 应用:淀积热稳定性差的材料

第四讲:淀积工艺(半导体制造技术)

电信学院微电子教研室

• 速度限制阶段

在实际大批量生产中,CVD反应的时间长 短很重要。温度升高会促使表面反应速度增加 。基于CVD反应的有序性,最慢的反应阶段会 成为整个工艺的瓶颈。换言之,反应速度最慢 的阶段将决定整个淀积过程的速度。 CVD的反应速度取决于质量传输和表面反 应两个因素。在质量传输阶段淀积工艺对温度 不敏感,这意味着无论温度如何,传输到硅片 表面加速反应的反应气体的量都不足。在此情 况下,CVD工艺通常是受质量传输所限制的。

电信学院微电子教研室

薄膜淀积

半导体器件工艺中的“薄膜”是一种固态薄 膜,薄膜的种类和制备方法在第四章中已作过简 单介绍。 薄膜淀积是指任何在硅片衬底上物理淀积一 层膜的工艺,属于薄膜制造的一种工艺,所淀积 的薄膜可以是导体、绝缘材料或者半导体材料。 比如二氧化硅(SiO2 )、氮化硅(Si3N4 )、多 晶硅以及金属(Cu、W).

物理工艺 电镀

电化学淀积 (ECD), 通常指电镀 化学镀层

物理气相淀积 (PVD)或溅射

直流二极管

蒸发

旋涂方法

旋涂玻璃 s (SOG) 旋涂绝缘介 质(SOD)

灯丝和电子束

射频 (RF)

分子束外延 (MBE)

直流磁电管

离子化金属等离子 体 (IMP)

半导体制造技术 by Michael Quirk and Julian Serda

半导体制造技术 by Michael Quirk and Julian Serda

电信学院微电子教研室

CVD 传输和反应步骤图

1) 反应物的质 量传输 气体传送

CVD 反应室

2) 薄膜先驱 物反应 3) 气体分 子扩散 4) 先驱物 的吸附

7) 副产物的解 吸附作用 副产物

《薄膜物理淀积技术》PPT课件

Target

Substrat e

Gas pane l

Chuc k

Turbo pump

RF generator

Microcontroller operator interfa

ce

Pressure controller

Exhaust

Argon

Roughing pump

• 射频溅射: 解决绝缘靶材料上的电荷堆积问题和合金材料的组分问题

第九章:薄膜物理淀积技术

Metal Layers in a Chip

Multilevel Metallization on a ULSI

Wafer

Passivation layer ILD-6

Bonding pad metal

ILD-5 M-4

ILD-4 M-3

ILD-3

M-2

ILD-2

M-1 Via

2. Titanium depositio

Titanium-silicon

n

reaction regions

TiSi2 for mation

3. Rapid thermal anneal treat ment

4. Titanium strip

Chip Performance Issues Related to a Salic ide Structure

• 9.4. 器件中的金属膜 作用: 、连线、肖特基接触

在器件中的 —欧姆电极

9.4.1.欧姆接触与肖特基接触(半导体物理)

1、金属功函数与半导体亲合能对金—半接触时的界面空间电荷区的影响 阻挡层和反阻挡层的形成

2、界面态的影响

?

费米能级钉扎

3、隧穿效应

半导体工艺-薄膜淀积

SiCl4浓度不能太高,否则反而侵蚀Si(图)

SiCl4 (vapor) + Si (solid)

2SiCl2 (vapor)

掺杂剂的反应:

AsH3 (vapor)

As (solid) + 3/2H2 (vapor)

15

Si外延薄膜CVD生长过程 SiCl4

吸附 反应或分解

表面迁移到突出位置,合并进生长层

18

1.3、外延层缺陷

从衬底来的缺陷:高质量衬底,无位错 从界面来的缺陷:界面污染物,清洗表面 沉淀或位错环:局部过饱和掺杂杂质或其他杂质 小角晶界或孪晶:不当方位外延薄膜相遇结合 线位错:晶格不匹配异质外延,形变由位错来弛豫

19

1.3、外延层缺陷

同质外延:严格的晶格匹配外延工艺,如Si/Si 异质外延:晶格匹配外延和形变层外延,如 AlxGa1-xAs/GaAs, GexSi1-x/Si

外延薄膜在真空环境中生长,杂质污染较小,无机械损伤; 灵活控制不同区域掺杂浓度,改善半导体器件性能。

外 延 生 长 工 艺 : 化 学 气 相 沉 积 ( CVD ) 和 分 子 束 外 延 (MBE)。

7

1.1、化学气相沉积(CVD)

化学气相沉积(Chemical Vapor Deposition, CVD)

氧化层

Si

气流层

C

C0

扩散通量F1

SiO2

Si

x C0为氧化层表面处氧化剂浓度

Ci为Si-SiO2界面处氧化剂浓度

20

晶格匹配外延

外延---晶格匹形配变层外延

同质外延:严格的晶格匹配外延工艺 异质外延:晶格匹配外延和形变层外延

21

异质外延:晶格匹配外延和形变层外延

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

单晶硅外延要采用图中的卧式反应设备, 放置硅片的石墨舟为什么要有倾斜?

这里界面层厚度s是x方向平板长度的函数。

为气体粘度

hG

DG s

为气体密度

U为气体速度

s (x)

x U

随着x的增加,s(x)增加,hG下降。如果淀

积受质量传输控制,则淀积速度会下降

沿支座方向反应气体浓度的减少, 同样导致 淀积速度会下降

一种或数种物质的气体,以某种方式激活后,在衬底表面发生

两 化学反应,并淀积出所需固体薄膜的生长技术。

类 主

Hale Waihona Puke 例如:APCVD, LPCVD, PECVD, HDPCVD

要 的 淀 积

2)物理气相淀积 — Physical Vapor Deposition (PVD) 利用某种物理过程实现物质的转移,即将原子或分子转移到衬 底(硅)表面上,并淀积成薄膜的技术。

因此,支座倾斜可以促使s(x)沿x变化减小

原理:由于支座倾斜后,气流的流过的截面积

下降,导致气流速度的增加,进而导致s(x)沿x

减小和hG的增加。从而用加大hG的方法来补偿 沿支座长度方向的气源的耗尽而产生的淀积速

率的下降。尤其对质量传输控制的淀积至关重 要,如APCVD法外延硅。

外延单晶硅的化学反应式

方 例如:蒸发 evaporation,溅射sputtering

式

除了CVD和PVD外,制备薄膜的方法还有:

✓旋涂Spin-on

✓镀/电镀electroless plating/electroplating

铜互连是由电镀工艺制作

外延硅应用举例

外延:在单晶衬底上生长一层新

的单晶层,晶向取决于衬底

多晶硅薄膜的应用

(3)化学反应生成的固态物质, 即所需要的淀积物,在硅片表 面成核、生长成薄膜 (4)反应后的气相副产物,离 开衬底表面,扩散回边界层,

化学气相淀积的基本过程

生长动力学

从简单的生长模型出发,用 动力学方法研究化学气相淀 积推导出生长速率的表达式 及其两种极限情况

与热氧化生长稍有 不同的是,没有了 在SiO2中的扩散流

F1是反应剂分子的粒子流密度 F2代表在衬底表面化学反应消耗的反应剂分子流密度

F 1hG (C GC S)

hG 是质量输运系数(cm/sec)

F2 ksCS

ks 是表面化学反应系数(cm/sec) 在稳态,两类粒子流密度应相等。这样得到

FF1F2

可得:

CS

CG1

ks hG

1

设

Y CG CT

这里 Y 为在气体中反应剂分子的摩尔比值, CG为每cm3中反应剂分子数,这里CT为在 气体中每cm3的所有分子总数

✓ 半导体、介质、金属薄膜

✓ 常压化学气相淀积(APCVD),低压CVD (LPCVD),等离子体增强淀积(PECVD)等

CVD反应必须满足三个挥发性标准

✓ 在淀积温度下,反应剂必须具备足够高的蒸汽压 ✓ 除淀积物质外,反应产物必须是挥发性的 ✓ 淀积物本身必须具有足够低的蒸气压

(1)反应剂被携带气体引入反应器 后,在衬底表面附近形成“滞留 层”,然后,在主气流中的反应剂 越过边界层扩散到硅片表面 (2)反应剂被吸附在硅片表面,并 进行化学反应

SiCl 4 H 2 SiHCl 3 HCl SiHCl 3 H 2 SiH 2Cl 2 HCl SiHCl 3 SiCl 2 HCl SiH 2Cl 2 SiCl 2 H 2 SiH 2Cl 2 Si 2 HCl SiCl 2 H 2 Si HCl

半导体工艺技术薄膜淀积

在集成电路制 备中,很多薄 膜材料由淀积 工艺形成

Deposition

✓半导体薄膜:Si

✓介质薄膜:SiO2,Si3N4, BPSG,… ✓金属薄膜:Al,Cu,W,Ti,…

单晶薄膜:Si, SiGe(外延) 多晶薄膜:poly-Si

1)化学气相淀积 — Chemical Vapor Deposition (CVD)

CMOS栅电极材料;多层金属化电极的导电材料

大家应该也有点累了,稍作休息

大家有疑问的,可以询问和交

Chemical Vapor Deposition (CVD)

Epitaxy Substrate

Single crystal (epitaxy)

Courtesy Johan Pejnefors, 2001

Polycrystalline

对薄膜的要求

1. 组分正确,玷污少,电学和机械性能好 2. 片内及片间(每一硅片和硅片之间)均匀性好 3. 台阶覆盖性好(conformal coverage — 保角覆盖) 4. 填充性好 5. 平整性好

化学气相淀积(CVD)

✓ 单晶 (外延)、多晶、非晶(无定型)薄膜

T对ks的影响较hG 大许多,因此:

hG≈constant

斜率与激活能 Ea成正比

✓ hG<<ks质量传 输控制过程出现 在高温

✓hG>>ks表面控制 过程在较低温度 出现

硅外延:Ea=1.6 eV

以硅外延为例(1 atm,APCVD)

hG 常数

外延硅淀积往往是 在高温下进行,以 确保所有硅原子淀 积时排列整齐,形 成单晶层。为质量 输运控制过程。此 时对温度控制要求 不是很高,但是对 气流要求高。

Ea 值相同

多晶硅生长是在低 温进行,是表面反 应控制,对温度要 求控制精度高。

当工作在高温区,质量控制为主导,hG是常数, 此时反应气体通过边界层的扩散很重要,即反 应腔的设计和晶片如何放置显得很重要。

记住关键两点:

✓ks 控制的淀积 主要和温度有关 ✓hG 控制的淀积 主要和反应腔体几何形状有关

Y一定时, v 由hG和ks中较小者决定

1、如果hG>>ks,则Cs≈CG,这种情况为表面反应控制过程

有

v

CT N

ksY

ks

k0

expEa kT

表面(反应)控制,对温度 特别敏感

2、如果hG<<ks,则CS≈0,这是质量传输控制过程

有

v

CT N

hGY

质量输运控制,对温度不敏感

生长速率和温度的关系

YC GP G

P G

C T P TotaP lGP G 1P G 2....

PG 是反应剂分子的分压,PG1, PG1 PG2 PG3…..等是系统中其它气体的分压

则生长速率 vFkshG C GkshG C TY N kshGN kshGN

N是形成薄膜的单位体积中的原子数。对硅外延N为5×1022 cm-3