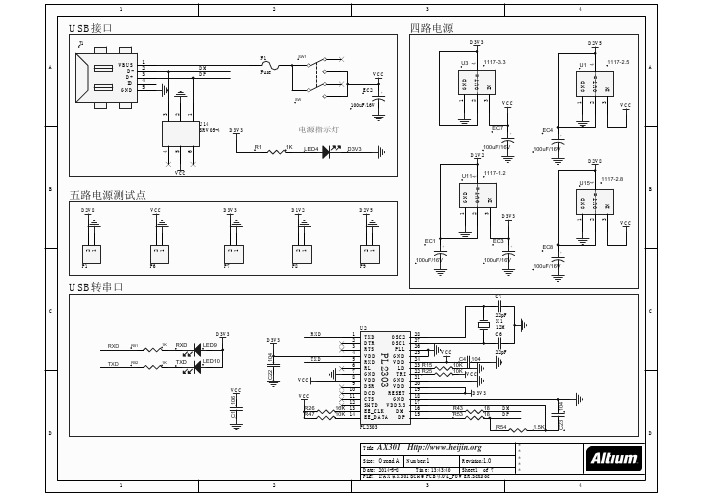

Altium公司的FPGA开发板的原理图

EDA第2章FPGACPLD结构原理

2.4 FPGA的结构及其工作原理

2.4.2 Cyclone III系列器件的结构与原理

2.5 硬件测试

2.5.1 内部逻辑测试 2.5.2 JTAG边界扫描测试

2.5 硬件测试

2.5.2 JTAG边界扫描测试

2.5 硬件测试

2.5.2 JTAG边界扫描测试

2.5 硬件测试

2.5.2 JTAG边界扫描测试

EDA技术实用教程

第2章

FPGA/CPLD结构原理

2.1 概 述

2.1 概 述

2.1.1 PLD的发展历程

2.1.2 PLD分类

2.2 简单PLD结构原理

2.2.1 逻辑元件符号表示

2.2 简单PLD结构原理

2.2.1 逻辑元件符号表示

2.2 简单PLD结构原理

2.2.2 PROM结构原理

2.7.1 CPLD在系统编程

2.7 CPLD/FPGA的编程与配置

2.7.1 CPLD在系统编程

2.7 CPLD/FPGA的编程与配置

2.7.2 FPGA配置方式

2.7 CPLD/FPGA的编程与配置

2.7.3 FPGA专用配置器件

2.7 CPLD/FPGA的编程与配置

2.7.4 使用单片机配置FPGA

2.6 PLD产品概述

2.6.4 Actel公司的PLD器件

2.6.5 Altera的FPGA配置方式

2.7 CPLD/FPGA的编程与配置

(1)基于电可擦除存储单元的EEPROM或Flash技术。 (2)基于SRAM查找表的编程单元。 (3)基于一次性可编程反熔丝编程单元。

2.7 CPLD/FPGA的编程与配置

加强交通建设管理,确保工程建设质 量。00:55:0800:55:0800:55Saturday, December 12, 2020

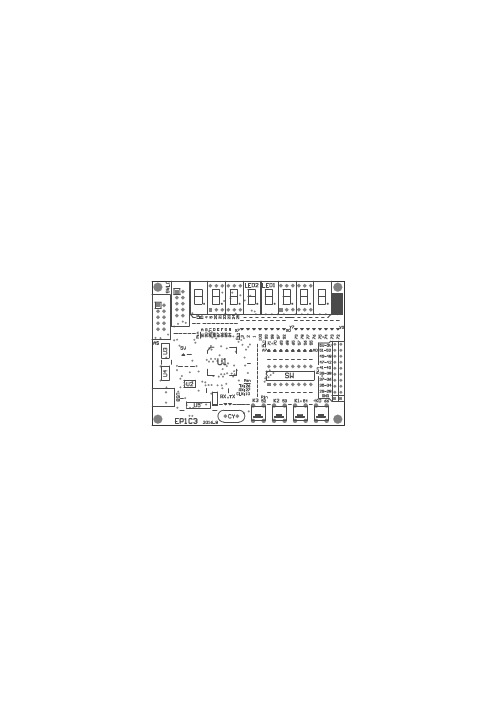

EP1C3T144 FPGA develop board manual(开发板原理图)

FPGA develop board manual ALTERA Cyclone EP1C3T144ALTERA Cyclone 系列的fpga是altera 公司针对底端用户推出的一个系列的fpga。

具有成本低,使用的方便的优点,规模从3000到20000LE。

这一块实验板用的EP1C3T144的芯片,有3000LE逻辑资源,另外还有13条M4K RAM (共6.5Kbyte),另外还有还有一个数字锁相环。

这些资源能够足够应付电子设计竞赛和日常教学的需要,也可以作为初学者入门学习fpga的工具。

1. 开发板介绍1.1. 总体介绍开发板的电路图,如附录所示,电路图一共可分为9个部分:电源部分、按键和LED、下载配置部分、复位部分、外部时钟、滤波电容、用户扩展接口、5 1单片机接口、FPGA 芯片。

1.2. 具体介绍1.2.1. 电源部分板子由外部提供5V电源,使用的圆头插座的封装,可以直接用5V的电源适配器插上使用,不需要直流稳压电源,FPGA的IO的电源是3.3V,内核的电压是1.5V,所以用上两个LEO,一个将5V转到3.3V,另一个将3.3V转到1.5V,加上一些滤波电容,板上的其他外设的电源均是3.3V,另外有3.3V的电源指示灯,表示电源是否正常,还有防反插二极管,防止电源反插,对器件造成损坏。

1.2.2. 按键和LED板上提供4个拨码按键和4个led,分别接到fpga的8个IO引脚上,具体的引脚可以参看电路图或者丝印。

对于初学者,按键和led可以用外当成最简单的外设,用和来控制这些外设。

对于用该板作开发的用户来说,可以把按键当成键盘控制,而把led当成提示来用。

1.2.3. 下载配置部分大家都知道fpga是sram型的可编程逻辑器件,不像rom型可编程器件cpld那样,通过jtag就可以直接把代码固化片子里面。

Fpga随便也可以通过jtag下载代码到片子里面运行。

Fpga下载到片子里面代码是存放在ram里,所以断电后这些代码马上就没有了。

AltiumDesigner原理图与PCB设计原理图绘制基础PPT课件

第25页/共261页

表3-1 Custom Style栏中各设置框的名称和意义

对话框名称 Custom Width Custom Height X Region Count Y Region Count Margin Width

第20页/共261页

(2) Options(选项栏)。在这一选项里,设计者可 以进行图样方向、标题栏、边框等的设定。

·O r i e n t a t i o n ( 图 样 方 向 ) 用鼠标左键单击Options选项栏中的Orientation右 侧的下拉选项框,将出现如图3-13所示的两个选项。选 择Landscape选项时,图样则水平放置,选择Portrait时, 图样则垂直放置。

3.1 工程化原理图设计流程及规范

原理图设计是整个电路设计的基础,它决定了后面 工作的进展,为印制电路板的设计提供了元件、连线的 依据。只有正确的原理图才有可能生成一张具备指定功 能的PCB。原理图的设计过程一般可以按如图3-1所示 的设计流程来进行。

(1) 启动原理图编辑器。原理图的设计是在原理图 编辑器中进行的,只有启动原理图编辑器,才能绘制原 理图,并且编辑。为了更好的管理设计文件,一般先建 立工程,在工程下建立所要设计的原理图文件,然后打 开原理图文件,进入原理图编辑器。

·S n a p ( 光 标 移 动 距 离 ) 该项设置可以用来改变光标的移动间距。Snap设 定主要用来决定光标位移的步长,即光标在移动过程中, 以设定的基本单位来做跳移,单位是mil(密尔,1000密 尔=1英吋=25.4毫米)。如当设定Snap = 10时,十字光 标在移动时,均以10个长度单位为基础。此设置的目 的是使设计者在画图过程上更加方便的对准目标和引脚。

FPGA(EP1C3)板原理图

100 99 98 97 96 95 94 93 92 91 90 89 88 87 86 85 84 83 82 81 80 79 78 77 76

AS

DCLK

IO IO IO IO GND VCCIO2 GND VCCINT IO IO IO IO IO IO IO IO IO GND VCCINT GND VCCIO2 IO IO IO IO

C4 105

1

C7 104

C8 104

C6 104

3.3V 1.5V

1.5V 3.3V

A

Title Size A4 Date: File: 1 2 3 Number Revision

A

3-Aug-2016 Sheet of D:\工程\Prtn 设计\DDA实验箱\STC单片机_Drawn 便携板\FPGA By: 开发板EP1C3 设计\EP1C3_PCB板设计\ 4

R10 5.1K

3.3V 75 74 73 72 71 70 69 68 67 66 65 64 63 62 61 60 59 58 57 56 55 54 53 52 51

CONF_DONE nCONFIG nCE

DATA0

C

nCSO C1 33p

X5 X6 X7 SEL7 SEL6

DATA0 nCONFIG 1.5V

3.3V

U3 AS1117-1.5V

GND 3 IN OUT Vout 2 0

1.5V

TXD RXD D0 D1

D2 D3 D4 D5 D6 D7 D8 D9 D10

D11 D12 D13 D14

26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50

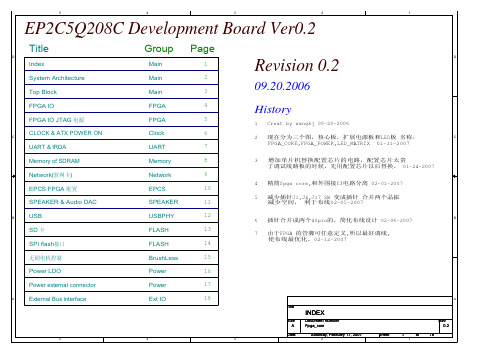

EP2C5Q208C开发板原理图

Rev 0.2 Sheet 2

1

of

18

5

4

3

2

1

10_POWER1

D

POWER

D

EXTIO1

EXTIO

FPGA1 IO_D[0..65]

CONFIG1 EPCS1/4 Data0 Dclk nCS0 ASDIO CONF_DONE nCONFIG nCE TDI TDO TMS TCK

IO_D[0..65]

DATA0 SD_CD SD_CLK SD_CMD SD_D[0..3] SPI_CS DCLK nCONFIG CONF_DONE nstatus UATXD1 UARXD1

A

BL[0..2] BrushLess_in1 BrushLess_in2 BrushLess_in3

USB PHY / pdownloads.cgi/list/usbhostslave POR 自包含reset电路?

USB1 PHY

nSDCAS nSDRAS nSDCS0 nSDWE

B

nSDCAS nSDRAS nSDCS0 nSDWE nWBE0 nWBE1 SDCLK SDCKE

USB_OE USB_SPEED USB_VM USB_VM0 USB_VP USB_VP0

USB_OE USB_SPEED USB_VM USB_VM0 USB_VP USB_VP0

5

4

3

2

1

EP2C5Q208C Development Board Ver0.2

Title

D

Group

Main Main Main FPGA FPGA Clock UART Memory Network EPCS SPEAKER USBPHY FLASH FLASH BrushLess Power Power Ext IO

chapter 4 用Altium设计FPGA

FPGA的设计可以采用自顶向下分析,自底向上设计的方法。 所谓“自顶向下分析”,就是指将数字系统的整体逐步分解为各个 子系统和模块,若子系统规模较大,则还需将子系统进一步分解为 更小的子系统和模块,层层分解,直至整个系统中各子系统关系合 理,并便于逻辑电路级的设计和实现为止。 用Altium Designer6.0 设计FPGA,同在进行设计时推荐采用层 次化的设计方式:底层设计,上层例化(调用)。在底层用语言或 原理图符号设计好各单元文件,并将这些文件生成图表符,上层在 原理图的环境中将这些代表各个文件的图表符连接起来,完成设计 与测试。 下面以一个Altium Designer6.0 自带的BCD计数器为例来说明。

STEP1: 创建FPGA项目

1. 点击:File\New\Project\FPGA Project 2. 为项目命名(如MYBCD.PrjFPG)

STEP2:为FPGA项目添加VHDL文件 1. 创建VHDL空白文件 2. 为新的文件命名(如BCD.VHD)

3.写入VHDL程序

STEP3:生成原理图元件符号,创建项目的VHDL元件库

3)可以在仿真测试平台中(用 wait for语句分段)进行一次性仿真。也可以 每次只仿真一种状态,多次修改测试平台 文件,多次仿真。

STEP6: 项目仿真 1. 设置仿真参数

点击进入仿真项目选项设置

注意: 名称为所需仿真的VHDL测试文 件的实体名和结构体名对应

2.设置FPGA优先选项参数:一般为默认

单击执行 步长设置

步长: 整个仿真的时间常数,步长设

置太短则仿真波形不能显示完整,设置

太长则系统容易出错。

局部仿真波形

完整仿真波形

FPGA黑金开发板AX301原理图

B

C

BANK 3

BANK 4

C

EP4CE6F17C8

EP4CE6F17C8

D Title Size:

D

AX301

Orcad A Number: 2

Revision:1.0

Time: 13:43:52 Date: 2014-5-8 Sheet 2 of 7 File: I:\AX\AX301\SCH@PCB\4.0\2_FPGA.SchDoc 1 2 3

* * * * * 4

1

2

3

4

U4E IO IO IO IO IO, RUP3, (DM1R/BWS#1R)/(_) IO, RDN3, (DQ1R)/(_) IO, DIFFIO_R11n, (DQS3R/CQ3R#)/(DQS3R/CQ3R#) IO, DIFFIO_R11p, (DQ1R)/(_) IO IO, DIFFIO_R10n, (DQ1R)/(_) IO, DIFFIO_R10p, (DQ1R)/(_) IO, VREFB5N0 IO, (DQ1R)/(_) IO, DIFFIO_R9n, (DQ1R)/(_) IO, DIFFIO_R9p IO IO, DIFFIO_R8n, (DQ1R)/(_) IO, DIFFIO_R8p, (DQS1R/CQ1R#,DPCLK4)/(DQS1R/CQ1R#,DPCLK4) IO, DIFFIO_R7n, (DEV_OE) IO, DIFFIO_R7p, (DEV_CLRn) IO, DIFFIO_R6n, (DQ1R)/(_) IO, DIFFIO_R6p IO, (DQ1R)/(_) N13 M12 L12 K12 N14 P15 P16 R16 K11 N16 N15 L14 L13 L16 L15 J11 K16 K15 J16 J15 J14 J12 J13 TFT_MODE M12 L12 K12 N14 S_A9 S_A8 S_A11 K11 S_A6 S_A7 L14 L13 S_A4 S_A5 J11 SD_DIN SD_NCS SD_DOUT SD_CLK J14 J12 J13

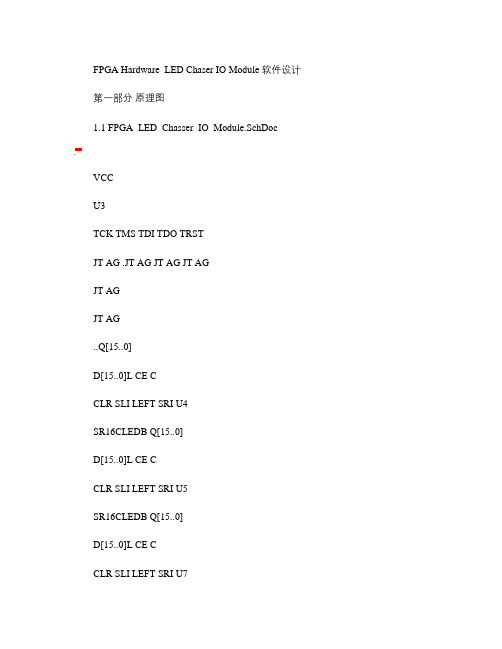

Altium教程FPGAHardwareD软件设计E0(精)

FPGA Hardware_LED Chaser IO Module 软件设计第一部分原理图1.1 FPGA_LED_Chasser_IO_Module.SchDocVCCU3TCK TMS TDI TDO TRSTJT AG .JT AG JT AG JT AGJT AGJT AG..Q[15..0]D[15..0]L CE CCLR SLI LEFT SRI U4SR16CLEDB Q[15..0]D[15..0]L CE CCLR SLI LEFT SRI U5SR16CLEDB Q[15..0]D[15..0]L CE CCLR SLI LEFT SRI U7SR16CLEDB Q[15..0]D[15..0]L CE CCLRSLI LEFT SRI U8SR16CLEDB Q[15..0]Q[31..16]Q[63..48]Q[47..32]D[15..0]D[31..16]D[63..48]D[47..32]VCCVCC VCC VCC Q16Q32Q48Q64Q[15..0]Q[16..31]Q[48..63]Q[47..32]Q71Q15Q31Q47 1 Ch x 8 Bit Digital IO AIN[7..0]AOUT[7..0]CTRL IOB_1X8A[7..0]A0A1D[15..0]D[31..16]D[63..48]D[47..32]A[15..0]B[15..0]Y[15..0]S0U9M16_B2B1A[15..0]B[15..0]Y[15..0]S0U10M16_B2B1A[15..0]B[15..0]Y[15..0]S0U11M16_B2B1 A[15..0]B[15..0]Y[15..0]S0U6M16_B2B1GNDGNDGNDA2U12OR3S LOADDIRMANUALQ[7..0]D[7..0]L CE CCLR SLI LEFT SRI U1 SR8CLEDBQ[71..64]D[71..64]VCC Q0Q63GNDGNDGNDGNDGND D[71..64]A[7..0]B[7..0]Y[7..0]S0U2M8_B2B1GNDDIVN[..] <= 1000000 C D QU19FDU17C D QU18FDVCC SHIFTGNDVCCDigital I/O LED Chaser U13U14/ NCNTL[31..0]LOADU15CDIVN_32/ 5U16CDIV54 Ch x 16 Bit Digital IO AIN[15..0]BIN[15..0]CIN[15..0]DIN[15..0] AOUT[15..0]BOUT[15..0]COUT[15..0]DOUT[15..0]DIGIOIOB_4X16CLK_BRD PXXTEST_BUTTONPXX JTAG_NEXUS_TMSPXXJTAG_NEXUS_TCK PXX JTAG_NEXUS_TDO PXX JTAG_NEXUS_TDI PXX This example implements a 72 bit shift register to "chase" LEDs around a 4x16 Digital I/O module.The speed is k ept down to 10Hz to allow the I/O module to k eep up.You will need to up the refresh speed on the I/O module to 100ms (Options button on the instrument.The 1x8 module controls extra functions.Bit 0 (toggle high the low will load the chaser with the settings entered into the4x16.The 4x16 inputs are used to display the state of the chaser - this is the display.The 4x16 output bits are used to control the value that will be loaded into the chaser when operating in "Manual Mode"Power-On LoadHolds Load high for two shift clock cycles to force a load on startup.Relies on the fact that the DFFs will come up with zero loaded.Load from three sources.1. Startup Load2. Test button Load3. Toggle Bit 0 of CTRL from instrument display.1.2FPGA_LED_Chasser.PAS {......................................................................................................} Procedure UnRouteNet(Board : IPCB_Board; Net : IPCB_Net;VarIterator : IPCB_GroupIterator;Prim : IPCB_Prim;KillList : TList;i : Integer;BeginIterator := Net.GroupIterator_Create;Prim := Iterator.FirstPCBObject;KillList := TList.Create;While Prim <> NIl DoBeginIf Prim.IsFreePrimitive ThenKillList.Add(Prim;Prim := Iterator.NextPCBObject;End;For i := 0 TO KillList.Count - 1 DoBoard.RemovePCBObject(KillList[i];KillList.Free;End; {......................................................................................................}{......................................................................................................} Procedure UnrouteClass(Board : IPCB_BOARD; NetClass : IPCB_OBjectClass;VarIterator : IPCB_BoardIterator;net : IPCB_Net;BeginIterator := Board.BoardIterator_Create;Iterator.SetState_FilterAll;Iterator.AddFilter_ObjectSet(MkSet(eNetObject;Net := Iterator.FirstPCBObject;While Net <> NIl DoBeginIf NetClass.IsMember( ThenUnrouteNet(Board, Net;Net := Iterator.NextPCBObject;End;Board.ViewManager_FullUpdate;End; {......................................................................................................}{......................................................................................................} Procedure UnRouteSelectedClasses(Board : I_PCBBoard;Vari : Integer;BeginFor i := 0 To GetNetClass.Classes.Items.Count - 1 DoIf GetNetClass.Classes.Selected[i] ThenUnrouteClass(Board, GetNetClass.Classes.Items.Objects[i];End; {......................................................................................................}{......................................................................................................} Function ChooseNetCLass(Dummy : Integer = 0 : Boolean;BeginResult := GetNetClass.showmodal = mrOK;End;{......................................................................................................}{......................................................................................................} Procedure FillNetClassList(Board : IPCB_Board;VarIterator : IPCB_BoardIterator;c : IPCB_ObjectClass;BeginIterator := Board.BoardIterator_Create;Iterator.SetState_FilterAll;Iterator.AddFilter_ObjectSet(MkSet(eClassObject;c := Iterator.FirstPCBObject;While c <> NIl DoBeginIf c.MemberKind = eClassMemberKind_Net ThenGetNetClass.Classes.Items.AddObject(, C;c := Iterator.NextPCBObject;End;End; {......................................................................................................}{......................................................................................................} Procedure UnRouteNetClass;VarClassToUnroute : IPCB_OBjectClass;Board : IPCB_Board;BeginPcbserver.PreProcess;TryBoard := PCBServer.GetCurrentPCBBoard;If Not Assigned(Board ThenBeginShowMessage('The Current Document is not a Protel PCB Document.';Exit;End;FillNetClassList(Board;If ChooseNetClass ThenUnrouteSelectedClasses(Board;FinallyPcbserver.PostProcess;End;End; {......................................................................................................}{......................................................................................................} procedure TGetNetClass.ClassesDblClick(Sender: TObject;beginModalResult := mrOK;end;。

3[AltiumDesignerFPGA设计指导]AltiumDesigner原理图和PCB设计

![3[AltiumDesignerFPGA设计指导]AltiumDesigner原理图和PCB设计](https://img.taocdn.com/s3/m/bffb417fec3a87c24128c4f5.png)

Corporate information

奥腾公司简介

第三页,共74页。

Altium 理念(lǐ niàn)

▪ Altium’s Vision

▪ "Historically, the most advanced, state of the art design tools have been prohibitively priced, with access being limited to engineers based in the few companies that could afford them. The Altium vision – unchanged since the company’s inception – is to break down these barriers to innovation and technological advancement and provide every engineer and system designer with easy access to the best possible design tools.〝

第四页,共74页。

Altium 简介(jiǎn jiè)

▪ 前身是 Protel 国际(guójì)

▪ PCB 设计历史悠久

▪ 不时创新 : 首创基于Windows 的印刷线路板设计(PCB) 集成式PCB设计产品。

▪ 全球性公司。

▪ 上世纪末,本世纪初,收买多家公司。

▪ 在2001年,改名为Altium Limited 公司。

▪

…….

……… ……….

第十六页,共74页。

DXP系统平台(píngtái)引见