解交织器VHDL源程序

VHDL入门教程

VHDL入门教程VHDL(Very High-speed Integrated Circuit HardwareDescription Language)是一种用于设计数字电路的硬件描述语言。

它是IEEE 1076标准中规定的一种语言,广泛应用于数字电路的设计、仿真和综合等领域。

本文将为大家介绍VHDL的基础知识和入门教程。

一、VHDL的基本概念1. 实体(Entity):VHDL代码的最高层次,用于定义模块的输入、输出和内部信号。

2. 架构(Architecture):定义了实体中的各个信号和组合逻辑的行为。

3. 信号(Signal):表示数据在电路中的传输和操作。

4. 进程(Process):定义了组合逻辑的行为,用于描述信号之间的关系。

5. 实体声明(Entity Declaration):用于描述模块的名称、输入、输出和内部信号。

6. 架构声明(Architecture Declaration):用于描述模块的内部逻辑。

二、VHDL的基本语法1.实体声明语法:```entity entity_name isport ( port_list );end entity_name;```其中,entity_name是实体的名称,port_list是实体的输入、输出和内部信号。

2.架构声明语法:```architecture architecture_name of entity_name issignal signal_list;beginprocess (sensitivity_list)begin--逻辑行为描述end process;end architecture_name;```其中,architecture_name是架构的名称,entity_name是实体的名称,signal_list是架构的内部信号,sensitivity_list是触发事件的信号列表。

三、VHDL的基本例子下面以一个简单的4位加法器为例介绍VHDL的编写和仿真流程。

Turbo码交织器的VHDL设计

Turbo 码交织器的VHDL 设计赵 华,殷奎喜,柯 炜,宋文娟(南京师范大学物理科学与技术学院 江苏南京 210097)摘 要:介绍了T u rbo 码和交织技术,以及交织技术在T u rbo 码中的重要作用。

并提出了一种交织器电路的设计思路,在这种设计下,各种不同类型的交织器具有相同的电路复杂度。

根据此设计思路,用V HDL 语言的编程设计了交织器的电路,并给出了仿真结果。

关键词:交织器;T u rbo 码;V HDL ;数字电路中图分类号:TN 91913+3 文献标识码:B 文章编号:1004373X (2003)0704203I n terleaver D esign of Turbo codes by VHDLZHAO H ua ,Y I N Ku ix i ,KE W ei ,SON G W en juan(Co llege of Physics Science and Techno l ogy ,N anjing N o r m alU niversity ,N anjing ,210097,Ch ina )Abstract :In troduces the T u rbo code and in terleave techno logy and the i m po rtan t u sage of in terleave in tu rbo codes 1It p ropo s 2es a k ind of design m ethod of in terleaver circu it 1T h is design m akes each k ind of in terleave have the sam e comp lex ity 1A t last it de 2sign s the circu it by V HDL ,and gives their si m u lati on resu lt 1Keywords :in terleaver ;T u rbo code ;V HDL ;digital circu it收稿日期:200301191 Turbo 码和交织技术介绍法国人C 1B errou 等人在1993年提出了T u rbo码[1],他在低信噪比下表现出了近Shannon 限的性能,其性能超过了其他编码方法。

基于vhdl(7,4)汉明码编解码器的设计说明书

(7,4)汉明码编解码器的设计序言VHDL语言具有功能强大的语言结构,可用明确的代码描述复杂的控制逻辑设计,并且具有多层次的设计描述功能,支持设计库和可重复使用的元件的生成。

近几十年来,EDA技术获得了飞速发展。

它以计算机为平台,根据硬件描述语言VHDL,自动地完成逻辑编译、化简分割、综合及优化,布局布线,仿真直至对特定目标芯片的适配编译,逻辑映射和编程下载等工作。

以自顶向下的设计方法,使硬件设计软件化,摆脱了传统手工设计的众多缺点。

随着EDA技术的深入发展基于硬件描述语言的方法将有取代传统手工设计方法的趋势。

EDA ( Elect ronics Design Automation) 技术是随着集成电路和计算机技术飞速发展应运而生的一种高级、快速、有效的电子设计自动化工具。

目前,VHDL语言已经成为EDA的关键技术之一,VHDL 是一种全方位的硬件描述语言,具有极强的描述能力,能支持系统行为级、寄存器传输级和逻辑门级三个不同层次的设计,支持结构、数据流、行为三种描述形式的混合描述,覆盖面广,抽象能力强,因此在实际应用中越来越广泛。

汉明码是在原编码的基础上附加一部分代码,使其满足纠错码的条件。

它属于线性分组码,由于汉明码的抗干扰能力较强,至今仍是应用比较广泛的一类码。

本文用VHDL语言实现了(7,4)汉明码的编码和译码,并通过实例来说明利用VHDL语言实现数字系统的过程。

在介绍(7,4)汉明码编码和译码原理的基础上,设计出了(7,4)汉明码的编码器和译码器,写出了基于VHDL实现的源程序,并通过QUARTUSⅡ软件进行仿真验证。

第1章QuartusⅡ与VHDL简介1.1 QuartusⅡ软件简介QuartusⅡ是Altera公司推出的CPLD/FPGA的开发工具,QuartusⅡ提供了完全集成且与电路结构无关的开发环境,具有数字逻辑设计的全部特性。

?/P>Quartus Ⅱ设计软件提供完整的多平台设计环境,可以很轻松地满足特定设计的需要。

VHDL语言程序及其详细注释

Y <=A after TDP when sel = ‘1’ else B after TDP; 延时 赋值 end;实体说明结束

if CLK = ‘1’ then Qi <=‘0’ after TRQ 条件 延时 赋值 elsif CLK’EVENT and CLK= ‘1’ 当时钟信号clk发生改变并且clk=1

then Qi <= D after TCQ; end if; end process;进程结束 end;结构体结束

end;实体说明结束 architecture Behave of DFFClr is实体的结构体名称及其所属关系 signal Qi : BIT;定义信号 begin QB <= not Qi ; Q <= Qi 结构体开始 信号赋值 process (CLR, CLK) begin 定义进程并且开始进程

stages: for i in 7 downto 0 generate 整体布局描述

LowBit: if i = 0 generate 局部布局描述

FA:Full_Adder port map (A(0),B(0),Cin,C(0),Sum(0));

end generate;

otherBits : if i /= 0 generate

STAGES: for i in 7 downto 0 generate 整体布局描述 FF:DFFClr port map (Clr,Clk,D(i),Q(i),open); 局部布局描述

end generate; 循环描述结束 end;结构体结束

第五讲 VHDL语言程序的基本结构

端口说明

端口说明是对基本设计实体(单元)与外部接口的描 述,也可以说是对外部引脚信号的名称,数据类型和 输入,输出方向的描述; 其一般书写格式为: PORT(端口名{,端口名}:方向 数据类型名; 端口名{,端口名}:方向 数据类型名); 举例: PORT(d0,d1,sel : IN BIT; q : OUT BIT; bus : OUT BIT_VECTOR(7 DOWNTO 0) );

敏感信号: 只要有一个发 生变化(如由 "0"变成"1" 或由"1"变为 "0")都将启 动PROCESS语 句.

PROCESS语句的特点

(1) 进程内部的所有语句都是顺序执行的. (2) 多进程之间,是并行执行的,并可访问构 造体或实体中所定义的信号. (3) 进程的启动是由进程标识符Process后的 敏感信号来触发,也可用WAIT语句等待一个 触发条件的成立. (4) 各进程之间的通信是由信号来传递的.

第2章 VHDL语言程序的基本结构 章 语言程序的基本结构

主要内容

VHDL语言设计的基本单元及其构成 : 语言

实体 + 构造体

VHDL语言构造体的子结构描述 : 语言

块,进程,子程序

包集合, 包集合,库及配置

一个完整的VHDL语言程序 通常包含5个部分:

必 备 部 分

库,包集合 实体(Entity)

构造体:描述系统内部的结构和行为;

包集合:存放各种设计模块都能共享的数据类型, 常数和子程序等; 库: 存放已经编译的实体,构造体,包集合和 配置.

前四种是可分别编译的源设计单元

2.1 VHDL语言设计的基本单元及其构成 语言 实体+构造体 构造体) (实体 构造体)

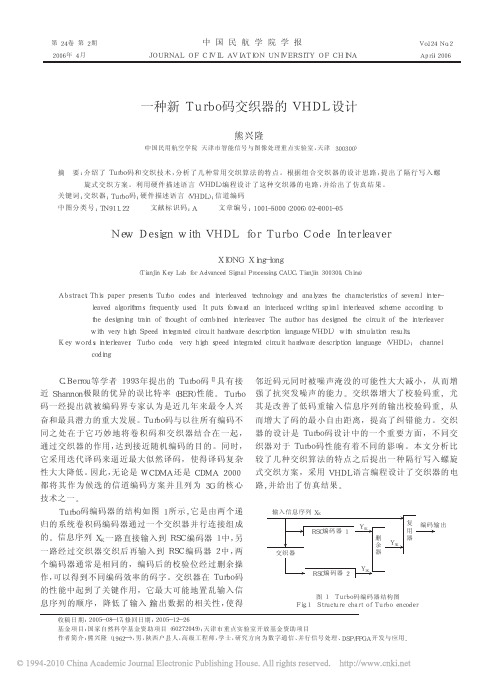

一种新Turbo码交织器的VHDL设计_熊兴隆

收稿日期:2005-08-17;修回日期:2005-12-26基金项目:国家自然科学基金资助项目(60272049);天津市重点实验室开放基金资助项目作者简介:熊兴隆(1962-),男,陕西户县人,高级工程师,学士,研究方向为数字通信、并行信号处理、DSP/FPGA开发与应用.C.Berrou等学者1993年提出的Turbo码[1]具有接近Shannon极限的优异的误比特率(BER)性能。

Turbo码一经提出就被编码界专家认为是近几年来最令人兴奋和最具潜力的重大发展。

Turbo码与以往所有编码不同之处在于它巧妙地将卷积码和交织器结合在一起,通过交织器的作用,达到接近随机编码的目的。

同时,它采用迭代译码来逼近最大似然译码,使得译码复杂性大大降低。

因此,无论是WCDMA还是CDMA2000都将其作为候选的信道编码方案并且列为3G的核心技术之一。

Turbo码编码器的结构如图1所示,它是由两个递归的系统卷积码编码器通过一个交织器并行连接组成的。

信息序列XK一路直接输入到RSC编码器1中,另一路经过交织器交织后再输入到RSC编码器2中,两个编码器通常是相同的,编码后的校验位经过删余操作,可以得到不同编码效率的码字。

交织器在Turbo码的性能中起到了关键作用,它最大可能地置乱输入信息序列的顺序,降低了输入/输出数据的相关性,使得邻近码元同时被噪声淹没的可能性大大减小,从而增强了抗突发噪声的能力。

交织器增大了校验码重,尤其是改善了低码重输入信息序列的输出校验码重,从而增大了码的最小自由距离,提高了纠错能力。

交织器的设计是Turbo码设计中的一个重要方面,不同交织器对于Turbo码性能有着不同的影响。

本文分析比较了几种交织算法的特点之后提出一种隔行写入螺旋式交织方案,采用VHDL语言编程设计了交织器的电路,并给出了仿真结果。

一种新Turbo码交织器的VHDL设计熊兴隆(中国民用航空学院天津市智能信号与图像处理重点实验室,天津300300)摘要:介绍了Turbo码和交织技术,分析了几种常用交织算法的特点。

密码锁设计VHDL源程序文档

2.2系统的输入、输出端口以及寄存器清单及说明:CLK 输入时钟方波信号端口KIN 键盘按键输入端口KOUT 键盘完整编码码值输出端口(七位二进制数)KOUT1 扫描信号输出端口(三位二进制数)SIN 键盘消抖输入端口(七位二进制数)SOUT 键盘消抖输出端口(七位二进制数)LIN 键盘按键编码模块输入端口(七位二进制数)DF 数字按键标志寄存器FF 功能按键标志寄存器ND 数字按键识别编码寄存器NF 功能按键识别编码寄存器LOCK 电子密码锁上锁状态标志寄存器LOCK1 电子密码锁报警状态标志寄存器UNLOCK 电子密码锁开锁状态标志寄存器NULL1 电子密码锁无密码状态标志寄存器DATA 电子密码锁数码显示数据寄存器CAT 电子密码锁数码显示位选寄存器DISPLAY 电子密码锁数码显示段选寄存器(十七位二进制数)NUM0、NUM1、NUM2、NUM3数码显示中分位显示数据寄存器DISNUM 数码显示段选数据寄存器I1 数码显示计数器SCANS 键盘扫描中按键完整编码寄存器SCAN 键盘扫描寄存器CNT 键盘消抖计数器SIN1 键盘按键键值寄存器I 键盘扫描计数器DF1 数字按键状态标志寄存器ACC 键盘数字输入暂存器T 报警计数器REG 电子密码锁密码存储器NC 计数器1键盘输入扫描部分源程序LIBRARY IEEE;USE IEEE.STD_LOGIC_ARITH.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;USE IEEE.STD_LOGIC_1164.ALL;ENTITY kbscan1 isPORT(clk:in STD_LOGIC;kin:in STD_LOGIC_VECTOR(3 DOWNTO 0);---PC7-PC4 kout:out STD_LOGIC_VECTOR(7 downto 0);--PC3--PCkout1: out STD_LOGIC_VECTOR(3 downto 0));end kbscan1;architecture a of kbscan1 issignal scans: std_logic_vector(7 downto 0);--PC7--PC0signal scan : std_logic_vector(3 downto 0);--PC3--PC0signal cnt :integer range 0 to 140;signal sin1:std_logic_vector(3 downto 0);signal i:integer range 0 to 3;beginscans<=scan& kin;kout<=scans;kout1<=scan;process(clk)beginif(falling_edge(clk))thenif(i=3)theni<=0;elsei<=i+1;end if;case i iswhen 0=>scan<="0001";when 1=>scan<="0010";when 2=>scan<="0100";when 3=>scan<="1000";end case;end if;end process;End a;2键盘输入消抖部分源程序LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY xiaodou isPort(clk :in STD_LOGIC;sin:in std_logic_vector(7 downto 0);sout:out std_logic_vector(7 downto 0));end xiaodou;architecture behavioral of xiaodou issignal cnt :integer range 0 to 120;signal sin1:std_logic_vector(7 downto 0);beginprocess(clk)beginsin1<=sin;if (rising_edge(clk))thenif(sin1=sin)thencnt<=cnt+1;elsesin1<=sin;cnt<=0;end if;if(cnt=120)thensout<=sin;cnt<=0;end if;end if;end process;end behavioral;3键盘输入编码部分源程序LIBRARY IEEE;USE IEEE.STD_LOGIC_ARITH.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;USE IEEE.STD_LOGIC_1164.ALL;ENTITY bianma isPORT(clk:in STD_LOGIC;lin:in STD_LOGIC_VECTOR(7 DOWNTO 0);---PC7-PC4DF,FF: out std_logic;nd,nf:BUFFER std_logic_vector(3 downto 0));end bianma;architecture b of bianma isbeginprocess(clk)beginif clk'event and clk='1' thencase lin iswhen"10000001"=>ND<="0000";--0when"00010001"=>ND<="0001";--1when"00010010"=>ND<="0010";--2when"00010100"=>ND<="0011";--3when"00100001"=>ND<="0100";--4when"00100010"=>ND<="0101";--5when"00100100"=>ND<="0110";--6when"01000001"=>ND<="0111";--7when"01000010"=>ND<="1000";--8when"01000100"=>ND<="1001";--9when others =>ND<="1111";END CASE;END IF;IF CLK'EVENT AND CLK='1' THENCASE LIN ISwhen"00011000"=>NF<="0001";--qingchuwhen"00101000"=>NF<="0010";--querenwhen"01001000"=>NF<="0011";--shangsuowhen"10001000"=>NF<="0100";--kaisuowhen"10000100"=>NF<="0101";--wangjimimawhen"10000010"=>NF<="0111";--genggaimimaWhen others =>NF<="1000";END CASE;END IF;END PROCESS;DF<=NOT(ND(3) AND ND(2) AND ND(1) AND ND(0));FF<=NF(2) OR NF(1) OR NF(0);end b;4 电子密码锁的控制部分程序DF 数字按键标志寄存器FF 功能按键标志寄存器ND 数字按键识别编码寄存器NF 功能按键识别编码寄存器LOCK 电子密码锁上锁状态标志寄存器LOCK1 电子密码锁报警状态标志寄存器UNLOCK 电子密码锁开锁状态标志寄存器NULL1 电子密码锁无密码状态标志寄存器DATA 电子密码锁数码显示数据寄存器LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY kongzhi ISPORT(CLK: IN STD_LOGIC;DF,FF: in STD_LOGIC;ND,NF:in STD_LOGIC_VECTOR(3 downTO 0);LOCK,LOCK1,UNLOCK:buffer STD_LOGIC;NULL1: buffer STD_LOGIC;DA TA: out STD_LOGIC_VECTOR(15 downTO 0) );END kongzhi;ARCHITECTURE V1 OF kongzhi ISsignal i1:integer range 0 to 3;signal df1:std_logic;signal ACC: STD_LOGIC_VECTOR(15 DOWNTO 0);signal t: INTEGER RANGE 0 TO 2;signal REG:STD_LOGIC_VECTOR(15 downTO 0);signal NC,A:INTEGER RANGE 0 TO 3;beginPROCESS(FF,DF)ISBEGINif rising_edge(clk) thenIF FF='1'THENIF NF="0001"THENACC<="0000000000000000";NC<=0;END IF;ELSEdf1<=df;IF df1='0'and DF='1' THENIF NC<4 THENACC<=ACC(11 DOWNTO 0)&ND;NC<=NC+1;END IF;END IF;END IF;IF FF='1' THENIF NF="0011" THENREG<=ACC;LOCK<='0';UNLOCK<='1';LOCK1<='1';NULL1<='1';elseIF NF="0100" THENIF REG=ACC THENLOCK<='1';UNLOCK<='0';LOCK1<='1';NULL1<='1';ELSELOCK<='0';UNLOCK<='1';IF t=2 THENREG<="1000100010001000";LOCK1<='0';lock<='1';unlock<='1';null1<='1';t<=0;ELSEt<=t+1;END IF;END IF;elseIF NF="0101" THENREG<="1000100010001000";LOCK<='0';UNLOCK<='1';LOCK1<='1';NULL1<='1';elseIF NF="0111" THENIF UNLOCK='1' THENIF REG=ACC THENREG<="0000000000000000";NULL1<='0';LOCK<='1';LOCK1<='1';UNLOCK<='1';END IF;END IF;elseIF NF="0010" THENREG<=ACC;NULL1<='1';LOCK<='0';LOCK1<='1';UNLOCK<='1';END IF;end if;end if;end if;end if;end if;end if;END PROCESS;DA TA<=ACC;END ARCHITECTURE V1;CAT 电子密码锁数码显示位选寄存器DISPLAY 电子密码锁数码显示段选寄存器(十七位二进制数)DISPLAY 电子密码锁数码显示段选寄存器(十七位二进制数)NUM0、NUM1、NUM2、NUM3数码显示中分位显示数据寄存器DISNUM 数码显示段选数据寄存器I1 数码显示计数器5电子密码锁的数码显示模块源程序LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY LEDXIANSHI ISPORT(CLK :IN STD_LOGIC;DA TA: in STD_LOGIC_VECTOR (15 DOWNTO 0);CA T:OUT STD_LOGIC_VECTOR(0 TO 3);DISPLAY:OUT STD_LOGIC_VECTOR(16 DOWNTO 0));END LEDXIANSHI;ARCHITECTURE BEHA VIORAL OF LEDXIANSHI ISSignal NUM0,NUM1,NUM2,NUM3: STD_LOGIC_VECTOR(3 DOWNTO 0);SIGNAL DISNUM:STD_LOGIC_VECTOR(16 DOWNTO 0);SIGNAL I1:INTEGER RANGE 0 TO 3;BEGINNUM0<=DATA(3 DOWNTO 0);NUM1<=DATA(7 DOWNTO 4);NUM2<=DATA(11 DOWNTO 8);NUM3<=DA TA(15 DOWNTO 12);DISPLAY<=DISNUM;PROCESS(CLK)BEGINIF(RISING_EDGE(CLK))THENIF(I1=3)THENI1<=0;ELSEI1<=I1+1;END IF;END IF;END PROCESS;PROCESS(I1)BEGINCASE I1 ISWHEN 0=>CA T<="1110";CASE NUM0 ISWHEN "0000"=>DISNUM<="00000000011111111";WHEN "0001"=>DISNUM<="00000000000001100";WHEN "0010"=>DISNUM<="00001000101110111";WHEN "0011"=>DISNUM<="00001000100111111";WHEN "0100"=>DISNUM<="01001010110000000";WHEN "0101"=>DISNUM<="00001100110111011";WHEN "0110"=>DISNUM<="00001000111111011";WHEN "0111"=>DISNUM<="00000000000001111";WHEN "1000"=>DISNUM<="00001000111111111";WHEN "1001"=>DISNUM<="00001000110111111";WHEN OTHERS=>DISNUM<=NULL;END CASE;WHEN 1 => CAT<="1101";CASE NUM1 ISWHEN "0000"=>DISNUM<="00000000011111111";WHEN "0001"=>DISNUM<="00000000000001100";WHEN "0010"=>DISNUM<="00001000101110111";WHEN "0011"=>DISNUM<="00001000100111111";WHEN "0100"=>DISNUM<="01001010110000000";WHEN "0101"=>DISNUM<="00001100110111011";WHEN "0110"=>DISNUM<="00001000111111011";WHEN "0111"=>DISNUM<="00000000000001111"; WHEN "1000"=>DISNUM<="00001000111111111"; WHEN "1001"=>DISNUM<="00001000110111111"; WHEN OTHERS=>DISNUM<=NULL;END CASE;WHEN 2=>CAT<="1011";CASE NUM2 ISWHEN "0000"=>DISNUM<="00000000011111111"; WHEN "0001"=>DISNUM<="00000000000001100"; WHEN "0010"=>DISNUM<="00001000101110111"; WHEN "0011"=>DISNUM<="00001000100111111"; WHEN "0100"=>DISNUM<="01001010110000000"; WHEN "0101"=>DISNUM<="00001100110111011"; WHEN "0110"=>DISNUM<="00001000111111011"; WHEN "0111"=>DISNUM<="00000000000001111"; WHEN "1000"=>DISNUM<="00001000111111111"; WHEN "1001"=>DISNUM<="00001000110111111"; WHEN OTHERS=>DISNUM<=NULL;END CASE;WHEN 3=>CAT<="0111";CASE NUM3 ISWHEN "0000"=>DISNUM<="00000000011111111"; WHEN "0001"=>DISNUM<="00000000000001100"; WHEN "0010"=>DISNUM<="00001000101110111";WHEN "0011"=>DISNUM<="00001000100111111";WHEN "0100"=>DISNUM<="01001010110000000";WHEN "0101"=>DISNUM<="00001100110111011";WHEN "0110"=>DISNUM<="00001000111111011";WHEN "0111"=>DISNUM<="00000000000001111";WHEN "1000"=>DISNUM<="00001000111111111";WHEN "1001"=>DISNUM<="00001000110111111";WHEN OTHERS=>DISNUM<=NULL;END CASE;END CASE;END PROCESS;END BEHA VIORAL;6电子密码锁的数码显示部分(附加)LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY LEDXIANSHI ISPORT(CLK :IN STD_LOGIC;DATA: in STD_LOGIC_VECTOR (15 DOWNTO 0);CA T:OUT STD_LOGIC_VECTOR(0 TO 3);DISPLAY:OUT STD_LOGIC_VECTOR(16 DOWNTO 0));END LEDXIANSHI;ARCHITECTURE BEHA VIORAL OF LEDXIANSHI ISsignal NUM0,NUM1,NUM2,NUM3: STD_LOGIC_VECTOR(3 DOWNTO 0);SIGNAL DISNUM:STD_LOGIC_VECTOR(16 DOWNTO 0);SIGNAL I1:INTEGER RANGE 0 TO 3;BEGINNUM0<=DATA(3 DOWNTO 0);NUM1<=DATA(7 DOWNTO 4);NUM2<=DATA(11 DOWNTO 8);NUM3<=DA TA(15 DOWNTO 12); DISPLAY<=DISNUM;PROCESS(CLK)BEGINIF(RISING_EDGE(CLK))THENIF(I1=3)THENI1<=0;ELSEI1<=I1+1;END IF;END IF;END PROCESS;PROCESS(I1)BEGINCASE I1 ISWHEN 0=>CAT<="1110";CASE NUM0 ISWHEN "0000"=>DISNUM<="00000000011111111";WHEN OTHERS=>DISNUM<="01111111100000000";END CASE;WHEN 1=>CAT<="1101";CASE NUM1 ISWHEN "0000"=>DISNUM<="00000000011111111";WHEN OTHERS=>DISNUM<="01111111100000000";END CASE;WHEN 2=>CAT<="1011";CASE NUM2 ISWHEN "0000"=>DISNUM<="00000000011111111"; WHEN OTHERS=>DISNUM<="01111111100000000"; END CASE;WHEN 3=>CAT<="0111";CASE NUM3 ISWHEN "0000"=>DISNUM<="00000000011111111"; WHEN OTHERS=>DISNUM<="01111111100000000"; END CASE;END CASE;END PROCESS;END BEHA VIORAL;数码管显示library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_ARITH.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;entity KeyScan isport(RESET : in std_logic;CLK : in std_logic; --基本时钟源6MHzKeyIn : in std_logic_vector(3 downto 0); --column列KeyOut : out std_logic_vector(3 downto 0); --row行LED_A : out std_logic; --4位数码管引脚LED_B : out std_logic;LED_C : out std_logic;LED_D : out std_logic;LED_E : out std_logic;LED_F : out std_logic;LED_G : out std_logic;LED_VCC1 : out std_logic; --时十位LED_VCC2 : out std_logic; --时个位LED_VCC3 : out std_logic; --分十位LED_VCC4 : out std_logic; --分个位LED_TimePoint:out std_logic; --冒号LED_Point :out std_logic; --小数点LED_EN1 :out std_logic --小数点);end KeyScan;architecture Behavioral of KeyScan issignal timecnt : integer range 0 to 100000 ; --分频计数器,用来得到10ms时钟signal time10ms : std_logic ; --10ms时钟signal scanvalue : std_logic_vector(3 downto 0);--记录扫描数据signal combvalue : std_logic_vector(7 downto 0);--KeyIn、KeyOut组合值signal cpy_scanvalue : std_logic_vector(3 downto 0);--备份扫描数据signal count : integer range 0 to 60000 ; --分频器,产生毫秒时钟基准signal scancnt : integer range 0 to 3 ; --LED扫描轮转signal Data0: integer range 0 to 9 ;beginLED_EN1<='0';--进程1:产生20ms时钟process( CLK,RESET)beginif RESET='0' then time10ms<='0'; --初始化elsif CLK'event and CLK='1' thentimecnt<=timecnt+1;if timecnt=100000then time10ms<=not time10ms; timecnt<=0;end if;end if;end process;--进程2:键盘扫描输出process( time10ms,RESET)beginif RESET='0' then scanvalue<="0001";combvalue<="00000000";Data0<=0; --初始化elsif time10ms'event and time10ms='1' then --每10ms进行一次键盘扫描KeyOut<=scanvalue; --输出扫描值cpy_scanvalue<=scanvalue; --备份扫描值,为了进程3对扫描结果进行比较case scanvalue is --扫描值移位when "0001" => scanvalue<="0010";when "0010" => scanvalue<="0100";when "0100" => scanvalue<="1000";when "1000" => scanvalue<="0001";when others => scanvalue<="0001";end case;combvalue<= (KeyIn & cpy_scanvalue); --组合键盘扫描的输入和输出case combvalue is --翻译扫描结果when "00010001" => Data0<=1; --对应键盘“1”when "00100001" => Data0<=2; --对应键盘“2”when "01000001" => Data0<=3; --对应键盘“3”when "00010010" => Data0<=4; --对应键盘“4”when "00100010" => Data0<=5; --对应键盘“5”when "01000010" => Data0<=6; --对应键盘“6”when "00010100" => Data0<=7; --对应键盘“7”when "00100100" => Data0<=8; --对应键盘“8”when "01000100" => Data0<=9; --对应键盘“9”when "00011000" => Data0<=0; --对应键盘“0”when others => null; --无键盘按下end case;end if;end process;--数码管扫描process(CLK,RESET) --时钟进程,产生各种时钟信号beginif RESET='0' then NULL;elsif CLK'event and CLK='1' thencount<=count+1;if count=60000 thencount<=0;if scancnt>3 then scancnt<=0;else scancnt<=scancnt+1;end if;end if;end if;end process;--数码管扫描process(CLK, RESET)begin--LED_VCC信号是‘1’有效,其余信号均为‘0’有效,中间的冒号两个点分别由VCC2和VCC3控制if RESET='0' then LED_A<='1';LED_B<='1';LED_C<='1';LED_D<='1';LED_E<='1';LED_F<='1';LED_G<='1';LED_VCC1<='0';LED_VCC2<='0';LED_VCC3<='0';LED_VCC4<='0';LED_TimePoint<='1'; LED_Point<='1';elseif scancnt=0 thencase Data0 is --分个位when 0 => LED_A<='0';LED_B<='0';LED_C<='0';LED_D<='0';LED_E<='0';LED_F<='0';LED_G<='1';LED_VCC1<='0';LED_VCC2<='0'; LED_VCC3<='0';LED_VCC4<='1';LED_Point<='1';when 1 => LED_A<='1';LED_B<='0';LED_C<='0';LED_D<='1';LED_E<='1';LED_F<='1';LED_G<='1';LED_VCC1<='0';LED_VCC2<='0'; LED_VCC3<='0';LED_VCC4<='1';LED_Point<='1';when 2 => LED_A<='0';LED_B<='0';LED_C<='1';LED_D<='0';LED_E<='0';LED_F<='1';LED_G<='0';LED_VCC1<='0';LED_VCC2<='0'; LED_VCC3<='0';LED_VCC4<='1';LED_Point<='1';when 3 => LED_A<='0';LED_B<='0';LED_C<='0';LED_D<='0';LED_E<='1';LED_F<='1';LED_G<='0';LED_VCC1<='0';LED_VCC2<='0'; LED_VCC3<='0';LED_VCC4<='1';LED_Point<='1';when 4 => LED_A<='1';LED_B<='0';LED_C<='0';LED_D<='1';LED_E<='1';LED_F<='0';LED_G<='0';LED_VCC1<='0';LED_VCC2<='0'; LED_VCC3<='0';LED_VCC4<='1';LED_Point<='1';when 5 => LED_A<='0';LED_B<='1';LED_C<='0';LED_D<='0';LED_E<='1';LED_F<='0';LED_G<='0';LED_VCC1<='0';LED_VCC2<='0'; LED_VCC3<='0';LED_VCC4<='1';LED_Point<='1';when 6 => LED_A<='0';LED_B<='1';LED_C<='0';LED_D<='0';LED_E<='0';LED_F<='0';LED_G<='0';LED_VCC1<='0';LED_VCC2<='0'; LED_VCC3<='0';LED_VCC4<='1';LED_Point<='1';when 7 => LED_A<='0';LED_B<='0';LED_C<='0';LED_D<='1';LED_E<='1';LED_F<='1';LED_G<='1';LED_VCC1<='0';LED_VCC2<='0'; LED_VCC3<='0';LED_VCC4<='1';LED_Point<='1';when 8 => LED_A<='0';LED_B<='0';LED_C<='0';LED_D<='0';LED_E<='0';LED_F<='0';LED_G<='0';LED_VCC1<='0';LED_VCC2<='0'; LED_VCC3<='0';LED_VCC4<='1';LED_Point<='1';when 9 => LED_A<='0';LED_B<='0';LED_C<='0';LED_D<='0';LED_E<='1';LED_F<='0';LED_G<='0';LED_VCC1<='0';LED_VCC2<='0'; LED_VCC3<='0';LED_VCC4<='1';LED_Point<='1';when others => null;end case;end if;end if;end process;end Behavioral;控制电路的软件仿真图(1)图2-11 控制电路的软件仿真图(2)控制电路的软件仿真图(3)控制电路的软件仿真图(4)控制电路的软件仿真图(5)5电子密码锁的数码显示模块源程序(改七段)LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY LEDXIANSHI ISPORT(CLK :IN STD_LOGIC;LED_TimePoint:out std_logic; --冒号LED_Point :out std_logic; --小数点LED_EN1 :out std_logic; --选择数码管显示DA TA: in STD_LOGIC_VECTOR (15 DOWNTO 0);CA T:OUT STD_LOGIC_VECTOR(0 TO 3);DISPLAY:OUT STD_LOGIC_VECTOR(6 DOWNTO 0));END LEDXIANSHI;ARCHITECTURE BEHA VIORAL OF LEDXIANSHI ISSignal NUM0,NUM1,NUM2,NUM3: STD_LOGIC_VECTOR(3 DOWNTO 0);SIGNAL DISNUM:STD_LOGIC_VECTOR(6 DOWNTO 0);SIGNAL I1:INTEGER RANGE 0 TO 3;BEGINNUM0<=DATA(3 DOWNTO 0);NUM1<=DATA(7 DOWNTO 4);NUM2<=DATA(11 DOWNTO 8);NUM3<=DA TA(15 DOWNTO 12);DISPLAY<=DISNUM;PROCESS(CLK)BEGINIF(RISING_EDGE(CLK))THENIF(I1=3)THENI1<=0;ELSEI1<=I1+1;END IF;END IF;END PROCESS;PROCESS(I1)BEGINCASE I1 ISWHEN 0=>CA T<="0001";CASE NUM0 ISWHEN "0000"=>DISNUM<="1000000";WHEN "0001"=>DISNUM<="1111001";WHEN "0010"=>DISNUM<="0100100";WHEN "0011"=>DISNUM<="0110000";WHEN "0100"=>DISNUM<="0011001";WHEN "0101"=>DISNUM<="0010010";WHEN "0110"=>DISNUM<="0000010";WHEN "0111"=>DISNUM<="1111000";WHEN "1000"=>DISNUM<="0000000";WHEN "1001"=>DISNUM<="0010000";WHEN OTHERS=>DISNUM<=NULL;END CASE;WHEN 1 => CAT<="0010";CASE NUM1 ISWHEN "0000"=>DISNUM<="1000000";WHEN "0001"=>DISNUM<="1111001";WHEN "0010"=>DISNUM<="0100100";WHEN "0011"=>DISNUM<="0110000";WHEN "0100"=>DISNUM<="0011001"; WHEN "0101"=>DISNUM<="0010010"; WHEN "0110"=>DISNUM<="0000010"; WHEN "0111"=>DISNUM<="1111000"; WHEN "1000"=>DISNUM<="0000000"; WHEN "1001"=>DISNUM<="0010000";WHEN OTHERS=>DISNUM<=NULL; END CASE;WHEN 2=>CAT<="0100";CASE NUM2 ISWHEN "0000"=>DISNUM<="1000000"; WHEN "0001"=>DISNUM<="1111001"; WHEN "0010"=>DISNUM<="0100100"; WHEN "0011"=>DISNUM<="0110000"; WHEN "0100"=>DISNUM<="0011001"; WHEN "0101"=>DISNUM<="0010010"; WHEN "0110"=>DISNUM<="0000010"; WHEN "0111"=>DISNUM<="1111000"; WHEN "1000"=>DISNUM<="0000000"; WHEN "1001"=>DISNUM<="0010000";WHEN OTHERS=>DISNUM<=NULL; END CASE;WHEN 3=>CAT<="1000";CASE NUM3 ISWHEN "0000"=>DISNUM<="1000000"; WHEN "0001"=>DISNUM<="1111001"; WHEN "0010"=>DISNUM<="0100100"; WHEN "0011"=>DISNUM<="0110000"; WHEN "0100"=>DISNUM<="0011001"; WHEN "0101"=>DISNUM<="0010010"; WHEN "0110"=>DISNUM<="0000010"; WHEN "0111"=>DISNUM<="1111000"; WHEN "1000"=>DISNUM<="0000000"; WHEN "1001"=>DISNUM<="0010000";WHEN OTHERS=>DISNUM<=NULL; END CASE;END CASE;END PROCESS;END BEHA VIORAL;。

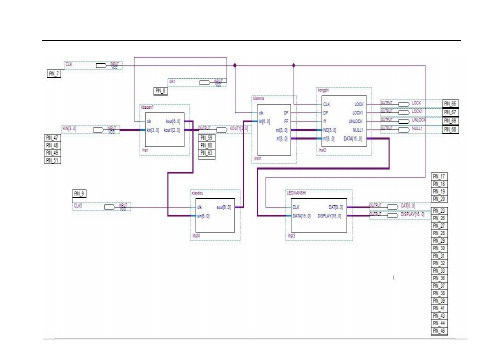

基于vhdl卷积码编解码器的设计说明书

长沙理工大学《通信电路EDA》课程项目报告系别水利计通系专业通信工程班级通信1003班指导教师项目组组长学号项目组成员学号项目组成员学号项目组成员学号完成日期2012年11月14日目录1 引言 (3)1.1项目背景 (3)2 卷积码编解码器的结构概述 (4)2.1 卷积码编码器的结构 (4)2.2 卷积译码器的结构 (4)3 卷积码编解码器的VHDL 设计 (5)3.1 VHDL 设计的优点与设计方法 (5)3.2 卷积码编码器的VHDL 实现 (5)3.2.1 卷积编码器顶层建模的VHDL 描述 (5)3.2.2 用MAX+PLUSⅡ编译后生成的编码器图形符号 (7)3.2.3 卷积编码器VHDL仿真波形 (7)3.3 卷积码解码器的VHDL实现 (7)3.3.1 卷积解码器顶层建模的VHDL 描述 (7)3.3.2 用MAX+PLUSⅡ编译后生成的解码器图形符号 (9)3.3.3 卷积解码器VHDL仿真波形 (9)4 参考文献 (9)5 后记 (10)基于VHDL的卷积码编解码器的设计1 引言1.1项目背景现代数字通信有两个基本的理论基础,即信息论和纠错编码理论,它们几乎是同时在第二次世界大战结束后不久诞生的。

前者首先由Shannon以他的不朽名著“通信的数学理论”为标志建立起来的,而后者则以Hamming的经典著作“纠错和检错编码”为代表。

Shannon信息论主要讨论信息的度量,以及对于信息表示和信息传输的基本限制。

信道编码定理告诉我们,只要信息传输速率小于信道容量,则信息传输可以以任何小的错误概率进行。

但是,Shannon信息论并没有告诉我们如何去实现这一点。

Hanmming提出的纠错编码理论正是为了解决这个问题。

科学技术的发展使人类跨入了高度发展的信息化时代。

在政治、军事、经济等各个领域,信息的重要性不言而喻,有关信息理论的研究正越来越受到重视。

20世纪50年代信息论在学术界引起了巨大的反响。

交织器解交织器设计说明文档

交织器与解交织器的Verilog设计0 引言在数字通信中由于信道固有的噪声特性以及衰落特性,信息在有干扰信道传输时不可避免的会发生差错。

为了提高通信系统信息传输的可靠性,一般采用纠错编码技术来提高通信系统抗干扰能力。

但是当信道发生突发差错时,会造成连续的错误,超过纠错码的纠错能力。

交织技术作为一项改善通信系统性能的方式,将数据按照一定的规则打乱,把原先连续的差错分散开来,使突发性错误转化为随机性错误,能够提高通信系统抗突发差错的能力和降低译码复杂度。

VHDL作为一种硬件设计时采用的标准语言,降低设计FPGA的难度,使整个系统的设计和调试周期缩短。

本设计利用FPGA实现交织,能大大缩减电路的体积,提高电路的稳定性。

1 卷积交织和解交织的原理交织过程可算作一个编码过程,他把经过纠错编码的数据进行一定的排列组合,提高原有纠错编码的纠突发错误的能力。

数字通信中一般采取的同步交织有 2 种:(1) 块交织也叫矩阵行列转置法。

可以表述为一个二维存储器阵列 ( N × B ) 。

交织过程是数据先按行写入,再按列读出;解交织过程则相反,是数据先按列写入,再按行读出。

块交织结构简单, 但数据延时时间长而且所需的存储器比较大。

(2) 卷积交织交织器的输入端的输入符号数据按顺序分别进入 B 条支路延时器, 每一路延时不同的符号周期。

第一路无延时,第二路延时M个符号周期,第三路延时2M个符号周期,…,第B路延时( B - 1 )M 个符号周期。

交织器的输出端按输入端的工作节拍分别同步输出对应支路经延时的数据。

卷积交织每条支路符号数据的延时节拍为 di = ( i - 1)M B , i = 1, 2, …, B 。

解交织器的延时数与交织器相反。

图1 卷积交织器和解交织器原理图在仔细对比块交织和卷积交织两种方法之后,考虑到缩短延时和减小器件体积,小组决定采用卷积交织的方法来设计。

然而实现卷积交织的延时方法有多种,一是采用移位寄存器法,直接利用FIFO实现每条支路的延时,这种方法实现简单,但是当B与M值较大时,需要消耗大量的寄存器(图2所示);二是利用RAM来实现移位寄存器的功能,通过控制读/写地址来实现每条支路延迟。

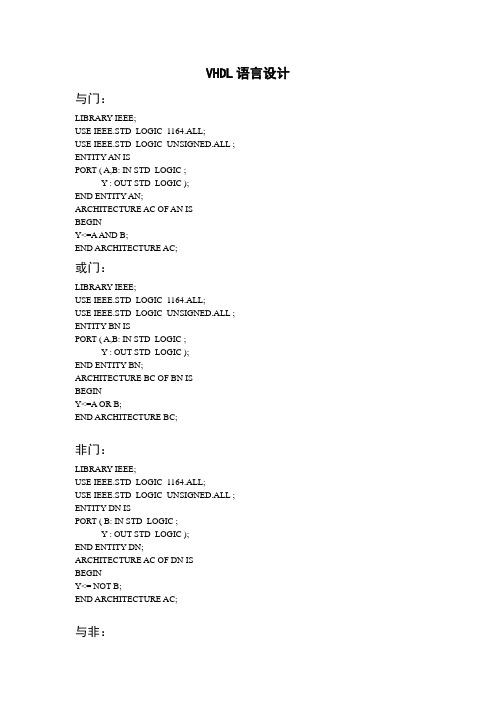

VHDL编写的基本元件程序

VHDL语言设计与门:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL ;ENTITY AN ISPORT ( A,B: IN STD_LOGIC ;Y : OUT STD_LOGIC );END ENTITY AN;ARCHITECTURE AC OF AN ISBEGINY<=A AND B;END ARCHITECTURE AC;或门:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL ;ENTITY BN ISPORT ( A,B: IN STD_LOGIC ;Y : OUT STD_LOGIC );END ENTITY BN;ARCHITECTURE BC OF BN ISBEGINY<=A OR B;END ARCHITECTURE BC;非门:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL ;ENTITY DN ISPORT ( B: IN STD_LOGIC ;Y : OUT STD_LOGIC );END ENTITY DN;ARCHITECTURE AC OF DN ISBEGINY<= NOT B;END ARCHITECTURE AC;与非:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL ; ENTITY CN ISPORT ( A,B: IN STD_LOGIC ;Y : OUT STD_LOGIC );END ENTITY CN;ARCHITECTURE AC OF CN ISBEGINY<=A NAND B;END ARCHITECTURE AC;或非:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL ; ENTITY HF ISPORT ( A,B: IN STD_LOGIC ;Y : OUT STD_LOGIC );END ENTITY HF; ARCHITECTURE AC OF HF ISBEGINY<=A NOR B;END ARCHITECTURE AC;异或:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL ; ENTITY FN ISPORT ( A,B: IN STD_LOGIC ;Y : OUT STD_LOGIC );END ENTITY FN;ARCHITECTURE AC OF FN ISBEGINY<=A XOR B;END ARCHITECTURE AC;同或:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL ;ENTITY EN ISPORT ( A,B: IN STD_LOGIC ;Y : OUT STD_LOGIC );END ENTITY EN;ARCHITECTURE AC OF EN ISBEGINY<=A XNOR B;END ARCHITECTURE AC;三线——八线译码器:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL ;ENTITY GN ISPORT ( A,B,C: IN STD_LOGIC ;Y0,Y1,Y2,Y3,Y4,Y5,Y6,Y7 : OUT STD_LOGIC ); END ENTITY GN;ARCHITECTURE DC OF GN ISBEGINY0<= NOT A AND NOT B AND NOT C;Y1<= NOT A AND NOT B AND C;Y2<= NOT A AND B AND NOT C;Y3<= NOT A AND B AND C;Y4<= A AND NOT B AND NOT C;Y5<= A AND NOT B AND C;Y6<= A AND B AND NOT C;Y7<= A AND B AND C;END ARCHITECTURE DC;八选一数据选择器:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL ;ENTITY H1N ISPORT ( A,B,C,D,E,F,G,H: IN STD_LOGIC ;Y1,Y2,Y3 : OUT STD_LOGIC );END ENTITY H1N;ARCHITECTURE AC OF H1N ISBEGINY1<= A OR B OR C OR D;Y2<= E OR F OR B OR A;Y3<= G OR E OR C OR A; END ARCHITECTURE AC;。

VHDL语言入门教程

VHDL语言入门教程VHDL是一种硬件描述语言,主要用于设计数字电路和系统。

它是由美国国防部门于1980年代初开发的,目的是为了改进电子设计自动化(EDA)工具的开发效率和设计文档的可重复性。

VHDL广泛应用于数字信号处理(DSP)、嵌入式系统、通信系统和各种ASIC(专用集成电路)和FPGA(现场可编程门阵列)的设计。

本教程将介绍VHDL的基础知识,包括语法、数据类型和常见的建模技术。

一、VHDL的语法VHDL的语法由标识符、关键字、运算符和分隔符组成。

其中,标识符用于给变量、信号和实体命名,关键字用于定义语言特定的操作,运算符用于数学和逻辑运算,分隔符用于分隔语句。

VHDL中的代码以一个实体(entity)的声明开始,然后是体(architecture)的声明,最后是信号声明和进程(process)的描述。

以下是一个简单的例子:```vhdlentity AND_gate isportA, B: in std_logic;C: out std_logicend entity AND_gate;architecture Behavior of AND_gate isbeginC <= A and B;end architecture Behavior;```在这个例子中,我们声明了一个名为AND_gate的实体,它有两个输入信号A和B,一个输出信号C。

然后我们定义了一个名为Behavior的体,它描述了AND门的行为:C等于A与B的逻辑与运算结果。

二、VHDL的数据类型VHDL支持许多数据类型,包括标量类型、数据类型、自定义类型和引用类型。

标量类型包括bit、bit_vector、integer、real、std_logic和std_ulogic等。

其中,bit_vector是一组连续的位,std_logic和std_ulogic用于表示单个信号。

数据类型是由标量类型和数组类型组成的。

数组类型可以是一维、二维或更高维的,用于存储多个数据。

16位ALUVHDL实现源程序

思考题:编写十六位运算器的VHDL程序——MYALU实验任务:用CPT16 的扩展实验板上的开关K3 、K2、K1、K0做为输入、八段数码管LED0..LED3做为输出,用VHDL语言编写程序,下载到EP1C6中,实现十六位模型机的MY ALU 功能见下表。

实验说明:在MY ALU.VHD程序设计中,定义A 为16位累加器,其值由K3 、K2 两组开关输入;W 为16位工作寄存器,其值由K1、K0 两组开关共输入;S2、S1、S0 为运算功能控制位,接在K4开关的第2、1、0个开关上,根据S2、S1、S0 的不同,MY ALU 实现不同功能D为运算结果输出,显示在四位八段管LED3..LED0上;CIn 为进位输入,由K4 开关组的第3 个开关输入;COut 为进位输出,用发光二极管L0 显示其状态。

逻辑功能:library ieee; ------库程序包调用use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity asanxia is ------实体:电路外观配置port(inA : IN UNSIGNED(15 DOWNTO 0); -- K3, K2 inAinW : IN UNSIGNED(15 DOWNTO 0); -- K1, K0 inWoutLED : OUT STD_LOGIC_VECTOR(15 DOWNTO 0); -- LED3~LED0 outLEDinC : IN STD_LOGIC_VECTOR(2 DOWNTO 0); --Control Input inCCin:IN STD_LOGIC; --C Input k4.3 CinCout: OUT STD_LOGIC -- C Output L0 Cout);end asanxia;architecture arch of asanxia is ------结构体:电路功能描述--中间变量signal c:std_logic_vector(15 downto 0); --暂存进位信号signal q:UNSIGNED(15 downto 0); --暂存各位数值beginprocess(inC,inA,inW,Cin)begincase inC iswhen "000"=> ------加法:A+B ;A+B+1q(0)<=inA(0)xor inW(0)xor Cin;c(0)<=(inA(0) and inW(0))or (inW(0)and Cin)or (inA(0)and Cin);--inA(0),inW(0),Cin有两个以上为1即产生进位。

VHDL程序设计

VLSI电路设计课设VHDL语言基础胡小玲主要内容z硬件描述语言简介z VHDL基本结构z VHDL数据和表达式z VHDL描述语句z系统仿真z综合硬件描述语言HDLz Hardware Description Language广义地说,描述电子实体的语言:逻辑图,电路图。

硬件描述语言能在高层设计阶段描述硬件。

z起源:大规模电路的出现,使得逻辑图、布尔方程不太适用,需要在更高层次上描述系统;出现多种HDL语言,为便于信息交换和维护,出现工业标准。

•分类:VHDL、Verilog HDL等。

硬件描述语言HDLz HDL语言的特点–用HDL语言设计电路能够获得非常抽象的描述–用HDL描述电路设计,在设计的前期就可以完成电路功能级的验证–用HDL设计电路类似于计算机编程。

带有注解的文字描述更有利于电路的开发与调试z能提供HDL模拟器的公司:Cadence、Altera、Mentor Graphics、Synopsys等大型EDA公司和专门公司学习HDL的几点重要提示了解HDL的可综合性问题HDL有两种用途:系统仿真和硬件实现。

如果程序只用于仿真,那么几乎所有的语法和编程方法都可以使用。

但如果我们的程序是用于硬件实现(例如:用于FPGA设计),那么我们就必须保证程序“可综合”(程序的功能可以用硬件电路实现)。

不可综合的HDL语句在软件综合时将被忽略或者报错。

我们应当牢记一点:“所有的HDL描述都可以用于仿真,但不是所有的HDL描述都能用硬件实现。

”用硬件电路设计思想来编写HDL学好HDL的关键是充分理解HDL语句和硬件电路的关系。

编写HDL,就是在描述一个电路,我们写完一段程序以后,应当对生成的电路有一些大体上的了解,而不能用纯软件的设计思路来编写硬件描述语言。

要做到这一点,需要我们多实践,多思考,多总结。

语法掌握贵在精,不在多30%的基本HDL语句就可以完成95%以上的电路设计,很多生僻的语句并不能被所有的综合软件所支持,在程序移植或者更换软件平台时,容易产生兼容性问题,也不利于其他人阅读和修改。

基于VHDL的多功能调制解调器的设计

基于VHDL的多功能调制解调器的设计VHDL(Very High Speed Integrated Circuit HardwareDescription Language)是一种硬件描述语言,广泛用于在数字电路领域中进行设计和仿真。

本文将介绍基于VHDL的多功能调制解调器的设计。

首先,我们需要了解调制解调器的基本原理。

调制解调器通常用于将数字信号转换为模拟信号(调制),或将模拟信号转换为数字信号(解调)。

在设计多功能调制解调器时,我们需要实现不同的调制和解调技术,使其适用于多种信号传输标准和通信协议。

下面,我们将使用VHDL进行多功能调制解调器的设计。

1. 模块分析:首先,我们需要定义各个子模块,例如信号发生器(Signal Generator)、调制器(Modulator)、解调器(Demodulator)等。

2.信号发生器:信号发生器用于产生调制信号。

这可以通过基带信号(例如音频信号)经过数字调制技术(如调幅、调频)生成模拟信号。

我们可以使用VHDL编写一个信号发生器模块,输入基带信号和调制方式,输出模拟信号。

3.调制器:调制器将数字信号转换为模拟信号。

根据不同的调制方式(如调幅、调频、相位调制等),我们可以使用不同的VHDL代码编写调制器子模块。

4.解调器:解调器将模拟信号转换为数字信号。

根据不同的解调方式,我们可以使用不同的VHDL代码编写解调器子模块。

5.信号处理:在多功能调制解调器中,信号处理是非常重要的一步。

在这个模块中,我们可以对接收到的信号进行滤波、抗干扰和误码纠正等处理。

6.通信接口:多功能调制解调器需要与其他设备进行通信,我们可以使用串口、并口、以太网端口等进行通信接口的设计。

这需要使用VHDL编写接口模块和协议。

7.整体系统:在设计完成各个子模块后,我们需要将它们集成到一个整体系统中。

通过使用VHDL编写一个顶层模块,将各个子模块连接起来,并将输入和输出端口进行适当的设置。

交织器VHDL源程序

交织器VHDL源程序LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.all;USE IEEE.STD_LOGIC_ARITH.all;ENTITY countern ISGENERIC(N:INTEGER:=16);PORT(clr,ena,clk :in STD_LOGIC;q: BUFFER INTEGER RANGE 0 TO n-1 ; --输出顺序地址cout: OUT STD_LOGIC ); --进位信号END countern; ARCHITECTURE rtl OF countern ISBEGINPROCESS(clk,clr)BEGINIF clr='1' THENq<=0;ELSEIF clk='1' AND clk'EVENT THENIF ena='1' THENIF q=q'high THENq<=0;ELSEq<=q+1;END IF;END IF;END IF;END IF;IF q=q'high THENcout<='1';ELSEcout<='0';END IF;END PROCESS;END rtl;--选择器模块LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY mux2 ISGENERIC(N:INTEGER:=16);port(d0: IN STD_LOGIC_VECTOR(7 DOWNTO 0); d1:IN INTEGER RANGE 0 TO N-1;SEL:IN STD_LOGIC;yout:OUT STD_LOGIC_VECTOR(7 DOWNTO 0) END mux2;ARCHITECTURE if_march OF mux2 isBEGINPROCESS(d0,d1,sel)BEGINIF(sel='1')THENyout<=CONV_STD_LOGIC_VECTOR(d1,8); ELSEyout<=d0;END IF;END PROCESS;END if_march;--只读存储器ROM模块LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY rom_16_8 isGENERIC(N:INTEGER:=16);PORT( addr : IN INTEGER RANGE 0 TO N-1;clk: IN STD_LOGIC;data: OUT STD_LOGIC_VECTOR(7 DOWNTO 0)); END rom_16_8;ARCHITECTURE rtl OF rom_16_8 ISSUBTYPE rom_word IS STD_LOGIC_VECTOR(7 DOWNTO 0); TYPE rom_table IS ARRAY(0 TO 15)OF rom_word; CONSTANt rom:rom_table:=rom_table'(rom_word'("00000000"),rom_word'("00000100"),rom_word'("00001000"),rom_word'("00001100"),rom_word'("00000001"),rom_word'("00000101"),rom_word'("00001001"),rom_word'("00001101"),rom_word'("00000010"),rom_word'("00000110"),rom_word'("00001010"),rom_word'("00001110"),rom_word'("00000011"),rom_word'("00000111"),rom_word'("00001011"),rom_word'("00001111"));PROCESS(clk)BEGINIF clk'EVENT AND clk='1' THENdata<=rom(addr);END IF;END PROCESS;END rtl;--读写存储器RAM模块LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY ram_16_8 ISPORT(ad:IN STD_LOGIC_VECTOR(7 DOWNTO 0); --地址线,用来选择读和写单元地址clk:IN STD_LOGIC;di:IN STD_LOGIC_VECTOR(7 DOWNTO 0); --输入数据do:OUT STD_LOGIC_VECTOR(7 DOWNTO 0); --输出数据wr_en: IN STD_LOGIC:='0'; --写信号rd_en: IN STD_LOGIC:='0'); --读信号END ram_16_8;ARCHITECTURE rtl OF ram_16_8 ISSUBTYPE ram_word IS STD_LOGIC_VECTOR(7 DOWNTO 0);TYPE ram_table IS ARRAY(0 TO 15) OF ram_word;SIGNAL ram:ram_table:=ram_table'(ram_word'("00000000"),ram_word'("00000000"),ram_word'("00000000"),ram_word'("00000000"),ram_word'("00000000"),ram_word'("00000000"),ram_word'("00000000"),ram_word'("00000000"),ram_word'("00000000"),ram_word'("00000000"),ram_word'("00000000"),ram_word'("00000000"),ram_word'("00000000"),ram_word'("00000000"),ram_word'("00000000"),ram_word'("00000000"));BEGINPROCESS(clk)BEGINIF clk'EVENT AND clk='1' THENIF rd_en='1' THENdo<=ram(CONV_INTEGER(ad));END IF;IF wr_en='1' THENram(CONV_INTEGER(ad))<=di;END IF;END IF;END PROCESS;END rtl;--交织器顶层模块LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;ENTITY top ISGENERIC(N:INTEGER:=16);PORT (clk: IN STD_LOGIC;clr: IN STD_LOGIC;ena: IN STD_LOGIC;di: IN STD_LOGIC_VECTOR(7 DOWNTO 0); do: OUT STD_LOGIC_VECTOR(7 DOWNTO 0);); END top;ARCHITECTURE rtl OF top ISCOMPONENT counternPORT(clr,ena,clk :IN STD_LOGIC;q: BUFFER INTEGER RANGE 0 TO N-1 :=0;cout: OUT STD_LOGIC );END COMPONENT;COMPONENT ROM_16_8PORT(addr : IN INTEGER RANGE 0 TO N-1;clk: IN STD_LOGIC;data: OUT STD_LOGIC_VECTOR(7 DOWNTO 0)); END COMPONENT;COMPONENT mux2PORT( d0: IN STD_LOGIC_VECTOR(7 DOWNTO 0);d1:IN INTEGER RANGE 0 TO N-1;sel:IN STD_LOGIC;yout:OUT STD_LOGIC_VECTOR(7 DOWNTO 0));END COMPONENT;COMPONENT ram_16_8PORT(ad:IN STD_LOGIC_VECTOR(7 DOWNTO 0);clk:IN STD_LOGIC;di: IN STD_LOGIC_VECTOR(7 DOWNTO 0);do:OUT STD_LOGIC_VECTOR(7 DOWNTO 0); wr_en: IN STD_LOGIC:='0';rd_en: IN STD_LOGIC:='0');END COMPONENT;SIGNAL qs:INTEGER RANGE 0 TO N-1:=0;SIGNAL ds:STD_LOGIC_VECTOR(7 DOWNTO 0); SIGNAL ys:STD_LOGIC_VECTOR(7 DOWNTO 0); SIGNAL cout: STD_LOGIC;SIGNAL wr_en:STD_LOGIC:='0';SIGNAL rd_en:STD_LOGIC:='0';SIGNAL sel: STD_LOGIC:='1';ct:counternPORT MAP(clk=>clk,clr=>clr,ena=>ena,cout=>cout,q=>qs);rom:ROM_16_8PORT MAP(clk=>clk,addr=>qs,data=>ds);mux:mux2PORT MAP(d1=>qs,d0=>ds,sel=>sel,yout=>ys);ram:ram_16_8PORT MAP(clk=>clk,do=>do,di=>di,wr_en=>wr_en,rd_en=>rd_en,ad=>ys);PROCESS(cout)BEGINIF cout'EVENT AND cout='0' THEN sel<=NOT sel;END IF;IF sel='1' THENwr_en<='1';rd_en<='1';END IF;END PROCESS; END rtl;。

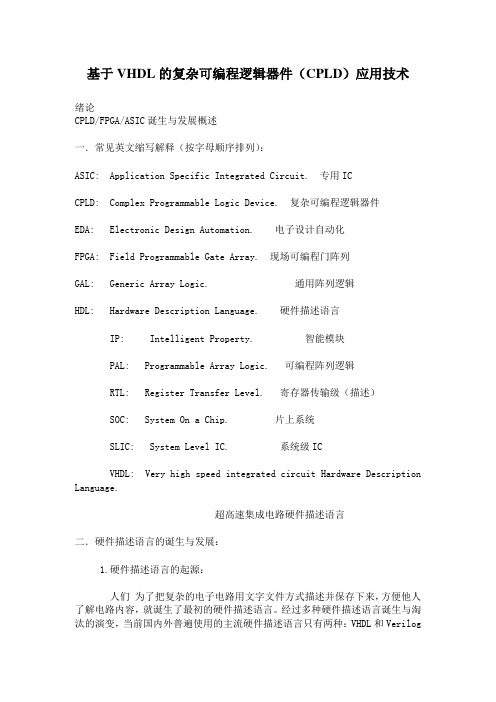

基于vhdl的复杂可编程逻辑器件(cpld)应用技术

基于VHDL的复杂可编程逻辑器件(CPLD)应用技术绪论CPLD/FPGA/ASIC诞生与发展概述一.常见英文缩写解释(按字母顺序排列):ASIC: Application Specific Integrated Circuit. 专用ICCPLD: Complex Programmable Logic Device. 复杂可编程逻辑器件EDA: Electronic Design Automation. 电子设计自动化FPGA: Field Programmable Gate Array. 现场可编程门阵列GAL: Generic Array Logic. 通用阵列逻辑HDL: Hardware Description Language. 硬件描述语言IP: Intelligent Property. 智能模块PAL: Programmable Array Logic. 可编程阵列逻辑RTL: Register Transfer Level. 寄存器传输级(描述)SOC: System On a Chip. 片上系统SLIC: System Level IC. 系统级ICVHDL: Very high speed integrated circuit Hardware Description Language.超高速集成电路硬件描述语言二.硬件描述语言的诞生与发展:1.硬件描述语言的起源:人们为了把复杂的电子电路用文字文件方式描述并保存下来,方便他人了解电路内容,就诞生了最初的硬件描述语言。

经过多种硬件描述语言诞生与淘汰的演变,当前国内外普遍使用的主流硬件描述语言只有两种:VHDL和VerilogHDL。

还有ABEL和AHDL等。

2.VHDL :以ADA语言为基础,由美国国防高级研究计划局(DARPA)开发。

1985年完成第一版,1987年成为IEEE标准(IEEE1076),1993年增修为IEEE1164标准并使用至今。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

--计数器模块LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.all;USE IEEE.STD_LOGIC_ARITH.all;ENTITY countern ISGENERIC(N:INTEGER:=16);PORT(clr,ena,clk :in STD_LOGIC;q: BUFFER INTEGER RANGE 0 TO n-1 ; --输出顺序地址cout: OUT STD_LOGIC ); --进位信号END countern;ARCHITECTURE rtl OF countern ISBEGINPROCESS(clk,clr)BEGINIF clr='1' THENq<=0;ELSEIF clk='1' AND clk'EVENT THENIF ena='1' THENIF q=q'high THENq<=0;ELSEq<=q+1;END IF;END IF;END IF;END IF;IF q=q'high THENcout<='1';ELSEcout<='0';END IF;END PROCESS;END rtl;--选择器模块LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY mux2 ISGENERIC(N:INTEGER:=16);port(d0: IN STD_LOGIC_VECTOR(7 DOWNTO 0);d1:IN INTEGER RANGE 0 TO N-1;SEL:IN STD_LOGIC;yout:OUT STD_LOGIC_VECTOR(7 DOWNTO 0)END mux2;ARCHITECTURE if_march OF mux2 isBEGINPROCESS(d0,d1,sel)BEGINIF(sel='1')THENyout<=CONV_STD_LOGIC_VECTOR(d1,8);ELSEyout<=d0;END IF;END PROCESS;END if_march;--只读存储器ROM模块LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY rom_16_8 isGENERIC(N:INTEGER:=16);PORT( addr : IN INTEGER RANGE 0 TO N-1;clk: IN STD_LOGIC;data: OUT STD_LOGIC_VECTOR(7 DOWNTO 0)); END rom_16_8;ARCHITECTURE rtl OF rom_16_8 ISSUBTYPE rom_word IS STD_LOGIC_VECTOR(7 DOWNTO 0); TYPE rom_table IS ARRAY(0 TO 15)OF rom_word; CONSTANt rom:rom_table:=rom_table'(rom_word'("00000000"),rom_word'("00000100"),rom_word'("00001000"),rom_word'("00001100"),rom_word'("00000001"),rom_word'("00000101"),rom_word'("00001001"),rom_word'("00001101"),rom_word'("00000010"),rom_word'("00000110"),rom_word'("00001010"),rom_word'("00001110"),rom_word'("00000011"),rom_word'("00000111"),rom_word'("00001011"),rom_word'("00001111"));PROCESS(clk)BEGINIF clk'EVENT AND clk='1' THENdata<=rom(addr);END IF;END PROCESS;END rtl;--读写存储器RAM模块LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY ram_16_8 ISPORT(ad:IN STD_LOGIC_VECTOR(7 DOWNTO 0); --地址线,用来选择读和写单元地址clk:IN STD_LOGIC;di:IN STD_LOGIC_VECTOR(7 DOWNTO 0); --输入数据do:OUT STD_LOGIC_VECTOR(7 DOWNTO 0); --输出数据wr_en: IN STD_LOGIC:='0'; --写信号rd_en: IN STD_LOGIC:='0'); --读信号END ram_16_8;ARCHITECTURE rtl OF ram_16_8 ISSUBTYPE ram_word IS STD_LOGIC_VECTOR(7 DOWNTO 0);TYPE ram_table IS ARRAY(0 TO 15) OF ram_word;SIGNAL ram:ram_table:=ram_table'(ram_word'("00000000"),ram_word'("00000000"),ram_word'("00000000"),ram_word'("00000000"),ram_word'("00000000"),ram_word'("00000000"),ram_word'("00000000"),ram_word'("00000000"),ram_word'("00000000"),ram_word'("00000000"),ram_word'("00000000"),ram_word'("00000000"),ram_word'("00000000"),ram_word'("00000000"),ram_word'("00000000"),ram_word'("00000000"));BEGINPROCESS(clk)BEGINIF clk'EVENT AND clk='1' THENIF rd_en='1' THENdo<=ram(CONV_INTEGER(ad));END IF;IF wr_en='1' THENram(CONV_INTEGER(ad))<=di;END IF;END IF;END PROCESS;END rtl;--解交织器顶层模块LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;ENTITY jtop ISGENERIC(N:INTEGER:=16);PORT (clk: IN STD_LOGIC;clr: IN STD_LOGIC;ena: IN STD_LOGIC;do: OUT STD_LOGIC_VECTOR(7 DOWNTO 0);di: IN STD_LOGIC_VECTOR(7 DOWNTO 0));END jtop;ARCHITECTURE rtl OF jtop ISCOMPONENT counternPORT(clr,ena,clk :IN STD_LOGIC;q: BUFFER INTEGER RANGE 0 TO N-1 :=0;cout: OUT STD_LOGIC );END component;COMPONENT ROM_16_8PORT( addr : IN INTEGER RANGE 0 TO N-1;clk: IN STD_LOGIC;data: OUT STD_LOGIC_VECTOR(7 DOWNTO 0)); END COMPONENT;COMPONENT mux2PORT( d0: IN STD_LOGIC_VECTOR(7 DOWNTO 0);d1:IN INTEGER RANGE 0 TO N-1;sel:IN STD_LOGIC;yout:OUT STD_LOGIC_VECTOR(7 DOWNTO 0)); END COMPONENT;COMPONENT ram_16_8PORT(ad:IN STD_LOGIC_VECTOR(7 DOWNTO 0);clk:IN STD_LOGIC;di: IN STD_LOGIC_VECTOR(7 DOWNTO 0);do:OUT STD_LOGIC_VECTOR(7 DOWNTO 0);wr_en: IN STD_LOGIC:='0';rd_en: IN STD_LOGIC:='0');END COMPONENT;SIGNAL qs:INTEGER RANGE 0 TO N-1:=0;SIGNAL ds:STD_LOGIC_VECTOR(7 DOWNTO 0); SIGNAL ys:STD_LOGIC_VECTOR(7 DOWNTO 0); SIGNAL cout: STD_LOGIC;SIGNAL wr_en:STD_LOGIC:='0';SIGNAL rd_en:STD_LOGIC:='0';SIGNAL sel: STD_LOGIC:='0';BEGINct:counternPORT MAP(clk=>clk,clr=>clr,ena=>ena,cout=>cout,q=>qs);rom:ROM_16_8PORT MAP(clk=>clk,addr=>qs,data=>ds);mux:mux2PORT MAP(d1=>qs,d0=>ds,sel=>sel,yout=>ys);ram:ram_16_8PORT MAP(clk=>clk,do=>do,di=>di,wr_en=>wr_en,rd_en=>rd_en,ad=>ys);PROCESS(cout)BEGINIF cout'EVENT AND cout='0' THENsel<=NOT sel;END IF;IF sel='0' THENwr_en<='1';ELSErd_en<='1';END IF; END PROCESS; END rtl;。