基于dspf2812的交通灯设计

DSP 课程设计 交通灯的控制与实现

设计结果部分截图

2.6心得体会

两周的课程设计结束了,在这次的课程设计中不仅检验了我所学习的知识,也培养了我如何去把握一件事情,如何去做一件事情,又如何完成一件事情。在设计过程中,和同学们相互探讨,相互学习。在此次的课程设计中,主要资料的查阅和对电路图的总体设计,对电路的设计包括绘制电路原理图。由于平时在对本课程的学习中,没有注重系统的设计,故在设计电路原理图的过程中也遇到了各种各样的问题。但是,这些问题在跟同组的同学讨论和向老师请教后也得到了解决。由此可以得出,我对本门课程的掌握还是很不好,动手的能力还是很欠缺的。在今后的学习过程中不仅要注意对理念知识的掌握,而且还要培养自己的对手操作能力。最后在老师的辛勤的指导下,终于迎刃而解,终于觉得平时所学的知识有了实用的价值,达到了理论与实际相结合的目的,不仅学到了不少知识,而且锻炼了自己的能力,使自己对以后的路有了更加清楚的认识,同时,对未来有了更多的信心。最后,对给过我帮助的所有同学和各位指导老师再次表示忠心的感谢!

};

void main(void)

{

int nWork1,nWork2,nWork3,nWork4,k;

int nNowStatus,nOldStatus,nOldTimeCount,nSaveTimeCount,nSaveStatus;

unsigned int nScanCode;

nTimeCount=0; bHold=0;

void Delay(unsigned int nTime);

void SetLEDArray1(int nNumber);//修改显示内容

dsp课程设计2812流水灯

dsp课程设计2812流水灯一、教学目标本课程的教学目标是使学生掌握DSP 2812流水灯的基本原理和实现方法。

具体包括以下三个方面:1.知识目标:使学生了解DSP 2812的基本结构和工作原理,掌握流水灯的硬件设计和软件编程方法。

2.技能目标:培养学生具备使用DSP 2812开发流水灯项目的能力,能够独立完成硬件电路设计和软件编程。

3.情感态度价值观目标:培养学生对电子技术的兴趣和热情,提高他们解决实际问题的能力和创新精神。

二、教学内容本课程的教学内容主要包括以下几个部分:1.DSP 2812的基本结构和工作原理:包括CPU、存储器、外围接口等组成部分,以及指令系统和工作模式。

2.流水灯的硬件设计:包括LED灯阵的设计、驱动电路的设计、时钟电路的设计等。

3.流水灯的软件编程:包括初始化程序、定时器程序、PWM控制程序等。

三、教学方法为了达到本课程的教学目标,我们将采用以下几种教学方法:1.讲授法:用于讲解DSP 2812的基本原理和流水灯的硬件设计。

2.讨论法:用于讨论流水灯的软件编程方法和实际应用。

3.实验法:让学生亲自动手进行硬件电路搭建和软件编程,增强实践能力。

四、教学资源为了支持本课程的教学内容和教学方法,我们将准备以下教学资源:1.教材:《DSP 2812原理与应用》。

2.参考书:包括DSP 2812的数据手册、硬件设计手册等。

3.多媒体资料:包括教学PPT、视频教程等。

4.实验设备:DSP 2812开发板、LED灯阵、驱动电路等。

五、教学评估为了全面、客观地评估学生在课程中的学习成果,我们将采取以下评估方式:1.平时表现:通过学生在课堂上的参与度、提问回答、小组讨论等表现来评估。

2.作业:布置与课程内容相关的编程练习和实验报告,通过学生的完成质量来评估。

3.考试:包括期中考试和期末考试,内容涵盖课程的全部知识点,以笔试形式进行。

4.项目演示:学生需要设计和实现一个DSP 2812流水灯项目,通过项目演示和报告来评估。

dsp2812流水灯课程设计

dsp2812流水灯课程设计一、课程目标知识目标:1. 理解DSP2812的基本原理和功能特点;2. 掌握流水灯的电路设计与程序编写方法;3. 学会运用定时器、中断等资源实现流水灯效果;4. 了解嵌入式系统在实际应用中的优势。

技能目标:1. 能够独立设计并搭建流水灯电路;2. 能够编写并调试DSP2812流水灯程序;3. 能够运用所学知识解决实际应用问题;4. 提高动手实践能力和团队协作能力。

情感态度价值观目标:1. 培养学生对电子技术的兴趣,激发学习热情;2. 培养学生的创新意识和动手能力,提高自信心;3. 培养学生良好的团队合作精神,增强沟通能力;4. 引导学生关注社会发展,认识科技对生活的改变。

分析课程性质、学生特点和教学要求,本课程目标旨在使学生通过学习DSP2812流水灯课程,掌握嵌入式系统的基础知识和应用技能,培养实际操作能力,同时注重培养学生的创新意识和团队协作能力,为后续学习打下坚实基础。

课程目标具体、可衡量,便于教师进行教学设计和评估。

二、教学内容1. DSP2812基本原理与功能特点:介绍DSP2812芯片的基本结构、性能参数和应用领域,帮助学生了解DSP芯片的内部组成和工作原理。

- 教材章节:第1章 嵌入式系统概述2. 流水灯电路设计与搭建:讲解流水灯电路原理,指导学生进行电路设计和搭建,培养学生的动手实践能力。

- 教材章节:第2章 嵌入式系统硬件设计3. DSP2812程序编写与调试:学习DSP2812的程序编写方法和调试技巧,重点掌握定时器、中断等资源的运用。

- 教材章节:第3章 嵌入式系统软件开发4. 流水灯程序设计与实现:结合所学知识,编写并调试流水灯程序,实现流水灯效果。

- 教材章节:第4章 嵌入式系统项目实践5. 嵌入式系统应用案例分析:分析实际应用案例,让学生了解嵌入式系统在实际项目中的应用和优势。

- 教材章节:第5章 嵌入式系统应用案例教学内容安排和进度:1. 第1周:DSP2812基本原理与功能特点;2. 第2周:流水灯电路设计与搭建;3. 第3周:DSP2812程序编写与调试;4. 第4周:流水灯程序设计与实现;5. 第5周:嵌入式系统应用案例分析。

DSP红绿灯课程设计2812

DSP红绿灯课程设计2812一、教学目标本课程旨在通过DSP红绿灯项目的设计与实现,让学生掌握数字信号处理(DSP)的基本原理和技能,培养学生的实际工程能力和团队协作精神。

具体的教学目标如下:1.理解DSP的基本概念和原理。

2.掌握DSP芯片的结构和编程方法。

3.学习DSP红绿灯控制系统的原理和设计方法。

4.能够使用DSP芯片进行程序设计和调试。

5.能够设计和实现简单的DSP红绿灯控制系统。

6.培养学生的团队协作和沟通能力。

情感态度价值观目标:1.培养学生的创新意识和解决问题的能力。

2.培养学生对交通控制系统的兴趣和责任感。

3.培养学生的团队合作和积极进取的精神。

二、教学内容本课程的教学内容主要包括DSP的基本原理、DSP芯片的结构和编程方法、DSP红绿灯控制系统的原理和设计方法。

具体的教学大纲如下:1.引言:介绍DSP红绿灯控制系统的基本概念和应用背景。

2.DSP基本原理:讲解DSP的基本原理和数字信号处理的基本概念。

3.DSP芯片结构:介绍DSP芯片的结构和功能,包括中央处理器、存储器和接口等。

4.DSP编程方法:讲解DSP的编程方法和编程语言。

5.DSP红绿灯控制系统设计:介绍DSP红绿灯控制系统的原理和设计方法,包括控制算法、硬件设计和软件编程等。

6.项目实践:学生分组进行DSP红绿灯项目的设计和实现。

三、教学方法为了激发学生的学习兴趣和主动性,本课程将采用多种教学方法,包括讲授法、讨论法、案例分析法和实验法等。

1.讲授法:通过讲解DSP的基本原理和概念,让学生掌握基本知识。

2.讨论法:通过小组讨论和报告,培养学生的思考和表达能力。

3.案例分析法:通过分析实际案例,让学生了解DSP红绿灯控制系统的应用和设计方法。

4.实验法:通过项目实践,让学生亲手进行DSP红绿灯系统的设计和实现,提高学生的实际工程能力。

四、教学资源为了支持教学内容和教学方法的实施,我们将选择和准备适当的教学资源,包括教材、参考书、多媒体资料和实验设备等。

基于DSP的交通灯控制系统设计与实现

毕业设计(论文)基于DSP的交通灯控制系统设计与实现姓名系别、专业计算机科学系、通信工程导师姓名、职称完成时间目录摘要 (I)ABSTRACT ........................................................................................................ I I 1绪言 .. (1)2DSP与VISUAL C++技术简介 (1)2.1DSP概述 (1)2.2TMS320CF2812DSP结构以及组成 (3)2.3DSP的开发流程 (4)2.4C++语言 (6)3总体设计方案 (8)3.1系统功能描述 (9)3.2系统设计流程图 (10)3.3硬件设计 (11)3.4软件设计 (13)4系统测试 (20)4.1DSP系统测试环境 (20)4.2程序的调试 (23)4.3系统测试结果 (23)5总结 (26)参考文献 (27)致谢 .................................................................................. 错误!未定义书签。

摘要数字信号处理(Digital Signal Processing,DSP),是20世纪60年代前后发展并广泛应用于许多领域的学科。

20世纪70年代以来,随着大规模集成电路(LSI)和超大规模集成电路(VLSI)及微处理器技术的迅猛发展,数学信号处理的理论和技术得到长足发展,使其在数字通信、雷达、遥感、声纳、语音合成、图像处理、测量与控制、多媒体技术、生物医学工程及机器人等各个领域都得到广泛的应用。

交通拥堵在我国的大部分城市特别是大城市一直是一个难以解决的问题,也成为了困扰我国城市发展的一个大问题。

所以本设计是基于DSP原理设计的交通灯控制系统,采用的是软硬件结合的方法。

在硬件上利用TI公司德州仪器生产的用于工业自动控制TMSC320F2812系列的DSP芯片,四组发光二极管,在软件上使用CCS集成开发环境,在此环境中用C语言编写定时器程序来控制发光二极管的亮灭情况以达到模拟十字路口的交通灯,从而管理十字路口车辆的秩序,使交通畅通无阻。

DSPTMS320F2812实验讲义

目次第一章 (2)1.1 系统概述 (2)1.2 实验箱整体配置与特点 (2)1.3 实验箱功能实现 (4)第二章 (5)2.1 电源设计 (5)2.2 复位电路设计 (7)2.3 时钟电路设计 (9)第三章 (11)3.1 硬件仿真器的安装 (11)3.2 CCS软件设置与项目管理 (18)3.3 CCS常用工具与窗口 (33)第四章 (40)4.1 CCS入门实验(C语言的使用) (40)4.2 片上外设实验----定时器控制实验 (43)4.3 片上外设实验----A/D采集实验 (47)4.4 有限冲击响应滤波器(FIR)算法实验 (54)4.5 快速傅立叶变换(FFT)算法实验 (60)附录 (65)定时器工作寄存器 (67)AD转换功能寄存器 (70)第一章实验系统介绍1.1系统概述SEED-DTK(DSP Teaching Kit)是由合众达公司提供的一套可以满足大学本科、研究生和教师科研工作的综合实验设备,具有独特的多DSP结构、较强的DSP主板功能、丰富的外围实验电路、与教学内容紧密结合的实验例程。

下面主要介绍下SEED-DTK2812实验箱,它由SEED-DEC2812板卡以及SEED-DTK_MBoard构成:其中主控板是合众达公司生产的SEED-DEC2812,母板是由该公司生产的SEED-DTK_MBoard板卡。

此外,该款实验箱还可以配置DSK板卡、图像处理卡等多种子卡。

1.1.1 SEED-DTK2812实验箱实验例程■ SEED_DEC2812板卡实验例程S软件应用实验:介绍CCS的使用,编写简单的实验例程。

2.DSP片上资源应用实验本部分例程介绍的是DSP的片上资源。

3.SEED_DEC2812板卡应用实验SEED_DEC2812板卡与实验箱资源的应用实验。

包括:异步、同步串口通讯;扩展I/O口使用;AD/DA的使用。

4.算法实验包括FFT,滤波(FIR、IIR),卷积,自适应滤波器算法实验5.参考实验包括USB使用实验、自举程序的编写以及SEED_DEC2812板卡与SEED-DTK_MBoard板卡之间数据传递实验。

基于某DSP实现道路交通灯控制系统设计

1 引言 (1)2项目设计实现功能 (2)2.1交通灯控制要求 (2)2.2 液晶显示器控制 (3)3 项目实现方案 (3)3.1项目设计整体思路 (3)3.2设计原理 (5)3.2.1 CPU定时器原理 (5)3.2.2 DSP外设中断扩展模块 (6)3.2.3 发光二极原理 (6)3.2.4 TMS320F28x DSP 的I/O (7)3.2.5 液晶显示器控制原理 (8)4 程序设计 (8)4.1 程序总体设计 (8)4.2 程序编写(见附页) (9)5 心得体会 (9)附页 (10)基于DSP实现道路交通灯控制系统设计摘要:DSP数字信号处理,是一门涉及多学科而又广泛应用于许多领域的新兴学科。

随着计算机和信息技术的飞速发展,数字信号处理技术应运而生并得到迅速发展。

数字信号处理是一种通过使用数学技巧执行转换或提取信息,来处理现实信号的方法。

本次设计是基于dsp原理设计交通灯控制系统软硬件系统,利用发光二极管亮灭模拟交通信号,数码管倒计时时间,利用TMS320F2812 DSP片上定时器产生时钟计数,设计模拟实际生活中的十字路口交通灯。

关键字:DSP;TMS320F2812;发光二极管;交通灯;Abstract: DSP digital signal processing, is a multidisciplinary and widely applied in many fields of the emerging discipline. Along with the computer and the rapid development of information technology, digital signal processing technology to emerge as the times require and develop rapidly. Digital signal processing is through the use of a mathematical skills to perform the conversion or extraction of information, to deal with real signal method. The design is based on the principle of DSP design of traffic light control system software and hardware system, using light-emitting diodes to eliminate simulated traffic signal countdown time, digital tube, the use of TMS320F2812 DSP on-chip timer generates a clock counting, designed to simulate the actual life of the crossroads traffic lights.Keyword: DSP; TMS320F2812; light emitting diode; traffic lights;1 引言交通是经济、社会发展的基础性产业,是社会、经济活动中人流、物流、资金流和信息流的主要流动方式。

基于DSP设计的交通信号灯设计

目录1. 需求分析 (1)2. 设计准备 (1)2.1. 芯片选择 (1)2.2. 七段码译码器CD4511 (2)2.3. Protel 99 SE软件 (3)2.4. CCS软件 (3)3. 交通灯控制原理 (4)4. 程序流程设计 (5)5. 总体设计 (6)5.1. 硬件原理图 (7)5.2. 硬件设计 (7)5.3. 代码设计 (8)6. 测试结果及其分析 (16)7. 项目设计总结 (16)参考文献 (16)1.需求分析随着社会经济的发展,城市交通问题越来越引起人们的关注。

人、车、路三者关系的协调,已成为交通管理部门需要解决的重要问题之一。

城市交通控制系统是用于城市交通数据监测、交通信号灯控制与交通疏导的计算机综合管理系统,它是现代城市交通监控指挥系统中最重要的组成部分。

如何采用合适的控制方法,最大限嚏利用好耗费巨资修建的城市高速道路,缓解主干道与匝道、城区同周边地区的交通拥堵状况,越来越成为交通运输管理和城市规刘部门亟待解决的主要问题。

而DSP是伴随着微电子学、数字信号处理技术和计算机技术等学科的发展而产生的,是体现这三个学科综合科研成果的器件。

由于它特殊的结构设计,可以把数宁信号处理中的一些理论和算法实时实现,并逐步进入了控制器市场,而在计算机应用领域中得到了广泛的使用。

所以本文提出了基于DSP的交通灯综合控制系统的设计。

2.设计准备2.1.芯片选择本系统所采用的是TI公司的TMS320VC5509A,TMS320VC5509A是TI公司推出的定点数字信号处理器C5000系列中的一种,TMS320VC5509A通过增加乘累加MAC单元,增强了DSP的运算能力,而且性能更好,功耗更低,是目前TMS320家族中最省电的芯片。

该芯片上的资源有:16Mbitflash196k*16bitSRAM2500gateCPLD模块上留有JTAG插口,用户可以通过仿真器和CCS下载程序和进行实验;其特点:⑴其低功耗设计,比上一代C54XX器件功耗低30%左右;⑵处理速度更快,双核结构,处理速度400MIPS;⑶软件程序兼容C54XXDSP;⑷片内存贮空间128K×16Bit;⑸大容量SDRAM设计:4M×16Bit;⑹2路10bit片上A/D接口;⑺8Mbit扩展FLASH,存储大量固化程序和数据;⑻设计有用户可以测试指示灯;⑼DSP扩展总线,包括数据、地址、I/O、控制;⑽4组标准扩展连接器,为用户进行二次开发提供条件;⑾具有IEEE1149.1相兼容的逻辑扫描电路,该电路仅用于测试和仿真;+5V电源输入,内部+3.3V、+1.6V电源管理;⑿高保真语音接口设计,双路语音采集,每路48K/S;USB2.0接口设计;本实验实验使用实验箱上外围控制接口P0的GPIO(通用输入输出脚)来实现功能,同时使用U4四路用户可控状态开关来实现中断功能。

基于DSP的 交通灯

目录第1章设计目的及要求.............................................................................. - 1 -1.1 设计目的........................................................................................ - 1 -1.2 设计要求........................................................................................ - 1 -1.2.1 设计任务............................................................................ - 1 -1.2.2 设计要求............................................................................ - 2 -第2章设计原理和方案.............................................................................. - 3 -2.1 设计思路........................................................................................ - 3 -2.2 设计原理........................................................................................ - 3 -2.3 设计方案........................................................................................ - 4 -2.4 工作状态设计................................................................................ - 5 -第3章硬件设计.......................................................................................... - 7 -3.1 总体设计........................................................................................ - 7 -3.2 单元电路设计................................................................................ - 8 -第4章软件调试........................................................................................ - 11 -4.1 总体设计...................................................................................... - 11 -4.2 源程序........................................................................................... - 14 -第5章系统调试........................................................................................ - 14 -5.1 硬件调试...................................................................................... - 14 -5.1.1 电源调试.......................................................................... - 14 -5.1.2 Emulator调试................................................................. - 15 -5.2 软件调试...................................................................................... - 17 -5.2.1 软件设置.......................................................................... - 17 -5.2.2程序运行........................................................................... - 19 -5.3 系统联调...................................................................................... - 21 -第6章结论分析及体会............................................................................ - 22 -参考文献...................................................................................................... - 23 -附录 ........................................................................................................... - 24 -第1章设计目的及要求1.1 设计目的(1)练习自主独立的设计,实现理论和实践的统一,提高自我动手能力。

基于DSP的十字路口交通灯的设计

基于DSP的十字路口交通灯的设计摘要数字信号处理是把信号用数字或符号表示的序列,通过计算机或通用信号处理设备,用数字的数值方法处理(例如滤波、变换、压缩、增强、估计、识别等),以达到提取有用信息的目的。

DSP数字信号处理(Digital Signal Processing,简称DSP)是一门涉及许多学科而又广泛应用于许多领域的新兴学科。

20世纪60年代以来,随着计算机和信息技术的飞速发展,有力地推动和促进了DSP技术的发展进程。

本次设计是基于DSP原理设计交通灯控制系统软硬件系统,利用发光二级管亮灭模拟交通信号,数码管显示倒计时时间,利用TMS320VC5402 DSP片上定时器定时产生时钟计数,设计模拟实际生活中十字路口交通灯。

关键词:DSP;TMS320VC5402;交通灯控制;发光二极管;目录第一章背景知识概述 (3)1.1 交通灯背景概述 (3)第二章基于DSP的交通灯的设计原理 (4)2.1 课题设计内容 (4)2.2 课程设计要求 (4)2.3设计原理 (5)2.3.1 系统工作原理 (5)2.3.2 系统工作状态 (5)第三章课程设计总体方案 (7)3.1课程设计总体方案 (7)3.1.1 设计思路 (7)3.1.2 设计流程图 (8)第四章设计步骤及过程 (10)4.1 硬件的选择 (10)4.1.1主控制器的选择 (10)4.1.2 电压转换芯片的选择 (10)4.1.3 锁存器的选择 (11)4.1.4 译码器的选择 (11)4.1.5 数码显示输出模块 (12)4.1.6 指示灯输出模块 (14)4.2软件的使用 (16)4.2.1 CCS文件名介绍 (16)4.2.2 汇编源程序(.asm)格式 (17)4.2.3 COFF目标文件 (17)第五章心得体会 (17)参考文献 (18)附录 (19)第一章背景知识概述1.1 交通灯背景概述十字路口交通灯在我们的日常生活中随处可见,它为繁忙的道路交通及人们的安全提供了较好的保障。

dsp2812流水灯实验报告

dsp2812流水灯实验报告1.设计任务:1.1基于dsp2812的Led显示控制系统设计要求:(1)绘制系统框图(VISIO);(2)包括复位电路设计、JTAG接口设计、时钟电路设计、电源设计等,并且用Protel软件绘制原理图;(3)编写程序,实现流水灯;(4)系统理论分析和设计陈述;(5)设计过程、源代码和注释、设计说明书。

2.实验目的:⑴学习并了解DSP开发版的基本原理;⑵学习并了解dsp2812芯片的基本结构和原理;⑶熟悉流水灯的软件实现原理和硬件设计;⑷熟悉Emulator方式下的程序调试规程,并最终能够熟练掌握在DSP软硬件环境下的程序开发流程;能够对现有器件进行简单地编程,实现各种简单地显示控制。

3.设计内容:(1)使用Altium Designer软件绘制原理图。

(2)使用VISIO 软件绘制系统框图和软件流程图。

(3)使用CCStudio v3.3软件设计程序实现流水灯。

4.实验原理:4.1 DSP(2812)性能概述(1)F2812 DSP芯片采用高性能静态CMOS技术1 主频高达150MHz,每个时钟周期为6.67ns。

2采用低电压供电,当主频为135MHz时,内核电压为1.8V,主频150MHz时内核电压为1.9V,I/O引脚电压为3.3V。

(2)支持JTAG在线仿真接口(3)32位高性能处理器1 支持16bX16b和32bX32b的乘法加法运算。

2 支持16bX16b双乘法运算。

3 采用哈佛总线结构模式。

4 快速的中断响应和中断处理能力。

5 统一的存储设计模式。

6 兼容C/C++语言以及汇编语言。

(4) 片内存储空间1片内FLASH空间大小为128KX16b,分为4个8KX16b和6个16KX16b存储段。

2 OTP ROM空间大小1KX16b。

3 L0、L1两块4KX16b单地址寻址随机存储器(SARAM)。

4 H0:一块8KX16b随机存储器(SARAM)。

5 M0、M1:两块1KX16bSARAM。

基于dspf2812的交通灯设计

电子信息工程专业CDIO三级项目项目设说明书项目设计说明书(2011/2012学年第二学期)项目名称:DSP应用系统题目:DSPICETEK—f2812B控制交通灯专业班级:电子信息工程学生姓名:学号:指导教师:设计周数:2周设计成绩:2012年7月6日目录1、项目设计目的 (2)2、项目设计正文 (2)2.1硬件设计 (2)2.1.1总体方案设计 (2)2.1.2数码管驱动显示电路设计 (3)2.1.3交通灯亮灭控制电路设计 (3)2.2项目软件设计 (6)2.2.1软件系统分析 (6)2.2.2软件系统设计 (7)2.2.3软件系统实施 (7)2.2.4软件开发环境的使用 (8)3、项目设计总结 (10)4、参考文献 (10)5、附录: (11)1、项目设计目的本学期我们主要学习了DSP硬件方面的一些基本原理,对于如何通过软件来控制DSP从而实现我们最终的需求,还不是很了解。

本次设计的目的就是基于TMS320CF2812平台的进行C语言编程,了解软件编程开发的基本流程,以及软硬件是如何共同协调工作从而实现最终的控制的。

熟练掌握TMS320F2812控制交通灯方法,树立正确的设计思想提高分析问题与解决具体问题的能力。

并通过此次项目设计熟练软件CCS的操作和使用,能够实现程序的编译、运行以及烧写。

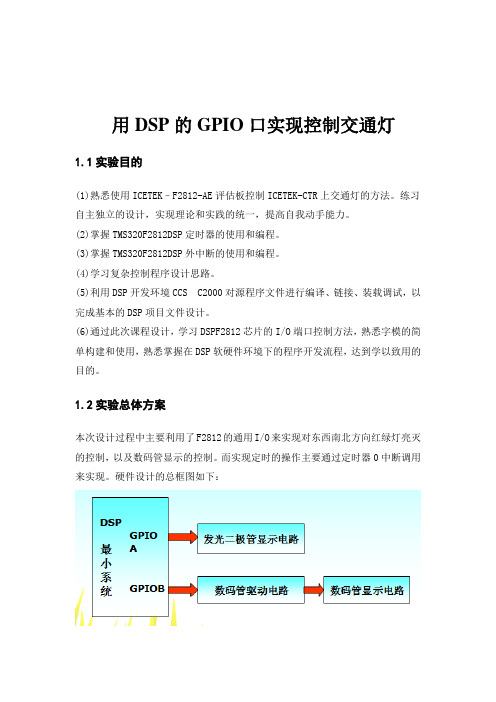

2、项目设计正文2.1硬件设计2.1.1总体方案设计本次设计过程中主要利用了F2812的通用I/O来实现对东西南北方向红绿黄灯亮灭的控制,以及数码管显示的控制。

而实现定时的操作主要通过通用定时器0的中断调用来实现。

硬件设计的总体框图如图1所示。

2.1.1.1F2812GPIO介绍TMS320F2812DSP有多达56个通用数字量输入输出端口(GPIO),其中绝大部分是通用I/O和专用功能复用引脚。

数字量I/O端口模块采用一种灵活配置的方法控制服用引脚功能,GPIOMUX寄存器用来选择F2812的引脚操作模式,可以通过该寄存器独立设置每个引脚的功能。

DSP交通灯控制实验

交通灯控制实验一、实验目的1.熟悉2812的指令系统;2.熟悉74HC573的使用方法;3.熟悉DSP的IO操作使用方法。

二、实验设备1. 一台装有CCS软件的计算机;2.插上2812主控板的DSP实验箱;3. DSP硬件仿真器。

三、实验原理此模块由发光二极管和一个锁存器组成。

数据由2812模块的低八位输入,锁存器的控制信号由2812模块输出,但经由CPLD模块译码后再控制锁存器。

74HC573功能:当锁存使能端为高时,这些器件的锁存对于数据是透明的(也就是说输出同步)。

当锁存使能变低时,符合建立时间和保持时间的数据会被锁存。

四、实验步骤1.把2812模块小板插到大板上;2.在CC2000环境中打开本实验工程编译Example_ crossled.prj,生成输出文件,用过仿真器把执行代码下载到DSP芯片;3.运行程序,发光二极管按交通灯方式点亮熄灭;4.参考源代码,自行修改程序,实现不同的交通灯控制方式。

五、实验现象及分析实验运行程序后,发光二极管按交通灯方式点亮熄灭。

交通控制灯有红黄绿三种颜色组成,红灯代表停止,黄灯代表警示,绿灯代表通行,在车辆逐渐增多的今天,交通灯的出现大大缓解了交通堵塞,以及减少了交通事故的发生。

目前交通信号灯控制系统有多种的实现方法,比如可编程序控制器PLC、标准逻辑器件、单片机等方案来实现,本实验采用插上 2812 主控板的DSP 实验箱为核心器件配以数码显示管,发光二极管来进行交通控制灯的设计,采用CCS2000 软件来进行模拟仿真,提高了系统的可实用性,在教学过程中能够使授课内容及过程更加形象生动。

六、实验心得在本次实验中使我掌握了 2812的指令系统和74HC573的使用方法及IO口的操作使用方法、锁存器等硬件结构的工作原理。

进一步掌握用C语言编写DSP程序的方法,及编译、除错能力。

这次试验也遇到很多编程上的问题,例如在一句程序结束之后一定要注意要加分号,数据类型要设好等等。

DSP作业用2812的定时器0实现对D6、D7、D8、D9流水灯显示定稿

用2812的定时器0实现对D6、D7、D8、D9流水灯显示一、引言DSP芯片,也称数字信号处理器,是一种具有特殊结构的微处理器。

DSP 芯片的内部采用程序和数据分开的哈佛结构,具有专门的硬件乘法器,广泛采用流水线操作,提供特殊的DSP指令,可以用来快速的实现各种数字信号处理算法。

数字信号处理是20世纪60年代,随着信息学科和计算机学科的高速发展而迅速发展起来的一门新兴学科。

它的重要性日益在各个领域的应用中表现出来。

其主要标志是两项重大进展,即快速傅里叶变换(FFT)算法的提出和数字滤波器设计方法的完善。

数字信号处理是把信号用数字或符号表示成序列,通过计算机或通用(专用)信号处理设备,用数值计算方法进行各种处理,达到提取有用信息便于应用的目的。

例如:滤波、检测、变换、增强、估计、识别、参数提取、频谱分析等。

根据数字信号处理的要求,DSP芯片一般具有如下的一些主要特点:(1)在一个指令周期内可完成一次乘法和一次加法。

(2)程序和数据空间分开,可以同时访问指令和数据。

(4)片内具有快速RAM,通常可通过独立的数据总线在两块中同时访问。

(4)具有低开销或无开销循环及跳转的硬件支持。

(5)快速的中断处理和硬件I/O支持。

(6)具有在单周期内操作的多个硬件地址产生器。

(7)可以并行执行多个操作。

(8)支持流水线操作,使取指、译码和执行等操作可以重叠执行。

(9)与通用微处理器相比,DSP芯片的其他通用功能相对较弱些。

随着大规模集成电路以及数字计算机的飞速发展,加之从60年代末以来数字信号处理理论和技术的成熟和完善,用数字方法来处理信号,即数字信号处理,已逐渐取代模拟信号处理。

在近20年时间里,DSP芯片已经在信号处理、通信、雷达等许多领域得到广泛的应用。

二、整体设计原理通过对DSP结构、原理及应用的学习。

在初步了解DSP结构和原理的基础上,进行简单的应用实验,掌握DSP的基本应用。

通过熟悉DSP模板的内部结构以及CCS软件,掌握DSP2812编程和调试方法,了解DSP的指令和I/O端口的寄存器的配置,并结合DSP实验模板对DSP进行编程控制数字输入/输出端口点亮LED显示管。

用DSP的GPIO口实现控制交通灯

用DSP的GPIO口实现控制交通灯1.1实验目的(1)熟悉使用ICETEK–F2812-AE评估板控制ICETEK-CTR上交通灯的方法。

练习自主独立的设计,实现理论和实践的统一,提高自我动手能力。

(2)掌握TMS320F2812DSP定时器的使用和编程。

(3)掌握TMS320F2812DSP外中断的使用和编程。

(4)学习复杂控制程序设计思路。

(5)利用DSP开发环境CCS C2000对源程序文件进行编译、链接、装载调试,以完成基本的DSP项目文件设计。

(6)通过此次课程设计,学习DSPF2812芯片的I/O端口控制方法,熟悉字模的简单构建和使用,熟悉掌握在DSP软硬件环境下的程序开发流程,达到学以致用的目的。

1.2实验总体方案本次设计过程中主要利用了F2812的通用I/O来实现对东西南北方向红绿灯亮灭的控制,以及数码管显示的控制。

而实现定时的操作主要通过定时器0中断调用来实现。

硬件设计的总框图如下:1.3实验原理1.2.1 F2812中GPIO的介绍F2812有多达56个通用数字量输入输出端口(GPIO),其中绝大部分是通用I/O和专用功能复用引脚。

数字量I/O端口模块采用一种灵活配置的方法控制复用引脚功能。

GPxMUX寄存器:选择F2812的引脚操作模式。

GPxDIR寄存器:配置数字量I/O的方向。

GPxSET寄存器:对数字量进行置位。

GPxDAT寄存器:独立读/写I/O信号。

GPxQUAL寄存器:消除数字量I/O引脚的噪声信号。

GPxCLEAR寄存器:对数字量进行清零。

1.2.2定时器0及其中断介绍F2812器件上有3个32位的CPU定时器(TIMERO/1/2)。

定时器1和2留给实时操作系统DSP/BIOS使用,只有定时器0可以在应用程序中使用。

若处理器采用30MHz的外部时钟经过锁相环10/2倍频之后,系统时钟工作在150MHz,一旦定时器被使能,定时器时钟经过与预定标记数器递减计数,预订标计数器产生下溢之后向定时器的32位计数器借位。

基于DSP的交通灯控制的设计

基于D S P的交通灯控制的设计Last updated on the afternoon of January 3, 2021目录1设计目的及要求 (4)设计目的.........................................4 设计要求.................................... (4)交通灯控制................................4 计时......................................5 紧急情况..................................5 程序设计. (5)2设计原理及方案.....................................7 课程设计总体方案.. (7)XXXXXX 电子信息工程学院课程设计报告交通灯综合控制设计人: XXX 专业: 电子信息工程 班级: 电子班学号: 指导教师:二零一X 年X 月设计思路 (7)课程设计原理 (7)系统工作原理 (7)系统工作状态 (8)3硬件设计 (10)硬件总体设计 (10)交通灯显示模块 (11)计数显示模块 (12)开关模块 (13)4软件设计 (14)程序流程 (14)交通灯模拟显示 (15)定时器及中断设计 (15)外中断设计 (16)5系统调试 (18)硬件调试 (18)电源调试 (18)调试 (18)软件调试 (21)系统下载 (24)6结论分析及体会 (25)7参考文献 (26)1设计目的及要求设计目的(1)熟悉使用ICETEK–F2812-AE评估板控制ICETEK-CTR上交通灯的方法。

练习自主独立的设计,实现理论和实践的统一,提高自我动手能力。

(2)(3)掌握TMS320F2812DSP定时器的使用和编程。

(4)掌握TMS320F2812DSP外中断的使用和编程。

(4)学习复杂控制程序设计思路。

DSP 课程设计 交通灯的控制与实现

#define nStatusNSYellowEWRed1 432

#define nTotalTime 448

#define nStatusHold 160

#define statusNSGreenEWRed 0

#define statusNSFlashEWRed 1

0xE2,0x91,0x91,0x8E,0x42,0x89,0x89,0x76,

0x38,0x24,0x22,0xFF,0x4F,0x89,0x89,0x71,

0x7E,0x89,0x89,0x72,0x01,0xF1,0x09,0x07,

0x76,0x89,0x89,0x76,0x4E,0x91,0x91,0x7E

PieVectTable.XINT2 = &XINT2_isr;

EDIS; // This is needed to disable write to EALLOW protected registers

//EALLOW; // This is needed to write to EALLOW protected registers

利用ICETEK-CTR上的发光二极管显示阵列模拟显示。

4.计时

使用TMS320F2812DSP片上定时器,定时产生时钟计数,再利用此计数对应具体时间。

计数

显示

20-0

0

20

20

20-1

0

20

20

20-1

5.紧急情况

利用ICETEK-CTR上键盘产生外中断,中断正常信号顺序,模拟突发情况。

6.程序设计

Uint16 var1 = 0;

(完整word版)DSP课程设计 交通灯的定时显示要点

14、4层板设计工艺,工作稳定可靠。

15、具有自启动功能设计,可以实现脱机工作。

16、可以选配多种应用接口板,包括语音板,网络板等。

3.3管脚的定义和说明

P1接口主要是扩展评估板上空闲的DSP外设引脚,以便于定制用户的硬件环境。注意:由于这组引脚是直接来自于F2812 DSP芯片,因此,这些引脚为TTL 3.3V标准,其输出最高电压为3.3V,如果要接入5V器件,外接时时要注意电平转换。(在扩展板上使用3.3V-5V兼容器件与扩展接口连接)。

#define CTRLCDCMDR *(int *)0x108001

#define CTRKEY *(int *)0x108001

#define CTRLCDCR *(int *)0x108002

#define CTRCLKEY *(int *)0x108002

#define CTRLCDLCR *(int *)0x108003

程序文件语言

program.asm汇编语言程序文件

filename.lib库文件

project.cmd连接命令文件

program.obj编译后的目标文件

program.out可在目标DSP上执行的文件,可在CCS监控下调试/执行

project.wks工作空间文件,可以记录你的工作环境设置。

定时器4比较输出

22

C1CTRIP

比较器1比较输出

23

C2CTRP

比较器2比较输出

24

C3CTRP

比较器3比较输出

25

TDIRA

定时器计数方向选择信号A

26

TCKINA

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

电子信息工程专业CDIO三级项目项目设计说明书(2011/2012学年第二学期)项目名称:DSP应用系统题目:DSPICETEK—f2812B控制交通灯专业班级:电子信息工程学生姓名:学号:指导教师:设计周数:2周设计成绩:2012年7月6日目录1、项目设计目的 (2)2、项目设计正文 (2)2.1硬件设计 (2)2.1.1总体方案设计 (2)2.1.2 数码管驱动显示电路设计 (3)2.1.3交通灯亮灭控制电路设计 (3)2.2项目软件设计 (6)2.2.1软件系统分析 (6)2.2.2 软件系统设计 (7)2.2.3 软件系统实施 (7)2.2.4软件开发环境的使用 (8)3、项目设计总结 (10)4、参考文献 (12)5、附录: (11)1、项目设计目的本学期我们主要学习了DSP 硬件方面的一些基本原理,对于如何通过软件来控制DSP 从而实现我们最终的需求,还不是很了解。

本次设计的目的就是基于TMS320CF2812平台的进行C 语言编程,了解软件编程开发的基本流程,以及软硬件是如何共同协调工作从而实现最终的控制的。

熟练掌握TMS320F2812控制交通灯方法,树立正确的设计思想提高分析问题与解决具体问题的能力。

并通过此次项目设计熟练软件CCS 的操作和使用,能够实现程序的编译、运行以及烧写。

2、项目设计正文 2.1硬件设计2.1.1总体方案设计本次设计过程中主要利用了F2812的通用I/O 来实现对东西南北方向红绿黄灯亮灭的控制,以及数码管显示的控制。

而实现定时的操作主要通过通用定时器0的中断调用来实现。

硬件设计的总体框图如图1所示。

图1 硬件设计总体框图2.1.1.1 F2812 GPIO 介绍TMS320F2812 DSP 有多达56个通用数字量输入输出端口(GPIO ),其中绝大部分是通用I/O 和专用功能复用引脚。

数字量I/O 端口模块采用一种灵活配置的方法控制服用引脚功能,GPIOMUX 寄存器用来选择F2812的引脚操作模式,可以通过该寄存器独立设置每个引脚的功能。

如果选择数字量I/O 模式,可以通过GPxDIR 寄存器配置数字量I/O 的方向,并通过GPxQUAL 进一步消除数字量I/O 引脚的噪声信号。

此外,处理器提供GPxSET 和GPxCLEAR 寄存器对数字量进行置位和清零,还可以通过GPxDAT 寄存器独立读/写I/O 信号。

2.1.1.2 定时器0及其中断介绍DSPGPIOA 最 小系GPIOB统数码管驱动电路发光二极管显示电路数码管显示电路F2812器件上有3个32位的CPU 定时器(TIMER0/1/2)。

定时器1和2留给实时操作系统DSP/BIOS 使用,只有定时器0可以在应用程序中使用。

若处理器采用30MHz 的外部时钟经过锁相环10/2倍频之后,系统时钟工作在150MHz,一旦定时器被使能,定时器时钟经过与预定标计数器递减计数,预订标计数器产生下溢之后向定时器的32位计数器借位。

最后定时器产生溢出使定时器想CPU 发出中断。

每次预订标计数器产生溢出后使用分频寄存器中的值重新装载,同样32位的周期寄存器为32位的计数器提供重新装载值。

2.1.1.3 基于F2812构成的最小系统 F2812构成的最小系统如图2所示。

图2 F2812最小系统原理图F2812芯片的最小系统,由11、12号引脚接外部时钟电路,用30MHz 的晶振提供时钟周期。

用1117电平转换芯片将外部寄存的电平+5V 转换为F2812能支持的电平+3.3V ,接到15号引脚(VDD )给F2812提供电源。

F2812芯片的复位电路由14号引脚接入。

2.1.2 数码管驱动显示电路设计本次设计为了节省F2812的端口的使用采用芯片CD4511来实现数码管的驱动以及显示。

CD4511是一个用于驱动共阴极 LED (数码管)显示器的 BCD 码—七段码译码器,特点如下:具有BCD 转换、消隐和锁存控制、七段译码及驱动功能的CMOS 电路能提供较大的拉电流。

可直接驱动LED 显示器。

其引脚图如图3所示。

GPIOA0_PWM11GPIOA0_PWM22GPIOA0_PWM33GPIOA0_PWM44GPIOA0_PWM55GPIOA0_PWM66GPIOB0_PWM77GPIOB0_PWM88GPIOB0_PWM99GPIOB0_PWM1010X111X212VDD15TESTSEL 13XRS14U1F2812P1P2P3P4P5P6P7P8P9P10+5VY130MHz 24p fC224p f R145.1k+C322u fS1SW-PB-4VCCVin 1G N D2Vout3U3LM1117图3 CD4511引脚电路图CD4511引脚功能介绍如下:BI:4脚是消隐输入控制端,当BI=0 时,不管其它输入端状态如何,七段数码管均处于熄灭(消隐)状态,不显示数字。

LT:3脚是测试输入端,当BI=1,LT=0 时,译码输出全为1,不管输入DCBA 状态如何,七段均发亮,显示“8”。

它主要用来检测数码管是否损坏。

LE:锁定控制端,当LE=0时,允许译码输出。

LE=1时译码器是锁定保持状态,译码器输出被保持在LE=0时的数值。

A1、A2、A3、A4为8421BCD码输入端。

a、b、c、d、e、f、g为译码输出端,输出为高电平1有效。

为了让数码管正常显示,进行引脚的焊接时BI与LT引脚接电源VCC,LE则连接地。

CD4511正常显示时用的真值表如表一:表一 CD4511真值表输入输出LE BI LI A3 A2 A1 A4 a b c d e f g 显示0 1 1 0 0 0 0 1 1 1 1 1 1 0 00 1 1 0 0 0 1 0 1 1 0 0 0 0 10 1 1 0 0 1 0 1 1 0 1 1 0 1 20 1 1 0 0 1 1 1 1 1 1 0 0 1 30 1 1 0 1 0 0 0 1 1 0 0 1 1 40 1 1 0 1 0 1 1 0 1 1 0 1 1 50 1 1 0 1 1 0 0 0 1 1 1 1 1 60 1 1 0 1 1 1 1 1 1 0 0 0 0 70 1 1 1 0 0 0 1 1 1 1 1 1 1 80 1 1 1 0 0 1 1 1 1 0 0 1 1 9电路进行连接时CD4511输出引脚a 、c 、d 、e 、f 、g 依次数码管的a 、c 、d 、e 、f 、g 引脚上即可。

另外由于数码管采用共阴的因此本次设计过程中即那个数码管的3脚与8脚接地,从而使数码管正常工作。

数码管的内部原理图以及其封装引脚如图4和图5所示。

图4 数码管内部原理图 图5 数码管封装引脚图数码管驱动现实的电路图如图6所示。

图6 数码管驱动电路图为了编写程序时与上述真值表相对应,将CD4511与DSP F2812的B 口进行连接时,应将其中,芯片CD4511引脚A4接芯片F2812的第13号引脚(GPIOB0/PWM7)、引脚A1接芯片F2812的第14号引脚(GPIOB1/PWM8)、引脚A2接芯片F2812的第15号引脚(GPIOB2/PWM9)、引脚A3接芯片F2812的第16号引脚(GPIOB3/PWM10)。

2.1.3交通灯亮灭控制电路设计由于F2812的通用I/O 口引脚输出高电平时,引脚的电压为3.3V ,而开发板上所提供的电源 电压为5V ,因此,发光二极管进行连接时只能采用共阴极。

因为当采用共阳极进行连接时,二极管阳极所接的电压为5V ,当通用I/O 口输出低电平时,发光二极管点亮。

但是,当通用I/O 口输出高电平时,电压为3.3V ,3.3V 与5V 存在1.7V 的压降,足以使发光二极管点亮。

这样就会造成,无论通用I/O 口输出低电平时,还是高电平时,发光二极管都点亮。

采用共阴极则不存在这个问题。

a bf cg d e DPY [LEDgn]1234567ab c d e fg DS1R7330ΩR8330ΩR9330ΩR10330ΩR11330ΩR12330ΩR13330ΩA11A22LT 3BI 4LE 5A36A47GND 8VCC 16f 15g 14a 13b 12c 11d 10e9U2CD4511P8P9P10P7g a b c d f ee f g a +5Vb c d +5V此次设计中为了简化地那路的连接,只将东西方向以及南北方向各一边的灯进行了设计连接。

共利用了6个通用I/O 口。

进行连接时,连接在了TMS320F2812 DSP 的GPIOA 的前六个引脚,即GPIOA0/PWM1- GPIOA5/PWM6。

总体硬件电路图如图7所示。

图7 总体硬件电路图实物图调试如图8所示。

图8 硬件实物图2.2项目软件设计12绿LED 12红LED12黄LED 12红LED12绿LED12黄LED a bf cg d e DPY [LEDgn]1234567abc d e fg DS1倒计时R1330ΩR2330ΩR3330ΩR4330ΩR5330ΩR6330ΩR7330ΩR8330ΩR9330ΩR10330ΩR11330ΩR12330ΩR13330ΩGPIOA0_PWM11GPIOA0_PWM22GPIOA0_PWM33GPIOA0_PWM44GPIOA0_PWM55GPIOA0_PWM66GPIOB0_PWM77GPIOB0_PWM88GPIOB0_PWM99GPIOB0_PWM1010X111X212VDD15TESTSEL 13XRS14U1F2812P1P2P3P4P5P6P1A11A22LT 3BI 4LE 5A36A47GND 8VCC 16f 15g 14a 13b 12c 11d 10e9U2CD4511P7P8P9P10P8P9P10P7g ab c d ee f g a b c d +5V+5VY130MHz C124pf C224pf R145.1k+C322ufS1SW-PB-4VCCVin 1G N D2Vout3U3LM1117F2812控制交通灯南北方向东西方向f2.2.1软件系统分析软件的设计主要是通过利用C 语言的编程来实现交通灯亮灭的控制,程序的设计包括初始化部分,对系统时钟的初始化、PIE 控制寄存器的初始化、中断向量表的初始化、GPIO 的初始化、定时器0的初始化。

接着就是对定时器0以及其中断周期进行配置。

最后进行中断程序的设计,中断程序的设计以及定时器中断周期的设置是本次软件设计的两块重要部分。

2.2.2 软件系统设计程序的总体流程图以及中断程序流程图如图9和图10所示。

2.2.3 软件系统实施主程序里面主要实现了对定时器0中断周期的设置,以为计时以秒为单位进行计时的,所以在进行配置时,将定时器的周期配置为1s ,在主程序的while (1)语句中每间隔1s 响应一次中断。