数字钟设计案例

多功能数字电子钟的方案设计书(郑思贺)

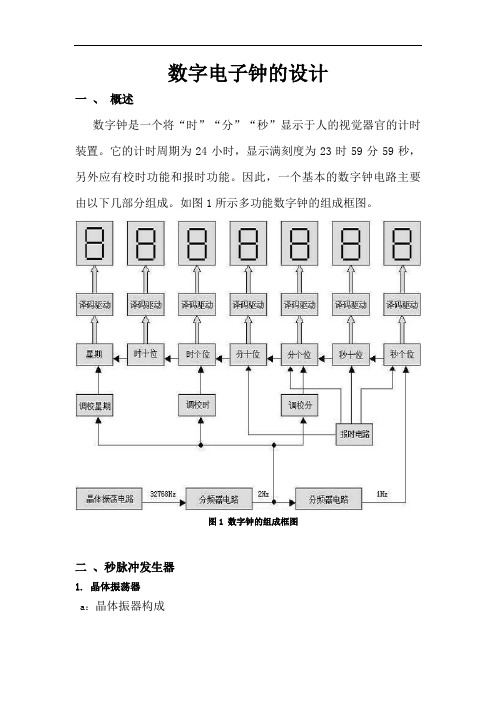

数字电子钟的设计一、概述数字钟是一个将“时”“分”“秒”显示于人的视觉器官的计时装置。

它的计时周期为24小时,显示满刻度为23时59分59秒,另外应有校时功能和报时功能。

因此,一个基本的数字钟电路主要由以下几部分组成。

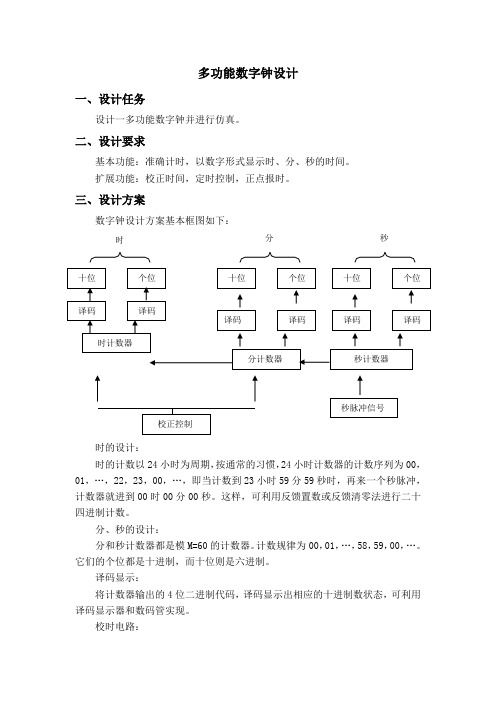

如图1所示多功能数字钟的组成框图。

图1 数字钟的组成框图二、秒脉冲发生器1. 晶体振荡器a:晶体振器构成晶体振荡器电路给数字电子钟提供一个频率稳定准确的32768Hz的方波信号,可保证数字钟的走时准确及稳定。

不管是指针式的电子钟还是数字显示的电子钟都使用了晶体振荡器电路。

如图2所示晶体振荡电路框图。

图2 晶体振荡电路框图b:晶体振荡器电路原理在电路中,非门U1与晶体、电容和电阻构成晶体振荡器电路,U2实现整形功能,将振荡器输出的近似于正弦波的波形转换为较理想的方波。

输出反馈电阻R1为非门提供偏置,使电路工作于放大区域,即非门的功能近似于一个高增益的反相放大器。

电容C1、C2与晶体构成一个谐振型网络,完成对振荡频率的控制功能,同时提供了一个180度相移,从而和非门构成一个正反馈网络,实现了振荡器的功能。

由于晶体具有较高的频率稳定性及准确性,从而保证了输出频率的稳定和准确。

晶体XTAL1的频率选为32768Hz。

其中C1的值取5~20 pF,C2为30pF。

C1作为校正电容可以对温度进行补偿,以提高频率准确度和稳定度。

由于电路的输入阻抗极高,因此反馈电阻R1可选为10MΩ。

较高的反馈电阻有利于提高振荡频率的稳定性。

2. 分频器电路分频器电路将32768Hz的高频方波信号经32768()次分频后得到1Hz的方波信号供秒计数器进行计数。

分频器实际上也就是计数器,为此电路输送一秒脉冲。

3. 秒脉冲发生器原理CD4060的10、11脚之间并接石英晶体和反馈电阻与其内部的反相器组成一个石英晶体振荡器。

电路产生的32768Hz的信号经过内部十四级分频后由3脚(Q14其分频系数为16384)输出脉冲频率为2Hz,再通过一个二分频器分频就得到了1Hz的时钟信号,也就是1S;CD4027为双JK触发器,其内部含有两个独立的JK触发器,其中16脚6脚(2J)5脚(2K)接电源,4脚(R2)7脚(S2)接地,3脚(CP2)输入2Hz脉冲信号,分频后的1Hz脉冲由1脚(Q2)输出。

数字钟设计(带仿真和连接图)

数字电子技术课程设计报告题目:数字钟的设计与制作专业:电气本一班学号:姓名:指导教师:时间:一、设计内容数字钟设计技术指标:(1)时间以24小时为周期;(2能够显示时,分,秒;(3)有校时功能,可以分别对时及分进行单独校时,使其校正到标准时间;(4)计时过程具有报时功能,当时间到达整点前5秒进行蜂鸣报时;(5)为了保证计时的稳定及准确须由晶体振荡器提供表针时间基准信号.二、设计时间:第十五、十六周三、设计要求:(1)画出设计的电路原理图;(2) 选择好元器件及给出参数,在原理图中反应出来;(3)并用仿真软件进行模拟电路工作情况;(4)编写课程报告。

摘要数字钟实际上是一个对标准频率(1Hz)进行计数的计数电路。

振荡器产生的时钟信号经过分频器形成秒脉冲信号,秒脉冲信号输入计数器进行计数,并把累计结果以“时”、“分”、“秒”的数字显示出来。

秒计数器电路计满60后触发分计数器电路,分计数器电路计满60后触发时计数器电路,当计满24小时后又开始下一轮的循环计数。

一般由振荡器、分频器、计数器、译码器、数码显示器等几部分组成。

振荡电路:主要用来产生时间标准信号,因为时钟的精度主要取决于时间标准信号的频率及稳定度,所以采用石英晶体振荡器。

分频器:因为振荡器产生的标准信号频率很高,要是要得到“秒”信号,需一定级数的分频器进行分频。

计数器:有了“秒”信号,则可以根据60秒为1分,24小时为1天的进制,分别设定“时”、“分”、“秒”的计数器,分别为60进制,60进制,24进制计数器,并输出一分,一小时,一天的进位信号。

译码显示:将“时”“分”“秒”显示出来。

将计数器输入状态,输入到译码器,产生驱动数码显示器信号,呈现出对应的进位数字字型。

由于计数的起始时间不可能与标准时间(如北京时间)一致,故需要在电路上加一个校时电路可以对分和时进行校时。

另外,计时过程要具有报时功能,当时间到达整点前10秒开始,蜂鸣器1秒响1秒停地响5次。

多功能数字钟设计报告+程序+原理图

实验设计报告项目名称:多功能数字钟电路设计作者姓名:指导教师:年级专业:所在学院:提交日期摘要20世纪末,电子技术获得了飞速的发展,在其推动下,现代电子产品几乎渗透了社会的各个领域,有力地推动了社会生产力的发展和社会信息化程度的提高,同时也使现代电子产品性能进一步提高,产品更新换代的节奏也越来越快。

现代生活的人们越来越重视起了时间观念,可以说是时间和金钱划上了等号。

对于那些对时间把握非常严格和准确的人或事来说,时间的不准确会带来非常大的麻烦,所以以数码管为显示器的时钟比指针式的时钟表现出了很大的优势。

数码管显示的时间简单明了而且读数快、时间准确显示到秒。

而机械式的依赖于机械震荡器,可能会导致误差。

数字钟是采用数字电路实现对“时”、“分”、“秒”数字显示的计时装置。

数字钟的精度、稳定度远远超过老式机械钟。

在这次设计中,我们采用LED数码管显示时、分、秒,以24小时计时方式,根据数码管动态显示原理来进行显示,用12MHz的晶振产生振荡脉冲,定时器计数。

在此次设计中,电路具有显示时间的其本功能,还可以实现对时间的调整。

数字钟以其小巧,价格低廉,走时精度高,使用方便,功能多,便于集成化而受广大消费的喜爱,因此得到了广泛的使用。

数字钟从原理上讲是一种典型的数字电路,其中包括了组合逻辑电路和时序电路。

因此,我们此次设计与制做数字钟就是为了了解数字钟的原理,从而学会制作数字钟.而且通过数字钟的制作进一步的了解各种在制作中用到的中小规模集成电路的作用及实用方法。

且由于数字钟包括组合逻辑电路和时叙电路。

通过它可以进一步学习与掌握各种组合逻辑电路与时序电路的原理与使用方法。

目录第一章:设计要求 (1)第二章:方案论证 (2)第三章:单元电路设计与计算 (13)第四章:软件设计 (20)第五章:系统测试 (36)第六章:结论 (38)参考文献 (39)附录 (40)第一章:设计要求1.1 基本要求1.1.1 时钟功能设计一个具有时、分、秒计时的数字钟电路,计时采用24小时制。

多功能数字钟(课程设计版)

题目: 多功能数字钟电路设计器材:74LS390,74LS48,数码显示器BS202, 74LS00 3片,74LS04,74LS08,电容,开关,蜂鸣器,电阻,导线要求完成的主要任务:用中、小规模集成电路设计一台能显示日、时、分秒的数字电子钟,要求如下:1.由晶振电路产生1HZ标准秒信号。

2.秒、分为00-59六十进制计数器。

3.时为00-23二十四进制计数器。

4.可手动校正:能分别进行秒、分、时的校正。

只要将开关置于手动位置。

可分别对秒、分、时进行连续脉冲输入调整。

5.整点报时。

整点报时电路要求在每个整点前鸣叫五次低音(500HZ),整点时再鸣叫一次高音(1000HZ)。

时间安排:指导教师签名:年月日系主任(或责任教师)签名:年月日索引摘要 (3)Abstract (3)1系统原理框图 (5)2方案设计与论证 (6)2.1时间脉冲产生电路 (6)2.2分频器电路 (9)2.3时间计数器电路 (10)2.4译码驱动及显示单元电路 (11)2.5校时电路 (12)2.6报时电路 (13)3单元电路的设计 (14)3.1时间脉冲产生电路的设计 (14)3.2计数电路的设计 (15)3.2.1 60进制计数器的设计 (15)3.2.2 24进制计数器的设计 (15)3.3译码及驱动显示电路 (16)3.4 校时电路的设计 (17)3.5 报时电路 (18)3.6电路总图 (20)4仿真结果及分析 (21)4.1时钟结果仿真 (21)4.2 秒钟个位时序图 (21)4.3报时电路时序图 (22)4.4测试结果分析 (22)5心得与体会 (23)6参考文献 (24)附录1原件清单 (25)附录2部分芯片引脚图与功能表 (26)摘要多功能数字钟具有时间显示、闹钟设置、环境温度测量、电网电压、电网频率显示,闹铃控制和电网电压的过压、欠压报警等功能,深受人们欢迎。

数字钟是采用数字电路实现对.时,分,秒.数字显示的计时装置,广泛用于个人家庭,车站, 码头办公室等公共场所,成为人们日常生活中不可少的必需品,由于数字集成电路的发展和石英晶体振荡器的广泛应用,使得数字钟的精度,远远超过老式钟表, 钟表的数字化给人们生产生活带来了极大的方便,而且大大地扩展了钟表原先的报时功能。

数字钟课程设计(完整原理图)

课程设计报告题目数字钟-数电课程设计2011-2012 第一学期班级姓名学号指导教师单位年月日前言20世纪末,电子技术获得了飞速的发展,在其推动下,现代电子产品几乎渗透了社会的各个领域,有力地推动了社会生产力的发展和社会信息化程度的提高,同时也使现代电子产品性能进一步提高,产品更新换代的节奏也越来越快。

时间对人们来说总是那么宝贵,工作的忙碌性和繁杂性容易使人忘记当前的时间。

忘记了要做的事情,当事情不是很重要的时候,这种遗忘无伤大雅。

但是,一旦重要事情,一时的耽误可能酿成大祸。

例如,许多火灾都是由于人们一时忘记了关闭煤气或是忘记充电时间。

尤其在医院,每次护士都会给病人作皮试,测试病人是否对药物过敏。

注射后,一般等待5分钟,一旦超时,所作的皮试试验就会无效。

手表当然是一个好的选择,但是,随着接受皮试的人数增加,到底是哪个人的皮试到时间却难以判断。

所以,要制作一个定时系统。

随时提醒这些容易忘记时间的人。

钟表的数字化给人们生产生活带来了极大的方便,而且大大地扩展了钟表原先的报时功能。

诸如定时自动报警、按时自动打铃、时间程序自动控制、定时广播、定时启闭电路、定时开关烘箱、通断动力设备,甚至各种定时电气的自动启用等,所有这些,都是以钟表数字化为基础的。

因此,研究数字钟及扩大其应用,有着非常现实的意义。

目录一、设计目的................................................................................................................................... - 2 -二、设计要求 ................................................................................................................................ - 3 -2.1设计指标 (3)2.2设计要求 (3)2.3制作要求 (3)2.4编写设计报告 (3)三、各单元电路设计 .................................................................................................................... - 4 -3.1工作原理 (4)3.2原理框图 (4)3.3振荡器 (5)3.3.1由石英晶体振荡器构成的1HZ秒脉冲信号 .................................................................. - 5 -3.4时间计数器电路 (6)3.4.1秒计数器的设计.............................................................................................................. - 6 -3.4.2分计数器的设计.............................................................................................................. - 7 -3.4.3时计数器电路.................................................................................................................. - 8 -3.5译码驱动及显示单元的设计 (9)3.6校时电路 (9)3.7整点报时电路 (10)3.7.1 论证............................................................................................................................. - 10 -3.7.2 实现............................................................................................................................. - 10 -四、总电路设计 .......................................................................................................................... - 12 -五、元件清单 .............................................................................................................................. - 12 -六、课程设计体会 ...................................................................................................................... - 13 -七、参考文献 .............................................................................................................................. - 14 -一、设计目的1、熟悉集成电路的引脚安排;2、掌握各芯片的逻辑功能及使用方法;3、了解数字钟的组成及工作原理;4、熟悉数字钟的设计与制作;5、熟悉Protel99 SE软件的操作;二、设计要求2.1设计指标时间以24小时为一个周期;能显示时,分,秒;有校时功能,可以分别对时及分进行单独校时,使其校正到标准时间;计时过程具有报时功能,当时间到达整点前10秒进行蜂鸣报时;为了保证计时的稳定及准确须由晶体振荡器提供表针时间基准信号。

多功能数字钟设计

多功能数字钟设计

一、设计任务

设计一多功能数字钟并进行仿真。

二、设计要求

基本功能:准确计时,以数字形式显示时、分、秒的时间。

扩展功能:校正时间,定时控制,正点报时。

三、设计方案

数字钟设计方案基本框图如下:

时的设计:

时的计数以24小时为周期,按通常的习惯,24小时计数器的计数序列为00,01,…,22,23,00,…,即当计数到23小时59分59秒时,再来一个秒脉冲,计数器就进到00时00分00秒。

这样,可利用反馈置数或反馈清零法进行二十四进制计数。

分、秒的设计:

分和秒计数器都是模M=60的计数器。

计数规律为00,01,…,58,59,00,…。

它们的个位都是十进制,而十位则是六进制。

译码显示:

将计数器输出的4位二进制代码,译码显示出相应的十进制数状态,可利用译码显示器和数码管实现。

校时电路: 分 秒

校时可用1s脉冲快速校正,也可手动产生单次脉冲慢校正至时或者分计数器。

可设置变量来控制实现校正或正常计数。

定时控制:

数字钟在指定的时刻发出信号,实现闹钟功能。

正点报时:

每当数字钟计时快要到正点时发出声响,通常按照4低音1高音的顺序发出间断声响,以最后一声高音结束的时刻为正点时刻。

四、电路仿真与分析。

多功能数字钟的设计

1多功能数字钟的设计1.1设计要求设计一个能进行时、分、秒计时的十二小时制或二十四小时制的数字钟,并具有定时与钟功能,能在设定的时间发出闹铃音,能非常方便地对小时、分钟和秒进行手动调节以校时间,每逢整点,产生报时音报时。

系统框图如图1-1所示:系统模式手动IHZ时钟源复位选择校时输入图IT多功能数字钟系统框图显示部分可以使用数码管(基本)或液晶LCD(扩展)。

1.2设计提示此设计问题可分为主控电路、计数器模块和扫描显示三大部,主控电路中各种特殊功能的实现设计问题的关键。

用两个电平信号A、B进行模式选择,AB=OO为模式0,系统为计时状态;AB=Ol为模式1,系统为手动校时状态;AB=Io为模式2,系统为闹钟设置状态。

设置一个turn信号,当turn=0时,表示在手动校对时,选择调整分钟部分;当turn=l 时,表示在手动校对时,选择调整小时部分。

设置一个Change信号,在手动校时或闹钟设置模式下,每按一次,计数器加1。

设置一个reset信号,当reset=O时,整个系统复位;当reset=1时,系统进行计时或其他特殊功能操作。

设置一个闹钟设置信号resell,当resetl=O时,对闹钟进行设置,当resetl=O时,关闭闹钟信号。

设置状态显示信号(连发光二极管):LD_alert指示是否设置了闹铃功能;LDjI指示当前调整的是小时信号;LD_m指示当前调整的是分钟信号。

当闹钟功能设置后(LD_alert=l),系统应启动一个比较电路,当计时与预设闹铃时间相等时,启动闹铃声,直到关闭闹铃信号有效。

整点报时部分由分和秒计时同时为0(或60)启动,与闹铃共用一个扬声器驱动信号OUto 系统计时时钟为Clk=IHz,选择另一时钟clk」k=1024Hz作为产生闹铃声、报时音的时钟信号。

主控电路状态表如表1-1所示。

硬件系统示意图如图1-2所示。

晶振[OOO1.D_hLD_mMs6Ms5..LD_alertclkjkClkFP∈Λ∕(PLDturnchangeresetreset1AIIII IIII IIII LlL∣abCdefg图1-2数字钟硬件系统示意图。

多功能数字钟电路设计

多功能数字钟电路设计多功能数字钟电路设计数字钟是现代生活中常见的电子产品之一,可以显示当前的时间,并且通常还具备闹钟、定时器等功能。

本文将介绍一个多功能数字钟的电路设计。

要设计一个多功能数字钟,我们首先需要选择一个合适的微控制器作为主控芯片。

在本设计中,我们选择了一款功能强大且易于编程的Arduino微控制器。

在电路设计方面,我们需要一个显示器来展示时间和其他功能。

这里我们选择了四位数码管作为显示器,并通过数码管驱动芯片将其与Arduino连接起来。

为了接收时间信号并实现精确的时间显示,我们需要一个实时时钟芯片(RTC)来提供时间基准。

我们选择了DS3231作为RTC芯片,该芯片具有高精度和低功耗的特点。

为了实现闹钟功能,我们需要一个蜂鸣器作为报警器。

通过Arduino控制蜂鸣器的开关,我们可以在设定的时间触发闹钟功能。

此外,我们还可以添加其他功能,比如温度显示、定时器等。

温度显示可以通过添加温度传感器并将其与Arduino连接来实现。

定时器功能可以通过编程实现,利用Arduino的计时器来设置定时任务。

整个电路的设计思路如下:首先,Arduino通过I2C总线与DS3231实时时钟芯片通信,以获取当前的时间。

然后,将时间数据和其他功能数据通过数码管驱动芯片发送到数码管上,实现时间和其他功能的显示。

同时,Arduino还通过GPIO控制蜂鸣器的开关,实现闹钟功能。

如果需要温度显示,Arduino还会通过模拟输入口读取温度传感器的数据,并将其显示在数码管上。

此外,定时任务可以通过编程设置,定时器的触发可以控制其他模块的开关或执行其他操作。

通过这样一个多功能数字钟的设计,我们可以不仅方便地获取当前的时间,还可以实现其他实用的功能。

这种设计适用于家庭、办公室等各种场合,可以提高生活和工作的便利性。

同时,这个设计的实现也展示了使用微控制器和外设芯片来构建和控制各种功能的能力,是对电子设计和嵌入式系统的一种实践。

多功能数字时钟毕业设计

摘要数字电子时钟是人们日常生活中不可或缺的必需品。

电子钟主要是利用现代电子技术将时钟电子化、数字化。

与传统的机械钟相比,具有时钟精确、显示直观、无机械传动装置等优点,因而得到广泛应用。

另外,在生活和工农业生产中,人们对电子钟的功能又提出了诸多要求:报时、闹钟、日历、温度显示,这就需要电子时钟的多功能性。

根据人们的不同要求,本设计主要为实现一款可正常显示时钟,测量环境温度、湿度,带有定时闹铃,倒计时的多功能电子时钟。

本设计采用液晶显示以其亮度高、显示直观等优点被广泛应用于智能仪器及家用电器等领域。

该时钟系统主要由时钟模块、闹钟模块、环境温度湿度检测模块、液晶显示模块、键盘控制模块以及信号提示模块组成。

能够准确显示时间(显示格式为时时:分分:秒秒,24小时制),可随时进行时间调整,具有闹钟时间设置、闹钟开/关、止闹功能,能够对时钟所在的环境温度进行测量并显示。

设计以硬件软件化为指导思想,充分发挥单片机功能,大部分功能通过软件编程来实现,电路简单明了,系统稳定性高。

关键词:电子时钟;单片机;多功能;温湿度传感器AbstractDigital electronic clock is indispensable to daily life. Electronic clock is the use of modern electronic technology to clock electronic, digital. Compared with the traditional mechanical clock, a clock-accurate, intuitive display, no mechanical transmission device, etc., and thus are widely used. In addition, the in the the in the life and industrial and agricultural production,, the people pairs of the the the function of of electronic bell also proposed a a lot of of the requirements of: timekeeping,alarm clock, calendar, temperature display, which requires the the the versatility of electronic clock.According to the different requirements of the people of this design to achieve a normal display clock / calendar, measuring the ambient temperature, humidity, multi-function electronic clock with alarm.This design uses the LCD its high brightness, intuitive and other advantages are widely used in intelligent instruments and appliances and other areas. The clock system clock module, alarm clock module, the ambient temperature and humidity detection module, LCD module, keyboard, control module and the signal prompt module composition. Be able to accurately to display the time (display format for the from time to time: sub-sub-the: seconds seconds, system of the 24 hours), can be at any time carried out the time to adjust, with a the alarm clock time setting, alarm clock On / Off, ended downtown function, be able to pairs the ambient temperature where the by the clock carried out measurement and displayed. Design hardware and software as the guiding ideology, give full play to the MCU function, most of the functionality through software programming simple circuit and system stability.Keywords: Electronic clock;single-chip; multi-function;temperature and humidity sensor目录摘要 .................................................. Abstract . (I)1 绪论 (4)1.1课题背景 (4)1.1.1 多功能数字电子钟研究的背景 (4)1.1.2多功能电子钟研究现状与意义 (4)1.1.3 多功能电子钟的功能 (5)2 硬件设计 (7)2.1 系统的设计思路 (7)2.1.1设计流程 (7)2.2单片机的选择 (7)2.2.1 单片机的发展趋势 (7)2.2.2 单片机主要应用领域和特点 (8)2.3 单片机 STC89C52简介 (8)2.4 温湿度传感器 (13)2.4.1 DHT11 概述 (13)2.4.2 应用电路连接说明 (14)2.4.3 DHT11数据结构 (14)2.5显示部分设计 (15)2.5.1 液晶显示屏LCD1602简介 (15)2.5.2 LCD1602功能介绍 (15)2.5.3 LCD1602初始化过程 (17)2.5.4 LCD1602硬件电路接口设计 (18)2.6 单片机最小系统 (18)2.7 键盘部分 (20)2.8 报警电路设计 (21)2.9 直流稳压电源部分 (22)2.10 硬件仿真 (22)2.10.1 仿真软件protues简介 (22)2.10.2 本设计的仿真原理图 (23)3 软件设计 (24)3.1 编程环境Keil简介 (24)3.2软件设计总体说明 (24)3.2.1主程序设计 (24)3.2.2 键盘部分 (25)3.2.3 闹钟子程序程序 (26)4 调试 (27)4.1软件调试 (27)4.2硬件调试 (33)5 系统可靠性的设计 (34)5.1 软件可靠性的设计 (34)5.2 硬件可靠性的设计 (35)5.3 本系统中的抗干扰的预防措施 (35)总结 (37)参考文献 (1)附录 (2)附录1:部分程序代码 (2)附录2:系统仿真原理图 (10)1 绪论一寸光阴一寸金,寸金难买寸光阴。

南理工数字钟设计(优秀)

多功能数字计时器设计实验报告姓名:专业:电气工程及其自动化学号:目录一.实验目的 (3)二.设计内容简介 (3)三.设计功能要求 (3)四.电路设计原理图 (3)五.电路原理介绍: (4)六.单元电路设计1.秒信号发生电路 (4)2.译码显示电路 (5)3.计时电路 (6)4.清零电路 (7)5.校分电路 (8)6.报时电路 (8)7.附加电路------动态显示 (9)七.实验中遇到的问题以及解决方法 (10)八. 实验体会 (11)附录一、实验目的1.掌握常见集成电路的工作原理和使用方法。

2.学会单元电路的设计方法。

二、设计内容简介本实验采用中小规模集成电路设计一个数字计时器。

数字计时器是由脉冲发生电路,计时电路,译码显示电路,和控制电路等几部分组成。

其中控制电路由清零电路,校分电路和报时电路组成。

三、设计功能要求1、设计一个脉冲发生电路,为计时器提供秒脉冲、为报时电路提供驱动蜂鸣器的脉冲信号(f1=1Hz,f2=1KHz,f3=2KHz)。

2、设计一个计时电路,完成0分00秒~9分59秒的计时功能。

3、设计报时电路,使数字计时器从9分53秒开始报时,每隔一秒发一声,共发三声低音,一声高音;即9分53秒、9分55秒、9分57秒发低音(频率1kHz),9分59秒发高音(频率2kHz)。

4、设计校分电路,在任何时候,拨动校分开关,可以2HZ进行校分。

5、设计清零电路,具有开机自动清零功能,并且在任何时候,按动清零开关,可以进行计时器清零。

6、系统级联调试,将以上电路进行级联完成计时器的所有功能。

7、可增加数字计时器附加功能,例如数字计时器定时功能、电路起停功能、电路采用动态显示等。

四.电路设计原理图数字计时器是由秒信号发生电路,9,5,9计时电路,清零电路,校分电路以及报时电路组成。

电路构造原理如下:五.电路原理介绍:本电路采用晶体产生稳定的高频振荡信号,通过分频电路产生计时器所需的1Hz脉冲信号。

简单的数字时钟设计(protel)

《数字电路》课程设计总结报告题目:数字钟设计2010 年 12 月 12 日数字钟设计 (3)一、设计任务 (3)1.1功能描述 (3)二、设计框图与整机概述 (3)2.1主题电路图 (3)2.2系统的工作原理 (3)三、各单元电路的设计方案及原理说明 (4)3.1设计思路 (4)3.2振荡器的设计 (4)3.3分频器的设计 (4)3.4分秒计数器的设计 (4)3.5校时电路的设计 (5)3.6显示电路的设计 (6)四、调试过程及结果分析 (6)4.1调试过程 (6)4.2结果分析 (6)五、设计、安装及调试中的体会 (6)六、对本次课程设计的意见和建议 (7)七、参考文献 (7)八、附录 (7)数字钟设计一、设计任务1.1功能描述设计一个多功能数字中电路,基本功能为:①准确计时,以数字形式显示分、秒的时间;②分和秒的计时要求为60进位;③校正时间。

二、设计框图与整机概述2.1主题电路图1s2.2系统的工作原理由振荡器产生高稳定的高频脉冲信号,作为数字钟的时间基准(系统时钟),再经分频器输出标准秒脉冲信号。

秒计数器计满60后向分计数器进位,分计数器计满60后重新开始计时。

计数器的输出经译码器送显示器。

计时出现误差时可以用校时电路进行校分。

分显示器 秒显示器时译码器 秒译码器分计数器 秒计数器 校时电路 分频器振荡器三、各单元电路的设计方案及原理说明3.1设计思路主体电路是由功能部件或单元电路组成的。

在设计这些电路或选择部件时,尽量用同类型的器件,如所有功能部件都采用TTL集成电路或都采用CMOS集成电路。

3.2振荡器的设计振荡器是数字钟的核心。

振荡器的稳定度及频率的精确度决定了数字钟计时的准确程度,通常选用石英晶体构成振荡器电路。

一般来说,振荡器的频率越高,计时精度越高。

在这里我们选用由集成电路定时器555与RC组成的多谐振荡器。

这里选用555构成的多谐振荡器,输出振荡频率v0=1KHz的脉冲,电路参数如下图所示。

多功能数字钟设计

多功能数字钟设计多功能数字钟设计数字钟是一种能够显示时间的钟表,可以帮助人们准确地掌握时间并管理自己的日程。

为了满足人们对数字钟的多种需求,我设计了一款多功能数字钟。

该数字钟具有以下功能:1. 时间显示:数字钟具有清晰的LED数字显示,可以显示小时和分钟。

时间显示具有灵活性,可以选择12小时制或24小时制。

2. 闹钟功能:数字钟具有闹钟功能,用户可以根据自己的需求,设定闹钟时间。

当闹钟时间到达时,数字钟会发出响亮的闹铃声,提醒用户。

3. 温度显示:数字钟具有温度传感器,可以显示当前室内温度。

用户可以随时掌握室内温度,从而调整合适的温度。

4. 日历功能:数字钟具有日历功能,可以显示当前日期和星期几。

用户可以通过数字钟了解日期,并根据需要安排自己的活动。

5. 天气预报:数字钟具有连接互联网的功能,可以通过天气预报网站获取实时的天气信息。

用户可以通过数字钟了解当前天气情况,从而合理安排出行和室内外活动。

6. 语音控制:数字钟具有语音识别功能,用户可以通过语音命令控制数字钟的各项功能。

比如,用户可以通过语音命令设置闹钟时间或调整温度。

7. USB充电口:数字钟具有USB充电口,用户可以通过数字钟为手机和其他电子设备充电。

这样,用户不仅能够准确掌握时间,还能方便地为其他设备充电。

8. 亮度调节:数字钟具有亮度可调节功能,用户可以根据自己的需求,调整数字钟的亮度。

在夜间,用户可以减小亮度,避免打扰睡眠。

9. 电池备份:数字钟具有电池备份功能,当电源中断时,数字钟可以使用备用电池继续工作,避免时间的丢失。

10. 远程控制:数字钟可以通过手机或其他远程设备进行控制,用户可以通过手机轻松设置闹钟、调整时间等功能,提高便利性。

总之,该多功能数字钟集合了时间显示、闹钟、温度显示、日历、天气预报、语音控制、USB充电口、亮度调节、电池备份和远程控制等多种功能于一身,既可以帮助人们准确掌握时间,又能方便管理自己的日程。

它的设计旨在提高人们的生活质量和便利性。

多功能数字钟的设计与实现项目设计方案

多功能数字钟的设计与实现项目设计方案1 数字钟设计功能及方案论证基本功能:1)设计一个数字钟。

要求用六位数码管显示时间,格式为00:00:00。

2)具有60进制和24进制(或12进制)计数功能,秒、分为60进制计数,时为24进制(或12进制)计数。

3)有译码、七段数码显示功能,能显示时、分、秒计时的结果。

扩展功能:1)设计提供连续触发脉冲的脉冲信号发生器,2)具有校时单元、闹钟单元和整点报时单元。

方案论证:方案一:用逻辑门电路直接搭接数字钟电路,此方案所需元件众多,频率稳定性差,电路复杂,所以不采用此方案。

方案二:用计数器74LS90以及译码器74LS48等芯片组成电路,用555振荡器及分频器产生1Hz信号供计数器技术,较之第一种方案容易实现。

方案三:用单片机实现计数及显示等,这种方案简单明了,电路简单只需要写好程序就可以,容易达到任务要求。

但单片机对个人能力要求较高,鉴于还没有学习单片机方面知识,所以不使用第三种方案。

综上,决定采用第二种方案。

2 设计原理及框图1)计数器电路:计数器电路由秒计数器、分计数器及时计数器构成。

根据设计要求,其中,时计数器为24进制,分计数器及秒计数器为60进制计数器。

2)译码显示电路:由74LS48芯片组成的译码电路将计数器输出的8421BCD码转化为数码管所需的逻辑状态,并为保证数码管正常工作提供足够工作电流。

3)整点报时电路:在数字钟电路出现整点时,数字钟会自动报时,其工作方式是发出连续的音频声波,复杂一些的可以是实时语音或音乐提示。

4)定时闹钟电路:要求可以设定一个指定的时间,是数字钟在指定时刻发出信号,使蜂鸣器“闹时”。

5)555振荡器电路:石英晶体振荡器电路给数字钟提供一个频率稳定的32768Hz的方波信号,可保证数字钟的走时准确及稳定。

6)分频器电路:分频器电路将32768HZ的高频方波信号经分频后得到1Hz的方波信号供秒计数器进行计数。

数字钟原理框图如下:图1.1 数字钟原理框图3 电路模块分析3.1计数器电路计数器电路我选择的是74LS90芯片。

数字钟设计(带仿真图)

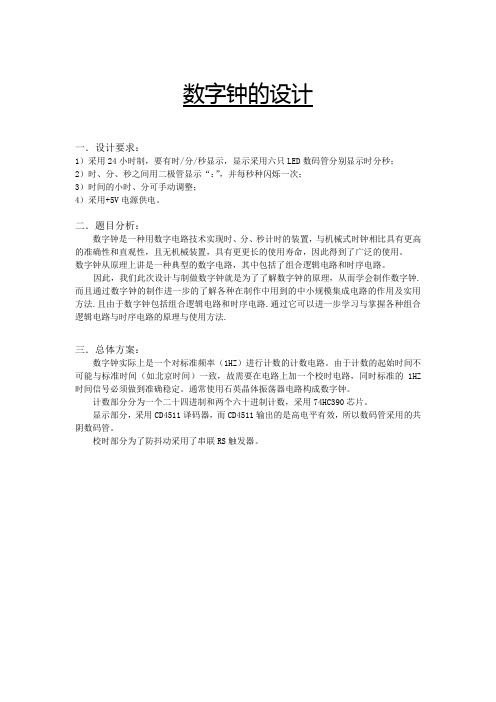

数字钟的设计一.设计要求:1)采用24小时制,要有时/分/秒显示,显示采用六只LED数码管分别显示时分秒;2)时、分、秒之间用二极管显示“:”,并每秒种闪烁一次;3)时间的小时、分可手动调整;4)采用+5V电源供电。

二.题目分析:数字钟是一种用数字电路技术实现时、分、秒计时的装置,与机械式时钟相比具有更高的准确性和直观性,且无机械装置,具有更更长的使用寿命,因此得到了广泛的使用。

数字钟从原理上讲是一种典型的数字电路,其中包括了组合逻辑电路和时序电路。

因此,我们此次设计与制做数字钟就是为了了解数字钟的原理,从而学会制作数字钟.而且通过数字钟的制作进一步的了解各种在制作中用到的中小规模集成电路的作用及实用方法.且由于数字钟包括组合逻辑电路和时序电路.通过它可以进一步学习与掌握各种组合逻辑电路与时序电路的原理与使用方法.三.总体方案:数字钟实际上是一个对标准频率(1HZ)进行计数的计数电路。

由于计数的起始时间不可能与标准时间(如北京时间)一致,故需要在电路上加一个校时电路,同时标准的1HZ 时间信号必须做到准确稳定。

通常使用石英晶体振荡器电路构成数字钟。

计数部分分为一个二十四进制和两个六十进制计数,采用74HC390芯片。

显示部分,采用CD4511译码器,而CD4511输出的是高电平有效,所以数码管采用的共阴数码管。

校时部分为了防抖动采用了串联RS触发器。

图1 数字时钟线路原理框图四.原理图设计我们这次做的数字钟总体分为四个部分,晶体振荡部分、计数部分、译码显示部分和校时部分。

图2 数字时钟整体原理图五.各部分定性说明以及定量计算:(一)晶体振荡部分由于要产生稳定的1Hz的脉冲信号,所以选用石英晶体振荡器。

选用的石英晶体振荡器的频率是32768Hz的,故需对其分频。

用CD4060分得2Hz的频率后再用CD4013双D触发器得到1Hz的频率。

原理图如下。

图3 晶体振荡部分原理图振荡部分使用的元器件主要有:1片CD4060,1片CD4013,1个3276Hz的晶体振荡器,1个22兆欧的电阻,1个20Pf和1个30Pf的电容。

多功能数字钟电路设计

多功能数字钟电路设计

多功能数字钟电路可以用来显示时间、日期、闹钟和定时器等功能。

下面是一个简单的多功能数字钟电路设计,它基于CD4511七段译码器和CD4543 BCD-七段译码器。

1. 时间显示功能

为了显示时间,我们需要使用CD4543 BCD-七段译码器。

该译码器接收来自实时时钟(RTC)模块的BCD编码输出。

RTC模块可以用来跟踪时间和日期,它通常包括一个晶体振荡器、计数器和存储器。

BCD 编码输出通过CD4543译码器转换为七段LED显示。

2. 日期显示功能

类似于时间显示功能,日期显示也需要使用RTC模块。

RTC模块可以提供年份、月份和日期的BCD编码输出。

这些编码输出通过CD4543译码器转换为七段LED显示。

3. 闹钟功能

闹钟功能可以通过计时器和比较器实现。

我们可以使用555定时器作

为计时器,它可以生成一个固定的时间间隔。

然后,我们可以使用一个比较器来比较当前时间和闹钟时间。

如果它们匹配,闹钟就会响起。

4. 定时器功能

定时器功能可以通过555定时器来实现。

我们可以设置计时器的时间间隔,并使用CD4511七段译码器来显示剩余时间。

当定时器完成计时时,它可以触发一个报警器或执行其他操作。

总之,多功能数字钟电路可以实现时间、日期、闹钟和定时器等多种功能。

这些功能可以通过RTC模块、CD4511七段译码器、CD4543 BCD-七段译码器和555定时器等元件来实现。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

数字电子技术课程设计报告题目:数字钟的设计与制作学年:03-04 学期:短学期专业:通信技术班级: 022学号:姓名:金雪指导教师及职称:钱裕禄讲师时间:2004年6月25日—2004年7月9日浙江万里学院电子信息学院一、设计目的1.熟悉集成电路的引脚安排。

2.掌握各芯片的逻辑功能及使用方法。

3.了解面包板结构及其接线方法。

4.了解数字钟的组成及工作原理。

5.熟悉数字钟的设计与制作。

二、设计要求1.设计指标时间以24小时为一个周期;显示时、分、秒;有校时功能,可以分别对时及分进行单独校时,使其校正到标准时间;计时过程具有报时功能,当时间到达整点前5秒进行蜂鸣报时;为了保证计时的稳定及准确须由晶体振荡器提供表针时间基准信号。

2.设计要求画出电路原理图(或仿真电路图);元器件及参数选择;电路仿真与调试;PCB文件生成与打印输出。

3.制作要求自行装配和调试,并能发现问题和解决问题。

4.编写设计报告写出设计与制作的全过程,附上有关资料和图纸,有心得体会。

三、设计原理及其框图1.数字钟的构成数字钟实际上是一个对标准频率(1HZ)进行计数的计数电路。

由于计数的起始时间不可能与标准时间(如北京时间)一致,故需要在电路上加一个校时电路,同时标准的1HZ时间信号必须做到准确稳定。

通常使用石英晶体振荡器电路构成数字钟。

图3-1所示为数字钟的一般构成框图。

图3-1 数字钟的组成框图⑴晶体振荡器电路晶体振荡器电路给数字钟提供一个频率稳定准确的32768Hz的方波信号,可保证数字钟的走时准确及稳定。

不管是指针式的电子钟还是数字显示的电子钟都使用了晶体振荡器电路。

⑵分频器电路2)次分频后得到1Hz的方波分频器电路将32768Hz的高频方波信号经32768(15信号供秒计数器进行计数。

分频器实际上也就是计数器。

⑶时间计数器电路时间计数电路由秒个位和秒十位计数器、分个位和分十位计数器及时个位和时十位计数器电路构成,其中秒个位和秒十位计数器、分个位和分十位计数器为60进制计数器,而根据设计要求,时个位和时十位计数器为12进制计数器。

⑷译码驱动电路译码驱动电路将计数器输出的8421BCD码转换为数码管需要的逻辑状态,并且为保证数码管正常工作提供足够的工作电流。

⑸数码管数码管通常有发光二极管(LED)数码管和液晶(LCD)数码管,本设计提供的为LED数码管。

2.数字钟的工作原理1)晶体振荡器电路晶体振荡器是构成数字式时钟的核心,它保证了时钟的走时准确及稳定。

图3-2所示电路通过CMOS非门构成的输出为方波的数字式晶体振荡电路,这个电路中,CMOS非门U1与晶体、电容和电阻构成晶体振荡器电路,U2实现整形功能,将振荡器输出的近似于正弦波的波形转换为较理想的方波。

输出反馈电阻R1为非门提供偏置,使电路工作于放大区域,即非门的功能近似于一个高增益的反相放大器。

电容C1、C2与晶体构成一个谐振型网络,完成对振荡频率的控制功能,同时提供了一个180度相移,从而和非门构成一个正反馈网络,实现了振荡器的功能。

由于晶体具有较高的频率稳定性及准确性,从而保证了输出频率的稳定和准确。

晶体XTAL的频率选为32768H Z。

该元件专为数字钟电路而设计,其频率较低,有利于减少分频器级数。

从有关手册中,可查得C1、C2均为30pF。

当要求频率准确度和稳定度更高时,还可接入校正电容并采取温度补偿措施。

由于CMOS电路的输入阻抗极高,因此反馈电阻R1可选为10MΩ。

较高的反馈电阻有利于提高振荡频率的稳定性。

非门电路可选74HC00。

图3-2 COMS晶体振荡器2)分频器电路通常,数字钟的晶体振荡器输出频率较高,为了得到1Hz的秒信号输入,需要对振荡器的输出信号进行分频。

通常实现分频器的电路是计数器电路,一般采用多级2进制计数器来实现。

例如,将32768Hz的振荡信号分频为1HZ的分频倍数为32768(215),即实现该分频功能的计数器相当于15极2进制计数器。

常用的2进制计数器有74HC393等。

本实验中采用CD4060来构成分频电路。

CD4060在数字集成电路中可实现的分频次数最高,而且CD4060还包含振荡电路所需的非门,使用更为方便。

CD4060计数为14级2进制计数器,可以将32768HZ的信号分频为2HZ,其内部框图如图3-3所示,从图中可以看出,CD4060的时钟输入端两个串接的非门,因此可以直接实现振荡和分频的功能。

图3-3 CD4046内部框图3)时间计数单元时间计数单元有时计数、分计数和秒计数等几个部分。

时计数单元一般为12进制计数器计数器,其输出为两位8421BCD码形式;分计数和秒计数单元为60进制计数器,其输出也为8421BCD码。

一般采用10进制计数器74HC390来实现时间计数单元的计数功能。

为减少器件使用数量,可选74HC390,其内部逻辑框图如图2.3所示。

该器件为双2—5-10异步计数器,并且每一计数器均提供一个异步清零端(高电平有效)。

图3-4 74HC390(1/2)内部逻辑框图秒个位计数单元为10进制计数器,无需进制转换,只需将QA与CPB(下降沿有效)相连即可。

CPA(下降没效)与1HZ秒输入信号相连,Q3可作为向上的进位信号与十位计数单元的CPA相连。

秒十位计数单元为6进制计数器,需要进制转换。

将10进制计数器转换为6进制计数器的电路连接方法如图3-5所示,其中Q2可作为向上的进位信号与分个位的计数单元的CPA相连。

图3-5 10进制——6进制计数器转换电路分个位和分十位计数单元电路结构分别与秒个位和秒十位计数单元完全相同,只不过分个位计数单元的Q3作为向上的进位信号应与分十位计数单元的CPA相连,分十位计数单元的Q2作为向上的进位信号应与时个位计数单元的CPA相连。

时个位计数单元电路结构仍与秒或个位计数单元相同,但是要求,整个时计数单元应为12进制计数器,不是10的整数倍,因此需将个位和十位计数单元合并为一个整体才能进行12进制转换。

利用1片74HC390实现12进制计数功能的电路如图3-6所示。

另外,图3-6所示电路中,尚余-2进制计数单元,正好可作为分频器2HZ输出信号转化为1HZ信号之用。

图3-6 12进制计数器电路4)译码驱动及显示单元计数器实现了对时间的累计以8421BCD码形式输出,选用显示译码电路将计数器的输出数码转换为数码显示器件所需要的输出逻辑和一定的电流,选用CD4511作为显示译码电路,选用LED数码管作为显示单元电路。

5)校时电源电路当重新接通电源或走时出现误差时都需要对时间进行校正。

通常,校正时间的方法是:首先截断正常的计数通路,然后再进行人工出触发计数或将频率较高的方波信号加到需要校正的计数单元的输入端,校正好后,再转入正常计时状态即可。

根据要求,数字钟应具有分校正和时校正功能,因此,应截断分个位和时个位的直接计数通路,并采用正常计时信号与校正信号可以随时切换的电路接入其中。

图3-7所示即为带有基本RS触发器的校时电路,图3-7 带有消抖动电路的校正电路6)整点报时电路一般时钟都应具备整点报时电路功能,即在时间出现整点前数秒内,数字钟会自动报时,以示提醒。

其作用方式是发出连续的或有节奏的音频声波,较复杂的也可以是实时语音提示。

根据要求,电路应在整点前10秒钟内开始整点报时,即当时间在59分50秒到59分59秒期间时,报时电路报时控制信号。

报时电路选74HC30,选蜂鸣器为电声器件。

四、元器件1.实验中所需的器材5V电源。

面包板1块。

示波器。

万用表。

镊子1把。

剪刀1把。

网络线2米/人。

共阴八段数码管6个。

CD4511集成块6块。

CD4060集成块1块。

74HC390集成块3块。

74HC51集成块1块。

74HC00集成块5块。

74HC30集成块1块。

10MΩ电阻5个。

500Ω电阻14个。

30p电容2个。

32.768k时钟晶体1个。

蜂鸣器。

2.芯片内部结构图及引脚图图4-1 7400 四2输入与非门图4-2 CD4511BCD七段译码/驱动器图4-3 CD4060BD 图4-4 74HC390D图4-5 74HC51D 图4-6 74HC303.面包板内部结构图面包板右边一列上五组竖的相通,下五组竖的相通,面包板的左边上下分四组,每组中X、Y列(0-15相通,16-40相通,41-55相通,ABCDE相通,FGHIJ相通,E和F之间不相通。

五、个功能块电路图1.一个CD4511和一个LED数码管连接成一个CD4511驱动电路,数码管可从0---9显示,以次来检查数码管的好坏,见附图5-1。

图5-1 4511驱动电路2. 利用一个LED 数码管,一块CD4511,一块74HC390,一块74HC00连接成一个十进制计数器,电路在晶振的作用下数码管从0—9显示,见附图5-2。

U1A74HC390D1QA 31QB 51QC 61QD71INA 11INB 41CLR2U2DA 7DB 1DC 2DD 6O A 13O D 10O E9O F 15O C 11O B 12O G 14~EL 5~BI 4~LT34511BDV160Hz 5V5VVCCU3SEVEN_SEG_COM_KA B C D E F GComU4A74HC00D 123U4B74HC00D456十进制接法测试仿真电路图5-2 74390十进制计数器3.利用一个LED数码管,一块CD4511,一块74HC390,一块74HC00和一个晶振连接成一个六进制计数器,数码管从0—6显示,见附图5-3。

图5-3 74390六进制计数器4.利用一个六进制电路和一个十进制连接成一个六十进制电路,电路可从0—59显示,见附图5-4。

U1A74HC00D123U1B74HC00D 456U2A74HC390D1QA 31QB 51QC 61QD71INA 11INB41CL R2U2B74HC390D2QA 132QB 112QC 102QD92INA 152INB122CL R14U3DA 7DB 1DC 2DD 6O A 13O D 10O E9O F 15O C 11O B 12O G14~EL 5~BI 4~L T34511BDU4DA 7DB 1DC 2DD6O A 13O D 10O E9O F 15O C 11O B 12O G14~EL 5~BI 4~L T34511BD5VVCCV1150Hz 5VU6S EV EN_SE G_COM _KA B C D E F GCo mU1C74HC00D 9108U1D74HC00D 121311六十进制电路调试图5-4 六十进制电路5. 利用两个六十进制的电路合成一个双六十进制电路,两个六十进制之间有进位,见附图5-5。

U1A74HC00D123U1B74HC00D 456U3A74HC390D1QA 31QB 51QC 61QD71INA 11INB41CL R2U3B74HC390D2QA 132QB 112QC 102QD92INA 152INB122CL R14U2DA 7DB 1DC 2DD 6O A 13O D 10O E9O F 15O C 11O B 12O G14~EL 5~BI 4~L T34511BDU5DA 7DB 1DC 2DD 6O A 13O D 10O E9O F 15O C 11O B 12O G14~EL 5~BI 4~L T34511BD5VVCCV1100kHz 5VU4S EV EN_SE G_COM _KA B C D E F GCo m U1C74HC00D9108U1D74HC00D121311U6S EV EN_SE G_COM _KA B C D E F GCo mU7S EV EN_SE G_COM _KA B C D E F GCo mU8A74HC390D1QA 31QB 51QC 61QD71INA 11INB41CL R 2U9DA 7DB 1DC 2DD 6O A 13O D 10O E9O F 15O C 11O B 12O G14~EL 5~BI 4~L T34511BDU10A74HC00D123U11B74HC00D 4565VVCCU12B74HC390D 2QA 132QB 112QC 102QD92INA 152INB122CL R14U13DA 7DB 1DC 2DD 6O A 13O D 10O E9O F 15O C 11O B 12O G14~EL 5~BI 4~L T34511BDU14S EV EN_SE G_COM _KA B C D E F G Co mU15C74HC00D 9108U16D 74HC00D1213115VVCC图5-5 双六十进制电路6. 利用CD4060、电阻及晶振连接成一个分频——晶振电路,见附图5-6。