EDA实验三 七段译码显示

十六进制7段数码显示译码器设计实验报告

实验名称:十六进制7段数码显示译码器设计实验目的:1.设计七段显示译码器2.学习文本文件进行逻辑设计输入;3.学习设计仿真工具的使用方法;工作原理:7段数码是纯组合电路,通常的小规模专用,如74或4000系列的器件只能作十进制码译码,然而数字系统中的数据处理和运算都是二进制的,所以输出表达都是十六进制的,为了满足十六进制数的译码显示,最方便的方法就是利用译码程序在中来实现。

例如6-18作为7段译码器,输出信号7S的7位分别接图6-17数码管的7个段,高位在左,低位在右。

例如当7S输出为“1101101”时,数码管的7个段分别接1,1,0,1,1,0,1;接有高电平的段发亮,于是数码管显示“5”。

注意,这里没有考虑表示小数点的发光管,如果要考虑,需要增加段h,例6-18中的7 (6 0)应改为…(7 0)。

实验内容1:将设计好的译码器程序在上进行编辑、编译、综合、适配、仿真,给出其所有信号的时序仿真波形。

实验步骤:步骤1:新建一个文件夹击打开文件;步骤2:编写源程序并保存步骤3:新建一个工程及进行工程设置步骤4:调试程序至无误;步骤5:接着新建一个文件及展出仿真波形设置步骤6:输入数据并输出结果(时序仿真图)步骤7:设置好这个模式步骤8:生成原理图步骤9:引脚锁定及源代码;1164;7S(A (3 0);7 (6 0));;7S(A)A"0000"=> 7S<="0111111"; "0001"=> 7S<="0000110"; "0010"=> 7S<="1011011"; "0011"=> 7S<="1001111"; "0100"=> 7S<="1100110"; "0101"=> 7S<="1101101"; "0110"=> 7S<="1111101"; "0111"=> 7S<="0000111"; "1000"=> 7S<="1111111"; "1001"=> 7S<="1101111"; "1010"=> 7S<="1110111"; "1011"=> 7S<="1111100"; "1100"=> 7S<="0111001"; "1101"=> 7S<="1011110"; "1110"=> 7S<="1111001"; "1111"=> 7S<="1110001"; =>;;;;实验内容二:1、硬件测试。

EDA实验三-七段译码显示

河北科技大学实验报告2013级电信专业132 班学号130701213 2016年6月7日姓名田继辉同组人指导教师于国庆实验名称实验三七段译码显示成绩实验类型设计型批阅教师一、实验目的(1)掌握VHDL语言的行为描述设计时序电路。

(2)掌握FPGA动态扫描显示电路设计方法。

(3)熟悉进程(process)和顺序语句的应用。

二、实验原理:用4个开关作为加法器的一组输入变量,共4组输入变量;对每组变量进行译码,变换成0~F标准段码,段码中“1”表示段亮,“0”表示段灭。

一位时钟输入作为扫描显示位扫时钟,四位位扫输出,依次输出高电平。

8位段码输出,根据位选状态选择输出四组输入变量的相应译码结果。

四组输入采用试验箱K1~K16,时钟输入选择试验箱CP1或CP2;试验箱LED显示选择动态显示方式(CZ1开关ST选择OFF),段码、位码分别扫描输出,某个管的位码有效期间,将其对应的段码输出,各位码依次有效,实现循环扫描显示,将输入的16位二进制数,每4位一组,分别显示到4个数码管上(0~F)。

三、实验内容及步骤1.打开MUXPLUS II VHDL编辑器,完成七段译码显示的设计。

包括VHDL程序输入、编译、综合。

实验程序如下:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;ENTITY alpher ISPORT(1 / 6clk : IN STD_LOGIC;choice : OUT STD_LOGIC_VECTOR(7 downto 0);data : OUT STD_LOGIC_VECTOR(7 downto 0)); END alpher;ARCHITECTURE a OF alpher ISSIGNAL count : STD_LOGIC_VECTOR(3 downto 0); SIGNAL temp : STD_LOGIC_VECTOR(3 downto 0);BEGINchoice<="10000000";clk1_label:PROCESS (clk)BEGINIF clk'event and clk='1' THENcount<=count+1;END IF;END PROCESS clk1_label;WITH count selectdata <= "11111100" WHEN "0000","01100000" WHEN "0001","11011010" WHEN "0010","11110010" WHEN "0011","01100110" WHEN "0100","10110110" WHEN "0101","10111110" WHEN "0110","11100000" WHEN "0111","11111110" WHEN "1000","11110110" WHEN "1001","11101110" WHEN "1010","00111110" WHEN "1011","10011100" WHEN "1100","01111010" WHEN "1101","10011110" WHEN "1110","10001110" WHEN OTHERS;END a;2、建立仿真波形文件,使用MAXPLUS II Simulator功能进行功能仿真。

实验3 七段字形显示译码器实验

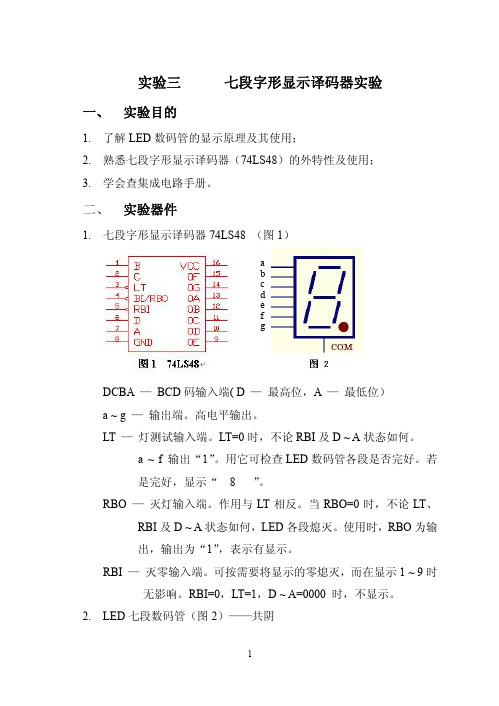

实验三七段字形显示译码器实验一、 实验目的1.了解LED数码管的显示原理及其使用;2.熟悉七段字形显示译码器(74LS48)的外特性及使用;3.学会查集成电路手册。

二、 实验器件1.七段字形显示译码器74LS48 (图1)abcdefgDCBA — BCD码输入端( D —最高位,A —最低位)a ~ g —输出端。

高电平输出。

LT —灯测试输入端。

LT=0时,不论RBI及D ~ A状态如何。

a ~ f 输出“1”。

用它可检查LED数码管各段是否完好。

若是完好,显示“8 ”。

RBO —灭灯输入端。

作用与LT相反。

当RBO=0时,不论LT、RBI及D ~ A状态如何,LED各段熄灭。

使用时,RBO为输出,输出为“1”,表示有显示。

RBI —灭零输入端。

可按需要将显示的零熄灭,而在显示1 ~ 9时无影响。

RBI=0,LT=1,D ~ A=0000 时,不显示。

2.LED七段数码管(图2)——共阴74LS48功能表LT RBI D C B A RBO a b c d e f g1 1 0 0 0 0 1 1 1 1 1 1 1 01 X 0 0 0 1 1 0 1 1 0 0 0 01 X 0 0 1 0 1 1 1 0 1 1 0 11 X 0 0 1 1 1 1 1 1 1 0 0 11 X 0 1 0 0 1 0 1 1 0 0 1 11 X 0 1 0 1 1 1 0 1 1 0 1 11 X 0 1 1 0 1 0 0 1 1 1 1 11 X 0 1 1 1 1 1 1 1 0 0 0 01 X 1 0 0 0 1 1 1 1 1 1 1 11 X 1 0 0 1 1 1 1 1 0 0 1 11 X 1 0 1 0 1 0 0 0 1 1 0 11 X 1 0 1 1 1 0 0 1 1 0 0 11 X 1 1 0 0 1 0 1 0 0 0 1 11 X 1 1 0 1 1 1 0 0 1 0 1 11 X 1 1 1 0 1 0 0 0 1 1 1 11 X 1 1 1 1 1 0 0 0 0 0 0 0X X X X X X 0* 0 0 0 0 0 0 01 0* 0 0 0 00 0 0 0 0 0 0 00 X X X X X 1 1 1 1 1 1 1 1三、 实验内容1.设计实验电路。

七段数码管显示实验报告

七段数码管显示实验报告实验目的:本实验的目的是通过控制7段数码管的亮灭状态来显示不同的数字和字母。

实验原理:7段数码管常用于显示数字和字母,每个数码管由7个LED灯组成,分别表示A、B、C、D、E、F、G等7个段。

通过控制这些LED灯的亮灭状态,就可以显示不同的数字和字母。

在实际应用中,通常需要使用一个译码器来根据输入的数字或字母输出相应的控制信号。

常用的译码器有7447、DM9368等。

这些译码器通常都是BCD码到7段数码管的译码器。

在本实验中,我们将使用7447译码器来控制7段数码管的亮灭状态。

7447译码器具有4个输入线和7个输出线,每个输入线上的BCD码可以转换成相应的控制信号,用于控制数码管的7个LED 灯。

实验材料:1.7段数码管2.7447译码器3.电路板4.电压源5.连接线实验步骤:1.将7447译码器插入电路板上相应的插槽中,并将数码管连接到电路板上。

2.将电压源连接到电路板上,并调节电压和电流值。

3.根据所需显示的数字或字母,设置相应的BCD码输入信号。

4.打开电源,观察数码管是否能够正确显示。

实验结果:通过本实验,我们可以成功控制7段数码管的亮灭状态,实现了数字和字母的显示。

同时,我们也了解了7447译码器的原理和使用方法。

实验小结:本实验是电子技术的基础实验之一,通过实验我们深入了解了7段数码管和7447译码器的原理和应用,同时也锻炼了我们的动手能力和实验技能。

在实际应用中,7段数码管和译码器常常被用于数字显示、计数器、时钟、温度计等电子设备中,具有广泛的应用前景。

EDA实验报告

EDA实验报告班级:姓名:目录实验一:七段数码显示译码器设计 (1)摘要 (1)实验原理 (1)实验方案及仿真 (1)引脚下载 (2)实验结果与分析 (3)附录 (3)实验二:序列检测器设计 (6)摘要 (6)实验原理 (6)实现方案及仿真 (6)引脚下载 (7)实验结果与分析 (8)实验三:数控分频器的设计 (11)摘要 (11)实验原理 (11)方案的实现与仿真 (11)引脚下载 (12)实验结果及总结 (12)附录 (12)实验四:正弦信号发生器 (14)摘要 (14)实验原理 (14)实现方案与仿真 (14)嵌入式逻辑分析及管脚下载 (16)实验结果与分析 (17)附录 (18)实验一:七段数码显示译码器设计摘要:七段译码器是一种简单的组合电路,利用QuartusII的VHDL语言十分方便的设计出七段数码显示译码器。

将其生成原理图,再与四位二进制计数器组合而成的一个用数码管显示的十六位计数器。

整个设计过程完整的学习了QuartusII的整个设计流程。

实验原理:七段数码是纯组合电路,通常的小规模专用IC,如74或4000系列的器件只能作十进制BCD码译码,然而数字系统中的数据处理和运算都是2进制的,所以输出表达都是16进制的,为了满足16进制数的译码显示,最方便的方法就是利用译码程序在FPGA\CPLD中来实现。

本实验作为7段译码器,输出信号LED7S的7位分别是g、f、e、d、c、b、a,高位在左,低位在右。

例如当LED7S 输出为“1101101”时,数码管的7个段g、f、e、d、c、b、a分别为1、1、0、1、1、1、0、1。

接有高电平段发亮,于是数码管显示“5”。

实验方案及仿真:I、七段数码显示管的设计实现利用VHDL描述语言进行FPGA上的编译实现七段数码显示译码器的设计。

运行QuartusII在G:\QuartusII\LED7S\下新建一个工程文件。

新建一个vhdl语言编译文件,编写七段数码显示管的程序见附录1-1。

EDA实验三七段数码管显示译码

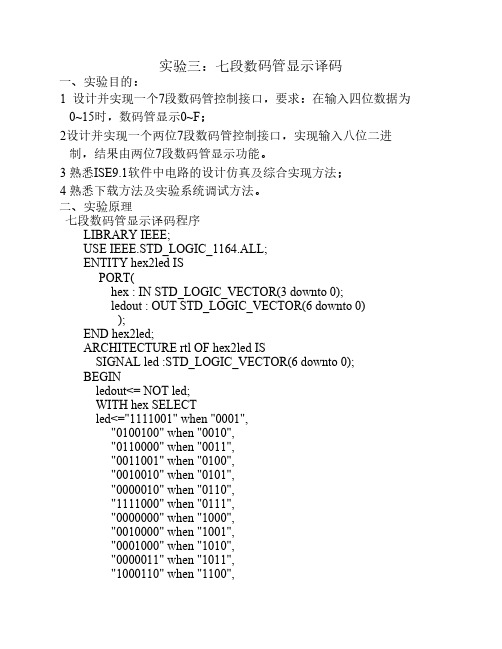

实验三:七段数码管显示译码一、实验目的:1 设计并实现一个7段数码管控制接口,要求:在输入四位数据为0~15时,数码管显示0~F;2设计并实现一个两位7段数码管控制接口,实现输入八位二进制,结果由两位7段数码管显示功能。

3 熟悉ISE9.1软件中电路的设计仿真及综合实现方法;4 熟悉下载方法及实验系统调试方法。

二、实验原理七段数码管显示译码程序LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY hex2led ISPORT(hex : IN STD_LOGIC_VECTOR(3 downto 0);ledout : OUT STD_LOGIC_VECTOR(6 downto 0));END hex2led;ARCHITECTURE rtl OF hex2led ISSIGNAL led :STD_LOGIC_VECTOR(6 downto 0);BEGINledout<= NOT led;WITH hex SELECTled<="1111001" when "0001","0100100" when "0010","0110000" when "0011","0011001" when "0100","0010010" when "0101","0000010" when "0110","1111000" when "0111","0000000" when "1000","0010000" when "1001","0001000" when "1010","0000011" when "1011","1000110" when "1100","0100001" when "1101","0000110" when "1110","0001110" when "1111","1000000" when others;END rtl;三、实验处理激励代码:tb : PROCESSBEGINhex<="0000";wait for 50 ns;for i in 0 to 15 loophex<=hex+1;wait for 50 ns;end loop;功能仿真图时序仿真图(图中黄线可以看出延时)延时报告:Data Sheet report:All values displayed in nanoseconds (ns) Pad to PadSource Pad |Destination Pad| Delay | hex<0> |ledout<0> | 5.963| hex<0> |ledout<1> | 5.963| hex<0> |ledout<2> | 5.963| hex<0> |ledout<3> | 5.958| hex<0> |ledout<4> | 5.963| hex<0> |ledout<5> | 5.958| hex<0> |ledout<6> | 5.958| hex<1> |ledout<0> | 5.963| hex<1> |ledout<1> | 5.963| hex<1> |ledout<2> | 5.963| hex<1> |ledout<3> | 5.958| hex<1> |ledout<4> | 5.963| hex<1> |ledout<5> | 5.958| hex<1> |ledout<6> | 5.958| hex<2> |ledout<0> | 5.963| hex<2> |ledout<1> | 5.963| hex<2> |ledout<2> | 5.963| hex<2> |ledout<3> | 5.958| hex<2> |ledout<4> | 5.963| hex<2> |ledout<5> | 5.958| hex<2> |ledout<6> | 5.958| hex<3> |ledout<0> | 5.963| hex<3> |ledout<1> | 5.963| hex<3> |ledout<2> | 5.963| hex<3> |ledout<3> | 5.958| hex<3> |ledout<4> | 5.963| hex<3> |ledout<5> | 5.958| hex<3> |ledout<6> | 5.958| ---------------+---------------+---------+可编程器件、拨码开关、与发光二极管关系#PACE: Start of PACE I/O Pin AssignmentsNET "hex<0>" LOC = "N17" ;NET "hex<1>" LOC = "H18" ;NET "hex<2>" LOC = "L14" ;NET "hex<3>" LOC = "L13" ;NET "ledout<0>" LOC = "B4" ;NET "ledout<1>" LOC = "A4" ;NET "ledout<2>" LOC = "D5" ;拨码开关状态数码管显示D1D2D3D4下下下下0下下下上1下下上下2下下上上3下上下下4下上下上5下上上下6下上上上7上下下下8上下下上9上下上下A 上下上上B 上上下下C 上上下上D 上上上下E 上上上上FNET "ledout<3>" LOC = "C5" ;NET "ledout<4>" LOC = "A6" ;NET "ledout<5>" LOC = "B6" ;NET "ledout<6>" LOC = "E7" ;设计表格记录实验结果,并分析其结果的正确性。

eda实验7段数码显示译码器

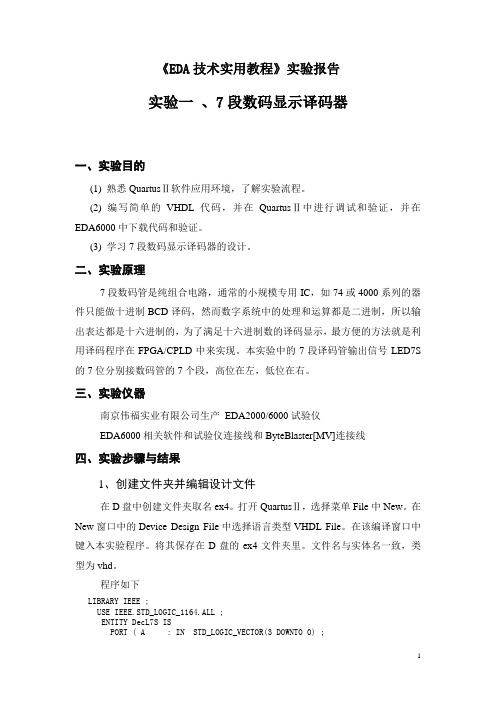

《EDA技术实用教程》实验报告实验一、7段数码显示译码器一、实验目的(1) 熟悉QuartusⅡ软件应用环境,了解实验流程。

(2) 编写简单的VHDL代码,并在QuartusⅡ中进行调试和验证,并在EDA6000中下载代码和验证。

(3) 学习7段数码显示译码器的设计。

二、实验原理7段数码管是纯组合电路,通常的小规模专用IC,如74或4000系列的器件只能做十进制BCD译码,然而数字系统中的处理和运算都是二进制,所以输出表达都是十六进制的,为了满足十六进制数的译码显示,最方便的方法就是利用译码程序在FPGA/CPLD中来实现。

本实验中的7段译码管输出信号LED7S 的7位分别接数码管的7个段,高位在左,低位在右。

三、实验仪器南京伟福实业有限公司生产EDA2000/6000试验仪EDA6000相关软件和试验仪连接线和ByteBlaster[MV]连接线四、实验步骤与结果1、创建文件夹并编辑设计文件在D盘中创建文件夹取名ex4。

打开QuartusⅡ,选择菜单File中New。

在New窗口中的Device Design File中选择语言类型VHDL File。

在该编译窗口中键入本实验程序。

将其保存在D盘的ex4文件夹里。

文件名与实体名一致,类型为vhd。

程序如下LIBRARY IEEE ;USE IEEE.STD_LOGIC_1164.ALL ;ENTITY DecL7S ISPORT ( A : IN STD_LOGIC_VECTOR(3 DOWNTO 0) ;LED7S : OUT STD_LOGIC_VECTOR(6 DOWNTO 0) ) ;END ;ARCHITECTURE one OF DecL7S ISBEGINPROCESS( A )BEGINCASE A(3 DOWNTO 0) ISWHEN "0000" => LED7S <= "0111111" ; -- X"3F"'0WHEN "0001" => LED7S <= "0000110" ; -- X"06"'1WHEN "0010" => LED7S <= "1011011" ; -- X"5B"'2WHEN "0011" => LED7S <= "1001111" ; -- X"4F"'3WHEN "0100" => LED7S <= "1100110" ; -- X"66"'4WHEN "0101" => LED7S <= "1101101" ; -- X"6D"'5WHEN "0110" => LED7S <= "1111101" ; -- X"7D"'6WHEN "0111" => LED7S <= "0000111" ; -- X"07"'7WHEN "1000" => LED7S <= "1111111" ; -- X"7F"'8WHEN "1001" => LED7S <= "1101111" ; -- X"6F"'9WHEN OTHERS => NULL ;END CASE ;END PROCESS ;END ;2、创建工程(1)选择菜单File中New Project Wizard命令,在如下“工程设置”对话框中单击右侧“…”按钮,找到文件夹D:\ex4,选中已存盘的ex4.vhd的文件。

可编程逻辑器件实验EDA-七段数码管显示电路

实验四 七段数码管显示电路

一、实验目的

实现十六进制计数显示。

二、硬件需求

EDA/SOPC 实验箱一台。

三、实验原理

七段数码管分共阳极与共阴极两种。

共阳极数码管其工作特点是,当笔段电极接低电平,公共阳极接高电平时,相应笔段可以发光。

共阴极数码管则与之相反,它是将发光二极管的阴极短接后作为公共阴极,当驱动信号为高电平、公共阴极接低电平时,才能发光。

图2-13为共阳极数码管和共阴极数码管的内部结构图。

a b c d e f g h

a

b

c

d

e

f

g

h

a b c d e f g h

DIG

DIG

共阴极七段数码管

共阳极七段数码管

图2-13 共阳极数码管和共阴极数码管的内部结构图

用七段数码管除了可以显示0~9的阿拉伯数字外,还可以显示一些英语字母。

下表是常见的字母与7段显示关系(共阴极数码管)。

编写一个0~F 轮换显示的电路(注意:选用实验箱中的共阳数码管DP1A ,FPGA 上

P25引脚连接50MHz时钟。

实验时为了便于观察,要将50MHz时钟经过分频得到1Hz时钟)。

五、实验步骤

(1)实验程序

(2)仿真结果

为方便观察程序功能,分频改为6分频,从上图可以看出数码管输出能够连续变化,同时输出正确稳定的七位码。

(3)管脚绑定

(4)实验实际结果

从实际的上电结果可以看出,每过一秒,数码管数值增1,并发生跳变显示。

十六进制7段数码显示译码器设计实验报告

实验名称:十六进制7段数码显示译码器设计实验目的:1.设计七段显示译码器2.学习Verilog HDL文本文件进行逻辑设计输入;3.学习设计仿真工具的使用方法;工作原理:7段数码是纯组合电路,通常的小规模专用IC,如74或4000系列的器件只能作十进制BCD码译码,然而数字系统中的数据处理和运算都是二进制的,所以输出表达都是十六进制的,为了满足十六进制数的译码显示,最方便的方法就是利用译码程序在FPGA/CPLD中来实现。

例如6-18作为7段译码器,输出信号LED7S 的7位分别接图6-17数码管的7个段,高位在左,低位在右。

例如当LED7S输出为“1101101”时,数码管的7个段g,f,e,d,c,b,a分别接1,1,0,1,1,0,1;接有高电平的段发亮,于是数码管显示“5”。

注意,这里没有考虑表示小数点的发光管,如果要考虑,需要增加段h,例6-18中的LED7S:OUT STD_LOGIC_VECTOR(6 DOWNTO 0)应改为…(7 DOWNTO 0)。

实验内容1:将设计好的VHDL译码器程序在Quartus II上进行编辑、编译、综合、适配、仿真,给出其所有信号的时序仿真波形。

实验步骤:步骤1:新建一个文件夹击打开vhdl文件;步骤2:编写源程序并保存步骤3:新建一个工程及进行工程设置步骤4:调试程序至无误;步骤5:接着新建一个VECTOR WAVEFOM文件及展出仿真波形设置步骤6:输入数据并输出结果(时序仿真图)步骤7:设置好这个模式步骤8:生成RTL原理图步骤9:引脚锁定及源代码LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY DECL7S ISPORT(A :IN STD_LOGIC_VECTOR(3 DOWNTO 0);LED7S:OUT STD_LOGIC_VECTOR(6 DOWNTO 0)); END;ARCHITECTURE one OF DECL7S ISBEGINPROCESS(A)BEGINCASE A ISWHEN"0000"=> LED7S<="0111111";WHEN"0001"=> LED7S<="0000110";WHEN"0010"=> LED7S<="1011011";WHEN"0011"=> LED7S<="1001111";WHEN"0100"=> LED7S<="1100110";WHEN"0101"=> LED7S<="1101101";WHEN"0110"=> LED7S<="1111101";WHEN"0111"=> LED7S<="0000111";WHEN"1000"=> LED7S<="1111111";WHEN"1001"=> LED7S<="1101111";WHEN"1010"=> LED7S<="1110111";WHEN"1011"=> LED7S<="1111100";WHEN"1100"=> LED7S<="0111001";WHEN"1101"=> LED7S<="1011110";WHEN"1110"=> LED7S<="1111001";WHEN"1111"=> LED7S<="1110001";WHEN OTHERS =>NULL;END CASE;END PROCESS;END;实验内容二:1、硬件测试。

微原实验3——七段数码管显示

微原实验:七段数码管一、实验目的掌握接口芯片的编址方法,掌握8255的初始化设置,及数码管显示原理,掌握段控及位控的概念。

二、实验内容①连接地址译码器与8255的连线及8255与数码管的连线;②在数据段中存放0到9的字型码;③从微机键盘输入2个数字的ASCII码,在输入过程中检查如非数字键的重新输入;④然后将输入的ASCII码变成相应的数字,再利用换码指令XLAT查表得到的相应的字型码;⑤将字型码送到8255输出口所接的数码管显示。

四、硬件连线实验箱上设有两个共阴极七段数码管及驱动电路,如下图示,段码为同相驱动器,位码为反向驱动器,从段码与位码的驱动器输入端(段码输入端:a、b、c、d、e、f、dp,位码输入端:s1、s2)输入不同的代码即可显示不同数字或符号。

连接电路时,将8255的A口PA0~PA6分别与七段数码管的段码驱动输入端a~g相连,位码驱动输入端S1,S0接8255C口的PC1,PC0。

连线时:CS——288H~28FH,PA0——a,PA1——b,PA2——c,PA3——d,PA4——ePA5——f,PA6——g,dp——GND,PC0——S0,PC1——S1四、程序流程图五、实验程序stack segment stackdw 100 dup(?)stack ends;data segmentx1 db 2 dup(0)val db 3fh,06h,5bh,4fh,66h,6dh,7dh,7fh porta equ 0ef00h-280h+288hportb equ 0ef00h-280h+289hportc equ 0ef00h-280h+28ahportcrl equ 0ef00h-280h+28bhdata ends;code segmentassume cs:code,ss:stackmain procmov ax,datamov ds,axmov al,10000010bmov dx,portcrlout dx,almov si,offset x1mov cx,2next1: call keyinand al,0fhmov si,[al]inc siloop next1mov si,offset x1mov bx,offset valnext: mov dx,portamov al,[si]out dx,almov dx,portcmov al,10bout dx,alcall delaymov dx,portamov al,[si+1]xlatout dx,almov dx,portcmov al,01bout dx,alcall delaymov dl,0ffhmov ah,6int 21hjz nextmov ah,4chint 21hmain endp;delay procpush bxpush cxmov bx,100mov cx,0next2: loop next2 dec bxjnz next2pop cxpop bxret;keyin procagain: mov ah,8int 21hcmp al,30hjb againcmp al,39hja againpush axmov dl,almov ah,2int 21hpop axkeyin endp;code endsend main六、结论符合预期,输入两个数字,七段数码管显示这两个数字。

EDA7段数码显示译码器设计(精)

EDA技术实验报告实验项目名称:7段数码显示译码器设计实验日期:2012.06.04实验成绩:实验评定标准:1)实验程序是否正确2)实验仿真、结果及分析是否合理3)实验报告是否按照规定格式实验目的实验器材学习7段数码显示译码器设计,学习VHDL的CASE语句应用及多层次设计方法。

Quartusll7.2 软件三、实验内容(实验过程)1、首先设计一个2选1的数据选择器(1)打开软件,选择菜单file —>new,在弹出的new对话框中选择Device Design Files 的VHDL File项,按OK键后进入VHDL文本编辑方式。

根据7段数码显示译码器的功能编辑相应的源程序。

如下: library ieee;use ieee.std」o gic_1164.all;en tity decl7s isport (a:i n std_logic_vector(3 dow nto 0; led7s:out std」o gic_vector(6 dow nto 0; end decl7s;architecture one of decl7s isbeg inprocess(abeg incase a iswhe n"0000"=>led7s<="0111111";whe n"0001"=>led7s<="0000110";whe n"0010"=>led7s<="1011011";whe n"0011"=>led7s<="1001111";whe n"0100"=>led7s<="1100110";whe n"0101"=>led7s<="1101101";whe n"0110"=>led7s<="1111101";whe n"0111"=>led7s<="0000111";whe n"1000"=>led7s<="1111111";whe n"1001"=>led7s<="1101111";whe n"1010"=>led7s<="1110111";whe n"1011"=>led7s<="1111100";whe n"1100"=>led7s<="0111001";whe n"1101"=>led7s<="1011110";whe n"1110"=>led7s<="1111001";whe n"1111"=>led7s<="1111001";whe n others =>nu II;end case;end process;end one;2、对该VHDL语言进行编辑后,无误后进行仿真。

EDA实验二_VHDL七段数码管显示译码

EDA实验二七段数码管显示译码的设计一、实验目的1、掌握七段数码管译码器的工作原理;2、学会运用波形仿真测试检验程序的正确性;3、学会运用波形仿真测试检验程序的正确性。

二、实验设备ZYE1502C型实验箱三、内容要求1、用拨位开关输入8421BCD码,七段数码管显示“0-F”16个16进制的数字。

2、观察字符亮度和显示刷新的效果:(1)在8个七段数码管上同时显示某一数字;(2)在8个七段数码管上动态显示某一数字。

3、扩展内容:(1)动态显示时,能即时改变显示的顺序;(2)动态显示时,实现显示数字从0~F的循环显示。

四、实验步骤1、输入:设计部分采用VHDL语言完成;2、编译;3、仿真;4、下载;5、连线。

(1)四个拨位开关(在P1、P2处选择)连接D3、D2、D1、D0信号所对应的管脚。

时钟CLK所对应的管脚同实验箱上的时钟源相连。

(2)扫描片选信号DIG(0 TO 3)的管脚同七段数码管(共阴)相连;(3)七段数码管驱动信号A,B,C,D,E,F,G的管脚分别同扫描数码管的段输入PCLK处的连接线孔A,B,C,D,E,F,G相连。

五、实验报告1、论述实验过程和步骤;2、填写正确的实验结果。

(1)通过两种显示效果分析:字符显示亮度同扫描频率的关系,且让人眼感觉不出光闪烁现象的最低扫描频率是多少?答:扫描频率越高,显示亮度越低。

人眼看是否闪烁与所用的时钟和分频方式有关,在频率稳定和分频均匀的情况下,最低扫描频率为256Hz,若分频不均匀或频率不稳定,则需更高频率。

(2)字形编码的种类,即一个7段数码管可产生多少种字符,产生所有字符需要多少根被译码信号线?答:一个7段数码管可产生2^7=128种字符,产生所有字符至少需要7根被译码信号线。

但假如只编译0-F,16个字符,则至少只需要4根被译码信号线。

六、实验小结。

答:1、不同控制端需要预先分配控制优先级,否则编写的时候会出现很多问题。

优先级分为普通和特殊,一般错误情况可以跨越权限显示出来。

EDA实验报告31_十六进制7段数码管显示译码设计

实验结果及分析

1.十六进制计数器计数到“1111”时cout产生进位信号

2.每一次计数对应数码管不同的显示译码输出,由顶层文件nt_7seg_top.vhdl的时序仿真波形图可见,当数码管显示到“71”即对应的十六进制“F”时,计数值清零(rst0 <= ‘0’),数码管重新从“3F”即‘1’递增至‘F’循环显示。

2.输出信号LED_7seg的7位分别接数码管的7个段a-b-c-d-e-f-g(-h),高位在左,低位在右(如果有小数点,增加h段)。由于使用的是共阴极数码管,各个段接高电平时发光,低电平不亮。

实验内容

实验一:十六进制7段数码显示译码设计

1.用VHDL文本输入方法,完成十六进制计数器和7段数码显示译码电路设计

EDA技术与应用实验报告

姓名

学号

专业年级

电子信息工程

实验题目

十六进制7段数码显示译码设计

实验目的

1.学习7段数码显示译码设计和硬件验证

2.通过VHDL语言设计7段数码显示译码电路,进一步掌握层次化设计方法

实验原理

1.数字系统中的数据处理和运算都是二进制的,输出表达为十六进制数。为了满足十六进制数的译码显示,可利用译码程序在FPGA/CPLD中来实现

3.将clk0接到78脚的时钟输出端,可以获得0-1MHz的时钟调节范围,这解决了数码管循环显示过快,看不清译码输出的问题

附录

(原理图或VHDL代码)

实验过程中所遇到的问题及相应的解决方法

7段显示译码器设计实验报告

数字钟实验报告学生专业:电子信息工程学生班级:151143C学生学号:*********学生姓名:***7段显示译码器设计151143324 ***一、实验目的:学习七段数码显示译码器设计,多层次设计方法和总线数据输入方式的仿真。

二、实验原理:7段BCD码译码器的设计,输出信号Segmentout的7位分别接数码管的7个段,高位在左,低位在右。

例如当Segmentout输出为“1101101”时,数码管的7个段:g、f、e、d、c、b、a分别接1、1、0、1、1、0、1,接有高电平的段发亮,于是数码管显示数字“5”。

如果是共阳极的数码显示器,则8段输出应取反,段显码为“10010010”,使用时要注意数码管的接法。

实际产品设计中,一般会用到多个数码管,显示几位数字。

4位数的7段数码管,4位数字共用同样的段输出。

若只想让第一个位显示,其他的位不显示,那么可以只给第一位数字供电,其他的断电,用4LED来控制的,4LED输出0001即可,若只让第二位显示则4LED输出0010即可。

这里的4LED选择控制要显示的位,称为位选。

三、实验内容:module BCD_Segment7(BCDin,Segmentout,Select);input[3:0]BCDin;output Select;output [6:0]Segmentout;reg[6:0]Segmentout;always@(BCDin)begincase(BCDin)4'h0:Segmentout=7'b1000000;4'h1:Segmentout=7'b1111001;4'h2:Segmentout=7'b0100100;4'h3:Segmentout=7'b0110000;4'h4:Segmentout=7'b0011001;4'h5:Segmentout=7'b0010010;4'h6:Segmentout=7'b0000010;4'h7:Segmentout=7'b1111000;4'h8:Segmentout=7'b0000000;4'h9:Segmentout=7'b0010000;4'hA:Segmentout=7'b0001000;4'hB:Segmentout=7'b0000011;4'hC:Segmentout=7'b1000110;4'hD:Segmentout=7'b0100001;4'hE:Segmentout=7'b0000110;4'hF:Segmentout=7'b0001110;default:Segmentout=7'bxxxxxxx;endcaseendassign Select=1'b0;endmodule四、时序仿真波形:引脚设定时序仿真波形参考设置:1、设置仿真时间。

EDA 数码管七段 译码电路

实验三数码管七段译码电路一、实验目的1、了解组合逻辑电路设计2、制作一个数码管显示的7段译码电路,以备后面的实验调用3、学习在QUARTUS II中实用VHDL设计功能模块,并将所生成的功能模块转换成QUARTUS II原理图的符号库,以便在使用原理图时调用该库二、实验内容1、实验前的准备(1)该实验不使用七个模块组各个功能单元,所以三个拨码开关处于“111”即MODEL_SEL1-3 拨下处于“ON”状态时,使用实验仪上的固定连接。

(2)拨码开关MODEL_SEL5-8 全置于“ON ”状态,即MODEL_SEL5-8 拨下处于“ON ”状态时通过USB BLASTER 接口下载。

(3)MODEL_SEL4 的状态可以处于任何状态。

2、实验步骤第一个实验:应用六个共阴极数码管显示译码结果,即用拨码开关产生8421BCD码,FPGA 器件产生译码电路,把BCD码显示在LED数码管上。

(一)创建工作库文件夹和编辑设计文件步骤1:建立工作库文件夹Fil e→New→VHDL File步骤2:输入设计项目VHDL文本相应程序如下:步骤3:存盘,注意原理图(文本)取名*(必使文件名与工程名相同,本文档名为:xdeled),并把文件存在新建的工作库文件夹中File→Save As(二)创建工程步骤4:创建工程(注意:名字不能与刚的文本文件同名,例如叫:yangxing)直接利用第3步创建或者File→New Project Wizard步骤5:将设计文件加入工程中(一般已加入)步骤6:选择仿真器和综合器类型(默认)步骤7:选择目标芯片Assignments→Device 选择EP2C35F672芯片,其中的其它选项Family:CycloneII;Pin count:672; Speed grade:8;Package:TQFP;步骤8:工具设置(默认)步骤9:结束设置(三)由VHDL程序代码创建模块:fil e→create/_update→create symbol files for current file(四)建立工作库文件夹和编辑设计文件步骤1:建立工作库文件夹步骤2:输入设计项目原理图或VHDL文本File→New→Block Diagram File/Schematic File (VHDL File)(调用元件的方式:在图形编辑器空白处单击鼠标左键确定输入位置,然后选择Edit→Insert Symbol,或双击鼠标左键)自己创建的器件xdeled在project里步骤3:存盘,注意原理图(文本)取名,并把文件存在新建的工作库文件夹中File →Save As (注意:取名应和工程名相同,为:yangxing)图如下:(五)编译前设置步骤10:选择目标芯片Assignments→Device 为芯片:EP2C35F672步骤11:选择配置器件的工作方式。

EDA 7段LED显示译码器的设计

《EDA技术》课程实验报告学生姓名:**所在班级:**指导教师:**记分及评价:报告满分3分得分一、实验名称实验5:7段LED显示译码器的设计二、任务及要求1、在QuartusII平台上,采用文本输入设计方法,通过编写VHDL语言程序,完成7段LED显示译码器的设计并进行时序仿真。

2、设计完成后生成一个元件,以供更高层次的设计调用。

3、实验箱上进行验证。

三、实验程序library ieee;use ieee.std_logic_1164.all;entity smg isport(d:in std_logic_vector(3 downto 0);seg:out std_logic_vector(7 downto 0);seg_sel:out std_logic);end;architecture one of smg isbeginseg_sel <= '0';seg <= X"C0" when d="0000" elseX"F9" when d="0001" elseX"A4" when d="0010" elseX"B0" when d="0011" elseX"99" when d="0100" elseX"92" when d="0101" elseX"82" when d="0110" elseX"F8" when d="0111" elseX"80" when d="1000" elseX"90" when d="1001" elseX"FF";end;四、仿真及结果分析五、硬件验证1、引脚锁定情况表:六、小结在之前的实验中我们对EDA已经有了初步的了解,所以这次实验是我们巩固EDA这门学科的一次好机会。

太原理工大学EDA实验 显示译码器

太原理工大学EDA实验显示译码器实验三显示译码器一、实验目的和要求1、学习七段显示译码器设计。

2、学习进程PROCESS和CASE语句的设计方法。

3、熟悉VHDL文本输入设计的流程。

二、实验内容和原理1、完成显示译码器的VHDL描述2、在isDensignEXPERT System 或者QuartusⅡ上对显示译码器的VHDL描述进行编辑、编译、综合、适配、仿真,给出其所有信号的时序仿真波形。

3、进行引脚锁定以及硬件下载测试。

三、主要仪器设备装有QuartusⅡ软件的电脑 Altera实验箱四、操作方法与实验步骤1、打开软件,新建一个VHDL File文件,输入需要设计的程序。

2、对该VHDL 语言进行编辑,无误后进行编译。

3、编译完成后分配管脚,之后进行编译4、把实验箱连接好电源和计算及接口,把程序下载下来,即可在实验箱上通过按键和发光二极管来检验实验的正确性。

5、实验成功,七段显示数码管可显示从0~15的所有数字。

五、实验数据记录和处理实验程序: LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL; ENTITY CHAI ISPORT(X :IN STD_LOGIC_VECTOR(3 DOWNTO 0);Y :OUT STD_LOGIC_VECTOR(6 DOWNTO 0)); END CHAI;ARCHITECTURE BEHAVE OF CHAI ISSIGNAL INDATA:STD_LOGIC_VECTOR(3 DOWNTO 0); BEGIN INDATA<=X;PROCESS(INDATA) BEGINCASE INDATA ISWHEN\WHEN\WHEN\WHEN\WHEN\WHEN\WHEN\WHEN\WHEN\WHEN\WHEN\WHEN\WHEN\WHEN\WHEN\WHE N\WHEN OTHERS=>Y<=NULL;END CASE;END PROCESS; END BEHAVE;七段译码管引脚分布:仿真结果:六、实验感想通过这次实验,我掌握了VHDL语言的写法,更加全面的掌握了QuartusⅡ的用法,为我们之后的学习应用打下了良好的基础。

EDA实验报告 序列检测器 七段数码显示译码 数控分频 全加器

目录:实验一:序列检测器设计 (1)1.1 实验原理 (1)1.2 实现方案与仿真 (1)1.2.1 预置数确定 (1)1.2.2 预置数待定 (2)1.3 引脚锁定与下载 (3)1.3.1 预置数确定 (3)1.3.2 预置数待定 (3)1.4 实验结论与总结 (4)1.5 附录 (4)实验二七段数码显示译码器设计 (6)2.1 实验原理 (6)2.2 实现方案与仿真 (6)2.2.1 七段显示译码的方案与仿真 (6)2.2.2 4位二进制加法计数器的方案与仿真 (7)2.2.3 顶层文件的方案与仿真 (7)2.3 引脚锁定与下载 (8)2.3.1 七段显示译码的硬件测试 (8)2.3.2 4位二进制加法计数器的硬件测试 (8)2.3.3 顶层文件的硬件测试 (8)2.4 实验结论与总结 (9)2.5 附录 (9)实验三数控分频器的设计 (10)3.1 实验原理 (10)3.2 实现方案与仿真 (10)3.2.1 数控分频器的实现方案与仿真 (10)3.2.2数控分频器的RTl电路图 (11)3.3 引脚锁定与下载 (11)3.4 实验结论与总结 (12)实验四用原理图输入法设计8位全加器 (13)4.1 实验原理 (13)4.1.1 一位全加器的原理 (13)4.1.2 八位全加器的原理 (13)4.2 实现方案与仿真 (13)4.2.1 一位全加器的实现方案与仿真 (13)4.2.2 八位全加器的实现方案与仿真 (15)4.3 引脚锁定与下载 (16)4.3.1 一位全加器的引脚锁定与下载 (16)4.3.2 八位全加器的引脚锁定与下载 (16)4.4 实验结论与总结 (17)实验一:序列检测器设计摘要:本实验的主要任务是通过状态机来实现序列检测器的设计,其中,本实验采用了单进程Moore状态机和多进程Moore状态机两种方案来实现序列检测器,进而通过软件仿真和硬件测试来检验所设计的序列检测器。

实验三七段数码显示译码器的设计

实验三七段数码显示译码器的设计[实验目的]1、熟悉QuartusII完成基本组合电路的设计;2、学习7段数码显示译码器设计;3、学习VHDL的CASE语句应用及多层次设计方法。

*[实验仪器]PC机、EDA实验箱一台Quartus II 6.0软件[实验内容](1) 实验内容1:说明例6-1中各语句的含义,以及该例的整体功能。

在QuartusII上对该例进行编辑、编译、综合、适配、仿真,给出其所有信号的时序仿真波形。

提示:用输入总线的方式给出输入信号仿真数据,仿真波形示如图6-1所示。

(2) 实验内容2:引脚锁定及硬件测试。

建议选GW48系统的实验电路模式6,用数码8显示译码输出(PIO46-PIO40),键8、键7、键6和键5四位控制输入,硬件验证译码器的工作性能。

(3) 实验内容3:按图6-3的方式连接成顶层设计电路(用VHDL表述),图中的CNT4B是一个4位二进制加法计数器;模块DECL7S即为例6-1实体元件,重复以上实验过程。

注意图6-3的tmp是4位总线,led是7位总线。

对于引脚锁定和实验,建议选电路模式6,用数码8显示译码输出,用键3作为时钟输入(每按2次键为1个时钟脉冲),或直接接时钟信号clock0。

[实验原理]7段数码是纯组合电路,通常的小规模专用IC,如74或4000系列的器件,只能作十进制BCD码译码,然而数字系统中的数据处理和运算都是2进制的,所以输出表达都是16进制的,为了满足16进制数的译码显示,最方便的方法就是利用译码程序在FPGA/CPLD中来实现。

例6-18作为7段译码器,输出信号LED7S的7位分别接如图6-2数码管的7个段,高位在左,低位在右。

例如当LED7S输出为“1101101”时,数码管的7个段:g、f、e、d、c、b、a分别接1、1、0、1、1、0、1;接有高电平的段发亮,于是数码管显示“5”。

注意,这里没有考虑表示小数点的发光管,如果要考虑,需要增加段h,例6-1中的LED7S:OUT STD_LOGIC_VECTOR(6 DOWNTO 0)应改为... (7 DOWNTO 0) 。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

河北科技大学

实验报告

2013级电信专业132 班学号130701213 2016年6月7日

姓名田继辉同组人指导教师于国庆

实验名称实验三七段译码显示成绩

实验类型设计型批阅教师

一、实验目的

(1)掌握VHDL语言的行为描述设计时序电路。

(2)掌握FPGA动态扫描显示电路设计方法。

(3)熟悉进程(process)和顺序语句的应用。

二、实验原理:

用4个开关作为加法器的一组输入变量,共4组输入变量;对每组变量进行译码,变换成0~F标准段码,段码中“1”表示段亮,“0”表示段灭。

一位时钟输入作为扫描显示位扫时钟,四位位扫输出,依次输出高电平。

8位段码输出,根据位选状态选择输出四组输入变量的相应译码结果。

四组输入采用试验箱K1~K16,时钟输入选择试验箱CP1或CP2;试验箱LED显示选择动态显示方式(CZ1开关ST选择OFF),段码、位码分别扫描输出,某个管的位码有效期间,将其对应的段码输出,各位码依次有效,实现循环扫描显示,将输入的16位二进制数,每4位一组,分别显示到4个数码管上(0~F)。

三、实验内容及步骤

1.打开MUXPLUS II VHDL编辑器,完成七段译码显示的设计。

包括VHDL程序输入、编译、综合。

实验程序如下:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

ENTITY alpher IS

PORT(

clk : IN STD_LOGIC;

choice : OUT STD_LOGIC_VECTOR(7 downto 0);

data : OUT STD_LOGIC_VECTOR(7 downto 0)); END alpher;

ARCHITECTURE a OF alpher IS

SIGNAL count : STD_LOGIC_VECTOR(3 downto 0); SIGNAL temp : STD_LOGIC_VECTOR(3 downto 0);

BEGIN

choice<="10000000";

clk1_label:

PROCESS (clk)

BEGIN

IF clk'event and clk='1' THEN

count<=count+1;

END IF;

END PROCESS clk1_label;

WITH count select

data <= "11111100" WHEN "0000",

"01100000" WHEN "0001",

"11011010" WHEN "0010",

"11110010" WHEN "0011",

"01100110" WHEN "0100",

"10110110" WHEN "0101",

"10111110" WHEN "0110",

"11100000" WHEN "0111",

"11111110" WHEN "1000",

"11110110" WHEN "1001",

"11101110" WHEN "1010",

"00111110" WHEN "1011",

"10011100" WHEN "1100",

"01111010" WHEN "1101",

"10011110" WHEN "1110",

"10001110" WHEN OTHERS;

END a;

2、建立仿真波形文件,使用MAXPLUS II Simulator功能进行功能仿真。

仿真结果如下:

3、目标器件选择与管脚锁定并重新编译、综合、适配。

FPGA型号:EP1K100QC208-3

引脚绑定:

4、下载并验证结果

7段数码是纯组合电路,通常的小规模专用IC,如74或4000系列的器件只能作十进制BCD 译码器,然而数字系统中的数据处理和运算都是二进制的,所以输出表达都是十六进制的,为了满足十六进制数的译码显示,最方便的方法就是利用译码程序在FPGA/CPLD中来实现。

实验采用动态扫描的方式进行输出译码结果,将引脚进行绑定与硬件配置后便可将程序下载到芯片中。

通过按实验箱上的单步按键,即可手动实现数码管连续并循环显示数值0、1、2、3、4、5、6、7、8、9、A、B、C、D、E、F;如果将时钟脉冲相应的引脚连接上,即可实现间隔为2或4或8等等的数值跳变,这是自动显示方式。

除此之外,默认只有数码管左边第一个显示数值,其余七位均不显示。

如果要求第一个不显示,其余的七个亮,可以修改程序,将控制数码管位选的变量由10000000改为01111111;要显示别的内容,对七段数码管进行编码,让需要的位选端打开即可。

四、实验结果与总结

学习了7段数码显示译码器设计,学习了VHDL的CASE语句应用及多层次设计方法,使我们对EDA这门学科的认识更进了一个层次。

在手忙脚乱而又充实的实验中,我们认真分析程序,弄清实验原理,在做实验时有耐心、认真,遇到问题争取自己解决。

为了下次更好发挥,我们认真总结实验,分析波形,完成实验报告。

通过此次实验,我们进一步熟悉了7段数码显示译码器的VHDL描述方法。

对VHDL的使用有了更深入的了解。

通过这次设计我们了解并掌握VHDL硬件描述语言的设计方法和思想,使自己能将已学过的数字电子系统设计、VHDL程序设计等知识综合运用于电子系统的设计中,基本掌握了运用VHDL 设计电子系统的流程和方法,加强和培养了自己对电子系统的设计能力。

我们也了解了VHDL

的一些知识,VHDL主要用于描述数字系统的结构,行为,功能和接口。

除了含有许多具有硬件特征的语句外,VHDL的语言形式和描述风格与句法是十分类似于一般的计算机高级语言。

VHDL 的程序结构特点是将一项工程设计,或称设计实体(可以是一个元件,一个电路模块或一个系统)分成外部(或称可是部分,及端口)和内部(或称不可视部分),既涉及实体的内部功能和算法完成部分。

在对一个设计实体定义了外部界面后,一旦其内部开发完成后,其他的设计就可以直接调用这个实体。

这种将设计实体分成内外部分的概念是VHDL系统设计的基本点。

VHDL 语言作为一种国际标准化的硬件描述语言,自1987年获得IEEE批准以来,经过了1993年和2001年两次修改,至今已被众多的国际知名电子设计自动化(EDA)工具研发商所采用,并随同EDA设计工具一起广泛地进入了数字系统设计与研发领域,目前已成为电子业界普遍接受的一种硬件设计技术。

VHDL语言的运用提高了我们设计电子系统的效率,简单实用,也在此次设计中提升了我们自身运用所学知识的能力,也更加体会出作为团队中的一员要以团队思想为主题发展自己的思维。