数据时钟恢复(CDR)工作原理及Altera的ASISDIIPcore应用.

一种新型的高速时钟数据恢复电路的设计和验证

一种新型的高速时钟数据恢复电路的设计和验证摘要:1.背景和动机2.电路设计原理3.具体设计方案4.验证和测试5.结果和分析6.结论和展望正文:一、背景和动机随着现代通信技术的快速发展,高速数据传输已经成为通信系统中的关键技术。

在高速数据传输过程中,时钟数据恢复电路(CDR)作为核心模块,对于确保数据传输的准确性和稳定性具有至关重要的作用。

本文针对一种新型的高速时钟数据恢复电路进行设计和验证,以满足不断提高的通信速率需求。

二、电路设计原理本文提出的高速时钟数据恢复电路主要基于数字信号处理技术,通过捕获和恢复发送端时钟信号的相位信息,实现接收端时钟与发送端时钟的同步。

电路设计的关键部分包括:高速锁相环电路、复用CDR环路、滤波器和相位插值控制电路。

三、具体设计方案1.高速锁相环电路:采用1.25GHz的参考时钟,通过16相频锁相环技术,提供数据恢复所需的等相位间隔参考时钟。

2.复用CDR环路:采用电流逻辑模式前端电路,构成复用CDR环路,以实现对高速数据信号的恢复。

3.滤波器和相位插值控制电路:设计滤除亚稳态时钟的采样超前、滞后鉴相器,以及选择时钟与相位插值的控制时钟电路。

四、验证和测试通过对所设计的高速时钟数据恢复电路进行数模混合仿真检测,验证电路在实际应用环境中的性能。

测试结果表明,该电路具有较高的恢复准确性和稳定性。

五、结果和分析本文提出的高速时钟数据恢复电路在仿真测试中表现出良好的性能,为实现高速数据传输提供了有效的同步解决方案。

相比传统电路设计,该方案具有更高的恢复速度和更低的功耗,有助于提高通信系统的整体性能。

六、结论和展望本文针对一种新型的高速时钟数据恢复电路进行了详细的设计和验证。

通过采用数字信号处理技术,实现了高精度、高速度的时钟信号恢复。

Clock and Data Recovery (CDR)

数据时钟恢复(CDR)

发送端不发送CLK信号,而是有接收端给据数据恢复出时钟, 并据此锁存数据。 常用的BUS: USB,SATA,PCI-E,…

编码举例 8b/10b

HGF EDCBA

Dx.y

abcdei fghj

RD=-1 :0比1多 RD=+1:1比0多 RD初始值為-1

8b/10b Encoding

A與B相位差=QA-QB

Hogge Phase Detector

鎖定狀態時,charge pump 輸出 電壓Vout在產生一個向上的紋波 ,隨即產生一個向下的紋波, Vout直流電平保持不變。

HPD鎖定前後理論波形示意圖

細節變化將 體現在 simulation中

X =1/2 TCLK Y =Din與CLK相位差

Clock and Data Recovery

数据时钟恢复 Stanley Team

Agenda

数据同步方式 数据时钟恢复 编码 时钟的提取

源同步(SS)

发送端同时传递时钟与数据信号给接收端。 接收端根据时钟锁存数据。 常用的Bus: PCI,LPC,SPI,I2C,SMBUS,DDR(I ,II, III), …

Digital Receiver

原理——滤波法实现CDR

Data Recovery with simple PLL

Incoming Date

Architecture of the designed PLL

1 頻率鎖定在 預定中心頻率

2 相位鎖定

Phase and Frequency Detector

8b/10b Encoding

/8b10b.php 这是我们模拟的PHP实现,您可以上去体会8b/10b的编码。HW部分, 可以用不同的算法,使用Verilog/VHDL 在FPGA里实现。

电脑芯片制造中的时钟与数据恢复技术分析

电脑芯片制造中的时钟与数据恢复技术分析在如今信息技术高速发展的时代,电脑芯片的制造越发重要。

无论是消费电子产品还是大型计算机系统,芯片的稳定性和可靠性都直接影响着设备的性能和用户体验。

其中,时钟与数据恢复技术作为电脑芯片制造中具有关键意义的部分,其功能和应用不容小觑。

本文将对电脑芯片制造中的时钟与数据恢复技术进行深入分析。

一、时钟技术的作用和原理时钟技术在电脑芯片制造中起着重要的作用。

时钟信号的稳定性直接影响着芯片内部各个电路的同步运作。

时钟信号可以看作是芯片内部各个电路的节拍器,通过提供精确的时间基准来控制芯片内部电路的工作状态。

时钟技术的原理主要包括两个方面:时钟源的产生和时钟分配。

时钟源的产生需要采用高精度的晶体振荡器,以产生稳定且准确的时钟信号。

而时钟分配则需经过专门的时钟配送网络,将时钟信号分发给芯片内部的各个功能模块。

二、时钟技术在数据传输中的作用在现代电脑芯片中,数据传输是一个核心问题。

而时钟技术在数据传输中起到了关键的作用。

数据传输需要在发送端和接收端之间精确地进行时钟同步,以确保数据的正确接收。

时钟技术通过提供一个统一的时间基准,使得发送端和接收端可以根据时钟信号在相同的时间点进行数据采集和传输。

具体来说,时钟技术可以帮助解决以下问题:时钟偏移、时钟抖动和时钟漂移。

时钟偏移是指发送端与接收端的时钟频率存在微小差异,而时钟抖动是时钟信号存在固定和随机的幅度波动。

而时钟漂移则是指时钟信号的频率在传输过程中逐渐发生变化。

针对这些问题,电脑芯片制造中的时钟与数据恢复技术应运而生。

三、数据恢复技术的原理和应用数据恢复技术是指在数据传输中通过特定的电路和算法,将接收到的模糊信号恢复为较为清晰和准确的数据。

在电脑芯片制造中,数据恢复技术常常与时钟技术相结合,实现对时钟抖动和时钟漂移等问题的克服。

数据恢复技术的原理主要包括两个方面:定时误差检测和决策电路。

定时误差检测是通过比较接收信号与本地时钟信号的差异,计算出信号的整体延迟,从而进行时钟相位调整。

高速串行通信系统设计中的时钟恢复技术

高速串行通信系统设计中的时钟恢复技术在高速串行通信系统设计中,时钟恢复技术起着至关重要的作用。

时钟恢复技术是指在通信过程中确保接收端能够正确恢复发送端的时钟信号,从而保证数据的准确传输。

下面将介绍高速串行通信系统设计中的时钟恢复技术的原理和方法。

首先,要了解为什么需要时钟恢复技术。

在高速串行通信系统中,由于信号传输距离远、传输速率高,信号在传输过程中受到多种因素的影响,例如传输介质的损耗、延迟等,导致接收端无法准确识别发送端的时钟信号。

如果接收端无法正确恢复时钟信号,就会导致数据传输错误,严重影响通信质量。

为了解决时钟信号恢复问题,一种常用的方法是采用时钟数据恢复电路。

时钟数据恢复电路通过对接收到的数据进行采样、比较和调整,从而恢复出正确的时钟信号。

常见的时钟数据恢复电路包括延时锁相环(DLL)和相位锁定环(PLL)。

延时锁相环是一种常用的时钟恢复技术,它通过调整延时单元的延时时间,使接收端的时钟信号与发送端的时钟信号同步。

延时锁相环通常包括相位检测器、环路滤波器和延时单元。

相位检测器用于检测两个时钟信号之间的相位误差,环路滤波器用于对误差进行滤波和放大,延时单元用于根据误差信号调整延时时间。

相位锁定环是另一种常用的时钟恢复技术,它通过比较接收端数据的相位和发送端的时钟信号相位,从而调整本地时钟信号的频率和相位,使两者同步。

相位锁定环通常包括相位频率检测器、环路滤波器和调节单元。

相位频率检测器用于检测相位和频率误差,环路滤波器用于对误差进行滤波和放大,调节单元用于根据误差信号调整本地时钟信号。

除了延时锁相环和相位锁定环,还有其他一些时钟恢复技术,如周期估计法、数据边界对齐法等。

这些技术在不同的通信系统中有着不同的应用,选择合适的时钟恢复技术对于提高通信系统的性能至关重要。

总的来说,时钟恢复技术在高速串行通信系统设计中扮演着关键的角色。

通过合理选择和设计时钟恢复电路,可以保证通信系统在高速传输时能够准确恢复时钟信号,确保数据的准确传输。

集成电路设计中的时钟及数据恢复技术

集成电路设计中的时钟及数据恢复技术时钟及数据恢复技术在集成电路设计中起着至关重要的作用。

时钟信号是整个系统的引擎,它同步着各个模块的工作,确保数据的准确传输和处理。

数据恢复技术则是为了解决信号传输中的噪声和失真问题,保证数据的完整性和可靠性。

本文将探讨时钟及数据恢复技术在集成电路设计中的应用和挑战。

一、时钟信号的重要性时钟信号是集成电路中的基准信号,它提供了一个统一的时间参考,使得各个模块能够协调工作。

在高速通信和数据处理领域,时钟信号的稳定性和准确性尤为重要。

一个好的时钟设计可以提高系统的性能和可靠性,同时减少功耗和噪声。

在时钟设计中,有几个关键的参数需要考虑。

首先是时钟频率,它决定了系统的处理速度。

高频时钟可以提高系统的响应速度,但也会带来更多的功耗和噪声。

其次是时钟的相位和抖动。

相位是时钟信号的起始时间,抖动是时钟信号的波动情况。

相位和抖动的不稳定会导致数据传输和处理的错误。

因此,在时钟设计中需要采取一系列措施来控制这些参数,例如使用锁相环(PLL)和时钟缓冲器。

二、数据恢复技术的应用数据恢复技术是为了解决信号传输中的噪声和失真问题,确保数据的准确传输和处理。

在高速通信和存储系统中,数据恢复技术尤为重要。

它可以有效地提高系统的抗噪声能力和数据传输速度。

常见的数据恢复技术包括时钟恢复、时钟数据恢复和信号再生。

时钟恢复是为了从复杂的数据信号中提取出时钟信号。

时钟数据恢复则是将时钟信号和数据信号分离开来,以便进行后续的处理。

信号再生则是为了恢复信号的形状和幅度,使其符合接收器的要求。

在数据恢复技术中,有几个关键的问题需要解决。

首先是时钟恢复的准确性和稳定性。

由于传输中的噪声和失真,时钟信号可能会被扭曲和改变。

因此,需要采用一些算法和技术来提取出准确的时钟信号。

其次是数据信号的恢复和再生。

由于传输中的噪声和失真,数据信号可能会被扭曲和丢失。

因此,需要采用一些算法和技术来恢复和再生数据信号。

三、时钟及数据恢复技术的挑战时钟及数据恢复技术在集成电路设计中面临着一些挑战。

时钟数据恢复(CDR)

时钟数据恢复(CDR)2009-11-01 21:40 5887人阅读评论(5) 收藏举报测试图形ui产品工作任务近年来,芯片功能的增强和数据吞吐量要求推动了芯片产业从低速率数据并行连接转变到高速串行连接。

这个概念被称为SERDES(Serializer-Deserializer),包括在高速差分对上串行地传送数据,而不是用低速的并行总线。

一个典型例子是用单个PCI-Express通道取代数据速率达2.112Gbps的传统32位66MHz PCI总线,PCI-Express可达到4Gbps的数据速率,但仅使用了工作在2.5GHz的4条线。

简而言之,SERDES协议允许用较少的引脚实现较高的数据速率。

图1给出了各种可能的SERDES接口。

这个例子展示了一个网络处理器位于系统中心的高性能电路板。

SERDES应用用紫色标明,可以用FPGA实现的芯片用黄色标明。

图1:典型的SERDES应用。

SERDES的类型有两种基本类型的SERDES接口:源同步(SS)协议和时钟数据恢复(CDR)协议。

这两种类型的主要差别是如何实现时钟控制。

源同步接口拥有一个伴随传送数据的时钟信号;CDR 没有单独的时钟信号,而是把时钟嵌入在数据中。

即CDR接收器将相位锁定在数据信号本身以获取时钟。

表1概括了这两种接口的基本差别。

表1:源同步和时钟数据恢复SERDES接口的比较。

通常CDR协议运行在较高的数据速率和较长的传送距离,因此带来很大的设计挑战。

时钟数据恢复的基础顾名思义,CDR接收器必须从数据中恢复嵌入的时钟。

更准确地说,是从数据信号的交换中获取时钟。

CDR发送器首先串行发送数据,然后将数据转换成8b/10b编码方案。

编码处理获得8位数据并将其转换成10位符号。

8b/10b编码方式可以在数据线上传送相等数目的0和1,从而减少码间干扰,并提供足够多的数据边沿,以便接收器在收到的数据流上锁定相位。

发送器将系统时钟倍频至传送比特率,并以该速率在TX差分对上发送8b/10b数据。

时钟数据恢复(CDR)

时钟数据恢复(CDR)时钟数据恢复(CDR)引言概述:时钟数据恢复(Clock Data Recovery, CDR)是一种用于恢复数字信号中的时钟信息的技术。

在数字通信中,时钟信号的准确性对于数据的传输和解析至关重要。

CDR技术可以通过对接收到的数字信号进行采样和重构,从而恢复出准确的时钟信息,保证数据的稳定传输和正确解析。

本文将介绍CDR的原理和应用,并详细阐述其在时钟恢复、数据传输和通信系统中的重要性。

一、CDR的原理和工作方式:1.1 采样和重构:CDR通过对接收到的数字信号进行采样,即在固定的时间间隔内对信号进行取样。

采样的目的是获取信号的瞬时状态,并将其转换为离散的数字值。

接着,CDR使用这些采样值来重构时钟信号,即通过插值和滤波等技术将离散的采样值转换为连续的时钟信号。

1.2 相位锁定环路(Phase Locked Loop, PLL):PLL是CDR的核心组成部分,用于将重构的时钟信号与接收到的信号进行比较和调整,以保持两者的相位同步。

PLL通过不断调整重构时钟信号的相位,使其与接收到的信号相位保持一致,从而实现时钟数据的恢复。

1.3 时钟频率调整:CDR还可以根据接收到的信号的频率特性来调整时钟的频率。

通过对信号进行频率分析和比较,CDR可以自动调整时钟频率,以适应信号的变化,确保数据的稳定传输和正确解析。

二、CDR在时钟恢复中的应用:2.1 光纤通信系统:在光纤通信系统中,光信号在传输过程中会受到光纤的衰减和色散等影响,导致信号的失真和时钟信息的丢失。

CDR技术可以通过恢复时钟信息,减小信号失真,提高数据传输的可靠性和稳定性。

2.2 高速串行通信接口:在高速串行通信接口中,时钟信号的准确性对于数据的传输速率和可靠性至关重要。

CDR技术可以通过恢复时钟信号,使接收端能够正确解析数据并保持与发送端的同步,实现高速数据传输。

2.3 数字存储系统:在数字存储系统中,时钟信号的准确性对于数据的读取和写入至关重要。

集成电路设计中的时钟和数据恢复技术

集成电路设计中的时钟和数据恢复技术时钟和数据恢复技术在集成电路设计中起着重要的作用。

时钟信号是控制电路各个部件协同工作的关键,而数据恢复技术则保证了在复杂电路系统中数据传输的可靠性和稳定性。

本文将详细介绍时钟和数据恢复技术在集成电路设计中的原理、应用和挑战。

一、时钟的作用和原理时钟信号在集成电路中充当一个定时器,控制电路各个部件按照特定时序进行操作。

时钟信号的频率和相位准确性对整个电路的性能和功耗都有着重要影响。

时钟信号的频率决定了电路处理能力的上限,而时钟信号的相位决定了电路操作的时序。

高频率时钟可以加快电路的运行速度,但也会增加功耗和散热。

相反,低频率时钟可以降低功耗,但会限制电路的最高工作频率。

因此,时钟的频率选择在平衡功耗和性能上是一个关键的设计考虑因素。

时钟信号通常由时钟发生器产生,发生器可以采用振荡器、频率锁定环或多级分频器等技术来保证时钟信号的质量。

在时钟设计中,需要考虑时钟稳定性、噪声、抖动和时钟切割等问题,以确保时钟信号的准确性和可靠性。

二、时钟与数据恢复技术的应用时钟和数据恢复技术在各个领域的集成电路设计中都有广泛的应用,例如通信、计算机、嵌入式系统等。

在通信领域,时钟和数据恢复技术常用于高速串行接口的设计中,例如以太网、USB、PCI Express等。

这些接口在传输数据时需要复杂的时钟沿和时序控制,时钟和数据恢复技术能够确保数据的传输稳定性和可靠性。

在计算机领域,时钟和数据恢复技术被广泛运用于处理器和内存控制器等核心器件的设计中。

时钟信号的频率和时钟相位对于处理器的性能至关重要,而数据恢复技术则用于解决高速存储器访问时的数据读取和写入问题。

在嵌入式系统中,时钟和数据恢复技术用于控制外设和内核之间的数据传输。

例如,时钟和数据恢复技术可以确保音频输出的时序和质量,同时也可以确保传感器数据的准确性和实时性。

三、时钟和数据恢复技术的挑战时钟和数据恢复技术在集成电路设计中面临着一些挑战。

数据时钟恢复(CDR)工作原理及Altera的ASI、SDI_IPcore应用

© 2004 Altera Corporation - Confidential 16

SVDB Board Overview

1SGX25FF1020 chip 2 SDI IO interfaces

3 VCXOs (27MHz, 74.25MHz (not installed)and 74.175MHz installed) 1 crystals (27MHz)

RP 178

Video Payload Identification for Digital Television Interfaces

SMPTE 352M-2001

Numerous Recommended Practices and Engineering Guidelines

Used for Synchronous Video Switching Definition, Error Detection Schemes, Jitter Measurement, etc…

DVB is a family of European digital video standards DVB-ASI is designed to transport MPEG-2 video stream serially over coax or fiber at up to 270M/s Competes with SMPTE -SDI & HD-SDI -SMPTE 310M Many equipment with SMPTE 310M interfaces also provide DVB-ASI interface

SDI ASI

Success story Summarize

高速数字信号传输设计中的时钟数据恢复算法

高速数字信号传输设计中的时钟数据恢复算法在高速数字信号传输设计中,时钟数据恢复算法扮演着至关重要的角色。

时钟数据恢复算法是指用于从接收到的高速数字信号中恢复出正确的时钟信号和数据的算法。

在数字通信系统中,由于传输介质和其他因素的影响,接收到的信号可能会受到时钟抖动、噪声干扰等问题,导致时钟信号和数据产生偏移或失真。

时钟数据恢复算法的作用就是通过对接收信号进行采样、时钟提取、相位调整等操作,来有效地恢复出正确的时钟和数据。

在高速数字信号传输中,时钟数据恢复算法通常应用在串行通信接口中,用于将串行数据信号还原为并行数据信号。

其中一个常见的时钟数据恢复算法是基于边沿速率的时钟恢复算法。

该算法通过检测接收到的信号中的边沿来生成时钟信号,然后利用这个时钟信号对数据信号进行采样和恢复。

另一个常见的算法是相关性检测算法,它通过对接收信号进行相关性分析,来估计时钟信号和数据信号之间的关系,进而进行时钟数据恢复。

时钟数据恢复算法的设计需要考虑到多个方面的因素,包括传输介质特性、信号特点、抖动噪声情况等。

首先,需要对接收信号的波形进行分析,了解信号中的时钟信息和数据信息的特点,进而选择合适的恢复算法。

其次,针对不同的传输介质和抖动噪声情况,需要进行合适的滤波和增益调整,以提高时钟数据恢复的准确性和稳定性。

此外,还需要考虑到时钟频率的漂移和偏移等问题,设计相应的自适应算法来进行校准和调整。

在实际应用中,时钟数据恢复算法的性能直接影响到数字通信系统的稳定性和可靠性。

一个高效的时钟数据恢复算法可以有效地降低误码率,提高通信质量。

因此,工程师们在设计数字通信系统时需要认真考虑时钟数据恢复算法的选择和优化,以确保系统能够在高速数字信号传输中保持高性能和稳定性。

总的来说,高速数字信号传输设计中的时钟数据恢复算法是一个复杂而关键的技。

用于时钟和数据恢复(CDR)电路的可复位压控振荡器(VCO)以及相关系统和方法[发明专利]

![用于时钟和数据恢复(CDR)电路的可复位压控振荡器(VCO)以及相关系统和方法[发明专利]](https://img.taocdn.com/s3/m/5fcbb2c6453610661fd9f4d7.png)

专利名称:用于时钟和数据恢复(CDR)电路的可复位压控振荡器(VCO)以及相关系统和方法

专利类型:发明专利

发明人:J·庄,N·V·丹恩

申请号:CN201380009427.1

申请日:20130215

公开号:CN104126282A

公开日:

20141029

专利内容由知识产权出版社提供

摘要:本发明公开了时钟和数据恢复(CDR)电路以及可复位压控振荡器(VCO)。

在一个实施例中,该CDR电路包括配置成接收数据路径中的数据流并采样该数据流的采样器。

然而,需要恢复该数据流的时钟信号以采样该数据流,因为该数据流可能不伴有时钟信号。

为了从该数据流恢复该时钟信号,该CDR电路可具有配置成生成时钟输出的可复位VCO。

采样器和可复位VCO可操作地相关联,以使得采样器基于该时钟输出来采样该数据路径中的数据流。

可复位VCO可被复位以调整该时钟输出的时钟相位,并且帮助减小由该时钟输出和/或数据流的漂移引起的采样误差。

申请人:高通股份有限公司

地址:美国加利福尼亚州

国籍:US

代理机构:上海专利商标事务所有限公司

代理人:周敏

更多信息请下载全文后查看。

揭秘集成电路设计中的时钟与数据恢复技术与应用

揭秘集成电路设计中的时钟与数据恢复技术与应用English Answer:Clock and data recovery (CDR) technology is an essential component in integrated circuit (IC) design. It plays a crucial role in maintaining the synchronization between the clock and the incoming data, especially in high-speed communication systems. In this article, we will delve into the intricacies of CDR technology and its applications in IC design.CDR technology is used to recover the clock signal from the incoming data stream. It ensures that the receiver's clock is synchronized with the transmitter's clock, allowing the data to be sampled accurately. Without proper clock recovery, the receiver may misinterpret the data, leading to errors and data loss.There are several techniques used in CDR technology. One common method is the Phase-Locked Loop (PLL), which uses a feedback loop to adjust the phase and frequency of the recovered clock signal. Another technique is the Delay-Locked Loop (DLL), which uses a delay line to align the phases of the incoming data and the local clock.In addition to clock recovery, CDR technology also addresses the issue of data recovery. High-speed communication systems often suffer from inter-symbol interference (ISI), which occurs when the transmitted signals overlap in time. To mitigate ISI, CDR circuits employ equalization techniques, such as decision-feedback equalization (DFE), to compensate for the distortion caused by the channel.The applications of CDR technology are vast. It is commonly used in communication systems, such as optical fiber networks, where the data rates are high and the transmission distances are long. CDR circuits are also found in high-speed serial interfaces, such as USB and PCIe, to ensure reliable data transmission.In conclusion, clock and data recovery technology is crucial in integrated circuit design. It enables synchronization between the clock and the incoming data, ensuring accurate data sampling and reducing errors. With the increasing demand for high-speed communication systems, the importance of CDR technology will only continue to grow.中文回答:时钟与数据恢复技术是集成电路设计中的关键组成部分。

超高速数码信号传输中的时钟恢复技术研究

超高速数码信号传输中的时钟恢复技术研究引言随着数字通信技术的进步和智能设备的不断出现,对于高速数据传输的需求也越来越大。

超高速数码信号传输中的时钟恢复技术是实现高速数据传输的关键技术之一。

本文将从时钟恢复技术的基本概念、原理和分类,时钟恢复技术在超高速数码信号传输中的应用以及研究进展等方面进行阐述和分析。

第一章时钟恢复技术的基本概念、原理和分类1.1 什么是时钟恢复技术时钟恢复技术是将接收机收到的信息进行采样,并根据采样的结果恢复出原信号的时钟信息,以保证正确的解析数据。

由于信号的传输存在着很多的不确定性,如信号失真、抖动、滞后……等,因此,时钟恢复技术在实际通信中显得十分重要,也是一项非常复杂的技术。

1.2 时钟恢复技术的原理对于高速信号,在信号传输过程中,由于存在着噪声、失真、抖动等因素,经过传输的信号时钟可能与原信号时钟有一定偏移,采样时钟与信号时钟之间也有可能存在较大的相位偏移。

因此,正确恢复原信号时钟信息是非常关键的。

时钟恢复技术的实现原理主要有两种方法:基于锁相环(PLL)的时钟恢复和基于延迟锁定环(DLL)的时钟恢复。

基于PLL的时钟恢复主要利用自适应滤波器将误差信号反馈到VCO来调整与发射时钟的相位,从而实现时钟的恢复。

而基于DLL的时钟恢复则是将接收到的信号和本地时钟进行延时,并将两路信号进行比较,通过调节延时量来实现时钟的恢复。

两种方式具有不同的优缺点,具体的应用需根据具体情况选择。

1.3 时钟恢复技术的分类时钟恢复技术根据采样时钟和数据时钟的关系,一般可分为三类:边沿对齐、符号同步和自适应时钟恢复。

边沿对齐主要是将参考时钟与接收到的时钟进行相位对齐,当接收到的时钟存在相位偏移,需要根据已知的速率调整时钟相位。

符号同步是指通过接收机对已传输数据的边界进行识别,并根据此对时钟相位进行调节。

自适应时钟恢复则是通过自适应算法将参考时钟与接收到的时钟进行相位同步。

第二章时钟恢复技术在超高速数码信号传输中的应用时钟恢复技术在高速通信中广泛应用于多种领域,特别是在超高速网络、高速存储系统、视频传输等领域中则有着广泛的应用。

一文看懂时钟是怎么恢复的?

一文看懂时钟是怎么恢复的?对于高速的串行总线来说,一般情况下都是通过数据编码把时钟信息嵌入到传输的数据流里,然后在接收端通过时钟恢复把时钟信息提取出来,并用这个恢复出来的时钟对数据进行采样,因此时钟恢复电路对于高速串行信号的传输和接收至关重要。

CDR电路原理时钟恢复的目的是跟踪上发送端的时钟漂移和一部分抖动,以确保正确的数据采样。

时钟恢复电路(CDR:Clock Data Recovery)一般都是通过PLL(Phase lock loop)的方式实现,如下图所示。

输入的数字信号和PLL的VCO(Voltage-controlled oscillator,压控振荡器)进行鉴相比较,如果数据速率和VCO的输出频率间有频率差就会产生相位差的变化,鉴相器对这个相位误差进行比较并转换成相应的电压控制信号,电压控制信号经过滤波器滤波后产生对VCO 的控制信号从而调整VCO的输出时钟频率。

使用滤波器的目的是把快速的相位变化信息积分后转换成相对缓慢的电压变化以调整VCO的输出频率,这个滤波器有时又称为环路滤波器,通常是一个低通的滤波器。

通过反复的鉴相和调整,最终VCO 的输出信号频率和输入的数字信号的变化频率一致,这时PLL电路就进入锁定状态。

环路带宽对眼图、抖动测量的影响值得注意的是,在真实的情况下,输入的数字信号并不是一个纯净的信号,而是包含了不同频率成分的抖动。

对于低频的抖动来说,其造成的是数据速率的缓慢变化,如果这个缓慢变化的频率低于环路滤波器的带宽,输入信号抖动造成的相位变化信息就可以通过环路滤波器从而产生对VCO输出频率的调整,这时VCO的输出时钟中就会跟踪上输入信号的抖动。

而如果输入信号中抖动的频率比较高,其造成的相位变化信号不能通过环路滤波器,则VCO输出的时钟中就不会有随输入信号一起变化的抖动成分,也就是说输入信号中的高频抖动成分被PLL电路过滤掉了。

如下图所示,我们通常会用PLL电路的JTF(Jitter Transfer Function,抖动传递函数)曲线描述PLL电路对于不同频率抖动的传递能力。

时钟与数据恢复(CDR)技术在高速串行通信链路中的应用

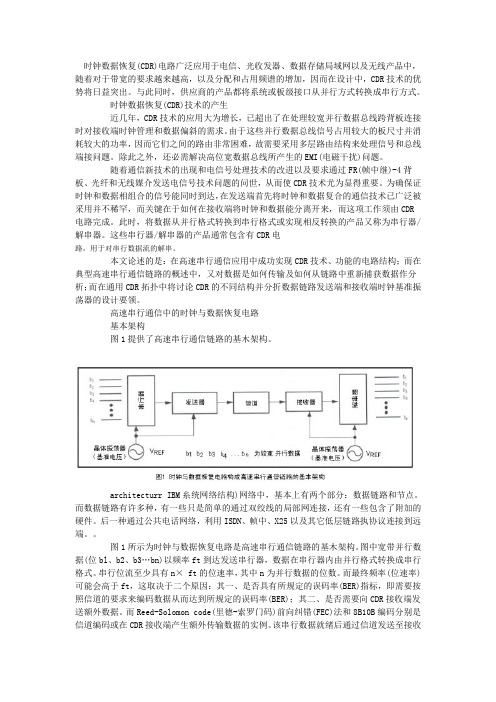

时钟数据恢复(CDR)电路广泛应用于电信、光收发器、数据存储局域网以及无线产品中,随着对于带宽的要求越来越高,以及分配和占用频谱的增加,因而在设计中,CDR技术的优势将日益突出。

与此同时,供应商的产品都将系统或板级接口从并行方式转换成串行方式。

时钟数据恢复(CDR)技术的产生近几年,CDR技术的应用大为增长,已超出了在处理较宽并行数据总线跨背板连接时对接收端时钟管理和数据偏斜的需求。

由于这些并行数据总线信号占用较大的板尺寸并消耗较大的功率,因而它们之间的路由非常困难,故需要采用多层路由结构来处理信号和总线端接问题。

除此之外,还必需解决高位宽数据总线所产生的EMI(电磁干扰)问题。

随着通信新技术的出现和电信号处理技术的改进以及要求通过FR(帧中继)-4背板、光纤和无线媒介发送电信号技术问题的问世,从而使CDR技术尤为显得重要。

为确保证时钟和数据相组合的信号能同时到达,在发送端首先将时钟和数据复合的通信技术已广泛被采用并不稀罕,而关键在于如何在接收端将时钟和数据能分离开来,而这项工作须由CDR电路完成。

此时,将数据从并行格式转换到串行格式或实现相反转换的产品又称为串行器/解串器。

这些串行器/解串器的产品通常包含有CDR电路,用于对串行数据流的解串。

本文论述的是:在高速串行通信应用中成功实现CDR技术、功能的电路结构;而在典型高速串行通信链路的概述中,又对数据是如何传输及如何从链路中重新捕获数据作分析;而在通用CDR拓扑中将讨论CDR的不同结构并分折数据链路发送端和接收端时钟基准振荡器的设计要领。

高速串行通信中的时钟与数据恢复电路基本架构图1提供了高速串行通信链路的基木架构。

architecturr IBM糸统网络结构)网络中,基本上有两个部分:数据链路和节点。

而数据链路有许多种,有一些只是简单的通过双绞线的局部网连接,还有一些包含了附加的硬件。

后一种通过公共电话网络,利用ISDN、帧中、X25以及其它低层链路执协议连接到远端。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

$2 ASSP solution Rx(Equilizer And encoder Etc integrate)

$4*

$2

Total $8

Tx(Cable Driver and decoder integrate $20 Total $40

SDI ASI

Success story Summarize

© 2004 Altera Corporation - Confidential 2

SDI/HD-SDI and ASI apllication

© 2004 Altera Corporation - Confidential 3

Pathological Case of 44 bits during Vertical Interval

© 2004 Altera Corporation - Confidential 8

Standards-SDI

© 2004 Altera Corporation - Confidential 9

© 2004 Altera Corporation - ConfidentPTE(电影和电视工程师协会)

Several Serial Digital Interfaces Specified

Focus on 259M-97 (SDI) and 292M-98 (HD-SDI)

© 2004 Altera Corporation - Confidential 7

Standards-SDI

SMPTE Cont.

SDI:259M-97

Standard for transporting uncompressed standard definition digital video serially over coax Channel Coding is Scrambled NRZI Max Run Length is 20 bits

Tx(Cable Driver and decoder integrate $40 Total $90

$50 *:base fpga resource(800LES)

© 2004 Altera Corporation - Confidential 4

FPGA Soluiton Vs ASIC Solution1(ASI)

RP 178

Video Payload Identification for Digital Television Interfaces

SMPTE 352M-2001

Numerous Recommended Practices and Engineering Guidelines

Used for Synchronous Video Switching Definition, Error Detection Schemes, Jitter Measurement, etc…

$2 ASSP solution Rx(Equilizer And encoder Etc integrate)

$60*

$2

Total $64

Tx(Cable Driver and decoder integrate $80 Total $180

$100 *:base fpga resource(4000LES)

ALTERA SDI/HD-SDI and DVB-ASI solution

Cytech FAE Robin luo

Oct,2004

© 2004 Altera Corporation

Agenda

SDI/HD-SDI and ASI application SDI interfaces DVB-ASI interface HD-SDI interface Altera FPGA Solution Reference design

Multiple Scan Formats supported for each Electrical Interface

Ancillary Data Packet and Space Formatting Specification (291M-98) Specification of Jitter in Bit Serial Digital Systems

$20 *:base fpga resource(1000LES)

© 2004 Altera Corporation - Confidential 5

FPGA Soluiton Vs ASIC Solution2(HD-SDI)

FPGA solution Equilizer FPGA (Straitx GX) Cable driver

FPGA Soluiton Vs ASIC Solution1(SDI)

FPGA solution Equilizer FPGA (Cyclone) Cable driver

$2 ASSP solution Rx(Equilizer And encoder Etc integrate)

$4*

$2

Total $8

SDI Interface composed of several parts

Electrical/Optical Interface Specification (259M and 292M) Scan Format (Bit-Parallel Interface) Specification (260M-99 for ex.)

Standards-SDI

© 2004 Altera Corporation - Confidential 10

Standards-SDI

© 2004 Altera Corporation - Confidential 11

Standards-DVB-ASI

DVB-ASI (digital video broadcast asynchronous serial interface):