光刻工艺概述

光刻工艺概述范文

光刻工艺概述范文光刻工艺是一种在微电子制造过程中使用的重要技术,它被用来制造集成电路、平板显示器、光学元件和微纳米结构等微系统设备。

光刻工艺可以实现高精度的图案转移,从而实现微电子器件的制造。

首先,光刻工艺的基础是光刻胶的使用。

光刻胶是一种特殊的液体材料,它可以在光照下发生化学反应,从而形成具有特定形状的图案。

光刻胶通常是由光敏剂、聚合物和溶剂组成的复合物。

在光刻过程中,光敏剂在光照下会发生光化学反应,而聚合物则起到保护胶膜的作用。

其次,光刻胶需要通过光刻机进行曝光。

光刻机是一种特殊的设备,它可以通过光源发射出特定波长的光,然后将光照射到光刻胶上。

光刻机通常采用紫外光或深紫外光作为光源,因为这些波长的光可以提供较高的分辨率和光刻胶的敏感性。

光照后,光刻胶中被光化学反应改变的区域会变得溶解性不同于未被照射的区域。

然后,曝光后的光刻胶需要进行显影。

显影是将光刻胶中未被光照的部分溶解掉,以显示出所需的图案。

显影过程常用的显影液是酸性的溶液,因为光刻胶通常是碱性的,酸性的显影液可以中和光刻胶中的碱性物质,从而加快显影的速度。

经过显影后,光刻胶上就会留下所需的图案。

最后,经过显影之后,就需要对光刻胶进行固化和清洗。

固化是通过加热或紫外光照射等方法使光刻胶变得硬化,以增加其耐用性和稳定性。

清洗是将显影后的光刻胶从器件表面去除。

清洗过程通常使用有机溶剂或酸碱溶液进行,以去除光刻胶的残留物。

除了上述基本步骤外,光刻工艺还有其他一些补充工艺,例如涂胶剥离、反蚀刻和多层光刻等。

涂胶剥离技术是在制造过程中用于去除曝光后的光刻胶的方法,可以使工艺更加容易进行。

反蚀刻是一种利用光化学反应来蚀刻材料的方法,可以形成多层结构。

多层光刻则是在多个层次上进行光刻,可以实现更加复杂的图案。

这些补充工艺可以根据不同需求进行选择和组合。

总的来说,光刻工艺是微电子制造中的一种重要技术,它通过使用光刻胶、光刻机和显影液等工具和材料,可以实现高精度的图案转移。

光刻工艺概述

光刻工艺流程图步骤1、前处理2、匀胶3、前烘4、光刻5、显影6、坚膜7、腐蚀8、去胶一前处理(OAP)通常在150~200℃对基片进行烘考以去除表面水份,以增强光刻胶与硅片的粘附性。

(亲水表面与光刻胶的粘附性差,SI的亲水性最小,其次SIO2,最后PSI玻璃和BSI玻璃)OAP的主要成分为六甲基二硅烷,在提升光刻胶的粘附性工艺中,它起到的作用不是增粘剂,而是改变SiO2的界面结构,变亲水表面为疏水表面。

OAP通常采用蒸汽涂布的方式,简单评价粘附性的好坏,可在前处理过的硅片上滴一滴水,通过测量水与硅片的接触角,角度越大,SI二、匀胶光刻胶通常采用旋涂方式,在硅片上得到一层厚度均匀的胶层。

影响胶厚的最主要因素:光刻胶的粘度及旋转速度。

次要因素:排风;回吸;胶泵压力;胶盘;温度。

胶厚的简单算法:光刻胶理论的最小胶厚的平方乘以理论的转速=目标光刻胶的胶厚的平方乘以目标转速例如:光刻胶理论厚度1微米需要转速3000转/分,那需要光刻胶厚度1.15微米时转速应为12 *3000/1.152三、前烘前烘的目的是为了驱除胶膜中残余的溶剂,消除胶膜的机械应力。

前烘的作用: 1)增强胶层的沾附能力;2)在接触式曝光中可以提高胶层与掩模板接触时的耐磨性能;3)可以提高和稳定胶层的感光灵敏度。

前烘是热处理过程,前烘通常的温度和时间:烘箱90~115℃ 30分钟热板90~120℃ 60~90秒四、光刻光刻胶经过前烘后,原来液态光刻胶在硅片表面上固化。

光刻的目的就是将掩膜版上的图形转移到硅片上。

曝光的设备分类接触式、接近式、投影式、步进式/扫描式、电子束曝光、软X射线曝光。

五、显影经过显影,正胶的曝光区域和负胶的非曝光区域被溶解,正胶的非曝光区域和负胶的曝光区域被保留下来,从而完成图形的转移工作。

正胶曝光区域经过曝光后,生成羧酸与碱性的显影液中和反应从而被溶解。

负胶的曝光区域经过曝光后产生胶联现象,不被显影液溶解。

而未曝光的区域则被显影液溶解掉。

光刻工艺的原理和目的

光刻工艺的原理和目的

光刻工艺是一种利用光刻胶或分子层结合物,将特定图案投影到基板

表面的复杂工艺。

它是集装置制造产业中的重要组成部分,是基于影

流分子沉积的微小精密表面处理技术,是大规模集成电路设计的核心

工艺。

光刻工艺的原理是在光刻胶或分子层表面利用UV光射线照射,使其发

生反应,从而使光刻胶或分子层表面产生结合或分离反应,结合起来

的是形成薄膜或层,分离出来的是沉积到基板上形成微小图案和通道。

光刻工艺的目的是制造出精巧的3D复杂图案,以满足现代电子行业的

要求。

它的用途也很广泛:将专有的形状准确地投影到某种固体表面,以塑造出物体的内部或三维形状;将其应用到芯片结构的加工和分辨;在电阻膜、电容膜、半导体膜、光学膜和其他微细表面加工领域扮演

着重要角色。

因此,光刻工艺可以生产出高精度、复杂的集成电路,其微小细节则

可能被微小的光线所照亮,弥补了它的局限性。

光刻工艺是影流技术

的一种,是大规模集成电路设计的核心工艺,有助于提高制造效率、

提高产品的性能和提高工程的质量。

自从20世纪80年代以来,光刻

技术的发展受到了越来越多的关注,在电子行业中获得了极大的发展

和推广作用。

光刻工艺介绍

光刻工艺过程

涂胶coating 前烘prebaking 曝光exposure 显影development 坚膜postbake

光刻工艺过程

涂胶

氧化,清洗

涂胶,前烘

涂胶目的: 在晶元表面形成厚度均匀,附着性强, 没有缺陷的光刻胶薄膜

光刻胶对大部分可见光敏感,但对黄光不敏感

光刻三要素

光刻胶主要成分

1.树脂(聚合物):光照不发生反应,保证光刻胶的附着性和抗腐 蚀性,决定光刻胶薄膜的膜厚,弹性和热稳定性。

2.光敏剂(PAC):受光辐照后发生化学反应,如果聚合物中不添 加光敏剂,那么他对光的敏感性差,而且光谱范围较宽,添加特 定的光敏剂后,可以增加感光灵敏度,而且限制反应光的光谱范 围,或者把反应光限制在某一特定的波长。

转速与膜厚:膜厚与旋转速度的平方根成反比

光刻工艺过程

前烘probake

目的

去除胶内的溶剂,提高胶的表面粘附力 提高胶的抗机械摩擦能力 减小高速旋转形成的薄膜应力

条件

温度:90 to 120℃ 时间:60 to 120s

光刻工艺过程

前烘probake

前烘不足

光刻胶与晶元粘附性变差 因光刻胶中溶剂含量过高致使曝光的精度下降

前烘过量

延长时间,产量下降 过高的温度使光刻胶变脆,粘附性下降 过高的温度会使光刻胶的感光剂发生反应,使 光刻胶在曝光时的敏感度下降

光刻工艺过程 曝光Exposure

光刻工艺过程

曝光Exposure

将电路图案转移到晶元上 为了将电路图案转移到晶片上,将光罩暴露在光下。 通过使用缩小透镜聚焦光,甚至可以转移更精细的 电路图案。电路图中的线越窄,可传输的半导体元 件数量越多,因此芯片的性能和功能也就越高

0.35um光刻工艺

0.35um光刻工艺1. 光刻工艺概述,光刻工艺是微电子制造过程中的一项关键技术,通过将光刻胶涂覆在硅片上,然后使用光刻机将图形投射到光刻胶上,最后通过化学腐蚀等步骤来转移图形到硅片上。

0.35um光刻工艺是指在这个过程中所使用的光刻胶的分辨率为0.35微米。

2. 分辨率,分辨率是光刻工艺中一个重要的指标,它决定了工艺可以实现多细小的结构。

0.35um的分辨率意味着该工艺可以制造出最小线宽为0.35微米的结构。

3. 应用领域,0.35um光刻工艺在微电子制造中有广泛的应用。

它适用于制造一些较为简单的电子元件和集成电路,例如逻辑门电路、存储器等。

虽然在现代微电子制造中,0.35um光刻工艺已经相对较老,但在一些特定的应用领域仍然具有一定的市场需求。

4. 工艺特点,0.35um光刻工艺具有一些特点。

首先,相对于更高分辨率的工艺,0.35um光刻工艺更容易实现,成本相对较低。

其次,0.35um工艺的制造设备和工艺流程已经相对成熟,稳定性较高,可靠性较好。

然而,由于分辨率相对较低,0.35um工艺无法满足现代微电子制造对更高集成度和更小尺寸的要求。

5. 工艺发展趋势,随着科技的不断进步,微电子制造对更高分辨率的需求不断增加。

因此,0.35um光刻工艺已经逐渐被更先进的工艺所取代,例如0.25um、0.18um、0.13um甚至更小的工艺。

这些更高分辨率的工艺可以实现更小尺寸的结构,提高集成度和性能。

综上所述,0.35um光刻工艺是一种用于微电子制造的工艺,它具有一定的应用领域和特点。

然而,随着技术的进步,更高分辨率的工艺已经逐渐取代了0.35um工艺。

希望以上回答能满足你的需求。

光刻工艺知识点总结

光刻工艺知识点总结光刻工艺是半导体制造工艺中的重要环节,通过光刻技术可以实现微米级甚至纳米级的精密图案转移至半导体芯片上,是芯片制造中最关键的工艺之一。

光刻工艺的基本原理是利用光学原理将图案投射到光刻胶上,然后通过化学蚀刻将图案转移到芯片表面。

下面将对光刻工艺的知识点进行详细总结。

一、光刻工艺的基本原理1. 光刻胶光刻胶是光刻工艺的核心材料,主要由树脂和溶剂组成。

树脂的种类和分子结构直接影响着光刻胶的分辨率和对光的敏感度,而溶剂的选择和比例则会影响着光刻胶的黏度、流动性和干燥速度。

光刻胶的选择要根据不同的工艺要求,如分辨率、坚固度、湿膜厚度等。

2. 掩模掩模是用来投射光刻图案的模板,通常是通过电子束刻蚀或光刻工艺制备的。

掩模上有所需的图形样式,光在通过掩模时会形成所需的图案。

3. 曝光曝光是将掩模上的图案投射到光刻胶表面的过程。

曝光机通过紫外线光源产生紫外线,通过透镜将掩模上的图案投射到光刻胶表面,形成图案的暗部和亮部。

4. 显影显影是通过化学溶液将光刻胶上的图案显现出来的过程。

曝光后,光刻胶在图案暗部和亮部会有不同的化学反应,显影溶液可以去除未暴露的光刻胶,留下所需的图案。

5. 蚀刻蚀刻是将图案转移到硅片上的过程,通过化学腐蚀的方式去除光刻胶未遮盖的部分,使得图案转移到硅片表面。

二、光刻工艺中的关键技术1. 分辨率分辨率是指光刻工艺能够实现的最小图案尺寸,通常用实际图案中两个相邻细线或空隙的宽度之和来表示。

分辨率受到光刻机、光刻胶和曝光技术等多个因素的影响,是衡量光刻工艺性能的重要指标。

2. 等效焦距等效焦距是光刻机的重要参数,指的是曝光光学系统的有效焦距,影响光刻图案在光刻胶表面的清晰度和分辨率。

3. 曝光剂量曝光剂量是指单位面积上接收的光能量,通常用mJ/cm^2或μC/cm^2来表示。

曝光剂量的选择对分辨率和光刻胶的副反应有重要影响。

4. 曝光对位精度曝光对位精度是指光刻胶上已存在的图案和新的曝光对位的精度,是保证多层曝光图案对位一致的重要因素。

光刻与刻蚀工艺

涂胶/显影技术

01

02

03

涂胶

在晶圆表面涂上一层光敏 胶,以保护非曝光区域并 提高图像对比度。

显影

用适当的溶剂去除曝光区 域的光敏胶,以形成所需 的图案。

控制胶厚

保持胶厚均匀,以避免图 像的扭曲和失真。

烘烤与曝光技术

烘烤

通过加热去除晶圆表面的湿气,以提高光敏胶的灵敏度和图像质 量。

曝光

将掩模图像投影到光敏胶上,通过光化学反应将图像转移到晶圆 上。

非接触式光刻

投影式非接触

利用光学系统将掩膜板上的图像投影到光刻胶涂层上,优点是无需直接接触,缺点是难度较高,需要精确的控 制系统。

电子束光刻

利用电子束在光刻胶上直接曝光,优点是分辨率高、无需掩膜板,缺点是生产效率低。

投影式光刻

接触式投影

掩膜板与光刻胶涂层之间保持接触,通过投影系统将图像投影到光刻胶上,优点是操作简单、高效, 缺点是图像质量可能受到掩膜板损伤和光刻胶污染的影响。

要点二

损伤控制

是指在刻蚀过程中避免对材料产生损伤。对于某些特殊 材料,如脆性材料,损伤控制尤为重要。如果刻蚀过程 中产生过多损伤,可能会导致材料性能下降甚至破裂。

感谢您的观看

THANKS

光刻工艺的基本步骤

涂胶

将光刻胶涂敷在硅片表面,以形成 光刻胶层。

烘烤

通过烘烤使光刻胶层干燥并固化。

曝光

将掩膜版上的图形对准硅片上的光 刻胶层,并使用曝光设备将图形转 移到光刻胶上。

显影

使用显影液将曝光后的光刻胶进行 化学处理,使图形更加清晰地展现 出来。

光刻工艺的重要性

光刻工艺是半导体制造中的关键环节,直接影响芯片的制造 质量和性能。

光刻工艺介绍

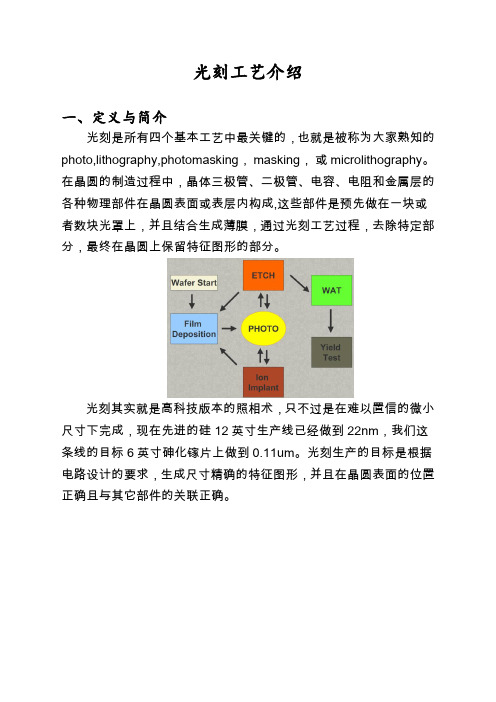

光刻工艺介绍一、定义与简介光刻是所有四个基本工艺中最关键的,也就是被称为大家熟知的photo,lithography,photomasking, masking, 或microlithography。

在晶圆的制造过程中,晶体三极管、二极管、电容、电阻和金属层的各种物理部件在晶圆表面或表层内构成,这些部件是预先做在一块或者数块光罩上,并且结合生成薄膜,通过光刻工艺过程,去除特定部分,最终在晶圆上保留特征图形的部分。

光刻其实就是高科技版本的照相术,只不过是在难以置信的微小尺寸下完成,现在先进的硅12英寸生产线已经做到22nm,我们这条线的目标6英寸砷化镓片上做到0.11um。

光刻生产的目标是根据电路设计的要求,生成尺寸精确的特征图形,并且在晶圆表面的位置正确且与其它部件的关联正确。

二、光刻工艺流程介绍光刻与照相类似,其工艺流程也类似:实际上,普通光刻工艺流程包括下面的流程:1)Substrate Pretreatment 即预处理,目的是改变晶圆表面的性质,使其能和光刻胶(PR)粘连牢固。

主要方法就是涂HMDS,在密闭腔体内晶圆下面加热到120℃,上面用喷入氮气加压的雾状HMDS,使得HMDS和晶圆表面的-OH健发生反应已除去水汽和亲水健结构,反应充分后在23℃冷板上降温。

该方法效果远比传统的热板加热除湿好。

2)Spin coat即旋转涂光刻胶,用旋转涂布法能提高光刻胶薄膜的均匀性与稳定性。

光刻胶中主要物质有树脂、溶剂、感光剂和其它添加剂,感光剂在光照下会迅速反应。

一般设备的稳定工作最高转速不超过4000rpm,而最好的工作转速在2000~3000rpm。

3)Soft Bake(Pre-bake)即软烘,目的是除去光刻胶中溶剂。

一般是在90℃的热板中完成。

4)Exposure即曝光,这也是光刻工艺中最为重要的一步,就是用紫外线把光罩上的图形成像到晶圆表面,从而把光罩上面的图形转移到晶圆表面上的光刻胶中。

光刻工艺.pptx

一、接触式曝光

由于掩膜版与硅片相接触磨损,是掩膜 版的寿命降低。

22

二、接近式曝光

接近式曝光是以牺牲分辨率来延长 了掩膜版的寿命 大尺寸和小尺寸器件上同时保持线 宽容限还有困难。另外,与接触式 曝光相比,接近式曝光的操作比较 复杂。

23

三、投影式曝光

避免了掩膜版与硅片表面的摩擦,延长 了掩膜版的寿命。

34

几种实用的光刻胶配方。 PMMA对210nm到260nm的紫外光有感光性, 感光性最佳的紫外光光谱约为220nm; PMIK的紫外光感光光谱为220nm到330nm, 峰值光谱约为190nm和285nm。

35

AZ240系列光刻胶的感光光谱为240nm到 310nm,峰值光谱约为248nm、300nm、 315nm。 ODVR系列光刻胶的感光光谱为200nm到 315nm,峰值光谱为230nm、280nm、 300nm。

3

打底膜(六甲基二硅亚胺HMDS)

六甲基二硅亚胺HMDS反应机理

OH

SiO2 +(CH3) 3SiNHSi(CH3)

3

OH

O-Si(CH3) 3

SiO2

+NH

O-Si(CH3) 33

4

5

6

曝光方法

曝光有多种方法:光学曝光就可分为接 触式、接近式、投影式、直接分步重复 曝光。此外,还有电子束曝光和X射线曝 光等。曝光时间、氮气释放、氧气、驻 波和光线平行度都是影响曝光质量

掩膜版的尺寸可以比实际尺寸大得多, 克服了小图形制版的困难。

消除了由于掩膜版图形线宽过小而产生 的光衍射效应,以及掩膜版与硅片表面接 触不平整而产生的光散射现象。

24

投影式曝光虽 有很多优点, 但由于光刻设 备中许多镜头 需要特制,设 备复杂

光刻工艺资料整理

光刻工艺资料整理光刻工艺资料整理上一篇/ 下一篇 2007-12-10 20:10:25 / 个人分类:光刻查看( 121 ) / 评论( 0 ) / 评分( 0 / 0 )光刻工艺资料整理概述:光刻技术是集成电路的关键技术之一,在整个产品制造中是重要的经济影响因子,光刻成本占据了整个制造成本的35%。

光刻也是决定集成电路按照摩尔定律发展的一个重要原因,如果没有光刻技术的进步,集成电路就不可能从微米进入深亚微米再进入纳米时代。

所以说光刻系统的先进程度也就决定了光刻工程的高低。

1.光刻工艺简介光刻是通过一系列生产步骤将晶圆表面薄膜的特定部分除去的工艺。

在此之后,晶圆表面会留下带有微图形结构的薄膜,被除去的部分可能形状是薄膜内的孔或是残留的岛状部分。

光刻工艺也被称为大家熟知的Photomasking, masking, photolithography, 或microlithography。

在晶圆的制造过程中,晶体三极管、二极管、电容、电阻和金属层的各种物理部件在晶圆表面或表层内构成。

这些部件是每次在一个掩膜层上生成的,并且结合生成薄膜及去除特定部分,通过光刻工艺过程,最终在晶圆上保留特征图形的部分。

光刻生产的目标是根据电路设计的要求,生成尺寸精确的特征图形,并且在晶圆表面的位置正确且与其它部件(parts)的关联正确。

光刻是所有四个基本工艺中最关键的。

光刻确定了器件的关键尺寸。

光刻过程中的错误可造成图形歪曲或套准不好,最终可转化为对器件的电特性产生影响。

图形的错位也会导致类似的不良结果。

光刻工艺中的另一个问题是缺陷。

光刻是高科技版本的照相术,只不过是在难以置信的微小尺寸下完成。

在制程中的污染物会造成缺陷。

事实上由于光刻在晶圆生产过程中要完成5层至20层或更多,所以污染问题将会放大。

光刻工艺过程包括有:涂胶、前烘、曝光、显影、坚膜、腐蚀、去胶等。

课程内容:1 光刻前的准备工作1.1 准备要求1.2 准备方法1.2.1 光刻前待光刻片子置于干燥塔中1.2.2 氧化片出炉后可立即送光刻工序涂胶1.2.3 对氧化片可在涂胶前重吹段时间干氧(氧化温度)1.2.4 涂胶前片子置于80度烘箱中烘30分钟2 涂胶2.1 涂胶的要求2.2 涂胶的方法2.2.1 旋转涂胶法2.2.2 喷涂法2.2.3 浸涂法3 前烘3.1 前烘要求3.2 前烘的方法3.2.1 在80度烘箱中烘15分钟-20分钟3.2.2 在红外烘箱中烘3分钟-5分钟4 曝光4.1 曝光的要求4.2 曝光的方法5 显影5.1 显影的要求5.2 显影的方法6 坚膜6.1 坚膜的要求6.2 坚膜的方法6.2.1 置于恒温箱中,在180度烘30 分钟左右6.2.2 置于红外烘箱中烘10分钟左右7 腐蚀7.1 腐蚀的要求7.2 腐蚀的方法7.2.1 腐蚀二氧化硅的方法7.2.2 腐蚀铝电极的方法8 去胶8.1 去胶的要求8.2 去胶的方法课程重点:本节介绍了光刻工艺及对各光刻工艺步骤的要求。

光刻工艺简介

概述光刻工艺是半导体制造中最为重要的工艺步骤之一。

主要作用是将掩膜板上的图形复制到硅片上,为下一步进行刻蚀或者离子注入工序做好准备。

光刻的成本约为整个硅片制造工艺的1/3,耗费时间约占整个硅片工艺的40~60%。

光刻机是生产线上最贵的机台,5~15百万美元/台。

主要是贵在成像系统(由15~20个直径为200~300mm的透镜组成)和定位系统(定位精度小于10nm)。

其折旧速度非常快,大约3~9万人民币/天,所以也称之为印钞机。

光刻部分的主要机台包括两部分:轨道机(Tracker),用于涂胶显影;扫描曝光机(Scanning )光刻工艺的要求:光刻工具具有高的分辨率;光刻胶具有高的光学敏感性;准确地对准;大尺寸硅片的制造;低的缺陷密度。

光刻工艺过程一般的光刻工艺要经历硅片表面清洗烘干、涂底、旋涂光刻胶、软烘、对准曝光、后烘、显影、硬烘、刻蚀、检测等工序。

1、硅片清洗烘干(Cleaning and Pre-Baking)方法:湿法清洗+去离子水冲洗+脱水烘焙(热板150~2500C,1~2分钟,氮气保护)目的:a、除去表面的污染物(颗粒、有机物、工艺残余、可动离子);b、除去水蒸气,是基底表面由亲水性变为憎水性,增强表面的黏附性(对光刻胶或者是HMDS-〉六甲基二硅胺烷)。

2、涂底(Priming)方法:a、气相成底膜的热板涂底。

HMDS蒸气淀积,200~2500C,30秒钟;优点:涂底均匀、避免颗粒污染; b、旋转涂底。

缺点:颗粒污染、涂底不均匀、HMDS用量大。

目的:使表面具有疏水性,增强基底表面与光刻胶的黏附性。

3、旋转涂胶(Spin-on PR Coating)方法:a、静态涂胶(Static)。

硅片静止时,滴胶、加速旋转、甩胶、挥发溶剂(原光刻胶的溶剂约占65~85%,旋涂后约占10~20%);b、动态(Dynamic)。

低速旋转(500rpm_rotation per minute)、滴胶、加速旋转(3000rpm)、甩胶、挥发溶剂。

光刻的基本原理

光刻的基本原理1. 光刻技术概述光刻(photolithography)是一种在微电子制造工艺中广泛应用的技术,用于将电路图案转移至硅片上。

它是一种光影刻蚀技术,通过使用特殊的光刻胶和掩膜来实现。

2. 光刻的基本步骤光刻的基本步骤包括掩膜制备、光刻胶涂布、曝光、显影和刻蚀等步骤。

2.1 掩膜制备掩膜是光刻中的一种重要工具,它由透明光刻胶和不透明掩膜板组成。

掩膜板的图案决定了最终在硅片上形成的电路。

2.2 光刻胶涂布在光刻过程中,需要将光刻胶均匀涂布在硅片上。

涂布需要控制好厚度,并保持均匀性。

2.3 曝光曝光是将掩膜上的图案转移到光刻胶层的过程。

曝光时,光源会将光刻胶层中的敏化剂激活,使其变得可显影。

2.4 显影显影是将曝光后的光刻胶层中未被曝光的部分去除,从而显现出所需图案的过程。

显影液会溶解未暴露于光的区域,使其变为可刻蚀的区域。

2.5 刻蚀刻蚀是将显影后的光刻胶层外的材料去除的过程。

通过刻蚀,可以形成所需的电路图案。

3. 光刻的基本原理光刻的基本原理可以分为光学透射原理和化学反应原理两个方面。

3.1 光学透射原理光学透射原理是光刻的基础,也是光刻胶和掩膜的关键。

光刻胶对于不同波长的光有不同的吸收特性,而掩膜上的图案会通过光刻胶的吸收和透射来形成图案。

当掩膜上的图案被光照射时,光刻胶中的敏化剂会被激活,从而改变光刻胶的溶解性质。

3.2 化学反应原理化学反应原理是光刻胶显影和刻蚀的基础。

在显影过程中,显影液与光刻胶表面的未暴露区域发生化学反应,使其溶解。

而在刻蚀过程中,刻蚀液与未被光刻胶保护的硅片表面或者下一层材料发生化学反应,使其被去除。

4. 光刻的影响因素光刻的效果受到多个因素的影响,主要包括曝光能量、曝光时间、光刻胶厚度、显影液浓度等因素。

4.1 曝光能量和曝光时间曝光能量和曝光时间决定了光刻胶的显影深度,对图案的清晰度和精度有重要影响。

4.2 光刻胶厚度光刻胶厚度会影响曝光和显影的效果,太厚会导致曝光不足,太薄则可能导致显影不均匀。

光刻工艺

三、工艺流程: 工艺流程:

以负胶为例来说明这八个步骤,一般可分 以负胶为例来说明这八个步骤, 为: 打底膜- 涂胶- 前烘- 曝光- 显影打底膜->涂胶->前烘->曝光->显影-> 后烘- 腐蚀- 去胶。 后烘->腐蚀->去胶。

3

打底膜(六甲基二硅亚胺HMDS HMDS) 打底膜(六甲基二硅亚胺HMDS)

G、衬底反射影响: H、显影和刻蚀的影响:

(2)针孔 (3)小岛 (4)浮胶 毛刺、 (5)毛刺、钻蚀

13

§3 光刻胶

光刻胶的分类和光刻胶的质量要求。 光刻胶的分类和光刻胶的质量要求。

一、正胶和负胶: 正胶和负胶:

根据光刻胶在曝光前后溶解特性的变化, 根据光刻胶在曝光前后溶解特性的变化 , 可将分为正胶和负胶。 可将分为正胶和负胶。 正胶:曝光前不可溶, 正胶:曝光前不可溶,曝光后 可溶 负胶: 可溶, 负胶:曝光前 可溶,曝光后不可溶

六甲基二硅亚胺HMDS反应机理 六甲基二硅亚胺HMDS反应机理

OH SiO2 +(CH3) 3SiNHSi(CH3)

3

SiO2

OH

O-Si(CH3) 3 +NH O-Si(CH3) 33

4

5

6

曝光方法

曝光有多种方法:光学曝光就可分为接 触式、接近式、投影式、直接分步重复 曝光。此外,还有电子束曝光和X 曝光。此外,还有电子束曝光和X射线曝 光等。曝光时间、氮气释放、氧气、驻 波和光线平行度都是影响曝光质量

分步重复曝光光学原理图

32

(3)由于采用了逐步对准技术可补偿硅片尺 寸的变化,提高了对准精度。逐步对准的方法 也可以降低对硅片表面平整度的要求。

33

光刻工艺简介 - 复制

遮蔽式(shadow)曝光

➢ 接触式:1μm左右的分辨率,尘埃或硅渣嵌入光刻胶的问 题;

➢ 接近式:(10-50μm的间隙),2-5μm分辨率,掩膜图形边 缘光学衍射,光进入阴影区。

临界尺寸(critical dimension,CD)

➢ 灵敏度

✓ 正胶的灵敏度:感光区变得完全可溶时所需的能量,因 此E T对应于灵敏度,是衡量曝光速度的指标(mJ/cm 2); ✓ 负胶的灵敏度:曝光区内的原始光刻胶厚度保留50%所 需的能量;

➢ 对比度

✓ 对比度(反差比)——直接影响光刻胶的分辨率;曝 光响应曲线斜率越大,对比度越大; ✓ γ较大表示曝光能量有一增量,光刻胶的可溶性就有较 大增加,结果图像边缘就比较陡。

(2)

➢ 式(1)说明分辨率的改善(即较小的lm),可以通过缩短 光源波长与增加数值孔径NA达到;

➢ 式(2)指出,聚焦深度会因NA的增加而衰减,而且增加 DA值比缩短光源波长λ对聚焦深度DOF衰减影响更快;

➢结论:缩短光源波长是光学图形曝光的必然 趋势。

➢ 高压汞灯(mercury-arc lamp) 具有较高的光强度与稳定度,故 被广泛用作曝光光源; ➢ 汞灯光谱的几个峰值: G-线:436nm H-线:405nm I-线:365nm

光刻胶主要参数

➢ 灵敏度 ➢ 对比度 ➢ 衍射影响 ➢ 抗刻蚀比

➢ 分辨能力 ➢ 曝光宽容度 ➢ 工艺宽容度 ➢ 其他

曝光响应曲线

下图为正、负胶曝光反应曲线和显影后图形截面 ➢ 光刻胶即使没有曝光,在显影液中也有一定的可溶性; ➢ 随着曝光剂量的增加,可溶性逐渐增加; ➢ 达到阈值E T后光刻胶完全可溶——对应于灵敏度。

光刻工艺介绍

光刻工艺介绍一、定义与简介光刻是所有四个基本工艺中最关键的,也就是被称为大家熟知的photo,lithography,photomasking,masking,或microlithography。

在晶圆的制造过程中,晶体三极管、二极管、电容、电阻和金属层的各种物理部件在晶圆表面或表层内构成,这些部件是预先做在一块或者数块光罩上,并且结合生成薄膜,通过光刻工艺过程,去除特定部分,最终在晶圆上保留特征图形的部分。

光刻其实就是高科技版本的照相术,只不过是在难以置信的微小尺寸下完成,现在先进的硅12英寸生产线已经做到22nm,我们这条线的目标6英寸砷化镓片上做到0.11um。

光刻生产的目标是根据电路设计的要求,生成尺寸精确的特征图形,并且在晶圆表面的位置正确且与其它部件的关联正确。

二、光刻工艺流程介绍光刻与照相类似,其工艺流程也类似:实际上,普通光刻工艺流程包括下面的流程:1)Substrate Pretreatment 即预处理,目的是改变晶圆表面的性质,使其能和光刻胶(PR)粘连牢固。

主要方法就是涂HMDS,在密闭腔体内晶圆下面加热到120℃,上面用喷入氮气加压的雾状HMDS,使得HMDS和晶圆表面的-OH健发生反应已除去水汽和亲水健结构,反应充分后在23℃冷板上降温。

该方法效果远比传统的热板加热除湿好.2)Spin coat即旋转涂光刻胶,用旋转涂布法能提高光刻胶薄膜的均匀性与稳定性。

光刻胶中主要物质有树脂、溶剂、感光剂和其它添加剂,感光剂在光照下会迅速反应。

一般设备的稳定工作最高转速不超过4000rpm,而最好的工作转速在2000~3000rpm.3)Soft Bake(Pre-bake)即软烘,目的是除去光刻胶中溶剂。

一般是在90℃的热板中完成。

4)Exposure即曝光,这也是光刻工艺中最为重要的一步,就是用紫外线把光罩上的图形成像到晶圆表面,从而把光罩上面的图形转移到晶圆表面上的光刻胶中。

光刻的工艺

光刻的工艺

光刻工艺是一种重要的微细加工技术,通常用于制造集成电路和微纳米器件。

下面是光刻工艺的一般步骤:

1. 接收光刻图案设计:根据需要制造的器件,设计图案,并将其转化为数字格式。

2. 芯片表面处理:对芯片表面进行预处理,例如清洗、去除杂质等,以确保光刻的质量。

3. 底片涂覆:将光刻底片(通常为玻璃或石英材料)涂覆在芯片表面,形成光刻胶层。

4. 软对准:使用专用设备将光刻底片和芯片对准,确保图案正确布局。

5. 曝光:使用光刻机器将光刻底片上的图案投射到光刻胶层上。

这通常通过使用紫外线光源,通过掩模和透镜将光照射到芯片的特定区域。

6. 显影:将芯片浸泡在特定的化学液中,将未暴露于光的光刻胶溶解掉,从而形成所需的图案。

这需要控制显影时间和温度以确保正确的图案转移。

7. 清洗:将芯片浸泡在去离子水或其他清洗剂中,去除显影过程中产生的任何

残留物。

8. 检验:检查芯片上的图案是否按照设计要求制造,并进行必要的测量和质量控制。

以上是光刻工艺的一般步骤,具体的工艺参数和步骤可能因应用和芯片制造技术的不同而有所变化。

光刻工艺的优化和控制是集成电路制造中的关键技术之一,对于实现高精度、高性能的微纳米器件具有重要意义。

光刻工艺工程师工作内容

光刻工艺工程师工作内容1. 光刻工艺概述要说光刻工艺工程师干啥,那简直就是在高科技里打工的超级英雄。

他们的工作就像是把微型的魔法画在芯片上,让这些芯片能够变成我们手里那些小巧的电子设备。

光刻工艺,说白了,就是把复杂的电路图案转移到半导体芯片上,一点都不简单。

这个过程就像是在做一场高科技的烹饪秀,只不过食材是光线和化学药剂,而成品是你手机里那些无处不在的芯片。

2. 光刻工艺的步骤2.1. 设计图案首先,光刻工艺工程师得从设计图开始。

就像做一道大菜之前,你得先画个食谱一样。

设计图案这一步是最基础也是最关键的。

工程师们会拿出一堆复杂的电子图纸,然后把那些细致入微的电路图案进行精准设计。

这些图案就像是未来芯片上的“小画作”,每一个细节都不能马虎。

图案设计好了,就进入了下一步。

2.2. 准备光刻机接下来,工程师们得准备光刻机了。

光刻机就是那个用来把设计图转移到芯片上的“大厨”。

这台机器可是个高精尖的设备,它能在芯片上精确地刻画出设计图案。

这一步就像是调配配料一样,需要非常精准的操作。

每一步都得细心,稍有差池,芯片上的图案就可能出错,整块芯片可能就废了。

2.3. 光刻过程光刻机准备好之后,工程师们会把光刻胶涂到半导体芯片上。

这个光刻胶就像是做饼干的面团,它会在光的作用下发生变化。

然后,光刻机会把光线投射到光刻胶上,把设计图案“照”到芯片上。

就像用大招打怪兽一样,光线把图案印在芯片上,接着要经过一系列的显影和蚀刻过程,把多余的光刻胶清理掉,留下我们需要的电路图案。

3. 光刻工艺的挑战与解决3.1. 精度要求高光刻工艺工程师面临的挑战可真不少。

首先是精度要求超高。

现在的芯片技术发展得飞快,图案越来越小,精度要求也越来越高。

就像在沙滩上画画一样,一点点细微的误差都会影响到最终效果。

工程师们得不断调整设备,确保每一个图案都能完美地展现在芯片上。

3.2. 解决问题的智慧再有就是解决问题的智慧。

光刻过程中可能会遇到各种各样的问题,比如光刻胶的质量问题、设备的故障,甚至是环境的变化都会影响到最终结果。

光刻清洗工艺简介

涂胶的质量要求是: (1)膜厚符合设计的要求,同时膜厚要均匀,胶面上看 不到干涉花纹; (2)胶层内无点缺陷(如针孔等); (3)涂层表面无尘埃和碎屑等颗粒。 膜厚的大小可由下式决定:

T KP2 / S 1/2

式中,T为膜厚;P为光刻胶中固体的百分比含量;S为涂 布机的转速;K为常数。

影响胶厚的因素有:

滴胶时常出现问题:

涂胶的典型过程为: 接片对中→稳定转速→滴胶→慢速匀胶→快速匀胶→硅片 底部清洗→硅片顶部去边→快速甩干 为什么要去边 去边分为两步,为底部去边和顶部去边。由于快速甩胶 时,整个涂胶腔体内弥漫着溶剂和光刻胶的微粒,一部分 光刻胶微粒会黏附在硅片的底部,在随后的工艺过程中会 对其它设备造成沾污,所以利用位于硅片底部的一个喷嘴, 对硅片底部进行清洗。在快速甩胶结束后,整个硅片上分 布的是均匀厚度的光刻胶,但在硅片表面的最外缘一圈, 由于气流的影响,胶层特别厚,因在随后的工艺(如腐蚀 或注入等)处理中,为了传输或固定,一些设备中的某些 机构会接触到硅片表面的边缘,摩擦会使边缘的胶脱落, 对设备造成颗粒沾污。

① 硅片的温度 ② 胶的温度 ③ 环境温度和湿度 ④ 排风量 ⑤ 涂胶程序(预匀的转速和时间,快速匀胶的速度, 加速度等) ⑥ 胶本身的黏度 ⑦ 胶量 前烘的温度、时间及方式

(三)前烘 :

目的 蒸发掉胶中的有机溶剂成分,使晶圆表面 的胶固化。增加光刻 胶与衬底间的粘附性、光吸收以及抗腐蚀能力;缓和涂胶过程中 胶膜内产生的应力等。这个过程中胶中的溶剂基本被蒸发掉,因 而通常 情况下胶的厚度会变薄(大约减少25%) 方法 可在热板或烘箱中进行。每一种胶都有其特定的前烘温度和时间, 更厚的胶可能需要更长的时间。

4、显影机

(1)工作原理:不同的显影方式(喷淋式、浸没式、水柱式)有 不同的显影过程,以喷涂式为例,它的显影过程为:显影液喷洒, 使显影液覆盖整个硅片表面 → 静臵显影 → 冲水清洗 (2)主要技术参数 (喷涂显影)

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第8章 光刻工艺概述

2014年11月5日2时34分

8.1 光刻技术的发展

3、将硅片进行化学处理以便制备 可以控制晶体管电流的源区和漏 区。在硅片上涂上一层称为感光 胶的光敏性材料膜。

3

第8章 光刻工艺概述

2014年11月5日2时34分

8.1 光刻技术的发展

4、对涂有感光胶的硅片, 用分步重复曝光机的设备, 通过掩膜板进行重复曝光。 它能将芯片图形分步重复 的曝光在整个硅片上。这 种重复曝光过程与复印负 性照片的过程相似。在显 影过程中曝过光的区域感 光胶留了下来,未曝过光 的胶层被清除掉了。

8

第8章 光刻工艺概述

2014年11月5日2时34分

8.1 光刻技术的发展

9、对于图形矩阵的硅片进行适当 的切割、压焊,即成了封装好的 芯片。引出适合的电学外引线。

9

第8章 光刻工艺概述

2014年11月5日2时34分

8.1 光刻技术的发展

8.1.2 光刻技术基本原理

光刻是现代IC制造业的基石,它能在硅 片衬底上印制出亚微米尺寸的图形。

2) Spin coat

3) Soft bake

4) Alignment and Exposure

5) Post-exposure bake

6) Develop

7) Hard bake

8) Develop inspect

2014年11月5日2时34分

正性光刻

Ultraviolet light Areas exposed to light are dissolved. Chrome island on glass mask Shadow on photoresist Island

photoresist Photoresist

22

第8章 光刻工艺概述

201ight Chrome island on glass mask Areas exposed to light become crosslinked and resist the developer chemical. Exposed area of photoresist Island Window

5

第8章 光刻工艺概述

2014年11月5日2时34分

8.1 光刻技术的发展

6、下一步是制备晶体管的栅极、 淀积SiO2层并使之图形化(形成 栅氧化层)之后淀积多晶硅和重 掺杂多晶硅层,形成多晶硅栅。 多晶硅栅对源区和漏区之间流动 的电流起到象水龙头那样的“开” 和“关”的作用。

6

第8章 光刻工艺概述

4

第8章 光刻工艺概述

2014年11月5日2时34分

8.1 光刻技术的发展

5、掺杂杂质的原子如硼、砷等 可以用注入技术来掺杂入硅原子 中去,然后用热退火的方法使注 入离子“活化”。感光胶层能阻 挡杂质离子的注入,离子注入后 的胶层可以用移胶的办法把它去 掉,当要在硅片的其它区域掺杂 别的杂质时,可以重复使用离子 注入工艺。在随后的几道工艺中, 还会多次用图形制备工艺(光刻 工艺),但感光胶层这时可用作 腐蚀掩膜用。

Photoresist

Shadow on photoresist

Photoresist Oxide Silicon substrate

Oxide Silicon substrate

Resulting pattern after the resist is developed. 23

第8章 光刻工艺概述

对大尺寸晶圆的加工

大尺寸的晶圆对光刻技术要求更为苛刻。

13

第8章 光刻工艺概述

2014年11月5日2时34分

8.1 光刻技术的发展

精密的套刻对准

因为最终的图形是用多个掩膜 版按照特定的顺序在晶圆表 面一层一层叠加建立起来的。 图形定位的要求就好像是一 幢建筑物每一层之间所要求 的正确对准。如果每一次的 定位不准,将会导致整个电 路失效。

2014年11月5日2时34分

8.1 光刻技术的发展

7、制备工艺的其它部分是将晶体 管的栅极、源极、漏极之间和对 其它元件、对外部的连线用金属 膜作连线将它们连起来。二氧化 硅层是一种介质层,也是一种绝 缘层,是用化学汽淀积(CVD)方法 形成的,在CVD方法中所含某种 材料的原子与淀积的受热硅片的 表面发生反应,形成某种材料的 固体薄膜。PVD又称溅射技术, 是气体离子受电场加速并轰击靶 材,使它的原子脱离靶材并溅落 和积累在硅片上。

21

第8章 光刻工艺概述

2014年11月5日2时34分

8.2 基本光刻工艺流程

刚才介绍了对光有负效应的光刻胶,称为负胶。同样 还有对光有正效应的光刻胶,称为正胶。用正胶和亮 场掩膜版在晶圆表面建立凸起图形的情况如图所示。 右图显示了用不同极 性的掩膜版和不同极 性的光刻胶相结合而 产生的结果。通常是 根据尺寸控制的要求 和缺陷保护的要求来 选择光刻胶和掩膜版 极性的。

Window

Exposed area of photoresist

photoresist Photoresist oxide Oxide silicon substrate Silicon substrate oxide Oxide silicon substrate substrate Silicon

Linewidth

Space Photoresist

Thickness

Substrate

19

第8章 光刻工艺概述

2014年11月5日2时34分

8.2 基本光刻工艺流程

如果掩膜版的图形是 由不透光的区域决定的, 称其为亮场掩膜版;而 在一个暗场掩膜版中, 掩膜版上的图形是用相 反的方式编码的,如果 按照同样的步骤,就会 在晶圆表面留下凸起的 图形(?)。 暗场掩膜版主要用来 制作反刻金属互联线。

7

第8章 光刻工艺概述

2014年11月5日2时34分

8.1 光刻技术的发展

8、第3、4和5步工艺会反复多次 使用,使SiO2层、金属层和其它 材料层形成图形,以往成完整的 电路设计。金属层(通常是铝和 铜)是用CVD或PVD方法淀积的, 经曝光光刻、腐蚀等工艺后形成 薄的金属连线。对于复杂的芯片 有时还要求用多金属层和通常所 称的通孔进行垂直连线来形成复 杂的芯片连线。

1:1 Mask 4:1 Reticle

2014年11月5日2时34分

投影掩模版(Reticle):石英板,包含了在晶圆上重复生成 的图形。由一个晶体管或多个晶体管组成。 光掩模版(Mask),也是石英板,包含了对于整块硅 片某一工艺层上所有晶体管加工信息。

18

第8章 光刻工艺概述

2014年11月5日2时34分

Cross section of CMOS inverter

15

PMOSFET

NMOSFET

第8章 光刻工艺概述

2014年11月5日2时34分

8.2 基本光刻工艺流程

工艺步骤

对准和曝光

目的 掩膜 / 图形

在掩膜版和图形在晶圆上 的精确对准和光刻胶的曝 光。负胶是聚合物

晶圆

光刻胶 氧化层

显影

去除非聚合的光刻胶

亮场

暗场

20

第8章 光刻工艺概述

2014年11月5日2时34分

亮场掩模版和暗场掩模版

Clear Field Mask Dark Field Mask

Simulation of metal interconnect lines (positive resist lithography)

Simulation of contact holes (positive resist lithography)

晶圆

光刻胶 氧化层

图形转移通过两步完成。首先,图形被转移到光刻胶层。光刻胶经过曝光 后自身性质和结构发生变化(由原来的可溶性物质变为非可溶性物质,或 者相反)。再通过化学溶剂(显影剂)把可以溶解的部分去掉,在光刻层 下就会留下一个孔,而这个孔就是和掩膜版不透光的部分相对应

16

第8章 光刻工艺概述

2014年11月5日2时34分

#2 栅掩膜

#1 阱掩膜

#3 接触 掩膜

#4 金属 掩膜 #5 PAD 掩膜

14

第8章 光刻工艺概述

2014年11月5日2时34分

Top view of CMOS inverter

The masking layers determine the accuracy by which subsequent processes can be performed. The photoresist mask pattern prepares individual layers for proper placement, orientation, and size of structures to be etched or implanted. Small sizes and low tolerances do not provide much room for error.

第8章 光刻工艺概述

2014年11月5日2时34分

8.1 光刻技术的发展

高灵敏度的光刻胶

光刻胶的灵敏度通常是指光刻胶的感光速度。 在集成电路工艺中,为了提高产品产量,希望 曝光速度越快越好。

12

第8章 光刻工艺概述

2014年11月5日2时34分

8.1 光刻技术的发展

低缺陷

一般集成电路的加工需要几十步甚至上百步工序,而在 其中光刻大概要占10~20次,每次光刻都要尽量避免缺 陷。

25

第8章 光刻工艺概述

2014年11月5日2时34分

8.2 基本光刻工艺流程

八步基本的光刻工艺

气相成底膜处理 曝光后烘焙

旋转涂胶