quartus常见错误集锦

使用QuartusII常犯的错误

使用QuartusII常犯的错误1) QuartusII对代码进行时序仿真时出现Error: Can't continue timing simulation because delay annotation information for design is missing.原因:如果只需要进行功能仿真,不全编译也是可以进行下去的,但时序仿真就必须进行全编译(即工具栏上的紫色实心三角符号那项)。

全仿真包括四个模块:综合器(Synthesis)、电路装配器(Fitter)、组装器(Assember)和时序分析器(Timing Analyzer),任务窗格中会有成功标志(对号)。

2) 在下载运行的时候,出现下面的错误:Warning: The JTAG cable you are using is not supported for Nios II systems. You may experience intermittent JTAG communicationfailures with this cable. Please use a USB Blaster revision B.在运行之前已经将.sof文件下载到开发板上面了,但是依然出现上面的问题。

解决:在配置的时候,在run之后,进行配置,选择target connection,在最后一项:NIOS II Terminal Communication Device中,要选择none(不要是Jtag_uart)如果采用USB Blaster,可以选择Jtag_uart。

之后再run就ok了!3)Error: Can't compile duplicate declarations of entity "count3" into library "work"此错误一般是原理图文件的名字和图中一个器件的名字重复所致,所以更改原理图文件的名字保存即可。

QUARTUS错误分析.doc

Quartus常见错误分析ErrorWarning: VHDL Process Statement warning at random.vhd(18): signal reset is in statement, but is not insensitivity list----没把singal放到process()中2 Warning: Found pins ing as undefined clocks and/or memory enablesInfo: Assuming node CLK is an undefined clock-=-----可能是说设计中产生的触发器没有使能端3 Error: VHDL Interface Declaration error in clk_gen.vhd(29): interface object "clk_scan" of mode outcannot be read. Change object mode to buffer or inout.------信号类型设置不对,out当作buffer来定义4 Error: Node instance "clk_gen1" instantiates undefined entity "clk_gen"-------引用的例化元件未定义实体--entity "clk_gen"5 Warning: Found 2 node(s) in clock paths which may be acting as ripple and/or gated clocks -- node(s)analyzed as buffer(s) resulting in clock skewInfo: Detected ripple clock "clk_gen:clk_gen1|clk_incr" as bufferInfo: Detected ripple clock "clk_gen:clk_gen1|clk_scan" as buffer6 Warning: VHDL Process Statement warning at ledmux.vhd(15): signal or variable "dataout" may not beassigned a new in every possible path through the Process Statement. Signal or variable "dataout" holdsits previous in every path with no new assignment, which may create a combinational loop in the currentdesign.7 Warning: VHDL Process Statement warning at divider_10.vhd(17): signal "cnt" is read inside the ProcessStatement but isn't in the Process Statement's sensivitity list-----缺少敏感信号8 Warning: No clock transition on "counter_bcd7:counter_counter_clk|q_sig[3]" register9 Warning: Reduced register "counter_bcd7:counter_counter_clk|q_sig[3]" with stuck clock port to stuckGND10 Warning: Circuit may not operate. Detected 1 non-operational path(s) clocked by clock "class[1]" withclock skew larger than data delay. See Compilation Report for details.11 Warning: Circuit may not operate. Detected 1 non-operational path(s) clocked by clock "sign" withclock skew larger than data delay. See Compilation Report for details.12 Error: VHDL error at counter_clk.vhd(90): actual port "class" of mode "in" cannot be associated withformal port "class" of mode "out"------两者不能连接起来13 Warning: Ignored node in vector source file. Can't find corresponding node name"class_sig[2]" indesign.------没有编写testbench文件,或者没有编辑输入变量的值 testbench里是元件申明和映射14 Error: VHDL Binding Indication error at freqdetect_top.vhd(19): port "class" in design entity doesnot have std_logic_vector type that is specified for the same generic in the associated component---在相关的元件里没有当前文件所定义的类型15 Error: VHDL error at tongbu.vhd(16): can't infer register for signal "gate" because signal does nothold its outside clock edge16 Warning: Found clock high time violation at 1000.0 ns on register"|fcounter|lpm_counter:temp_rtl_0|dffs[4]"17 Warning: Compiler packed, optimized or synthesized away node "temp[19]". Ignored vector source filenode.---"temp[19]"被优化掉了18 Warning: Reduced register "gate~reg0" with stuck data_in port to stuck GND19 Warning: Design contains 2 input pin(s) that do not drive logicWarning: No output dependent on input pin "clk"Warning: No output dependent on input pin "sign"------输出信号与输入信号无关,20 Warning: Found clock high time violation at 16625.0 ns on register "|impulcomp|gate1"21 Error: VHDL error at impulcomp.vhd(19): can't implement clock enable condition specified using binaryoperator "or"22 Error: VHDL Association List error at period_counter.vhd(38): actual parameter assigned to formalparameter "alarm", but formal parameter is not declared-------连接表错误,形参"alarm"赋值给实参,形参没定义,可能是形参与实参的位置颠倒了,规定形参在实参之前。

quartus ii 常见的19个错误28个警告

(一) Q uartus警告解析(二)(三) 1.Found clock-sensitive change during active clock edge at time<time> on register"<name>"(四) 原因:vector source file中时钟敏感信号(如:数据,允许端,清零,同步加载等)在时钟的边缘同时变化。

而时钟敏感信号是不能在时钟边沿变化的。

其后果为导致结果不正确。

(五) 措施:编辑vector source file(六)(七) 2.Verilog HDL assignment warning at <location>: truncated with size <number> tomatch size of target (<number>(八) 原因:在HDL设计中对目标的位数进行了设定,如:reg[4:0] a;而默认为32位,将位数裁定到合适的大小(九) 措施:如果结果正确,无须加以修正,如果不想看到这个警告,可以改变设定的位数(十)(十一) 3.All reachable assignments to data_out(10) assign '0', register removed by optimization(十二) 原因:经过综合器优化后,输出端口已经不起作用了(十三)(十四) 4.Following 9 pins have nothing, GND, or VCC driving datain port -changes to this connectivity may change fitting results(十五) 原因:第9脚,空或接地或接上了电源(十六) 措施:有时候定义了输出端口,但输出端直接赋‘0’,便会被接地,赋‘1’接电源。

Quartus常见错误

Quartus常见错误1:看看警告:it conflicts with Quartus II primitive name,实体名和QUARTUS 的保留字冲突,楼主把实体名改一下就行了。

有很多这种名字都不能乱起的比如or2 and2 啥的。

为什么还提示“Error: Top-level design entity "and2" is undefined”library ieee;use ieee.std_logic_1164.all;entity and2 isport(a,b:in std_logic;y ut std_logic);end and2;architecture and2_1 of and2 isbeginy<=a nand b;end and2_1;在设置里已经设定top-level entity为and2了怎么还是报错啊!标题:关于quartus中模块的引用2009-05-27 17:10:35quartus中一个工程中可包含一个顶层模块,多个子模块,通过顶层模块引用子模块。

1:顶层模块的实体名必须与建立工程时的实体名一致,否则编译时会出错,如下Error: Top-level design entity "AND" is undefined2,多个实体文件建立后在quartus界面左边的工程文件夹中找到要作为顶层文件的文件点击右键设置为顶层文件3.所有文件设置好后再进行编译,单独编译某个文件的话肯定错误很多。

/Detail/DefaultView.aspx?BookId=ISBN7-115-13204-6里面有一个调用模块的例子,书中间的子模块命名为NAND编译时不能通过,后来改个名字NAND11就通过了,难道NAND是关键词不可用来命名?错误为:Top-level design entity "rojectName" is undefined我已经把项目名称和顶层设计的名称设为一样的而且有时候出现这样的情况,有时候又不出现这样的情况例如下面这个例子//与非门行为描述module NAND(in1,in2,out);input in1,in2;output out;//连续赋值语句assign out=~(in1&in2);endmodule我建工程后就会提示Top-level design entity "NAND" is undefined这个例子是从电子书上直接拷贝过来的,我很好奇的是有的例子可以运行,有的例子不可以。

Quartus II常见错误

1.Found clock-sensitive change during active clock edge at time <time> on register "<name>"原因:vector source file中时钟敏感信号(如:数据,允许端,清零,同步加载等)在时钟的边缘同时变化。

而时钟敏感信号是不能在时钟边沿变化的。

其后果为导致结果不正确。

措施:编辑vector source file2.Verilog HDL assignment warning at <location>: truncated with size <number> to match size of target (<number>原因:在HDL设计中对目标的位数进行了设定,如:reg[4:0] a;而默认为32位,将位数裁定到合适的大小措施:如果结果正确,无须加以修正,如果不想看到这个警告,可以改变设定的位数3.All reachable assignments to data_out(10) assign '0', register removed by optimization原因:经过综合器优化后,输出端口已经不起作用了4.Following 9 pins have nothing, GND, or VCC driving datain port -- changes to this connectivity may change fitting results原因:第9脚,空或接地或接上了电源措施:有时候定义了输出端口,但输出端直接赋…0‟,便会被接地,赋…1‟接电源。

如果你的设计中这些端口就是这样用的,那便可以不理会这些warning5.Found pins ing as undefined clocks and/or memory enables原因:是你作为时钟的PIN没有约束信息。

Quartus常见问题

Quartus常见错误1.Error (10028): Can't resolve multiple constant drivers for net ……解析:不能在两个以上always内对同一变量赋值,这个细节一般看书看资料会看到,但是编程时,就是没想到。

2.Error (10158): Verilog HDL Module Declaration error at clkseg.v(1): port"XXXX" is not declared as port解析:大意了,端口类型还没定义啊!3.Error (10110): variable "en" has mixed blocking and nonblocking ProceduralAssignments -- must be all blocking or all nonblocking assignments解析:en在程序中有时用非阻塞赋值,有时用阻塞赋值,这是禁止的。

在初学的时候,可能分得不是很清楚,所以在检查时,一定要一步步观察慢慢来。

4.Error (10161): Verilog HDL error at clkseg.v(36): object "count" is notdeclared解析:这个错误应该很明显啦,只要能读得懂。

5.Error (10170): Verilog HDL syntax error at clkseg.v(37) near text "***";expecting ";"解析:意思应该也很简单,就是检查的时候要细心点。

6.Error (10171): Verilog HDL syntax error at ir_ctrl.v(149) near end of file ;expecting an identifier, or "endmodule", or a parallel statement解析:最后上了endmodule。

Quartus常见错误分析Error

Quartus常见错误分析ErrorQuartus常见错误分析ErrorWarning: VHDL Process Statement warning at random.vhd(18): signal reset is in statement, but is not in sensitivity list----没把singal放到process()中2 Warning: Found pins ing as undefined clocks and/or memory enablesInfo: Assuming node CLK is an undefined clock-=-----可能是说设计中产⽣的触发器没有使能端3 Error:VHDL Interface Declaration error in clk_gen.vhd(29): interface object "clk_scan" of mode out cannot be read. Change object mode to buffer or inout.------信号类型设置不对,out当作buffer来定义4 Error:Node instance "clk_gen1" instantiates undefined entity "clk_gen"-------引⽤的例化元件未定义实体--entity "clk_gen"5 Warning: Found 2 node(s) in clock paths which may be acting as ripple and/or gated cl ocks -- node(s) analyzed as buffer(s) resulting in clock skewInfo: Detected ripple clock "clk_gen:clk_gen1|clk_incr" as bufferInfo: Detected ripple clock "clk_gen:clk_gen1|clk_scan" as buffer6 Warning: VHDL Process Statement warning at ledmux.vhd(15): signal or variable "datao ut" may not be assigned a new in every possible path through the Process Statement. Signal or variable " dataout" holds its previous in every path with no new assignment, which may create a combinational loo p in the current design.7 Warning: VHDL Process Statement warning at divider_10.vhd(17): signal "cnt" is read i nside the Process Statement but isn't in the Process Statement's sensivitity list-----缺少敏感信号8 Warning: No clock transition on "counter_bcd7:counter_counter_clk|q_sig[3]" register9 Warning: Reduced register "counter_bcd7:counter_counter_clk|q_sig[3]" with stuck clock port to stuck GND10 Warning: Circuit may not operate. Detected 1 non-operational path(s) clocked by clock "class[1]" with clock skew larger than data delay. See Compilation Report for details.11 Warning: Circuit may not operate. Detected 1 non-operational path(s) clocked by clock "sign" with clock skew larger than data delay. See Compilation Report for details.12 Error:VHDL error at counter_clk.vhd(90): actual port "class" of mode "in" cannot be associated with formal port "class" of mode "out"------两者不能连接起来13 Warning: Ignored node in vector source file. Can't find corresponding node name "clas s_sig[2]" indesign.------没有编写testbench⽂件,或者没有编辑输⼊变量的值 testbench⾥是元件申明和映射14 Error:VHDL Binding Indication error at freqdetect_top.vhd(19): port "class"in design entity doesnot have std_logic_vector type that is specified for the same generic in the associated com ponent---在相关的元件⾥没有当前⽂件所定义的类型15 Error:VHDL error at tongbu.vhd(16): can't infer register for signal "gate" because sign al does nothold its outside clock edge16 Warning: Found clock high time violation at 1000.0 ns on register"|fcounter|lpm_counter:temp_rtl_0|dffs[4]"17 Warning: Compiler packed, optimized or synthesized away node "temp[19]". Ignored ve ctor source filenode.---"temp[19]"被优化掉了18 Warning: Reduced register "gate~reg0" with stuck data_in port to stuck GND19 Warning: Design contains 2 input pin(s) that do not drive logicWarning: No output dependent on input pin "clk"Warning: No output dependent on input pin "sign"------输出信号与输⼊信号⽆关,20 Warning: Found clock high time violation at 16625.0 ns on register "|impulcomp|gate1"21 Error:VHDL error at impulcomp.vhd(19): can't implement clock enable condition speci fied using binaryoperator "or"22 Error:VHDL Association List error at period_counter.vhd(38): actual parameter assigned to formalparameter "alarm", but formal parameter is not declared-------连接表错误,形参"alarm"赋值给实参,形参没定义,可能是形参与实参的位置颠倒了,规定形参在实参之前。

Quartus_2_使用错误集锦

版本修订日期修订内容0.12013年11月14日初始版本目录Chapter1软件安装常出现的错误 (3)Chapter2软件编译常出现的错误 (4)Quartus安装和编译常见错误和警告在QuartusII软件安装和编译过程中会出现一些错误和警告,有的可以忽略,有的却需要注意。

虽然按F1可以了解关于该警告的帮助,但有时候帮助解释的仍然不清楚。

这篇教程总结了一些常见的错误和警告,并给出了相应的解决办法。

Chapter1软件安装常出现的错误本章主要介绍在QuartusII软件安装是常出现的错误,并给出了相应的解决办法。

1.软件的安装文件选取不对解决方法:在使用4代开发板时,需要安装两个文件,分别为:2.破解是破解器使用不对解决方法:我们的开发板支持12.0以上的quartus软件,如果您安装了较低版本的软件,请完全卸载后,在安装,否则会照成USB-blaster安装驱动出现问题。

安装软件时还要注意您电脑的系统是32位还是64位(点击计算机图标右键属性就可以查看),如果是32位请选择x86,例如:如果是64位请选择x64,请注意。

3.在复制网卡号时,没有复制一个,而是复制多个。

解决方法:如果在破解时出现多个网卡号时,复制一个就可以,不要全部复制。

4.下载时无法使用JTAG或者AS正常下载解决办法:检查开发板是否上电;检查下载器驱动是否安装;检查下载器是否连接对应下载口(4代开发板左边JTAG接口,右边AS下载接口);检查mode选取是否正确,JTAG模式下选取:AS模式下选取:5.下载程序失败解决方法:检查开发板是否上电;检查下载器的驱动是否安装;检查烧写文件的格式是否正确,开发板有两种模式可以进行下载,JATG和AS模式,JATG模式下载的文件后缀为.sof。

在JATG模式下,掉电后文件会丢失。

AS模式下载的文件后缀为.pof。

在AS模式下,掉电后文件不会丢失。

Chapter2软件编译常出现的错误本章主要介绍在QuartusII在编译过程中是常出现的错误和警告,并给出了相应的解决办法。

Quartus中仿真出现错误解决方案汇总(可编辑)

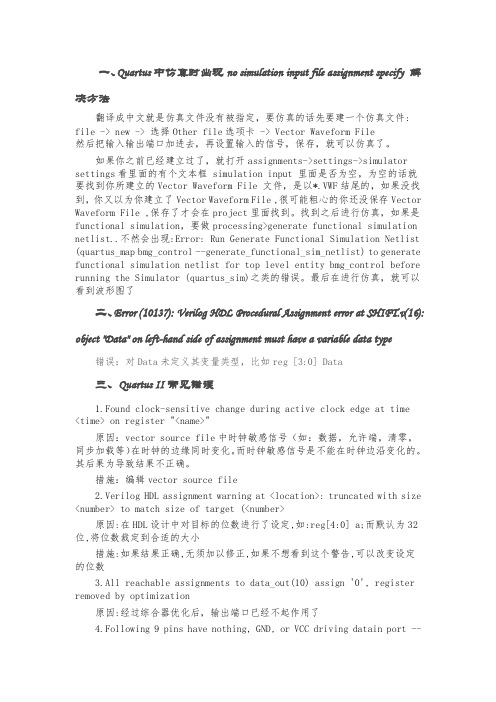

一Quartus 中仿真时出现no simulation input file assignment specify 解决方法翻译成中文就是仿真文件没有被指定要仿真的话先要建一个仿真文件file - new - 选择 Other file 选项卡 - Vector Waveform File然后把输入输出端口加进去再设置输入的信号保存就可以仿真了如果你之前已经建立过了就打开assignments- settings- simulatorsettings 看里面的有个文本框 simulation input 里面是否为空为空的话就要找到你所建立的 Vector Waveform File 文件是以VWF 结尾的如果没找到你又以为你建立了 Vector Waveform File 很可能粗心的你还没保存VectorWaveform File 保存了才会在 project 里面找到找到之后进行仿真如果是functional simulation要做processing generate functional simulationnetlist不然会出现Error Run Generate Functional Simulation Netlist quartus_map bmg_control--generate_functional_sim_netlist to generatefunctional simulation netlist for top level entity bmg_control beforerunning the Simulator quartus_sim 之类的错误最后在进行仿真就可以看到波形图了二Error 10137 Verilog HDL Procedural Assignment error at SHIFTv 16object "Data" on left-hand side of assignment must have a variable data type错误对 Data 未定义其变量类型比如 reg [30] Data三Quartus II 常见错误1Found clock-sensitive change during active clock edge at time on register " "原因vector source file 中时钟敏感信号如数据允许端清零同步加载等在时钟的边缘同时变化而时钟敏感信号是不能在时钟边沿变化的其后果为导致结果不正确措施编辑 vector source file2Verilog HDL assignment warning at truncated with sizeto match size of target原因在 HDL 设计中对目标的位数进行了设定如reg[40] a而默认为32位将位数裁定到合适的大小措施如果结果正确无须加以修正如果不想看到这个警告可以改变设定的位数3All reachable assignments to data_out 10 assign 0 register removed by optimization原因经过综合器优化后输出端口已经不起作用了4Following 9 pins have nothing GND or VCC driving datain port --changes to this connectivity may change fitting results原因第 9 脚空或接地或接上了电源措施有时候定义了输出端口但输出端直接赋 0便会被接地赋 1 接电源如果你的设计中这些端口就是这样用的那便可以不理会这些warning5Found pins ing as undefined clocks andor memory enables 原因是你作为时钟的 PIN 没有约束信息可以对相应的 PIN 做一下设定就行了主要是指你的某些管脚在电路当中起到了时钟管脚的作用比如flip-flop 的 clk 管脚而此管脚没有时钟约束因此 QuartusII 把 clk 作为未定义的时钟措施如果 clk 不是时钟可以加 not clock的约束如果是可以在clock setting 当中加入在某些对时钟要求不很高的情况下可以忽略此警告或在这里修改Assignments Timing analysis settings Individualclocks6Timing characteristics of device EPM570T144C5 are preliminary 原因因为II 是比较新的元件在 QuartusII 中的时序并不是正式版的要等 Service Pack措施只影响 Quartus 的 Waveform7Warning Clock latency analysis for PLL offsets is supported for the current device family but is not enabled措施将 setting 中的timing RequirementsOption-- More Timing Setting-- setting-- Enable Clock Latency 中的on 改成OFF8Found clock high time violation at 148 ns on register"counterlpm_countercount1_rtl_0dffs[11]"原因违反了 steuphold 时间应该是后仿真看看波形设置是否和时钟沿符合 steuphold 时间措施在中间加个寄存器可能可以解决问题9warning circuit may not operatedetected 46 non-operational pathsclocked by clock clk44 with clock skew larger than data delay 原因时钟抖动大于数据延时当时钟很快而 if 等类的层次过多就会这种问题但这个问题多是在器件的最高频率中才会出现措施setting-- timing RequirementsOptions-- Default required f改小一些如改到 50MHZ10Design contains input pin s that do not drive logic 原因输入引脚没有驱动逻辑驱动其他引脚所有的输入引脚需要有输入逻辑措施如果这种情况是故意的无须理会如果非故意输入逻辑驱动 11WarningFound clock high time violation at 89ns on node TEST3CLK原因FF 中输入的PLS 的保持时间过短措施在 FF 中设置较高的时钟频率12Warning Found 10 node s in clock paths which may be acting asripple andor gated clocks -- node s analyzed as buffer s resulting inclock skew原因如果你用的 CPLD 只有一组全局时钟时用全局时钟分频产生的另一个时钟在布线中当作信号处理不能保证低的时钟歪斜 SKEW 会造成在这钟上工作的时序电路不可靠甚至每次布线产生的问题都不一样措施如果用有两组以上全局时钟的 FPGA 芯片可以把第二个全局时钟作为另一个时钟用可以解决这个问题13Critical Warning Timing requirements were not met See Report window for details原因时序要求未满足措施双击Compilation Report-- Time Analyzer-- 红色部分如clocksetupclk等-- 左键单击 list path查看 f 的 SLACK REPORT 再根据提示解决有可能是程序的算法问题14Cant achieve minimum setup。

Quartus常规错误集锦

Quartus常规错误集锦FPGA错误集锦1) QuartusII对代码进行时序仿真时出现Error: Can't continue timing simulation because delay annotation information for design is missing.原因:如果只需要进行功能仿真,不全编译也是可以进行下去的,但时序仿真就必须进行全编译(即工具栏上的紫色实心三角符号那项)。

全仿真包括四个模块:综合器(Synthesis)、电路装配器(Fitter)、组装器(Assember)和时序分析器(Timing Analyzer),任务窗格中会有成功标志(对号)。

2) 在下载运行的时候,出现下面的错误:Warning: The JTAG cable you are using is not supported for Nios II systems. You may experience intermittent JTAG communicationfailures with this cable. Please use a USB Blaster revision B.在运行之前已经将.sof文件下载到开发板上面了,但是依然出现上面的问题。

解决:在配置的时候,在run之后,进行配置,选择target connection,在最后一项:NIOS II Terminal Communication Device中,要选择none(不要是Jtag_uart)如果采用USB Blaster,可以选择Jtag_uart。

之后再run就ok了!3)Error: Can't compile duplicate declarations of entity "count3" into library "work"此错误一般是原理图文件的名字和图中一个器件的名字重复所致,所以更改原理图文件的名字保存即可。

Quartus 中仿真出现错误解决方案汇总

一、Quartus中仿真时出现no simulation input file assignment specify 解决方法翻译成中文就是仿真文件没有被指定,要仿真的话先要建一个仿真文件: file -> new -> 选择Other file选项卡 -> Vector Waveform File然后把输入输出端口加进去,再设置输入的信号,保存,就可以仿真了。

如果你之前已经建立过了,就打开assignments->settings->simulator settings看里面的有个文本框 simulation input 里面是否为空,为空的话就要找到你所建立的Vector Waveform File 文件,是以*.VWF结尾的,如果没找到,你又以为你建立了Vector Waveform File ,很可能粗心的你还没保存Vector Waveform File ,保存了才会在project里面找到。

找到之后进行仿真,如果是functional simulation,要做processing>generate functional simulation netlist..不然会出现:Error: Run Generate Functional Simulation Netlist (quartus_map bmg_control --generate_functional_sim_netlist) to generate functional simulation netlist for top level entity bmg_control before running the Simulator (quartus_sim)之类的错误。

最后在进行仿真,就可以看到波形图了二、Error (10137): Verilog HDL Procedural Assignment error at SHIFT.v(16): object "Data" on left-hand side of assignment must have a variable data type 错误:对Data未定义其变量类型,比如reg [3:0] Data三、Quartus II常见错误1.Found clock-sensitive change during active clock edge at time<time> on register "<name>"原因:vector source file中时钟敏感信号(如:数据,允许端,清零,同步加载等)在时钟的边缘同时变化。

Quartus错误大全

Quartus常见错误分析1 Warning: VHDL Process Statement warning at random.vhd(18): signal reset is in statement, but is not in sensitivity list----没把singal放到process()中2 Warning: Found pins ing as undefined clocks and/or memory enables Info: Assuming node CLK is an undefined clock-=-----可能是说设计中产生的触发器没有使能端3 Error: VHDL Interface Declaration error in clk_gen.vhd(29): interface object "clk_scan" of mode out cannot be read. Change object mode to buffer or inout.------信号类型设置不对,out当作buffer来定义4 Error: Node instance "clk_gen1" instantiates undefined entity "clk_gen" -------引用的例化元件未定义实体--entity "clk_gen"5 Warning: Found 2 node(s) in clock paths which may be acting as ripple and/or gated clocks -- node(s) analyzed as buffer(s) resulting in clock skewInfo: Detected ripple clock "clk_gen:clk_gen1/clk_incr" as buffer Info: Detected ripple clock "clk_gen:clk_gen1/clk_scan" as buffer6 Warning: VHDL Process Statement warning at ledmux.vhd(15): signal or variable "dataout" may not be assigned a new in every possible path through the Process Statement. Signal or variable "dataout" holds its previous in every path with no new assignment, which may create a combinational loop in the current design.7 Warning: VHDL Process Statement warning at divider_10.vhd(17): signal "cnt" is read inside the Process Statement but isn''t in the Process Statement''s sensivitity list-----缺少敏感信号8 Warning: No clock transition on"counter_bcd7:counter_counter_clk/q_sig[3]" register9 Warning: Reduced register "counter_bcd7:counter_counter_clk/q_sig[3]" with stuck clock port to stuck GND10 Warning: Circuit may not operate. Detected 1 non-operational path(s) clocked by clock "class[1]" with clock skew larger than data delay. See Compilation Report for details.11 Warning: Circuit may not operate. Detected 1 non-operational path(s) clocked by clock "sign" with clock skew larger than data delay. See Compilation Report for details.12 Error: VHDL error at counter_clk.vhd(90): actual port "class" of mode "in" cannot be associated with formal port "class" of mode "out"------两者不能连接起来13 Warning: Ignored node in vector source file. Can''t find corresponding node name "class_sig[2]" in design.------没有编写testbench文件,或者没有编辑输入变量的值 testbench里是元件申明和映射14 Error: VHDL Binding Indication error at freqdetect_top.vhd(19): port "class" in design entity does not have std_logic_vector type that is specified for the same generic in the associated component---在相关的元件里没有当前文件所定义的类型15 Error: VHDL error at tongbu.vhd(16): can''t infer register for signal "gate" because signal does not hold its outside clock edge16 Warning: Found clock high time violation at 1000.0 ns on register "/fcounter/lpm_counter:temp_rtl_0/dffs[4]"17 Warning: Compiler packed, optimized or synthesized away node "temp[19]". Ignored vector source file node.---"temp[19]"被优化掉了18 Warning: Reduced register "gate~reg0" with stuck data_in port to stuck GND19 Warning: Design contains 2 input pin(s) that do not drive logic Warning: No output dependent on input pin "clk"Warning: No output dependent on input pin "sign"------输出信号与输入信号无关,20 Warning: Found clock high time violation at 16625.0 ns on register "/impulcomp/gate1"21 Error: VHDL error at impulcomp.vhd(19): can''t implement clock enable condition specified using binary operator "or"22 Error: VHDL Association List error at period_counter.vhd(38): actual parameter assigned to formal parameter "alarm", but formal parameter is not declared-------连接表错误,形参"alarm"赋值给实参,形参没定义,可能是形参与实参的位置颠倒了,规定形参在实参之前。

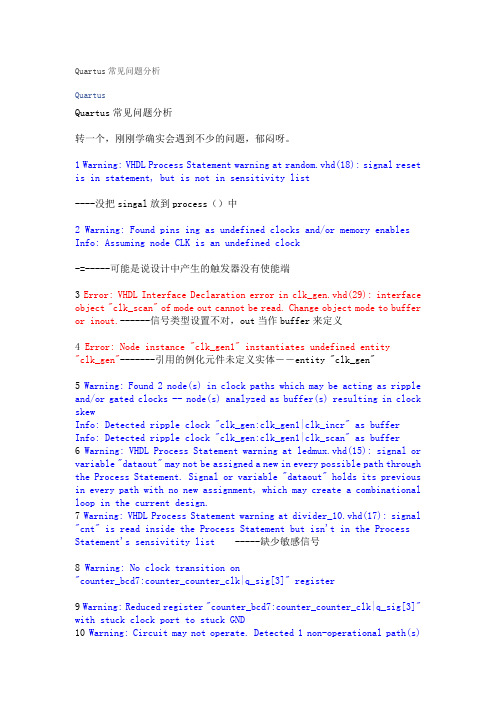

Quartus常见问题分析

Quartus常见问题分析QuartusQuartus常见问题分析转一个,刚刚学确实会遇到不少的问题,郁闷呀。

1 Warning: VHDL Process Statement warning at random.vhd(18): signal reset is in statement, but is not in sensitivity list----没把singal放到process()中2 Warning: Found pins ing as undefined clocks and/or memory enables Info: Assuming node CLK is an undefined clock-=-----可能是说设计中产生的触发器没有使能端3 Error: VHDL Interface Declaration error in clk_gen.vhd(29): interface object "clk_scan" of mode out cannot be read. Change object mode to buffer or inout.------信号类型设置不对,out当作buffer来定义4 Error: Node instance "clk_gen1" instantiates undefined entity"clk_gen"-------引用的例化元件未定义实体--entity "clk_gen"5 Warning: Found 2 node(s) in clock paths which may be acting as ripple and/or gated clocks -- node(s) analyzed as buffer(s) resulting in clock skewInfo: Detected ripple clock "clk_gen:clk_gen1|clk_incr" as buffer Info: Detected ripple clock "clk_gen:clk_gen1|clk_scan" as buffer6 Warning: VHDL Process Statement warning at ledmux.vhd(15): signal or variable "dataout" may not be assigned a new in every possible path through the Process Statement. Signal or variable "dataout" holds its previous in every path with no new assignment, which may create a combinational loop in the current design.7 Warning: VHDL Process Statement warning at divider_10.vhd(17): signal "cnt" is read inside the Process Statement but isn't in the Process Statement's sensivitity list -----缺少敏感信号8 Warning: No clock transition on"counter_bcd7:counter_counter_clk|q_sig[3]" register9 Warning: Reduced register "counter_bcd7:counter_counter_clk|q_sig[3]" with stuck clock port to stuck GND10 Warning: Circuit may not operate. Detected 1 non-operational path(s)clocked by clock "class[1]" with clock skew larger than data delay. See Compilation Report for details.11 Warning: Circuit may not operate. Detected 1 non-operational path(s) clocked by clock "sign" with clock skew larger than data delay. See Compilation Report for details.12 Error: VHDL error at counter_clk.vhd(90): actual port "class" of mode "in" cannot be associated with formal port "class" of mode "out"------两者不能连接起来13 Warning: Ignored node in vector source file. Can't find corresponding node name "class_sig[2]" in design.------没有编写testbench文件,或者没有编辑输入变量的值 testbench里是元件申明和映射14 Error: VHDL Binding Indication error at freqdetect_top.vhd(19): port "class" in design entity does not have std_logic_vector type that is specified for the same generic in the associated component---在相关的元件里没有当前文件所定义的类型15 Error: VHDL error at tongbu.vhd(16): can't infer register for signal "gate" because signal does not hold its outside clock edge16 Warning: Found clock high time violation at 1000.0 ns on register "|fcounter|lpm_counter:temp_rtl_0|dffs[4]"17 Warning: Compiler packed, optimized or synthesized away node "temp[19]". Ignored vector source file node.---"temp[19]"被优化掉了18 Warning: Reduced register "gate~reg0" with stuck data_in port to stuck GND19 Warning: Design contains 2 input pin(s) that do not drive logic Warning: No output dependent on input pin "clk"Warning: No output dependent on input pin "sign"------输出信号与输入信号无关,20 Warning: Found clock high time violation at 16625.0 ns on register "|impulcomp|gate1"21 Error: VHDL error at impulcomp.vhd(19): can't implement clock enable condition specified using binary operator "or"22 Error: VHDL Association List error at period_counter.vhd(38): actual parameter assigned to formal parameter "alarm", but formal parameter is not declared-------连接表错误,形参"alarm"赋值给实参,形参没定义,可能是形参与实参的位置颠倒了,规定形参在实参之前。

Quartus常见错误分析Error

Quartus常见错误分析ErrorQuartus常见错误分析ErrorWarning: VHDL Process Statement warning at random.vhd(18): signal reset is in statement, but is not in sensitivity list----没把singal放到process()中2 Warning: Found pins ing as undefined clocks and/or memory enablesInfo: Assuming node CLK is an undefined clock-=-----可能是说设计中产生的触发器没有使能端3 Error:VHDL Interface Declaration error in clk_gen.vhd(29): interface object "clk_scan" of mode outcannot be read. Change object mode to buffer or inout.------信号类型设置不对,out当作buffer来定义4 Error:Node instance "clk_gen1" instantiates undefined entity "clk_gen"-------引用的例化元件未定义实体--entity "clk_gen"5 Warning: Found 2 node(s) in clock paths which may be acting as ripple and/or gated cl ocks -- node(s)analyzed as buffer(s) resulting in clock skewInfo: Detected ripple clock "clk_gen:clk_gen1|clk_incr" as bufferInfo: Detected ripple clock "clk_gen:clk_gen1|clk_scan" as buffer6 Warning: VHDL Process Statement warning at ledmux.vhd(15): signal or variable "datao ut" may not be assigned a new in every possible path through the Process Statement. Signal or variable " dataout" holdsits previous in every path with no new assignment, whichmay create a combinational loo p in the currentdesign.7 Warning: VHDL Process Statement warning at divider_10.vhd(17): signal "cnt" is read i nside the Process Statement but isn't in the Process Statement's sensivitity list -----缺少敏感信号8 Warning: No clock transition on "counter_bcd7:counter_counter_clk|q_sig[3]" register9 Warning: Reduced register "counter_bcd7:counter_counter_clk|q_sig[3]" with stuck clock port to stuckGND10 Warning: Circuit may not operate. Detected 1 non-operational path(s) clocked by clock "class[1]" withclock skew larger than data delay. See Compilation Report for details.11 Warning: Circuit may not operate. Detected 1 non-operational path(s) clocked by clock "sign" withclock skew larger than data delay. See Compilation Report for details.12 Error:VHDL error at counter_clk.vhd(90): actual port "class" of mode "in" cannot be associated withformal port "class" of mode "out"------两者不能连接起来13 Warning: Ignored node in vector source file. Can't find corresponding node name "clas s_sig[2]" indesign.------没有编写testbench文件,或者没有编辑输入变量的值testbench里是元件申明和映射14 Error:VHDL Binding Indication error atfreqdetect_top.vhd(19): port "class"in design entity does not have std_logic_vector type that is specified for the same generic in the associated com ponent---在相关的元件里没有当前文件所定义的类型15 Error:VHDL error at tongbu.vhd(16): can't infer register for signal "gate" because sign al does nothold its outside clock edge16 Warning: Found clock high time violation at 1000.0 ns on register"|fcounter|lpm_counter:temp_rtl_0|dffs[4]"17 Warning: Compiler packed, optimized or synthesized away node "temp[19]". Ignored ve ctor source filenode.---"temp[19]"被优化掉了18 Warning: Reduced register "gate~reg0" with stuck data_in port to stuck GND19 Warning: Design contains 2 input pin(s) that do not drive logicWarning: No output dependent on input pin "clk"Warning: No output dependent on input pin "sign"------输出信号与输入信号无关,20 Warning: Found clock high time violation at 16625.0 ns on register "|impulcomp|gate1"21 Error:VHDL error at impulcomp.vhd(19): can't implement clock enable condition speci fied using binaryoperator "or"22 Error:VHDL Association List error at period_counter.vhd(38): actual parameter assigned to formalparameter "alarm", but formal parameter is not declared-------连接表错误,形参"alarm"赋值给实参,形参没定义,可能是形参与实参的位置颠倒了,规定形参在实参之前。

quartus_错误警告分析

Quartus常见警告分析1.Found clock-sensitive change during active clock edge at time<time>on register"<name>"原因:vector source file中时钟敏感信号(如:数据,允许端,清零,同步加载等)在时钟的边缘同时变化。

而时钟敏感信号是不能在时钟边沿变化的。

其后果为导致结果不正确。

措施:编辑vector source file2.Verilog HDL assignment warning at<location>:truncatedwith size<number>to match size of target(<number>原因:在HDL设计中对目标的位数进行了设定,如:reg[4:0]a;而默认为32位,将位数裁定到合适的大小措施:如果结果正确,无须加以修正,如果不想看到这个警告,可以改变设定的位数3.All reachable assignments to data_out(10)assign'0',registerremoved by optimization原因:经过综合器优化后,输出端口已经不起作用了4.Following9pins have nothing,GND,or VCC driving datain port--changes to this connectivity may change fitting results原因:第9脚,空或接地或接上了电源措施:有时候定义了输出端口,但输出端直接赋‘0’,便会被接地,赋‘1’接电源。

如果你的设计中这些端口就是这样用的,那便可以不理会这些warning5.Found pins ing as undefined clocks and/or memory enables原因:是你作为时钟的PIN没有约束信息。

quartusII常见错误

2 Warning: Found pins ing as undefined clocks and/or memory enables

Info: Assuming node CLK is an undefined clock

-=-----可能是说设计中产生的触发器没有使能端

3 Error: VHDL Interface Declaration error in clk_gen.vhd(29): interface object

outside clock edge

28 Error: Can't elaborate top-level user hierarchy

29 Error: Can't resolve multiple constant drivers for net "cs_in" at

led_key.vhd(32) ----------有两个以上赋值语句,不能确定“cs_in”的值

cannot be associated with formal port "class" of mode "out"

------两者不能连接起来

13 Warning: Ignored node in vector source file. Can't find corresponding node

read inside the Process Statement but isn't in the Process Statement's

sensivitity list

-----缺少敏感信号

8 Warning: No clock transition on "counter_bcd7:counter_counter_clk|q_sig[3]"

Quartus常见警告和错误

Quartus常见警告和错误【转】2009-08-07 14:00Quartus常见警告和错误1 Warning: VHDL Process Statement warning at random.vhd(18): signal reset is in statement, but is not in sensitivity list----没把singal放到process()中2 Warning: Found pins ing as undefined clocks and/or memory enables Info: Assuming node CLK is an undefined clock-=-----可能是说设计中产生的触发器没有使能端3 Error: VHDL Interface Declaration error in clk_gen.vhd(29): interface object "clk_scan" of mode out cannot be read. Change object mode to buffer or inout.------信号类型设置不对,out当作buffer来定义4 Error: Node instance "clk_gen1" instantiates undefined entity "clk_gen" -------引用的例化元件未定义实体--entity "clk_gen"5 Warning: Found 2 node(s) in clock paths which may be acting as ripple and/or gated clocks -- node(s) analyzed as buffer(s) resulting in clock skewInfo: Detected ripple clock "clk_gen:clk_gen1|clk_incr" as buffer Info: Detected ripple clock "clk_gen:clk_gen1|clk_scan" as buffer6 Warning: VHDL Process Statement warning at ledmux.vhd(15): signal or variable "dataout" may not be assigned a new in every possible path through the Process Statement. Signal or variable "dataout" holds its previous in every path with no new assignment, which may create a combinational loop in the current design.7 Warning: VHDL Process Statement warning at divider_10.vhd(17): signal "cnt" is read inside the Process Statement but isn't in the Process Statement's sensivitity list-----缺少敏感信号8 Warning: No clock transition on"counter_bcd7:counter_counter_clk|q_sig[3]"register9 Warning: Reduced register "counter_bcd7:counter_counter_clk|q_sig[3]" with stuck clock port to stuck GND10 Warning: Circuit may not operate. Detected 1 non-operational path(s)clocked by clock "class[1]" with clock skew larger than data delay. See Compilation Report for details.11 Warning: Circuit may not operate. Detected 1 non-operational path(s) clocked by clock "sign" with clock skew larger than data delay. See Compilation Report for details.12 Error: VHDL error at counter_clk.vhd(90): actual port "class" of mode "in"cannot be associated with formal port "class" of mode "out"------两者不能连接起来13 Warning: Ignored node in vector source file. Can't find corresponding node name "class_sig[2]" in design.------没有编写testbench文件,或者没有编辑输入变量的值 testbench里是元件申明和映射14 Error: VHDL Binding Indication error at freqdetect_top.vhd(19): port "class"in design entity does not have std_logic_vector type that is specified for thesame generic in the associated component---在相关的元件里没有当前文件所定义的类型15 Error: VHDL error at tongbu.vhd(16): can't infer register for signal "gate"because signal does not hold its outside clock edge16 Warning: Found clock high time violation at 1000.0 ns on register "|fcounter|lpm_counter:temp_rtl_0|dffs[4]"17 Warning: Compiler packed, optimized or synthesized away node "temp[19]".Ignored vector source file node.---"temp[19]"被优化掉了18 Warning: Reduced register "gate~reg0" with stuck data_in port to stuck GND19 Warning: Design contains 2 input pin(s) that do not drive logic Warning: No output dependent on input pin "clk"Warning: No output dependent on input pin "sign"------输出信号与输入信号无关,20 Warning: Found clock high time violation at 16625.0 ns on register"|impulcomp|gate1"21 Error: VHDL error at impulcomp.vhd(19): can't implement clock enable condition specified using binary operator "or"22 Error: VHDL Association List error at period_counter.vhd(38): actual parameter assigned to formal parameter "alarm", but formal parameter is not declared-------连接表错误,形参"alarm"赋值给实参,形参没定义,可能是形参与实参的位置颠倒了,规定形参在实参之前。

quartus编译时常见错误和警告

~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~1编译常见错误和警告~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~2在QuartusII 下进行编译和仿真的时候,会出现一堆warning ,有的可以忽略,有的却需要注意。

虽然按F1可以了解关于该警告的帮助,但有时候帮助解释的仍然不清楚,大家群策群力,把自己知道和了解的一些关于警告的问题都说出来讨论一下,免得后来的人走弯路。

1.Found clock-sensitive change during active clock edge at time <time>on register "<name>"原因:vector source file 中时钟敏感信号(如:数据,允许端,清零,同步加载等)在时钟的边缘同时变化。

而时钟敏感信号是不能在时钟边沿变化的。

其后果为导致结果不正确。

措施:编辑vector source file2.Verilog HDL assignment warning at <location>:truncated value with size <number>to match size of target (<number>原因:在HDL 设计中对目标的位数进行了设定,如:reg[4:0]a ,而默认为32位,将位数裁定到合适的大小。

措施:如果结果正确,无须加以修正,如果不想看到这个警告,可以改变设定的位数。

3.All reachable assignments to data_out(10)assign '0',register removed by optimization 原因:经过综合器优化后,输出端口已经不起作用了。

4.Following 9pins have nothing,GND,or VCC driving datain port --changes to thisconnectivity may change fitting results results..原因:第9脚,空或接地或接上了电源措施:有时候定义了输出端口,但输出端直接赋‘0’,便会被接地,赋‘1’接电源。

Quartus常见错误说明

quartus的功能仿真出错怎么办Error: Run Generate Functional Simulation Netlist (quartus_map and_gate --generate_functional_sim_netlist) to generate functional simulation netlist for top level entity "and_gate" before running the Simulator (quartus_sim)一般如果出现这些错误信息,可以作如下处理功能仿真出错你要运行下processing->Generate Functional Simulation Netlist 下再功能仿真就没有问题一、Quartus 中仿真时出现no simulation input file assignment specify 解决方法翻译成中文就是仿真文件没有被指定,要仿真的话先要建一个仿真文件: file -> new -> 选择Other file 选项卡-> Vector Waveform File 然后把输入输出端口加进去,再设置输入的信号,保存,就可以仿真了。

如果你之前已经建立过了,就打开assignments->settings->simulator settings 看里面的有个文本框simulation input 里面是否为空,为空的话就要找到你所建立的Vector Waveform File 文件,是以*.VWF 结尾的,如果没找到,你又以为你建立了Vector Waveform File ,很可能粗心的你还没保存Vector Waveform File ,保存了才会在project 里面找到。

找到之后进行仿真,如果是functional simulation,要做processing>generate functional simulation netlist..不然会出现:Error: Run Generate Functional Simulation Netlist (quartus_map bmg_control --generate_functional_sim_netlist) to generate functional simulation netlist for top level entity bmg_control before running the Simulator (quartus_sim)之类的错误。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1) QuartusII对代码进行时序仿真时出现Error: Can't continue timing simulation because delay annotation information for design is missing.原因:如果只需要进行功能仿真,不全编译也是可以进行下去的,但时序仿真就必须进行全编译(即工具栏上的紫色实心三角符号那项)。

全仿真包括四个模块:综合器(Synthesis)、电路装配器(Fitter)、组装器(Assember)和时序分析器(Timing Analyzer),任务窗格中会有成功标志(对号)。

2) 在下载运行的时候,出现下面的错误:Warning: The JTAG cable you are using is not supported for Nios II systems.You may experience intermittent JTAG communicationfailures with this cable. Please use a USB Blaster revision B.在运行之前已经将.sof文件下载到开发板上面了,但是依然出现上面的问题。

解决:在配置的时候,在run之后,进行配置,选择target connection,在最后一项:NIOS II Terminal Communication Device中,要选择none(不要是Jtag_uart)如果采用USB Blaster,可以选择Jtag_uart。

之后再run就ok了!3)Error: Can't compile duplicate declarations of entity "count3" into library "work"此错误一般是原理图文件的名字和图中一个器件的名字重复所致,所以更改原理图文件的名字保存即可。

-------------------1.Found clock-sensitive change during active clock edge at time <time> on register "<name>"原因:vector source file中时钟敏感信号(如:数据,允许端,清零,同步加载等)在时钟的边缘同时变化.而时钟敏感信号是不能在时钟边沿变化的.其后果为导致结果不正确.措施:编辑vector source file2.Verilog HDL assignment warning at <location>: truncated with size <number> to match size of target (<number>原因:在HDL设计中对目标的位数进行了设定,如:reg[4:0] a;而默认为32位, 将位数裁定到合适的大小措施:如果结果正确,无须加以修正,如果不想看到这个警告,可以改变设定的位数3.All reachable assignments to data_out(10) assign '0', register removed by optimization原因:经过综合器优化后,输出端口已经不起作用了4.Following 9 pins have nothing, GND, or VCC driving datain port -- changes to this connectivity may change fitting results原因:有9个脚为空或接地或接上了电源措施:有时候定义了输出端口,但输出端直接赋‘0’,便会被接地,赋‘1’接电源. 如果你的设计中这些端口就是这样用的,那便可以不理会这些warning5.Found pins functioning as undefined clocks and/or memory enables原因:是你作为时钟的PIN没有约束信息.可以对相应的PIN做一下设定就行了. 主要是指你的某些管脚在电路当中起到了时钟管脚的作用,比如flip-flop的clk 管脚,而此管脚没有时钟约束,因此QuartusII把“clk”作为未定义的时钟.措施:如果clk不是时钟,可以加“not clock”的约束;如果是,可以在clock setting当中加入;在某些对时钟要求不很高的情况下,可以忽略此警告或在这里修改:Assignments>Timing analysis settings...>Individualclocks...>...6.Timing characteristics of device EPM570T144C5 are preliminary原因:因为MAXII 是比較新的元件在QuartusII 中的時序并不是正式版的,要等Service Pack 措施:只影响Quartus 的Waveform7.Warning: Clock latency analysis for PLL offsets is supported for the current device family, but is not enabled措施:将setting中的timing Requirements&Option-->More Timing Setting-->setting-->Enable Clock Latency中的on改成OFF8.Found clock high time violation at 14.8 ns on register"|counter|lpm_counter:count1_rtl_0|dffs[11]"原因:违反了steup/hold时间,应该是后仿真,看看波形设置是否和时钟沿符合steup/hold时间措施:在中间加个寄存器可能可以解决问题9.warning: circuit may not operate.detected 46 non-operational paths clocked by clock clk44 with clock skew larger than data delay原因:时钟抖动大于数据延时,当时钟很快,而if等类的层次过多就会出现这种问题,但这个问题多是在器件的最高频率中才会出现措施:setting-->timing Requirements&Options-->Default required fmax 改小一些,如改到50MHZ 10.Design contains <number> input pin(s) that do not drive logic原因:输入引脚没有驱动逻辑(驱动其他引脚),所有的输入引脚需要有输入逻辑措施:如果这种情况是故意的,无须理会,如果非故意,输入逻辑驱动.11.Warning:Found clock high time violation at 8.9ns on node 'TEST3.CLK'原因:FF中输入的PLS的保持时间过短措施:在FF中设置较高的时钟频率12.Warning: Found 10 node(s) in clock paths which may be acting as ripple and/or gated clocks -- node(s) analyzed as buffer(s) resulting in clock skew原因:如果你用的CPLD 只有一组全局时钟时,用全局时钟分频产生的另一个时钟在布线中当作信号处理,不能保证低的时钟歪斜(SKEW).会造成在这个时钟上工作的时序电路不可靠,甚至每次布线产生的问题都不一样.措施:如果用有两组以上全局时钟的FPGA 芯片,可以把第二个全局时钟作为另一个时钟用,可以解决这个问题.13.Critical Warning: Timing requirements were not met. See Report window for details.原因:时序要求未满足,措施:双击Compilation Report-->Time Analyzer-->红色部分(如clock setup:'clk'等)-->左键单击list path,查看fmax的SLACK REPORT再根据提示解决,有可能是程序的算法问题14.Can't achieve minimum setup and hold requirement <text> along <number> path(s). See Report window for details.原因:时序分析发现一定数量的路径违背了最小的建立和保持时间,与时钟歪斜有关,一般是由于多时钟引起的措施:利用Compilation Report-->Time Analyzer-->红色部分(如clock hold:'clk'等),在slack中观察是hold time为负值还是setup time 为负值, 然后在:Assignment-->Assignment Editor-->To中增加时钟名(fromnode finder),Assignment Name中增加和多时钟有关的Multicycle 和Multicycle Hold选项,如hold time为负,可使Multicycle hold的值>multicycle,如设为2和1.15: Can't analyze file -- file E://quartusii/*/*.v is missing原因:试图编译一个不存在的文件,该文件可能被改名或者删除了措施:不管他,没什么影响16.Warning: Can't find signal in vector source file for input pin |whole|clk10m原因:因为你的波形仿真文件( vector source file )中并没有把所有的输入信号(input pin)加进去,对于每一个输入都需要有激励源的17.Error: Can't name logic scfifo0 of instance "inst" -- has same name as current design file原因:模块的名字和project的名字重名了措施:把两个名字之一改一下,一般改模块的名字18.Warning: Using design file lpm_fifo0.v, which is not specified as a design file for the current project, but contains definitions for 1 design units and 1 entities in project Info: Found entity 1: lpm_fifo0原因:模块不是在本项目生成的,而是直接copy了别的项目的原理图和源程序而生成的,而不是用QUARTUS将文件添加进本项目措施:无须理会,不影响使用19.Timing characteristics of device <name> are preliminary原因:目前版本的QuartusII只对该器件提供初步的时序特征分析措施:如果坚持用目前的器件,无须理会该警告.关于进一步的时序特征分析会在后续版本的Quartus得到完善.20.Timing Analysis does not support the analysis of latches as synchronous elements for the currently selected device family原因:用analyze_latches_as_synchronous_elements setting可以让Quaruts II来分析同步锁存,但目前的器件不支持这个特性措施:无须理会.时序分析可能将锁存器分析成回路.但并不一定分析正确.其后果可能会导致显示提醒用户:改变设计来消除锁存器。