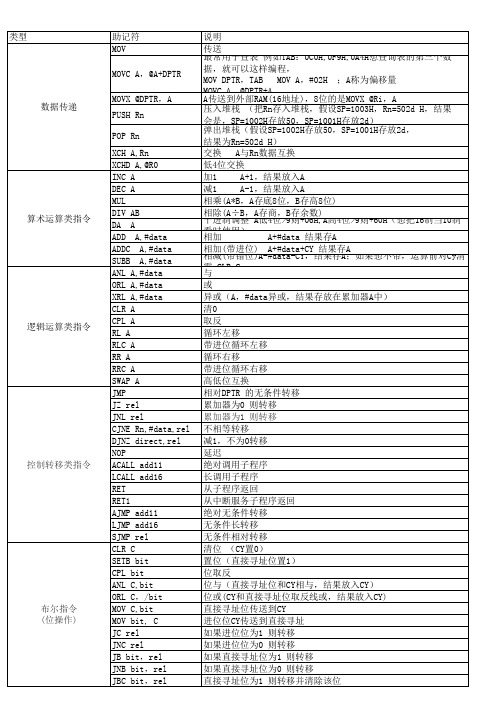

各类命令助记符

说明指令助记符

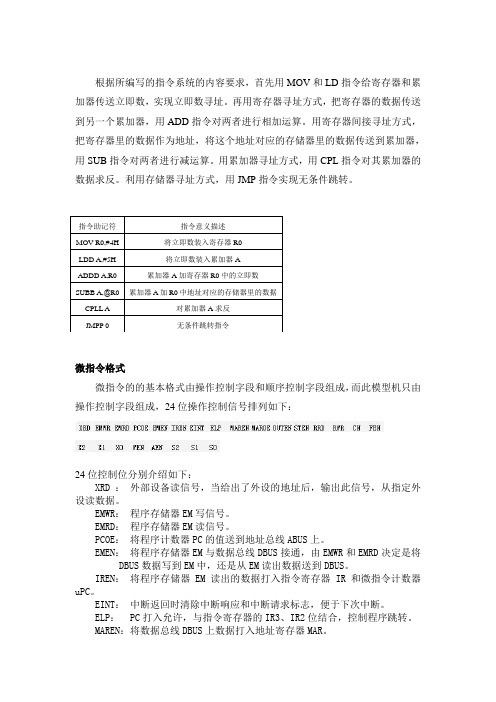

根据所编写的指令系统的内容要求,首先用MOV和LD指令给寄存器和累加器传送立即数,实现立即数寻址。

再用寄存器寻址方式,把寄存器的数据传送到另一个累加器,用ADD指令对两者进行相加运算。

用寄存器间接寻址方式,把寄存器里的数据作为地址,将这个地址对应的存储器里的数据传送到累加器,用SUB指令对两者进行减运算。

用累加器寻址方式,用CPL指令对其累加器的数据求反。

利用存储器寻址方式,用JMP指令实现无条件跳转。

微指令格式微指令的的基本格式由操作控制字段和顺序控制字段组成,而此模型机只由操作控制字段组成,24位操作控制信号排列如下:24位控制位分别介绍如下:XRD :外部设备读信号,当给出了外设的地址后,输出此信号,从指定外设读数据。

EMWR:程序存储器EM写信号。

EMRD:程序存储器EM读信号。

PCOE:将程序计数器PC的值送到地址总线ABUS上。

EMEN:将程序存储器EM与数据总线DBUS接通,由EMWR和EMRD决定是将DBUS数据写到EM中,还是从EM读出数据送到DBUS。

IREN:将程序存储器EM读出的数据打入指令寄存器IR和微指令计数器uPC。

EINT:中断返回时清除中断响应和中断请求标志,便于下次中断。

ELP: PC打入允许,与指令寄存器的IR3、IR2位结合,控制程序跳转。

MAREN:将数据总线DBUS上数据打入地址寄存器MAR。

MAROE:将地址寄存器MAR的值送到地址总线ABUS上。

OUTEN:将数据总线DBUS上数据送到输出端口寄存器OUT里。

STEN:将数据总线DBUS上数据存入堆栈寄存器ST中。

RRD:读寄存器组R0-R3,寄存器R?的选择由指令的最低两位决定。

RWR:写寄存器组R0-R3,寄存器R?的选择由指令的最低两位决定。

CN:决定运算器是否带进位移位,CN=1带进位,CN=0不带进位。

FEN:将标志位存入ALU内部的标志寄存器。

X2: X2、X1、X0三位组合来译码选择将数据送到DBUS上的寄存器。

助记符

3

2

CJNE

Rn,#data,rel

比较寄存器和立即数,不相等转移

2

2

CJNE

@Ri,#data,rel

比较立即数和间接RAM,不相等转移

3

2

DJNZ

Rn,rel

寄存器减1,不为0 则转移

3

2

DJNZ

direct,rel

直接地址减1,不为0 则转移

3

2

NOP

空操作,用于短暂延时

A,direct

直接地址与累加器求和

2

1

ADD

A,@Ri

间接RAM 与累加器求和

1

1

ADD

A,#data

立即数与累加器求和

2

1

ADDC

A,Rn

寄存器与累加器求和(带进位)

1

1

ADDC

A,direct

直接地址与累加器求和(带进位)

2

1

ADDC

A,@Ri

间接RAM 与累加器求和(带进位)

1

1

ADDC

A,#data

间接RAM“异或”到累加器

1

1

XRL

A,#data

立即数“异或”到累加器

2

1

XRL

direct,A

累加器“异或”到直接地址

2

1

XRL

direct, #data

立即数“异或”到直接地址

3

1

CLR

A

累加器清零

1

2

CPL

A

累加器求反

1

1

RL

A

累加器循环左移

1

汇编指令符号大全

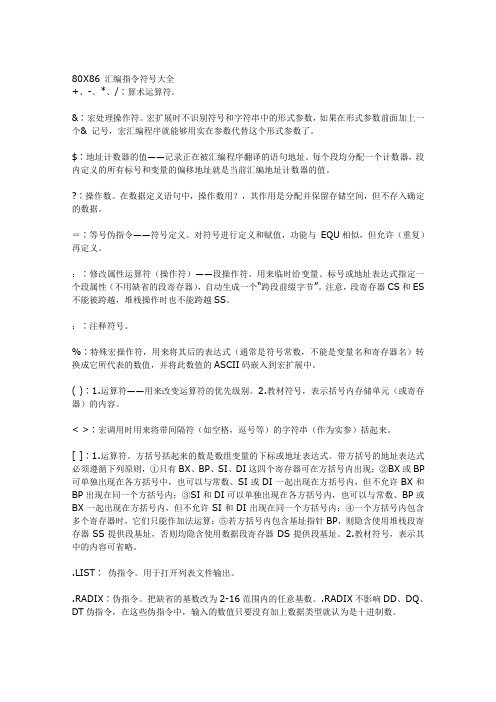

80X86 汇编指令符号大全+、-、*、/∶算术运算符。

&∶宏处理操作符。

宏扩展时不识别符号和字符串中的形式参数,如果在形式参数前面加上一个& 记号,宏汇编程序就能够用实在参数代替这个形式参数了。

$∶地址计数器的值——记录正在被汇编程序翻译的语句地址。

每个段均分配一个计数器,段内定义的所有标号和变量的偏移地址就是当前汇编地址计数器的值。

?∶操作数。

在数据定义语句中,操作数用?,其作用是分配并保留存储空间,但不存入确定的数据。

=∶等号伪指令——符号定义。

对符号进行定义和赋值,功能与EQU相似,但允许(重复)再定义。

:∶修改属性运算符(操作符)——段操作符。

用来临时给变量、标号或地址表达式指定一个段属性(不用缺省的段寄存器),自动生成一个“跨段前缀字节”。

注意,段寄存器CS和ES 不能被跨越,堆栈操作时也不能跨越SS。

;∶注释符号。

%∶特殊宏操作符,用来将其后的表达式(通常是符号常数,不能是变量名和寄存器名)转换成它所代表的数值,并将此数值的ASCII码嵌入到宏扩展中。

( )∶1.运算符——用来改变运算符的优先级别。

2.教材符号,表示括号内存储单元(或寄存器)的内容。

< >∶宏调用时用来将带间隔符(如空格,逗号等)的字符串(作为实参)括起来。

[ ]∶1.运算符。

方括号括起来的数是数组变量的下标或地址表达式。

带方括号的地址表达式必须遵循下列原则,①只有BX、BP、SI、DI这四个寄存器可在方括号内出现;②BX或BP 可单独出现在各方括号中,也可以与常数、SI或DI一起出现在方括号内,但不允许BX和BP出现在同一个方括号内;③SI和DI可以单独出现在各方括号内,也可以与常数、BP或BX一起出现在方括号内,但不允许SI和DI出现在同一个方括号内;④一个方括号内包含多个寄存器时,它们只能作加法运算;⑤若方括号内包含基址指针BP,则隐含使用堆栈段寄存器SS提供段基址,否则均隐含使用数据段寄存器DS提供段基址。

助记符

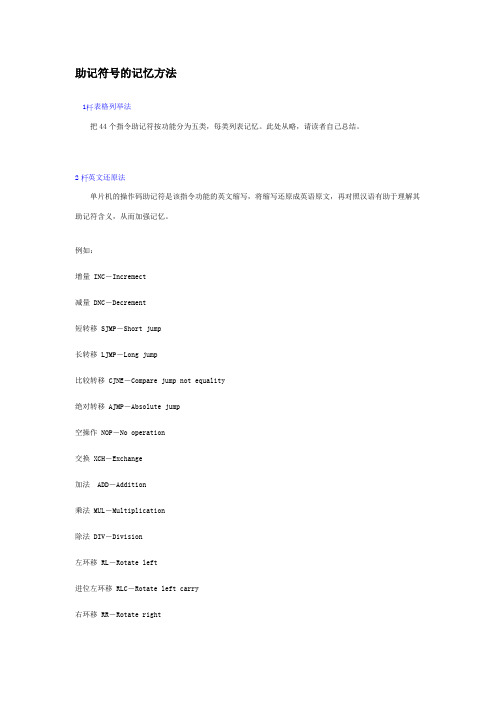

助记符号的记忆方法1表格列举法把44个指令助记符按功能分为五类,每类列表记忆。

此处从略,请读者自己总结。

2英文还原法单片机的操作码助记符是该指令功能的英文缩写,将缩写还原成英语原文,再对照汉语有助于理解其助记符含义,从而加强记忆。

例如:增量 INC-Incremect减量 DNC-Decrement短转移 SJMP-Short jump长转移 LJMP-Long jump比较转移 CJNE-Compare jump not equality绝对转移 AJMP-Absolute jump空操作 NOP-No operation交换 XCH-Exchange加法ADD-Addition乘法 MUL-Multiplication除法 DIV-Division左环移 RL-Rotate left进位左环移 RLC-Rotate left carry右环移 RR-Rotate right进位右环移RRC-Rotate right carryMCS-51系列单片机指令解读:18条以A字母开头的单片机的指令10条以C字母开头的单片机的指令8条以D字母开头的单片机的指令5条以I字母开头的单片机的指令8条以J字母开头的单片机的指令2条以L字母开头的单片机的指令24条以M字母开头的单片机的指令1条以N字母开头的单片机的指令8条以O字母开头的单片机的指令2条以字母P开头的单片机的指令6条以字母R开头的单片机的指令8条以字母S开头的单片机的指令18个以A字母开头的MCS-51系列单片机的指令1、ACALL addr11指令名称:绝对调用指令指令代码:指令功能:构造目的地址,进行子程序调用。

其方法是以指令提供的11位地址(al0~a0),取代PC的低11位,PC的高5位不变。

操作内容:PC←(PC)+2SP←(SP)+1(SP)←(PC)7~0SP←(SP)+1(SP)←(PC)15~8PC10~0←addrl0~0字节数: 2机器周期:2使用说明:由于指令只给出子程序入口地址的低11位,因此调用范围是2KB。

汇编助记符

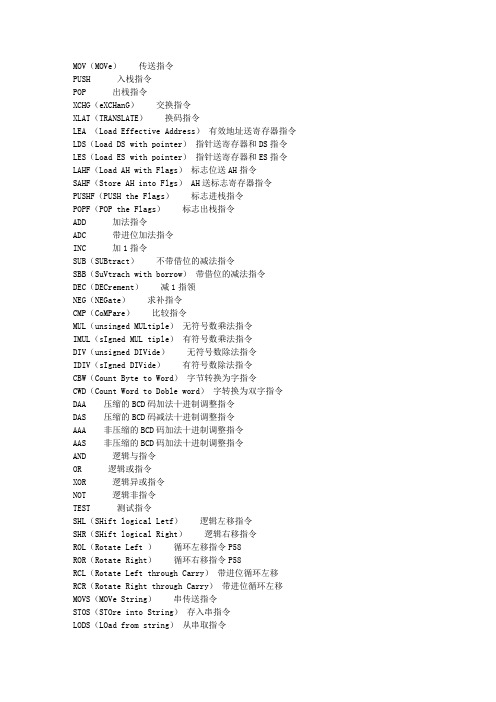

MOV(MOVe)传送指令PUSH 入栈指令POP 出栈指令XCHG(eXCHanG)交换指令XLAT(TRANSLATE)换码指令LEA (Load Effective Address)有效地址送寄存器指令LDS(Load DS with pointer)指针送寄存器和DS指令LES(Load ES with pointer)指针送寄存器和ES指令LAHF(Load AH with Flags)标志位送AH指令SAHF(Store AH into Flgs) AH送标志寄存器指令PUSHF(PUSH the Flags)标志进栈指令POPF(POP the Flags)标志出栈指令ADD 加法指令ADC 带进位加法指令INC 加1指令SUB(SUBtract)不带借位的减法指令SBB(SuVtrach with borrow)带借位的减法指令DEC(DECrement)减1指领NEG(NEGate)求补指令CMP(CoMPare)比较指令MUL(unsinged MULtiple)无符号数乘法指令IMUL(sIgned MUL tiple)有符号数乘法指令DIV(unsigned DIVide)无符号数除法指令IDIV(sIgned DIVide)有符号数除法指令CBW(Count Byte to Word)字节转换为字指令CWD(Count Word to Doble word)字转换为双字指令DAA 压缩的BCD码加法十进制调整指令DAS 压缩的BCD码减法十进制调整指令AAA 非压缩的BCD码加法十进制调整指令AAS 非压缩的BCD码加法十进制调整指令AND 逻辑与指令OR 逻辑或指令XOR 逻辑异或指令NOT 逻辑非指令TEST 测试指令SHL(SHift logical Letf)逻辑左移指令SHR(SHift logical Right)逻辑右移指令ROL(Rotate Left )循环左移指令P58ROR(Rotate Right)循环右移指令P58RCL(Rotate Left through Carry)带进位循环左移RCR(Rotate Right through Carry)带进位循环左移MOVS(MOVe String)串传送指令STOS(STOre into String)存入串指令LODS(LOad from string)从串取指令REP(REPeat)重复操作前CLD(CLear Direction flag)清除方向标志指令STD(SeT Direction flag)设置方向标志指令CMPS(CoMPare String)串比较指令SCAS(SCAn String)串扫描指令REPE/REPZ(REPeat while Equal/Zero)相等/为零时重复操作前缀答案补充REPNE/REPNZ(REPeat while Not Equal/Zero)不相等/不为零进重复前缀IN(INput)输入指令OUT(OUTput)输出指令JMP(JuMP)无条件转移指令JZ,JNZ,JS,JNS,JO,JNO,JP,JNP,JB,JNB,JBE,JNBE,JL,JNL,JLE,JNLE,JCXZ 条件转移指令LOOP 循环指令P70LOOPZ/LOOPE 为零/相等时循环指令LOOPNZ/LOOPNE 不为零/不相等时循环指令CALL 子程序调用指令RET(RETun)子程序返回指令CLC(CLear Carry)进位位置0指令CMC(CoMplement Carry)进位位求反指令SRC(SeT Carry)进位位置1指令NOP(No OPeretion)无操作指令答案补充HLT(HaLT)停机指令OFFSET 返回偏移地址SEG 返回段地址EQU(=) 等值语句PURGE 解除语句DUP 操作数字段用复制操作符SEGMENT,ENDS 段定义指令ASSUME 段地址分配指令ORG 起始偏移地址设置指令$ 地址计数器的当前值PROC,ENDP 过程定义语句NAME,TITLE,END 程序开始结束语句MACRO,ENDM 宏定义指令JZ OPR //结果为零转移JNZ OPR //结果不为零转移JS OPR //结果为负转移JNS OPR //结果为正转移JO OPR //溢出转移JNO OPR //不溢出转移JP OPR //结果为偶转移JNP OPR //结果为奇转移JC OPR //有进位转移JNC OPR //无进位转移NV: 未溢出0 OV: 溢出1 ------------------------------OF UP: 方向为上0(di,si += 1) DN:方向为下1(di,si -= 1)---- DI: 关中断0 EI: 开中断1--------PL: 正0 NG: 负1-------------SFNZ: 非0 0 ZR: 0 1----------------ZFNA: 无辅助进位0 AC: 辅助进位1-------AFPO: 奇数0 PE: 偶数1 ------------PFNC: 无进位0 CY: 进位1 ----------Cf。

指令系统中各种助记符的英文全名

我现将指令系统中各种助记符的英文全名写出来,各种助记符的记忆就会变得很简单o(∩_∩)o...在这之前,先说一下寄存器:数据寄存器分为:AH&AL=AX(accumulator):累加寄存器,常用于运算;在乘除等指令中指定用来存放操作数,另外,所有的I/O指令都使用这一寄存器与外界设备传送数据.BH&BL=BX(base):基址寄存器,常用于地址索引;CH&CL=CX(count):计数寄存器,常用于计数;常用于保存计算值,如在移位指令,循环(loop)和串处理指令中用作隐含的计数器.DH&DL=DX(data):数据寄存器,常用于数据传递。

他们的特点是,这4个16位的寄存器可以分为高8位: AH, BH, CH, DH.以及低八位:AL,BL,CL,DL。

这2组8位寄存器可以分别寻址,并单独使用。

另一组是指针寄存器和变址寄存器,包括:SP(Stack Pointer):堆栈指针,与SS配合使用,可指向目前的堆栈位置;BP(Base Pointer):基址指针寄存器,可用作SS的一个相对基址位置;SI(Source Index):源变址寄存器可用来存放相对于DS段之源变址指针;DI(Destination Index):目的变址寄存器,可用来存放相对于 ES 段之目的变址指针。

指令指针IP(Instruction Pointer)标志寄存器FR(Flag Register)OF(overflow flag)DF(direction flag)CF(carrier flag)PF(parity flag)AF(auxiliary flag)ZF(zero flag)SF(sign flag)IF(interrupt flag)TF(trap flag)段寄存器(Segment Register)为了运用所有的内存空间,8086设定了四个段寄存器,专门用来保存段地址:CS(Code Segment):代码段寄存器;DS(Data Segment):数据段寄存器;SS(Stack Segment):堆栈段寄存器;ES(Extra Segment):附加段寄存器。

指令助记符

汇编语言操作码助记符共44个,寻址方式七种:立即寻址、直接寻址、寄存器寻址、寄存器间接寻址、变址寻址、相对寻址、位寻址。

可组合111条指令。

数据传送类助记符8个MOV : move 对内部RAM和SFR之间的数据传送MOVC: move code 读取ROM的数据传送MOVX: move external RAM 对外部RAM的传送XCH: exchange 字节交换XCHD: exchange low-order digit 低半字节交换SWAP: A中低4位与高4位互换PUSH: push into stack入栈POP: pop from stack 出栈算术运算操作码助记符(8个)ADD : addition 加法ADDC: add with carry 带进位加法SUBB: subtract with borrow 带借位减法DA: decimal adjust 十进制调整INC: increment 加1DEC: decrement 减1MUL: multiplication ,multiply 乘法DIV : division ,divide 除法逻辑运算和移位操作码助记符(10个)ANL : and logic 与逻辑ORL : or logic 或逻辑XRL : exclusive-or logic 异或逻辑CLR : clear 清0CPL : complement 取反RL: rotate left 左移RLC : rotate left throught the carry flag带进位左移RR: rotate right 右移RRC : rotate right throught the carry flag 带进位右移NOP: no operation 空操作控制转移类操作码助记符(12个)(一)无条件转移(4个)LJMP : LONG JUMP 长跳转AJMP : Absolute jump 绝对转移SJMP : short jump 短转移JMP :jump 转移(二)调用(2个)LCALL : long subroutine call 长调用SCALL : short subroutine call 短调用(三)返回(2个)RET : return from subroutine 子程序返回RETI : return from interruption 中断子程序返回(四)条件转移)(4个)(1)判零转移JZ: jump if zero 结果为0转移JNZ : jump if not zero 结果不为0转移(2 )比较转移CJNE: compare jump if not equal 比较不相等转移(3 )循环转移DJNZ: decrement jump if not zero 结果不为零转移位操作码助记符(11个实质为6 个)(一)数据传送MOV(二)位状态控制(1个)CLRSETB : SET BITCPL(三)位逻辑运算ANLORL(四)布尔条件转移(5个)JC : jump if the carry flag is set 有进位则转移JNC:jump if not carry 无进位则转移JB:jump if the bit is set 位为1则转移JNB:jump if the bit is not set 位为0则转移JBC:jump if the bit is set and clear the bit 位为1则转移,并清除该位。

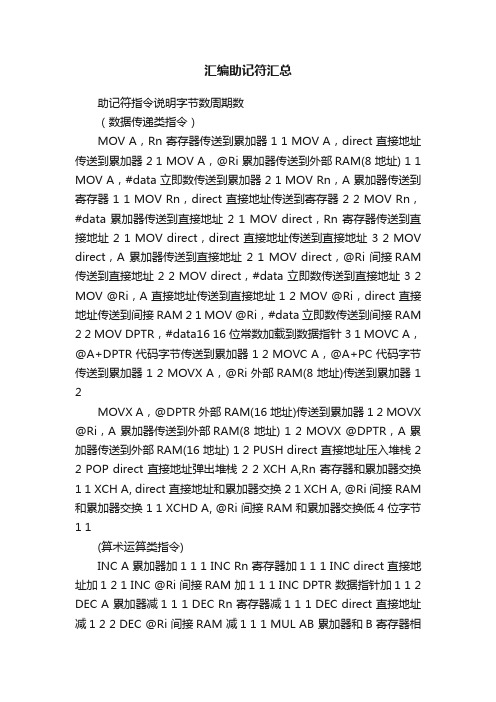

汇编助记符汇总

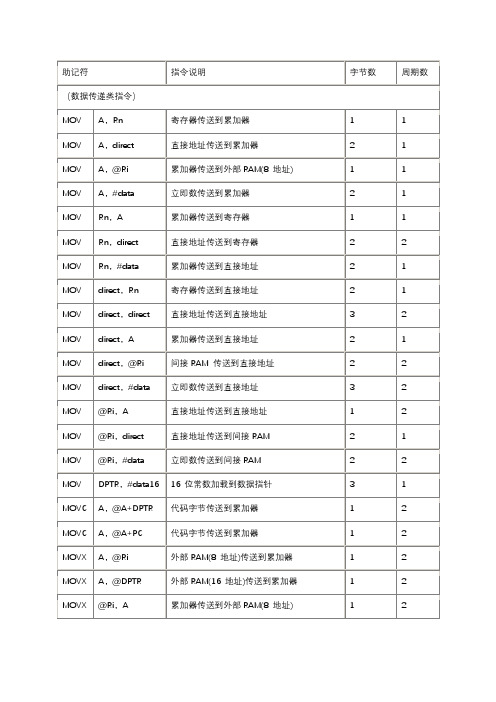

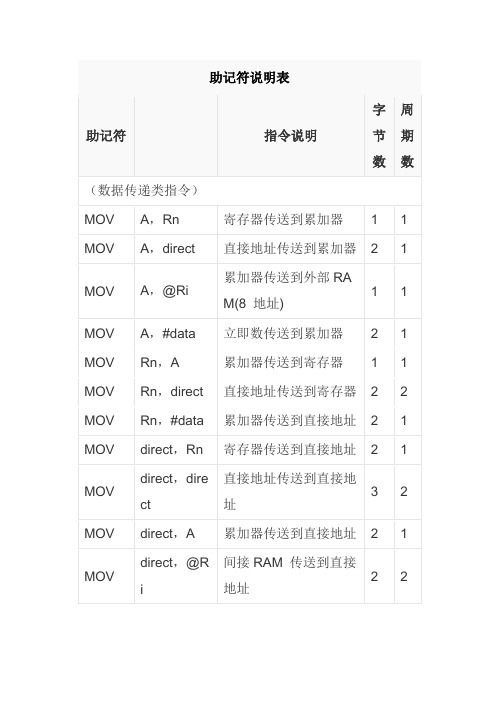

助记符指令说明字节数周期数(数据传递类指令)MOV A,Rn 寄存器传送到累加器 1 1 MOV A,direct 直接地址传送到累加器 2 1 MOV A,@Ri 累加器传送到外部RAM(8 地址) 1 1 MOV A,#data 立即数传送到累加器 2 1 MOV Rn,A 累加器传送到寄存器 1 1 MOV Rn,direct 直接地址传送到寄存器 2 2 MOV Rn,#data 累加器传送到直接地址 2 1 MOV direct,Rn 寄存器传送到直接地址 2 1 MOV direct,direct 直接地址传送到直接地址 3 2 MOV direct,A 累加器传送到直接地址 2 1 MOV direct,@Ri 间接RAM 传送到直接地址 2 2 MOV direct,#data 立即数传送到直接地址 3 2 MOV @Ri,A 直接地址传送到直接地址 1 2 MOV @Ri,direct 直接地址传送到间接RAM 2 1 MOV @Ri,#data 立即数传送到间接RAM 2 2 MOV DPTR,#data16 16 位常数加载到数据指针 3 1 MOVC A,@A+DPTR 代码字节传送到累加器 1 2 MOVC A,@A+PC 代码字节传送到累加器 1 2 MOVX A,@Ri 外部RAM(8 地址)传送到累加器 1 2MOVX A,@DPTR 外部RAM(16 地址)传送到累加器 1 2 MOVX @Ri,A 累加器传送到外部RAM(8 地址) 1 2 MOVX @DPTR,A 累加器传送到外部RAM(16 地址) 1 2 PUSH direct 直接地址压入堆栈 2 2 POP direct 直接地址弹出堆栈 2 2 XCH A,Rn 寄存器和累加器交换 1 1 XCH A, direct 直接地址和累加器交换 2 1 XCH A, @Ri 间接RAM 和累加器交换 1 1 XCHD A, @Ri 间接RAM 和累加器交换低4 位字节 1 1(算术运算类指令)INC A 累加器加1 1 1 INC Rn 寄存器加1 1 1 INC direct 直接地址加1 2 1 INC @Ri 间接RAM 加1 1 1 INC DPTR 数据指针加1 1 2 DEC A 累加器减1 1 1 DEC Rn 寄存器减1 1 1 DEC direct 直接地址减1 2 2 DEC @Ri 间接RAM 减1 1 1 MUL AB 累加器和B 寄存器相乘 1 4 DIV AB 累加器除以B 寄存器 1 4DA A 累加器十进制调整 1 1 ADD A,Rn 寄存器与累加器求和 1 1 ADD A,direct 直接地址与累加器求和 2 1 ADD A,@Ri 间接RAM 与累加器求和 1 1 ADD A,#data 立即数与累加器求和 2 1 ADDC A,Rn 寄存器与累加器求和(带进位) 1 1 ADDC A,direct 直接地址与累加器求和(带进位) 2 1 ADDC A,@Ri 间接RAM 与累加器求和(带进位) 1 1 ADDC A,#data 立即数与累加器求和(带进位) 2 1 SUBB A,Rn 累加器减去寄存器(带借位) 1 1 SUBB A,direct 累加器减去直接地址(带借位) 2 1 SUBB A,@Ri 累加器减去间接RAM(带借位) 1 1 SUBB A,#data 累加器减去立即数(带借位) 2 1(逻辑运算类指令)ANL A,Rn 寄存器“与”到累加器 1 1 ANL A,direct 直接地址“与”到累加器 2 1 ANL A,@Ri 间接RAM“与”到累加器 1 1 ANL A,#data 立即数“与”到累加器 2 1 ANL direct,A 累加器“与”到直接地址 2 1 ANL direct, #data 立即数“与”到直接地址 3 2 ORL A,Rn 寄存器“或”到累加器 1 2ORL A,direct 直接地址“或”到累加器 2 1 ORL A,@Ri 间接RAM“或”到累加器 1 1 ORL A,#data 立即数“或”到累加器 2 1 ORL direct,A 累加器“或”到直接地址 2 1 ORL direct, #data 立即数“或”到直接地址 3 1 XRL A,Rn 寄存器“异或”到累加器 1 2 XRL A,direct 直接地址“异或”到累加器 2 1 XRL A,@Ri 间接RAM“异或”到累加器 1 1 XRL A,#data 立即数“异或”到累加器 2 1 XRL direct,A 累加器“异或”到直接地址 2 1 XRL direct, #data 立即数“异或”到直接地址 3 1 CLR A 累加器清零 1 2 CPL A 累加器求反 1 1 RL A 累加器循环左移 1 1 RLC A 带进位累加器循环左移 1 1 RR A 累加器循环右移 1 1 RRC A 带进位累加器循环右移 1 1 SWAP A 累加器高、低4 位交换 1 1(控制转移类指令)JMP @A+DPTR 相对DPTR 的无条件间接转移 1 2 JZ rel 累加器为0 则转移 2 2JNZ rel 累加器为1 则转移 2 2 CJNE A,direct,rel 比较直接地址和累加器,不相等转移 3 2 CJNE A,#data,rel 比较立即数和累加器,不相等转移 3 2 CJNE Rn,#data,rel 比较寄存器和立即数,不相等转移 2 2 CJNE @Ri,#data,rel 比较立即数和间接RAM,不相等转移 3 2 DJNZ Rn,rel 寄存器减1,不为0 则转移 3 2 DJNZ direct,rel 直接地址减1,不为0 则转移 3 2 NOP 空操作,用于短暂延时 1 1 ACALL add11 绝对调用子程序 2 2 LCALL add16 长调用子程序 3 2 RET 从子程序返回 1 2 RETI 从中断服务子程序返回 1 2 AJMP add11 无条件绝对转移 2 2 LJMP add16 无条件长转移 3 2 SJMP rel 无条件相对转移 2 2(布尔指令)CLR C清进位位11 CLR bit清直接寻址位21 SETB C置位进位位11 SETB bit置位直接寻址位21 CPL C取反进位位11CPL bit取反直接寻址位21 ANL C,bit直接寻址位“与”到进位位22 ANL C,/bit直接寻址位的反码“与”到进位位22 ORL C,bit直接寻址位“或”到进位位22 ORL C,/bit直接寻址位的反码“或”到进位位22 MOV C,bit直接寻址位传送到进位位21 MOV bit, C进位位位传送到直接寻址22 JC rel如果进位位为1 则转移22 JNC rel如果进位位为0 则转移22 JB bit,rel如果直接寻址位为1 则转移32 JNB bit,rel如果直接寻址位为0 则转移32 JBC bit,rel直接寻址位为1 则转移并清除该位22(伪指令)ORG 指明程序的开始位置DB 定义数据表DW 定义16 位的地址表EQU 给一个表达式或一个字符串起名DATA 给一个8 位的内部RAM 起名XDATA 给一个8 位的外部RAM 起名BIT 给一个可位寻址的位单元起名END 指出源程序到此为止(指令中的符号标识)Rn 工作寄存器R0-R7Ri 工作寄存器R0 和R1@Ri 间接寻址的8 位RAM 单元地址(00H-FFH)#data8 8 位常数#data16 16 位常数addr16 16 位目标地址,能转移或调用到64KROM 的任何地方addr11 11 位目标地址,在下条指令的2K 范围内转移或调用Rel 8 位偏移量,用于SJMP 和所有条件转移指令,范围-128~+127 Bit 片内RAM 中的可寻址位和SFR 的可寻址位Direct 直接地址,范围片内RAM 单元(00H-7FH)和80H-FFH$ 指本条指令的起始位置。

助记符说明表

助记符

指令说明

字节数

周期数

(数据传递类指令)

MOV

A,Rn

寄存器传送到irect

直接地址传送到累加器

2

1

MOV

A,@Ri

累加器传送到外部RAM(8地址)

1

1

MOV

A,#data

立即数传送到累加器

2

1

MOV

Rn,A

累加器传送到寄存器

1

1

MOV

Rn,direct

直接地址传送到寄存器

1

2

MOVX

A,@Ri

外部RAM(8地址)传送到累加器

1

2

MOVX

A,@DPTR

外部RAM(16地址)传送到累加器

1

2

MOVX

@Ri,A

累加器传送到外部RAM(8地址)

1

2

MOVX

@DPTR,A

累加器传送到外部RAM(16地址)

1

2

PUSH

direct

直接地址压入堆栈

2

2

POP

direct

直接地址弹出堆栈

2

2

MOV

Rn,#data

累加器传送到直接地址

2

1

MOV

direct,Rn

寄存器传送到直接地址

2

1

MOV

direct,direct

直接地址传送到直接地址

3

2

MOV

direct,A

累加器传送到直接地址

2

1

MOV

direct,@Ri

间接RAM传送到直接地址

2

2

MOV

direct,#data

命令指示符大全

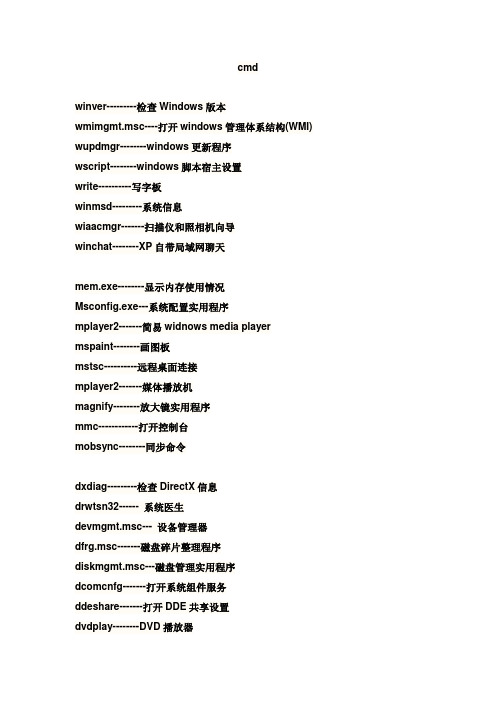

cmdwinver---------检查Windows版本wmimgmt.msc----打开windows管理体系结构(WMI) wupdmgr--------windows更新程序wscript--------windows脚本宿主设置write----------写字板winmsd---------系统信息wiaacmgr-------扫描仪和照相机向导winchat--------XP自带局域网聊天mem.exe--------显示内存使用情况Msconfig.exe---系统配置实用程序mplayer2-------简易widnows media player mspaint--------画图板mstsc----------远程桌面连接mplayer2-------媒体播放机magnify--------放大镜实用程序mmc------------打开控制台mobsync--------同步命令dxdiag---------检查DirectX信息drwtsn32------ 系统医生devmgmt.msc--- 设备管理器dfrg.msc-------磁盘碎片整理程序diskmgmt.msc---磁盘管理实用程序dcomcnfg-------打开系统组件服务ddeshare-------打开DDE共享设置dvdplay--------DVD播放器net stop messenger-----停止信使服务net start messenger----开始信使服务notepad--------打开记事本nslookup-------网络管理的工具向导ntbackup-------系统备份和还原narrator-------屏幕“讲述人”ntmsmgr.msc----移动存储管理器ntmsoprq.msc---移动存储管理员操作请求netstat -an----(TC)命令检查接口syncapp--------创建一个公文包sysedit--------系统配置编辑器sigverif-------文件签名验证程序sndrec32-------录音机shrpubw--------创建共享文件夹secpol.msc-----本地安全策略syskey---------系统加密,一旦加密就不能解开,保护windows xp系统的双重密码services.msc---本地服务设置Sndvol32-------音量控制程序sfc.exe--------系统文件检查器sfc /scannow---windows文件保护tsshutdn-------60秒倒计时关机命令tourstart------xp简介(安装完成后出现的漫游xp程序)taskmgr--------任务管理器eventvwr-------事件查看器eudcedit-------造字程序explorer-------打开资源管理器packager-------对象包装程序perfmon.msc----计算机性能监测程序progman--------程序管理器regedit.exe----注册表rsop.msc-------组策略结果集regedt32-------注册表编辑器rononce -p ----15秒关机regsvr32 /u *.dll----停止dll文件运行regsvr32 /u zipfldr.dll------取消ZIP支持cmd.exe--------CMD命令提示符chkdsk.exe-----Chkdsk磁盘检查certmgr.msc----证书管理实用程序calc-----------启动计算器charmap--------启动字符映射表cliconfg-------SQL SERVER 客户端网络实用程序Clipbrd--------剪贴板查看器conf-----------启动netmeetingcompmgmt.msc---计算机管理cleanmgr-------垃圾整理ciadv.msc------索引服务程序osk------------打开屏幕键盘odbcad32-------ODBC数据源管理器oobe/msoobe /a----检查XP是否激活lusrmgr.msc----本机用户和组logoff---------注销命令iexpress-------木马捆绑工具,系统自带Nslookup-------IP地址侦测器fsmgmt.msc-----共享文件夹管理器utilman--------辅助工具管理器gpedit.msc-----组策略ipconfig /all。

51汇编指令集助记符符号标识伪指令大全

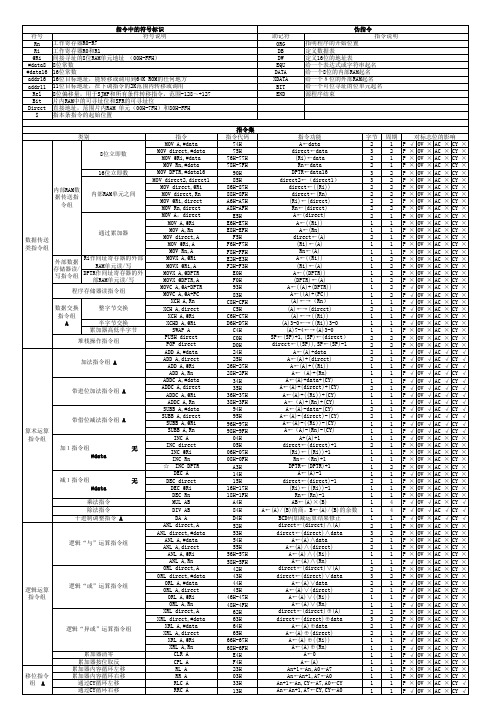

对标志位的影响 P √ OV × AC × CY × P × OV × AC × CY × P × OV × AC × CY × P × OV × AC × CY × P × OV × AC × CY × P × OV × AC × CY × P × OV × AC × CY × P × OV × AC × CY × P × OV × AC × CY × P × OV × AC × CY × P × OV × AC × CY × P × OV × AC × CY × P × OV × AC × CY × P × OV × AC × CY × P × OV × AC × CY × P × OV × AC × CY × P × OV × AC × CY × P × OV × AC × CY × P × OV × AC × CY × P × OV × AC × CY × P √ OV × AC × CY × P √ OV × AC × CY × P √ OV × AC × CY × P √ OV × AC × CY × P √ OV × AC × CY × P √ OV × AC × CY × P × OV × AC × CY × P × OV × AC × CY × P × OV × AC × CY × P √ OV √ AC √ CY √ P √ OV √ AC √ CY √ P √ OV √ AC √ CY √ P √ OV √ AC √ CY √ P √ OV √ AC √ CY √ P √ OV √ AC √ CY √ P √ OV √ AC √ CY √ P √ OV √ AC √ CY √ P √ OV √ AC √ CY √ P √ OV √ AC √ CY √ P √ OV √ AC √ CY √ P √ OV √ AC √ CY √ P √ OV × AC × CY × P × OV × AC × CY × P × OV × AC × CY × P × OV × AC × CY × P × OV × AC × CY × P √ OV × AC × CY × P × OV × AC × CY × P × OV × AC × CY × P × OV × AC × CY × P √ OV √ AC × CY √

汇编语言助记符

汇编语言助记符汇编语言是一种低级语言,是计算机硬件能够直接执行的语言。

在编写汇编代码时,为了方便记忆和使用,人们使用了一些助记符(mnemonic)来代表机器指令和操作数的操作符。

本文将介绍一些常见的汇编语言助记符以及它们的用法和含义。

1. MOV(Move)MOV是汇编语言中最常见的助记符之一,用于将数据从一个位置移动到另一个位置。

例如,MOV AX, 42表示将值42移动到寄存器AX中。

MOV指令通常用于数据传输和寄存器之间的操作。

2. ADD(Addition)ADD助记符用于执行加法操作。

例如,ADD AX, BX表示将寄存器BX的值加到寄存器AX中。

ADD指令还可以用于将常数加到寄存器中或将内存中的值与寄存器中的值相加。

3. SUB(Subtraction)SUB助记符用于执行减法操作。

例如,SUB AX, BX表示将寄存器BX的值从寄存器AX中减去。

与ADD指令类似,SUB指令也可以用于将常数从寄存器中减去或从内存中的值中减去寄存器中的值。

4. JMP(Jump)JMP助记符用于实现无条件跳转,即程序将跳转到指定地址处继续执行。

例如,JMP Label表示跳转到标签(Label)所指示的位置。

使用JMP指令可以实现程序的循环、条件分支等控制结构。

5. CMP(Compare)CMP助记符用于进行比较操作,通常与条件跳转指令(如JMP、JZ、JG等)配合使用。

例如,CMP AX, BX表示比较寄存器AX和BX 中的值。

通过CMP指令可以判断两个值的大小关系,并根据比较结果执行不同的操作。

6. NOP(No Operation)NOP助记符表示空操作,即不进行任何实际操作。

在编写汇编代码时,可以使用NOP来占据一段空白的指令空间或进行调试时的代码标记。

7. INC(Increment)INC助记符用于将寄存器或内存中的值加1。

例如,INC AX表示将寄存器AX中的值加1,INC [BX]表示将寄存器BX所指向的内存单元中的值加1。

51助记符汇总

注意 MOV A,@Ri 累加器到外部RAM(8 地址),其他包含(MOVXA,@Ri)都是右到左

/p-314104000.html

MUL AB DIV AB

// //ቤተ መጻሕፍቲ ባይዱ

制看时使用)

清零 CLR C

/view/0df0fe05a6c30c2259019ef4.html

布尔指令 (位操作)

压入堆栈 (把Rn存入堆栈,假设SP=1003H,Rn=502d H,结果 会是,SP=1002H存放50,SP=1001H存放2d) 弹出堆栈(假设SP=1002H存放50,SP=1001H存放2d, 结果为Rn=502d H) 交换 A与Rn数据互换 低4位交换 加1 A+1,结果放入A 减1 A-1,结果放入A 相乘(A*B,A存底8位,B存高8位) 相除(A÷B,A存商,B存余数) 十进制调整 A低4位>9则+06H,A高4位>9则+60H(想把16制当10制看时使用 相加 A+#data 结果存A 相加(带进位) A+#data+CY 结果存A 相减(带错位)A-#data-CY,结果存A;如果想不带,运算前对Cy清零 CLR 与 或 异或(A,#data异或,结果存放在累加器A中) 清0 取反 循环左移 带进位循环左移 循环右移 带进位循环右移 高低位互换 相对DPTR 的无条件转移 累加器为0 则转移 累加器为1 则转移 不相等转移 减1,不为0转移 延迟 绝对调用子程序 长调用子程序 从子程序返回 从中断服务子程序返回 绝对无条件转移 无条件长转移 无条件相对转移 清位 (CY置0) 置位(直接寻址位置1) 位取反 位与(直接寻址位和CY相与,结果放入CY) 位或(CY和直接寻址位取反线或,结果放入CY) 直接寻址位传送到CY 进位位CY传送到直接寻址 如果进位位为1 则转移 如果进位位为0 则转移 如果直接寻址位为1 则转移 如果直接寻址位为0 则转移 直接寻址位为1 则转移并清除该位

汇编语言助记符

汇编语言助记符一、MOV指令MOV指令是汇编语言中最基本的指令之一,用于将数据从一个位置复制到另一个位置。

它有多种格式,可以用来复制寄存器、内存和立即数。

1. MOV AX, BX这条指令将BX寄存器中的数据复制到AX寄存器中。

MOV指令可以用于寄存器之间的数据传输。

2. MOV [SI], AL这条指令将AL寄存器中的数据复制到SI寄存器指向的内存单元中。

MOV指令还可以用于将数据从寄存器传输到内存。

二、ADD指令ADD指令用于将两个数相加,并将结果存储在目标操作数中。

1. ADD AX, BX这条指令将AX寄存器和BX寄存器中的数据相加,并将结果存储在AX寄存器中。

ADD指令可以用于寄存器之间的相加运算。

2. ADD [SI], AL这条指令将AL寄存器中的数据与SI寄存器指向的内存单元中的数据相加,并将结果存储在该内存单元中。

ADD指令还可以用于将数据与内存中的数据相加。

三、SUB指令SUB指令用于将一个数减去另一个数,并将结果存储在目标操作数中。

1. SUB AX, BX这条指令将BX寄存器中的数据从AX寄存器中的数据中减去,并将结果存储在AX寄存器中。

SUB指令可以用于寄存器之间的相减运算。

2. SUB [SI], AL这条指令将SI寄存器指向的内存单元中的数据从AL寄存器中的数据中减去,并将结果存储在该内存单元中。

SUB指令还可以用于将内存中的数据从寄存器中的数据中相减。

四、INC指令INC指令用于将一个操作数加1。

1. INC AX这条指令将AX寄存器中的数据加1,并将结果存储在AX寄存器中。

INC指令可以用于寄存器的自增操作。

2. INC [SI]这条指令将SI寄存器指向的内存单元中的数据加1,并将结果存储在该内存单元中。

INC指令还可以用于内存中数据的自增操作。

五、DEC指令DEC指令用于将一个操作数减1。

1. DEC AX这条指令将AX寄存器中的数据减1,并将结果存储在AX寄存器中。

指令系统中各种助记符的英文全名

指令系统中各种助记符的英文全名我现将指令系统中各种助记符的英文全名写出来,各种助记符的记忆就会变得很简单o(∩_∩)o...在这之前,先说一下寄存器:数据寄存器分为:AH&AL=AX(accumulator):累加寄存器,常用于运算;在乘除等指令中指定用来存放操作数,另外,所有的I/O指令都使用这一寄存器与外界设备传送数据.BH&BL=BX(base):基址寄存器,常用于地址索引;CH&CL=CX(count):计数寄存器,常用于计数;常用于保存计算值,如在移位指令,循环(loop)和串处理指令中用作隐含的计数器.DH&DL=DX(data):数据寄存器,常用于数据传递。

他们的特点是,这4个16位的寄存器可以分为高8位: AH, BH, CH, DH.以及低八位:AL,BL,CL,DL。

这2组8位寄存器可以分别寻址,并单独使用。

另一组是指针寄存器和变址寄存器,包括:SP(Stack Pointer):堆栈指针,与SS配合使用,可指向目前的堆栈位置;BP(Base Pointer):基址指针寄存器,可用作SS的一个相对基址位置;SI(Source Index):源变址寄存器可用来存放相对于DS段之源变址指针;DI(Destination Index):目的变址寄存器,可用来存放相对于ES 段之目的变址指针。

指令指针IP(Instruction Pointer) 标志寄存器FR(Flag Register)OF(overflow flag)DF(direction flag)CF(carrier flag)PF(parity flag)AF(auxiliary flag)ZF(zero flag)SF(sign flag)IF(interrupt flag)TF(trap flag)段寄存器(Segment Register)为了运用所有的内存空间,8086设定了四个段寄存器,专门用来保存段地址:CS(Code Segment):代码段寄存器;DS(Data Segment):数据段寄存器;SS(Stack Segment):堆栈段寄存器;ES(Extra Segment):附加段寄存器。

51汇编助记符大全

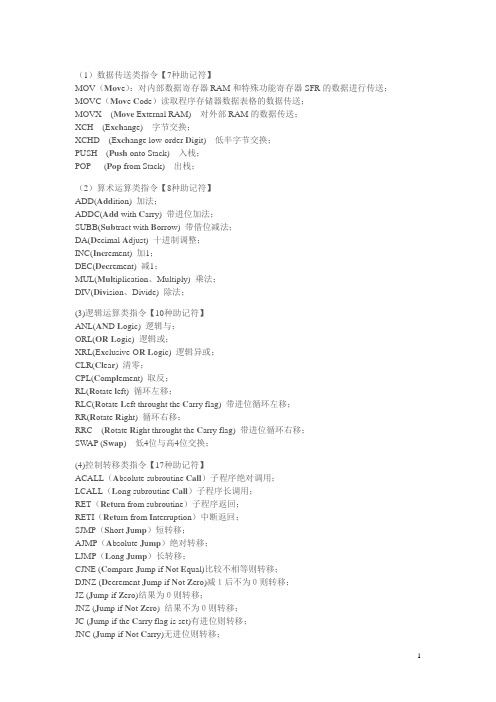

(1)数据传送类指令【7种助记符】MOV(Mov e):对内部数据寄存器RAM和特殊功能寄存器SFR的数据进行传送;MOVC(Mov e C ode)读取程序存储器数据表格的数据传送;MOVX(Move E x ternal RAM)对外部RAM的数据传送;XCH(E xch ange)字节交换;XCHD(E xch ange low-order D igit)低半字节交换;PUSH(Push onto Stack)入栈;POP (Pop from Stack)出栈;(2)算术运算类指令【8种助记符】ADD(Add ition) 加法;ADDC(Add with C arry) 带进位加法;SUBB(Sub tract with B orrow) 带借位减法;DA(D ecimal A djust) 十进制调整;INC(Inc rement) 加1;DEC(Dec rement) 减1;MUL(Mul tiplication、Multiply) 乘法;DIV(Div ision、Divide) 除法;(3)逻辑运算类指令【10种助记符】ANL(AN D L ogic) 逻辑与;ORL(OR L ogic) 逻辑或;XRL(E x clusive-O R L ogic) 逻辑异或;CLR(Cl ea r) 清零;CPL(C om pl ement) 取反;RL(R otate l eft) 循环左移;RLC(R otate L eft throught the C arry flag) 带进位循环左移;RR(R otate R ight) 循环右移;RRC(R otate R ight throught the C arry flag) 带进位循环右移;SWAP (Swap)低4位与高4位交换;(4)控制转移类指令【17种助记符】ACALL(A bsolute subroutine Call)子程序绝对调用;LCALL(L ong subroutine Call)子程序长调用;RET(Ret urn from subroutine)子程序返回;RETI(Ret urn from I nterruption)中断返回;SJMP(S hort J u mp)短转移;AJMP(A bsolute J u mp)绝对转移;LJMP(L ong J u mp)长转移;CJNE (C ompare J ump if N ot E qual)比较不相等则转移;DJNZ (D ecrement J ump if N ot Z ero)减1后不为0则转移;JZ (J ump if Z ero)结果为0则转移;JNZ (J ump if N ot Z ero) 结果不为0则转移;JC (J ump if the C arry flag is set)有进位则转移;JNC (J ump if N ot C arry)无进位则转移;JB (J ump if the B it is set)位为1则转移;JNB (J ump if the B it is N ot set) 位为0则转移;JBC(J ump if the B it is set and C lear the bit) 位为1则转移,并清除该位;NOP (N o Op eration)空操作;(5)位操作指令【1种助记符】SETB(Set B it)位置1。

各类命令助记符

MCS-51的基本指令共111条;按功能分为5类:(1)数据传送(29条)(2)算术操作(24条)(3)逻辑操作(24条)(4)控制转移(17条)(5)布尔变量操作(17条)按指令所占的字节来分:(1) 单字节指令49条;(2) 双字节指令46条;(3) 三字节指令16条。

数据传送指令(29条)按指令的执行时间来分:(1) 1个机器周期(12个时钟振荡周期)指令64条;(2) 2个机器周期(24个时钟振荡周期)指令45条;(3) 只有乘、除两条指令的执行时间为4个机器周期(48个时钟振荡周期)。

12MHz晶振:机器周期为1μs。

向累加器A的传送:MOV A, Rn ;(A)←(Rn)向通用寄存器传送:MOV Rn, A ;(Rn)←(A)向直接地址传送:MOV direct,A ;(direct)←(A)间址传送:MOV @Ri,A ;((Ri))←(A)入栈指令:PUSH direct ;(sp)←(sp)+1,;((sp))←(direct)出栈指令:POP direct ;(direct)←((sp)),;(sp)←(sp)-1累加器传送指令字节交换指令:XCH A,Rn ;(A)↔(Rn)半字节交换指令:XCHD A,@Ri ; (A0~3) ↔((Ri) 0~3)累加器高4位与低4位数据互换:SWAP A ;(A0~3) ↔(A4~7)累加器与外部RAM的传送:MOVX A,@Ri ;(A) ←((Ri))累加器与程序存储器传送:MOVC A,@A+DPTR目标地址传送指令:MOV DPTR,#data16算术运算指令(24条)加法指令:ADD A,Rn ;(A) ←(A)+(Rn)带进位加法:ADDC A,Rn ;(A) ←(A)+(Rn)+(C)加1指令:INC A ;(A) ←(A)+1十进制调整指令:DA A ;减法指令:带借位减法指令:SUBB A,Rn;(A) ←(A)-(Rn)-(C)减1指令:DEC A ;(A) ←(A)-1乘法指令:MUL AB;(BA) ←(A)*(B)除法指令:DIV AB ;(A) ←(A)/(B); (B) ←(A)%(B)单操作数逻辑运算指令累加器A清零:CLR A ;(A) ←0累加器A取反:CPL A ;(A) ←(A)累加器A循环左移:RL A;累加器A循环右移: RR A;累加器A带进位循环左移:RLC A;累加器A带进位循环右移:RRC A;双操作数逻辑运算指令逻辑“与”指令:ANL A, Rn ;(A) ←(A)&(Rn)逻辑“或”指令:ORL A, Rn ;(A) ←(A)|(Rn)“异或”指令:XRL A, Rn ;(A) ←(A)^(Rn)控制转移指令(17条)1无条件转移指令调用指令绝对调用(2K)ACALL addr11;(pc) ←(pc+2);(sp) ←(sp)+1,((sp)) ←(pc0~7);(sp) ←(sp)+1,((sp)) ←(pc8~15);(pc0~10) ← addr0~10;(pc11~15)不变长调用(64K)LCALL addr16;(pc) ←(pc)+3;(sp) ← (sp)+1,((sp)) ←(pc0~7);(sp) ← (sp)+1,((sp)) ←(pc8~15);(pc) ← addr16返回指令子程序返回(ACALL和LCALL)RET;(pc8~15) ←((sp)),(sp) ←(sp)-1;(pc0~7) ←((sp)),(sp) ←(sp)-1中断程序返回RETI;(pc8~15) ←((sp)),(sp) ←(sp)-1;(pc0~7) ←((sp)),(sp) ←(sp)-1 ;开放中断逻辑转移指令绝对转移AJMP addr11;(pc0~10) ← addr0~10;(pc11~15)不变长转移:LJMP addr16;(pc) ← addr16相对转移(短转移,双向)SJMP rel ;(pc) ←(pc)+rel间接转移指令(散转指令)JMP @A+DPTR ;(pc)←(A)+(DPTR)空操作指令:NOP ;(pc) ←(pc)+1条件转移指令(1)判零转移指令JZ rel;当(A)为0则(pc) ←(pc)+rel ;否则,顺序执行JNZ rel;当(A)非0,则(pc) ←(pc)+rel;否则,顺序执行比较转移指令(-128B~+127B)CJNE A,direct,rel跳转循环指令(减1不为0转移指令):DJNZ Rn,rel ;(Rn) ←(Rn)-1,;若(Rn)非0,则(pc) ←(pc)+rel;否则,顺序执行DJNZ direct,rel;(direct) ←(direct)-1,;若(direct)非0,则(pc) ←(pc)+rel;否则,顺序执行布尔处理器指令(17条)位变量地址空间片内低RAM,Bit地址范围:00H~7FH(128位)片内高RAM,地址能被8整除的SFR中对应各位(11个):80H~F7H布尔数据传送指令:MOV C ,bit ;(C) ←(bit)※C为进位标志位Cy(不影响PSW)布尔状态控制位清“0”指令CLR C ;(C) ← 0位置“1”指令:SETB C ;(C) ← 1位取反指令:CPL C ;(C) ← (C)位逻辑运算位逻辑“与”指令:ANL C,bit ;(C) ← (C)&(bit)位逻辑“或”指令:ORL C,bit ;(C) ← (C)|(bit)位条件转移指令:判断C转移:J C rel;当(C)为1,则(pc) ←(pc)+rel;否则,顺序执行JNC rel;当(C)为0,则(pc) ←(pc)+rel;否则,顺序执行判断位变量转移指令:JB bit, rel;当(bit)为1,则(pc) ←(pc)+rel;否则,顺序执行JNB bit, rel;当(bit)为0,则(pc) ←(pc)+rel;否则,顺序执行※pc+rel中,(pc)表示为当前的指令地址即:执行跳转指令后的下一条指令地址判断位变量转移并清0指令:JBC bit, rel ;当(bit)为1,则(bit)←0,(pc) ←(pc)+rel ;否则,顺序执行※可用于对SFR的bit检测和软件复位(TFX)汇编语言语句的种类和格式:程序段说明伪指令ORG ORG 1000H汇编结束伪指令END [标号:] END伪指令语句等值伪指令EQU和DL DDR EQU 1020H(不可改)数据说明伪指令DB和DW TAB DB 0, 4, 8, 16, 32保留存储区说明伪指令:STA DS 10H软件延时子程序DELAY:MOV R2, #data ;指令周期数=1DELAY1: DJNZ R2, DELAY1;指令周期数=2RET延时时间=1(第一条指令周期)+(R2)×2(周期数); 影响CPU工作效率延时范围:3~513个机器周期,由(R2)决定有符号数X存于内部RAM的DATA单元,Y存于FUNC单元,按以下要求编程实现给Y赋值。

汇编助记符汇总

汇编助记符汇总助记符指令说明字节数周期数(数据传递类指令)MOV A,Rn 寄存器传送到累加器 1 1 MOV A,direct 直接地址传送到累加器 2 1 MOV A,@Ri 累加器传送到外部RAM(8 地址) 1 1 MOV A,#data 立即数传送到累加器 2 1 MOV Rn,A 累加器传送到寄存器 1 1 MOV Rn,direct 直接地址传送到寄存器 2 2 MOV Rn,#data 累加器传送到直接地址 2 1 MOV direct,Rn 寄存器传送到直接地址 2 1 MOV direct,direct 直接地址传送到直接地址 3 2 MOV direct,A 累加器传送到直接地址 2 1 MOV direct,@Ri 间接RAM 传送到直接地址 2 2 MOV direct,#data 立即数传送到直接地址 3 2 MOV @Ri,A 直接地址传送到直接地址 1 2 MOV @Ri,direct 直接地址传送到间接RAM 2 1 MOV @Ri,#data 立即数传送到间接RAM 2 2 MOV DPTR,#data16 16 位常数加载到数据指针 3 1 MOVC A,@A+DPTR 代码字节传送到累加器 1 2 MOVC A,@A+PC 代码字节传送到累加器 1 2 MOVX A,@Ri 外部RAM(8 地址)传送到累加器 1 2MOVX A,@DPTR 外部RAM(16 地址)传送到累加器 1 2 MOVX @Ri,A 累加器传送到外部RAM(8 地址) 1 2 MOVX @DPTR,A 累加器传送到外部RAM(16 地址) 1 2 PUSH direct 直接地址压入堆栈 2 2 POP direct 直接地址弹出堆栈 2 2 XCH A,Rn 寄存器和累加器交换1 1 XCH A, direct 直接地址和累加器交换 2 1 XCH A, @Ri 间接RAM 和累加器交换 1 1 XCHD A, @Ri 间接RAM 和累加器交换低4 位字节1 1(算术运算类指令)INC A 累加器加1 1 1 INC Rn 寄存器加1 1 1 INC direct 直接地址加1 2 1 INC @Ri 间接RAM 加1 1 1 INC DPTR 数据指针加1 1 2 DEC A 累加器减1 1 1 DEC Rn 寄存器减1 1 1 DEC direct 直接地址减1 2 2 DEC @Ri 间接RAM 减1 1 1 MUL AB 累加器和B 寄存器相乘 1 4 DIV AB 累加器除以B 寄存器 1 4DA A 累加器十进制调整 1 1 ADD A,Rn 寄存器与累加器求和 1 1 ADD A,direct 直接地址与累加器求和 2 1 ADD A,@Ri 间接RAM 与累加器求和 1 1 ADD A,#data 立即数与累加器求和 2 1 ADDC A,Rn 寄存器与累加器求和(带进位) 1 1 ADDC A,direct 直接地址与累加器求和(带进位) 2 1 ADDC A,@Ri 间接RAM 与累加器求和(带进位) 1 1 ADDC A,#data 立即数与累加器求和(带进位) 2 1 SUBB A,Rn 累加器减去寄存器(带借位) 1 1 SUBB A,direct 累加器减去直接地址(带借位) 2 1 SUBB A,@Ri 累加器减去间接RAM(带借位) 1 1 SUBB A,#data 累加器减去立即数(带借位) 2 1(逻辑运算类指令)ANL A,Rn 寄存器“与”到累加器 1 1 ANL A,direct 直接地址“与”到累加器 2 1 ANL A,@Ri 间接RAM“与”到累加器 1 1 ANL A,#data 立即数“与”到累加器 2 1 ANL direct,A 累加器“与”到直接地址 2 1 ANL direct, #data 立即数“与”到直接地址 3 2 ORL A,Rn 寄存器“或”到累加器 1 2ORL A,direct 直接地址“或”到累加器2 1 ORL A,@Ri 间接RAM“或”到累加器1 1 ORL A,#data 立即数“或”到累加器2 1 ORL direct,A 累加器“或”到直接地址 2 1 ORL direct, #data 立即数“或”到直接地址3 1 XRL A,Rn 寄存器“异或”到累加器1 2 XRL A,direct 直接地址“异或”到累加器2 1 XRL A,@Ri 间接RAM“异或”到累加器1 1 XRL A,#data 立即数“异或”到累加器2 1 XRL direct,A 累加器“异或”到直接地址2 1 XRL direct, #data 立即数“异或”到直接地址 3 1 CLR A 累加器清零 1 2 CPL A 累加器求反 1 1 RL A 累加器循环左移 1 1 RLC A 带进位累加器循环左移 1 1 RR A 累加器循环右移 1 1 RRC A 带进位累加器循环右移 1 1 SWAP A 累加器高、低4 位交换 1 1(控制转移类指令)JMP @A+DPTR 相对DPTR 的无条件间接转移 1 2 JZ rel 累加器为0 则转移 2 2JNZ rel 累加器为1 则转移 2 2 CJNE A,direct,rel 比较直接地址和累加器,不相等转移 3 2 CJNE A,#data,rel 比较立即数和累加器,不相等转移3 2 CJNE Rn,#data,rel 比较寄存器和立即数,不相等转移2 2 CJNE @Ri,#data,rel 比较立即数和间接RAM,不相等转移3 2 DJNZ Rn,rel 寄存器减1,不为0 则转移 3 2 DJNZ direct,rel 直接地址减1,不为0 则转移 3 2 NOP 空操作,用于短暂延时 1 1 ACALL add11 绝对调用子程序 2 2 LCALL add16 长调用子程序 3 2 RET 从子程序返回 1 2 RETI 从中断服务子程序返回1 2 AJMP add11 无条件绝对转移2 2 LJMP add16 无条件长转移 3 2 SJMP rel 无条件相对转移 2 2 (布尔指令)CLR C清进位位11 CLR bit清直接寻址位21 SETB C置位进位位11 SETB bit置位直接寻址位21 CPL C取反进位位11CPL bit取反直接寻址位21 ANL C,bit直接寻址位“与”到进位位22 ANL C,/bit直接寻址位的反码“与”到进位位22 ORL C,bit直接寻址位“或”到进位位22 ORL C,/bit直接寻址位的反码“或”到进位位22 MOV C,bit直接寻址位传送到进位位21 MOV bit, C进位位位传送到直接寻址22 JC rel如果进位位为1 则转移22 JNC rel如果进位位为0 则转移22 JB bit,rel如果直接寻址位为1 则转移32 JNB bit,rel如果直接寻址位为0 则转移32 JBC bit,rel直接寻址位为1 则转移并清除该位22(伪指令)ORG 指明程序的开始位置DB 定义数据表DW 定义16 位的地址表EQU 给一个表达式或一个字符串起名DATA 给一个8 位的内部RAM 起名XDATA 给一个8 位的外部RAM 起名BIT 给一个可位寻址的位单元起名END 指出源程序到此为止(指令中的符号标识)Rn 工作寄存器R0-R7Ri 工作寄存器R0 和R1@Ri 间接寻址的8 位RAM 单元地址(00H-FFH)#data8 8 位常数#data16 16 位常数addr16 16 位目标地址,能转移或调用到64KROM 的任何地方addr11 11 位目标地址,在下条指令的2K 范围内转移或调用Rel 8 位偏移量,用于SJMP 和所有条件转移指令,范围-128~+127 Bit 片内RAM 中的可寻址位和SFR 的可寻址位Direct 直接地址,范围片内RAM 单元(00H-7FH)和80H-FFH $ 指本条指令的起始位置。

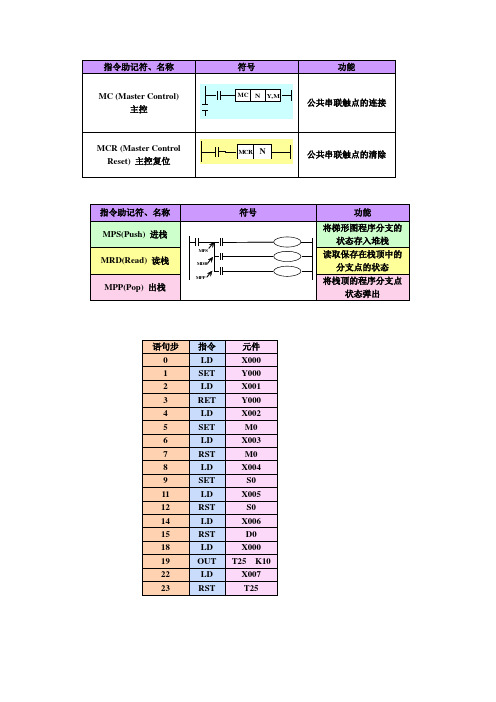

指令助记符、名称

语句步

指令

元件

0

LD

X000

1

SET

Y000

2

LD

X001

3

RET

Y000

4

LD

X002

5

SET

M0

6

LD

X003

7

RST

M0

8

LD

X004

9

SET

S0

11

LD

X005

12

RST

S0

14

LD

X006

15

RST

D0

18

LD

X000

19

OUT

T25 K10

22

LD

X007

23

RST

T25

语句步

指令

元件

0

LD

X000

1

OUT

Y000

2

LDI

X000

3

AND

X001

4

OUT

M0

5

ANI

X002

6

OUT

Y001

7

LDI

X001

8

OR

X002

9

ORI

X003

10

OUT

Y002

11

END

指令名称

助记符

指令代码

操作数

程序步

S1•

SH、KnX、KnY、KnM、KnS、T、C、D、V、Z

指令助记符、名称

符号

功能

MC (Master Control)

主控

公共串联触点的连接

MCR (Master Control Reset)主控复位

03-MIPS指令助记符表

令集(共31条)rt <- rs + (zero-extend)immediate ;其中 rt=$1js=$2 rt <- rs & (zero-extend)i mmedi ate ;其中 rt=$1js=$2 rt <- rs | (zero-extend)immedi ate ;其中 rt=$1js=$2 rt <- rs xor (zero-extend)i mmedi ate ;其 中 rt=$1,rs=$2 rt <- immediate*65536 ;将16<^即数 放到目标寄存器高16 位,目标寄存器的低16©填0rt <- memory[rs + (sign- exteiKl)immediate] ; rt=$1,rs=$2 memory[rs + (sign-extend)immediate] <- rt ; rt=$1,rs=$2 if (rs == rt) PC <- PC+4 + (sign- extend)immediate«2 if (rs != rt) PC <- PC+4 + (sign- extend)immediate«2 if (rs <(sign -extend)immediate) rt=1 else rt=O ; 其中 rs = $2 , rt=$1 if (rs <(zero-extend)i mmedi ate) rt=1 else rt=O ;其中 rs = $2, rt=$1 PC <- (PC+4)[3L28],address,0,0 ; address=10000/4 $31 <-PC+4 ; PC <- (PCM)[31 _28],address 旦 0;address=10000/4 immediate immediate if($2<10)$1=1 else000010 address 000011 address memory[$2+10] =$1注意:为MIPS16只有16个1過的寄存器.所以JAL 指令中$31改成S15,所有立即数均无需扩展,LUI 指令直接就是将立即数付始RTS 存既 immediate immediate immediate immediate immediate immediate immediate addiu $1,52,100 $1=$2+100 andi $1,$2,10 $1=$2 &10 andi $1=$2|10 andi $1=$2A 10 lw$1,10($2) sw$1,10($2) beq$1,$2,10 bne$1,$2,10 if($2<10)slti$1,$2,10goto 10000 $31<-PC+4;goto 10000$1=memory[$2+10]if($1 !=$2) gotoPC+4+40if($1==$2) gotoPC+4+40$1=100*65536。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

MCS-51的基本指令共111条;按功能分为5类:(1)数据传送(29条)(2)算术操作(24条)(3)逻辑操作(24条)(4)控制转移(17条)(5)布尔变量操作(17条)按指令所占的字节来分:(1) 单字节指令49条;(2) 双字节指令46条;(3) 三字节指令16条。

数据传送指令(29条)按指令的执行时间来分:(1) 1个机器周期(12个时钟振荡周期)指令64条;(2) 2个机器周期(24个时钟振荡周期)指令45条;(3) 只有乘、除两条指令的执行时间为4个机器周期(48个时钟振荡周期)。

12MHz晶振:机器周期为1μs。

向累加器A的传送:MOV A, Rn ;(A)←(Rn)向通用寄存器传送:MOV Rn, A ;(Rn)←(A)向直接地址传送:MOV direct,A ;(direct)←(A)间址传送:MOV @Ri,A ;((Ri))←(A)入栈指令:PUSH direct ;(sp)←(sp)+1,;((sp))←(direct)出栈指令:POP direct ;(direct)←((sp)),;(sp)←(sp)-1累加器传送指令字节交换指令:XCH A,Rn ;(A)↔(Rn)半字节交换指令:XCHD A,@Ri ; (A0~3) ↔((Ri) 0~3)累加器高4位与低4位数据互换:SWAP A ;(A0~3) ↔(A4~7)累加器与外部RAM的传送:MOVX A,@Ri ;(A) ←((Ri))累加器与程序存储器传送:MOVC A,@A+DPTR目标地址传送指令:MOV DPTR,#data16算术运算指令(24条)加法指令:ADD A,Rn ;(A) ←(A)+(Rn)带进位加法:ADDC A,Rn ;(A) ←(A)+(Rn)+(C)加1指令:INC A ;(A) ←(A)+1十进制调整指令:DA A ;减法指令:带借位减法指令:SUBB A,Rn;(A) ←(A)-(Rn)-(C)减1指令:DEC A ;(A) ←(A)-1乘法指令:MUL AB;(BA) ←(A)*(B)除法指令:DIV AB ;(A) ←(A)/(B); (B) ←(A)%(B)单操作数逻辑运算指令累加器A清零:CLR A ;(A) ←0累加器A取反:CPL A ;(A) ←(A)累加器A循环左移:RL A;累加器A循环右移: RR A;累加器A带进位循环左移:RLC A;累加器A带进位循环右移:RRC A;双操作数逻辑运算指令逻辑“与”指令:ANL A, Rn ;(A) ←(A)&(Rn)逻辑“或”指令:ORL A, Rn ;(A) ←(A)|(Rn)“异或”指令:XRL A, Rn ;(A) ←(A)^(Rn)控制转移指令(17条)1无条件转移指令调用指令绝对调用(2K)ACALL addr11;(pc) ←(pc+2);(sp) ←(sp)+1,((sp)) ←(pc0~7);(sp) ←(sp)+1,((sp)) ←(pc8~15);(pc0~10) ← addr0~10;(pc11~15)不变长调用(64K)LCALL addr16;(pc) ←(pc)+3;(sp) ← (sp)+1,((sp)) ←(pc0~7);(sp) ← (sp)+1,((sp)) ←(pc8~15);(pc) ← addr16返回指令子程序返回(ACALL和LCALL)RET;(pc8~15) ←((sp)),(sp) ←(sp)-1;(pc0~7) ←((sp)),(sp) ←(sp)-1中断程序返回RETI;(pc8~15) ←((sp)),(sp) ←(sp)-1;(pc0~7) ←((sp)),(sp) ←(sp)-1 ;开放中断逻辑转移指令绝对转移AJMP addr11;(pc0~10) ← addr0~10;(pc11~15)不变长转移:LJMP addr16;(pc) ← addr16相对转移(短转移,双向)SJMP rel ;(pc) ←(pc)+rel间接转移指令(散转指令)JMP @A+DPTR ;(pc)←(A)+(DPTR)空操作指令:NOP ;(pc) ←(pc)+1条件转移指令(1)判零转移指令JZ rel;当(A)为0则(pc) ←(pc)+rel ;否则,顺序执行JNZ rel;当(A)非0,则(pc) ←(pc)+rel;否则,顺序执行比较转移指令(-128B~+127B)CJNE A,direct,rel跳转循环指令(减1不为0转移指令):DJNZ Rn,rel ;(Rn) ←(Rn)-1,;若(Rn)非0,则(pc) ←(pc)+rel;否则,顺序执行DJNZ direct,rel;(direct) ←(direct)-1,;若(direct)非0,则(pc) ←(pc)+rel;否则,顺序执行布尔处理器指令(17条)位变量地址空间片内低RAM,Bit地址范围:00H~7FH(128位)片内高RAM,地址能被8整除的SFR中对应各位(11个):80H~F7H布尔数据传送指令:MOV C ,bit ;(C) ←(bit)※C为进位标志位Cy(不影响PSW)布尔状态控制位清“0”指令CLR C ;(C) ← 0位置“1”指令:SETB C ;(C) ← 1位取反指令:CPL C ;(C) ← (C)位逻辑运算位逻辑“与”指令:ANL C,bit ;(C) ← (C)&(bit)位逻辑“或”指令:ORL C,bit ;(C) ← (C)|(bit)位条件转移指令:判断C转移:J C rel;当(C)为1,则(pc) ←(pc)+rel;否则,顺序执行JNC rel;当(C)为0,则(pc) ←(pc)+rel;否则,顺序执行判断位变量转移指令:JB bit, rel;当(bit)为1,则(pc) ←(pc)+rel;否则,顺序执行JNB bit, rel;当(bit)为0,则(pc) ←(pc)+rel;否则,顺序执行※pc+rel中,(pc)表示为当前的指令地址即:执行跳转指令后的下一条指令地址判断位变量转移并清0指令:JBC bit, rel ;当(bit)为1,则(bit)←0,(pc) ←(pc)+rel ;否则,顺序执行※可用于对SFR的bit检测和软件复位(TFX)汇编语言语句的种类和格式:程序段说明伪指令ORG ORG 1000H汇编结束伪指令END [标号:] END伪指令语句等值伪指令EQU和DL DDR EQU 1020H(不可改)数据说明伪指令DB和DW TAB DB 0, 4, 8, 16, 32保留存储区说明伪指令:STA DS 10H软件延时子程序DELAY:MOV R2, #data ;指令周期数=1DELAY1: DJNZ R2, DELAY1;指令周期数=2RET延时时间=1(第一条指令周期)+(R2)×2(周期数); 影响CPU工作效率延时范围:3~513个机器周期,由(R2)决定有符号数X存于内部RAM的DATA单元,Y存于FUNC单元,按以下要求编程实现给Y赋值。

绘出程序框图。

程序清单:ORG 4000HMOV A,DATA;取出X送AJZ COMP ;若X=0则转移到COMPJNB ACC.7,POSI ;若X>0则转移到POSIMOV A,#0FFH;若X<0则A= -1SJMP COMP ;转分支结构出口POSI:MOV A,#01H;X>0时A=1COMP:MOV FUNC,A;存函数Y值HERE:SJMP HERH;结束2重以上的循环,内外层分明,且不能交叉例1、50ms延时程序(设系统为12M的晶振)DELAY: MOV R7,#200DELAY_1 :MOV R6,#123NOPDELAY_2: DJNZ R6,DELAY_2DJNZ R7,DELAY_1RET计算:【(123*2+1+1)+2】*200=250*200us例2、定时程序如下:MOV R5,#TIME1LOOP2: MOV R4,#TIME2LOOP1: NOPNOPDJNZ R4,LOOP1DJNZ R5,LOOP2RET 该定时程序的执行时间为:其中T0为单片机的机器周期T=(((1+1+2)*TIME2+1+2)*TIME1+1)*T08051/8751最小应用系统(如图所示)(1全部I/O口线开放(2内部存储器容量有限(3)EA接高(4)P0、P2使用要注意图6-2为用8031外接程序存储器构成的最小系统。

特点是:无内部ROM,需要构成三片最小系统,ALE下降沿锁存地址底8位。

芯片选择方法:线选法和地址译码法。

8255A的3种工作方式:方式0(基本输入/输出方式)数据输出有锁存,数据输入有缓冲(无锁存)方式1(选通输入/输出方式)A组包括A口和C口的高四位(PC7~PC4),A口可由程序设定为输入口或输出口,C口的高四位则用来作为输入/输出操作的控制和同步信号;B组包括B口和C口的低四位(PC3~PC0),功能和A组相同。

方式2(双向I/O口方式)A口为8位双向I/O口,C口的PC7~PC3用来作为输入输出的控制和同步信号。

此时,B口可以工作在方式0或方式1。

8255有两个控制字:方式控制字,置位/复位控制字接口(Interface):计算机与外设的数据传送电路。

端口(Port):编程寻址的口寄存器,编址方式:独立编址,统一编址CPU与外设数据传送方式:直接、查询、中断、DMA中断:计算机暂停正在执行的程序,去执行中断服务程序,服务完成后回到原程序断开出继续执行。

CPU响应中断的条件:(1)有中断请求(2)中断请求没有被屏蔽(3)中断是开放的或者是允许的(4)在现行指令结束后才响应中断中断响应及中断期间应做的工作:(1)关中断(2)保留断点(3)保护现场(4)给出中断,入口转入相应的中断服务程序(5)恢复现场(6)开中断与返回。