6.3 STM32F107VCT的时钟深入剖析(32M,40M,72M灵活切换)

stm32时钟概念

stm32时钟概念(实用版)目录1.STM32 时钟概念概述2.STM32 时钟的分类3.STM32 时钟的配置方法4.STM32 时钟的应用实例5.总结正文一、STM32 时钟概念概述STM32 时钟是指基于 STM32 单片机的时钟系统,STM32 单片机是一款高性能、低功耗的微控制器,内部集成了多种时钟源,可为系统提供多样化的时钟信号。

时钟系统是 STM32 单片机的重要组成部分,对系统的稳定性和准确性具有重要影响。

二、STM32 时钟的分类STM32 时钟可分为以下几类:1.高速时钟(HCLK):高速时钟是 STM32 单片机内最快的时钟,通常用于处理高速信号,如高速串行通信、音频信号处理等。

2.高速低功耗时钟(HCLK_LP):高速低功耗时钟是高速时钟的低功耗版本,可在降低功耗的同时保持较高的时钟频率。

3.中速时钟(MCLK):中速时钟是 STM32 单片机内部时钟信号的默认选择,适用于大多数应用场景。

4.低速时钟(LCLK):低速时钟是 STM32 单片机内部最慢的时钟信号,适用于对时钟频率要求不高的场景,如按键扫描等。

5.实时时钟(RTC):实时时钟是 STM32 单片机内部的实时时钟模块,可用于提供年月日时分秒等时间信息。

三、STM32 时钟的配置方法STM32 时钟的配置方法主要包括以下步骤:1.配置时钟源:根据应用需求选择合适的时钟源,如高速时钟源(HSE)或高速低功耗时钟源(HSI)等。

2.配置时钟预分频:根据实际需求,对时钟源进行预分频,以得到所需的时钟频率。

3.配置时钟倍频:对预分频后的时钟信号进行倍频,以进一步提高时钟频率。

4.配置时钟输出:将配置好的时钟信号输出到相应的时钟引脚。

5.配置时钟使能:使能所需的时钟信号。

四、STM32 时钟的应用实例以下是一个基于 STM32F103 系列的实时时钟(RTC)实验例程:1.首先,配置 RTC 时钟源为高速时钟源(HSE)。

STM32F407ZGT的时钟深入剖析(32M_40M_72M灵活切换)

时钟频率的配置

{开始

ቤተ መጻሕፍቲ ባይዱ

{ /**** 程序总共 2 部分之第 1 部分 时钟频率的配置 ********************/

/***** 以下是关于 RCC 时钟 详细请见《STM32F20XXX 参考手册》5.3 节 RCC 寄存 器描述 *******/

unsigned char sws = 0; RCC->CR |= 0X00010000; //使能外部高速时钟 HSEON while(!(RCC->CR>>17)); //将 RCC_CR 寄存器的值右移 17 位,等待 HSERDY 就绪, 即外部时钟就绪

对于 5, 通过 PLL 选择位预先选择后续 PLL 分支的输入时钟(假设选择外部晶振);

对于 7,设置外部晶振的分频数(假设 1 分频);

对于 21,选择 PLL 倍频的时钟源(假设选择经过分频后的外部晶振时钟);

对于 8,设置 PLL 倍频数(假设 9 倍频);

对于 9,选择系统时钟源(假设选择经过 PLL 倍频所输出的时钟);

众所周知,微控制器(处理器)的运行必须要依赖周期性的时钟脉冲来驱动——往往由 一个外部晶体振荡器提供时钟输入为始,最终转换为多个外部设备的周期性运作为末,这种 时钟“能量”扩散流动的路径,犹如大树的养分通过主干流向各个分支,因此常称之为“时 钟树”。在一些传统的低端 8 位单片机诸如 51,AVR,PIC 等单片机,其也具备自身的一个 时钟树系统,但其中的绝大部分是不受用户控制的,亦即在单片机上电后,时钟树就固定在 某种不可更改的状态(假设单片机处于正常工作的状态)。比如 51 单片机使用典型的 12MHz 晶振作为时钟源,则外设如 IO 口、定时器、串口等设备的驱动时钟速率便已经是固定的, 用户无法将此时钟速率更改,除非更换晶振。

STM32系列MCU硬件实时时钟(RTC)应用笔记说明书

2017年6月Doc ID 018624 Rev 1 [English Rev 5]1/45AN3371应用笔记在 STM32 F0、F2、F3、F4 和 L1 系列MCU 中使用硬件实时时钟(RTC )前言实时时钟 (RTC) 是记录当前时间的计算机时钟。

RTC 不仅应用于个人计算机、服务器和嵌入式系统,几乎所有需要准确计时的电子设备也都会使用。

支持 RTC 的微控制器可用于精密计时器、闹钟、手表、小型电子记事薄以及其它多种设备。

本应用笔记介绍超低功耗中等容量、超低功耗大容量、F0、F2和 F4 系列器件微控制器中嵌入式实时时钟 (RTC) 控制器的特性,以及将 RTC 用于日历、闹钟、定时唤醒单元、入侵检测、时间戳和校准应用时所需的配置步骤。

本应用笔记提供了含有配置信息的示例,有助于您快速准确地针对日历、闹钟、定时唤醒单元、入侵检测、时间戳和校准应用配置 RTC 。

注:所有示例和说明均基于 STM32L1xx 、STM32F0xx 、STM32F2xx 、STM32F4xx 和STM32F3xx 固件库,以及 STM32L1xx (RM0038)、STM32F0xx (RM0091)、STM32F2xx (RM0033)、STM32F4xx (RM0090)、STM32F37x (RM0313) 和 STM32F30x(RM0316) 的参考手册。

本文提到的STM32 指超低功耗中等容量、超低功耗大容量、F0、F2 和 F4 系列器件。

超低功耗中等 (ULPM) 容量器件包括 STM32L151xx 和 STM32L152xx 微控制器,Flash 容量在 64 KB 到 128 KB 之间。

超低功耗大 (ULPH) 容量器件包括 STM32L151xx 、STM32L152xx 和 STM32L162xx 微控制器,Flash 容量为 384 KB 。

F2 系列器件包括 STM32F205xx 、STM32F207xx 、STM32F215xx 和 STM32F217xx 微控制器。

STM32F107VC的嵌入式远程监控终端设计

STM32F107VC的嵌入式远程监控终端设计关丽敏;李思慧;李伟刚【期刊名称】《单片机与嵌入式系统应用》【年(卷),期】2014(14)6【摘要】针对处于偏远地区或恶劣环境中的无人值守设备的运行状态的监控问题,本文应用嵌入式技术以及工业以太网技术设计了一种数据采集与监控系统的远程监控终端。

围绕核心处理器 STM32 F107 VC构建了终端的硬件系统,介绍了网络接口设计、输入/输出接口设计和本地存储电路设计。

监控终端软件基于 ARM公司的 RL ARM中间件,实现了多任务并行的网络实时通信、基于 WebServer的远程配置服务和临时存储现场数据的文件系统。

应用结果表明,系统可靠性高、实时性强,有效降低了远程监控系统成本。

%Aiming at the problem that unattended equipments are usually in remote areas and harsh environments,the paper designs a re-mote monitoring terminal of data acquisition and monitoring system.Based on the the core processorSTM32F107VC,the hardware sys-tem of the terminal is designed,theinput/output interface and local storage circuit are designed.The softwareof the monitoring terminal is based on RL-ARM middleware of ARM.It completes the multitasking parallel network real-time communication,based on the Web-Server remote configuration services and temporary storage of field data file system.Application results show that the system has high reliability,strong real-time performance and effectively reduces the cost of remote monitoring system.【总页数】4页(P72-75)【作者】关丽敏;李思慧;李伟刚【作者单位】长安大学电子与控制工程学院,西安 710064;长安大学电子与控制工程学院,西安 710064;西安昆仑工业集团有限责任公司【正文语种】中文【中图分类】TP23【相关文献】1.对ARM和Linux的物联网远程监控终端设计分析及实现 [J], 谢娜2.基于云服务的干式变压器远程监控终端设计 [J], Chen Erkui;Jia Meng;Han Qingchun3.煤矿井下远程监控终端设计 [J], 张新4.分布式光伏电站远程监控系统的双无线终端设计 [J], 童友波5.基于GPRS的纯电动矿山车远程监控车载终端设计 [J], 张宸宇因版权原因,仅展示原文概要,查看原文内容请购买。

STM32入门教程--系统时钟配置

STM32 系统时钟配置一、STM32的时钟系统时钟是什么?时钟通常是振荡器(如晶振)产生的特定频率的方波信号,时钟周期是时钟频率的倒数,时钟频率1MHz时钟周期为1/1000000=1us。

时钟周期是MCU处理指令的最小时间单元,每个程序指令都需要若干个时钟周期,MCU的时钟频率越快,完成一个指令的时间就越短,速度就越快。

时钟是MCU运行的基础,好比MCU的脉搏,是MCU性能的重要参数。

每个MCU 都是在某个特定的时钟频率下进行工作的,如C51单片机时钟频率为12MHz,而STM32F103 的系统时钟频率是72MHz。

STM32的时钟系统STM32时钟频率较高,时钟越快功耗越大,同时抗电磁干扰能力也会越弱。

而且STM32外设非常多,而通常外设是不需要像系统时钟那么高的频率的,比如看门狗和RTC 只需要几十K的时钟即可。

另外实际使用的时候通常只会用到有限的几个外设,STM32可以只给需要启动的外设分配时钟,以此来降低功耗。

由此可看出STM32 的时钟系统较为复杂,它采用了多个时钟源的方法来解决这些问题。

STM32 有4个独立时钟源:HSI、HSE、LSI、LSE。

①、HSI是高速内部时钟,RC振荡器,频率为8MHz,精度不高。

②、HSE是高速外部时钟,可接石英/陶瓷谐振器,或者接外部时钟源,频率范围为4MHz~16MHz。

③、LSI是低速内部时钟,RC振荡器,频率为40kHz,提供低功耗时钟。

④、LSE是低速外部时钟,接频率为32.768kHz的石英晶体。

其中LSI是作为IWDGCLK(独立看门狗)时钟源和RTC时钟源而独立使用,HSI高速内部时钟 HSE高速外部时钟 PLL锁相环时钟这三个经过分频或者倍频作为系统时钟来使用基本时钟源(图中绿色箭头指出):(1)HSI高速内部时钟,RC振荡器,8MHz。

(2)HSE高速外部时钟,石英/陶瓷谐振器,8MHz。

(3)LSI低速内部时钟,RC振荡器,40kHz。

6.3 STM32F107VCT的时钟深入剖析(32M,40M,72M灵活切换)

2. 调试说明: 下载代码,并且按下【复位】键,在神舟 IV 号板上找到 LED2,可以看到该 LED1 灯一

亮一灭。

3. 关键代码: /*************** 程 序 总 共 2 部 分 之 第 1 部 分 时 钟 频 率 的 配 置 { 开 始 *********************************/

基于STM32F107VCT6微控制器的控制系统解决方案

基于STM32F107VCT6微控制器的控制系统解决方案 本文简要介绍了电动汽车交流充电桩的内容和研究现状。

针对需要设计了基于STM32F107VCT6微控制器的控制系统解决方案,并详细介绍了控制系统的软硬件设计和桩体的电气部分设计。

该系统提供包括人机交互、充电控制、电能计量、IC卡付费、票据打印、运行状态监测、充电保护和充电信息存储和上传等多种完善的功能,满足充电过程的要求。

随着全球能源危机的不断加深,石油资源的日趋枯竭以及大气污染、全球气温上升的危害加剧,各国政府及汽车企业普遍认识到节能和减排是未来汽车技术发展的方向,发展电动汽车将是解决这两个难题的最佳途径。

我国高度重视电动汽车的发展,国家相继出台了一系列标准来扶持和规范电动汽车的发展。

但要实现电动汽车大面积普及我国还有很长的路要走,需要解决的问题还有很多。

在最近发布的《节能与新能源汽车产业规划》草案中指出将以纯电动汽车作为主要战略取向。

有关专家指出纯电动汽车的发展存在三大瓶颈问题:一是标准的缺失,二是配套政策的不完善,三是基础设施的规划和建设的有序推进。

本文所研究的电动汽车交流充电桩作为充电基础设施的一部分对于推进电动汽车的普及具有重要的意义。

1 电动汽车交流充电桩介绍 交流充电桩,又称交流供电装置,是指固定在地面或墙壁,安装于公共建筑(办公楼宇、商场、公共停车场等)和居民小区停车场或充电站内,采用传导方式为具有车载充电机的电动汽车提供人机交互操作界面及交流充电接口,并具备相应测控保护功能的专用装置。

交流充电桩采用大屏幕LCD彩色触摸屏作为人机交互界面,可选择定电量、定时间、定金额、自动(充满为止)四种模式充电,具备运行状态监测、故障状态监测、充电分时计量、历史数据记录和存储等功能。

充电桩的交流工作电压(220±15%)V,额度输出电流(AC)为32 A(七芯插座),普通纯电动轿车用交流充电桩充满电大约需要6~8 h,充电桩更适用于慢速充电。

STM32F107VCT6 微控制器用户手册说明书

Open107V用户手册目录1. 硬件介绍 (2)1.1.资源简介 (2)2. 例程分析 (4)2.1. 8Ios (4)2.2. ADC+DMA (4)2.3. ADC+DMA+KEYPAD (5)2.4. CAN- Normal (5)2.5. DAC (6)2.6. ETH_LwIP (6)2.7. GPIO LED JOYSTICK (7)2.8. I2C (7)2.9. LCD (8)2.10. OneWire (9)2.11. PS2 (9)2.12. RTC (9)2.13. FATFS V0.08A-SD Card (10)2.14. SL811 USB (10)2.15. AT45DB-SPI (11)2.16. TouchPanel (11)2.17. uCOSII2.91+UCGUI3.90A (12)2.18. USART (13)2.19. USB_Host_HID_KBrd_Mouse (13)2.20. USB_ Host_MSC(efsl) (13)2.21. USB_Host_MSC(FATFS) (14)2.22. USB-JoyStickMouse (15)2.23. USB-Mass_Storage-MCU Flash (15)2.24. VS1003B (16)3. 版本修订 (16)1.硬件介绍1.1. 资源简介[ 芯片简介 ]1.STM32F107VCT6STM32功能强大,下面仅列出STM32F107VCT6的核心资源参数:内核:Cortex-M3 32-bit RISC;工作频率:72MHz,1.25 DMIPS/MHz;工作电压:2-3.6V;封装:LQFP100;I/O口:80;存储资源:256kB Flash,64kB RAM;接口资源:3 x SPI,3 x USART,2 x UART,2 x I2S,2 x I2C;1 x Ethernet MAC,1 x USB OTG,2 x CAN;模数转换:2 x AD(12位,1us,分时16通道),[ 其它器件简介 ]3."5V DC"或"USB"供电选择开关切换到上面,选择5V DC供电;切换到下面,选择USB供电。

STM32时钟详解

STM32中有一个全速功能的USB模块,其串行接口引擎需要一个频率为48MHz的时钟源。该时钟源只能从PLL输出端获 取,可以选择为1.5分频或者1分频,也就是,当需要使用USB模块时,PLL必须使能,并且时钟频率配置为48MHz或72MHz。

在以上的时钟输出中,有很多是带使能控制的,例如AHB总线时钟、内核时钟、各种APB1外设、APB2外设等等。当需要 使用某模块时,记得一定要先使能对应的时钟。

需要注意的是定时器的倍频器,当APB的分频为1时,它的倍频值为1,否则它的倍频值就为2。

连接在APB1(低速外设)上的设备有:电源接口、备份接口、CAN、USB、I2C1、I2C2、UART2、UART3、SPI2、窗口看门 狗、Timer2、Timer3、Timer4。注意USB模块虽然需要一个单独的48MHz时钟信号,但它应该不是供USB模块工作的时钟,而 只是提供给串行接口引擎(SIE)使用的时钟。USB模块工作的时钟应该是由APB1提供的。

同时这种设定也是有规律可循的设定参数也是有顺序规范的这是应用中应当注意的例如pll的设定需要在使能之前一旦pll使能后参数不可更经过此番设置后由于我的电路板上是8mhz晶振所以系统时钟为72mhz高速总线和低速总线2都为72mhz低速总线1为36mhzadc时钟为12mhzusb时钟经过15分频设置就可以实现48mhz的数据传输

static void RCC_Config(void)

第2页

STM32时钟讲解.txt {

/* 这里是重置了RCC的设置,类似寄存器复位 */ RCC_DeInit();

STM32F072从零配置工程-自定义时钟配置详解

STM32F072从零配置⼯程-⾃定义时钟配置详解从⾃⼰的板⼦STM32F407⼊⼿,参考官⽅的SystemInit()函数:核⼼在SetSysClock()这个函数,官⽅默认是采⽤HSE(设定为8MHz)作为PLL锁相环的输⼊输出168MHz的SYSCLK;/*** @brief Setup the microcontroller system* Initialize the Embedded Flash Interface, the PLL and update the* SystemFrequency variable.* @param None* @retval None*/void SystemInit(void){/* Reset the RCC clock configuration to the default reset state ------------*//* Set HSION bit */RCC->CR |= (uint32_t)0x00000001;/* Reset CFGR register */RCC->CFGR = 0x00000000;/* Reset HSEON, CSSON and PLLON bits */RCC->CR &= (uint32_t)0xFEF6FFFF;/* Reset PLLCFGR register */RCC->PLLCFGR = 0x24003010;/* Reset HSEBYP bit */RCC->CR &= (uint32_t)0xFFFBFFFF;/* Disable all interrupts */RCC->CIR = 0x00000000;/* Configure the System clock source, PLL Multiplier and Divider factors,AHB/APBx prescalers and Flash settings ----------------------------------*/SetSysClock();}这⾥⼤致分析⼀下官⽅默认的SetSysClock()配置:由于我个⼈采⽤的是STM32F407型号的芯⽚,因此精简⼀下函数;总体思路的话:使能HSE;等待HSE初始化完毕,进⾏下⼀步设置;设置HCLK、PCLK1、PCLK2的分频系数;配置PLL,使能PLL,等待PLL初始化完毕;选择PLL作为SYSCLK,等待SYSCLK时钟设置完毕;/*** @brief Configures the System clock source, PLL Multiplier and Divider factors,* AHB/APBx prescalers and Flash settings* @Note This function should be called only once the RCC clock configuration* is reset to the default reset state (done in SystemInit() function).* @param None* @retval None*/static void SetSysClock(void){/******************************************************************************//* PLL (clocked by HSE) used as System clock source *//******************************************************************************/__IO uint32_t StartUpCounter = 0, HSEStatus = 0;/* Enable HSE */RCC->CR |= ((uint32_t)RCC_CR_HSEON);/* Wait till HSE is ready and if Time out is reached exit */do{HSEStatus = RCC->CR & RCC_CR_HSERDY;StartUpCounter++;} while((HSEStatus == 0) && (StartUpCounter != HSE_STARTUP_TIMEOUT));if ((RCC->CR & RCC_CR_HSERDY) != RESET){else{HSEStatus = (uint32_t)0x00;}if (HSEStatus == (uint32_t)0x01){/* Select regulator voltage output Scale 1 mode */RCC->APB1ENR |= RCC_APB1ENR_PWREN;PWR->CR |= PWR_CR_VOS;/* HCLK = SYSCLK / 1*/RCC->CFGR |= RCC_CFGR_HPRE_DIV1;/* PCLK2 = HCLK / 2*/RCC->CFGR |= RCC_CFGR_PPRE2_DIV2;/* PCLK1 = HCLK / 4*/RCC->CFGR |= RCC_CFGR_PPRE1_DIV4;/* PCLK2 = HCLK / 1*/RCC->CFGR |= RCC_CFGR_PPRE2_DIV1;/* PCLK1 = HCLK / 2*/RCC->CFGR |= RCC_CFGR_PPRE1_DIV2;/* Configure the main PLL */RCC->PLLCFGR = PLL_M | (PLL_N << 6) | (((PLL_P >> 1) -1) << 16) |(RCC_PLLCFGR_PLLSRC_HSE) | (PLL_Q << 24);/* Enable the main PLL */RCC->CR |= RCC_CR_PLLON;/* Wait till the main PLL is ready */while((RCC->CR & RCC_CR_PLLRDY) == 0){}/* Configure Flash prefetch, Instruction cache, Data cache and wait state */FLASH->ACR = FLASH_ACR_PRFTEN | FLASH_ACR_ICEN |FLASH_ACR_DCEN |FLASH_ACR_LATENCY_5WS; /* Configure Flash prefetch, Instruction cache, Data cache and wait state */FLASH->ACR = FLASH_ACR_PRFTEN | FLASH_ACR_ICEN |FLASH_ACR_DCEN |FLASH_ACR_LATENCY_2WS; /* Select the main PLL as system clock source */RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_SW));RCC->CFGR |= RCC_CFGR_SW_PLL;/* Wait till the main PLL is used as system clock source */while ((RCC->CFGR & (uint32_t)RCC_CFGR_SWS ) != RCC_CFGR_SWS_PLL);{}}else{ /* If HSE fails to start-up, the application will have wrong clockconfiguration. User can add here some code to deal with this error */}}在官⽅的基础上,直接设定HSE作为SYSCLK时钟:初始化HSE;等待HSE初始化成功后再继续;设置调压器电压输出级别为1以便使器件在最⼤频率⼯作;设置HCLK、PCLK1、PCLK2分频系数;设置HSE作为系统时钟;void HSE_SetSysClock(void){__IO uint32_t HSEStartUpStatus = 0; /* 开启HSE时钟 */ /* 此函数从stm32f0xx_rcc.c获取,⽤于配置外部时钟HSE: * 有三个配置:RCC_HSE_OFF关闭外部HSE时钟 * RCC_HSE_ON开始外部HSE晶振 * RCC_HSE_Bypass开始HSE旁路设置 */ RCC_HSEConfig(RCC_HSE_ON); /* 若时钟配置成功 */if(HSEStartUpStatus == SUCCESS){RCC->APB1ENR |= RCC_APB1ENR_PWREN;PWR->CR |= PWR_CR_VOS;RCC_HCLKConfig(RCC_SYSCLK_Div1);RCC_PCLK2Config(RCC_HCLK_Div1);RCC_PCLK1Config(RCC_HCLK_Div1); /* 将SYSCLK系统时钟设置为HSE */RCC_SYSCLKConfig(RCC_SYSCLKSource_HSE); /* 等待SYSCLK系统时钟设置成功 */while(RCC_GetSYSCLKSource() != 0x04){}}else{while(1);}}使⽤HSI经过PLL配置系统时钟:使能HSI时钟;获取HSI状态并等待HSI稳定;设置调节器电压输出级别配置为1;设置HCLK、PCLK1/2分频系数;设置PLL时钟分频系数;使能PLL并等待PLL稳定后配置PLL状态;设置PLL作为SYSCLK时钟并等待设置完成;void HSI_SetSysClock(uint32_t m, uint32_t n, uint32_t p, uint32_t q) {__IO uint32_t HSIStartUpStatus = 0;/* 去初始化RCC */RCC_DeInit();/* 使能HSI时钟 */RCC_HSICmd(ENABLE);/* 从RCC的CR寄存器中获取HSI配置状态 */HSIStartUpStatus = RCC->CR & RCC_CR_HSIRDY;/* 若HSI配置成功 */if(HSIStartUpStatus == RCC_CR_HSIRDY){/* 配置调节器电压输出级别为1 */RCC->APB1ENR |= RCC_APB1ENR_PWREN;PWR->CR |= PWR_CR_VOS;/* 配置SYSCLK到HCLK的分频系数为1 */RCC_HCLKConfig(RCC_SYSCLK_Div1);/* 配置HCLK到PCLK1/2的分频系数为2/4 */RCC_PCLK2Config(RCC_HCLK_Div2);RCC_PCLK1Config(RCC_HCLK_Div4);/* 配置PLL参数,选⽤HSI作为PLL参数,同时使能PLL */RCC_PLLConfig(RCC_PLLSource_HSI, m, n, p, q);RCC_PLLCmd(ENABLE);/* 等待PLL设置完成 */while(RCC_GetFlagStatus(RCC_FLAG_PLLRDY) == RESET); FLASH->ACR = FLASH_ACR_PRFTEN| FLASH_ACR_ICEN| FLASH_ACR_DCEN| FLASH_ACR_LATENCY_5WS;RCC_SYSCLKConfig(RCC_SYSCLKSource_PLLCLK);while(RCC_GetSYSCLKSource() != 0x08);}else{while(1);}}HAL时钟配置分析:与STM32标准外设库不同,HAL库来实现时钟配置需要重新适应配置⽅式,但是本质的寄存器调动是类似不变的,且配置的过程也和STM32标准外设库相似;参考使⽤STMCube⽣成的代码,时钟树如图所⽰:在STM32Cube中设置:HSE设置为Crystal/Ceramic Resonator,Input Frequency设置为16MHz;在⼯程中要配置的参数:第⼀个HSE_VALUE参数位于stm32f0xx_hal_conf.h中,此参数与在STMCube时钟树上定义的⼀致,需要⼿动设置为实际的参数值;第⼆个HSE_VALUE参数位于system_stm32f0xx.c中,此参数默认为8MHz,可以通过⽤户程序来提供和调整;第三个SystemCoreClock参数位于system_stm32f0xx.c中,其默认值也是8MHz,可以根据以下三种⽅式来更新: 调⽤CMSIS函数SystemCoreClockUpdate()、 调⽤HAL API函数HAL_RCC_GetHCLKFreq()、 调⽤HAL_RCC_ClockConfig();/*** @brief Adjust the value of External High Speed oscillator (HSE) used in your application.* This value is used by the RCC HAL module to compute the system frequency* (when HSE is used as system clock source, directly or through the PLL).*/#if !defined (HSE_VALUE)#define HSE_VALUE ((uint32_t)16000000) /*!< Value of the External oscillator in Hz */#endif /* HSE_VALUE */#if !defined (HSE_VALUE)#define HSE_VALUE ((uint32_t)8000000)/*!< Default value of the External oscillator in Hz.This value can be provided and adapted by the user application. */#endif /* HSE_VALUE *//** @addtogroup STM32F0xx_System_Private_Variables* @{*//* This variable is updated in three ways:1) by calling CMSIS function SystemCoreClockUpdate()2) by calling HAL API function HAL_RCC_GetHCLKFreq()3) each time HAL_RCC_ClockConfig() is called to configure the system clock frequencyNote: If you use this function to configure the system clock there is no need to call the 2 first functions listed above, since SystemCoreClock variable is updated automatically.uint32_t SystemCoreClock = 8000000;实际的时钟配置函数如下图:使⽤了三个参数来配置:RCC_OscInitStruct⽤来配置外部时钟参数,这⾥设置晶振类型为HSE、设置HSE的状态为开启状态、不使⽤PLL;RCC_ClkInitStruct⽤来配置系统时钟内的参数(如Sys CLK、HCLK、PCLK1),这⾥设置要配置的时钟类型为HCLK、SYSCLK、PCLK1,选择HSE时钟作为SYSCLK的时钟源,并设置系统时钟SYSCLK分频系数为0、HCLK的分频系数为4;PeriphClkInit⽤来配置外设时钟的时钟源,这⾥设置USART1/2的时钟源为PCLK1;/*** @brief System Clock Configuration* @retval None*/void SystemClock_Config(void){RCC_OscInitTypeDef RCC_OscInitStruct = {0};RCC_ClkInitTypeDef RCC_ClkInitStruct = {0};RCC_PeriphCLKInitTypeDef PeriphClkInit = {0};/** Initializes the CPU, AHB and APB busses clocks*/RCC_OscInitStruct.OscillatorType = RCC_OSCILLATORTYPE_HSE;RCC_OscInitStruct.HSEState = RCC_HSE_ON;RCC_OscInitStruct.PLL.PLLState = RCC_PLL_NONE;if (HAL_RCC_OscConfig(&RCC_OscInitStruct) != HAL_OK){Error_Handler();}/** Initializes the CPU, AHB and APB busses clocks*/RCC_ClkInitStruct.ClockType = RCC_CLOCKTYPE_HCLK|RCC_CLOCKTYPE_SYSCLK|RCC_CLOCKTYPE_PCLK1;RCC_ClkInitStruct.SYSCLKSource = RCC_SYSCLKSOURCE_HSE;RCC_ClkInitStruct.AHBCLKDivider = RCC_SYSCLK_DIV1;RCC_ClkInitStruct.APB1CLKDivider = RCC_HCLK_DIV4;if (HAL_RCC_ClockConfig(&RCC_ClkInitStruct, FLASH_LATENCY_0) != HAL_OK){Error_Handler();}PeriphClkInit.PeriphClockSelection = RCC_PERIPHCLK_USART1|RCC_PERIPHCLK_USART2;art1ClockSelection = RCC_USART1CLKSOURCE_PCLK1;art2ClockSelection = RCC_USART2CLKSOURCE_PCLK1;if (HAL_RCCEx_PeriphCLKConfig(&PeriphClkInit) != HAL_OK){Error_Handler();}HAL_SYSTICK_Config(SystemCoreClock / 1000);HAL_SYSTICK_CLKSourceConfig(SYSTICK_CLKSOURCE_HCLK);HAL_NVIC_SetPriority(SysTick_IRQn, 0, 0);}这⾥加⼊了对SysTick的时钟配置,参考HAL库本⾝的设置:HAL_SYSTICK_Config()⽤来配置使能和配置SysTick寄存器;HAL_SYSTICK_CLKSourceConfig()选择AHB时钟(或AHB时钟除以8)作为SysTick时钟源;HAL_NVIC_SetPriority()配置SysTick_IRQn的中断优先级为0,默认为最⾼;。

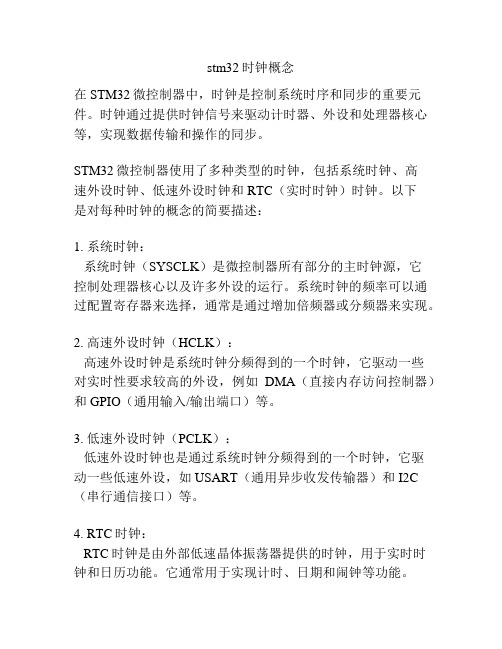

stm32时钟概念

stm32时钟概念

在STM32微控制器中,时钟是控制系统时序和同步的重要元件。

时钟通过提供时钟信号来驱动计时器、外设和处理器核心等,实现数据传输和操作的同步。

STM32微控制器使用了多种类型的时钟,包括系统时钟、高

速外设时钟、低速外设时钟和RTC(实时时钟)时钟。

以下

是对每种时钟的概念的简要描述:

1. 系统时钟:

系统时钟(SYSCLK)是微控制器所有部分的主时钟源,它

控制处理器核心以及许多外设的运行。

系统时钟的频率可以通过配置寄存器来选择,通常是通过增加倍频器或分频器来实现。

2. 高速外设时钟(HCLK):

高速外设时钟是系统时钟分频得到的一个时钟,它驱动一些

对实时性要求较高的外设,例如DMA(直接内存访问控制器)和GPIO(通用输入/输出端口)等。

3. 低速外设时钟(PCLK):

低速外设时钟也是通过系统时钟分频得到的一个时钟,它驱

动一些低速外设,如USART(通用异步收发传输器)和I2C (串行通信接口)等。

4. RTC时钟:

RTC时钟是由外部低速晶体振荡器提供的时钟,用于实时时钟和日历功能。

它通常用于实现计时、日期和闹钟等功能。

时钟源的选择和设置可以通过微控制器的时钟控制寄存器来完成,这些寄存器提供了配置时钟的选项。

根据具体的应用需求,可以选择不同的时钟源和频率来优化系统性能和功耗。

stm32时钟概念

stm32时钟概念摘要:1.STM32 时钟概念概述2.STM32 时钟的分类3.STM32 时钟的配置方法4.STM32 时钟的应用实例5.总结正文:一、STM32 时钟概念概述STM32 时钟是指基于STM32 单片机的实时时钟(Real-Time Clock,RTC)功能。

实时时钟功能是指单片机内部集成的一个用于提供时间信息的时钟,它可以提供年、月、日、星期、时、分、秒等时间信息。

STM32 时钟广泛应用于各种嵌入式系统中,如智能家居、自动控制、消费电子等领域。

二、STM32 时钟的分类STM32 时钟主要分为以下两类:1.RTC 时钟:RTC 时钟是STM32 单片机内部集成的实时时钟,它可以提供年、月、日、星期、时、分、秒等时间信息。

RTC 时钟可以通过实时时钟控制器(RTC)和实时时钟寄存器(RTC Register)进行配置和控制。

2.EXTI 时钟:EXTI 时钟是STM32 单片机外部中断时钟,它可以通过外部中断控制器(EXTI)进行配置和控制。

EXTI 时钟主要用于实现对外部事件的实时响应和处理,如按键、传感器等外部事件的检测。

三、STM32 时钟的配置方法STM32 时钟的配置方法主要包括以下几个步骤:1.配置RCC 时钟:RCC 时钟是STM32 单片机的核心时钟,它决定了单片机的工作频率。

在配置RCC 时钟时,需要根据实际应用需求选择合适的时钟源和倍频,以满足系统的性能要求。

2.配置RTC 时钟:配置RTC 时钟需要设置RTC 时钟控制器的控制和状态寄存器(RTCCSR),以启用RTC 时钟并设置其工作模式。

同时,还需要配置RTC 时钟寄存器(RTC Register),以设置年、月、日、星期、时、分、秒等时间信息。

3.配置EXTI 时钟:配置EXTI 时钟需要设置外部中断控制器的控制和状态寄存器(EXTICSR),以启用EXTI 时钟并设置其工作模式。

同时,还需要配置外部中断事件表(EXTIEVT),以定义外部中断事件的优先级和中断响应方式。

STM32神舟IV号(STM32F107VCT6)开发板-TIMER定时器中断实验--STM32_QQ群:101409705

神舟系列开发板资料之神舟IV号用户手册STM32开发板产品目录:神舟 I 号: STM32F103RBT6 (不带 TFT 触摸彩屏)神舟 I 号: STM32F103RBT6 + 2.4"TFT 触摸彩屏神舟 I 号: STM32F103RBT6 + 2.8"TFT 触摸彩屏神舟 II号: STM32F103VCT6 (不带 TFT 触摸彩屏)神舟 II号: STM32F103VCT6 + 2.8"TFT 触摸彩屏神舟 II号: STM32F103VCT6 + 3.2"TFT 触摸彩屏神舟III号: STM32F103ZET6 (不带 TFT 触摸彩屏)神舟III号: STM32F103ZET6 + 2.8"TFT 触摸彩屏神舟III号: STM32F103ZET6 + 3.2"TFT 触摸彩屏神舟 IV号: STM32F107VCT6 (不带 TFT 触摸彩屏)神舟 IV号: STM32F107VCT6 + 2.8"TFT 触摸彩屏神舟 IV号: STM32F107VCT6 + 3.2"TFT 触摸彩屏声明本手册版权归属所有, 并保留一切权利。

非经书面同意,任何单位或个人不得擅自摘录本手册部分或全部内容,违者我们将追究其法律责任。

本文档为网站推出的神舟IV号STM32开发板配套用户手册,详细介绍STM32芯片的开发过程和神舟IV号开发板的使用方法。

本文档如有升级恕不另行通知,欢迎您访问 论坛获取最新手册文档及最新固件代码。

目录1.第一章硬件篇 (13)1.1.神舟IV号STM32F107VCT开发板简介 (13)1.2.神舟IV号开发板硬件详解 (22)1.2.1.MCU处理器 (22)1.2.2.JTAG/SWD调试下载接口 (26)1.2.3.10M/100M以太网接口 (26)B 2.0 OTG电路 (31)1.2.5.触摸TFT彩屏接口 (34)1.2.6.音频解码电路 (34)1.2.7.SD卡接口 (35)1.2.8.315M无线模块接口 (35)1.2.9. 2.4G无线模块接口 (37)1.2.10.两组CAN总线接口 (37)1.2.11.RS232C串口 (38)1.2.12.485总线接口 (39)1.2.13.SPI FLASH (40)1.2.14.I2C EEPROM (40)1.2.15.蜂鸣器电路 (41)1.2.16.复位电路 (42)1.2.17.LED指示灯 (42)1.2.18.按键输入 (43)1.2.19.RTC实时时钟电路 (43)1.2.20.电位器AD电路 (43)1.2.21.AD、DA转换和PWM接口 (44)1.2.22.电源电路 (44)1.2.23.扩展接口 (45)2.第二章软件篇 (47)2.1.RVMDK简介 (47)2.2.新建RVMDK工程 (47)2.3.代码的编译 (54)2.4.在线仿真与程序下载 (56)2.5.神舟IV号实验例程结构 (58)2.6.RVMDK使用技巧 (61)2.6.1.快速定位函数/变量被定义的地方 (61)2.6.2.快速注释与快速消注释 (62)2.6.3.快速打开头文件 (63)3.第三章基本操作篇 (64)3.1.如何安装JLINK驱动程序 (64)3.2.如何使用JLINK仿真器软件 (66)3.2.1.如何使用J-FLASH ARM 烧写固件到芯片FLASH (66)3.2.2.使用J-Link command 设置和查看相关调试信息 (69)3.3.如何给神舟IV号板供电 (69)3.1.1.使用USB供电 (69)3.1.2.使用外接电源供电 (69)3.1.3.使用JLINK V8供电 (70)3.4.如何通过串口下载一个固件到神舟IV号开发板 (71)3.5.如何在MDK开发环境中使用JLINK在线调试 (74)3.6.神舟IV号跳线含义 (77)3.6.1.启动模式选择跳线 (78)3.6.2.RS-232/RS-485选择跳线 (78)3.6.3.RTC实时时钟跳线 (78)4.第四章实战篇 (79)4.1.LED跑马灯实验 (80)4.1.1.意义与作用 (80)4.1.2.硬件设计 (83)4.1.3.软件设计 (83)4.1.4.下载与验证 (87)4.2.按键实验 (89)4.2.1.意义与作用 (89)4.2.2.实验原理 (90)4.2.3.硬件设计 (90)4.2.4.软件设计 (91)4.2.5.下载与验证 (93)4.3.蜂鸣器实验 (94)4.3.1.意义与作用 (94)4.3.2.实验原理 (95)4.3.3.硬件设计 (96)4.3.4.软件设计 (97)4.3.5.下载与验证 (98)4.4.1.意义与作用 (100)4.4.2.实验原理 (101)4.4.3.硬件设计 (102)4.4.4.软件设计 (103)4.4.5.下载与验证 (108)4.5.串口输入输出验 (109)4.5.1.意义与作用 (110)4.5.2.实验原理 (111)4.5.3.硬件设计 (112)4.5.4.软件设计 (113)4.5.5.下载与验证 (115)4.6.S YS T ICK系统滴答实验 (115)4.6.1.意义与作用 (116)4.6.2.实验原理 (117)4.6.3.硬件设计 (118)4.6.4.软件设计 (119)4.6.5.下载与验证 (122)4.7.产品唯一身份标识(U NIQUE D EVICE ID)实验 (123)4.7.1.意义与作用 (124)4.7.2.实验原理 (125)4.7.3.硬件设计 (126)4.7.4.软件设计 (127)4.7.5.下载与验证 (129)4.8.ADC模数转换实验 (130)4.8.1.意义与作用 (131)4.8.2.实验原理 (132)4.8.3.硬件设计 (133)4.8.4.软件设计 (134)4.8.5.下载与验证 (137)4.9.C ALENDAR简单RTC实时时钟实验 (138)4.9.1.意义与作用 (139)4.9.2.实验原理 (140)4.9.3.硬件设计 (141)4.9.4.软件设计 (142)4.9.5.下载与验证 (145)4.10.C ALENDAR实时时钟与年月日实验 (146)4.10.2.实验原理 (148)4.10.3.硬件设计 (149)4.10.4.软件设计 (151)4.10.5.下载与验证 (154)4.11.EEPROM读写测试实验 (155)4.11.1.意义与作用 (156)4.11.2.实验原理 (157)4.11.3.硬件设计 (159)4.11.4.软件设计 (161)4.11.5.下载与验证 (163)4.12.TIMER定时器实验 (164)4.12.1.意义与作用 (165)4.12.2.实验原理 (166)4.12.3.硬件设计 (167)4.12.4.软件设计 (169)4.12.5.下载与验证 (172)4.13.EXTI外部中断实验 (173)4.13.1.意义与作用 (174)4.13.2.实验原理 (175)4.13.3.硬件设计 (176)4.13.4.软件设计 (178)4.13.5.下载与验证 (181)4.14.315M无线模块扫描实验 (182)4.14.1.意义与作用 (183)4.14.2.实验原理 (184)4.14.3.硬件设计 (185)4.14.4.软件设计 (186)4.14.5.下载与验证 (188)4.15.EXTI无线315M模块外部中断实验 (189)4.15.1.意义与作用 (190)4.15.2.实验原理 (191)4.15.3.硬件设计 (192)4.15.4.软件设计 (195)4.15.5.下载与验证 (197)4.16.TFT彩屏显示实验 (198)4.16.1.意义与作用 (199)4.16.3.硬件设计 (201)4.16.4.软件设计 (204)4.16.5.下载与验证 (207)4.17.TFT触摸屏显示加触摸实验 (208)4.17.1.意义与作用 (209)4.17.2.实验原理 (211)4.17.3.硬件设计 (213)4.17.4.软件设计 (216)4.17.5.下载与验证 (221)4.18.硬件CRC循环冗余检验实验 (224)4.18.1.意义与作用 (225)4.18.2.实验原理 (226)4.18.3.硬件设计 (227)4.18.4.软件设计 (228)4.18.5.下载与验证 (230)4.19.PVD电源电压监测实验 (231)4.19.1.意义与作用 (232)4.19.2.实验原理 (233)4.19.3.硬件设计 (234)4.19.4.软件设计 (235)4.19.5.下载与验证 (237)4.20.STANDBY待机模式实验 (238)4.20.1.意义与作用 (239)4.20.2.实验原理 (240)4.20.3.硬件设计 (241)4.20.4.软件设计 (242)4.20.5.下载与验证 (244)4.21.STOP停止模式实验 (245)4.21.1.意义与作用 (246)4.21.2.实验原理 (247)4.21.3.硬件设计 (248)4.21.4.软件设计 (249)4.21.5.下载与验证 (251)4.22.CAN总线回环实验 (252)4.22.1.意义与作用 (253)4.22.2.实验原理 (254)4.22.4.软件设计 (256)4.22.5.下载与验证 (259)4.23.双CAN收发测试实验 (260)4.23.1.意义与作用 (261)4.23.2.实验原理 (262)4.23.3.硬件设计 (263)4.23.4.软件设计 (264)4.23.5.下载与验证 (266)4.24.485总线收发实验 (266)4.24.1.意义与作用 (267)4.24.2.实验原理 (268)4.24.3.硬件设计 (269)4.24.4.软件设计 (270)4.24.5.下载与验证 (272)4.25.SPI存储器W25X16实验 (273)4.25.1.意义与作用 (274)4.25.2.实验原理 (275)4.25.3.硬件设计 (276)4.25.4.软件设计 (277)4.25.5.下载与验证 (279)4.26.SD卡实验实验 (280)4.26.1.意义与作用 (281)4.26.2.实验原理 (282)4.26.3.硬件设计 (283)4.26.4.软件设计 (284)4.26.5.下载与验证 (286)4.27.音乐播放器实验 (287)4.27.1.意义与作用 (288)4.27.2.实验原理 (289)4.27.3.硬件设计 (290)4.27.4.软件设计 (291)4.27.5.下载与验证 (293)4.28. 2.4G无线模块收发实验 (294)4.28.1.意义与作用 (295)4.28.2.实验原理 (296)4.28.3.硬件设计 (297)4.28.5.下载与验证 (300)B固件升级DFU实验 (301)4.29.1.意义与作用 (303)4.29.2.实验原理 (306)4.29.3.硬件设计 (310)4.29.4.软件设计 (314)4.29.5.下载与验证 (317)B实现SD读卡器实验 (320)4.30.1.意义与作用 (321)4.30.2.实验原理 (322)4.30.3.硬件设计 (323)4.30.4.软件设计 (324)4.30.5.下载与验证 (326)B人机交互设备实验 (327)4.31.1.意义与作用 (328)4.31.2.实验原理 (329)4.31.3.硬件设计 (332)4.31.4.软件设计 (334)4.31.5.下载与验证 (336)B实现虚拟串口实验 (337)4.32.1.意义与作用 (338)4.32.2.实验原理 (340)4.32.3.硬件设计 (342)4.32.4.软件设计 (344)4.32.5.下载与验证 (348)B实现PC音频播放器实验 (349)4.33.1.意义与作用 (350)4.33.2.实验原理 (352)4.33.3.硬件设计 (354)4.33.4.软件设计 (355)4.33.5.下载与验证 (358)4.34.以太网实现HTTP服务器实验 (359)4.34.1.意义与作用 (361)4.34.2.实验原理 (364)4.34.3.硬件设计 (367)4.34.4.软件设计 (371)4.35.以太网实现T ELNET服务器实验 (377)4.35.1.意义与作用 (378)4.35.2.实验原理 (380)4.35.3.硬件设计 (382)4.35.4.软件设计 (383)4.35.5.下载与验证 (385)4.36.以太网实现TFTP服务器实验 (386)4.36.1.意义与作用 (387)4.36.2.实验原理 (389)4.36.3.硬件设计 (394)4.36.4.软件设计 (395)4.36.5.下载与验证 (397)4.37.以太网实现固件升级实验 (400)4.37.1.意义与作用 (401)4.37.2.实验原理 (403)4.37.3.硬件设计 (407)4.37.4.软件设计 (409)4.37.5.下载与验证 (411)4.12.TIMER定时器中断实验4.12.1.意义与作用对于TIMER定时器大家应该不会陌生,51单片机内部就有定时器,作为高性能的STM32开发板自然少不了对其介绍。

STM32全部时钟概述

STM32时钟概述:

HSE:high speed external clock signal,高速外部时钟,最常用8M无源晶振,可以2分频或不分频,一般不分频,为8M。

HS I:high speed internal clock signal,高速内部时钟,8M,有温漂。

PLL时钟源:来源于HSE或者HSI/2,一般选HSE为时钟源。

PLLCLK时钟:通过设置PLL的倍频因子,对PLL时钟源进行倍频,倍频因子为:2-16。

一般设为9,则PLLCLK为72M。

(72M为官方推荐的稳定时钟源)。

SYSCLK:系统时钟,可来源于HSE、HSI、PLLCLK,一般设置SYSCLK=PLLCLK=72Mhz。

HCLK:AHB总线时钟(也有的说APB总线时钟),可分频,一般不分频,即HCLK=SYSCLK=72M。

PCLK2:APB2总线时钟,由HCLK经过APB2预分频器得到,一般1分频,PCLK2=HCLK=72M。

PCLK1:APB1总线时钟,由HCLK经过APB1预分频器得到,一般2分频,PCLK1=HCLK/2=36M。

RTC时钟:来源于HSE/128、LSE、LSI(一般40KHZ),独立的看门狗时钟由LSI提供。

MCO时钟输出:由PA8复用所得,可以对外提供时钟,可以检查所配置好的时钟(结合示波器使用),可来源于PLLCLK/2 SYSCLK HSE HSI。

STM32时钟配置方法详解

STM32时钟配置方法详解STM32是意法半导体(STMicroelectronics)公司推出的一系列32位Flash微控制器,被广泛应用于各种嵌入式系统中。

时钟是STM32微控制器的核心部分,正确配置时钟可以确保系统正常工作并达到预期的性能。

本文将详细介绍STM32时钟配置的方法。

1.时钟源:STM32微控制器提供了多个时钟源,包括内部时钟(HSI、LSI)和外部时钟(HSE、LSE)。

其中,HSI(高速内部时钟)是一个高频率(通常为8MHz)的内部RC振荡器,适用于低功耗应用;LSI(低速内部时钟)是一个低频率(通常为40kHz)的内部RC振荡器,用于RTC(实时时钟)模块;HSE(高速外部时钟)是一个外接的高频晶振,用于提供更精确的时钟信号;LSE(低速外部时钟)是一个外接的低频晶振,适用于RTC模块。

2.主频和系统时钟:主频是指CPU的时钟频率,系统时钟是指STM32微控制器的总线时钟,包括AHB(高性能总线)、APB1(低速外设总线)和APB2(高速外设总线)。

在进行STM32时钟配置之前,需要按照以下几个步骤来完成。

1.启用对应的时钟源:根据具体需求,选择合适的时钟源并启用相应的时钟。

可以通过设置RCC_CR寄存器和RCC_APB1ENR/RCC_APB2ENR寄存器来实现。

例如,要使用HSE作为时钟源,需要首先启用HSE时钟。

2.配置时钟分频器:为了使系统时钟不超过芯片规格要求的最大频率,需要对时钟进行分频。

分频器有两个,即AHB分频器和APB分频器。

可以通过设置RCC_CFGR寄存器来实现。

例如,将AHB分频器设置为8,将APB1和APB2分频器分别设置为4,可以将主频分别分频为8MHz、32MHz和64MHz。

3.等待时钟稳定:当启用外部时钟源时,需要等待时钟稳定。

可以通过读取RCC_CR寄存器的特定标志位来判断时钟是否稳定。

4. 配置Flash存储器的延时:根据主频的不同,需要设置Flash存储器的访问延时,以确保正常读写数据。

stm32时钟概念

stm32时钟概念摘要:一、STM32 时钟概念概述二、STM32 时钟的分类三、STM32 时钟的配置方法四、STM32 时钟的应用实例五、总结正文:一、STM32 时钟概念概述STM32 时钟是指基于STM32 单片机的时钟系统,能够为系统提供精确的时间基准。

STM32 时钟系统包括内部高速时钟(HSI)、内部高速时钟(HSE)、外部高速时钟(HSE)、实时时钟(RTC)等。

这些时钟可以为系统提供不同精度和功能的时间基准,以满足各种应用场景的需求。

二、STM32 时钟的分类1.内部高速时钟(HSI):内部高速时钟是STM32 单片机内部产生的高速时钟,其频率固定为高速晶振的频率,一般为8MHz。

2.内部高速时钟(HSE):内部高速时钟是STM32 单片机内部产生的高速时钟,其频率由用户通过编程设定,最高可达25MHz。

3.外部高速时钟(HSE):外部高速时钟是外部晶振产生的高速时钟,其频率由用户通过编程设定,最高可达50MHz。

4.实时时钟(RTC):实时时钟是STM32 单片机内部集成的实时时钟模块,能够提供年月日时分秒等精确时间信息。

三、STM32 时钟的配置方法1.内部高速时钟(HSI)的配置:内部高速时钟的配置较为简单,只需要在时钟配置函数中开启相应功能即可。

2.内部高速时钟(HSE)的配置:内部高速时钟的配置需要用户根据实际需求,在时钟配置函数中设置相应的频率和模式。

3.外部高速时钟(HSE)的配置:外部高速时钟的配置需要用户根据实际需求,在时钟配置函数中设置相应的频率和模式,并连接外部晶振。

4.实时时钟(RTC)的配置:实时时钟的配置需要用户根据实际需求,在时钟配置函数中开启相应功能,并设置相应的时间格式和校准方式。

四、STM32 时钟的应用实例1.基于实时时钟(RTC)的闹钟功能:通过配置实时时钟,可以使STM32 单片机在指定时间发出闹钟信号。

2.基于内部高速时钟(HSI)的定时器功能:通过配置内部高速时钟,可以实现基于时间的定时器功能,例如秒表、计时器等。

stm32几种时钟控制介绍,含原理图

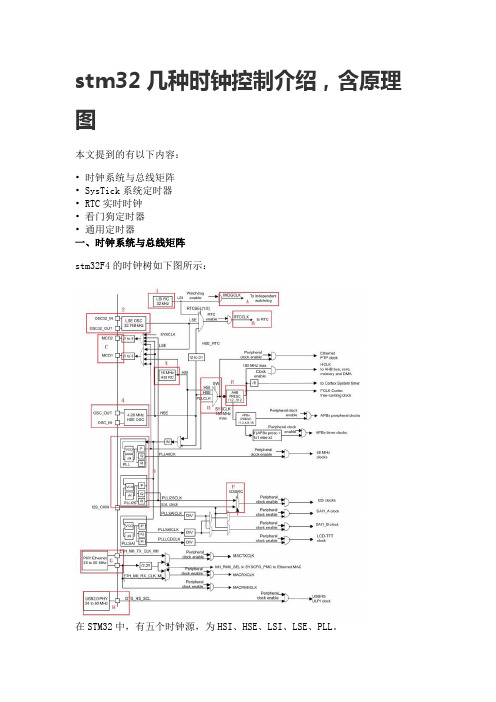

stm32几种时钟控制介绍,含原理图本文提到的有以下内容:• 时钟系统与总线矩阵• SysTick系统定时器• RTC实时时钟• 看门狗定时器• 通用定时器一、时钟系统与总线矩阵stm32F4的时钟树如下图所示:在STM32中,有五个时钟源,为HSI、HSE、LSI、LSE、PLL。

HSI是高速内部时钟,RC振荡器,频率为8MHz。

HSE是高速外部时钟,可接石英/陶瓷谐振器,或者接外部时钟源,频率范围为4MHz~16MHz。

LSI是低速内部时钟,RC振荡器,频率为40kHz。

LSE是低速外部时钟,接频率为32.768kHz的石英晶体。

PLL为锁相环倍频输出,其时钟输入源可选择为HSI/2、HSE或者HSE/2。

倍频可选择为2~16倍,但是其输出频率最大不得超过72MHz。

我们在学习51单片机的时候,其内部是没有晶振的,而stm32是有的。

stm32可以通过RCC(时钟控制寄存器)对时钟进行参数配置以及使能。

我们还可以通过修改system_stm32f4xx.c文件,来配置上述时钟树上的一些分频、倍频参数,得到理想的频率。

在单片机系统中,CPU和总线以及外设的时钟设置是非常重要的,因为没有时钟就没有时序,组合电路需要好好理解清楚。

我们先来看一下总线矩阵。

片上总线标准种类繁多,而由ARM公司推出的AMBA片上总线受到了广大IP开发商和SoC系统集成者的青睐,已成为一种流行的工业标准片上结构。

AMBA规范主要包括了AHB(Advanced High performance Bus)系统总线和APB(Advanced Peripheral Bus)外围总线。

二者分别适用于高速与相对低速设备的连接。

一般性的时钟设置需要先考虑系统时钟的来源,是内部RC还是外部晶振还是外部的振荡器,是否需要PLL。

然后考虑内部总线和外部总线,最后考虑外设的时钟信号。

遵从先倍频作为CPU时钟,然后在由内向外分频,下级迁就上级的原则。

基于STM32F107VC的 IEEE1588精密时钟同步分析与实现

基于STM32F107VC的 IEEE1588精密时钟同步分析与实现张小强;谢鹏程【期刊名称】《现代电子技术》【年(卷),期】2011(034)013【摘要】随着网络化与分布式系统的应用,对系统各节点间的时钟同步精度要求越来越高,尤其在分布式运动控制中,高精度时钟同步更是一切应用的基础.针对此问题,首先分析了IEEE 1588时钟同步的基本原理,并从理论上深入研究了影响时钟同步的关键因素,经过综合分析对比各实现方案的优劣,创新性提出了具有较高性价比的基于STM32F107VC的IEEE 1588实现方案,通过捕获硬件时间戳和校正频率漂移,在自定义协议中实现了低于300 ns的高精度时钟同步.%A higher precision of clock synchronization is needed with the development of network and distributed system, and especially the high-precision clock synchronization is the foundation of all applications in a distributed "motion control system. The basic principle of IEEE 1588 standard is introduced, and the key factors which affect the clock synchronization are studied theoretically. Through comparison of various methods, the best cost-effective implementation based on STM32F107VC microprocessor is decided, and the high precision clock synchronization below 300ns is realized by capturing hardware time stamp and adjusting frequency drift.【总页数】4页(P172-174,178)【作者】张小强;谢鹏程【作者单位】华南理工大学机械与汽车工程学院,广东广州 510640;华南理工大学机械与汽车工程学院,广东广州 510640【正文语种】中文【中图分类】TN911.7-34【相关文献】1.基于ARM的IEEE1588精密时钟同步协议的实现 [J], 孔亚广;孙祥祥2.基于ARM的IEEE1588精密时钟同步协议的实现 [J], 孔亚广;孙祥祥;3.基于ARM的IEEE1588精密时钟同步协议实现 [J], 王晋祺; 陈鸿4.IEEE1588精密时钟同步协议的实现探讨 [J], 董广玉5.IEEE1588精密时钟同步协议的分析与实现 [J], 庾智兰;李智因版权原因,仅展示原文概要,查看原文内容请购买。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

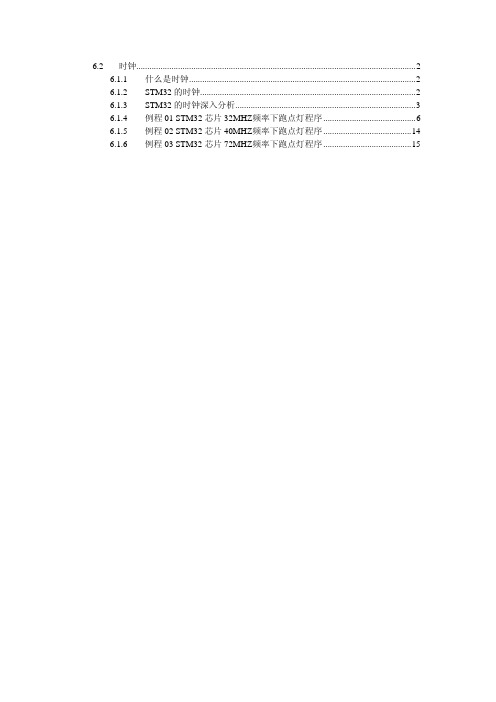

6.2 时钟...............................................................................................................................2 6.1.1 什么是时钟.......................................................................................................2 6.1.2 STM32 的时钟..................................................................................................2 6.1.3 STM32 的时钟深入分析..................................................................................3 6.1.4 例程 01 STM32 芯片 32MHZ频率下跑点灯程序 ..........................................6 6.1.5 例程 02 STM32 芯片 40MHZ频率下跑点灯程序 ........................................14 6.1.6 例程 03 STM32 芯片 72MHZ频率下跑点灯程序 ........................................15

晶振作为时钟源,则外设如 IO 口、定时器、串口等设备的驱动时钟速率便已经是固定的, 用户无法将此时钟速率更改,除非更换晶振。

而 STM32 微控制器的时钟树则是可配置的,其时钟输入源与最终达到外设处的时钟速 率不再有固定的关系,下面来详细解析 STM32 微控制器的时钟树。下图是 STM32 微控制 器的时钟树:

在认识这颗时钟树之前,首先要明确“主干”和最终的“分支”。假设使用外部 8MHz 晶振作为 STM32 的时钟输入源(这也是最常见的一种做法),则这个 8MHz 便是“主干”, 而“分支”很显然是最终的外部设备比如通用输入输出设备(GPIO)。这样可以轻易找出第 一条时钟的“脉络”: 3——5——7——21——8——9——11——13 对此条时钟路径做如下解析: 对于 3,首先是外部的 3-25MHz(前文已假设为 8MHz)输入; 对于 5,通过 PLL 选择位预先选择后续 PLL 分支的输入时钟(假设选择外部晶振); 对于 7,设置外部晶振的分频数(假设 1 分频); 对于 21,选择 PLL 倍频的时钟源(假设选择经过分频后的外部晶振时钟); 对于 8,设置 PLL 倍频数(假设 9 倍频); 对于 9,选择系统时钟源(假设选择经过 PLL 倍频所输出的时钟); 对于 11,设置 AHB 总线分频数(假设 1 分频); 对于 13,时钟到达 AHB 总线;

unsigned char sws = 0; RCC->CR |= 0X00010000; //使能外部高速时钟 HSEON while(!(RCC->CR>>17)); //将 RCC_CR 寄存器的值右移 17 位,等待 HSERDY 就绪, 即外部时钟就绪

RCC->CFGR2 |= 4<<4; // 5 分频

在上一章节中所介绍的 GPIO 外设属于 APB2 设备,即 GPIO 的时钟来源于 APB2 总线, 同样在上图中也可以寻获 GPIO 外设的时钟轨迹: 3——5——7——21——8——9——11——15——16 对于 3,首先是外部的 3-25MHz(前文已假设为 8MHz)输入; 对于 5, 通过 PLL 选择位预先选择后续 PLL 分支的输入时钟(假设选择外部晶振); 对于 7,设置外部晶振的分频数(假设 1 分频); 对于 21,选择 PLL 倍频的时钟源(假设选择经过分频后的外部晶振时钟); 对于 8,设置 PLL 倍频数(假设 9 倍频); 对于 9,选择系统时钟源(假设选择经过 PLL 倍频所输出的时钟); 对于 11,设置 AHB 总线分频数(假设 1 分频); 对于 15,设置 APB2 总线分频数(假设 1 分频) 对于 16,时钟到达 APB2 总线; 现在来计算一下 GPIO 设备的最大驱动时钟速率(各个条件已在上述要点中假设):

6.1.4 例程01 STM32芯片32MHZ频率下跑点灯程序

1. 示例简介 让点灯程序在时钟主频 32MHz 下面运行,LED 灯的正极接的是 3.3V 电源,所以我们编 程让 LED 负极拉低即 GPIO 引脚端口 D 的管脚 2 拉低,即 PD2 拉低,那么 LED 灯就会 变亮,相关电路图如下图所示:

3) 时钟到达 AHB 预分频器,由 11 知时钟经过 AHB 预分频器之后的速率仍为 72MHz。 4) 时钟到达 APB2 预分频器,由 15 经过 APB2 预分频器后速率仍为 72MHz。 5) 时钟到达 APB2 总线外设 上面是原理的剖析,如果再不明白的,可以接下来看例程代码,理论联系实践是最好的老师。

4. LSE 是低速外部时钟,接频率为 32.768kHz 的石英晶体,也可以被用来驱动 RTC,时钟 树的截图如下:

5. PLL 为锁相环倍频输出,其时钟输入源可选择为 HSI/2、HSE。倍频可选择为 4~9 倍, 但是其输出频率最大不得超过 72MHz,时钟树的截图如下:

6.1.3 STM32的时钟深入分析

RCC->CFGR2 |= 6<<8; / 1<<16; //PLL2 作为 PRED2V1 时钟 RCC->CR |= 1<<26; //将 PLL2 使能

while(!(RCC->CR>>27));

RCC->CFGR2 |= 0x00000004; //5 分频 RCC->CFGR |= 1<<16; //PREDIV1 作为 PLL 时钟 RCC->CFGR |= 2<<18; //本例程希望设置成 32MHZ 的工作频率,我们在这里尝试

下表是结合图表明出来的: 标号 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23

释义 内部低速振荡器(LSI,40Khz) 外部低速振荡器(LSE,32.768Khz) 外部高速振荡器(HSE,3-25MHz) 内部高速振荡器(HSI,8MHz) PLL输入选择位 RTC时钟选择位 PLL1分频数寄存器 PLL1倍频寄存器 系统时钟选择位 USB分频寄存器 AHB分频寄存器 APB1分频寄存器 AHB总线 APB1外设总线 APB2分频寄存器 APB2外设总线 ADC预分频寄存器 ADC外设 PLL2分频数寄存器 PLL2倍频寄存器 PLL 时钟源选择寄存器 独立看门狗设备 RTC 设备

一下

晶振是 8MHZ

//2 右移动 18 位,即 0010 使得 PLL 获得 4 倍频输出,外部

//乘以 4 就是 32MHZ 了 RCC->CFGR |= 1<<16; //PLLSRC 设置 78 成 1,使得 HSE 时钟作为 PLL 输入时钟 RCC->CR |= 1<<24; //将 PLL 使能

2. HSE 是高速外部时钟,可接石英/陶瓷谐振器,或者接外部时钟源,频率范围为 3MHz~25MHz,时钟树的截图如下:

3. LSI 是低速内部时钟,RC 振荡器,频率为 40kHz,可以用于驱动独立看门狗和通过程序 选择驱动 RTC(RTC 用于从停机/待机模式下自动唤醒系统),时钟树的截图如下:

//FLASH->ACR|=0x32;

while(!(RCC->CR>>25)); //监控寄存器 CR 的 PLLRDY 位,等待 PLL 时钟就绪

6.2 时钟

6.1.1 什么是时钟

从 CPU 的时钟说起。 计算机是一个十分复杂的电子设备。它由各种集成电路和电子器件组成,每一块集成电 路中都集成了数以万计的晶体管和其他电子元件。这样一个十分庞大的系统,要使它能够正 常地工作,就必须有一个指挥,对各部分的工作进行协调。各个元件的动作就是在这个指挥 下按不同的先后顺序完成自己的操作的,这个先后顺序我们称为时序。时序是计算机中一个 非常重要的概念,如果时序出现错误,就会使系统发生故障,甚至造成死机。那么是谁来产 生和控制这个操作时序呢?这就是“时钟”。“时钟”可以认为是计算机的“心脏”,如同人 一样,只有心脏在跳动,生命才能够继续。不要把计算机的“时钟”等同于普通的时钟,它 实际上是由晶体振荡器产生的连续脉冲波,这些脉冲波的幅度和频率是不变的,这种时钟信 号我们称为外部时钟。它们被送入 CPU 中,再形成 CPU 时钟。不同的 CPU,其外部时钟 和 CPU 时钟的关系是不同的,下表列出了几种不同 CPU 外部时钟和 CPU 时钟的关系。 CPU 时钟周期通常为节拍脉冲或T周期,它是处理操作的最基本的单位。 在微程序控制器中,时序信号比较简单,一般采用节拍电位——节拍脉冲二级体制。就 是说它只要一个节拍电位,在节拍电位又包含若干个节拍脉冲(时钟周期)。节拍电位表示 一个CPU周期的时间,而节拍脉冲把一个CPU周期划分为几个叫较小的时间间隔。根据 需要这些时间间隔可以相等,也可以不等。 指令周期是取出并执行一条指令的时间。 指令周期常常有若干个CPU周期,CPU周期也称为机器周期,由于CPU访问一次 内存所花费的时间较长,因此通常用内存中读取一个指令字的最短时间来规定CPU周期。 这就是说,这就是说一条指令取出阶段(通常为取指)需要一个CPU周期时间。而一个C PU周期时间又包含若干个时钟周期(通常为节拍脉冲或T周期,它是处理操作的最基本的 单位)。这些时钟周期的总和则规定了一个CPU周期的时间宽度。