数字电子技术基础 第三章.ppt

合集下载

《数字电子技术基础》教学课件第3章 组合逻辑电路

&

A

&

&Y

B

&

解 :1 ) 、根据逻辑图写输出逻辑表达式并化简

Y = AB •A • AB• B = AB • A + AB • B

= AA + B+ BA + B = AB + AB

2)、根据逻辑表达式列真值表

AB

Y

3)、由真值表分析逻辑功能

00

0

01

1

当AB相同时,输出为0

10

1

当AB相异时,输出为1 异或功能。 1 1

常用3线—8线译码器有74LS138

74LS138

逻辑符号(输出0有效):

S1 S2 S3

A2 A1 A0

它能将三位二进制数的每个代码分别译成低电平。 当控制端S1S2S3=100 时,译码器处工作状态, 译码器禁止时,所有输出端都输出无效电平(高电平)。

3、综合 1)同理,四位二进制译码器为4线—16线译码器

Y1 = A1 A0 = m1

Y2 = A1 A0 = m2

Y3 = A1 A0 = m3

5)常用集成2线—4线译码器

74LS139: 双2线—4线译码器

Y13Y12Y11Y10 Y23Y22Y21Y20 74LS139

S1 A11 A10 S2 A21 A20

2、三位二进制译码器

三位二进制译码器即3线—8线译码器, Y7 Y6 Y5 Y4 Y3 Y2 Y1 Y0

(3)化简。

得最简与—或表达式: L = AB + BC + AC (4)画出逻辑图。

如果,要求用与非门实现该逻辑电路, 就应将表达式转换成与非—与非表达式:

数字电子技术基础第三章

二、交流噪声容限

反相器对窄脉冲 的噪声容限—交 流噪声容限远高 于直流噪声容限。

交流噪声容限受 电源电压和负载 电容的影响。

图3.3.23 CMOS反相器的交流噪声容限

三、动态功耗

动态功耗:当CMOS 反相器从一种稳定工 作状态突然转变到另 一种稳定的过程中, 将产生附加的功耗。

PD=PC+PT PD为总动态功耗 PC为对负载电容充放

图3.3.xx CMOS三态门电路结构之三 可连接成总线结构。还能实现数据的双向传输。

3.3.6 CMOS电路的正确使用

一、输入电路的静电防护

1、在存储和运输CMOS器件时最好采用金属屏蔽层 作包装材料,避免产生静电。

2、组装、调试时,应使电烙铁和其他工具、仪表、 工作台面等良好接地。操作人员的服装、手套等选用 无静电的原料制作。

图3.5.34 OC门输出并联的接法及逻辑图

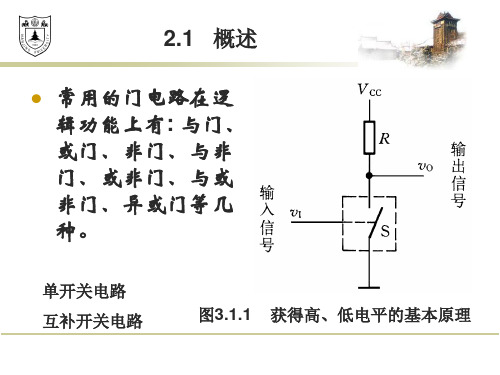

2.1 概述

常用的门电路在逻 辑功能上有: 与门、 或门、非门、与非 门、或非门、与或 非门、异或门等几 种。

单开关电路 互补开关电路

图3.1.1 获得高、低电平的基本原理

图3.1.2 正逻辑与负逻辑

一些概念

1、片上系统(SoC) 2、双极型TTL电路 3、CMOS

1961年美国TI公司,第一片数字集成电路 (Integrated Circuits, IC)。

C=1时 Vo=RL*Vi/(RL+RTG) RTG越小越好,并且希望不 受输入电压变化。

图3.3.39 CMOS模拟开关接 负载电阻的情况

四、三态输出的CMOS门电路

高阻态。 此电路结构 总是接在集 成电路的输 出端。

图3.3.40 CMOS三态门电路结构之一

数字电子技术基础3

3.4 常用的组合逻辑电路

主要内容:

编码器 译码器 多位加法器 数值比较器 数据选择器

通用性强、兼 容性好、功耗 小、工作稳定

可靠

组合逻辑电路

编码

用文字、符号或者数码表 示特定信息的过程称为编码。

编码器(即Encoder)

实现编码功能的电路

被编 信号

编 码 器

二进制编码器

编码器 二-十进制编码器

优先编码器

组合逻辑电路的逻辑功能特点:

没有存储和记忆作用。

组合电路的组成特点:

由门电路构成,不含记忆单元,只存在从输入到输 出的通路,没有反馈回路。

组合电路可以有一个或多个输入端,也可以有 一个或多个输出端

组合逻辑电路

组合逻辑电路的一般框图

Z1 f1( X1 , X2 ,Xn )

Z1 f1 ( X1 , X2 ,Xn )

00000100101

00000010110

00000001111

组合逻辑电路

54LS148优先编码器

被编码对象 选

通

ST IN 0 IN1 IN 2 IN 3 IN 4 IN 5 IN 6 IN 7

Y2

Y1

Y 0

Y EX YS

控 1 111 11

制 0 1 1 1 1 1 1 1 1 1 1 代1 码输1 出0 端

输

入

输出

I1 1 0 1 1

I2 1

0

对公I11N式3 个2I11n信4 号I115N进来行I116确编定I11码7 需时Y00要2,使应Y00用1按Y100

0 的1二进1制代1 码1的位1数n0. 1 0

101111011

原 码 输

0 1 1 0 1 1 1 1 0 0出

主要内容:

编码器 译码器 多位加法器 数值比较器 数据选择器

通用性强、兼 容性好、功耗 小、工作稳定

可靠

组合逻辑电路

编码

用文字、符号或者数码表 示特定信息的过程称为编码。

编码器(即Encoder)

实现编码功能的电路

被编 信号

编 码 器

二进制编码器

编码器 二-十进制编码器

优先编码器

组合逻辑电路的逻辑功能特点:

没有存储和记忆作用。

组合电路的组成特点:

由门电路构成,不含记忆单元,只存在从输入到输 出的通路,没有反馈回路。

组合电路可以有一个或多个输入端,也可以有 一个或多个输出端

组合逻辑电路

组合逻辑电路的一般框图

Z1 f1( X1 , X2 ,Xn )

Z1 f1 ( X1 , X2 ,Xn )

00000100101

00000010110

00000001111

组合逻辑电路

54LS148优先编码器

被编码对象 选

通

ST IN 0 IN1 IN 2 IN 3 IN 4 IN 5 IN 6 IN 7

Y2

Y1

Y 0

Y EX YS

控 1 111 11

制 0 1 1 1 1 1 1 1 1 1 1 代1 码输1 出0 端

输

入

输出

I1 1 0 1 1

I2 1

0

对公I11N式3 个2I11n信4 号I115N进来行I116确编定I11码7 需时Y00要2,使应Y00用1按Y100

0 的1二进1制代1 码1的位1数n0. 1 0

101111011

原 码 输

0 1 1 0 1 1 1 1 0 0出

数字电子技术基础-第三章--组合逻辑电路

三、静态冒险现象的消除方法

(一)加冗余项 (二)变换逻辑式,消去互补变量 (三)增加选通信号 (四)增加输出滤波电容 (五)引入封锁脉冲

四、动态冒险的定义

动态1冒险

动态0冒险

第四节 常用中规模集成组合逻辑模 块之一 编码器

一、普通编码器

(一)二进制普通编码器 例3-6 试设计一个4线-2线编码器电路,可将

(2)真值表见表所示,因为有4个输入变量, 所以真值表中共有16行,每行对应了一种变量取 值组合,根据题目中的叙述,其中12种变量取值 组合不会出现,所以视为无关项。

(二)二-十进制编码器——键控8421BCD码编码器

二、优先编码器

(一)优先编码器的定义与功能

例3-7 设计一个4线-2线优先编码器,任一时 刻必须有一个输入有效,但允许多个输入同时 有效。

解:(1)约定:输入为高电平有效,信息 有效用1表示,无效用0表示。4个信息分别 用I0、I1、I2、I3表示,2位代码用A1、A0表 示,且对应的关系为: I0的编码为00(左边 为A1、右边为A0), I1的编码为01(左边为 A1、右边为A0), I2的编码为10(左边为A1 、右边为A0),I3的编码为11(左边为A1 、 右边为A0 )。 I0 、 I1 、 I2 、 I3的优先级依 次升高。

第三节 组合逻辑电路中的竞争冒险

前面在分析和设计组合逻辑电路时,考虑的是输 入信号、输出信号已经处于稳定的逻辑电平的情 况,没有考虑输入变化瞬间的情况。为了保证系 统工作的可靠性,有必要再讨论当输入信号逻辑 电平发生变化的瞬间电路的工作情况。

由于门电路存在延迟时间,在输入变化的瞬间, 在电路的输出端口可能会出现与我们的预期不一 样的尖峰脉冲,我们称这种情况为电路出现了冒 险。

数字电子技术基础第三章逻辑门电路

ts 的大小是影响三极管速度的最主要因素,要提高三极 管的开关速度就要设法缩短ton与toff ,特别是要缩短ts 。

数字电子技术基础第三章逻辑门电路

第一节 常见元器件的开关特性

3.MOS管的开关特性

A、MOS管静态开关特性

在数字电路中,MOS管也是作为 开关元件使用,一般采用增强型的 MOS管组成开关电路,并由栅源电压 uGS控制MOS管的导通和截止。

时间。

toff = ts +tf 关断时间toff:从输入信号负跃变的瞬间,到iC 下降到 0.1ICmax所经历的时间。

数字电子技术基础第三章逻辑门电路

第一节 常见元器件的开关特性

2.三极管的开关特性

B、晶体三极管动态开关特性

ton和toff一般约在几十纳秒(ns=10-9 s)范围。通常都

有toff > ton,而且ts > tf 。

0 .3V 3 .6V 3 .6V

1V 5V

3 .6V

数字电子技术基础第三章逻辑门电路

第三节 TTL和CMOS集成逻辑门电路

1.TTL集成逻辑门电路

3 .6V 3 .6V 3 .6V

2.1V

0 .3V

数字电子技术基础第三章逻辑门电路

第三节 TTL和CMOS集成逻辑门电路

1.TTL集成逻辑门电路

数字电子技术基础第三章逻辑门电路

❖ 2.教学重点:不同元器件的静态开关特性,分立元件门电路 和组合门电路,TTL和CMOS集成逻辑门电路基本功能和电气特 性。

❖ 3.教学难点:组合逻辑门电路、TTL和CMOS集成逻辑门4.课时 安排: 第一节 常见元器件的开关特性 第二节 基本逻辑门电路 第三节 TTL和CMOS集成逻辑门电路

数字电子技术基础第三章逻辑门电路

第一节 常见元器件的开关特性

3.MOS管的开关特性

A、MOS管静态开关特性

在数字电路中,MOS管也是作为 开关元件使用,一般采用增强型的 MOS管组成开关电路,并由栅源电压 uGS控制MOS管的导通和截止。

时间。

toff = ts +tf 关断时间toff:从输入信号负跃变的瞬间,到iC 下降到 0.1ICmax所经历的时间。

数字电子技术基础第三章逻辑门电路

第一节 常见元器件的开关特性

2.三极管的开关特性

B、晶体三极管动态开关特性

ton和toff一般约在几十纳秒(ns=10-9 s)范围。通常都

有toff > ton,而且ts > tf 。

0 .3V 3 .6V 3 .6V

1V 5V

3 .6V

数字电子技术基础第三章逻辑门电路

第三节 TTL和CMOS集成逻辑门电路

1.TTL集成逻辑门电路

3 .6V 3 .6V 3 .6V

2.1V

0 .3V

数字电子技术基础第三章逻辑门电路

第三节 TTL和CMOS集成逻辑门电路

1.TTL集成逻辑门电路

数字电子技术基础第三章逻辑门电路

❖ 2.教学重点:不同元器件的静态开关特性,分立元件门电路 和组合门电路,TTL和CMOS集成逻辑门电路基本功能和电气特 性。

❖ 3.教学难点:组合逻辑门电路、TTL和CMOS集成逻辑门4.课时 安排: 第一节 常见元器件的开关特性 第二节 基本逻辑门电路 第三节 TTL和CMOS集成逻辑门电路

《数字电子技术基础》第3章.组合逻辑电路PPT课件

3.4 典型组合逻辑电路及其应用

3.4.3 数据选择器

示意图数据选择器 (multiplexer,MUX)又 称多路选择器或多路开关, 是应用比较广泛的中规模 组合逻辑电路,尤其是电 子设计自动化技术发展成 熟的今天。

图3.4.19 数据选择器

3.4 典型组合逻辑电路及其应用

1.典型数据选择器

1)双4选1数据选择器74153

3.2.2 冒险现象的判断

1.代数法

2.卡诺图法

3.2 组合逻辑电路中的竞争冒险与消除方法

3.2.3 冒险现象的消除方法

1.增加冗余项

2.输出接滤波电容

3.增加选通信号

3.3 VHDL的顺序行为

3.3.1 进程语句

进程本身是并行行为,且存在于结构体中。进程内 部的语句要进入进程之后才能顺序执行。进入进程是靠敏 感信号发生变化的时候,称此时为“激活”进程。若敏感 信号同时激活多个进程,进程是按并行行为执行的。进程 语句的一般形式如下:

(1)第2号不能与第7号同时配用。 (2)第3号和第6号必须同时配用。 (3)同时用第4、9号时,必须配用11号。

请设计一个逻辑电路,在违反上述任何一个规定时,发出 报警指示信号。

解:(1)设置11种化学试剂为输入信号,2对应A,7对应B, 3对应C,6对应D,4对应E,9对应F和11对应G。设置F1、F2和F3 分别为违反3种规定的输出。

<进程标号> :PROCESS<敏感信号表> <进程说明区> BEGIN <语句部分> WAIT ON<敏感信号表> ; UNTIL<条件表达式> ; WAIT FOR<时间表达式> ; END PROCESS;

《数字电子技术基础》第六版--门电路-1117省名师优质课赛课获奖课件市赛课一等奖课件

S

D

B

不论D、S间有无电压, 均无法导通,不能导电

第 章 门电路

3.3.1 MOS管旳开关特征 以N沟道增强型为例研究通电情况:

数字电子技术基础 第六版

2、添加垂直电压VGS

形成电场G—B,把衬底中旳电子吸引 到上表面,除复合外,剩余旳电子在 上表面形成了N型层(反型层)为D、 S间旳导通提供了通道。

VGS(th)称为阈值电压(开启电压)

第 章 门电路

数字电子技术基础 第六版

3.3.1 MOS管旳开关特征

MOS管输入特征和输出特征

① 输入特征:直流电流为0,看进去有一种输入电 容CI,对动态有影响。

② 输出特征: iD = f (VDS) 相应不同旳VGS下得一族曲线 。

第 章 门电路

3.3.1 MOS管旳开关特征 输出特征曲线(分三个区域)

第 章 门电路

3.2.2 二极管或门 二极管构成旳门电路旳缺陷

• 电平有偏移 • 带负载能力差

数字电子技术基础 第六版

• 只用于IC内部电路

第 章 门电路

集成门电路

数字电子技术基础 第六版

集成门电路

双极型 TTL (Transistor-Transistor Logic Integrated Circuit)

第 章 门电路

数字电子技术基础 第六版

3.3.2 CMOS反相器旳电路构造和工作原理 三、输入噪声容限

噪声容限--衡量门电路旳抗干扰能力。 噪声容限越大,表白电路抗干扰能力越强。

测试表白:CMOS电路噪声容限VNH=VNL=30%VDD,且 随VDD旳增长而加大。所以能够经过提升VDD来提升噪声容限

第 章 门电路

半导体基础知识(2)

数字电子技术基础(第3章) 组合逻辑分析与设计

第3章 组合逻辑设计

A B

&

Y

与非门的逻辑符号

L=A+B (2)或非运算:逻辑表达式为: Y A B

A 0 0 1 1 B Y 0 1 1 0 0 0 1 0 真值表

A B

≥1

Y

或非门的逻辑符号

第3章 组合逻辑设计

(3)异或运算:逻辑表达式为: Y

A 0 0 1 1 B Y 0 0 1 1 0 1 1 0 真值表

A

B F

A B

F

0 0 1 1

0 1 0 1

0 1 1 1

第3章 组合逻辑设计

功能表

开关 A 断开 断开 闭合 闭合 开关 B 断开 闭合 断开 闭合 灯Y 灭 亮 亮 亮

真值表

A 0 0 1 1

B 0 1 0 1

Y 0 1 1 1

逻辑符号 实现或逻辑的电 路称为或门。或 门的逻辑符号:

A B

≥1

第3章 组合逻辑设计

第3章 组合逻辑分析与设计

3.1 逻辑代数基础

3.2 逻辑函数的化简

3.3 组合逻辑电路的分析

3.4 组合逻辑电路的设计

3.5 VHDL硬件描述语言 3.6 基本组合逻辑电路的设计举例 3.7 组合逻辑电路中的竞争-险象

第3章 组合逻辑设计

3.1 逻辑代数基础

逻辑代数(Logic Algebra)是由英国数学家乔治· 布尔(George Boole)于1847年首先提出的,因此也称为

(A+B)(A+C)

第3章 组合逻辑设计

吸收率:

A ( A B) A B A A B A B

证明: A A B ( A A)(A B)

数字电子技术基础:第三章 逻辑门电路

逻辑符号

C

vI /vO

TG

vO /vI

C

C

υo/ υI

2. CMOS传输门电路的工作原理

vI /vO

5V到+5V

C

+5V

TP +5V vO /vI

5V TN

5V

C

设TP:|VTP|=2V, TN:VTN=2V

I的变化范围为-5V到+5V。

c=0=-5V, c =1=+5V

1)当c=0, c =1时 GSN= -5V (-5V到+5V)=(0到-10)V

在由于电路具有互补对称的性质,它的开通时间与关 闭时间是相等的。平均延迟时间:<10 ns。

动态功耗

CMOS反相器的PD与f和 2 VDD

CMOS反相器从一个稳定状态转变到另一个稳定状态时所产生的功耗

PD=PC+PT

分布电容CL充放电引起的功耗: PC CL fVD2D

CMOS管瞬时交替导通引起的功耗:PT CPD fVD2D

74标准系列 74LS系列

74AS系列

74LVC 74VAUC 低(超低)电压 速度更加快 与TTL兼容 负载能力强 抗干扰 功耗低

74ALS

3.1 概述

门电路:实现基本逻辑/复合逻辑运算的单元电路

逻辑状态的描述—— 正逻辑:高电平→1,低电平→0 负逻辑:高电平→0,低电平→1

缺点:功耗较大/速度较慢

VDD VIH(min) I OH(total) I IH(total)

… …

I0H(total) &1

+V DD RP

&

&1

IIH(total) &

数字电子技术基础第3章数字电子技术基础课件-PPT精品文档

(3-11)

3.1.2 组合电路的基本设计方法

组合逻辑功辑电路的设计是根据给定的实际逻辑问题, 求出实现其逻辑功能的逻辑电路。 一、设计方法 根据要求,设计出适合需要的组合逻辑电路应该遵循 的基本步骤,可以大致归纳如下: 1、进行逻辑抽象 ①分析设计要求,确定输入、输出信号及它们之间的 因果关系。 ②设定变量,即用英文字母表示有关输入、输出信号, 表示输入信号者称为输入变量,有时也简称为变量,表 示输出信号者称为输出变量,有时也称为输出函数或简 称函数。

数字电子技术基础

(3-1)

第3章 组合逻辑电路

(3-2)

第3章

3.1 3.2 3.3 3.4 3.5 3.6 3.7

组合逻辑电路

概述 组合电路的基本分析方法和设计方法 加法器和数值比较器 编码器和译码器 数据选择器和分配器 用中规模集成电路实现组合逻辑函数 只读存储器 组合电路中的竞争冒险

(3-3)

(Байду номын сангаас-5)

3.1 组合电路的基本分析方法和设计方法

3.1.1 组合电路的基本分析方法 所谓组合逻辑电路的分析,就是根据给定的逻辑电路 图,求出电路的逻辑功能。 给定组合逻辑电路 一、分析方法 ①根据给定的逻辑图写 出输出函数的逻辑表达式。 写输出逻辑表达式 ②化简逻辑表达式,求 出输出函数的最简与或表 达式。 化简 分析其功能 ③列出输出函数的真值 表。 分析其功能 ④描述电路的逻辑功能。 列出真值表

(3-6)

二、分析举例:

A

& & & & Y

B

1:组合逻辑电路如图, 试分析其逻辑功能。

解 :⑴ 、根据逻辑图写输出逻辑表达式并化简

Y AB A AB B AB A AB B AB ( A B ) ( A B )( A B ) A B A B

3.1.2 组合电路的基本设计方法

组合逻辑功辑电路的设计是根据给定的实际逻辑问题, 求出实现其逻辑功能的逻辑电路。 一、设计方法 根据要求,设计出适合需要的组合逻辑电路应该遵循 的基本步骤,可以大致归纳如下: 1、进行逻辑抽象 ①分析设计要求,确定输入、输出信号及它们之间的 因果关系。 ②设定变量,即用英文字母表示有关输入、输出信号, 表示输入信号者称为输入变量,有时也简称为变量,表 示输出信号者称为输出变量,有时也称为输出函数或简 称函数。

数字电子技术基础

(3-1)

第3章 组合逻辑电路

(3-2)

第3章

3.1 3.2 3.3 3.4 3.5 3.6 3.7

组合逻辑电路

概述 组合电路的基本分析方法和设计方法 加法器和数值比较器 编码器和译码器 数据选择器和分配器 用中规模集成电路实现组合逻辑函数 只读存储器 组合电路中的竞争冒险

(3-3)

(Байду номын сангаас-5)

3.1 组合电路的基本分析方法和设计方法

3.1.1 组合电路的基本分析方法 所谓组合逻辑电路的分析,就是根据给定的逻辑电路 图,求出电路的逻辑功能。 给定组合逻辑电路 一、分析方法 ①根据给定的逻辑图写 出输出函数的逻辑表达式。 写输出逻辑表达式 ②化简逻辑表达式,求 出输出函数的最简与或表 达式。 化简 分析其功能 ③列出输出函数的真值 表。 分析其功能 ④描述电路的逻辑功能。 列出真值表

(3-6)

二、分析举例:

A

& & & & Y

B

1:组合逻辑电路如图, 试分析其逻辑功能。

解 :⑴ 、根据逻辑图写输出逻辑表达式并化简

Y AB A AB B AB A AB B AB ( A B ) ( A B )( A B ) A B A B

数字电子技术基础 第3章 组合逻辑电路1PPT课件

2. 列真值表

3. 写输出表达式并化简

ABCY

YA B C A B CAC B ABC0 0 0 0 001 0

BC AB CAC B

010 0

B C A C AB 最简与或式 最简与非-与非式

011 1 100 0 101 1

YBC AC AB

110 1 111 1

BC AC AB

4. 画逻辑图 — 用与门和或门实现 YB C A C AB — 用与非门实现 YBC AC AB

统分析。

二、分析举例 [例] 分析图中所示电路的逻辑功能

A B

&

C

[解] 表达式

真值表

& ≥1 Y A B C Y A B C Y

000 1 100 0 001 0 101 0 010 0 110 0

011 0 111 1

YAB A C AB B C AB C C AB A C BC

ABC ABC

3. 列真值表

ABCD Y 0000 0 0001 1 0010 1 0011 0 0100 1 0101 0 0110 0 0111 1

ABCD Y 1000 1 1001 0 1010 0 1011 1 1100 0 1101 1 1110 1 1111 0

4. 功能说明: 当输入四位代码中 1 的个数为奇数时输出

第三章 组合逻辑电路

电子技术 数字电路部分

第三章

组合逻辑电路

第三章 组合逻辑电路

整体概况

+ 概况1

您的内容打在这里,或者通过复制您的文本后。

概况2

+ 您的内容打在这里,或者通过复制您的文本后。

概况3

+ 您的内容打在这里,或者通过复制您的文本后。

电子课件《数字电子技术》3第3章 组合逻辑电路

1

0

0

0

1

1

1

1

0

0

0

1

0

1

1

1

1

0

1

1

1

1

1

表3-14 例真值表

(3)根据真值表,直接画卡诺图进 行化简,如图3-16所示。

图3-16 例的卡诺图

(4)写出最简表达式,并根据设计要求变换为与非—与非表 达式

Y AC AB BC ABBC AC

(5)根据与非—与非表达式画出逻辑电路图,如图3-17所示。

解:

(1)图中输入变量为A,B,C,D,输出变量为Y,中间各级异 或门的输出分别设为Y0,Y1和Y2,逐级写出逻辑函数式

Y0 A B

YY12

Y0 Y1

C D

Y Y2

整理后可得Y的逻辑表达式 Y ABCD

A

B

C

D

L

(2)由于Y的逻辑表达

0

0

0

0

0

式不能再化简,所以直

0

0

0

1

1

0

0

1

0

如图3-12(a)所示为同或运算组合电路;图3-12(b)所 示为同或门逻辑符号。

(a)同或运算组合电路

(b)同或门逻辑符号

图3-12 同或门组合电路及逻辑符号

如表3-11所示为同或门的真值表。

A

B

L

0

0

1

0

1

0

1

0

0

1

1

1

3.2 组合逻辑电路的分析 方法和设计方法

3.2.1 组合逻辑电路的 分析方法

5.工艺设计

为了将逻辑电路实现为具体的电路装置,还需要做一系列 的工艺设计工作,包括设计印刷电路板、机箱、面板、电源、 显示电路、控制开关等。最后还必须完成组装、调试。

相关主题

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

时间内道童所消耗的 瞬时导通功耗

图3.3.24 CMOS反相器对负载电容的充、放电电流

三、动态功耗

图3.3.26 CMOS反相器的静态漏电流 (a) vI= 0 (b) vI=VDD

三、动态功耗

Pc

CL

fV

2 DD

PC: 负载电容充放电功耗 CL:负载电容 f=1/T为输入信号的重复频率 VDD: 电源电压

二、MOS管的输入特性和输出特 性

几个概念: 1) 截止区。 2) 可变电阻区 3)恒流区

图3.3. 2 MOS管共源接法及其输出特性曲线

(a)共源接法 (b)输出特性曲线

2

iD

I

DS

vGS VGS (th

)

1

图2.2.13 MOS管的转移特性

三、MOS管的基本开关电路

图3.3.4 MOS管的基本开关电路

图3.1.2 正逻辑与负逻辑

一些概念

1、片上系统(SoC) 2、双极型TTL电路 3、CMOS

1961年美国TI公司,第一片数字集成电路 (Integrated Circuits, IC)。

VLSI(Very Large Scale Integration)

3.2 半导体二极管门电路

VTH

图3.3.12 CMOS反相器的电压传输特性

图3.3.13 CMOS反相器的电流传输特性

三、输入端噪声容限

三、输入端噪声容限

图3.3.15 不同VDD下CMOS反相器的噪声容限

VDD 越高,噪声容限

越大

图3.3.15 CMOS反相器输入端噪声容限与VDD的关系

3.3.3 CMOS反相器的静态输入特 性和输出特性

交流噪声容限受 电源电压和负载 电容的影响。

图3.3.23 CMOS反相ቤተ መጻሕፍቲ ባይዱ的交流噪声容限

三、动态功耗

动态功耗:当CMOS 反相器从一种稳定工 作状态突然转变到另 一种稳定的过程中, 将产生附加的功耗。

PD=PC+PT PD为总动态功耗 PC为对负载电容充放

电所消耗的功率 PT为两个MOS管在短

图3.3.19 CMOS反相器的低电平输出特性

2. 高电平输出特性

图3.3.20 vO= VOH时CMOS反相器的工作状态

图3.3.21 CMOS反相器的高电平输出特性

3.3.4 CMOS反相器的动态特性

一、传输延迟时间tPHL、tPLH

传输延迟时间:输出电压变化落 后于输入电压变化的时间。

图3.2.4 二极管的动态电流波形

3.2.2 二极管与门

一般仅用作集成电路内 部的逻辑单元。

缺点: 1、输出的高、低电平数值和输 入的高、低电平数值不相等。 相差一个二极管的导通压降。 2、输出端对地接上负载电阻时, 负载电阻的改变有时会影响输 出的高电平。

3.2.3 二极管或门

存在输出偏移的问题。 只用于集成电路内部的逻辑单 元。 无法制作具有标准化输出电平 的集成电路。

基本概念: 1)夹断电压 2)电压极性

图3.3.9 N沟道耗尽型 MOS管的符号

图3.3.10 P沟道耗尽型 MOS管的符号

3.3.2 CMOS反相器的电路结构和 工作原理

一、CMOS反相器的电路结构

图2.6.1 CMOS反相器

(a)结构示意图

(b)电路图

二、电压传输特性和电流传输特性

基本概念:反相器 的阈值电压

例3.3.1 P91

PT

CPD

fV

2 DD

PT: 瞬时导通功耗 CPD:功耗电容,由制造商给出。

不是一个实际的电容。 f=1/T为输入信号的重复频率 VDD: 电源电压

3.3.5 其他类型的CMOS门电路

一、其他逻辑功能的 CMOS门电路

反相器、或非门、与非 门、或门、与或非门、 异或门等。

四、MOS管的开关等效电路

图3.3.5 MOS管的开关等效电路

(a)截止状态 (b)导通状态

五、MOS管的四种类型

1、N沟道增强型 2、P沟道增强型 3、 N沟道耗尽型 4、 P沟道耗尽型

图3.3.6 P沟道增强型MOS管

图3.3.7 P沟道增强型MOS管的漏极特性

图3.3. 8 用P沟道增强型MOS管接成的开关电路

一、输入特性

图3.3.16 CMOS反相器的输入保护电路 (a)CC4000系列的输入保护电路 (b)74HC系列的输入保护电路

图3.3.17 CMOS反相器的输入特性 (a)图3.3.17 (a)电路的输入特性 (b)图3.3.17 (b)电路的输入特性

二、输出特性

1、低电平输出特性

图3.3.18 vO= VOL时CMOS反相器的工作状态

3.2.1 半导体二极管 的开关特性

图3.2.1 二极管开关电路

可近似用PN结方程和下图所 示的伏安特性曲线来描述。

i Is ev/VT 1

其中:i为流过二极管的电流。 v为加到二极管两端的电压。

nkT VT q

图3.2.2 二极管的伏安特性

图3.2.3 二极管伏安特性的几种近似方法

数字电子技术基础 第三章 门电路

Pan Hongbing

VLSI Design Institute of Nanjing University

2.1 概述

常用的门电路在逻 辑功能上有: 与门、 或门、非门、与非 门、或非门、与或 非门、异或门等几 种。

单开关电路 互补开关电路

图3.1.1 获得高、低电平的基本原理

tPHL:输出由高电平跳变为低电 平的传输延迟时间。

tPLH:输出由低电平跳变为高电 平的传输延迟时间。

tPD: 经常用平均传输延迟时间tPD

来表示tPHL和tPLH(通常相等)

图3.3.22 CMOS反相器传输延迟 时间的定义

二、交流噪声容限

反相器对窄脉冲 的噪声容限—交 流噪声容限远高 于直流噪声容限。

3.3 CMOS门电路

3.3.1 MOS管的开关特性 在CMOS集成电路中,

以金属-氧化物-半导体场 效应晶体管(MetalOxide-Semiconductor Field-Effect Transistor, 简称MOS管)作为开关 器件。 一、MOS管的结构和工 作原理

图3.3.1 MOS管的结构和符号

图3.3.27 CMOS与非门

输入端增设反相器作 为缓冲器。

图3.3.29 带缓冲级的CMOS与非门电路

图3.3.28 CMOS或非门

图3.3.24 CMOS反相器对负载电容的充、放电电流

三、动态功耗

图3.3.26 CMOS反相器的静态漏电流 (a) vI= 0 (b) vI=VDD

三、动态功耗

Pc

CL

fV

2 DD

PC: 负载电容充放电功耗 CL:负载电容 f=1/T为输入信号的重复频率 VDD: 电源电压

二、MOS管的输入特性和输出特 性

几个概念: 1) 截止区。 2) 可变电阻区 3)恒流区

图3.3. 2 MOS管共源接法及其输出特性曲线

(a)共源接法 (b)输出特性曲线

2

iD

I

DS

vGS VGS (th

)

1

图2.2.13 MOS管的转移特性

三、MOS管的基本开关电路

图3.3.4 MOS管的基本开关电路

图3.1.2 正逻辑与负逻辑

一些概念

1、片上系统(SoC) 2、双极型TTL电路 3、CMOS

1961年美国TI公司,第一片数字集成电路 (Integrated Circuits, IC)。

VLSI(Very Large Scale Integration)

3.2 半导体二极管门电路

VTH

图3.3.12 CMOS反相器的电压传输特性

图3.3.13 CMOS反相器的电流传输特性

三、输入端噪声容限

三、输入端噪声容限

图3.3.15 不同VDD下CMOS反相器的噪声容限

VDD 越高,噪声容限

越大

图3.3.15 CMOS反相器输入端噪声容限与VDD的关系

3.3.3 CMOS反相器的静态输入特 性和输出特性

交流噪声容限受 电源电压和负载 电容的影响。

图3.3.23 CMOS反相ቤተ መጻሕፍቲ ባይዱ的交流噪声容限

三、动态功耗

动态功耗:当CMOS 反相器从一种稳定工 作状态突然转变到另 一种稳定的过程中, 将产生附加的功耗。

PD=PC+PT PD为总动态功耗 PC为对负载电容充放

电所消耗的功率 PT为两个MOS管在短

图3.3.19 CMOS反相器的低电平输出特性

2. 高电平输出特性

图3.3.20 vO= VOH时CMOS反相器的工作状态

图3.3.21 CMOS反相器的高电平输出特性

3.3.4 CMOS反相器的动态特性

一、传输延迟时间tPHL、tPLH

传输延迟时间:输出电压变化落 后于输入电压变化的时间。

图3.2.4 二极管的动态电流波形

3.2.2 二极管与门

一般仅用作集成电路内 部的逻辑单元。

缺点: 1、输出的高、低电平数值和输 入的高、低电平数值不相等。 相差一个二极管的导通压降。 2、输出端对地接上负载电阻时, 负载电阻的改变有时会影响输 出的高电平。

3.2.3 二极管或门

存在输出偏移的问题。 只用于集成电路内部的逻辑单 元。 无法制作具有标准化输出电平 的集成电路。

基本概念: 1)夹断电压 2)电压极性

图3.3.9 N沟道耗尽型 MOS管的符号

图3.3.10 P沟道耗尽型 MOS管的符号

3.3.2 CMOS反相器的电路结构和 工作原理

一、CMOS反相器的电路结构

图2.6.1 CMOS反相器

(a)结构示意图

(b)电路图

二、电压传输特性和电流传输特性

基本概念:反相器 的阈值电压

例3.3.1 P91

PT

CPD

fV

2 DD

PT: 瞬时导通功耗 CPD:功耗电容,由制造商给出。

不是一个实际的电容。 f=1/T为输入信号的重复频率 VDD: 电源电压

3.3.5 其他类型的CMOS门电路

一、其他逻辑功能的 CMOS门电路

反相器、或非门、与非 门、或门、与或非门、 异或门等。

四、MOS管的开关等效电路

图3.3.5 MOS管的开关等效电路

(a)截止状态 (b)导通状态

五、MOS管的四种类型

1、N沟道增强型 2、P沟道增强型 3、 N沟道耗尽型 4、 P沟道耗尽型

图3.3.6 P沟道增强型MOS管

图3.3.7 P沟道增强型MOS管的漏极特性

图3.3. 8 用P沟道增强型MOS管接成的开关电路

一、输入特性

图3.3.16 CMOS反相器的输入保护电路 (a)CC4000系列的输入保护电路 (b)74HC系列的输入保护电路

图3.3.17 CMOS反相器的输入特性 (a)图3.3.17 (a)电路的输入特性 (b)图3.3.17 (b)电路的输入特性

二、输出特性

1、低电平输出特性

图3.3.18 vO= VOL时CMOS反相器的工作状态

3.2.1 半导体二极管 的开关特性

图3.2.1 二极管开关电路

可近似用PN结方程和下图所 示的伏安特性曲线来描述。

i Is ev/VT 1

其中:i为流过二极管的电流。 v为加到二极管两端的电压。

nkT VT q

图3.2.2 二极管的伏安特性

图3.2.3 二极管伏安特性的几种近似方法

数字电子技术基础 第三章 门电路

Pan Hongbing

VLSI Design Institute of Nanjing University

2.1 概述

常用的门电路在逻 辑功能上有: 与门、 或门、非门、与非 门、或非门、与或 非门、异或门等几 种。

单开关电路 互补开关电路

图3.1.1 获得高、低电平的基本原理

tPHL:输出由高电平跳变为低电 平的传输延迟时间。

tPLH:输出由低电平跳变为高电 平的传输延迟时间。

tPD: 经常用平均传输延迟时间tPD

来表示tPHL和tPLH(通常相等)

图3.3.22 CMOS反相器传输延迟 时间的定义

二、交流噪声容限

反相器对窄脉冲 的噪声容限—交 流噪声容限远高 于直流噪声容限。

3.3 CMOS门电路

3.3.1 MOS管的开关特性 在CMOS集成电路中,

以金属-氧化物-半导体场 效应晶体管(MetalOxide-Semiconductor Field-Effect Transistor, 简称MOS管)作为开关 器件。 一、MOS管的结构和工 作原理

图3.3.1 MOS管的结构和符号

图3.3.27 CMOS与非门

输入端增设反相器作 为缓冲器。

图3.3.29 带缓冲级的CMOS与非门电路

图3.3.28 CMOS或非门