UART(串口)收发模块设计

单片机UART通信实现

单片机UART通信实现在单片机系统中,UART(通用异步收发器)通信是一种常见的串口通信方式。

通过UART通信,可以实现单片机与外部设备之间的数据传输。

本篇文章将介绍如何使用单片机实现UART通信,并提供相应的代码示例。

一、UART通信原理UART通信是一种串行通信方式,其中数据按照位的形式依次传输。

UART接口包括发送端和接收端,发送端将要传输的数据通过串行方式发送出去,接收端将接收到的数据按位恢复为原始数据。

通信的核心是波特率,即数据传输的速度。

发送端和接收端必须以相同的波特率进行通信,以确保数据的正确传输。

二、单片机UART通信的硬件连接实现单片机UART通信的关键是正确连接相应的硬件。

典型的单片机UART通信硬件连接如下:发送端:- 单片机的TX(发送)引脚连接到外部设备的RX(接收)引脚- 单片机的GND引脚连接到外部设备的GND引脚接收端:- 单片机的RX(接收)引脚连接到外部设备的TX(发送)引脚- 单片机的GND引脚连接到外部设备的GND引脚三、单片机UART通信的软件实现在软件方面,需要编写相应的代码来配置单片机的UART通信模块。

以下是一个示例代码,用于实现基本的UART通信功能。

```c#include <reg51.h>#define BAUDRATE 9600 // 波特率设置为9600bpsvoid uart_init(){TMOD = 0x20; // 设置定时器1为8位自动重装模式TH1 = -(256 - (11059200 / 12 / 32) / BAUDRATE); // 设置波特率TL1 = TH1; // 初始化定时器1的初值TR1 = 1; // 启动定时器1SCON = 0x50; // 标识为8位UART模式EA = 1; // 允许全局中断ES = 1; // 允许串口中断}void uart_send(unsigned char dat)SBUF = dat; // 将数据写入发送寄存器 while (!TI); // 等待发送完毕TI = 0; // 清除发送完成标志}unsigned char uart_receive(){while (!RI); // 等待接收完毕RI = 0; // 清除接收标志return SBUF; // 返回接收到的数据}void main(){unsigned char data;uart_init(); // 初始化UART通信模块 while (1)data = uart_receive(); // 接收数据uart_send(data); // 发送接收到的数据}}```以上代码是基于8051系列单片机的实现示例,具体的单片机型号和编程语言可能有所不同,但基本原理是相同的。

浅谈UART通信协议 UART接收数据时序设计

浅谈UART通信协议UART接收数据时序设计串口通信也是一个基础实验,是FPGA与电脑、单片机、DSP通信的一种最简单的方案,对通信速率要求不高时可以选择UART通信。

您可能已经知道UART时序的控制、波特率的配置等方面的内容,但在实际使用时还是会遇到一些问题,比如如何才能恰当的和其它模块进行衔接?为什么时序明明没问题,却无法和其它控制单元成功通信?本文致力于全面解析在设计UART通信时的思路方法。

UART通信协议UART通信的一帧一般由11到12位数据组成。

1bit的起始位,检测为低电平表示数据开始传输;紧接着8bits的数据;然后是1bit的奇偶校验位,可以是奇校验或者偶校验;最后是1bit或2bits的停止位,必须为高电平,表示一个字符数据的传输结束。

其中校验位是可选的,用来检验数据是否传输正确。

如果有校验位,则需要保证收发双方选择同样的一种检验方式。

奇校验就是保证数据中的1是奇数,比如如果8bit数据中有3bits的1,校验位置0;如果有4bits的1,校验位置1。

偶校验就是保证数据中的1是偶数。

波特率的配置波特率表示数据传输的速率,单位bps,表示位每秒。

比如9600bps就表示1s可以传输9600bits的数据。

异步收发没有时钟打拍来控制数据的传输,就需要保证收发双方在波特率设置上的一致。

确保接收数据的完整性。

程序中通常使用16倍速率对UART通信时序进行采样,则UART通信所需的时钟就是16*bps,如9600bps通信所需的驱动时钟大小就是16*9600=153.6kHz。

程序中可以使用一个计数器对系统时钟分频产生UART通信时钟。

// 分频生成UART通信时钟always @(posedge clk50 or negedge rst_n)if (!rst_n)beginclkout 《=1b0;。

uart串口发送和接受的程序的实现原理

UART串行端口传输和接收程序工作像繁忙的邮政办公室为你的数据!它遵循UART(UART)通用同步接收器、传输器(Transmitter)协议,其中数据以特定baud速率的节奏舞蹈比特发送,开始和停止比

特引导方向。

当您想要将数据发送到世界时,程序首先会设置带有正

确baud率和其他配置的UART模块,然后它会欢快地将您的数据丢

入传输缓冲器。

从那里,UART硬件接管,刷刷你的数据并发送出来在TX针,遵循所有的规则和设置你已经规定。

这就像一个精心编程的表演,与你的数据占据中心阶段!

基本上,UART模块总是在检查RX针上的任何线程数据。

一旦它检

测到一个起始位,它开始根据指定的baud速率抓取其余位。

在获得

包括开始和停止位数在内的整个数据包后,它会保存接收缓冲中的所

有数据。

程序可以从接收缓冲器中获取数据来查看里面有什么。

处理任何潜在的错误,如框架错误或等值错误,在接收过程中可能出现,

也是非常重要的。

UART串行端口传输和接收程序的实施遵循UART协议的原则和政策,促进设备之间的数据交换。

程序精心配置了UART模块,其中包含关于baud率,数据比特,stop比特,以及等价的具体参数,并认真遵

守了规定的准则。

随后,要传输的数据被有效存储并写入UART传输缓冲器。

接收后,从接收缓冲中勤勉地检索数据,确保UART模块准确处理并存储了iing数据。

通过坚持规定的UART协议和有条不紊地

配置UART模块,程序按照既定的政策和指令,有效建立了设备间连续免疫的可靠和安全的通道。

UART总线

UART (Universal Asynchronous Receiver/Transmitter)通用异步收发器UART是用于控制计算机与串行设备的芯片。

有一点要注意的是,它提供了RS-232C数据终端设备接口,这样计算机就可以和调制解调器或其它使用RS-232C接口的串行设备通信了。

作为接口的一部分,UART还提供以下功能:将由计算机内部传送过来的并行数据转换为输出的串行数据流。

将计算机外部来的串行数据转换为字节,供计算机内部使用并行数据的器件使用。

在输出的串行数据流中加入奇偶校验位,并对从外部接收的数据流进行奇偶校验。

在输出数据流中加入启停标记,并从接收数据流中删除启停标记。

处理由键盘或鼠标发出的中断信号(键盘和鼠票也是串行设备)。

可以处理计算机与外部串行设备的同步管理问题。

有一些比较高档的UART还提供输入输出数据的缓冲区,现在比较新的UART是16550,它可以在计算机需要处理数据前在其缓冲区内存储16字节数据,而通常的UART是8250。

现在如果您购买一个内置的调制解调器,此调制解调器内部通常就会有16550 UART。

1.UART协议的工作特点1.1数据采样UART协议是实现设备之间低速数据通信的标准协议。

因发送时不需同时发送时钟,故此协议为异步。

UART链接典型为38400,9600波特。

如下图1,UART字符格式为1个起始位,5~8个数据位,1个地址位或奇偶位(可选),1个停止位。

由于接收器、发送器异步工作,无需联接接收和发送时钟。

接收器采取对输入数据流高度采样方式,通常采样为16,并根据采样值确定位值。

按惯例,使用16个采样值的中间三个值。

1.2 UART帧区分UART一参数MAX-IDL,用来设置空闲字符的多少。

一旦一字符在线上被接收,UART 控制器开始计数接收到的空闲字符。

若下一数据字符接收前,一MAX-IDL多个空闲字符被接收,则产生空闲时间,缓冲区被关闭。

顺次对CPU32+核心发出一中断请求,要求从缓冲区接收数据。

串口通信UART模块基本介绍

串口通信UART模块基本介绍串口通信(UART)是一种通过串行接口进行数据传输的通信协议和硬件实现方式。

它是计算机和外设之间最常用的通信方式之一,也是嵌入式系统和单片机等小型设备中常用的通信方式。

UART通过串行方式传输数据,即通过单一的数据线一次只能传输一个bit位。

在串口通信中,通常需要两条线,一条用于发送数据(TX),一条用于接收数据(RX)。

UART通常通过一对相互连接的芯片实现,称为UART芯片或UART模块。

它包含一个发送器和一个接收器。

发送器将要发送的数据从并行格式转换为串行格式,并通过发送线路发送出去。

接收器则接收到的串行数据转换为并行格式以供系统使用。

UART芯片通常由硬件设计工程师在集成电路中设计和实现。

UART通信具有以下特点和优势:1.简单易用:UART通信是一种非常简单和易用的通信协议。

它的实现简单,适用于各种不同的应用场景。

2.可靠性高:UART通信使用的是硬件实现,不受软件的控制和干扰。

它具有较高的可靠性和稳定性。

3. 速度灵活可调:UART通信可以根据不同的应用需求进行速度调整。

通常,UART通信支持的波特率范围很大,可以从几十bps到多Mbps。

4.支持半双工和全双工通信:UART通信可以支持半双工和全双工两种通信方式。

在半双工模式下,发送和接收不能同时进行;而在全双工模式下,可以同时进行发送和接收。

5.通信距离远:UART通信使用串行线路进行数据传输,因此可以通过扩展串行线路的长度来实现较远距离的通信。

6.多种应用:UART通信广泛应用于各种设备和领域,如计算机、嵌入式系统、单片机、电子设备、通信设备等。

值得注意的是,UART通信只是一个物理层的通信协议,它只负责数据的传输,而不负责数据的解码和处理。

因此,在使用UART通信时,通常需要配合其他协议或编码方式,如RS-232、RS-485、Modbus等,来完成完整的通信过程。

总结来说,UART通信是一种简单、可靠、灵活的串行通信协议和硬件实现方式。

TTL,RS232,UART,485,远距离串口数传模块规格书介绍

大功率无线数传模块说明书2012年01月VER 3.0 A应用:特点:●无线远距离传感器●5000米传输距离(9600bps)●无线抄表●工作频率460 ~ 510MHz (1KHz步进)●机器人控制●16 个频道●自动化数据采集●RC2FSK 调制方式●工业遥测,遥控●高效循环交织纠错编码●远距离无线爆破●UART, RS232,RS485可任定制●小区楼宇自动化及安防●较短的通信时延●车辆管理●适合任意大小的数据量传输●长距离地磅●超高的频率稳定度●气象,遥感●看门狗监护,长期可靠运行技术咨询:284382376AD524X 系列大功率无线数传模块特点1、大功率发射,最大发射功率2W2、ISM 频段,无需申请频点,载频频段471.25MHz3、高抗干扰能力和低误码率基于GFSK 的调制方式,采用高效前向纠错信道编码技术,提高了数据抗突发干扰和随机干扰的能力。

4、小尺寸:52.5mm x 42mm(不含天线座及天线)注:去两个工艺边体积更可小到:52mm x 31.5mm。

AD524X 系列大功率无线数传模块技术指标ADF524X无线数传模块技术指标工作频率471.25MHz (0 频道)频道间隔100KHz发射功率2000mW接收灵敏度-120dBm@2400bps接口速率1200 - 9600bps接口效验方式8E1/8N1工作湿度10%~90%(无冷凝)工作温度-20℃ --- +75℃电源+3V —— 5.5V发射电流≦1400mA@4000mW (7V)接收电流≦ 38mA休眠电流≦ 10uA传输距离>6000m (开阔地可视距离,RF = 4800bps)尺寸52.5mm x 42.5/31.5mm(不含天线座及天线)AD524X模块引脚定义技术咨询:284382376共有8个接脚,具体定义如下表:AD524X无线数传模块引脚定义引脚定义说明1 GND 电源地2 VCC 电源 3.3V-5.5V3 CE 模块电源使能端,高或悬空使能,低休眠4 RXD URAT输入口5 TXD URAT输出口6 TX RS232 跟据用户要求可选7 RX RS232跟据用户要求可选8 SET 模块设置使能,低有效AD524X模块的参数设置:模块使用SET引脚接低后,可根据用户的需求设置不同的选项。

uart串口通信电路设计 -回复

uart串口通信电路设计-回复UART(通用异步收发传输)是一种常用的串口通信协议,可以实现设备之间的数据传输和通信。

在本文中,将详细介绍UART串口通信电路的设计步骤。

一、什么是UART串口通信电路?UART串口通信电路是一种数字电路,用于将串行数据转换为并行数据,实现设备之间的数据传输和通信。

UART串口通信电路通常由发送电路和接收电路两部分组成。

发送电路:发送电路将并行数据转换为串行数据,并对数据进行格式化。

它通常由一个发送缓冲器、一个发送时钟和控制逻辑组成。

接收电路:接收电路将串行数据转换为并行数据,并对数据进行解码和处理。

它通常由一个接收缓冲器、一个接收时钟和控制逻辑组成。

二、UART串口通信电路的设计步骤1. 确定通信参数在设计UART串口通信电路之前,首先需要确定通信参数,包括波特率、数据位数、校验位数和停止位数等。

这些参数将决定串口通信的速率和精度。

2. 设计发送电路发送电路的主要任务是将并行数据转换为串行数据,并将数据发送到接收设备。

设计发送电路时,需要考虑以下几点:(1)发送缓冲器:发送缓冲器用于存储待发送的数据。

它通常由一个FIFO (先进先出)缓冲器实现,可以提高通信的效率。

(2)时钟和控制逻辑:发送电路需要一个时钟信号来同步数据传输,并且需要控制逻辑来控制数据的发送和处理。

(3)格式化:发送电路需要对数据进行格式化,包括数据位、校验位和停止位的配置。

格式化的目的是提高数据的准确性和可靠性。

3. 设计接收电路接收电路的主要任务是将串行数据转换为并行数据,并将数据传输到接收设备。

设计接收电路时,需要考虑以下几点:(1)接收缓冲器:接收缓冲器用于存储接收到的数据。

它通常由一个FIFO 缓冲器实现,可以提高数据的接收效率。

(2)时钟和控制逻辑:接收电路需要一个时钟信号来同步数据传输,并且需要控制逻辑来控制数据的接收和处理。

(3)解码和处理:接收电路需要对接收到的数据进行解码和处理,包括校验数据的正确性和提取有效数据。

uart通信的详细讲解

uart通信的详细讲解UART(Universal Asynchronous Receiver/Transmitter)是一种常见的串行通信协议,常用于将数据传输至微控制器、传感器、无线模块等外部设备。

它是一种异步通信方式,意味着数据是以字节为单位发送和接收的,并且在数据发送和接收之间没有时钟信号进行同步。

下面将详细介绍UART通信的原理和工作流程。

UART通信基于一对输入输出引脚,其中TX(发送)和RX(接收)引脚分别用于数据的发送和接收。

通过这对引脚,数据可以以位的形式在串行总线上传输。

TX引脚用于将数据发送给接收方,RX引脚用于接收从发送方发送的数据。

在UART通信中,发送方和接收方之间需要事先约定好一些通信参数,包括波特率(通信速率),数据位宽,校验位和停止位。

通信起始阶段,发送方将要发送的数据从最高有效位(MSB)开始依次发送到TX引脚上。

UART通信是异步的,没有外部时钟信号作为同步信号,因此发送方和接收方之间需要通过提前约定的波特率来进行同步。

波特率表示每秒传输的位数,通常以波特(baud)为单位进行衡量。

在发送数据前,发送方需要先发送一个起始位(通常为逻辑低电平)来通知接收方数据的到来。

然后连续发送数据的位数。

发送方还可以选择在数据位之后发送一位校验位来增强数据的可靠性。

最后,发送方发送一个或多个停止位(通常为逻辑高电平)来标志数据的结束。

接收方在接收数据时,根据约定好的波特率等参数从RX引脚接收数据。

接收方在接收到起始位时开始接收数据,并按照波特率计时以正确的速率接收数据位。

在接收数据后,接收方还可以验证校验位的正确性。

如果校验位不匹配,接收方可以丢弃接收到的数据或者发生错误的数据信号。

最后,接收方等待一个或多个停止位来表示数据的结束。

UART通信的数据传输速率受到波特率的限制,快速的数据通信需要更高的波特率。

波特率的选择要根据通信双方的要求和硬件性能来确定。

总之,UART通信是一种简单、低成本的串行通信方式,用于将数据以位的形式在发送方和接收方之间传输。

UART控制器设计

UART控制器设计UART(通用异步收发传输)控制器是一种常见的串行通信接口,它被广泛应用于微控制器、传感器、通信模块等电子设备中。

UART控制器通过将并行数据转换为串行数据进行传输,实现了设备之间的串行通信。

本文将对UART控制器的设计进行详细介绍,包括其工作原理、主要功能、硬件设计和软件设计。

一、工作原理:1.发送数据时,UART控制器将要发送的数据按照指定格式进行编码,包括起始位、数据位、校验位和停止位等。

2.编码后的数据通过串口线发送至接收设备。

3.接收设备接收到数据后,解码数据,恢复为原始的并行数据。

二、主要功能:1.数据发送:用户通过将待发送的数据写入发送缓冲区,UART控制器将缓冲区中的数据按照指定格式进行编码,并通过串口线发送至接收设备。

2.数据接收:UART控制器从接收缓冲区中获取接收到的数据,并将其解码,恢复为原始的并行数据,供用户使用。

三、硬件设计:1.时钟控制:UART控制器需要一个时钟源,用来同步发送和接收数据。

时钟源可以是外部晶体振荡器或者其他可靠的时钟信号。

2.发送电路:发送电路包括发送缓冲区、发送数据编码器和串口线驱动电路。

发送缓冲区用来存储待发送的数据,发送数据编码器将待发送的数据按照指定格式进行编码,串口线驱动电路将编码后的数据通过串口线发送至接收设备。

3.接收电路:接收电路包括接收缓冲区、接收数据解码器和串口线接收电路。

接收缓冲区用来存储接收到的数据,接收数据解码器将接收到的数据解码,并恢复为原始的并行数据,供用户使用。

串口线接收电路用来接收串口线上的数据,并将其输入到接收缓冲区。

四、软件设计:1.数据的发送和接收:用户可以通过写入发送缓冲区实现数据的发送,也可以通过读取接收缓冲区实现数据的接收。

发送数据编码器和接收数据解码器的设置需要在软件中进行。

2.中断处理:UART控制器可以使用中断机制进行数据的发送和接收。

在发送和接收缓冲区有数据时,可以产生相应的中断请求,软件在中断服务程序中进行数据的发送和接收。

【总线】UART、Modbus、I2C、SPI、RS232、RS485及串口通讯常用参数

【总线】UART、Modbus、I2C、SPI、RS232、RS485及串⼝通讯常⽤参数⼀、UART异步收发传输,作为集成于微处理器中的周边设备,把并⾏输⼊信号转成串⾏输出信号,(⼀般是RS-232C规格的,与类似Maxim的MAX232之类的标准信号幅度变换芯⽚进⾏搭配)作为连接外部设备的接⼝。

该总线双向通信,可以实现全双⼯传输和接收。

在嵌⼊式设计中,UART⽤于主机与辅助设备通信,如与PC机通信包括与监控调试器和其它器件,如EEPROM通信。

⼀个字符接着⼀个字符传输,⼀个字符的信息由起始位、数据位、奇偶校验位和停⽌位组成。

传输时低位在前⾼位在后。

发送端和接收端必须按照相同的字节帧格式和波特率进⾏通信。

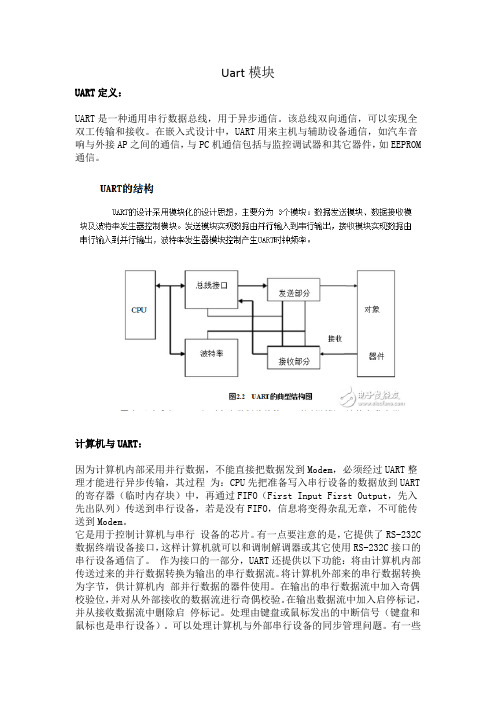

UART的设计采⽤模块化的设计思想,主要分为 3个模块:数据发送模块、数据接收模块及波特率发⽣器控制模块。

发送模块实现数据由并⾏输⼊到串⾏输出,接收模块实现数据由串⾏输⼊到并⾏输出,波特率发⽣器模块控制产⽣UART时钟频率。

发送逻辑对从发送FIFO读取的数据执⾏“并→串”转换。

控制逻辑输出起始位在先的串⾏位流,并且根据控制寄存器中已编程的配置,后⾯紧跟着数据位(注意:最低位 LSB 先输出)、奇偶校验位和停⽌位。

在检测到⼀个有效的起始脉冲后,接收逻辑对接收到的位流执⾏“串→并”转换。

此外还会对溢出错误、奇偶校验错误、帧错误和线中⽌(line-break)错误进⾏检测,并将检测到的状态附加到被写⼊接收FIFO的数据中。

需要两根信号线和⼀根地线。

⼆、Modbus1、ASCII模式与RTU模式的区别(1)ASCII:消息中每个ASCII字符都是⼀个⼗六进制字符组成(2)RTU:消息中每个8位域都是两个⼗六进制字符组成在同样波特率下,RTU可⽐ASCII⽅式传输更多的数据三、RS232、RS485(1)RS232RS232接⼝可以实现点对点的通信⽅式,但这种⽅式不能实现联⽹功能。

个⼈计算机上的通讯接⼝之⼀,异步传输标准接⼝。

串口通信功能模块深入剖析

串口通信功能模块深入剖析导言在嵌入式开发领域,串口通信是一种常见的通信方式。

串口通信通过发送和接收数据来实现设备之间的数据交换。

本文将对串口通信功能模块进行深入剖析,探讨其原理和应用。

什么是串口通信功能模块串口通信功能模块是一种嵌入式系统中的硬件或软件模块,用于实现串口通信。

一般而言,串口通信功能模块包括串口收发器、波特率发生器、缓冲区和相关的控制逻辑等组成部分。

串口收发器串口收发器是串口通信功能模块的主要组成部分之一。

它负责将串行数据转换为并行数据,并将并行数据转换为串行数据。

通常,串口收发器采用一种称为UART(Universal Asynchronous Receiver/Transmitter)的协议。

波特率发生器波特率发生器是用来控制串口通信中数据传输速率的关键模块。

它根据预设的波特率值来生成时钟信号,用于串口收发器进行数据的传输。

波特率发生器通常是由硬件电路实现的。

缓冲区为了提高串口通信的效率,串口通信功能模块通常会设置缓冲区。

缓冲区用于存储待发送或接收的数据,当数据量较大时,可以通过缓冲区进行批量处理,提高通信速度。

控制逻辑串口通信功能模块还包括一些控制逻辑,用于控制串口通信的各个环节,如数据的发送和接收、缓冲区的管理等。

控制逻辑通常由软件实现,可以根据具体需求进行配置和修改。

串口通信的原理在串口通信中,数据是以字节的形式进行传输的。

每个字节包含起始位、数据位、校验位和停止位。

起始位由逻辑0表示,用于标识一个数据传输的开始;数据位用于存储要传输的数据;校验位用于检测传输数据的正确性;停止位由逻辑1表示,用于标识一个数据传输的结束。

串口通信使用的是异步通信方式,即发送方和接收方的时钟信号不同步。

在发送数据时,发送方根据预设的波特率向接收方发送数据位、校验位和停止位。

接收方根据起始位的边沿信号来同步时钟,并按照设定的数据位数进行数据的接收。

串口通信的应用串口通信在众多嵌入式系统中被广泛应用,如单片机、工控设备、智能家居等。

嵌入式系统_UART

备,从而让两者的电平实现兼容,在嵌入式系统中,这种物理连接方式常见于嵌

入式系统与PC之间的连接,其原理图如图4.3所示。

电平转换

TxD

TxD

LPC2214

PC

RxD

RxD

图4.3 UART设备间的电平转换物理连接 这种物理连接方式主要应用与电平无法兼容的设备之间的通信。LPC2214 的串口电平是TTL电平,逻辑1为高电平为不低于3.0V,逻辑0为低电平不高于 0.5V。而PC的串口使用的RS232电平,其逻辑1为负电平(-3~-15V),逻辑0 为正电平(3~15V)。显然,这两者之间的电平不能相互兼容。为了让两者能顺 利通信,在两者之间的物理线路上加入了一个电平转换单元,目的是实现TTL电 平和RS232电平之间的变换。 试验板与PC之间的连接是通过USB转换成的串口来实现的,其框图如图4.4 所示。

4.2所示。

UxLCR 的位 功能

描述

00:5 位字符长度

1:0

数据长度选择 01:6 位字符长度 10:7 位字符长度

11:8 位字符长度

0:1 个停止位

2

停止位选择

1:2 个停止位(如果 U0LCR[1:0]=00 则

为 1.5)

3

校验允许

0:禁止奇偶产生和校验 1:使能奇偶产生和校验

00:奇数

在设定了通信速度之后,还需要进行通信格式的设置,所谓通信格式,指的

是在通信过程数据传输的先后和如何启动、结束一次传输。只有通信格式相同的

收发双方才能实现成功通信。在LPC2214中,通信格式是通过UxLCR(UART

Line Control Register,线控制寄存器)来控制的,该寄存器的内容如表

许为0 的。波特率时钟必须是波特率的16倍,波特率计算公式如下:

实验二 UART串口通信实验

实验二UART串口通信实验一、实验目的:1、了解S3C2410X处理器UART相关控制寄存器的使用;2、熟悉ARM处理器系统硬件电路中UART接口的设计方法;3、掌握ARM处理器串行通信的软件编程方法。

二、实验原理S3C2410X UART 单元提供三个独立的异步串行通信接口,皆可工作于中断和DMA模式。

使用系统时钟最高波特率达230.4Kbps,如果使用外部设备提供的时钟,可以达到更高的速率。

每一个UART单元包含一个16字节的FIFO,用于数据的接收和发送。

S3C2410X UART支持可编程波特率,红外发送/接收,一个或两个停止位,8bit数据宽度和1bit奇偶校验。

三、实验仪器设备1、EDUKIT-IV实验平台2、Mini2410 核心子板3、5V/2A电源适配器4、Emlink-w仿真器套件5、交叉串口线四、实验步骤(4)打开H-JTAG软件设置LPT线连接(5)探测芯片内核(ARM920T)(6)打开工程文件UART_TEST.UV2,选择Bulild Target或编译链接工程,如果显示0 Errors表示编译成功。

(7)选择开始->程序->附件->通讯->超级终端,设置COM1通讯,115200波特率,8位数据位,1位奇偶校验位。

(8)选择Debug->Start Debug Session或者调试工程并下载至SDRAM中。

(9)选择Debug->Run运行程序或者全速运行程序,并在超级终端中观察实验结果。

5、实验结果分析超级终端显示:UART0 Communication Test ExamplePlease input words, then press Enter:/> abcThe words that you input are: abc满足实验要求。

uart的基本编程步骤

uart的基本编程步骤UART(通用异步收发传输)是一种常见的串行通信协议,用于在微控制器和外部设备之间进行数据传输。

下面是UART的基本编程步骤:1. 初始化UART,首先,你需要在微控制器上初始化UART模块。

这通常涉及设置波特率(通信速率)、数据位、停止位和校验位等参数。

这些参数的设置取决于你的具体应用需求和外部设备的要求。

2. 配置引脚,UART通常使用两个引脚进行数据传输,一个用于发送(TX),一个用于接收(RX)。

你需要在微控制器上配置这些引脚,并确保它们与外部设备正确连接。

3. 发送数据,要发送数据,你需要将要发送的数据加载到UART发送缓冲区。

一旦数据被加载,UART模块将自动开始发送数据。

你需要确保发送的数据符合UART的规范,并且在发送数据之前,需要检查发送缓冲区是否为空,以避免数据丢失。

4. 接收数据,接收数据与发送类似,你需要设置接收缓冲区,并在接收到数据后从中读取数据。

同样,你需要检查接收缓冲区是否有新的数据可用,以避免数据丢失。

5. 中断处理(可选),在一些情况下,你可能需要使用中断来处理UART的发送和接收。

这可以帮助你及时响应数据的到来或发送完成等事件。

6. 错误处理,最后,你需要考虑如何处理可能出现的错误,比如数据丢失、校验错误等。

这可能涉及到错误标志的检查和相应的处理流程。

总的来说,UART的基本编程步骤包括初始化UART模块、配置引脚、发送数据、接收数据、中断处理(可选)和错误处理。

在实际编程中,你需要根据具体的微控制器型号和外部设备的通信协议要求来进行相应的设置和处理。

Uart模块

Uart模块UART定义:UART是一种通用串行数据总线,用于异步通信。

该总线双向通信,可以实现全双工传输和接收。

在嵌入式设计中,UART用来主机与辅助设备通信,如汽车音响与外接AP之间的通信,与PC机通信包括与监控调试器和其它器件,如EEPROM 通信。

计算机与UART:因为计算机内部采用并行数据,不能直接把数据发到Modem,必须经过UART整理才能进行异步传输,其过程为:CPU先把准备写入串行设备的数据放到UART 的寄存器(临时内存块)中,再通过FIFO(First Input First Output,先入先出队列)传送到串行设备,若是没有FIFO,信息将变得杂乱无章,不可能传送到Modem。

它是用于控制计算机与串行设备的芯片。

有一点要注意的是,它提供了RS-232C 数据终端设备接口,这样计算机就可以和调制解调器或其它使用RS-232C接口的串行设备通信了。

作为接口的一部分,UART还提供以下功能:将由计算机内部传送过来的并行数据转换为输出的串行数据流。

将计算机外部来的串行数据转换为字节,供计算机内部并行数据的器件使用。

在输出的串行数据流中加入奇偶校验位,并对从外部接收的数据流进行奇偶校验。

在输出数据流中加入启停标记,并从接收数据流中删除启停标记。

处理由键盘或鼠标发出的中断信号(键盘和鼠标也是串行设备)。

可以处理计算机与外部串行设备的同步管理问题。

有一些比较高档的UART还提供输入输出数据的缓冲区,现在比较新的UART是16550,它可以在计算机需要处理数据前在其缓冲区内存储16字节数据,而通常的UART 是8250。

现在如果您购买一个内置的调制解调器,此调制解调器内部通常就会有16550 UART。

UART是计算机中串行通信端口的关键部分。

在计算机中,UART相连于产生兼容RS232规范信号的电路。

RS232标准定义逻辑“1”信号相对于地为-3到-15伏,而逻辑“0”相对于地为+3到+15伏。

USB-UART-JTAG模块说明文档

USB ,UART ,JTAG 模块设计说明文档制作人:硬件平台部 陈定一, USB 模块USB(Universal serial bus)的中文含义是通用串行总线。

USB 接口的特点是速度快、兼容性好、不占中断、可以串接、支持热插拔等。

目前USB 接口有四种标准,分别为USB1.0(1.5Mbps),USB1.1(12Mbps ),和USB2.0(480Mbps )以及最新的标准USB3.0(5Gbps)。

USB 线缆由四根线组成:VBUS,GND,D+,D-,VBUS 在理想状态下的供电电压是5V ,但在设计当中应当注意的是USB Hub 从供电能力分为High Power 和Low Power 。

High Power 能提供最大500mA 的电流,电压范围(4. 75--5.25V ),Low Power 能提供最大电流只有100mA ,输出电压范围(4.4--5.25V )。

USB 充电接口电路模块设计原理图:GNDUSB 口VDD51.外围元器件的选择:a. USB 充电接口选用USB 口-7.5*3.7*9.3mm-屏蔽壳0.4mm 铜合金-基座黑色LCP 料。

b. 电源线和地线之间分别串联一个阻抗为100欧姆、100MHZ,额定电流为2A 的磁珠。

(用磁珠来抑制高频噪声和尖峰干扰,还具有吸收静电脉冲)c. 电容的选择注意用大电容(10UF 以上)与小电容(0.1UF )配合使用(大小电容配合使用频率特性比较好,并可减小电源对地阻抗)。

2.使用注意事项:a.具体的USB 封装,磁珠,电容大小可以调节,以达到最佳电路效果。

b.电路原理图可根据实际电路需要进行修改。

USB 有不同的速度模式,每个USB 设备必须支持低速或全速的一种,上位机端通过检测两根信号线上的电平来判断外接的是一个支持低速还是全速的的外设。

在上位机端的两根信号线D+和D-上分别都下拉了一个15K 的电阻到地,作为新接入的外设端设备则应该在D+或者D-线上上拉一个1.5K 电阻到3.3V 电源,分别代表全速设备或低速设备。

基于DSP+FPGA的UART设计与实现

基于DSP+FPGA的UART设计与实现发表时间:2020-07-07T03:20:20.125Z 来源:《学习与科普》2020年4期作者:孙小美[导读] 这样设计可以大大减少电路体积、简化电路,也提高了系统的灵活性,使整个系统更加紧凑、稳定且可靠。

陕西烽火通信集团有限公司陕西宝鸡 721006摘要:UART作为RS232协议的控制接口得到广泛的应用,将UART功能集成在DSP和FPGA芯片组成的系统中,可使整个系统更为灵活、紧凑,减小电路体积,提高系统的可靠性和稳定性。

本文提出了一种基于DSP和FPGA 系统的UART 实现方法。

关键词:通用异步收发器;DSP;FPGA1 引言通用异步收发器(Universal Asynchronous Receiver/Transmitter,通常称作UART)是一种串行异步收发协议,应用十分广泛。

UART可以和各种标准串行接口,如RS232、RS485等进行全双工异步通信,具有传输距离远、成本低、可靠性高等优点。

一般UART 由专用芯片来实现,但专用芯片引脚较多,内含许多辅助功能,在实际使用时往往只需要用到UART 的基本功能,使用专用芯片会造成资源浪费和成本提高[1]。

在DSP和FPGA组成的系统中,利用DSP芯片完成UART数据收发控制,FPGA完成UART数据具体的收发时序,二者利用EMIF接口配合,即可实现UART通信功能。

这样设计可以大大减少电路体积、简化电路,也提高了系统的灵活性,使整个系统更加紧凑、稳定且可靠。

2 UART原理UART是一种串行数据总线,用于全双工异步通信。

工作原理是将数据的二进制位按位进行传输。

基本的UART 只需要两条信号线(收、发)和一条地线就可以完成数据的互通,接收和发送互不干扰。

在UART通信协议中,信号线上的状态位高电平代表“1”,低电平代表“0”。

图1 UART数据传输格式UART 数据传输格式如图1所示,一个字符由起始位、数据位、校验位和停止位组成(其中校验位可选)。

基于FPGA的UART模块设计及仿真

Q a ul软件进行顶层和 R L级的仿真和观察 , dl ur s t I T Moe —

S 仿真 工 具 仿真 发 送 过 程 以及 应 用 开 发 板 上 L D等辅 i e r E 助显 示 接 收 数据 。结 果 使其 性 能 稳 定 ,并 在 此 设 计 基 础 上 更 容 易 扩 展 为 U A O E, 于 A I 计 的重 复 R TI C R 利 P SC设

Ke wo ds F y r : PGA ; UART; rlg;i l t n Ve i o smu a i o

UART( ie slAs n h o o sRe ev rTr n mi e Unv ra y c r n u c ie / a s t r) t

通 用 异 步 收 发 器 是 各 种 设 备 之 问进 行 通 信 的关 键 模 块 , 当一 个设 备 需 要 和另 一 个 连 接 的设 备 进 行 通信 时 ,通 常 采 用 数 字 信 号 。在 硬 件 方 面 采 用 的 是 基 于 Cc n yl eI o I FG P A系列 的开 发 板 ,时钟 晶振 为 5 z 0 MH 。本 文 在 做 以 FG P A为处理 器 的系 统设 计 时 , 用 V ro 硬件 描 述语 言 采 eig l

设 计 ,在 片 内集 成 了一 款 通用 性 较 强 的 U T模 块 。用 AR

起始位

( tr) s t a

2

奇偶位

( ai ) p r y t

停 止位

(t s p) o

图 1 数 据 传 输 时 序 图

2 U ART控 制器 的 Vei g实现 ro l

21 顶 层 模块 组成 结 构 .

Ab t a tT e s s e , sn P s r c : h y t m u i gF GA h pa ep o e s r p o i e c i s h r c s o , r v d s UART mo u e, h c e in d b rlg h r wa ed s rp i n t a d l w i h i d sg e yVe i a d r e c i t s o o

亿佰特-E51系列是230M直插型无线串口模块(UART)-半双工-收发一体-透明传输方式

产品概述E51系列是230M直插型无线串口模块(UART),半双工,收发一体,透明传输方式,接口方式分贴片或插片两种;工作在225~237.6MHz电力频段(默认230MHz),TTL电平输出,具有空中唤醒功能(超低功耗)。

模块具有软件FEC前向纠错算法,其编码效率较高,纠错能力强,在突发干扰的情况下,能主动纠正被干扰的数据包,大大提高可靠性和传输距离。

在没有FEC 的情况下,这种数据包只能被丢弃。

模块具有数据加密和压缩功能。

模块在空中传输的数据,具有随机性,通过严密的加解密算法,使得数据截获失去意义。

而数据压缩功能有概率减小传输时间,减小受干扰的概率,提高可靠性和传输效率。

E51系列均严格遵守FCC、CE、CCC等国内国外设计规范,满足各项射频相关认证,满足出口要求。

目录1.产品特点32.技术参数32.1电气参数32.1.1.发射电流32.1.2.接收电流42.1.3.关断电流42.1.4.供电电压42.1.5.通信电平42.2射频参数42.2.1.发射功率42.2.2.接收灵敏度52.2.3.推荐工作频率52.3实测参数52.3.1.实测距离53.机械特性63.1.E51-TTL-50 (6)3.2.E51-TTL-500 (7)3.3.E51-TTL-2W (8)4.推荐连线图 (9)5.功能详解95.1.定点发射 (9)5.2广播发射105.3广播地址105.4监听地址105.5模块复位105.6AUX详解105.6.1串口数据输出指示 (10)5.6.2无线发射指示115.6.3模块正在配置过程中 (11)5.6.4AUX注意事项116.工作模式126.1.模式切换 (12)6.2一般模式(模式0) (12)6.3唤醒模式(模式1) (13)6.4.省电模式(模式2) (13)6.5.休眠模式(模式3) (13)7.指令格式137.1出厂默认参数 (13)7.2工作参数读取 (14)7.3版本号读取147.4复位指令147.5参数设置指令 (14)8.参数配置169.生产指导179.1回流焊温度179.2回流焊曲线图 (17)10.常见问题1810.1通信距离很近 (18)10.2模块易损坏1811.重要声明1812.关于我们181.产品特点●【超强穿透】:230M 频率低,波长较长,因此拥有极强的穿透绕射能力,适合于比较复杂的环境。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

UART(串口)收发模块设计

UART(串口)收发模块设计- 02

整体架构回顾

整体结构如下图,整个UART有两个大模块,一个接收模块,一个发送模块。

具体大家可以回顾文章《UART(串口)收发模块设计- 01》。

波特率时钟产生模块

收发模块里面都有一个波特率时钟产生模块BuadRate_set,用于将系统时钟clk进行分频,得到波特率时钟Buad_clk,以控制数据的收发。

端口如下,通过CLK_Period指定当前的clk时钟频率,比如50M,则为50000000。

Buad_Rate为设定的波特率。

主要设计代码如下,通过localparam DIV_PEREM指定分频计数值。

分频计数器为cnt,当enable为高时,cnt开始循环的从0递增到DIV_PEREM。