浙江理工大学数字电路2015--2017,2019年考研真题

2015年浙江理工大学考研试题347心理学专业综合

浙江理工大学2015年硕士学位研究生招生入学考试试题考试科目:心理学专业综合代码:347(请考生在答题纸上答题,在此试题纸上答题无效)一、单项选择题(本类题共130分,每小题2分)1.物体失认症患者往往是因为( )A. 感觉出现障碍而知觉正常B. 感觉正常而知觉出现障碍C. 感觉和知觉都出现障碍D. 感知觉均正常而注意出现障碍2.在下列哪种情况中,人会更多地采用知觉的自上而下加工()A. 鉴别一个人的签名B. 鉴别一张假钞C. 观赏一幅毕加索的画D. 记住一张人脸3. “鸡尾酒会效应”可以通过以下哪种理论模型来解释()A.衰减模型B.过滤器模型C.反应选择模型D.知觉选择模型4. 许多人认为,坐火车比乘飞机更安全。

这种观点的成因是( )A. 调整性启发法B. 可得性启发法C. 代表性启发法D. 参照点启发法5. 属于界定清晰的问题(well-defined problem)是()A. 如何成为一名优秀教师B.如何根据已知条件解应用题C. 怎样读好一本书D. 怎样教育子女成才6. 受到猛烈撞击的汽车驾驶员经常不能回忆出受伤前几秒的事情,但对受伤前几分钟或几小时间发生的事情却能很好地回忆出来,这属于哪种类型的遗忘症()A. 顺行性遗忘症B. 逆行性遗忘症C. 心因性遗忘症D. 柯萨可夫氏记忆障碍7.以个人经历为参照,以时空为框架的记忆是()A. 程序性记忆B. 情景记忆C. 语义记忆D. 闪光灯记忆8.从问题的目标状态开始搜索直至找到解决问题的方法的问题解决策略是:()A. 手段-目的分析B.爬山法C. 逆向分析D.简化计划法9.故地重游往往令人触景生情,回忆起许多在其他情况下不太容易想起的往事,能解释此现象的是( )A. 层次网络模型B. 激活扩散模型C. 编码特异性原则D. 加工水平理论10.按照希波克拉底关于气质类型的“体液说”,“黑旋风”李逵应该属于 ( )A. 胆汁质B. 多血质C. 粘液质D. 抑郁质11.人类视觉信息处理主要在大脑皮层的()A. 额叶B. 顶叶C. 枕叶D. 颞叶12.5.12四川大地震中,有些学生虽然已经不幸遇难,但家长仍每天去学校等孩子的消息,这应该是自我防御机制中( ) 的表现A. 理智化B. 压抑C. 拒绝D. 投射13.我们对如何骑自行车和游泳的记忆应属于()A. 程序性记忆B. 情景记忆C. 感觉记忆D. 内隐记忆14.经常说谎的人会认为别人也会经常欺骗他,所以很难相信别人,这主要是哪种自我防御机制在起作用()?A. 拒绝B. 替代C. 反向作用D. 投射15.有研究认为开车时打手机其危险性不亚于醉酒驾车,这应该是 ( )问题A. 短时记忆B. 注意的转移C. 注意的分配D. 感觉记忆16.上课的时候,教室的某个位置突然传出一声巨响,同学们都会转头看过去,这属于()A.有意注意B.无意注意C.有意后注意D.无意后注意17.人类智力中,主要受后天经验学习的影响,可以一直处于发展上升中的是 ( )A.液态智力B.正态智力C.晶态智力D.偏态智力18.多年不见的朋友或老同学,在自己的脑海中的印象最深的,就包括临别时的情景,这是( )A.首因效应B.近因效应C.犯错误效应D.马太效应19.管子曾说过:“仓廪实而知礼节,衣食足而知荣辱”。

浙江理工大学电子技术基础(模电、数电)考研真题2011年、2012年

图2 3. 电 路 如 图 3 所 示 , 晶 体 管 的 = 80, rbe=1kΩ 。(15 分)

(1)求出 Q 点;

( 2) 分 别 求 出 RL= ∞ 和 RL= 3kΩ 时 电 路 的 Au 和 Ri;

第 1 页 ,共 4 页

(3)求出 Ro。

图3 4. 电路如图 4 所示:(10 分)

浙江理工大学

二 O 一二年硕士学位研究生招生入学考试试题 考试科目:电子技术基础(模电、数电)A 代码:954

(请考生在答题纸上答题,在此试题纸上答题无效) Ⅰ、模拟部分

1.电路如图 1 所示,晶体管导通时 UBE=0.7V,β=50。试分析 VBB 为 0V、1V、3V 三种情况下 T 的工作状态及输出电压 uO 的值。(10 分)

+/cc

jⅠ t:1

C

叫

R:2

+1/cc

R:1

舀

丿?。 2

一 /cc

R:1

C

叫

R:2

图4

第 2页 ,共 4页

+/cc

五。电路如图 5所 示,已 知集成运放的最大输 出电压幅值为±12V, 山的数值在 u。 1

的峰峰值之 间。 (1)求解 u。3的 占空 比与 uI的 关系式。

(2)设uI=2。 5Ⅴ ,画 出u。 卜 %2和 u。 3的 波形 。(20分 )

(1) 判断电路中引入了哪种组态的交流负反馈,并计算它们的反馈系数; (2) 估算电路在深度负反馈条件下的电压放大倍数。

图4 5. 电 路 如 图 5 所 示 。(15 分)

( 1) 写 出 uO 与 uI1、 uI2 的 运 算 关 系 式 ; ( 2) 当 RW 的 滑 动 端 在 最 上 端 时 , 若 uI1= 10mV, uI2= 20mV, 则 uO= ? ( 3) 若 uO 的 最 大 幅 值 为 ± 14V, 输 入 电 压 最 大 值 uI1max= 10mV, uI2max= 20mV,最 小 值 均 为 0V,则 为 了 保 证 集 成 运 放 工 作 在 线 性 区 ,R2 的 最 大 值 为 多 少 ?

浙江理工大学机械设计基础2015--2017,2019年考研真题

5. 设已知一对渐开线标准斜齿轮传动,Z1=20,Z2=40,mn 8mm , n 20 ,ha*n 1,cn* 0.25 ,

角 为

。

2.在机械系统速度波动的一个周期中,当系统出现盈功时,系统的运转速度将______,此时飞

轮将_______能量。

3.在图示所示铰链四杆机构中,若机构以 AD 杆为机架时,则为

机构;以 CD 杆为机架

时,它为

机构。

4.由 M 个构件铰接于一点的复合铰链应包含

转动副。

5. 主 动 件 为 匀 速 转 动 ,为 了 使 从 动 件 获 得 往 复 转 动 ,可 以 使 用

B.基圆半径越小,压力角越大

C.滚子半径越小,压力角越小

D.滚子半径越大,压力角越小

10. 平面连杆机构急回运动的相对程度,通常用( )来衡量。

A. 极位夹角

B. 行程速比系数 K

C. 压力角

D. 运动系数τ

11. 以下螺纹属于传动螺纹的有 (

)

A. 60 度牙型角的三角螺纹 B. 英寸制螺纹 C.锯齿形螺纹 12. 在承受横向载荷或旋转力矩的普通紧螺栓组连接中,螺栓杆 (

2. 设计标准齿轮时,为了增大重合度,可以采用的方法是( )。

A. 加大模数

B.减小齿顶高

C. 加大中心距. D. 增加齿数

3. 一般低副平面机构中引入一个二副杆,则增加了( )个约束。

A. 2

B.0

C. 1

D.3

4. 若忽略摩擦,一对渐开线齿廓啮合时,齿廓间作用力沿着( )方向。

A. 齿廓公切线

B. 节圆公切线

D.管螺纹 )作 用 。

A. 受切应力 B.受拉应力 C.受扭转切应力和拉应力

浙江理工大学电子技术基础考研真题2007—2011、2017—2019年

浙江理工大学

二 O 一 O 年硕士学位研究生招生入学考试试题 考试科目:电子技术基础(模电、数电) 代码:954

(*请考生在答题纸上答题,在此试题纸上答题无效)

Ⅰ、模拟部分

1、现有两只稳压管,它们的稳定电压分别为 6V 和 8V,正向导通电压为 0.7V。试问:

(1)若将它们串联相接,则可得到几种稳压值?各为多少? (2)若将它们并联相接,则又可得到几种稳压值?各为多少?

(15 分)

第 2 页,共 5 页

图5 7、已知三个电压比较器的电压传输特性分别如图 6(a)、(b)、(c)所示,它们的输入

电压波形均如图(d)所示,试画出 uO1、uO2 和 uO3 的波形。

(9 分)

图6

第 3 页,共 5 页

Ⅱ、数字部分

8、利用卡诺图化简具有约束的逻辑函数。

m3

Y(A, B,C, D) m5 m9 m10

Ci

S

≥1 ﹠

=1

=1

A1 A2

Ci1

图8

12、设计一个控制步进电动机三相六状态工作的逻辑电路,如果用“1”表示电机绕组 导通,“0”表示电机绕组截止,则 3 个绕组 ABC 的状态转换图应如图 9 所示,M 为输入控制变量,当 M=1 时为正转,M=0 时为反转。(要求用 D 触发器) (20 分)

(2) 若电容 Ce 开路,则将引起电路的哪些动态参数发生变化?如何变化? (15 分)

图2

第 1 页,共 5 页

4、设 图 3 所 示 电 路 的 静 态 工 作 点 均 合 适 , 画 出 它 的 交 流 等 效 电 路 , 并 写

出 Au 、 Ri 和 Ro 的 表 达 式 。

(10 分)

2019浙江大学信号系统与数字电路考研真题与答案解析16页word文档

《2019浙江大学信号系统与数字电路考研复习精编》《复习精编》是惟学浙大精品考研专业课系列辅导材料中的核心产品。

本书严格依据学校官方最新指定参考书目,并结合考研的精华笔记、题库和内部考研资讯进行编写,是惟学浙大老师的倾力之作。

通过本书,考生可以更好地把握复习的深度广度,核心考点的联系区分,知识体系的重点难点,解题技巧的要点运用,从而高效复习、夺取高分。

考试分析——解析考题难度、考试题型、章节考点分布以及最新试题,做出考试展望等;复习之初即可对专业课有深度把握和宏观了解。

复习提示——揭示各章节复习要点、总结各章节常见考查题型、提示各章节复习重难点与方法。

知识框架图——构建章节主要考点框架、梳理全章主体内容与结构,可达到高屋建瓴和提纲挈领的作用。

核心考点解析——去繁取精、高度浓缩初试参考书目各章节核心考点要点并进行详细展开解析、以星级多寡标注知识点重次要程度便于高效复习。

历年真题与答案解析——反复研究近年真题,洞悉考试出题难度和题型;了解常考章节与重次要章节,有效指明复习方向。

《复习精编》具有以下特点:(1)立足教材,夯实基础。

以指定教材为依据,全面梳理知识,注意知识结构的重组与概括。

让考生对基本概念、基本定理等学科基础知识有全面、扎实、系统的理解、把握。

(2)注重联系,强化记忆。

复习指南分析各章节在考试中的地位和作用,并将各章节的知识体系框架化、网络化,帮助考生构建学科知识网络,串联零散的知识点,更好地实现对知识的存储,提取和应用。

(3)深入研究,洞悉规律。

深入考研专业课考试命题思路,破解考研密码,为考生点拨答题技巧。

1、全面了解,宏观把握。

备考初期,考生需要对《复习精编》中的考前必知列出的院校介绍、师资力量、就业情况、历年报录情况等考研信息进行全面了解,合理估量自身水平,结合自身研究兴趣,科学选择适合自己的研究方向,为考研增加胜算。

2、稳扎稳打,夯实基础。

基础阶段,考生应借助《复习精编》中的考试分析初步了解考试难度、考试题型、考点分布,并通过最新年份的试题分析以及考试展望初步明确考研命题变化的趋势;通过认真研读复习指南、核心考点解析等初步形成基础知识体系,并通过做习题来进一步熟悉和巩固知识点,达到夯实基础的目的。

浙江理工大学_990数字电路2017年_考研专业课真题

浙 江 理 工 大 学2017年硕士研究生招生考试初试试题考试科目:数字电路 代码:990(请考生在答题纸上答题,在此试题纸上答题无效)一、填空题(每空1.5分,共15分)。

1. D A C AB +在四变量卡诺图中有( )个小方格是“1”。

2. 如果对键盘上108个符号进行二进制编码,则至少要( )位二进制数码。

3.A/D 转换的过程可分为( )、保持、量化、编码4个步骤。

4. 在CMOS 门电路中,输出端能并联使用(或线与)的电路有( );5. 8线—3线优先编码器74LS148的优先编码顺序是7I 、6I 、5I 、…、0I ,输出为2Y 1Y 0Y 。

输入输出均为低电平有效。

当输入7I 6I 5I …0I 为11010101时,输出2Y 1Y 0Y 为( )。

6.图1为与非门组成的基本SR 锁存器,为使锁存器处于“置1”状态,其S R 应为( )。

2R Cv v O R12C dR d图1 图2 图37. 将一个包含有32768个基本存储单元的存储电路设计16位为一个字的ROM 。

该ROM 有( )根地址线。

8.由555定时器构成的电路如图2所示,该电路的名称是( )。

9.已知某电路的输入输出波形如图3所示,则该电路可能为( )。

10.门电路参数输入输出参数V IH (min )、V IL (max )、V OH (min )和V OL (max )由小到大的排列正确的是( )。

二、选择题在每小题列出的四个备选项中只有一个是符合题目要求的,请将其代码填写在题后的括号内(本大题共10小题,每小题3分,共30分)。

1.下列四个数中与十进制数(163)10不相等的是 。

A .(A3)16B .(10100011)2C .(000101100011)8421BCD D .(100100011)8 2.若已知Y XY YZ Z Y XY +=++,判断等式=+++))()((Z Y Z Y Y X Y Y X )(+成立的最简单方法是依据 。

浙江理工大学《990数字电路》考研专业课真题试卷

RD

第 3 页 ,共 5 页

7.图(a)示为由 555 定时器构成的心率失常报警电路。经放大后的心电信号 vI 如图(b)所示,

vI 的峰值 Vm=4 V。

(1)分别说出 555 定时器Ⅰ和 555 定时器Ⅱ所构成单元电路的名称;

Y7 Y6 Y5 Y4 Y3Y2 Y1Y0 应为(

)。

7. 将一个包含有 32768 个基本存储单元的存储电路设计 16 位为一个字节的 ROM。该 ROM 有

(

)根地址线,有(

)根数据读出线。

8. 模/数转换器(ADC)两个最重要的指标是转换精度和(

)。

二、选择题在每小题列出的四个备选项中只有一个是符合题目要求的,请将其代码

考试科目:数字电路

代码:990

(请考生在答题纸上答题,在此试题纸上答题无效)

一、填空题(每空 1.5 分,共 15 分)。

1. 有一数码 10010011,作为自然二进制数时,它相当于十进制数(

码时,它相当于十进制数(

)。

2. 三态门电路的输出有高电平、低电平和(

)3 种状态。

3. TTL 与非门多余的输入端应接(

说明 保持 置0 置1 翻转

A. Qn+1 =A

B. Qn1 AQn AQn

C. Qn1 AQn BQn

D. Qn+1 = B

9. 有一个 4 位的 D/A 转换器,设它的满刻度输出电压为 10V,当输入数字量为 1101 时,输出电

压为(

)。

A. 8.125V

B.4V

C.6.25V

浙江理工大学947信号与系统17-19年真题

考试科目:信号与系统

代码:947

(请考生在答题纸上答题,在此试题纸上答题无效)

一、 填空题(每空 3 分,12 个空格,共 36 分)

1、

(4 2 ) (

t

1)d

。

2、已知序列 x1(n) n[u(n) u(n 6)];x2 (n) u(n 6) u(n 1) ,

求卷积y(n) x1(n) * x2 (n)

的拉普拉斯变换为

F (s)

(s

s )2 02

,其中为

有限实常数,则当 0时,f (t)的傅立叶变换F( j)

;

当 0时,f (t)的傅立叶变换F( j)

;

当 0时,f (t)的傅立叶变换F( j)

8、

f

(t)

1 2

sin(2t)u(t)

2

(t )的拉普拉斯变换F ( s)

9、已知 F(z)

Im[ F (

j)]

sin

0

u(

0 )

u(

0 ),试求

f

(t)

。

4、 求f (t) (e3t 4)u(t)的拉普拉斯变换F(s)。

5、 求X z

1 z 1

1 5 z 1 1 z 2

66

z 1 的反变换x(n)。 2

三、(32 分)线性时不变离散系统的单位阶跃响应为 g(n) n (2)n1 u(n),试求:

初始条件不变,当输入 2e(t),完全响应为r2 (t) 2etu(t),求零输入响应 rzi (t) 和输 入为 3e(t)时的完全响应r3(t)。

2、如下面左图所示系统,低通滤波器的频率响应 H ( j) 如下面右图所示,

其中 e(t) 4Sa(2t),s(t) cos(20t) 求输出r(t),并画出e(t)、s(t)、f (t)、g(t)和r(t)的频谱图。

浙江理工大学933单片机原理与接口技术2015-2017年考研专业课真题试卷

KB。

5、假定(SP)= 30 H,(ACC)= 40 H,(B)= 50 H,执行下列指令:

PUSH B

PUSH ACC

后,SP 的内容为

,31H 单元的内容为

,32H 单元的内容为

。

6. 如果 8051 单片机采用 12Mhz 的晶振频率,则定时器工作在方式 0 时最大定时时间是 8192us,

考试科目:单片机原理与接口技术

代码: 933

(请考生在答题纸上答题,在此试题纸上答题无效)

一、填空题(每空 1 分,共 20 分)

1. 8051 单片机内部 RAM 地址从 00H~1FH 的区域是通用工作寄存器区。该区域可以分为

__________组,其中组与组之间的切换可通过寄存器

用第

组。

来实现,工作寄存器缺省采

(1)请画出实现上述操作的主程序框图和中断程序框图; (2)根据程序框图编写出题目要求的程序。

第 2 页 ,共 4 页

2. 在 MCS-51 系统中,片内 RAM 存放有 20 个数据,首地址为 50H,试编程将数据 块传送到片外 RAM 以 3000H 为首地址的存储单元中。

(1)请画出实现上述操作的程序框图; (2)根据程序框图编写出题目要求的程序段。 3. 变量 x、y 均为小于 10 的正整数,试通过查表(0-9 平方表)编程计算 z=x2+y2, 其中变量 x、y 分别存放在 MCS-51 单片机片内 RAM 的 41H 和 42H 单元中,计算结 果 z 存放到片内 RAM 的 43H 单元。 4. 有一 8051 单片机连接有数模转换器 DAC0832,如下图所示。现在需要通过图中 U0 处输出一锯齿波。已知单片机使用的晶振频率为 12MHz。锯齿波周期为 256ms, 每个周期由 256 个点构成。 (1)如通过 U0 输出电压-2.5V,则需要向 DAC0832 传送的数字量多少。 (2)按照图中的连线,DAC0832 的地址范围为多少。 (3)编程实现锯齿波输出(锯齿波电压范围 0~ -5v)。

浙江理工大学模拟电子技术基础试题(1)

浙江理工大学《模拟电子技术基础》试题(1)一、 填空(共30分,1分/空)1、在本征半导体中加入 5 价元素可形成N 型半导体,加入 3 价元素可形成P 型半导体。

2、在一个交流放大电路中,测出某三极管三个管脚对地电位:①端为1.5V 、②端为4V 、③端为2.1V ,则①端为 发射 极、②端为 集电 极、3端为 基 极,该管子为 NPN 型。

3、集成运放实际上是一种高性能的直接耦合放大电路。

通常由 输入级 、 中间级 、 输出级 和 偏置电路 等四部分组成。

4、放大电路在高频信号作用时放大倍数数值下降的原因是 ,而低频信号作用时放大倍数数值下降的原因是 。

5、为了增大放大电路的输入电阻,应引入 串联 负反馈;为了增大放大电路的输出电阻,应引入 电流 负反馈。

6、电路如图1.1所示,已知集成运放的开环差模增益和差模输入电阻均近于无穷大,最大输出电压幅值为±14V 。

填空:电路引入了 电压串联负反馈 (填入反馈组态)交流负反馈,电路的输入电阻趋近于 无穷大 ,电压放大倍数=f u A 11 。

设V U I 1=,则=O U 11V ;若1R 开路,则O U 变为 1 V ;若1R 短路,则O U 变为 14 V ;若2R 开路,则O U 变为 14 V ;若2R 短路,则O U 变为 1 V 。

图1.17、 同相 比例运算电路的输入电流等于零,而 反相 比例运算电路的输入电流等于流过反馈电阻中的电流。

8、当信号频率等于石英晶体的串联谐振频率或并联谐振频率时,石英晶体呈 阻性 ;当信号频率在石英晶体的串联谐振频率和并联谐振频率之间时,石英品体呈 感性 ;其余情况下石英晶体呈 容性 。

9、已知电路如图1.2所示,电路中D 1和D 2管的作用是消除 。

图1.210、整流的目的是 ;直流稳压电源中滤波电路的目的是 。

二、 判断题(20分,1分/题)1、因为N 型半导体的多子是自由电子,所以它带负电。

【应用心理(专硕)】2019年浙江理工大学真题详解(回忆版)

2019年浙江理工大学硕士研究生招生考试初试试题科目代码:347科目名称:应用心理满分:300分注意:全部答案一律写在答题纸上,答在试题纸上的不计分!答题要写清题号,不必抄题。

一、单项选择题(本部分共20小题,每小题3分,共计60分)1.除嗅觉外,各类感觉信息在向皮层传递过程中均须通过()A.上丘脑B.下丘脑C.丘脑D.脑桥2.鲁利亚第一机能系统的神经生理基础是()A.脑干网状结构B.颞叶C.额叶D.顶叶3.现代感觉编码理论中,认为不同性质的感觉是由不同的神经元来传递信息的理论是()A.神经特殊能量学说(Theory of specific nerve energy)B.模式理论(Pattern theory)C.模块理论(Module theory)D.特异化理论(Specificity theory)4.视觉传导通路是()A.视网膜—视交叉—外侧膝状体—枕叶B.视网膜—视交叉—内侧膝状体—顶叶C.视网膜—视交叉—外侧膝状体—顶叶D.视网膜—视交叉—内侧膝状体—枕叶5.以下最可能属于普肯耶现象的是()A.阳光下感觉同样亮度的红色物体和蓝色物体,夜幕降临时,红色物体显得更亮B.阳光下感觉同样亮度的红色物体和蓝色物体,夜幕降临时,蓝色物体显得更亮C.傍晚时感觉同样亮度的橙色物体和紫色物体,正午阳光下紫色会感觉更亮D.傍晚时感觉同样亮度的橙色物体和紫色物体,正午阳光下依然会同样亮度6.如下图,人们识别出左边的符号为数字13或字母B,此时知觉加工中更多的是()A.控制性加工B.自动化加工C.自下而上的加工D.自上而下的加工7.比较适于对垂直—水平错觉进行解释的是()A.眼动说C.透视说D.常性误用说8.下列方法中通常用来测量持续性注意的是()A.警戒作业B.双作业操作C.双耳分听D.负启动9.成龙的电影《我是谁》中,男主角无法回忆受伤的原因和经过,这属于哪种类型的遗忘症()A.顺行性遗忘症B.逆行性遗忘症C.心因性遗忘症D.柯萨可夫氏记忆障碍10.“英雄救美往往会成就一段佳话”,其实质主要是一种()A.认知失调B.归因C.社会助长D.利他行为11.多元智力理论主要是由()所提出A.GuilfordB.SpearmanC.GardnerD.Sternberg12.如果要建立两个变量之间的数学模型,下列统计方法中,最恰当的是()A.方差分析法B.因素分析法C.回归分析法D.聚类分析法13.()首次提出心理学必须用实验的方法进行研究,从而搭建了实验心理学的框架。

浙江理工大学《951自动控制理论》考研专业课真题试卷

(a)

(b)

图2

第 1 页 ,共 3 页

三、(15 分) 已知系统的单位阶跃响应为 c(t) 1 0.2e60t 1.2e10t ,试求:

(1)系统的传递函数;

(2)系统的阻尼比 和自然振荡频率n 。

四、(20 分)给定系统如图 3 所示, K 0 ,试画出系统的根轨迹,并分析增益对系统阻尼特性

图1

G(s) K

二、 (30 分) 系统结构如图 2 所示,

s(Ts 1) ,定义误差 e(t) r(t) c(t) ,

(1) 若希望图(a)中,系统所有的特征根位于 s 平面上 s 2 的左侧,且阻尼比为 0.5,求

满足条件的 K,T 的取值范围。

(2) 求图(a)系统的单位斜坡输入下的稳态误差。 (3) 为了使稳态误差为零,让斜坡输入先通过一个比例微分环节,如图(b)所示,试求出

海天课堂

中国考研专业课辅导知名品牌

浙江理工大学考研专业课真题试卷

951 自动控制理论

2016 年《951 自动控制理论》专业课真题试卷 2017 年《951 自动控制理论》专业课真题试卷 2018 年《951 自动控制理论》专业课真题试卷 2019 年《951 自动控制理论》专业课真题试卷

浙江理工大学

R(s)

E(s)

—

K

C(s)

s(Ts 1)

Hale Waihona Puke 图 3(a)第 1 页 ,共 2 页

图 3(b)

五、(30 分)单位反馈系统对数幅频特性如图 4 所示(最小相位系统)。要求: 1)写出系统的开环传递函数;2)判别系统的稳定性;3)如果系统是稳定的,求 r(t)= t 时的稳 态误差。

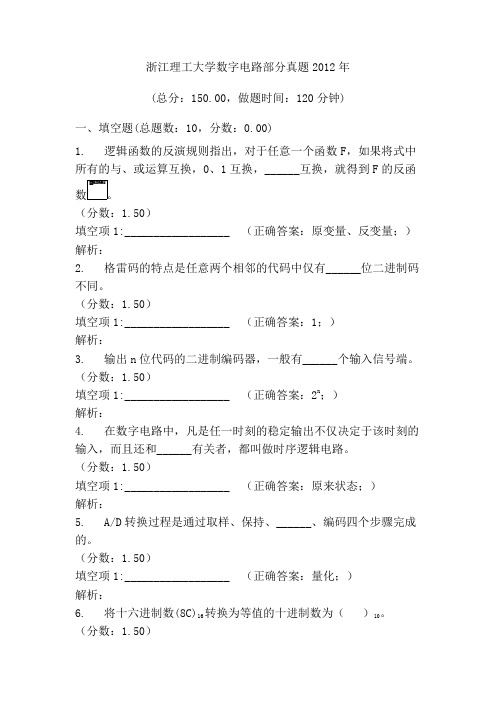

浙江理工大学数字电路部分真题2012年

浙江理工大学数字电路部分真题2012年(总分:150.00,做题时间:120分钟)一、填空题(总题数:10,分数:0.00)1. 逻辑函数的反演规则指出,对于任意一个函数F,如果将式中所有的与、或运算互换,0、1互换,______互换,就得到F的反函数。

(分数:1.50)填空项1:__________________ (正确答案:原变量、反变量;)解析:2. 格雷码的特点是任意两个相邻的代码中仅有______位二进制码不同。

(分数:1.50)填空项1:__________________ (正确答案:1;)解析:3. 输出n位代码的二进制编码器,一般有______个输入信号端。

(分数:1.50)填空项1:__________________ (正确答案:2n;)解析:4. 在数字电路中,凡是任一时刻的稳定输出不仅决定于该时刻的输入,而且还和______有关者,都叫做时序逻辑电路。

(分数:1.50)填空项1:__________________ (正确答案:原来状态;)解析:5. A/D转换过程是通过取样、保持、______、编码四个步骤完成的。

(分数:1.50)填空项1:__________________ (正确答案:量化;)解析:6. 将十六进制数(8C)16转换为等值的十进制数为()10。

(分数:1.50)填空项1:__________________ (正确答案:140;)解析:7. 当J=K=______时,JK触发器Q n+1=Q n。

(分数:1.50)填空项1:__________________ (正确答案:1;)解析:8. n位二进制加法计数器的最大计数值为______。

(分数:1.50)填空项1:__________________ (正确答案:2n;)解析:9. 自动产生方波信号的电路称为______。

(分数:1.50)填空项1:__________________ (正确答案:多谐振荡器;)解析:10. 当RAM的字数够用、位数不够用时,应扩展位数。

浙江理工大学990数字电路2015-2019年考研专业课真题试卷

)和(

)。

4.某集成电路芯片,查手册知其最大输出低电平VOLmax=0.4V ,最大输入低电平VILmax=0.8V,最小

输出高电平VOHmin =2.6V ,最小输入高电平VIHmin =2.0V,则其高电平和低电平的噪声容限分别等于

(

)和(

)。

5.一个8 位数模转换器(DAC)的最小输出电压增量为0.02V,当输入代码为11011010时,输出电

2019年浙江理工大学考研专业课初试真题试卷

2019年浙江理工大学考研专业课初试真题试卷

2019年浙江理工大学考研专业课初试真题试卷

2019年浙江理工大学考研专业课初试真题试卷

2019年浙江理工大学考研专业课初试真题试卷

精都教育——全国 100000 考生的选择

我们的梦想,为成就更多人的梦想

为( )。

A.11001111

B.11110100

C.11110010

D.11110011

5.已知某电路的输入输出波形如图所示,则该电路可能为( )。 A.多谐振荡V器DD B.双稳态触发器 C.单稳态触发器 D.施密特触发器

Cd

R C

vI

≥1

1

vo

Rd

G1

G2

6.一个8 位移位寄存器的移位脉冲的频率是1MHz,将8 位二进制数并行地移入这个移位寄存器需 要( )。

A.经过8 个触发器的传输延迟时间

B.8μs

C.经过1 个触发器的传输延迟时间

D.1μs

7.若要将一异或非门当作反相器使用,则输入端 A、B 端的连接方式是( )。

A.A 或 B 中有一个接“1”

B.A 或 B 中有一个接“0”能实现

8.TTL 门电路组成的JK 触发器,时钟端接5kHz 脉冲,J与K悬空,则输出Q 的频率为( )。

(NEW)浙江理工大学信息学院《990数字电路》[专业硕士]历年考研真题汇编

![(NEW)浙江理工大学信息学院《990数字电路》[专业硕士]历年考研真题汇编](https://img.taocdn.com/s3/m/a3640db6a2161479171128fb.png)

B.(12F)16 C.(301)10 D.(10010111)8421BCD

2.下列逻辑等式中不成立的是______

A.

B.

C.

D.

3.图2所示为一门电路的输入输出波形图,其中A和B为输入信 号,L为输出信号。请问该门电路是______。

2.格雷码的特点是任意两个相邻的代码中仅有_______位二进制码 不同。

3.输出n位代码的二进制编码器,一般有______个输入信号端。

等于______

14.将TTL与非门正常使用时,多余的输入端应______ A.全部接高电平 B.部分接高电平,部分接地 C.全部接地 D.部分接地,部分悬空 15.S R触发器不具有______功能。 A.保持 B.翻转 C.置1 D.置0

16.图1时序电路的状态图中,具有自启动功能的是______ A.

目 录

2014年浙江理工大学信息学院990数字电路[专业硕士]考研真题 2013年浙江理工大学信息学院990数字电路[专业硕士]考研真题 2012年浙江理工大学信息学院990数字电路[专业硕士]考研真题 2011年浙江理工大学信息学院990数字电路[专业硕士]考研真题 2010年浙江理工大学信息学院990数字电路[专业硕士]考研真题

1.四个电路输入vI、输出vO的波形如图1所示,试写出分别实现下 列功能的最简电路类型(不必画出电路)。

(a)______;(b)______;(c)______;(d)______。

图1

2.5个变量的逻辑函数,全体最小项之和为______。

3.三位二进制减法计数器的初始状态为101,四个CP脉冲后它的 状态为______。

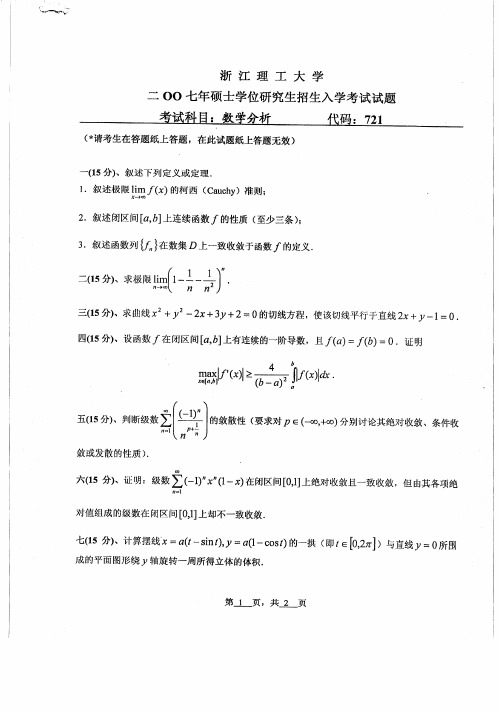

浙江理工大学数学分析考研真题2007—2012、2017—2019年

四(15 分)、设 f 为区间 I 上严格凸函数.证明:若 x0 I 为 f 的极小值点,则 x0 为 f 在 I 上唯

一的极小值点.

五(15 分)、求椭圆 x 2 y 2 1绕 y 轴旋转所得旋转曲面的面积(假设 a b ). a2 b2

六(15

分)、把函数

f

(x)

1 x, x 3,

0 x 2, 在 (0,4) 上展开成余弦级数.

(D) f (0) 为极大值

8.设函数 f (x) (x 1)(x 2)(x 3) ,则方程 f "(x) 0 有( ).

(A)三个实根 (B)二个实根 (C)一个实根 (D)无实根

9.已知曲线 y ax3 bx 2 cx d 有一个拐点,其中 a 0 ,且在拐点处有一水平切线, 则 a , b , c 之间的关系是( ). (A) a b c 0 (B) b2 6ac 0 (C) b2 4ac 0 (D) b2 3ac 0

na对任给的??0存在自然数n使得对所有自然数p都有an?p?an??b对任给的??0存在唯一自然数n使当mn?n时都有am?an??c存在??0及自然数n使当mn?n时都有am?an??d对任给自然数n存在??0使得对所有自然数p都有an?p?an??2??xsin1x4

浙江理工大学

二 OO 八年硕士学位研究生招生入学考试试题

2 x4

七(15 分)、证明函数项级数

x2

在 (0,) 上收敛,但不一致收敛.进一

n1 [1 (n 1)x 2 ](1 nx 2 )

步问,该函数项级数在区间[ ,) 上一致收敛吗?(其中 0 是一个正实数)

第 1 页,共 2 页

八(15

分)、计算积分

I

浙江理工大学977电子技术基础(模电丶数电)B2015年考研专业课真题试卷

1. 填空(1 分/空,共 30 分)

(1) 在一个交流放大电路中,测出某三极管三个管脚对地电位:①端为 1.5V、②端为 4V、③端

为 2.1V,则①端为( )极、②端为( )极、③端为( )极,该管子为( )型。

(5) 当温度升高时,二极管的反向饱和电流将( )。

(6) 将二进制数(1010101.0011)2 分别转换成下列进制数:十进制数( 进制数( )。

)、八进制数(

)及十六

(7) 一个基本 RS 触发器在正常工作时,它的约束条件是 R S 1,则它不允许输入 S ( )

且 R ( )的信号。

(8) 寄存器和计数器属( )逻辑电路,译码器和加法器属( )逻辑电路。

(9) 常见的脉冲产生电路有( ),常见的脉冲整形路有( )、ห้องสมุดไป่ตู้ )。

(10) 一个逻辑函数除了波形表示方法外,还有四种表示方法:( )、( )、( ) 及( )。

(11) 图 1 所示电路中,设灯 Y 亮为逻辑 1,灭为逻辑 0;开关 A、B、C 导通为 1,断开为 0;则

D、编码是将为了区分一系列不同的事物,将其中的每个事物用一个二值代码表示 (6) 在输入不变的情况下,若引入反馈后( ),则说明引入的反馈是负反馈。

A、输入电阻大 B、输出量增大 C、净输入量增大 D、净输入量减小

(7) 在运算电路中,欲将方波电压转化成三角波电压,应选用( )。

A、比例运算电路 B、加法运算电路 C、积分运算电路 D、微分运算电路

(2) 电压并联负反馈放大器是一种输出端取样量为( ),输入端比较量为( )的负反馈放大

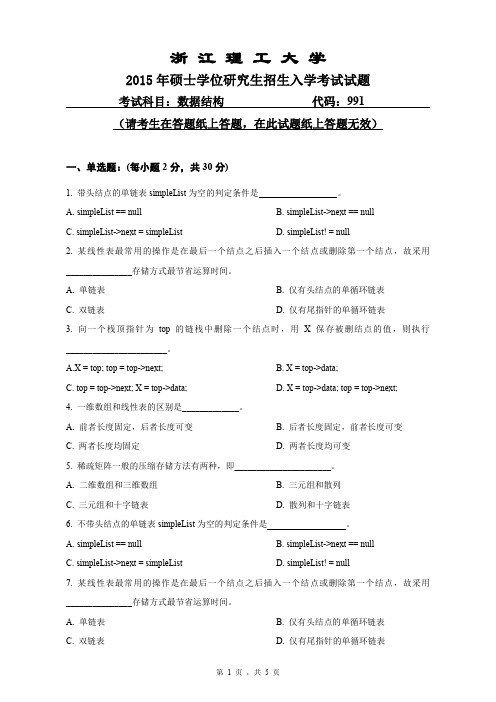

2015年浙江理工大学考研试题991数据结构

8. 一个有 n 个顶点的无向图最多有_________条边。 9. 在堆排序和快速排序中,若原始记录接近正序或反序,则选用_______比较好。

2. 某线性表最常用的操作是在最后一个结点之后插入一个结点或删除第一个结点,故采用 _______________存储方式最节省运算时间。 A. 单链表 C. 双链表 B. 仅有头结点的单循环链表 D. 仅有尾指针的单循环链表个结点时,用 X 保存被删结点的值,则执行 _______________________。 A.X = top; top = top->next; C. top = top->next; X = top->data; 4. 一维数组和线性表的区别是_____________。 A. 前者长度固定,后者长度可变 C. 两者长度均固定 B. 后者长度固定,前者长度可变 D. 两者长度均可变 B. X = top->data; D. X = top->data; top = top->next;

5. 稀疏矩阵一般的压缩存储方法有两种,即______________________。 A. 二维数组和三维数组 C. 三元组和十字链表 6. 不带头结点的单链表 simpleList 为空的判定条件是 A. simpleList == null C. simpleList->next = simpleList B. 三元组和散列 D. 散列和十字链表 。 B. simpleList->next == null D. simpleList! = null

9. 采用邻接表存储的图的深度优先遍历算法类似于二叉树的____________________。 A. 先序遍历 C. 后序遍历 B. 中序遍历 D. 按层遍历

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

C1

1 A

1K

Q

A.

B.

C.

D.

图5

8.一个 5 位的二进制加计数器,由 00000 状态开始,经过 75 个时钟脉冲后,此计数器的状态

为

:

A.01011

B.01100

C.01010

D.00111

9.为了构成 4096×8 的 RAM,需要

片 1024×2 的 RAM。

A.8 片

B.16 片

C.2 片

浙江理工大学

2017 年硕士研究生招生考试初试试题

考试科目:数字电路

代码:990

(请考生在答题纸上答题,在此试题纸上答题无效)

一、填空题(每空 1.5 分,共 15 分)。

1. ABC AD 在四变量卡诺图中有( )个小方格是“1”。 2. 如果对键盘上 108 个符号进行二进制编码,则至少要( )位二进制数码。 3.A/D 转换的过程可分为( )、保持、量化、编码 4 个步骤。 4. 在 CMOS 门电路中,输出端能并联使用(或线与)的电路有( );

1.下列四个数中与十进制数(163)10 不相等的是

。A.(A3)16来自B.(10100011)2C.(000101100011)8421BCD

D.(100100011)8

2.若已知 XY Y Z YZ XY Y ,判断等式 (X Y )(Y Z)(Y Z) (X Y )Y 成立的最简单方法是依

VDD

G1

S

&

Q

Cd

R

&

vIQ

R1

RD

DISC 7 4 8

R2

vI1VD6D 555 3

vO

vC

vI2 2 R1 5

C

C

≥1

1 0.01μvFo

G2

图1

Rd

G1

G2

图2

图3

7. 将一个包含有 32768 个基本存储单元的存储电路设计 16 位为一个字的 ROM。该 ROM 有( )

根地址线。

8.由 555 定时器构成的电路如图 2 所示,该电路的名称是( )。

A& B

C EN

K 1

V

vO/V 4.3

vI/V 1.1

0.2 0

vI/V

0

10kΩ

R1

(a)

(b) 图7 表1

ABC

K

电压表读数/ V

0 0 0 断开

0 0 1 断开

1

1 0 闭合

1

1 1 闭合

4.图 8 所示电路是由 3 线-8 线译码器 74HC138 及门电路构成的地址译码电路。试分析电路工作原 理,并列出此译码电路每个输出对应的地址关系表,要求输入地址 A7A6A5A4A3A2A1A0 用十六进制表 示。(10 分)

9.已知某电路的输入输出波形如图 3 所示,则该电路可能为( )。

10.门电路参数输入输出参数 VIH(min)、VIL(max)、VOH(min)和 VOL(max)由小到大的排列正确的是( )。

二、选择题在每小题列出的四个备选项中只有一个是符合题目要求的,请将其代码填写在题后的括

号内(本大题共 10 小题,每小题 3 分,共 30 分)。

5. 8 线—3 线优先编码器 74LS148 的优先编码顺序是 I7 、 I 6 、 I5 、…、 I 0 ,输出为 Y2 Y1 Y0 。输入

输出均为低电平有效。当输入 I7 I 6 I5 … I 0 为 11010101 时,输出 Y2 Y1 Y0 为( )。

6.图 1 为与非门组成的基本 SR 锁存器,为使锁存器处于“置 1”状态,其 S R 应为( )。

vC

R 1

vC

vO

0

t

C

vO

0

t

图9

第 3 页 ,共 5 页

6.10 位 R-2R 网络型 D/A 转换器如图 10 所示: (1)求输出电压的取值范围; (2)若要求输入数字量为 200H 时输出电压 vO=5V,试问 VREF 应取何值?

G1

A

1

F

EN

G2

G3

A

&

F

A

≥1

悬空

F

100Ω

。

VCC

1kΩ G4

A

=1 F

A.

B.

C.

D.

图4

5.用取样法消除两级与非门电路中可能出现的冒险,以下说法哪一种是正确并优先考虑的 ?

A.在输出级加正取样脉冲

B.在输入级加正取样脉冲

C.在输出级加负取样脉冲

D.在输入级加负取样脉冲

6.比较两位二进制数 A=A1A0 和 B=B1B0,当 A>B 时输出 F=1,则 F 表达式是

。

A. F A1 B1

B. F A1 A0 B1 B0

C. F A1 B1 A1 B1A0 B0

D. F A1 B1 A0 B0

7.电路如图 5 所示。实现 Qn1 Qn A 的电路是

。

A

& 1D Q

CP

C1

Q

Q 1S

CP

C1

Q

A 1R

A

& 1J

Q

CP

C1

Q

1 1K

Q 1J

CP

图6

2 . 若 两 个 逻 辑 变 量 X 、 Y 同 时 满 足 X+Y=1 和 XY = 0 , 则 有 X Y 。 利 用 该 公 理 证 明 : ABCD A B C D AB BC CD DA 。 (8 分)

第 2 页 ,共 5 页

3. 图 7(a)所示为 LSTTL 门电路,其电气特性曲线如图 7(b)所示。请详细分析在 4 种不同给定 条件下图(a)所示电路的工作原理,并将电压表的读数填入表 1 中。假设电压表的内阻≥100kΩ。 (8 分)

D.4 片

10.哪种器件中存储的信息在掉电以后即丢失

?

A.SRAM

B.UVEPROM

C.E2PROM

D.PAL

三、分析计算题(总分 63 分)

1.根据图 6 所示波形图,写出逻辑关系表达式 Z= f(A,B,C),并将表达式简化成最简或非-或非 表达式和最简与-或-非表达式。 (9 分)

A B C Z

A0

A0

Y0

A1

A1

Y1

A2

A2

Y2

Y3

A3

E1

Y4

A4 A5

&

E2

A6 A7

≥1

E3

Y5 Y6 Y7

图8

5.图 9 所示的电路是用施密特触发器构成的多谐振荡器,电源工作电压 VDD=5V,施密特触发器 的阈值电压分别为 VT+=3V 和 VT—=2V,试分析电路的工作原理,画出电容器 C 两端电压 vC 和输出 电压 vO 的波形。如要使输出波形的占空比可调,试问电路要如何修改?当电容为 0.1μF 时,设计一 组参数,使输出方波频率为 1KHz,占空比为 75%。(12 分)

据

。

A .代入规则

B.对偶规则 C.反演规则 D.反演定理

3. 对 CMOS 门电路,以下

说法是错误的。

A.输入端悬空会造成逻辑出错

B.输入端接 510kΩ 的大电阻到地相当于接高电平

C.噪声容限与电源电压有关

D.输入端接 510Ω 的小电阻到地相当于接低电平

第 1 页 ,共 5 页

4.设图 4 所示电路均为 LSTTL 门电路,能实现 F A 功能的电路是