LED芯片封装缺陷检测方法研究

半导体光刻中晶圆缺陷问题的研究

半导体光刻中晶圆缺陷问题的研究半导体光刻是一项关键的技术,用于制造集成电路中的微型器件。

在光刻过程中,光源通过光学系统将图案投射到晶圆上,以形成集成电路的图案。

然而,晶圆上的缺陷问题是一个常见的挑战,可能对电路性能产生负面影响。

研究半导体光刻中晶圆缺陷问题至关重要。

通过深入研究这一问题,我们可以识别缺陷的来源,寻找解决方法,并进一步提高光刻技术的质量和效率。

1. 缺陷的来源晶圆缺陷可以分为两类:内部和外部来源。

内部缺陷主要由晶圆制造过程中的杂质、结构缺陷或薄膜不均匀性引起。

外部缺陷主要由杂质、尘埃或环境条件引入光刻机器中。

这些缺陷可能会导致光刻过程中图案的形变、分辨率降低和器件性能的下降。

2. 缺陷评估方法为了评估晶圆上的缺陷问题,一些常见的方法包括扫描电子显微镜(SEM)、光学显微镜、拉曼光谱和原子力显微镜(AFM)。

这些方法可以帮助我们观察和分析晶圆上的缺陷,了解其形态、大小和位置。

3. 解决方法针对晶圆上的缺陷问题,我们可以采取多种方法来解决。

优化晶圆的制备过程,确保杂质和结构缺陷的控制。

加强半导体设备的清洗和维护,以减少外部缺陷的影响。

改进光刻机器的性能和控制系统,提高图案的分辨率和稳定性。

4. 个人观点和理解在我看来,研究半导体光刻中晶圆缺陷问题对于高质量的集成电路制造至关重要。

通过深入了解晶圆上缺陷的来源和评估方法,我们可以更好地解决该问题,并提高光刻技术的可靠性和稳定性。

我认为研究者还应该关注新的解决方法和技术,以应对不断发展的半导体行业的挑战。

半导体光刻中晶圆缺陷问题的研究对于提高集成电路制造的质量和效率至关重要。

通过深入研究晶圆缺陷的来源、评估方法和解决方法,我们可以更好地理解和应对该问题。

我对于研究者在这一领域的努力和创新充满期待,并期望看到更多的突破和进展。

1. 问题的重要性和背景晶圆上的缺陷对于半导体光刻技术的可靠性和稳定性至关重要。

晶圆是制造集成电路的基础,任何缺陷都可能导致电路的故障或性能下降。

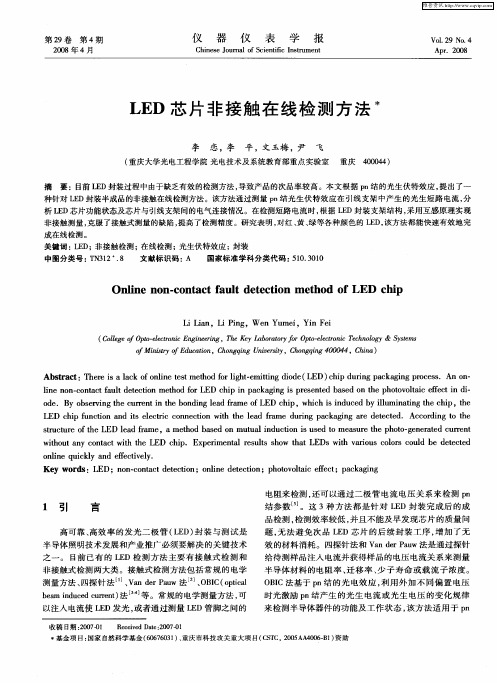

LED芯片非接触在线检测方法

E h c o n se cr o n c o i h e a u n ak g gaed t e L D c i fnt na di l tccn et n wt tel df med r gp ca n r eet .A c rigt te pu i t e i i h a r i i c d codn oh

Ke o d : E n ncnat e c o ;ol ed tc o ;p o vh i e et p ca n yw r s L D; o — t t t n ni e t n h t o a f c; ak g g o cdei n ei o c i

电阻来 检 测 , 还可 以通 过二 极 管 电 流 电 压 关 系 来 检 测 p n

L D 芯 片 非 接触 在 线 检 测 方 法 米 E

李 恋 ,李 平 ,文 玉梅 ,尹 飞

404 ) 00 4

( 重庆 大学 光电工程 学院 光 电技 术及系统教育部重 点实验室 重庆 摘

要 :目前 L D封装过程 中由于缺乏有效 的检测方法 , E 导致产品 的次 品率 较高 。本文 根据 p n结 的光生伏特效 应 , 提出 了一

A s at T eei a ako l e et e o rih—miigdo e L D) hpd r gpc a i rcs.A n b t c : h r s c f ni s m t df g t tn id ( E c i u n ak g gpoes no — r l o n t h ol e t i n

ห้องสมุดไป่ตู้

种针对 L D封装半成 品的非 接触 在线 检测 方法。该 方法通过测量 p E n结光 生伏 特效应在 引线 支架 中产生 的光生短 路 电流 , 分 析 L D芯片功能状态及芯 片与引线支架 间的电气 连接情 况 。在检测短路 电流时 , E 根据 L D封装 支架结构 , E 采用 互感原理 实现 非 接触 测量 , 克服 了接触式测量 的缺 陷 , 提高了检测精度 。研究表 明 , 对红 、 绿等各种颜色 的 L D, 黄、 E 该方法 都能快速有效地完

led芯片检验报告

LED芯片检验报告1. 背景介绍LED(Light Emitting Diode)芯片是一种半导体器件,具有发光功能。

在各种电子产品中广泛应用,例如照明灯具、显示屏等。

为了确保产品质量和性能稳定性,LED芯片在生产过程中需要经过严格的检验。

2. 检验步骤LED芯片的检验过程可以分为以下几个步骤:2.1 外观检查LED芯片的外观检查主要包括以下几个方面: - 确保芯片外观没有明显的破损或变形; - 检查芯片表面是否有杂质、污渍等; - 观察芯片引脚的连接情况,确保没有松动。

2.2 电性能测试LED芯片的电性能测试是检验其电特性的关键步骤,包括以下几个方面: - 测试芯片的正向电压(Forward Voltage)和正向电流(Forward Current); - 测试芯片的反向电流(Reverse Current)和反向电压(Reverse Voltage); - 测试芯片的发光亮度和色温。

2.3 光学性能测试LED芯片的光学性能测试是检验其光特性的重要步骤,包括以下几个方面: -测试芯片的发光角度,以确定其发光范围; - 测试芯片的发光强度,以评估其亮度;- 测试芯片的色彩均匀性,以检查是否有色差。

2.4 寿命测试LED芯片寿命测试是为了评估其使用寿命和稳定性,常见的寿命测试方法包括:- 连续工作时间测试,以观察芯片在长时间工作下是否会出现性能变化; - 温度变化测试,以模拟不同环境下芯片的工作情况; - 开关次数测试,以模拟芯片开关频繁情况下的可靠性。

3. 检验结果分析根据LED芯片的检验结果,可以对其质量进行评估和分析,包括以下几个方面:- 外观检查结果是否符合要求,是否存在破损或污渍等问题; - 电性能测试结果是否在规定范围内,是否满足产品要求; - 光学性能测试结果是否达到预期的亮度和色彩要求; - 寿命测试结果是否符合产品设计寿命要求。

4. 结论LED芯片检验报告通过对芯片的外观、电性能、光学性能和寿命进行全面测试,评估了其质量和性能。

芯片封装基本流程及失效分析处理方法

芯片封装基本流程及失效分析处理方法一、芯片封装芯片封装的目的在于对芯片进行保护与支撑作用、形成良好的散热与隔绝层、保证芯片的可靠性,使其在应用过程中高效稳定地发挥功效。

二、工艺流程流程一:硅片减薄分为两种操作手段。

一是物理手段,如磨削、研磨等;二是化学手段,如电化学腐蚀、湿法腐蚀等,使芯片的厚度达到要求。

薄的芯片更有利于散热,减小芯片封装体积,提高机械性能等。

其次是对硅片进行切割,用多线切割机或其它手段如激光,将整个大圆片分割成单个芯片。

流程二:将晶粒黏着在导线架上,也叫作晶粒座,预设有延伸IC晶粒电路的延伸脚,用银胶对晶粒进行黏着固定,这一步骤为芯片贴装。

流程三:芯片互联,将芯片焊区与基板上的金属布线焊区相连接,使用球焊的方式,把金线压焊在适当位置。

芯片互联常见的方法有,打线键合,载在自动键合(TAB)和倒装芯片键合。

流程四:用树脂体将装在引线框上的芯片封起来,对芯片起保护作用和支撑作用。

包封固化后,在引线条上所有部位镀上一层锡,保证产品管脚的易焊性,增加外引脚的导电性及抗氧化性。

流程五:在树脂上印制标记,包含产品的型号、生产厂家等信息。

将导线架上已封装完成的晶粒,剪切分离并将不需要的连接用材料切除,提高芯片的美观度,便于使用及存储。

流程六:通过测试筛选出符合功能要求的产品,保证芯片的质量可靠性;最后包装入库,将产品按要求包装好后进入成品库,编带投入市场。

三、芯片失效芯片失效分析是判断芯片失效性质、分析芯片失效原因、研究芯片失效的预防措施的技术工作。

对芯片进行失效分析的意义在于提高芯片品质,改善生产方案,保障产品品质。

四、测试方法1、外部目检对芯片进行外观检测,判断芯片外观是否有发现裂纹、破损等异常现象。

2、X-RAY对芯片进行X-Ray检测,通过无损的手段,利用X射线透视芯片内部,检测其封装情况,判断IC封装内部是否出现各种缺陷,如分层剥离、爆裂以及键合线错位断裂等。

3、声学扫描芯片声学扫描是利用超声波反射与传输的特性,判断器件内部材料的晶格结构,有无杂质颗粒以及发现器件中空洞、裂纹、晶元或填胶中的裂缝、IC封装材料内部的气孔、分层剥离等异常情况。

led封装实验报告

led封装实验报告LED封装实验报告引言:近年来,随着科技的飞速发展,LED(Light Emitting Diode)作为一种新型的照明装置,逐渐在各个领域得到广泛应用。

本实验旨在通过对LED封装过程的研究与实践,探究其原理和技术,并对其性能进行评估。

一、实验目的本实验的主要目的是研究LED封装过程中的关键技术和参数,探究其对LED性能的影响,并通过实验数据分析和对比,评估不同封装工艺对LED性能的影响。

二、实验原理LED封装是将LED芯片与外部环境隔离,并提供电气连接和机械保护的过程。

封装过程中的关键技术包括芯片粘合、导线焊接、封装胶固化等。

不同的封装工艺和材料选择会对LED的光电性能产生重要影响。

三、实验步骤1. 芯片粘合:将LED芯片粘贴在导电胶水上,确保芯片与基板之间的良好接触。

2. 导线焊接:将导线焊接到芯片的金属引脚上,以实现电气连接。

3. 封装胶固化:使用特定的封装胶固化装置,对封装胶进行固化,以提供机械保护和光学性能。

四、实验结果与分析通过实验数据的记录和分析,我们可以得出以下结论:1. 不同的芯片粘合技术会对LED的热导性能产生影响,影响LED的散热效果。

2. 导线焊接的质量直接影响LED的电气连接性能,焊接不良会导致电流传输不畅,影响LED的亮度和稳定性。

3. 封装胶的固化时间和温度对LED的机械保护和光学性能有重要影响,过长或过短的固化时间都会影响LED的稳定性和寿命。

五、实验总结通过本次实验,我们深入了解了LED封装的原理和技术,了解了不同封装工艺对LED性能的影响。

同时,我们也认识到在实际应用中,除了封装过程本身,LED的性能还受到其他因素的影响,如芯片质量、散热设计等。

因此,在实际应用中,需要综合考虑多个因素,以实现最佳的LED性能。

六、展望随着科技的不断进步,LED封装技术也将不断创新和完善。

未来,我们可以进一步研究和探索LED封装过程中的新材料、新工艺和新技术,以提高LED的光电性能和应用范围。

半导体器件中的深度缺陷检测和测量

半导体器件中的深度缺陷检测和测量半导体器件是一种重要的电子元器件,广泛应用于现代电子技术中。

半导体器件的制造需要考虑到许多参数,其中最重要的是电子能级。

电子能级对半导体器件的性能和特性具有很大影响,如果存在深度缺陷,则会导致半导体器件的性能下降或完全失效。

因此,深度缺陷检测和测量是半导体器件制造中的一项关键技术。

深度缺陷指的是在半导体材料中存在的能级深的空穴或电子态。

它们的存在会影响半导体器件的性能和可靠性。

因此,深度缺陷的检测和测量是半导体器件的关键过程。

目前,许多成熟的深度缺陷检测和测量技术已广泛应用于半导体器件制造中。

首先,注入电荷法是一种常用的深度缺陷检测方法。

该方法利用瞬态电流的反应来测量深度缺陷。

它需要在测试中施加电荷,并测量在电荷注入期间电流的变化。

根据这些数据,可以计算出存在于被测材料中的缺陷浓度和深度分布。

此外,激光光谱学也是一种常用的深度缺陷检测方法。

该方法是通过激光光谱法来测量半导体材料中的光吸收谱。

在这种方法中,激光产生的光会与半导体材料相互作用,激发其中的电子和空穴等载流子。

半导体材料吸收了激光光子后,它的运动状态会发生变化,光吸收谱也会随之变化。

通过分析这些变化,可以得出半导体材料中深度缺陷的位置和浓度等信息。

此外,Ti:sapphire激光微打孔技术也是一种常用的深度缺陷检测方法。

这种技术利用激光微打孔技术来破坏半导体材料的结构,然后通过分析微打孔后电流和电压的变化来检测深度缺陷。

这种方法能够检测到非常细微的缺陷,因此非常适合用于半导体器件的制造。

总之,深度缺陷检测和测量是半导体器件制造中非常关键的过程。

目前,众多的深度缺陷检测和测量技术已经成熟应用于半导体器件的制造中,并得到了广泛应用。

对于半导体器件制造过程的控制和质量保证来说,这些技术都具有非常重要的意义。

芯片缺陷检测

芯片缺陷检测芯片缺陷检测技术是保证芯片质量的重要手段之一,它可以有效地发现芯片生产过程中存在的各种缺陷,从而提高产品的可靠性和性能。

本文将针对芯片缺陷检测技术进行详细介绍,包括芯片缺陷的类型、常用的缺陷检测方法和检测设备,以及对未来芯片缺陷检测技术的展望。

芯片缺陷的类型主要有以下几种:结构缺陷、材料缺陷和功能缺陷。

结构缺陷是指芯片内部结构的缺陷,如硅片上的金属线路断裂和电流漏露等;材料缺陷是指芯片材料本身存在的缺陷,如晶体缺陷和氧化层中的杂质等;功能缺陷是指芯片在工作过程中出现的功能异常,如逻辑电路错误和存储单元故障等。

不同类型的缺陷需要采用不同的检测方法。

常用的芯片缺陷检测方法包括光学检测、电子显微镜检测、X射线检测和电子束检测等。

光学检测是最常用的一种方法,它利用光学显微镜对芯片进行观察和分析,可以检测到一些表面缺陷和结构缺陷;电子显微镜检测利用高分辨率的电子显微镜对芯片进行观察和分析,可以检测到更小尺寸和更细微的缺陷;X射线检测利用X射线对芯片进行照射,通过照射后产生的散射和吸收来检测缺陷;电子束检测是一种高分辨率的检测方法,通过电子束对芯片进行扫描和分析,可以检测到更小尺寸的缺陷。

除了上述常用的检测方法外,还有一些新兴的芯片缺陷检测方法值得关注。

例如超声波检测技术可以通过对芯片进行超声波照射和接收来检测内部结构缺陷;红外热像仪检测技术可以通过对芯片进行红外热像仪照射和观察来检测温度异常和热点;激光干涉检测技术可以通过对芯片进行激光干涉测量来检测表面形貌和薄膜厚度等。

芯片缺陷检测设备的发展也得到了长足的进步,从最初的手工检测到自动化检测,从单一检测设备到多功能综合检测设备。

现在的芯片缺陷检测设备已经具备了高分辨率、高灵敏度和高效率的特点,可以实现快速准确地检测芯片缺陷,提高生产效率和产品质量。

未来,芯片缺陷检测技术将继续朝着更高的分辨率、更深的检测范围和更快的速度发展。

随着芯片尺寸的不断缩小和芯片功能的不断增强,对缺陷的检测要求也会越来越高。

LED照明产品检测方法的决陷和改善的对策

与 传 统 光 源不 同 的是 ,仅 仅 保持

L D模 块测量环境 的一样是无法保证测 E

量 结 果 的 重复 性 的。

特 点:这种 方法看似 比较严 密 ,但 实 际上 ,它 的热平衡 条件和工作条 件与 此类LE D装入 最终 的照 明器具 中 的状态

仍 没 有 好 的 关 联 性 ,所 以 所 测 光 电参 数

功率和热 阻系数 的不准确 ,所 以测量精

度 比较 低 ;

3 4

分 辨率 要求高 , 只能测量未 封装 的单个

裸 芯 片 ,不 能测 量 封 装 后 L D; E

量 一次 ;

从2 ℃ 到 10 5 3  ̄ 测 时 问 约 为25 小 C检 .个

5利 用二极 管P ) N结电压与结 温的Vf T 关 系曲线 ,来测量L D的结温。 - I E

■ 技 应用T c n lg n p l ain ■ 术 e h oo ya da pi t c o

LD E 照明产品检测方法的 缺陷和改善的对策

俞安琪 国家 电光源质量监督检验 中心( 海) 上 副主任

一

厅 吾

用有 明显差异,不具有可参比性。 第 二种检测 方法是把L ED模块 安装 在 检 测装 置上 后 ,可 能 带上 一 固定 的

准 和 检 测 方 法 的 回顾 、 小 结 的 时候 已经 基本到来 。

结 温 的不 同会 造 成 这 些参 数 的明显 不 同 ,所 以测 量 ,L ED的光 电参 数首 先

应 考 虑在 设 定 的 工作 结 温 的条 件 下 来

进行 。

LED达 到 热 平衡 时开始 测 量 它 的光 电

试 验 的 可 复 现 性 。如 可 能 监 测 L D模 块 E

采用光生伏特效应的LED芯片在检测方法上的研究(doc)

采用光生伏特效应的LED芯片在检测方法上的研究(doc)摘要:基于pn结的光生伏特效应,本文研究了一种非接触式LED芯片在线检测方法。

通过测量pn结光生伏特效应在引线支架中产生的光生电流,检测LED封装过程中芯片质镀及芯片与支架之间的电气连接状态。

通过分析pn结光生伏特效应的等效电路,详细论述了半导体材料的各种参数及等效电路中各电参数与支架上流过的光生电流的关系。

实验对各种不同颜色的LED样品进行了测量。

研究表明,该方法可以实现LED芯片的在线检测,有较大的应用价值。

1、引言发光二极管(LED)以其体积小、响应速度快、寿命长、可靠性高、功耗低等优点已广泛应用于指示、显示、普通照明等领域[1-3]。

随着其应用范围的不断扩大,提高LED产品的可靠性和稳定性,降低其生产成本成为不可忽视的问题,因此LED生产过程中的质量检测显得尤为重要。

目前对LED的检测主要集中在封装前的晶片检测及封装完成后的成品检测。

晶片检测主要是针对LED的核心结构pn结的检测,包括EBIC(electronbeam induced current)【4-5】别、OBIC(optical beam in—duced current)【6-7】、SPV(surface photovohaic)【8】及SQUID(superconducting quantum interference device)法[9-10]等。

其中EBIC、OBIC和SPV法都是基于半导体的光电效应,通过接触式测量电子束或者光激励半导体产生的电流或电压的变化规律来检测半导体器件的参数、功能及工作状态。

SQUID法则是通过非接触方式测苣光电流产生的磁场分布来实现pn结的检测,但由于磁场变化极其微弱,必须采用超导量子磁强计(SQUID),检测仪器系统构成非常复杂,且价格昂贵。

这几种方法都不适用于大批量牛产的在线应用。

目前在LED生产过程中在线应用的测量方式都是针对封装完成后的成品检测,如LED分光分色机等。

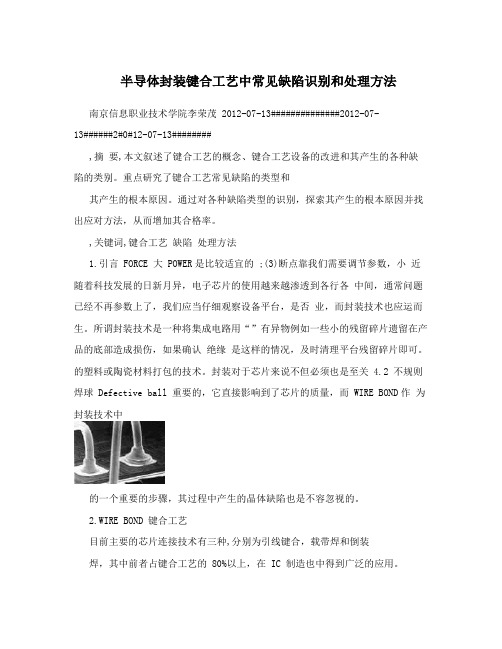

半导体封装键合工艺中常见缺陷识别和处理方法

半导体封装键合工艺中常见缺陷识别和处理方法南京信息职业技术学院李荣茂 2012-07-13##############2012-07-13######2#0#12-07-13########,摘要,本文叙述了键合工艺的概念、键合工艺设备的改进和其产生的各种缺陷的类别。

重点研究了键合工艺常见缺陷的类型和其产生的根本原因。

通过对各种缺陷类型的识别,探索其产生的根本原因并找出应对方法,从而增加其合格率。

,关键词,键合工艺缺陷处理方法1.引言 FORCE 大 POWER是比较适宜的 ;(3)断点靠我们需要调节参数,小近随着科技发展的日新月异,电子芯片的使用越来越渗透到各行各中间,通常问题已经不再参数上了,我们应当仔细观察设备平台,是否业,而封装技术也应运而生。

所谓封装技术是一种将集成电路用“”有异物例如一些小的残留碎片遗留在产品的底部造成损伤,如果确认绝缘是这样的情况,及时清理平台残留碎片即可。

的塑料或陶瓷材料打包的技术。

封装对于芯片来说不但必须也是至关 4.2 不规则焊球 Defective ball 重要的,它直接影响到了芯片的质量,而 WIRE BOND作为封装技术中的一个重要的步骤,其过程中产生的晶体缺陷也是不容忽视的。

2.WIRE BOND 键合工艺目前主要的芯片连接技术有三种,分别为引线键合,载带焊和倒装焊,其中前者占键合工艺的 80%以上,在 IC 制造也中得到广泛的应用。

引线键合是半导体封装制程的一站,自晶粒 (Die或 Chip)各电极上,以金线或铝线进行各式打线结合,再牵线至脚架(Lead Frame)的各内脚处续行打线以完成回路,这种两端打线的工作称为 WireB ond。

Wire bond 图 2 不规则焊球在芯片封装厂称为前工序,又叫做金属线键合是将 die 的 PAD飞线连如图 2 所示金线打在芯片上的球并非圆形且球与球的大小厚度还接到外部封装的 BALL 的工序。

不一样,表示同一粒芯片上的球是不规则的,一粒芯片大约有百来粒 3.键合工艺为什么会产生缺陷球,有可能只有一到两粒是产生这样异常的,可对质量的影响确是大打 3.1 键合工艺产生缺陷的原因折扣。

半导体光刻中晶圆缺陷问题的研究

半导体光刻中晶圆缺陷问题的研究在半导体制造过程中,光刻技术被广泛应用于芯片的制造。

光刻是通过使用光源、掩模和投影透镜等工具,在晶圆表面上定义形状和位置的一种方法。

然而,光刻过程中晶圆缺陷问题是一项非常重要的研究课题。

晶圆缺陷问题对芯片制造质量以及设备可靠性等方面都有着重要影响。

晶圆缺陷指的是晶圆表面或内部存在的缺陷,例如微裂纹、气泡、颗粒和缺陷等。

这些缺陷可能导致芯片器件性能不稳定,甚至失效。

因此,研究晶圆缺陷问题对于提高芯片制造质量和设备可靠性至关重要。

首先,光刻过程中晶圆缺陷的形成机理是研究的重点之一。

晶圆缺陷的形成与光刻过程中的物理和化学反应有关。

例如,光刻胶在曝光和显影等过程中会释放出化学物质,这些化学物质会对晶圆表面产生腐蚀和侵蚀作用,从而引起缺陷的形成。

此外,光刻过程中的光能量和热能也会对晶圆材料产生应力,导致晶圆表面产生应变,从而引发缺陷的生成。

因此,研究晶圆缺陷的形成机理,可以帮助我们更好地理解光刻过程中的缺陷生成机制,从而采取相应的措施来减少晶圆的缺陷。

其次,研究晶圆缺陷问题还包括缺陷检测和监控。

在光刻过程中,及时发现和识别晶圆上的缺陷非常重要。

因此,需要开发出高分辨率的缺陷检测设备和技术,能够实现对晶圆表面和内部的缺陷进行快速、准确的检测。

传统的缺陷检测技术包括光学检测、扫描电子显微镜(SEM)和原子力显微镜(AFM)等。

但是,由于晶圆上的缺陷数量和尺寸在不断减小,传统的检测技术已经很难满足需求。

因此,研究如何开发出更高分辨率、更灵敏的缺陷检测设备和技术,成为一个重要的课题。

最后,研究晶圆缺陷问题还需要探索缺陷修复和缺陷防治的方法。

一旦在晶圆上发现了缺陷,那么将如何进行修复是一个非常重要的问题。

目前,常见的缺陷修复方法包括化学机械抛光(CMP)、激光修复和等离子修复等。

这些方法可以将晶圆上的缺陷进行修复,从而提高芯片的制造质量。

此外,研究如何预防晶圆缺陷的生成也是非常重要的。

LED照明产品检测方法中的缺陷和改善的对策

LED照明产品检测方法中的缺陷和改善的对策目前LED照明产品成为了照明行业的主流产品,因其节能、环保等优点。

然而,在大规模应用过程中,经常会出现一些质量问题。

因此,为了保证LED照明产品的品质和性能,进行合理的检测是非常重要的。

然而,在现有的检测方法中存在一些缺陷,导致了一些问题的遗漏或误判。

以下是一些常见的缺陷和改善对策:1.光通量测试缺陷:光通量是LED照明产品最重要的参数之一,但现有的测试方法主要是通过单一的光探测器测量,不完全准确。

这可能会导致在生产中出现光通量不稳定或不合格的情况。

为了解决这个问题,可以将多个光探测器布置在不同位置,全面检测光通量,并进行多次测试取平均值,以提高测试结果的准确性。

2.色彩一致性测试缺陷:对于一些特定应用,如商业照明和舞台灯光,色彩一致性是至关重要的。

然而,现有的测试方法往往只测试产品的色温和色坐标,无法完全反映产品在实际使用中的色彩一致性。

为了改善这个问题,可以考虑加入人眼感知的测试仪器,如光谱辐射计,以更全面地评估产品的色彩一致性。

3.散热性能测试缺陷:由于LED照明产品长时间工作会产生大量的热量,散热性能是一个关键的指标。

然而,现有的测试方法主要是通过温升测量或热阻测量,不能完全反映产品在实际使用中的散热效果。

为了解决这个问题,可以考虑采用红外热成像仪等非接触式测试方法,实时监测产品的温度分布,以更准确地评估产品的散热性能。

4.寿命测试缺陷:寿命是衡量LED照明产品质量的关键指标,但现有的测试方法主要是通过加速寿命测试,可能无法完全模拟实际使用环境下的寿命。

为了改善这个问题,可以考虑采用长时间稳定工作的测试方法,例如在真实使用环境下长时间监测产品的性能衰减情况,以更准确地评估产品的寿命。

5.环境适应性测试缺陷:LED照明产品通常需要在不同的环境条件下使用,包括温度、湿度、振动等。

然而,现有的测试方法主要是在固定环境条件下进行测试,无法全面评估产品的环境适应性。

led封装实验报告

led封装实验报告LED封装实验报告引言LED(Light Emitting Diode)作为一种新型的光源,具有节能、长寿命、环保等优点,被广泛应用于照明、显示、通信等领域。

LED封装是LED制造过程中的重要环节,直接影响LED的性能和稳定性。

本实验旨在探究LED封装的工艺流程和影响因素,为LED的生产提供参考和指导。

实验目的1. 了解LED封装的工艺流程;2. 探究LED封装中的关键影响因素;3. 分析LED封装对LED性能的影响。

实验材料和仪器1. LED芯片;2. 封装胶;3. 封装模具;4. 封装设备(封装机、烘箱等);5. 测试仪器(光度计、电流表、电压表等)。

实验步骤1. 准备LED芯片和封装胶;2. 将LED芯片放入封装模具中;3. 加入封装胶并进行封装;4. 将封装后的LED芯片放入烘箱中进行固化;5. 进行LED性能测试,包括光通量、色温、色彩均匀度等指标。

实验结果与分析1. 工艺流程:LED封装的工艺流程主要包括芯片贴合、封装胶注入、固化等环节。

每个环节都对LED的性能产生影响,需要严格控制。

2. 影响因素:封装胶的选择、封装温度、压力等因素都会影响LED的封装质量和性能稳定性。

尤其是封装胶的选择对LED的光通量和色温影响较大。

3. 性能测试:经过封装后的LED进行了性能测试,结果显示封装质量良好,光通量、色温等指标符合要求。

结论LED封装是LED制造过程中的关键环节,对LED的性能和稳定性有着重要影响。

通过本实验,我们了解了LED封装的工艺流程和影响因素,为LED生产提供了参考和指导。

在今后的LED生产中,需要严格控制封装工艺,选择合适的封装胶和工艺参数,以确保LED产品的质量和性能稳定性。

LED照明产品检测方法中的缺陷和改善的对策

LED照明产品检测方法中的缺陷和改善的对策一、现有LED照明产品检测方法存在的问题1.检测方法单一化。

目前市面上大部分LED照明产品检测方法仍停留在单一参数的测试阶段,往往只注重对光通量、色温等基本参数的测量,而对于产品的色彩渲染指数、光束角度等重要参数的检测往往被忽略。

2.检测精度不高。

在实际应用中,LED照明产品的性能和特性十分复杂,存在很多不确定性因素,因此仅仅通过传统的检测方法往往无法准确评估产品的性能和质量,导致检测结果不够准确和可靠。

3.检测成本较高。

传统的LED照明产品检测方法通常需要专业的检测设备和技术人员进行操作,需要较高的检测成本,对于一些中小型LED照明产品生产企业而言往往难以承受。

4.检测效率低下。

由于现有检测方法通常需要进行多轮测试和数据分析,检测时间较长,且存在复杂的操作流程和步骤,导致检测效率较低,无法满足实际生产需求。

二、改进建议1.多参数综合检测。

建议在LED照明产品检测中引入多参数综合检测方法,考虑到产品性能的多样性和复杂性,同时充分考虑产品的各项参数指标,确保检测结果更加全面和准确。

2.引入先进检测技术。

随着科技的发展,LED照明产品检测技术也在不断更新和完善,可以引入先进的检测设备和技术,如光电子测量技术、光学成像技术等,提高检测的精度和准确性。

3.简化检测流程。

优化检测流程和操作步骤,简化检测操作,降低检测成本和人力成本,提高检测效率,提供更加便捷和高效的检测服务。

4.开发智能化检测工具。

可以研发智能化的LED照明产品检测工具,如智能检测仪器、检测软件等,实现自动化和智能化检测,提高检测效率和准确性,降低人力和时间成本。

5.加强标准化管理。

建议LED照明产品检测遵循一定的标准和规范,加强对检测数据的管理和分析,确保检测结果的可靠性和可比性,提高产品质量和竞争力。

综上所述,LED照明产品检测方法存在着诸多问题和挑战,但通过采取相应的改进建议,可以有效提高检测效率和准确性,保障LED照明产品质量,促进LED照明产业的健康发展。

半导体缺陷检测 流程

半导体缺陷检测的流程一般包括以下步骤:

1. 芯片准备:将芯片从封装中取出,并清洁芯片表面和测试点。

2. 功能测试:通过编写测试程序,对芯片进行功能测试,以验证芯片是否正常工作。

3. 电学测试:通过测量芯片的电学参数,如电压、电流、电阻等,对芯片进行电学测试,以验证芯片的电学性能是否符合要求。

4. 光学测试:通过使用激光扫描仪等设备,对芯片的外观和表面缺陷进行光学测试。

5. 机械测试:通过测试芯片的机械性能,如硬度、韧性等,验证芯片是否具有良好的耐用性。

此外,还有一些专门的半导体制程缺陷检测方法,包括以下步骤:

1. 建立数据库:数据库中包括多种半导体制程缺陷的图片。

2. 按照半导体制程缺陷的形貌特征,将所述半导体制程缺陷进行分类。

3. 扫描晶片,并通过识别所述半导体制程缺陷的形貌特征,在所述晶片上获得多个预选区域。

4. 通过半导体制程缺陷识别系统,提取所述预选区域中所述半导体制程缺陷的图片特征,并识别所述半导体制程缺陷的类型。

5. 根据所述半导体制程缺陷的类型,确定扫描机器的最佳扫描参数。

6. 根据所述最佳扫描参数,扫描所述晶片,并识别所述晶片上所述半导体制程缺陷的类型及位置。

当识别某一种半导体制程缺陷时,将扫描机器的参数设置为该类型半导体制程缺陷对应的最佳扫描参数时,扫描机器获得的半导体制程缺陷图片能够最清晰地显示该类型的半导体制程缺陷。

以上信息仅供参考,如有需要,建议咨询专业人士。

芯片缺陷检测

一是光学性能检测,主要参数包括工作电压,光强,波长范围,半峰宽,色温,显色指数等等,这些数据可以用积分球测试。

二是可靠性检测,主要参数包括光衰,漏电,反压,抗静电,I-V曲线等等,这些数据一般通过老化进展测试。

方片&大圆片:晶圆上的不同位置抽取九个点做参数测试:1、主要对电压、波长、亮度进展测试,能符合正常出货标准参数的晶圆片再继续做下一步的操作,如果这九点测试不符合相关要求的晶圆片,就放在一边另外处理。

2、晶圆切割成芯片后,100%的目检〔VI/VC〕,操作者要使用放大30倍数的显微镜下进展目测。

3、接着使用全自动分类机根据不同的电压,波长,亮度的预测参数对芯片进展全自动化挑选、测试和分类。

4、最后对LED芯片进展检查〔VC〕和贴标签。

芯片区域要在蓝膜的中心,蓝膜上最多有5000粒芯片,但必须保证每X蓝膜上芯片的数量不得少于1000粒,芯片类型、批号、数量和光电测量统计数据记录在标签上,附在蜡光纸的反面。

蓝膜上的芯片将做最后的目检测试与第一次目检标准一样,确保芯片排列整齐和质量合格。

这样就制成LED芯片〔目前市场上统称方片〕。

在LED芯片制作过程中,把一些有缺陷的或者电极有磨损的芯片,分捡出来,这些就是后面的散晶,此时在蓝膜上有一些不符合正常出货要求的晶片,也就自然成了边片或毛片等。

刚刚谈到在晶圆上的不同位置抽取九个点做参数测试,对于不符合相关要求的晶圆片作另外处理,这些晶圆片是不能直接用来做LED方片,也就不做任何分检了,直接卖给客户了,也就是目前市场上的LED大圆片。

漏电:静电和漏电是两个完全不同的概念,但是静电对chip的击伤可以导致漏电的增大。

3.--理论上不建议使用IR超规的外延片切割为Chip,寿命,抗静电能力,亮度都会大幅下降。

LED外延片[浏览次数:约244次]•目前LED外延片生长技术主要采用有机金属化学气相沉积方法,这种方法的引用是基于LED外延生长根本原理,LED外延生长的根本原理是在一块加热至适当温度的衬底基片〔主要有蓝宝石和SiC,Si〕上,气态物质In,Ga,Al,P有控制的输送到衬底外表,生长出特定单晶薄膜。

晶圆级Micro-LED_芯片检测技术研究进展

第 38 卷第 5 期2023 年 5 月Vol.38 No.5May 2023液晶与显示Chinese Journal of Liquid Crystals and Displays晶圆级Micro-LED芯片检测技术研究进展苏昊1,李文豪1,李俊龙1,刘慧2,王堃1,张永爱1,3,周雄图1,3,吴朝兴1,3*,郭太良1,3*(1.福州大学物理与信息工程学院,福建福州 350108;2.福建江夏学院电子信息科学学院,福建福州 350108;3.中国福建光电信息科学与技术创新实验室,福建福州 350108)摘要:随着微型氮化镓(GaN)发光二极管(LED)制造工艺的不断进步,Micro-LED显示有望成为新一代显示技术并在近眼显示、大尺寸高清显示器件、柔性屏幕等领域大放异彩。

在Micro-LED显示众多技术环节中,晶圆级Micro-LED芯片的检测是实现坏点拦截,提升显示屏良品率、降低整机制造成本的关键环节。

针对大数量(百万数量级)、小尺寸(<50 μm)的晶圆级Micro-LED芯片阵列,现有的电学检测手段存在检测效率低、成本高等缺点。

因此,提高检测效率、提升检测准确度、降低检测成本是晶圆级Micro-LED检测技术的发展趋势。

本文首先介绍了晶圆级Micro-LED芯片检测时所需要检测的几个指标,其次详细介绍并分析了现有的或已经提出的检测手段,最后对晶圆级Micro-LED芯片检测技术进行总结并展望了未来技术发展方向。

关键词:Micro-LED;缺陷检测;接触型检测;无接触检测中图分类号:TN364+.2;TN383+.1 文献标识码:A doi:10.37188/CJLCD.2022-0392Recent progress of wafer level Micro-LED chip inspection technology SU Hao1,LI Wen-hao1,LI Jun-long1,LIU Hui2,WANG Kun1,ZHANG Yong-ai1,3,ZHOU Xiong-tu1,3,WU Chao-xing1,3*,GUO Tai-liang1,3*(1. College of Physics and Information Engineering, Fuzhou University, Fuzhou 350108, China;2. College of Electronic Information Science, Fujian Jiangxia University, Fuzhou 350108, China;3. Fujian Science & Technology Innovation Laboratory for Optoelectronic Information of China,Fuzhou 350108, China)Abstract:With the continuous progress in the manufacturing process of gallium nitride (GaN)-based light-emitting diodes (LEDs), Micro-LED display is considered as an emerging display technology, which has broad prospects for near-eye display, large-scale displays device, flexible display, and other fields. The inspection of wafer-level Micro-LED chips can improve the yield of the screens and reduce the manufacturing cost of displayers,which is one of the key technologies related to Micro-LED display.For the inspection 文章编号:1007-2780(2023)05-0582-13收稿日期:2022-11-24;修订日期:2022-12-16.基金项目:国家重点研发计划(No.2021YFB3600404);闽都创新实验室自主部署项目(No.2020ZZ113)Supported by National Key Research and Development Program of China (No.2021YFB3600404);FujianScience & Technology Innovation Laboratory for Optoelectronic Information of China (No.2020ZZ113)*通信联系人,E-mail:chaoxing_wu@;gtl_fzu@第 5 期苏昊,等:晶圆级Micro-LED芯片检测技术研究进展needs of large quantity (millions of orders)and small size (<50 μm)of wafer-level Micro-LED chip arrays, the existing electrical inspection technology has the disadvantages of low inspection efficiency and high cost.Therefore,Micro-LED chips inspection technology with improving inspection efficiency,improving inspection accuracy,and reducing inspection cost is the future development trend.In this paper,several indicators required for Micro-LED chip inspection are summarized.Then,the existing or proposed inspection methods are introduced and analyzed in detail.Finally,the future development of inspection technology is prospected.Key words: Micro-LED; defect inspection; contact inspection; non-contact inspection1 引言具有功耗低、寿命长、体积小、可靠性高等优点的氮化镓基微型发光二极管(Micro-LED)有望作为新一代高效光源[1-7],应用于光通信、固态照明、显示技术等领域。

一种芯片焊线缺陷的检测方法及系统[发明专利]

![一种芯片焊线缺陷的检测方法及系统[发明专利]](https://img.taocdn.com/s3/m/091bedcdaff8941ea76e58fafab069dc50224700.png)

(19)中华人民共和国国家知识产权局(12)发明专利申请(10)申请公布号 (43)申请公布日 (21)申请号 202011365827.4(22)申请日 2020.11.29(71)申请人 惠州高视科技有限公司地址 516000 广东省惠州市惠澳大道惠南高新科技产业园华泰路南路2号科技创业中心CD栋第四层西侧(72)发明人 郭遗敏 邹伟金 王巧彬 邹双盛 周波 (74)专利代理机构 惠州市超越知识产权代理事务所(普通合伙) 44349代理人 陈文福(51)Int.Cl.G01N 21/956(2006.01)(54)发明名称一种芯片焊线缺陷的检测方法及系统(57)摘要本发明涉及一种芯片焊线缺陷的检测方法及系统,使用检测光源,将检测相机成像视野内的芯片照射均匀,使视野内芯片上的焊线均能接收到特定角度的光线;所述芯片焊线部分根据形状被分为n个区域,n≥3;所述特定角度被设置为,当光线照射到n个区域时,使其中m个区域照射到的光线被反射进入与检测相机连接的检测镜头,1≤m<n;所述m个区域在检测相机中成像为亮区域,以所述亮区域为特征点区域。

通过分析比对检测的芯片焊线的特征点区域信息与合格焊线的特征点区域信息,判断缺陷类型。

本文提出的焊线缺陷检测方法和系统,不需要3D方案,效率高且成本低。

权利要求书1页 说明书4页 附图3页CN 112179920 A 2021.01.05C N 112179920A1.一种芯片焊线缺陷的检测方法,其特征在于:使用检测光源,将检测相机成像视野内的芯片照射均匀,使视野内芯片上的焊线均能接收到特定角度的光线;所述芯片焊线部分根据形状被分为n个区域,n≥3;所述特定角度被设置为,当光线照射到n个区域时,使其中m个区域照射到的光线被反射进入与检测相机连接的检测镜头,1≤m<n;所述m个区域在检测相机中成像为亮区域,以所述亮区域为特征点区域;通过分析比对检测的芯片焊线的特征点区域信息与合格焊线的特征点区域信息,判断缺陷类型。

《基于Transformer的激光器芯片缺陷检测技术研究》范文

《基于Transformer的激光器芯片缺陷检测技术研究》篇一一、引言激光器芯片是现代光电技术中重要的元器件之一,其制造过程中的质量控制对产品的性能和可靠性具有至关重要的作用。

激光器芯片的缺陷检测是制造过程中的关键环节,其准确性和效率直接影响到产品的良品率和生产效率。

近年来,随着深度学习技术的发展,基于深度学习的激光器芯片缺陷检测技术已成为研究热点。

本文提出了一种基于Transformer的激光器芯片缺陷检测技术,以提高检测的准确性和效率。

二、相关技术综述2.1 激光器芯片缺陷检测的重要性激光器芯片的缺陷可能来自于制造过程中的各种因素,如材料质量、工艺控制等。

这些缺陷会对激光器芯片的性能和可靠性产生严重影响,因此,准确的缺陷检测是保证产品质量的关键环节。

2.2 传统缺陷检测方法传统的激光器芯片缺陷检测方法主要依赖于人工目视检查或使用特定的检测设备。

然而,这些方法往往存在检测速度慢、准确性低、成本高等问题。

2.3 深度学习在缺陷检测中的应用深度学习在图像处理和模式识别方面取得了显著的成果,被广泛应用于各种缺陷检测任务中。

基于深度学习的激光器芯片缺陷检测技术可以有效地提高检测的准确性和效率。

三、基于Transformer的激光器芯片缺陷检测技术3.1 Transformer模型概述Transformer是一种基于自注意力机制的深度学习模型,在自然语言处理和计算机视觉等领域取得了重要的突破。

在激光器芯片缺陷检测中,我们可以利用Transformer模型对图像进行特征提取和分类。

3.2 技术实现本技术主要包含以下几个步骤:首先,使用深度卷积神经网络对激光器芯片图像进行预处理,提取出图像中的关键特征;然后,利用Transformer模型对提取出的特征进行自注意力机制的计算,得到更加丰富的特征信息;最后,通过全连接层对特征进行分类,实现对激光器芯片缺陷的检测。

四、实验与分析4.1 实验数据集我们使用了一组包含各种类型缺陷的激光器芯片图像作为实验数据集,对基于Transformer的缺陷检测技术进行了验证。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

LED芯片封装缺陷检测方法研究

LED(Light-emitting diode)由于寿命长、能耗低等优点被广泛地应用于指示、显示等领域。

可靠性、稳定性及高出光率是LED 取代现有照明光源必须考虑的因素。

封装工艺是影响LED功能作用的主要因素之一, 封装工艺关键工序有装架、压焊、封装。

由于封装工艺本身的原因, 导致LED封装过程中存在诸多缺陷(如重复焊接、芯片电极氧化等), 统计数据显示[1-2]: 焊接系统的失效占整个半导体失效模式的比例是25%~30%, 在国内[3], 由于受到设备和产量的双重限制, 多数生产厂家采用人工焊接的方法, 焊接系统不合格占不合格总数的40%以上。

从使用角度分析, LED

封装过程中产生的缺陷, 虽然使用初期并不影响其光电性能, 但在以后的使用过程中会逐渐暴露出来并导致器件失效。

在LED的某些应用领域, 如高精密航天器材, 其潜在的缺陷比那些立即出现致命性失效的缺陷危害更大。

因此, 如何在封装过程中实现对LED 芯片的检测、阻断存在缺陷的LED进入后序封装工序, 从而降低生产成本、提高产品的质量、避免使用存在缺陷的LED造成重大损失就成为LED封装行业急需解决的难题。

当前, LED产业的检测技术主要集中于封装前晶片级的检测[4-5]及封装完成后的成品级检测[6-7], 而国内针对封装过程中LED的检测技术尚不成熟。

本文在LED芯片非接触检测方法的基础上[8-9], 在LED引脚式封装过程中, 利用p-n结光生伏特效应, 分析了封装缺陷对光照射LED芯片在引线支架中产生的回路光

电流的影响, 采用电磁感应定律测量该回路光电流, 实现LED封装过程中芯片质量及封装缺陷的检测。

1理论分析

1.1 p-n结的光生伏特效应[m]根据p-n结光生伏特效应, 光生电流IL表示为:

式中, A为p-n结面积, q是电子电量, Ln、 Lp分别为电子和空穴的扩散长度, J表示以光子数计算的平均光强, α为p-n结材料的吸收系数, β是量子产额, 即每吸收一个光子产生的电子一空穴对数。

在LED引脚式封装过程中, 每个LED芯片是被固定在引线支架上的, LED芯片经过压焊金丝(铝丝)与引线支架形成了闭合回路, 如图1。

若忽略引线支架电阻, LED支架回路光电流等于芯片光

生电流IL。

可见, 当p-n结材料和掺杂浓度一定时, 支架回路光电流与光照强度I成正比。

1.2封装缺陷机理

LED芯片受到腐蚀因素影响或沾染油污时, 在芯片电极表面

生成一层非金属膜, 产生封装缺陷[11]。

电极表面存在非金属膜层的LED芯片压焊工序后, 焊接处形成金属一介质-金属结构, 也称为隧道结。

当一定强度的光照射在LED芯片上, 若LED芯片失效, 支架回路无光电流流过若非金属膜层足够厚, 只有极少数电子能够隧穿膜层势垒, LED支架回路也无光电流流过;若非金属膜层较薄, 由于LED芯片光生电流在隧道结两侧形成电场, 电子主要以场致发射的方式隧穿膜层, 流过单位面积膜层的电流可表示为[12]。

其中q为电子电量, m为电子质量, 矗为普朗克常数, vx、vy、 vz分别是电子在x、 y、 z方向的隧穿速度, T(x)为电子的隧穿概率。

又任意势垒的电子隧穿概率可表示为[13]

其中jin、 jout。

分别是进入膜层和穿过膜层的电流密度,

, x指向为芯片电极表面到压焊点, 为膜层中z方向任意点的势垒, E是垂直芯片电极表面速度为vx电子的能量。

图2为在电场f’作用‘F芯片电极表面的势垒图, 其中EF为费米能级, U为电子发射势垒。

由图。