DDS信号发生器电路设计

DDS信号发生器设计

DDS信号发生器设计DDS(直接数字频率合成)信号发生器是一种数字技术制造高质量频率合成信号的装备。

本文将介绍DDS信号发生器的设计原理、关键技术和性能评估。

一、设计原理:DDS信号发生器的设计原理基于数字频率合成技术,其核心是数字信号处理器(DSP)和数字锁相环(PLL)。

DDS信号发生器通过频率控制字(FTW)和相位控制字(PTW)控制DDS芯片的输出频率、波形和相位。

在DDS芯片中,数字频率合成器通过数模转换器将较高的待合成信号转换为模拟信号,进而通过滤波器、放大器等模拟电路产生高质量的输出信号。

二、关键技术:1.高精度的频率合成:DDS信号发生器需要具备高精度的频率合成能力。

此需求需要DDS芯片具备较高的分辨率和较低的相位噪声。

分辨率是DDS芯片产生频率变化最小步进的能力,通常用位数来表示。

较高的分辨率可以确保DDS信号发生器输出的频率表现更加连续平滑。

相位噪声则与DDS芯片的时钟抖动、量化噪声等因素有关,较低的相位噪声能够保证信号在频谱中的纯净度。

2.高动态范围的输出:DDS信号发生器通常需要提供广泛的频率范围和大范围内的输出功率调节。

此需求需要DDS芯片具备高动态范围的输出能力。

动态范围包括频率动态范围和幅度动态范围。

频率动态范围是指DDS信号发生器能够合成的频率范围,幅度动态范围则指DDS信号发生器能够调节的输出功率范围。

通过优化DDS芯片的设计,可以提高输出的动态范围。

3.高速的输出信号更新:DDS信号发生器需要具备快速更新输出信号的能力。

通常,DDS芯片具备更高的时钟频率和更大的内存储存能力可以实现更高的输出信号更新速率。

高速更新输出信号可以保证DDS信号发生器能够满足实时调节信号的需求。

三、性能评估:DDS信号发生器的性能评估包括频率稳定度、相位噪声、调制信号质量等几个方面。

频率稳定度是指DDS信号发生器输出频率的稳定性,通常通过测量短期和长期的频率漂移来评估。

相位噪声则是度量DDS信号发生器输出信号相位纯净度的参数,使用杂散频谱测量方法和相位噪声密度谱评估。

实验五 DDS信号发生器设计

实验五DDS信号发生器的设计(1) 实验目的:学习利用EDA技术和FPGA实现直接数字频率综合器DDS的设计。

(2) 实验原理:直接数字频率综合技术,即DDS技术,是一种新型的频率合成技术和信号产生方法。

其电路系统具有较高的频率分辨率,可以实现快速的频率切换,并且在改变时能够保持相位的连续,很容易实现频率、相位和幅度的数控调制。

f SIN = M(f clk/2n)DDS基本结构相位累加器位宽和采样点关系【例11-12】LIBRARY ieee; --波形数据ROMUSE ieee.std_logic_1164.all;LIBRARY altera_mf;USE altera_mf.altera_mf_components.all;ENTITY data_rom ISPORT( address : IN STD_LOGIC_VECTOR (9 DOWNTO 0);inclock : IN STD_LOGIC ;q : OUT STD_LOGIC_VECTOR (7 DOWNTO 0) );END data_rom;. . .init_file => "./data/ rom_data.mif ", --波形数据初始化文件路径lpm_hint => "ENABLE_RUNTIME_MOD=YES, INSTANCE_NAME=rom2",. . .END;【例11-13】LIBRARY IEEE; --32位加法器模块USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY ADDER32B ISPORT ( A : IN STD_LOGIC_VECTOR(31 DOWNTO 0);B : IN STD_LOGIC_VECTOR(31 DOWNTO 0);S : OUT STD_LOGIC_VECTOR(31 DOWNTO 0) );END ADDER32B;ARCHITECTURE behav OF ADDER32B ISBEGINS <= A + B;END behav;【例11-14】--32位寄存器模块LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY REG32B ISPORT ( Load : IN STD_LOGIC;DIN : IN STD_LOGIC_VECTOR(31 DOWNTO 0);DOUT : OUT STD_LOGIC_VECTOR(31 DOWNTO 0) );END REG32B;ARCHITECTURE behav OF REG32B ISBEGINPROCESS(Load, DIN)BEGINIF Load'EVENT AND Load = '1' THEN -- 时钟到来时,锁存输入数据DOUT <= DIN;END IF;END PROCESS;END behav;【例11-15】rom_data.mif 10位正弦波数据文件,读者可用MATLAB/DSP Builder 生成 WIDTH=10;DEPTH=1024;ADDRESS_RADIX=DEC;DATA_RADIX=DEC;CONTENT BEGIN0 : 513; 1 : 515; 2 : 518; 3 : 521; 4 : 524; 5 : 527; 6 : 530; 7 : 533; 8 : 537; 9 : 540; 10 : 543; 11 : 546; 13 : 549; 13 : 552; 14 : 555;. . . . . .(略去部分数据)1018 : 493; 1019 : 496; 1020 : 499; 1021 : 502; 1022 : 505; 1023 : 508; END;(3) 实验内容1:详细述叙DDS 的工作原理,依据例11-12至例11-15完成仿真,并由仿真结果进一步说明DDS 的原理。

实验六 DDS信号发生器设计

实验五DDS信号发生器设计一.实验目的:学习利用EDA技术和FPGA实现直接数字频率综合器DDS的设计。

二.实验设备:1.电脑,quartus ii 集成开发环境2.GX_SOPC_EP3C10_EDK系统三.实验实训要求1.使用quartus ii 集成开发环境完成直接数字频率综合器DDS的设计2.利用GX_SOPC_EP3C10_EDK系统和电脑完成实验并观察波形四.实验原理:参考6.12节。

图6-72是根据图6-71的基本DDS原理框图作出的电路原理图的顶层设计,其中相位累加器的位宽是32。

图中共有六组元件模块和一些接口,说明如下:图6-72 DDS信号发生器顶层原理图(1) 32位加法器ADDER32。

由LPM_ADD_SUB宏模块构成。

设置了2级流水线结构,使其在时钟控制下有更高的运算速度和输入数据稳定性。

(2) 32位寄存器DFF32。

由LPM_FF宏模块担任。

ADDER32与DFF32构成一个32位相位累加器,其高8位A[31..24]作为波形数据ROM的地址。

(3) 正弦波形数据ROM。

正弦波形数据ROM模块sin_8X8的地址线和数据线位宽都是8位。

这就是说,其中的一个周期的正弦波数据有256个,每个数据有8位。

其输出可以接一个8位的高速DAC。

ROM中的MIF数据文件可用专用软件工具获得,这里不再深入探讨。

(4) 频率控制字输入B[20..17]由计数器CNT4B产生。

本来的频率控制字是32位的,但为了方便实验验证,把高于20和低于17的输入位预先设置成0或1。

频率控制字B[31..0]与由DAC[7..0]驱动的DAC 的正弦信号频率的关系,可以由公式CLK out f B f 322]0..31[ 算出。

其中f out 为DAC 输出的正弦波信号频率,f clk 是CLK 的时钟频率,直接输入是50MHz ,接入锁相环后可达到更高频率。

频率上限要看DAC 的速度。

如果接高速DAC ,如10位的5651,输出速度可达180MHz 。

基于DSP的DDS信号发生器硬件设计电路图

---------------------------------------------------------------范文最新推荐------------------------------------------------------ 基于DSP的DDS信号发生器硬件设计+电路图摘要在21世纪的今天,基于DSP的信号发生器以其编程的高度灵活性,波形的高精度与高稳定性等特点而脱颖而出,具有极大的应用价值和广泛的应用前景。

本文利用高性能DSP芯片加上合理的外围控制电路构成基于DSP的DDS信号发生器,完成电压监测电路的硬件设计工作。

通过对DDS的相应介绍采用查表法实现正弦波的产生,采用高速微处理器实现DDS。

然后完成硬件芯片的选型(TMS320LF2407)和硬件电路的设计工作。

硬件设计主要有核心控制模块电路、片选电路、串行通信电路、AD转换电路及信号采集电路,以此实现硬件电路完成接收上位机的控制信号,采集外部电压信号处理后送给上位机,实现对电压的监控。

关键词:信号发生器,DDS,电压监控,硬件设计11870毕业设计说明书(论文)外文摘要1 / 10TitleDDS signal generator hardware design based on DSPAbstractIn the 21st century,the DSP signal generator stand out for its high degree of flexibility of the programming waveforms, high precision and high stability characteristics, shows great value and broad application prospects.This article takes use of high performance DSP chip with peripheral control circuit DSP-based DDS signal generator,complete the hardware design of the voltage monitoring circuit.Achieve the generation of sine wave with look-up table method corresponding introduction of DDS.Then complete selection of hardware chip(TMS320LF2407)and hardware design.The hardware design mainly consists of core control module circuit, chip select circuit, the serial communication circuit, AD converter circuit and the signal acquisition circuit,In order to achieve the hardware circuit to complete the PC to receive the control signal.The acquisition of an external---------------------------------------------------------------范文最新推荐------------------------------------------------------voltage signal processing to give the host computer,in order to monitoring the voltage.Key words: signal generator,DDS,voltage monitoring,hardware design4.4 PC机与DSP的点对点的串行通信接口244.5 输入输出接口254.5.1A/D的接口254.5.2电压信号采样电路265电路设计中注意的问题28致谢30参考文献313 / 10附录硬件电路原理图321 绪论1.1 信号发生器简介信号发生器又称信号源或振荡器,在生产实践和科技领域中有着广泛的应用。

DDS信号发生器设计

实验12-9. DDS信号发生器设计程序设计与硬件实验

AD_DA板与FPGA EP1C6/12接口原理图详细说明可参考《SOPC_EDA实验讲义》

AD_DA板与FPGA EP1C3接口原理图详细说明可参考《SOPC_EDA实验讲义》

位频率控制字,

、键1给出

相位控制字,已在程序中预设

32Pin RAM/ROM与FPGA接口原理图

详细说明可参考《SOPC_EDA实验讲义》

模式1的电路结构

选择模式1

时钟选择Clock5=20MHz 打开+/-12V电源

32Pin RAM/ROM与FPGA接口原理图

详细说明可参考《SOPC_EDA实验讲义》

接示波器Y2端

接示波器Y1端

短路帽向下接:

时钟选择Clock5=20MHz

K X 康芯科技FWORD 是8位频率控制字,由模式1的键2、键1给出

数码管2/1显示键2/1给出的频率字11H

K X康芯科技

示波器波形

位频率控制字,

的键2、键1给出

K X SignalTapII设置。

DDS信号发生器实验报告含原理图PCB和代码

电子信息技术综合实训报告格式竞赛题名称:《DDS信号发生器的设计》队员名称:评阅人签名:2012年9月15日1、设计思路描述:本设计是一个以AT89C51单片机为核心基于DAC0832芯片的DDS信号发生器。

信号发生器采用数字波形合成技术,通过硬件电路和软件程序相结合,可输出正弦波和三角波,波形的转换可通过软件控制。

本设计通过按键选择波形,经过AT89C51单片机将数据输出到DAC0832,由数字信号转变为模拟信号,再通过运放器稳定地输出到示波器上。

原理框图如下:2、硬件电路图:DAC0832是采样频率为八位的D/A转换器件,芯片内有两级输入寄存器,使DAC0832具备双缓冲、单缓冲和直通三种输入方式,以便适于各种电路的需要(如要求多路D/A异步输入、同步转换等)。

D/A转换结果采用电流形式输出。

要是需要相应的模拟信号,可通过一个高输入阻抗的线性运算放大器实现这个供功能。

运放的反馈电阻可通过RFB端引用片内固有电阻,还可以外接。

该片逻辑输入满足TTL电压电平范围,可直接与TTL电路或微机电路相接。

下面是DAC0832引脚图和内部结构电路图DAC0832引脚功能说明:DI0~DI7:数据输入线,TLL电平。

ILE:数据锁存允许控制信号输入线,高电平有效。

CS:片选信号输入线,低电平有效。

WR1:为输入寄存器的写选通信号。

XFER:数据传送控制信号输入线,低电平有效。

WR2:为DAC寄存器写选通输入线。

Iout1:电流输出线。

当输入全为1时Iout1最大。

Iout2: 电流输出线。

其值与Iout1之和为一常数。

Rfb:反馈信号输入线,芯片内部有反馈电阻。

Vcc:电源输入线 (+5v~+15v)Vref:基准电压输入线 (-10v~+10v)AGND:模拟地,摸拟信号和基准电源的参考地。

DGND:数字地,两种地线在基准电源处共地比较好。

主控电路及数模转换电路分别如下:主控电路数模转换电路3软件流程图:4测试方法描述:运用proteus软件设计好电路图,将程序代码编译好以后载入proteus中的AT89C51芯片进行仿真。

DDS信号发生器设计

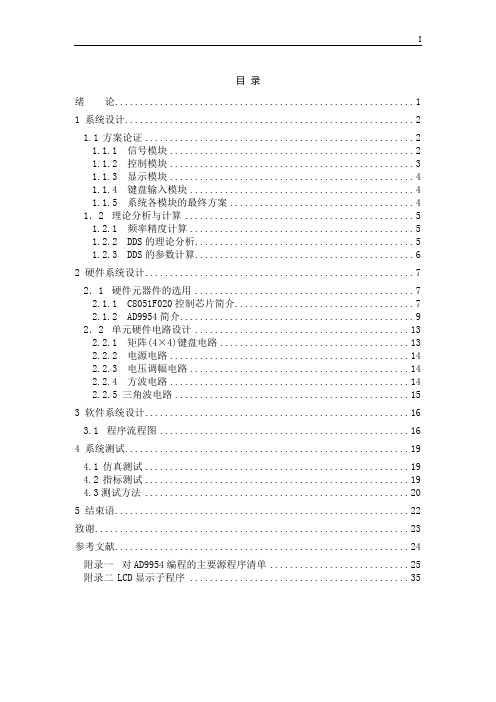

目录绪论 (1)1 系统设计 (2)1.1方案论证 (2)1.1.1 信号模块 (2)1.1.2 控制模块 (3)1.1.3 显示模块 (4)1.1.4 键盘输入模块 (4)1.1.5 系统各模块的最终方案 (4)1.2理论分析与计算 (5)1.2.1 频率精度计算 (5)1.2.2 DDS的理论分析 (5)1.2.3 DDS的参数计算 (6)2 硬件系统设计 (7)2.1硬件元器件的选用 (7)2.1.1 C8051F020控制芯片简介 (7)2.1.2 AD9954简介 (9)2.2单元硬件电路设计 (13)2.2.1 矩阵(4×4)键盘电路 (13)2.2.2 电源电路 (14)2.2.3 电压调幅电路 (14)2.2.4 方波电路 (14)2.2.5 三角波电路 (15)3 软件系统设计 (16)3.1程序流程图 (16)4 系统测试 (19)4.1仿真测试 (19)4.2指标测试 (19)4.3测试方法 (20)5 结束语 (22)致谢 (23)参考文献 (24)附录一对AD9954编程的主要源程序清单 (25)附录二LCD显示子程序 (35)摘要:随着数字集成电路、微电子技术和EDA技术的深入研究,DDS技术以其有别于其它频率合成技术的优越性能和特点,成为现代频率合成技术中的佼佼者。

根据题目要求,我们以单片机C8051F020芯片和AD9954芯片为核心,辅以必要的模拟电路,设计一台信号发生器,使之能产生正弦波、方波和三角波。

该系统主要由控制模块、信号模块、显示模块、键盘输入模块构成。

仅用单片AD9954就实现了直接数字频率合成技术(DDS),产生稳幅正弦波。

输出的正弦波经过比较电路来实现方波的输出,而三角波则是在方波的基础上通过接入积分电路来实现的。

单片机对内部寄存器控制,AD9954就可以产生一个频谱纯净、频率和相位都可编程控制且稳定性很好的模拟波形,整个系统结构紧凑,电路简单,功能强大,可扩展性强。

DDS信号发生器设计

DDS信号发生器设计DDS(Direct Digital Synthesis)信号发生器是一种数字信号发生器,通过数字方式产生任意频率、任意波形的信号。

在信号处理中,DDS信号发生器具有重要的作用,例如在通信系统、音频信号生成、测试测量仪器等领域都需要使用到DDS信号发生器。

DDS信号发生器基本原理是通过数字的方式产生一个频率为Fs的正弦波,然后对该正弦波进行相位和幅度的调制,从而得到所需要的信号。

具体来说,DDS信号发生器主要由相位累加器、相位查找表、数字控制振荡器(NCO)以及低通滤波器等组成。

首先是相位累加器,它主要用于产生相位信息。

通过一个计时器不断累加一个步进量,得到一个连续变化的相位值。

相位累加器的工作原理是通过一个加法器加上步进量,然后将结果输出给相位查找表。

接下来是相位查找表,它主要用于存储正弦波的值。

相位查找表中存储了一个完整周期的正弦波值,根据相位累加器的输出值,可以从相位查找表中读取相应的正弦波值。

然后是数字控制振荡器(NCO),它主要用于控制频率。

通过调整相位累加器的步进量,可以改变输出信号的频率。

当相位累加器的步进量为1时,输出信号的频率为Fs。

当步进量为2时,输出信号的频率为Fs/2,以此类推。

最后是低通滤波器,它主要用于去除由于相位调制引起的高频成分。

由于DDS信号发生器在频率上是离散的,会产生一些高频的杂散信号。

通过使用低通滤波器,可以去除这些高频成分,得到我们所需要的信号。

综上所述,DDS信号发生器通过数字方式产生信号,具有灵活性高、调制精度高的优点。

在DDS信号发生器的设计中,需要注意一些关键参数的选择,例如采样率、分辨率、时钟稳定性等。

此外,还需要注意信号输出的波形质量、相位噪声、非线性失真等指标的优化。

在实际应用中,DDS信号发生器通常需要结合外部DAC(数字模拟转换器)芯片进行实现。

DAC芯片将数字信号转换为模拟信号,从而输出到各种应用中。

总而言之,DDS信号发生器是一种重要的数字信号发生器,通过数字方式产生任意频率、任意波形的信号。

基于DDS技术的信号发生器的设计与实现

基于DDS技术的信号发生器的设计与实现DDS(Direct Digital Synthesis,直接数字合成)技术是一种通过数字方式产生任意波形信号的技术。

DDS信号发生器是一种能够产生可控频率、幅度和相位的信号的设备。

本文将介绍基于DDS技术的信号发生器的设计与实现。

首先,信号发生器的核心部件是DDS芯片。

DDS芯片是一种集成电路,能够通过数字方式产生任意波形信号。

它包含一个相位累加器和一个查找表。

相位累加器用于生成连续的相位值,而查找表则用于根据相位值输出相应的幅度值。

通过不断更新相位累加器的数值,就可以产生连续的信号。

然后,需要一个高性能的时钟源来提供DDS芯片所需的时钟信号。

一般使用晶振来提供稳定的时钟信号。

时钟信号的频率决定了DDS芯片所能产生的最高频率。

因此,选择合适的晶振对于信号发生器的性能和稳定性至关重要。

接下来,需要设计一个控制电路来控制DDS芯片的工作模式。

控制电路可以通过按键、旋钮或者电脑串口等方式与用户进行交互。

用户可以通过控制电路设定信号的频率、幅度和相位等参数。

控制电路接收用户输入的数据,并将数据传输给DDS芯片进行处理。

在实现过程中,还需要一块数模转换器(DAC)将DDS芯片输出的数字信号转换为模拟信号。

DAC负责将DDS芯片输出的数字信号转换为与之对应的模拟信号。

数模转换的精度直接影响信号发生器的性能,因此需要选择高性能的DAC。

最后,可以通过一个显示屏显示当前信号的频率、幅度和相位等参数。

显示屏可以直接与控制电路相连,通过控制电路获取当前信号的参数,并将参数显示在屏幕上。

这样用户可以直观地了解当前信号的状态。

总结起来,基于DDS技术的信号发生器的设计与实现包括选择合适的DDS芯片、时钟源和DAC,设计控制电路和显示屏,并将各部件进行连接。

通过这些步骤可以实现一个功能完善的信号发生器,能够产生任意波形信号,并提供简单的用户界面进行参数设置和显示。

基于DDS的信号发生器设计

基于DDS的信号发生器设计一、引言信号发生器是电子测量仪表中常见的一种设备,用于产生具有不同特性的信号,以便在各种实验、测试和校准工作中使用。

传统的信号发生器通常通过模拟电路来实现,但由于其受到尺寸、可调性和稳定性等限制,逐渐被数字信号发生器(DDS)所取代。

DDS信号发生器利用数字技术直接生成信号,具有调频范围广、频率稳定度高、精度高等优点。

二、DDS技术原理DDS技术(Direct Digital Synthesis,直接数字合成)是一种通过数字信号直接合成模拟信号的技术,它将数字信号与时钟同步,并通过数模转换得到模拟信号。

DDS技术的实现核心是相位累加器、数控振荡器和数模转换器。

相位累加器用于累加相位值,数控振荡器通过相位值生成相应频率的信号,而数模转换器将生成的数字信号转换为模拟信号。

基于DDS的信号发生器可以通过使用FPGA(Field Programmable Gate Array)和AD(Analog Devices)公司的AD9854芯片来实现。

使用FPGA实现相位累加器和控制逻辑,AD9854负责生成模拟信号。

下面是基于DDS的信号发生器的设计步骤:1.系统架构设计DDS信号发生器可分为控制模块、相位累加模块、频率累加模块和数模转换模块。

控制模块负责接收用户输入的参数,并控制相位、频率等;相位累加模块负责相位的累加和输出;频率累加模块负责频率的累加和输出;数模转换模块负责将数字信号转换为模拟信号。

2.相位累加模块设计相位累加器使用FPGA中的计数器模块实现。

设置计数器的位宽,根据所需的相位分辨率来确定。

通过改变计数器的初始值和计数步长,可以实现相位的变化。

3.频率累加模块设计频率累加器使用FPGA中的加法器模块实现。

根据所需的频率范围和分辨率,对加法器的输入信号进行控制,实现频率的变化。

4.数模转换器设计AD9854芯片负责将数字信号转换为模拟信号。

将FPGA中的数字信号输入AD9854中,经过数模转换后输出模拟信号。

基于DDS的移相正弦信号发生器设计

基于DDS 的移相正弦信号发生器设计一.设计原理1.1 利用DDS 产生正弦波信号的工作原理由DDS 产生频率、相位可控制的正弦波。

频率累加器对输入信号进行累加运算,产生频率控制数据M( 或相位步进量)。

读出的数据送入D/A 转换器和低通滤波器以恢复实际波形。

频率控制字M 和相位控制字分别控制DDS 输出正(余)弦的频率和相位。

DDS 系统的核心是相位累加器,它由一个累加器和一个N 位相位寄存器组成。

每来一个时钟脉冲,相位寄存器以步长M 增加。

相位寄存器的输出与相位控制字相加,其结果作为正(余)弦查找表的地址。

ROM 查找表中储存着一个完整周期的正弦波数字幅度信息,,每个查找表的地址对应正弦波中O 一360度范围中的一个相位点。

ROM 查找表把输入的地址信息映射成正(余)弦幅度信号,同时输出数模转换器(DAC)的输入端,DAC 输出的模拟信号经过低通滤波器(LPF),可得到一个频谱纯净的正(余)弦波。

从而实现正弦波信号的产生。

直接数字合成DDS 的可移相数字信号发生器原理图:1.2 DDS 的数字移相原理DDS 技术的核心是相位累加器,它类似一个计数器. 每来一个时钟信号,相位累加器的输出就增加一个步长的相位增量,相位增量的大小由频率控制字确定. 经DDS 输出的信号可描述为)2sin()sin(t f A wt A S out out π== (1)其中, Sout 为经DDS 输出的信号,fout 为对应的输出频率,时间t 是连续的。

为便于数字逻辑描述该表达式,需进行离散化处理,用基准时钟信号clk 进行抽样,设正弦信号的相位φ= 2πfout t ,而在一个时钟周期Tclk 相位φ变化量为clk out clk out f f T f ππφ22==∆ (2) 式(2)中, fclk 是clk 的频率,对于2π可以看成是满相位的1为了对输出的相位进行控制,通过一个常数P 来实现,而每个clk 周期的相位增量Δθ用P 来表示,即Δθ= P ·Δφ式1 与式(2) 联立可得clkout f f P πθ2⋅=∆ (3) 显然,信号发生器的输出可描述为)sin().sin(θφφφ∆+=∆+=A p A S out上式中,φ代表正弦信号发生器原始相位值,可看出,对相位值进行简单的累加运算,就可以得到正弦信号当前相位值,也就得到了DDS 输出的正弦信号。

基于DDS信号发生器的设计

基于DDS信号发生器的设计基于DDS(Direct Digital Synthesis)信号发生器的设计是一种使用数字技术生成模拟信号的方法。

DDS信号发生器采用数字频率合成技术,具有频率范围广、频率分辨率高、频率稳定性好等优点,被广泛应用于通信、测量、无线电频率合成等领域。

在本文中,将详细介绍基于DDS信号发生器的设计方案。

一、DDS信号发生器的基本原理DDS信号发生器利用数字技术生成模拟信号,主要由时钟、相位累加器(Phase Accumulator)、相位调制器(Phase Modulator)和数模转换器(Digital-to-Analog Converter)等部分组成。

其基本原理如下:1.时钟:提供稳定的时钟信号,作为DDS信号发生器的时间基准。

2.相位累加器:接收时钟信号,用于累加相位增量,并生成数字相位信息。

3.相位调制器:将数字相位信息转换为模拟的、连续的相位信息。

4.数模转换器:将相位信息转换为模拟信号,并提供给外部使用。

二、基于DDS信号发生器的设计方案1.频率范围:DDS信号发生器的频率范围应满足实际应用需求。

一般DDS芯片的频率范围为几千Hz到几百兆Hz,可以选择适当的芯片。

2.频率分辨率:DDS信号发生器的频率分辨率应足够高,能够满足对精细频率调整的需求。

一般DDS芯片的频率分辨率为1Hz或更高。

3.频率稳定性:DDS信号发生器的频率稳定性应较高,能够保证频率输出的准确性和稳定性。

可以通过选择高质量的时钟源来提高频率稳定性。

4.输出波形:DDS信号发生器可以生成多种波形,如正弦波、方波、三角波、锯齿波等。

设计时应根据应用需求选择适合的波形。

5.控制接口:DDS信号发生器通常需提供控制接口,如USB、串口、以太网等,方便用户对信号发生器进行控制和调整。

设计方案可以按以下步骤进行:1.选择DDS芯片:根据需求选择合适的DDS芯片,如AD9850、AD9833等。

2.系统架构设计:根据芯片和性能要求设计系统架构,包括时钟源、数模转换器、滤波电路等。

DDS信号发生器电路设计方案

DDS信号发⽣器电路设计⽅案DDS信号发⽣器电路设计⽅案1、了解电⼦电路设计的⼀般⽅法、根据题⽬要求选择设计⽅案。

2、根据理论计算分析,查阅相关资料和⼿册,选择电⼦元器件。

3、学会使⽤电⼦设计⾃动化软件对电路进⾏设计、分析、验证。

利⽤可编程逻辑器件实现电路的设计、仿真、下载。

4、熟练使⽤常⽤电⼦仪器(⽰波器、万⽤表、信号发⽣器等)对电路进⾏测试。

5、写出符合要求的课程设计报告。

⼀、实验设备1、Altera DE2开发板 (CycloneⅡ EP2C35F672C6)2、QuartusⅡ9.1开发软件3、数字电路实验⾯包板4、⽰波器、万⽤表等⼆、实验任务要求利⽤DE2实验开发装置,在给定电源条件下,完成正弦波信号发⽣器电路设计。

1、技术指标①信号频率输出围50Hz~10kHz,频率可调。

步进调整,步长0.5Hz或50Hz;②频率稳定度10-3。

2、发挥部分①增加脉冲信号的输出,信号频率输出围50Hz~10kHz;②脉冲信号占空⽐可调,调整围2%~98%;③正弦或脉冲频率步长调整分别为1Hz、10Hz、100Hz、1kHz、10kHz;④完成在数码管上数字频率显⽰功能;三、实验原理介绍1、DDS直接数字合成(Direct Digital Synthesis、DDS)是⼀种新的频率合成技术和信号产⽣的⽅法。

直接数字频率合成器(DDS)具有超⾼速的频率转换时间,极⾼的频率分辨率和较低的相位噪声,在频率改变与调频时,DDS 能够保持相位的连续,因此很容易实现频率、相位和幅度调制。

此外,DDS 技术⼤部分是基于数字电路技术的,具有可编程控制的突出优点。

因此这种信号产⽣技术得到了越来越⼴泛的应⽤,很多⼚家已经⽣产出了DDS专⽤芯⽚,这种器件成为当今电⼦系统及设备中频率源的⾸选器件。

2、相位累加器⼀个正弦波,虽然它的幅度不是线性的,但是它的相位却是线性增加的。

DDS利⽤了这⼀特点来产⽣正弦信号。

根据DDS的频率控制字M的位数N,把360°平均分成了2的N次等份。

基于dds技术的信号发生器设计与实现

基于dds技术的信号发生器设计与实现基于DDS技术的信号发生器设计与实现1、引言信号发生器是电子测试与测量领域中的重要仪器之一,用于产生各种形式的信号,以供电子设备的测试、校准和研发使用。

传统的信号发生器通常采用模拟电路设计,存在精度不高、调节麻烦等问题。

而基于Direct Digital Synthesis (DDS) 技术的信号发生器,能够以数字方式生成精确的任意波形信号,具备灵活性、精度高、调节方便等特点。

本文将重点探讨基于DDS技术的信号发生器的设计与实现。

2、DDS技术原理DDS技术是一种通过数字方式生成任意波形信号的技术,其核心是一个快速数字频率合成器 (NCO)。

NCO通过参考频率和累加器的相位变化,生成具有不同频率、相位和幅度的数字信号,然后通过数字模拟转换器 (DAC) 将数字信号转换为模拟信号输出。

DDS技术的关键在于通过调整参考频率和相位累加器的步进值,可以在很短的时间内生成高精度和高稳定度的任意波形信号。

3、基于DDS技术的信号发生器设计在设计基于DDS技术的信号发生器时,需要考虑以下几个关键要素:3.1 参考频率参考频率是DDS信号发生器中的基准频率,它决定了信号发生器能够产生的最高频率。

通常选择一个稳定、精确的参考时钟作为参考频率源,这可以是一个稳定的晶振或者其他同步源。

参考频率的选择应当考虑设备的应用场景,以及对生成信号频率范围和分辨率的需求。

3.2 相位累加器相位累加器是DDS技术中的核心组成部分,它记录了信号的相位信息,并根据参考频率的步进值来更新相位。

相位累加器的位宽决定了相位分辨率,位宽越高,相位分辨率越高,生成的信号表现越精细。

相位累加器的更新速度也决定了信号发生器的输出速率,更新速度越快,信号发生器的输出频率范围越大。

3.3 数字模拟转换器DDS技术生成的是数字信号,因此需要通过数字模拟转换器将数字信号转换为模拟信号输出。

DAC的精度和速度决定了信号发生器的输出质量和速率。

DDS函数信号发生器的设计

DDS函数信号发生器的设计第一篇:DDS函数信号发生器的设计DDS函数信号发生器的设计、仿真及下载一、实验设计① 利用DDS(Direct DIgital Frequency Synthesis,即直接数字频率合成)技术产生稳定的正弦波,三角波和方波输出,输出频率为10~1000kHz且频率可调,步进为10Hz,1kHz,10kHz,100kHz。

② 用VerilogHDL进行建模和模拟仿真,再利用FPGA进行实现D/A转换。

③ 下载到DE0板上利用VGA端口的一个四位孔进行A/D转换显示在示波器上。

二、实验原理一个直接数字频率合成器由相位累加器、波形ROM、D/A转换器和低通滤波器构成。

DDS的原理框图如下所示:图 1 直接数字频率合成器原理图其中K为频率控制字,fc为时钟频率,N为相位累加器的字长,D为ROM数据位及D/A转换器的字长。

相位累加器在时钟 fc的控制下以步长K作为累加,输出N位二进制码作为波形ROM的地址,对波形ROM进行寻址,波形ROM输出的幅码S(n)经D/A转换器变成梯形波S(t),再经低通滤波器平滑后就可以得到合成的信号波形了。

合成的信号波形形状取决于波形ROM中存放的幅码,因此用DDS可以产生任意波形。

【来自百度】本设计中直接利用DE0开发板通过D/A转换得到输出波形,省略了低通滤波器这一环节。

DDS工作流程示意图:DDS的具体实现框图:三、实验内容:1、相位累加器和数据锁存器的设计本设计采用模24的二进制累加器和寄存器,其中累加器和寄存器在一个模块中,只取锁存数据的高十位作为查表的地址值。

//地址计数器模块;module counter(clk,fre_word,address);input clk;//声明系统时钟为clkinput [23:0] fre_word;//声明24为频率控制字output reg [9:0] address;reg [23:0] phaseadder;always @(posedge clk)beginphaseadder=phaseadder+fre_word;address=phaseadder[23 :14];//地址取输出锁存后十位(对应波形为一个周期取1024点)end endmodule2、波形存储器设计本设计要求DDS系统能输出方波、三角波及正弦波三种波形。

基于DDS的信号发生器设计

基于DDS的信号发生器设计基于DDS(Direct Digital Synthesis,直接数字合成)的信号发生器是一种数字技术信号发生器,利用计算机和高速数字转换器(DAC)以及DDS芯片来合成各种频率和幅度的信号。

DDS信号发生器具有频率精度高、频率调谐范围宽、频率稳定性好、相位噪声低等优点,被广泛应用于通信、电子测试、音频设备等领域。

一、DDS信号发生器的基本原理DDS信号发生器的基本原理是通过将一个稳定的参考时钟信号输入到DDS芯片中,在芯片内部进行数字信号处理,得到所需的频率、相位和振幅信息后,通过DAC转换成模拟信号输出。

其基本流程如下:1.参考时钟信号:DDS信号发生器的核心是DDS芯片,其工作稳定性依赖于参考时钟信号的精度和稳定性,通常使用TCXO(温控振荡器)或OCXO(温控晶体振荡器)等高稳定性时钟源作为参考时钟信号。

2.预分频器:参考时钟信号通过预分频器进行分频,得到基准频率。

3.相位累加器:基准频率经过相位累加器进行相位调整,实现频率的精确控制。

相位累加器的输入为一个相位累加器寄存器,该寄存器主要用于存储相位累加的数值,相位累加器以一定步长累加,每累加一次产生的相位对应一个时钟周期。

4.数字正弦曲线生成器:相位累加器产生的相位信息通过数字正弦曲线生成器生成对应的幅度信息,通常采用查表法实现。

5.数字控制振幅器:数字正弦曲线生成器产生的幅度信息经过数字控制振幅器进行振幅调整,得到最终的幅度信息。

6.高速DAC:数字振幅信息通过高速DAC转换成模拟信号输出,DAC 的速度和分辨率决定了信号发生器的输出品质。

7.滤波器:由于DAC输出是离散的,需要通过滤波器对其进行滤波,以去除高频成分和伪像,得到平滑的连续信号。

二、基于DDS的信号发生器设计思路在设计基于DDS的信号发生器时,需要考虑以下几个关键问题:1.DDS芯片选择:选择合适的DDS芯片作为信号发生器的核心,要考虑芯片的性能、频率范围、精度等因素。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1. 信号产生部分

1.1 频率控制字输入模块

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

use ieee.std_logic_arith.all;

entity ddsinput is

port(a,b,c,clk,clr:in std_logic;

q1,q2,q3,q4,q5:buffer unsigned(3 downto 0));

end ddsinput;

architecture a of ddsinput is

signal q:std_logic_vector(2 downto 0);

begin

q<=c&b&a;

process(cp,q,clr)

begin

if clr='1'then q1<="0000";q2<="0000";q3<="0000";q4<="0000";q5<="0000"; elsif clk 'event and clk='1'then

DDS信号信号发生器电路设计

case q is

when"001"=>q1<=q1+1;

when"010"=>q2<=q2+1;

when"011"=>q3<=q3+1;

when"100"=>q4<=q4+1;

when"101"=>q5<=q5+1;

when others=>NULL;

end case;

end if;

end process;

end a;

1.2 相位累加器模块

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

use ieee.std_logic_arith.all;

entity xiangwei is

port(m:in std_logic_vector(19 downto 0);

clk,clr:in std_logic;

data:out std_logic_vector(23 downto 0)); end xiangwei;

architecture a of xiangwei is

signal q:std_logic_vector(23 downto 0);

begin

process(clr,clk,m,q)

begin

if clr='1'then q<="000000000000000000000000"; elsif (clk'event and clk='1')then

q<=q+m;

end if;

data<=q;

end process;

end a;

向学壮201308354020

2. ROM数据存储器

3. 数码管显示部分

3.1 七段数码管显示模块

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL ;

ENTITY led7seg_1 IS

PORT ( A : IN STD_LOGIC_VECTOR(1 DOWNTO 0);

LED7S : OUT STD_LOGIC_VECTOR(12 DOWNTO 0) ) ; END ;

DDS信号信号发生器电路设计

ARCHITECTURE one OF led7seg_1 IS

BEGIN

PROCESS( A )

BEGIN

CASE A IS

WHEN "00" => LED7S <= "0000000011111";

WHEN "01" => LED7S <= "0100100011111";

WHEN "10" => LED7S <= "1111001011111";

WHEN "11" => LED7S <= "0010010011111";

WHEN OTHERS => NULL ;

END CASE ;

END PROCESS ;

END ;

4. 总电路图

a,b,c是改变波形频率

key_1选择波形,有锯齿波、三角波、方波、正弦波。

向学壮201308354020 锯齿波

三角波

方波

DDS信号信号发生器电路设计正弦波。